ATMEL AT91SAM9260 User Manual

BDTIC www.bdtic.com/ATMEL

Features

•Incorporates the ARM926EJ-S™ ARM® Thumb® Processor

–DSP Instruction Extensions, ARM Jazelle® Technology for Java® Acceleration

–8-KByte Data Cache, 8-KByte Instruction Cache, Write Buffer

–200 MIPS at 180 MHz

–Memory Management Unit

–EmbeddedICE™, Debug Communication Channel Support

•Additional Embedded Memories

–One 32 KByte Internal ROM, Single-cycle Access At Maximum Matrix Speed

–Two 4 KByte Internal SRAM, Single-cycle Access At Maximum Matrix Speed

•External Bus Interface (EBI)

–Supports SDRAM, Static Memory, ECC-enabled NAND Flash and CompactFlash®

•USB 2.0 Full Speed (12 Mbits per second) Device Port

–On-chip Transceiver, 2,432-byte Configurable Integrated DPRAM

•USB 2.0 Full Speed (12 Mbits per second) Host Single Port in the 208-lead PQFP Package and Double Port in 217-ball LFBGA Package

–Single or Dual On-chip Transceivers

–Integrated FIFOs and Dedicated DMA Channels

•Ethernet MAC 10/100 Base T

–Media Independent Interface or Reduced Media Independent Interface

–28-byte FIFOs and Dedicated DMA Channels for Receive and Transmit

•Image Sensor Interface

–ITU-R BT. 601/656 External Interface, Programmable Frame Capture Rate

–12-bit Data Interface for Support of High Sensibility Sensors

–SAV and EAV Synchronization, Preview Path with Scaler, YCbCr Format

•Bus Matrix

–Six 32-bit-layer Matrix

–Boot Mode Select Option, Remap Command

•Fully-featured System Controller, including

–Reset Controller, Shutdown Controller

–Four 32-bit Battery Backup Registers for a Total of 16 Bytes

–Clock Generator and Power Management Controller

–Advanced Interrupt Controller and Debug Unit

–Periodic Interval Timer, Watchdog Timer and Real-time Timer

•Reset Controller (RSTC)

–Based on a Power-on Reset Cell, Reset Source Identification and Reset Output Control

•Clock Generator (CKGR)

–Selectable 32,768 Hz Low-power Oscillator or Internal Low Power RC Oscillator on Battery Backup Power Supply, Providing a Permanent Slow Clock

–3 to 20 MHz On-chip Oscillator, One up to 240 MHz PLL and One up to 130 MHz PLL

•Power Management Controller (PMC)

–Very Slow Clock Operating Mode, Software Programmable Power Optimization Capabilities

–Two Programmable External Clock Signals

•Advanced Interrupt Controller (AIC)

–Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

–Three External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt Protected

AT91 ARM

Thumb

Microcontrollers

AT91SAM9260

Summary

6221HS–ATARM–31-Jan-08

•Debug Unit (DBGU)

–2-wire UART and Support for Debug Communication Channel, Programmable ICE Access Prevention

•Periodic Interval Timer (PIT)

–20-bit Interval Timer plus 12-bit Interval Counter

•Watchdog Timer (WDT)

–Key-protected, Programmable Only Once, Windowed 16-bit Counter Running at Slow Clock

•Real-time Timer (RTT)

–32-bit Free-running Backup Counter Running at Slow Clock with 16-bit Prescaler

•One 4-channel 10-bit Analog-to-Digital Converter

•Three 32-bit Parallel Input/Output Controllers (PIOA, PIOB, PIOC)

–96 Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os

–Input Change Interrupt Capability on Each I/O Line

–Individually Programmable Open-drain, Pull-up Resistor and Synchronous Output

–High-current Drive I/O Lines, Up to 16 mA Each

•Peripheral DMA Controller Channels (PDC)

•One Two-slot MultiMedia Card Interface (MCI)

–SDCard/SDIO and MultiMediaCard™ Compliant

–Automatic Protocol Control and Fast Automatic Data Transfers with PDC

•One Synchronous Serial Controller (SSC)

–Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

–I²S Analog Interface Support, Time Division Multiplex Support

–High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

•Four Universal Synchronous/Asynchronous Receiver Transmitters (USART)

–Individual Baud Rate Generator, IrDA® Infrared Modulation/Demodulation, Manchester Encoding/Decoding

–Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

–Full Modem Signal Control on USART0

•Two 2-wire UARTs

•Two Master/Slave Serial Peripheral Interfaces (SPI)

–8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

–Synchronous Communications

•Two Three-channel 16-bit Timer/Counters (TC)

–Three External Clock Inputs, Two Multi-purpose I/O Pins per Channel

–Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

–High-Drive Capability on Outputs TIOA0, TIOA1, TIOA2

•One Two-wire Interface (TWI)

–Master, Multi-master and Slave Mode Operation

–General Call Supported in Slave Mode

•IEEE® 1149.1 JTAG Boundary Scan on All Digital Pins

•Required Power Supplies:

–1.65V to 1.95V for VDDBU, VDDCORE and VDDPLL

–1.65V to 3.6V for VDDIOP1 (Peripheral I/Os)

–3.0V to 3.6V for VDDIOP0 and VDDANA (Analog-to-digital Converter)

–Programmable 1.65V to 1.95V or 3.0V to 3.6V for VDDIOM (Memory I/Os)

•Available in a 208-lead PQFP Green and a 217-ball LFBGA Green Package

2 AT91SAM9260

6221HS–ATARM–31-Jan-08

AT91SAM9260

AT91SAM9260

1. Description

The AT91SAM9260 is based on the integration of an ARM926EJ-S processor with fast ROM and RAM memories and a wide range of peripherals.

The AT91SAM9260 embeds an Ethernet MAC, one USB Device Port, and a USB Host controller. It also integrates several standard peripherals, such as the USART, SPI, TWI, Timer Counters, Synchronous Serial Controller, ADC and MultiMedia Card Interface.

The AT91SAM9260 is architectured on a 6-layer matrix, allowing a maximum internal bandwidth of six 32-bit buses. It also features an External Bus Interface capable of interfacing with a wide range of memory devices.

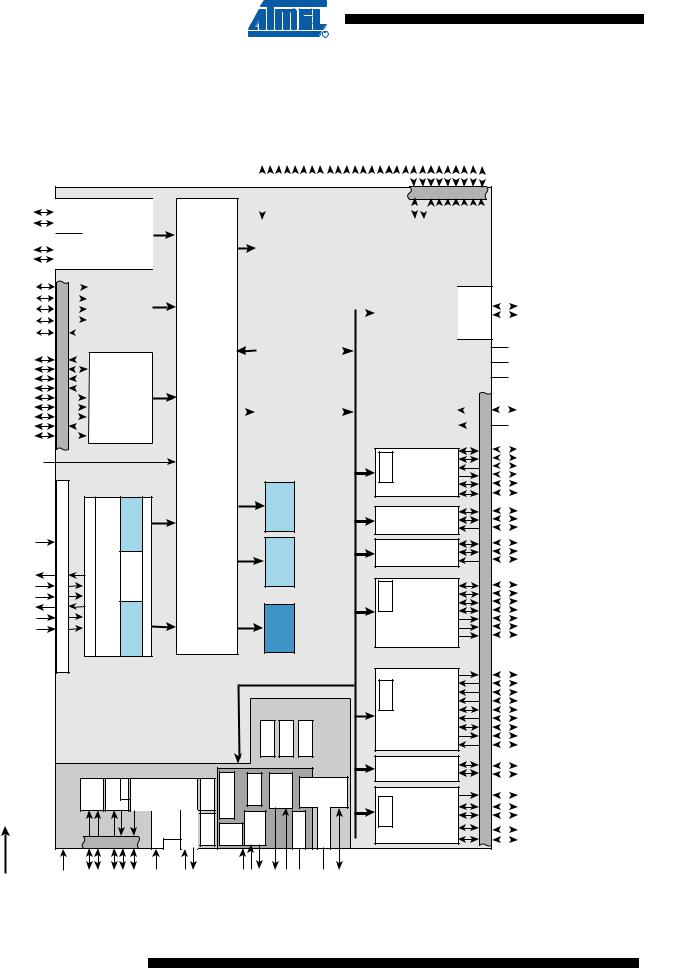

2. AT91SAM9260 Block Diagram

The block diagram shows all the features for the 217-LFBGA package. Some functions are not accessible in the 208-pin PQFP package and the unavailable pins are highlighted in “Multiplexing on PIO Controller A” on page 34, “Multiplexing on PIO Controller B” on page 35, “Multiplexing on PIO Controller C” on page 36. The USB Host Port B is not available in the 208pin package. Table 2-1 on page 3 defines all the multiplexed and not multiplexed pins not available in the 208-PQFP package.

Table 2-1. |

Unavailable Signals in 208-lead PQFP Package |

|

||

|

PIO |

Peripheral A |

|

Peripheral B |

|

|

|

|

|

|

- |

HDPB |

|

- |

|

|

|

|

|

|

- |

HDMB |

|

- |

|

|

|

|

|

|

PA30 |

SCK2 |

|

RXD4 |

|

|

|

|

|

|

PA31 |

SCK0 |

|

TXD4 |

|

|

|

|

|

|

PB12 |

TXD5 |

|

ISI_D10 |

|

|

|

|

|

|

PB13 |

RXD5 |

|

ISI_D11 |

|

|

|

|

|

|

PC2 |

AD2 |

|

PCK1 |

|

|

|

|

|

|

PC3 |

AD3 |

|

SPI1_NPCS3 |

|

|

|

|

|

|

PC12 |

IRQ0 |

|

NCS7 |

|

|

|

|

|

3

6221HS–ATARM–31-Jan-08

Figure 2-1. AT91SAM9260 Block Diagram

NCS3/NANDCS

NCS2, NCS6, NCS7

CFCE1-CFCE2

A25/CFRNW

NCS5/CFCS1

NCS4/CFCS0

A23-A24

NWAIT

D16-D31

A22/NANDCLE

A21/NANDALE

NANDOE, NANDWE

SDWE, SDA10

RAS, CAS

SDCK, SDCKE

NWR3/NBS3/CFIOW

NWR1/NBS1/CFIOR

NWR0/NWE/CFWE

NRD/CFOE

NCS1/SDCS

NCS0

A17/BA1

A16/BA0

A2-A15, A18-A20

A1/NBS2/NWR2

A0/NBS0

D0-D15

HDMB |

||

HDPB |

||

HDMA |

||

HDPA |

||

HSYNC |

|

|

ISIVSYNC |

|

|

D7 |

_ |

|

_ |

|

ISI |

- |

_ |

|

DO |

ISI |

|

|

_ |

|

PCKISI |

||

|

_ |

|

MCKISI |

||

|

_ |

|

|

|

ISI |

|

F100 |

|

ETX3MDIO |

||

ERX3 |

MDC |

|

ERXDV- |

ETX0 |

|

- |

|

|

- |

|

|

ECOL ERX0 |

||

ETXER-ERXER |

||

ERXCKECRS |

||

- |

|

|

ETXEN |

||

ETXCK |

||

Transc. Transc. |

|

|

|

USB OHCI |

|

|

DMA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

EBI |

CompactFlash |

NAND Flash |

|

|

|

SDRAM Controller |

|

Static Memory |

Controller |

|

ECC Controller |

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

Ethernet10/100Image |

MAC Interface |

FIFOFIFO |

|

DMADMA |

Matrixlayer |

|

|

channel-22Peripheral |

PeripheralBridge |

DMA |

|

|

|

|

|

|

|

|

PDCDPRAM |

|

channel-4 |

ADCbit-10 |

|

|

|

|

|

Transceiver |

|||||||||||||

|

|

|

|

|

Sensor |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

USB |

Device |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BMS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PDC |

SSC |

|

|

|

|

|

|

andSelectionJTAGBoundary Scan |

|

EmulatorCircuit-In |

S-ARM926EJProcessor |

|

|

InterfaceBus |

I D |

|

|

|

|

|

FastROMSRAM Fast SRAM |

4Kbytes32Kbytes 4 Kbytes |

|

|

|

TC2 TC5 |

|

|

|||

|

|

ICache |

Kbytes8 |

|

|

|

|

|

|

|

PDC |

SPI0 |

SPI1 |

|

|

|||||||||

JTAGSEL |

|

|

|

|

DCache |

Kbytes 8 |

|

|

|

|

|

|

|

|

|

|

|

|

TC3 |

TC4 |

|

|

|

|

RTCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TC0 |

TC1 |

|

|

|

|

|

|

|

|

MMU |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

TCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

TMS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TDO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TDI |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NTRST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

APB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIOA |

|

PIOB |

|

PIOC |

PDC |

USART0 USART1 USART2 |

USART3 |

USART4 |

USART5 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

SLAVE |

System |

Controller |

AIC |

DBGU |

PDC |

|

PMC |

PLLA |

PLLB |

OSC |

PITWDT |

RC |

OSCRTT |

|

SHDWC |

POR |

POR |

PDC |

TWI |

|

|

|

|

|

|

|

MCI |

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

4GPREG |

|

|

|

|

RSTC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Filter |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MASTER |

TST |

FIQ IRQ0-IRQ2 |

DRXD DTXD PCK0-PCK1 |

PLLRCA |

XIN XOUT |

OSCSEL XIN32 XOUT32 |

SHDN WKUP |

VDDBU |

VDDCORE |

NRST |

|

|

|

DDP |

|

|

|

|

|

|

|

|

|

|

|

DDM |

|

|

|

|

GNDANA |

|

|

|

|

|

VDDANA |

|

|

|

|

|

ADVREF |

|

|

|

|

|

|

ADTRIG |

|

|

|

|

|

|

||

|

|

|

AD3 |

|

|

- |

|

|

|||

|

|

|

AD0 |

||

|

|

|

RK |

|

|

|

|

|

|

||

|

|

|

RF |

|

|

|

|

|

|

||

|

|

|

RD |

|

|

|

|

|

|

||

|

|

|

TD |

|

|

|

|

|

TF |

|

|

|

|

|

TK |

|

|

|

|

|

|

|

|

|

|

|

TIOB5 |

|

|

|

|

|

|

||

|

|

|

|

||

|

|

|

TIOA5 |

|

|

- |

|

||||

|

|

|

TCLK5TIOB3 |

||

- |

|

||||

|

|

|

TIOB2TIOA3 |

||

|

|

|

|

- |

|

|

|

|

TIOA2 |

TCLK3 |

|

|

|

|

- |

|

|

|

|

|

TCLK2TIOB0 |

||

|

|

|

|||

- |

|

||||

|

|

|

|

TIOA0 |

|

|

|

|

|

- |

|

|

|

|

MISO |

|

TCLK0 |

|

|

|

|

||

|

|

|

|

||

|

|

|

MOSI |

|

|

|

|

|

SPCK |

|

SPI1_ |

|

|

|

|

||

|

|

|

NPCS0 |

||

|

|

|

|||

|

|

|

NPCS1 |

, |

|

|

|

|

|

||

|

|

|

NPCS2 |

SPI0 |

|

|

|

|

NPCS3 |

||

|

|

|

DTR0 |

|

|

|

|

|

|

|

|

|

|

|

RI0 |

|

|

|

|

|

DCD0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DSR0 |

|

|

|

|

|

|

|

|

|

|

|

TXD5 |

|

|

|

|

|

|

|

|

|

|

|

RXD5 |

|

|

- |

|

||||

|

|

|

SCK3TXD0 |

||

|

|

|

|||

- |

|

||||

|

|

|

RTS3 RXD0 |

||

|

|

|

|||

- |

|

||||

|

|

|

CTS3SCK0 |

||

|

|

|

|||

- |

|

||||

|

|

|

|

RTS0 |

|

|

|

|

- |

|

|

|

|

|

TWCK |

|

|

|

|

|

TWD |

CTS0 |

|

|

|

|

|

|

|

|

|

|

MCCK |

|

|

|

|

|

|

||

|

|

|

|

||

|

|

|

MCCDA |

||

|

|

|

|||

|

|

|

MCDA3- |

||

|

|

|

|||

|

|

|

MCCDBMCDA0 |

||

|

|

|

|||

|

|

|

MCDB3- |

||

|

|

|

|

|

MCDB0 |

4 AT91SAM9260

6221HS–ATARM–31-Jan-08

|

|

|

|

|

|

|

|

AT91SAM9260 |

|

|

|

|

|

|

|

|

|

|

3. Signal Description |

|

|

|

||||

|

|

|

|

|

||||

|

|

|

|

|

||||

|

Table 3-1. |

Signal Description List |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Active |

|

|

|

Signal Name |

|

Function |

|

Type |

Level |

|

Comments |

|

|

|

|

|

|

|

|

|

|

|

|

Power Supplies |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDDIOM |

|

EBI I/O Lines Power Supply |

|

Power |

|

|

1.65V to 1.95V or 3.0V to3.6V |

|

|

|

|

|

|

|

|

|

|

VDDIOP0 |

|

Peripherals I/O Lines Power Supply |

|

Power |

|

|

3.0V to 3.6V |

|

|

|

|

|

|

|

|

|

|

VDDIOP1 |

|

Peripherals I/O Lines Power Supply |

|

Power |

|

|

1.65V to 3.6V |

|

|

|

|

|

|

|

|

|

|

VDDBU |

|

Backup I/O Lines Power Supply |

|

Power |

|

|

1.65V to 1.95V |

|

|

|

|

|

|

|

|

|

|

VDDANA |

|

Analog Power Supply |

|

Power |

|

|

3.0V to 3.6V |

|

|

|

|

|

|

|

|

|

|

VDDPLL |

|

PLL Power Supply |

|

Power |

|

|

1.65V to 1.95V |

|

|

|

|

|

|

|

|

|

|

VDDCORE |

|

Core Chip Power Supply |

|

Power |

|

|

1.65V to 1.95V |

|

|

|

|

|

|

|

|

|

|

GND |

|

Ground |

|

Ground |

|

|

|

|

|

|

|

|

|

|

|

|

|

GNDPLL |

|

PLL and Oscillator Ground |

|

Ground |

|

|

|

|

|

|

|

|

|

|

|

|

|

GNDANA |

|

Analog Ground |

|

Ground |

|

|

|

|

|

|

|

|

|

|

|

|

|

GNDBU |

|

Backup Ground |

|

Ground |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Clocks, Oscillators and PLLs |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

XIN |

|

Main Oscillator Input |

|

Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

XOUT |

|

Main Oscillator Output |

|

Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

XIN32 |

|

Slow Clock Oscillator Input |

|

Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

XOUT32 |

|

Slow Clock Oscillator Output |

|

Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

OSCSEL |

|

Slow Clock Oscillator Selection |

|

Input |

|

|

Accepts between 0V and |

|

|

|

|

|

VDDBU. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PLLRCA |

|

PLL A Filter |

|

Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

PCK0 - PCK1 |

|

Programmable Clock Output |

|

Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Shutdown, Wakeup Logic |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

SHDN |

|

Shutdown Control |

|

Output |

|

|

Driven at 0V only. Do not tie |

|

|

|

|

|

over VDDBU. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WKUP |

|

Wake-up Input |

|

Input |

|

|

Accepts between 0V and |

|

|

|

|

|

VDDBU. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICE and JTAG |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NTRST |

|

Test Reset Signal |

|

Input |

Low |

|

Pull-up resistor |

|

|

|

|

|

|

|

|

|

|

TCK |

|

Test Clock |

|

Input |

|

|

No pull-up resistor |

|

|

|

|

|

|

|

|

|

|

TDI |

|

Test Data In |

|

Input |

|

|

No pull-up resistor |

|

|

|

|

|

|

|

|

|

|

TDO |

|

Test Data Out |

|

Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

TMS |

|

Test Mode Select |

|

Input |

|

|

No pull-up resistor |

|

|

|

|

|

|

|

|

|

|

JTAGSEL |

|

JTAG Selection |

|

Input |

|

|

Pull-down resistor. Accepts |

|

|

|

|

|

between 0V and VDDBU. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RTCK |

|

Return Test Clock |

|

Output |

|

|

|

|

|

|

|

|

|

|

|

|

5

6221HS–ATARM–31-Jan-08

Table 3-1. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Signal Description List (Continued) |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Active |

|

|

Signal Name |

|

Function |

Type |

Level |

Comments |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Reset/Test |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

NRST |

|

Microcontroller Reset |

I/O |

Low |

Pull-up resistor |

|

|||

|

|

|

|

|

|

|

|

|

|

TST |

|

Test Mode Select |

Input |

|

Pull-down resistor. Accepts |

|

|||

|

|

between 0V and VDDBU. |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BMS |

|

Boot Mode Select |

Input |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Debug Unit - DBGU |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

DRXD |

|

Debug Receive Data |

Input |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

DTXD |

|

Debug Transmit Data |

Output |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Advanced Interrupt Controller - AIC |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

IRQ0 - IRQ2 |

|

External Interrupt Inputs |

Input |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

FIQ |

|

Fast Interrupt Input |

Input |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

PIO Controller - PIOA - PIOB - PIOC |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

PA0 - PA31 |

|

Parallel IO Controller A |

I/O |

|

Pulled-up input at reset |

|

|||

|

|

|

|

|

|

|

|

|

|

PB0 - PB31 |

|

Parallel IO Controller B |

I/O |

|

Pulled-up input at reset |

|

|||

|

|

|

|

|

|

|

|

|

|

PC0 - PC31 |

|

Parallel IO Controller C |

I/O |

|

Pulled-up input at reset |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

External Bus Interface - EBI |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

D0 - D31 |

|

Data Bus |

I/O |

|

Pulled-up input at reset |

|

|||

|

|

|

|

|

|

|

|

|

|

A0 - A25 |

|

Address Bus |

Output |

|

0 at reset |

|

|||

|

|

|

|

|

|

|

|

|

|

NWAIT |

|

External Wait Signal |

Input |

Low |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Static Memory Controller - SMC |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

NCS0 - NCS7 |

|

Chip Select Lines |

Output |

Low |

|

|

|||

|

|

|

|

|

|

|

|

||

NWR0 - NWR3 |

Write Signal |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

NRD |

|

Read Signal |

Output |

Low |

|

|

|||

|

|

|

|

|

|

|

|

|

|

NWE |

|

Write Enable |

Output |

Low |

|

|

|||

|

|

|

|

|

|

|

|

|

|

NBS0 - NBS3 |

|

Byte Mask Signal |

Output |

Low |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

CompactFlash Support |

|

|

|

||||

|

|

|

|

|

|

|

|

||

CFCE1 - CFCE2 |

CompactFlash Chip Enable |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

CFOE |

|

CompactFlash Output Enable |

Output |

Low |

|

|

|||

|

|

|

|

|

|

|

|

|

|

CFWE |

|

CompactFlash Write Enable |

Output |

Low |

|

|

|||

|

|

|

|

|

|

|

|

|

|

CFIOR |

|

CompactFlash IO Read |

Output |

Low |

|

|

|||

|

|

|

|

|

|

|

|

|

|

CFIOW |

|

CompactFlash IO Write |

Output |

Low |

|

|

|||

|

|

|

|

|

|

|

|

|

|

CFRNW |

|

CompactFlash Read Not Write |

Output |

|

|

|

|||

|

|

|

|

|

|

|

|

||

CFCS0 - CFCS1 |

CompactFlash Chip Select Lines |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

6 AT91SAM9260

6221HS–ATARM–31-Jan-08

|

|

|

|

|

|

|

|

|

|

|

|

|

AT91SAM9260 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 3-1. |

Signal Description List (Continued) |

|

|

|

|||||||

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Active |

|

|

|

|

Signal Name |

|

|

Function |

Type |

Level |

|

Comments |

||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

NAND Flash Support |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

NANDCS |

|

|

NAND Flash Chip Select |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

NANDOE |

|

|

NAND Flash Output Enable |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

NANDWE |

|

|

NAND Flash Write Enable |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

NANDALE |

|

|

NAND Flash Address Latch Enable |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

NANDCLE |

|

|

NAND Flash Command Latch Enable |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

SDRAM Controller |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

SDCK |

|

|

SDRAM Clock |

Output |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

SDCKE |

|

|

SDRAM Clock Enable |

Output |

High |

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

SDCS |

|

|

SDRAM Controller Chip Select |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

BA0 - BA1 |

|

|

Bank Select |

Output |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

SDWE |

|

|

SDRAM Write Enable |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

RAS - CAS |

|

|

Row and Column Signal |

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

SDA10 |

|

|

SDRAM Address 10 Line |

Output |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

Multimedia Card Interface MCI |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

MCCK |

|

|

Multimedia Card Clock |

Output |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

MCCDA |

|

|

Multimedia Card Slot A Command |

I/O |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||||

|

|

MCDA0 - MCDA3 |

|

Multimedia Card Slot A Data |

I/O |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

MCCDB |

|

|

Multimedia Card Slot B Command |

I/O |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||||

|

|

MCDB0 - MCDB3 |

|

Multimedia Card Slot B Data |

I/O |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

Universal Synchronous Asynchronous Receiver Transmitter USARTx |

|||||||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

SCKx |

|

|

USARTx Serial Clock |

I/O |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

TXDx |

|

|

USARTx Transmit Data |

I/O |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

RXDx |

|

|

USARTx Receive Data |

Input |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

RTSx |

|

|

USARTx Request To Send |

Output |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

CTSx |

|

|

USARTx Clear To Send |

Input |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

DTR0 |

|

|

USART0 Data Terminal Ready |

Output |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

DSR0 |

|

|

USART0 Data Set Ready |

Input |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

DCD0 |

|

|

USART0 Data Carrier Detect |

Input |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

RI0 |

|

|

USART0 Ring Indicator |

Input |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

Synchronous Serial Controller - SSC |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

TD |

|

|

SSC Transmit Data |

Output |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

RD |

|

|

SSC Receive Data |

Input |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

TK |

|

|

SSC Transmit Clock |

I/O |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

RK |

|

|

SSC Receive Clock |

I/O |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

TF |

|

|

SSC Transmit Frame Sync |

I/O |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

RF |

|

|

SSC Receive Frame Sync |

I/O |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6221HS–ATARM–31-Jan-08

Table 3-1. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Signal Description List (Continued) |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Active |

|

|

Signal Name |

|

Function |

|

Type |

Level |

Comments |

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

Timer/Counter - TCx |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

TCLKx |

|

TC Channel x External Clock Input |

|

Input |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

TIOAx |

|

TC Channel x I/O Line A |

|

I/O |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

TIOBx |

|

TC Channel x I/O Line B |

|

I/O |

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

Serial Peripheral Interface - SPIx_ |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

SPIx_MISO |

|

Master In Slave Out |

|

I/O |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

SPIx_MOSI |

|

Master Out Slave In |

|

I/O |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

SPIx_SPCK |

|

SPI Serial Clock |

|

I/O |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

SPIx_NPCS0 |

|

SPI Peripheral Chip Select 0 |

|

I/O |

Low |

|

|

|||

|

|

|

|

|

|

|

|

|

||

SPIx_NPCS1-SPIx_NPCS3 |

SPI Peripheral Chip Select |

|

Output |

Low |

|

|

||||

|

|

|

|

|

|

|

|

|

||

|

|

Two-Wire Interface |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

TWD |

|

Two-wire Serial Data |

|

I/O |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

TWCK |

|

Two-wire Serial Clock |

|

I/O |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

USB Host Port |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

HDPA |

|

USB Host Port A Data + |

|

Analog |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

HDMA |

|

USB Host Port A Data - |

|

Analog |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

HDPB |

|

USB Host Port B Data + |

|

Analog |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

HDMB |

|

USB Host Port B Data + |

|

Analog |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

USB Device Port |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

DDM |

|

USB Device Port Data - |

|

Analog |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

DDP |

|

USB Device Port Data + |

|

Analog |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Ethernet 10/100 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

ETXCK |

|

Transmit Clock or Reference Clock |

|

Input |

|

MII only, REFCK in RMII |

|

|||

|

|

|

|

|

|

|

|

|

|

|

ERXCK |

|

Receive Clock |

|

Input |

|

MII only |

|

|||

|

|

|

|

|

|

|

|

|

|

|

ETXEN |

|

Transmit Enable |

|

Output |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

ETX0-ETX3 |

|

Transmit Data |

|

Output |

|

ETX0-ETX1 only in RMII |

|

|||

|

|

|

|

|

|

|

|

|

|

|

ETXER |

|

Transmit Coding Error |

|

Output |

|

MII only |

|

|||

|

|

|

|

|

|

|

|

|

|

|

ERXDV |

|

Receive Data Valid |

|

Input |

|

RXDV in MII , CRSDV in RMII |

|

|||

|

|

|

|

|

|

|

|

|

|

|

ERX0-ERX3 |

|

Receive Data |

|

Input |

|

ERX0-ERX1 only in RMII |

|

|||

|

|

|

|

|

|

|

|

|

|

|

ERXER |

|

Receive Error |

|

Input |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

ECRS |

|

Carrier Sense and Data Valid |

|

Input |

|

MII only |

|

|||

|

|

|

|

|

|

|

|

|

|

|

ECOL |

|

Collision Detect |

|

Input |

|

MII only |

|

|||

|

|

|

|

|

|

|

|

|

|

|

EMDC |

|

Management Data Clock |

|

Output |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

EMDIO |

|

Management Data Input/Output |

|

I/O |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

EF100 |

|

Force 100Mbit/sec. |

|

Output |

High |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

8 AT91SAM9260

6221HS–ATARM–31-Jan-08

|

|

|

|

|

|

|

AT91SAM9260 |

|

|

|

|

|

|

|

|

|

Table 3-1. |

Signal Description List (Continued) |

|

|

|

||

|

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Active |

|

|

|

Signal Name |

|

Function |

Type |

Level |

|

Comments |

|

|

|

|

|

|

|

|

|

|

|

Image Sensor Interface |

|

|

|

|

|

|

|

|

|

|

|

|

|

ISI_D0-ISI_D11 |

Image Sensor Data |

Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

ISI_MCK |

|

Image Sensor Reference Clock |

Output |

|

|

|

|

|

|

|

|

|

|

|

|

ISI_HSYNC |

|

Image Sensor Horizontal Synchro |

Input |

|

|

|

|

|

|

|

|

|

|

|

|

ISI_VSYNC |

|

Image Sensor Vertical Synchro |

Input |

|

|

|

|

|

|

|

|

|

|

|

|

ISI_PCK |

|

Image Sensor Data clock |

Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Analog to Digital Converter |

|

|

|

|

|

|

|

|

|

|

|

|

|

AD0-AD3 |

|

Analog Inputs |

Analog |

|

|

Digital pulled-up inputs at |

|

|

|

|

reset |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADVREF |

|

Analog Positive Reference |

Analog |

|

|

|

|

|

|

|

|

|

|

|

|

ADTRG |

|

ADC Trigger |

Input |

|

|

|

|

|

|

|

|

|

|

|

9

6221HS–ATARM–31-Jan-08

4. Package and Pinout

The AT91SAM9260 is available in two packages:

•208-pin PQFP Green package (0.5mm pitch) (Figure 4-1)

•217-ball LFBGA Green package (0.8 mm ball pitch) (Figure 4-2).

4.1208-pin PQFP Package Outline

Figure 4-1 shows the orientation of the 208-pin PQFP package.

A detailed mechanical description is given in the section “AT91SAM9260 Mechanical Characteristics” of the product datasheet.

Figure 4-1. 208-pin PQFP Package

156 |

105 |

157 |

104 |

208

53

1 |

52 |

10 AT91SAM9260

6221HS–ATARM–31-Jan-08

AT91SAM9260

4.2208-pin PQFP Pinout

Table 4-1. |

Pinout for 208-pin PQFP Package |

|

|

|

|

|

|

|||

Pin |

Signal Name |

|

Pin |

Signal Name |

|

Pin |

Signal Name |

|

Pin |

Signal Name |

1 |

PA24 |

|

53 |

GND |

|

105 |

RAS |

|

157 |

ADVREF |

|

|

|

|

|

|

|

|

|

|

|

2 |

PA25 |

|

54 |

DDM |

|

106 |

D0 |

|

158 |

PC0 |

|

|

|

|

|

|

|

|

|

|

|

3 |

PA26 |

|

55 |

DDP |

|

107 |

D1 |

|

159 |

PC1 |

|

|

|

|

|

|

|

|

|

|

|

4 |

PA27 |

|

56 |

PC13 |

|

108 |

D2 |

|

160 |

VDDANA |

|

|

|

|

|

|

|

|

|

|

|

5 |

VDDIOP0 |

|

57 |

PC11 |

|

109 |

D3 |

|

161 |

PB10 |

|

|

|

|

|

|

|

|

|

|

|

6 |

GND |

|

58 |

PC10 |

|

110 |

D4 |

|

162 |

PB11 |

|

|

|

|

|

|

|

|

|

|

|

7 |

PA28 |

|

59 |

PC14 |

|

111 |

D5 |

|

163 |

PB20 |

|

|

|

|

|

|

|

|

|

|

|

8 |

PA29 |

|

60 |

PC9 |

|

112 |

D6 |

|

164 |

PB21 |

|

|

|

|

|

|

|

|

|

|

|

9 |

PB0 |

|

61 |

PC8 |

|

113 |

GND |

|

165 |

PB22 |

|

|

|

|

|

|

|

|

|

|

|

10 |

PB1 |

|

62 |

PC4 |

|

114 |

VDDIOM |

|

166 |

PB23 |

|

|

|

|

|

|

|

|

|

|

|

11 |

PB2 |

|

63 |

PC6 |

|

115 |

SDCK |

|

167 |

PB24 |

|

|

|

|

|

|

|

|

|

|

|

12 |

PB3 |

|

64 |

PC7 |

|

116 |

SDWE |

|

168 |

PB25 |

|

|

|

|

|

|

|

|

|

|

|

13 |

VDDIOP0 |

|

65 |

VDDIOM |

|

117 |

SDCKE |

|

169 |

VDDIOP1 |

|

|

|

|

|

|

|

|

|

|

|

14 |

GND |

|

66 |

GND |

|

118 |

D7 |

|

170 |

GND |

|

|

|

|

|

|

|

|

|

|

|

15 |

PB4 |

|

67 |

PC5 |

|

119 |

D8 |

|

171 |

PB26 |

|

|

|

|

|

|

|

|

|

|

|

16 |

PB5 |

|

68 |

NCS0 |

|

120 |

D9 |

|

172 |

PB27 |

|

|

|

|

|

|

|

|

|

|

|

17 |

PB6 |

|

69 |

CFOE/NRD |

|

121 |

D10 |

|

173 |

GND |

|

|

|

|

|

|

|

|

|

|

|

18 |

PB7 |

|

70 |

CFWE/NWE/NWR0 |

|

122 |

D11 |

|

174 |

VDDCORE |

|

|

|

|

|

|

|

|

|

|

|

19 |

PB8 |

|

71 |

NANDOE |

|

123 |

D12 |

|

175 |

PB28 |

|

|

|

|

|

|

|

|

|

|

|

20 |

PB9 |

|

72 |

NANDWE |

|

124 |

D13 |

|

176 |

PB29 |

|

|

|

|

|

|

|

|

|

|

|

21 |

PB14 |

|

73 |

A22 |

|

125 |

D14 |

|

177 |

PB30 |

|

|

|

|

|

|

|

|

|

|

|

22 |

PB15 |

|

74 |

A21 |

|

126 |

D15 |

|

178 |

PB31 |

|

|

|

|

|

|

|

|

|

|

|

23 |

PB16 |

|

75 |

A20 |

|

127 |

PC15 |

|

179 |

PA0 |

|

|

|

|

|

|

|

|

|

|

|

24 |

VDDIOP0 |

|

76 |

A19 |

|

128 |

PC16 |

|

180 |

PA1 |

|

|

|

|

|

|

|

|

|

|

|

25 |

GND |

|

77 |

VDDCORE |

|

129 |

PC17 |

|

181 |

PA2 |

|

|

|

|

|

|

|

|

|

|

|

26 |

PB17 |

|

78 |

GND |

|

130 |

PC18 |

|

182 |

PA3 |

|

|

|

|

|

|

|

|

|

|

|

27 |

PB18 |

|

79 |

A18 |

|

131 |

PC19 |

|

183 |

PA4 |

|

|

|

|

|

|

|

|

|

|

|

28 |

PB19 |

|

80 |

BA1/A17 |

|

132 |

VDDIOM |

|

184 |

PA5 |

|

|

|

|

|

|

|

|

|

|

|

29 |

TDO |

|

81 |

BA0/A16 |

|

133 |

GND |

|

185 |

PA6 |

|

|

|

|

|

|

|

|

|

|

|

30 |

TDI |

|

82 |

A15 |

|

134 |

PC20 |

|

186 |

PA7 |

|

|

|

|

|

|

|

|

|

|

|

31 |

TMS |

|

83 |

A14 |

|

135 |

PC21 |

|

187 |

VDDIOP0 |

|

|

|

|

|

|

|

|

|

|

|

32 |

VDDIOP0 |

|

84 |

A13 |

|

136 |

PC22 |

|

188 |

GND |

|

|

|

|

|

|

|

|

|

|

|

33 |

GND |

|

85 |

A12 |

|

137 |

PC23 |

|

189 |

PA8 |

|

|

|

|

|

|

|

|

|

|

|

34 |

TCK |

|

86 |

A11 |

|

138 |

PC24 |

|

190 |

PA9 |

|

|

|

|

|

|

|

|

|

|

|

35 |

NTRST |

|

87 |

A10 |

|

139 |

PC25 |

|

191 |

PA10 |

|

|

|

|

|

|

|

|

|

|

|

36 |

NRST |

|

88 |

A9 |

|

140 |

PC26 |

|

192 |

PA11 |

|

|

|

|

|

|

|

|

|

|

|

37 |

RTCK |

|

89 |

A8 |

|

141 |

PC27 |

|

193 |

PA12 |

|

|

|

|

|

|

|

|

|

|

|

38 |

VDDCORE |

|

90 |

VDDIOM |

|

142 |

PC28 |

|

194 |

PA13 |

|

|

|

|

|

|

|

|

|

|

|

39 |

GND |

|

91 |

GND |

|

143 |

PC29 |

|

195 |

PA14 |

|

|

|

|

|

|

|

|

|

|

|

40 |

BMS |

|

92 |

A7 |

|

144 |

PC30 |

|

196 |

PA15 |

|

|

|

|

|

|

|

|

|

|

|

41 |

OSCSEL |

|

93 |

A6 |

|

145 |

PC31 |

|

197 |

PA16 |

|

|

|

|

|

|

|

|

|

|

|

42 |

TST |

|

94 |

A5 |

|

146 |

GND |

|

198 |

PA17 |

|

|

|

|

|

|

|

|

|

|

|

43 |

JTAGSEL |

|

95 |

A4 |

|

147 |

VDDCORE |

|

199 |

VDDIOP0 |

|

|

|

|

|

|

|

|

|

|

|

44 |

GNDBU |

|

96 |

A3 |

|

148 |

VDDPLL |

|

200 |

GND |

|

|

|

|

|

|

|

|

|

|

|

45 |

XOUT32 |

|

97 |

A2 |

|

149 |

XIN |

|

201 |

PA18 |

|

|

|

|

|

|

|

|

|

|

|

46 |

XIN32 |

|

98 |

NWR2/NBS2/A1 |

|

150 |

XOUT |

|

202 |

PA19 |

|

|

|

|

|

|

|

|

|

|

|

47 |

VDDBU |

|

99 |

NBS0/A0 |

|

151 |

GNDPLL |

|

203 |

VDDCORE |

|

|

|

|

|

|

|

|

|

|

|

48 |

WKUP |

|

100 |

SDA10 |

|

152 |

NC |

|

204 |

GND |

|

|

|

|

|

|

|

|

|

|

|

11

6221HS–ATARM–31-Jan-08

Table 4-1. |

Pinout for 208-pin PQFP Package (Continued) |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin |

Signal Name |

|

Pin |

Signal Name |

|

|

Pin |

|

Signal Name |

|

Pin |

Signal Name |

|

||

49 |

SHDN |

|

101 |

CFIOW/NBS3/NWR3 |

|

153 |

|

GNDPLL |

|

205 |

PA20 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

HDMA |

|

102 |

CFIOR/NBS1/NWR1 |

|

154 |

|

PLLRCA |

|

206 |

PA21 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

HDPA |

|

103 |

SDCS/NCS1 |

|

155 |

|

VDDPLL |

|

207 |

PA22 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

VDDIOP0 |

|

104 |

CAS |

|

156 |

|

GNDANA |

|

208 |

PA23 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.3217-ball LFBGA Package Outline

Figure 4-2 shows the orientation of the 217-ball LFBGA package.

A detailed mechanical description is given in the section “AT91SAM9260 Mechanical Characteristics” of the product datasheet.

Figure 4-2. 217-ball LFBGA Package (Top View)

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1