ATMEL AT89C51CC01 User Manual

BDTIC www.bdtic.com/ATMEL

Features

•80C51 Core Architecture

•256 Bytes of On-chip RAM

•1K Bytes of On-chip XRAM

•32K Bytes of On-chip Flash Memory

–Data Retention: 10 Years at 85°C Erase/Write Cycle: 100K

•Boot Code Section with Independent Lock Bits

•2K Bytes of On-chip Flash for Bootloader

•In-System Programming by On-Chip Boot Program (CAN, UART) and IAP Capability

•2K Bytes of On-chip EEPROM Erase/Write Cycle: 100K

•14-sources 4-level Interrupts

•Three 16-bit Timers/Counters

•Full Duplex UART Compatible 80C51

•Maximum Crystal Frequency 40 MHz, in X2 Mode, 20 MHz (CPU Core, 20 MHz)

•Five Ports: 32 + 2 Digital I/O Lines

•Five-channel 16-bit PCA with:

–PWM (8-bit)

–High-speed Output

–Timer and Edge Capture

•Double Data Pointer

•21-bit Watchdog Timer (7 Programmable Bits)

•A 10-bit Resolution Analog to Digital Converter (ADC) with 8 Multiplexed Inputs

•Full CAN Controller:

–Fully Compliant with CAN Rev2.0A and 2.0B

–Optimized Structure for Communication Management (Via SFR)

–15 Independent Message Objects:

Each Message Object Programmable on Transmission or Reception Individual Tag and Mask Filters up to 29-bit Identifier/Channel 8-byte Cyclic Data Register (FIFO)/Message Object

16-bit Status and Control Register/Message Object

16-bit Time-Stamping Register/Message Object

CAN Specification 2.0 Part A or 2.0 Part B Programmable for Each Message Object

Access to Message Object Control and Data Registers Via SFR Programmable Reception Buffer Length Up To 15 Message Objects

Priority Management of Reception of Hits on Several Message Objects at the Same Time (Basic CAN Feature)

Priority Management for Transmission Message Object Overrun Interrupt

– Supports:

Time Triggered Communication

Autobaud and Listening Mode Programmable Automatic Reply Mode

–1-Mbit/s Maximum Transfer Rate at 8 MHz (1) Crystal Frequency in X2 Mode

–Readable Error Counters

–Programmable Link to On-chip Timer for Time Stamping and Network Synchronization

–Independent Baud Rate Prescaler

–Data, Remote, Error and Overload Frame Handling

•On-chip Emulation Logic (Enhanced Hook System)

•Power Saving Modes:

–Idle Mode

–Power-down Mode

1.At BRP = 1 sampling point will be fixed.

Enhanced 8-bit Microcontroller with CAN Controller and Flash Memory

T89C51CC01

AT89C51CC01

Rev. 4129N–CAN–03/08

1

•Power Supply: 3V to 5.5V

•Temperature Range: Industrial (-40° to +85°C)

•Packages: VQFP44, PLCC44

Description

The T89C51CC01 is the first member of the CANaryTM family of 8-bit microcontrollers dedicated to CAN network applications.

In X2 mode a maximum external clock rate of 20 MHz reaches a 300 ns cycle time.

Besides the full CAN controller T89C51CC01 provides 32K Bytes of Flash memory including In-System-Programming (ISP), 2K Bytes Boot Flash Memory, 2K Bytes EEPROM and 1.2-Kbyte RAM.

Special attention is paid to the reduction of the electro-magnetic emission of T89C51CC01.

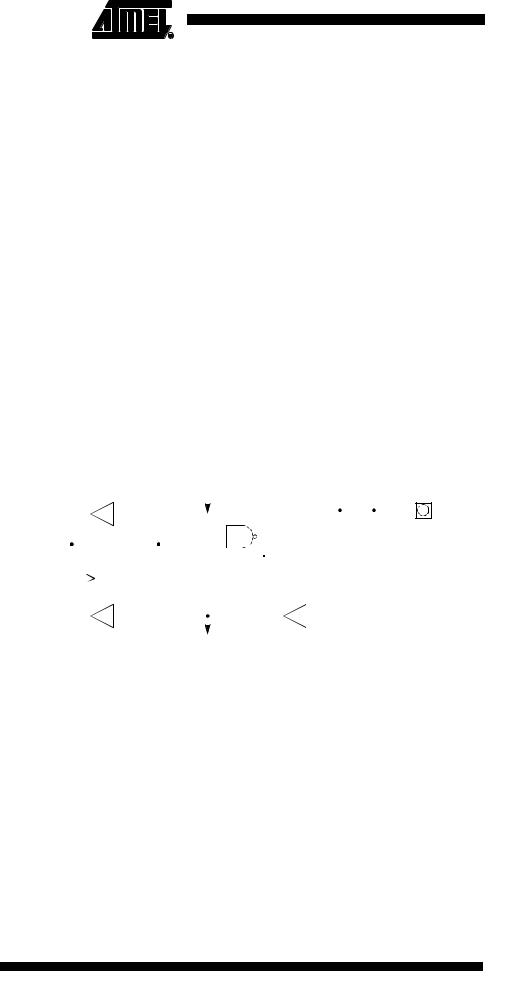

Block Diagram

RxD |

TxD |

Vcc |

Vss |

ECI |

PCA |

T2EX |

T2 |

RxDC |

TxDC |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XTAL1 |

|

|

|

|

UART |

|

RAM |

|

Flash |

|

Boot |

|

EE |

|

XRAM |

|

PCA |

|

Timer 2 |

|

CAN |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

XTAL2 |

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

256x8 |

|

32kx |

|

loader |

|

PROM |

|

1kx8 |

|

|

|

||||||

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

8 |

|

2kx8 |

|

2kx8 |

|

|

|

|

|

|

|

CONTROLLER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ALE |

C51 |

|

|

|

|

PSEN |

CORE |

IB-bus |

CPU |

|

|

|

|

|

EA |

|

|

|

|

|

|

|

|

|

|

|

Timer 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

INT |

|

|

|

Parallel I/O Ports and Ext. Bus |

|

|

Watch |

|

|

10 bit |

|

|

|||||||||||||||||

RD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

Timer 1 |

|

|

Ctrl |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Dog |

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Port 0 |

Port 1 |

Port 2 |

Port 3 |

Port 4 |

|

|

|

|

ADC |

|

|

|||||||||||||||||

WR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P0 |

P1(1) |

P2 |

P3 |

P4(2) |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

RESET |

|

T0 T1 |

|

INT0 |

|

INT1 |

|

|

VAREF |

VAVCC |

VAGND |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

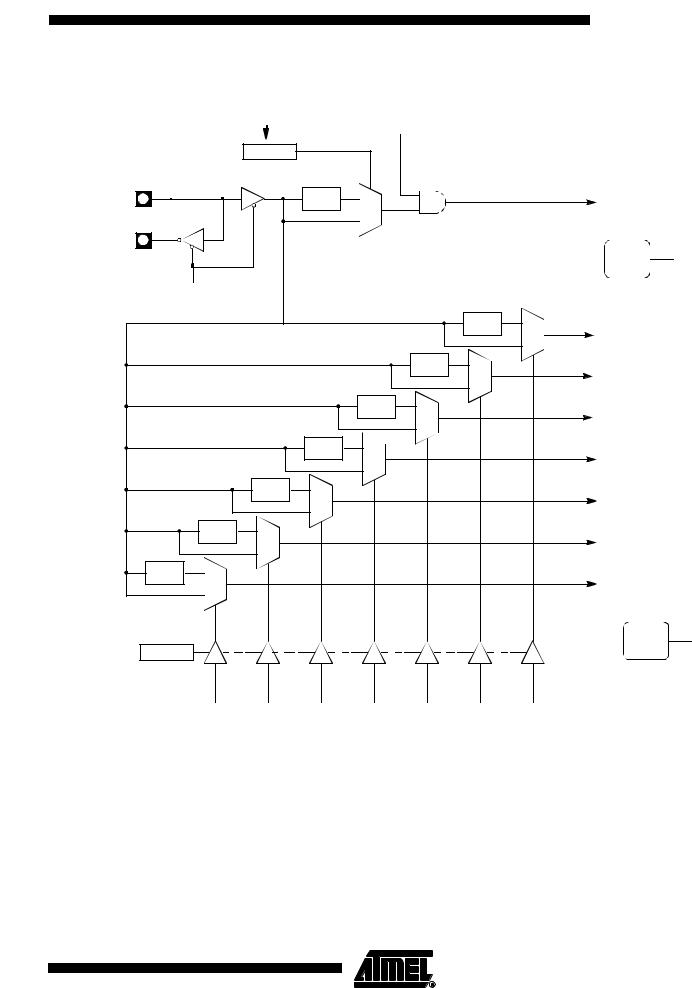

Notes: 1. 8 analog Inputs/8 Digital I/O 2. 2-Bit I/O Port

2A/T89C51CC01

4129N–CAN–03/08

A/T89C51CC01

Pin Configuration

|

|

|

P1.3/AN3/CEX0 |

P1.2/AN2/ECI |

P1.1/AN1/T2EX |

P1.0/AN 0/T2 |

VAREF |

VAGND |

RESET |

VSS |

VCC |

XTAL1 |

XTAL2 |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

5 |

4 |

3 |

2 |

1 |

44 |

43 |

42 |

41 |

40 |

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

P1.4/AN4/CEX1 |

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

|

ALE |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P1.5/AN5/CEX2 |

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

|

PSEN |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P1.6/AN6/CEX3 |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

P0.7/AD7 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P1.7/AN7/CEX4 |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

|

P0.6/AD6 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

EA |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

P0.5/AD5 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P3.0/RxD |

|

12 |

|

|

|

|

|

|

|

|

PLCC44 |

|

|

|

|

34 |

|

P0.4/AD4 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

P3.1/TxD |

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

P0.3/AD3 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

P3.2/INT0 |

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

P0.2/AD2 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P3.3/INT1 |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

P0.1/AD1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P3.4/T0 |

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

|

P0.0/AD0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P3.5/T1 |

|

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

29 |

|

P2.0/A8 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P3.6/WR |

P3.7/RD |

P4.0/ TxDC |

P4.1/RxDC |

P2.7/A15 |

P2.6/A14 |

P2.5/A13 |

P2.4/A12 |

P2.3/A11 |

P2.2/A10 |

P2.1/A9 |

|

|

||||||||||||

|

|

|

|

|

P1.3/AN3/CEX0 |

P1.2/AN2/ECI |

P1.1/AN1/T2EX |

P1.0/AN 0/T2 VAREF VAGND RESET VSS |

VCC |

XTAL1 |

XTAL2 |

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 43 42 41 40 39 38 37 36 35 34 |

|

|

|

|

||||||||||||||||||||||||

P1.4/AN4/CEX1 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

ALE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

P1.5/AN5/CEX2 |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

PSEN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

P1.6/AN6/CEX3 |

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

|

P0.7/AD7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

P1.7/AN7/CEX4 |

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

|

|

P0.6/AD6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

EA |

|

|

5 |

|

|

|

|

|

|

|

VQFP44 |

|

|

|

|

29 |

|

|

P0.5/AD5 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

P3.0/RxD |

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

28 |

|

|

P0.4 /AD4 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

P3.1/TxD |

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

27 |

|

|

P0.3 /AD3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

P3.2/INT0 |

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

26 |

|

|

P0.2 /AD2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

P3.3/INT1 |

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

|

|

P0.1 /AD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

P3.4/T0 |

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

|

|

P0.0 /AD0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

P3.5/T1 |

|

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

23 |

|

|

P2.0/A8 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

12 13 14 15 16 17 18 19 20 21 22 |

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P3.6/WR |

P3.7/RD |

P4.0/TxDC |

P4.1/RxDC P2.7/A15 P2.6/A14 P2.5/A13 P2.4/A12 |

P2.3/A11 |

P2.2/A10 |

P2.1/A9 |

|

|

|

|||||||||||||||

3

4129N–CAN–03/08

I/O Configurations

Each Port SFR operates via type-D latches, as illustrated in Figure 1 for Ports 3 and 4. A CPU "write to latch" signal initiates transfer of internal bus data into the type-D latch. A CPU "read latch" signal transfers the latched Q output onto the internal bus. Similarly, a "read pin" signal transfers the logical level of the Port pin. Some Port data instructions activate the "read latch" signal while others activate the "read pin" signal. Latch instructions are referred to as Read-Modify-Write instructions. Each I/O line may be independently programmed as input or output.

Port 1, Port 3 and Port 4 Figure 1 shows the structure of Ports 1 and 3, which have internal pull-ups. An external source can pull the pin low. Each Port pin can be configured either for general-purpose I/O or for its alternate input output function.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 1,3 or 4). To use a pin for general-purpose input, set the bit in the Px register. This turns off the output FET drive.

To configure a pin for its alternate function, set the bit in the Px register. When the latch is set, the "alternate output function" signal controls the output level (see Figure 1). The operation of Ports 1, 3 and 4 is discussed further in the "quasi-Bidirectional Port Operation" section.

Figure 1. Port 1, Port 3 and Port 4 Structure

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

||||||||

|

|

|

|

|

|

|

|

|

|

ALTERNATE |

|

|

|

|

|

|

|

|

|

INTERNAL |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

OUTPUT |

|

|

|

|

|

|

|

|

|

|||||||

READ |

|

|

|

|

|

|

|

|

FUNCTION |

|

|

|

|

|

|

|

|

|

PULL-UP (1) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

LATCH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.x |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P3.x |

INTERNAL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P4.x |

|||

BUS |

|

|

D P1.X Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

P3.X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

P4.X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WRITE |

|

|

LATCH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

TO |

|

|

|

|

|

CL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

LATCH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

READ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

PIN |

|

|

|

|

|

|

|

ALTERNATE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

INPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

FUNCTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Port 0 and Port 2

Note: The internal pull-up can be disabled on P1 when analog function is selected.

Ports 0 and 2 are used for general-purpose I/O or as the external address/data bus. Port 0, shown in Figure 3, differs from the other Ports in not having internal pull-ups. Figure 3 shows the structure of Port 2. An external source can pull a Port 2 pin low.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 0 or 2). To use a pin for general-purpose input, set the bit in the Px register to turn off the output driver FET.

4A/T89C51CC01

4129N–CAN–03/08

A/T89C51CC01

A/T89C51CC01

Read-Modify-Write

Instructions

Figure 2. Port 0 Structure |

|

|

||

|

|

ADDRESS LOW/ |

CONTROL |

VDD |

|

|

DATA |

|

|

READ |

|

|

|

(2) |

|

|

|

|

|

LATCH |

|

|

|

P0.x (1) |

|

|

|

|

|

|

|

|

1 |

|

INTERNAL |

|

|

0 |

|

BUS |

DP0.X |

Q |

|

|

|

|

|||

WRITE |

LATCH |

|

|

|

|

|

|

|

|

TO |

|

|

|

|

LATCH |

|

|

|

|

READ |

|

|

|

|

PIN |

|

|

|

|

Notes: 1. Port 0 is precluded from use as general-purpose I/O Ports when used as address/data bus drivers.

2.Port 0 internal strong pull-ups assist the logic-one output for memory bus cycles only. Except for these bus cycles, the pull-up FET is off, Port 0 outputs are open-drain.

Figure 3. Port 2 Structure |

|

|

||

|

|

ADDRESS HIGH/ CONTROL |

VDD |

|

|

|

|

|

INTERNAL |

READ |

|

|

|

PULL-UP (2) |

LATCH |

|

|

|

P2.x (1) |

|

|

|

|

|

|

|

|

1 |

|

INTERNAL |

|

|

0 |

|

BUS |

DP2.X |

Q |

|

|

|

|

|||

WRITE |

LATCH |

|

|

|

|

|

|

|

|

TO |

|

|

|

|

LATCH |

|

|

|

|

READ |

|

|

|

|

PIN |

|

|

|

|

Notes: 1. Port 2 is precluded from use as general-purpose I/O Ports when as address/data bus drivers.

2.Port 2 internal strong pull-ups FET (P1 in FiGURE) assist the logic-one output for memory bus cycle.

When Port 0 and Port 2 are used for an external memory cycle, an internal control signal switches the output-driver input from the latch output to the internal address/data line.

Some instructions read the latch data rather than the pin data. The latch based instructions read the data, modify the data and then rewrite the latch. These are called "Read- Modify-Write" instructions. Below is a complete list of these special instructions (see Table ). When the destination operand is a Port or a Port bit, these instructions read the latch rather than the pin:

5

4129N–CAN–03/08

Quasi-Bidirectional Port

Operation

Table 1. Read-Modify-Write Instructions

Instruction |

Description |

Example |

|

|

|

ANL |

logical AND |

ANL P1, A |

|

|

|

ORL |

logical OR |

ORL P2, A |

|

|

|

XRL |

logical EX-OR |

XRL P3, A |

|

|

|

JBC |

jump if bit = 1 and clear bit |

JBC P1.1, LABEL |

|

|

|

CPL |

complement bit |

CPL P3.0 |

|

|

|

INC |

increment |

INC P2 |

|

|

|

DEC |

decrement |

DEC P2 |

|

|

|

DJNZ |

decrement and jump if not zero |

DJNZ P3, LABEL |

|

|

|

MOV Px.y, C |

move carry bit to bit y of Port x |

MOV P1.5, C |

|

|

|

CLR Px.y |

clear bit y of Port x |

CLR P2.4 |

|

|

|

SET Px.y |

set bit y of Port x |

SET P3.3 |

|

|

|

It is not obvious the last three instructions in this list are Read-Modify-Write instructions. These instructions read the port (all 8 bits), modify the specifically addressed bit and write the new byte back to the latch. These Read-Modify-Write instructions are directed to the latch rather than the pin in order to avoid possible misinterpretation of voltage (and therefore, logic) levels at the pin. For example, a Port bit used to drive the base of an external bipolar transistor can not rise above the transistor’s base-emitter junction voltage (a value lower than VIL). With a logic one written to the bit, attempts by the CPU to read the Port at the pin are misinterpreted as logic zero. A read of the latch rather than the pins returns the correct logic-one value.

Port 1, Port 2, Port 3 and Port 4 have fixed internal pull-ups and are referred to as "quasi-bidirectional" Ports. When configured as an input, the pin impedance appears as logic one and sources current in response to an external logic zero condition. Port 0 is a "true bidirectional" pin. The pins float when configured as input. Resets write logic one to all Port latches. If logical zero is subsequently written to a Port latch, it can be returned to input conditions by a logical one written to the latch.

Note: Port latch values change near the end of Read-Modify-Write instruction cycles. Output buffers (and therefore the pin state) update early in the instruction after Read-Modify- Write instruction cycle.

Logical zero-to-one transitions in Port 1, Port 2, Port 3 and Port 4 use an additional pullup (p1) to aid this logic transition (see Figure 4.). This increases switch speed. This extra pull-up sources 100 times normal internal circuit current during 2 oscillator clock periods. The internal pull-ups are field-effect transistors rather than linear resistors. Pullups consist of three p-channel FET (pFET) devices. A pFET is on when the gate senses logical zero and off when the gate senses logical one. pFET #1 is turned on for two oscillator periods immediately after a zero-to-one transition in the Port latch. A logical one at the Port pin turns on pFET #3 (a weak pull-up) through the inverter. This inverter and pFET pair form a latch to drive logical one. pFET #2 is a very weak pull-up switched on whenever the associated nFET is switched off. This is traditional CMOS switch convention. Current strengths are 1/10 that of pFET #3.

6A/T89C51CC01

4129N–CAN–03/08

A/T89C51CC01

Figure 4. Internal Pull-Up Configurations

VCC VCC VCC

2 Osc. PERIODS

|

|

|

|

|

|

|

|

|

p1(1) |

|

|

p2 |

|

|

p3 |

||

|

|

|

||||||

|

|

|

|

|

|

|

|

|

P1.x

P1.x

P2.x

P3.x

P4.x

OUTPUT DATA |

|

|

|

n |

|

|

INPUT DATA

READ PIN

Note: Port 2 p1 assists the logic-one output for memory bus cycles.

7

4129N–CAN–03/08

SFR Mapping

The Special Function Registers (SFRs) of the T89C51CC01 fall into the following categories:

Table 2. C51 Core SFRs

Mnemonic |

Add |

Name |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

ACC |

E0h |

Accumulator |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

B |

F0h |

B Register |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

PSW |

D0h |

Program Status Word |

CY |

AC |

F0 |

RS1 |

RS0 |

OV |

F1 |

P |

|

|

|

|

|

|

|

|

|

|

|

SP |

81h |

Stack Pointer |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

|

|

Data Pointer Low |

|

|

|

|

|

|

|

|

DPL |

82h |

byte |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

LSB of DPTR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Data Pointer High |

|

|

|

|

|

|

|

|

DPH |

83h |

byte |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

MSB of DPTR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 3. I/O Port SFRs

Mnemonic |

Add |

Name |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

P0 |

80h |

Port 0 |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

P1 |

90h |

Port 1 |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

P2 |

A0h |

Port 2 |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

P3 |

B0h |

Port 3 |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

P4 |

C0h |

Port 4 (x2) |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

Table 4. Timers SFRs

Mnemonic |

Add |

Name |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

TH0 |

8Ch |

Timer/Counter 0 High |

– |

– |

– |

– |

– |

– |

– |

– |

|

byte |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

TL0 |

8Ah |

Timer/Counter 0 Low |

– |

– |

– |

– |

– |

– |

– |

– |

|

byte |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

TH1 |

8Dh |

Timer/Counter 1 High |

– |

– |

– |

– |

– |

– |

– |

– |

|

byte |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

TL1 |

8Bh |

Timer/Counter 1 Low |

– |

– |

– |

– |

– |

– |

– |

– |

|

byte |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

TH2 |

CDh |

Timer/Counter 2 High |

– |

– |

– |

– |

– |

– |

– |

– |

|

byte |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

TL2 |

CCh |

Timer/Counter 2 Low |

– |

– |

– |

– |

– |

– |

– |

– |

|

byte |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

TCON |

88h |

Timer/Counter 0 and |

TF1 |

TR1 |

TF0 |

TR0 |

IE1 |

IT1 |

IE0 |

IT0 |

|

1 control |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

TMOD |

89h |

Timer/Counter 0 and |

GATE1 |

C/T1# |

M11 |

M01 |

GATE0 |

C/T0# |

M10 |

M00 |

|

1 Modes |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

8A/T89C51CC01

4129N–CAN–03/08

A/T89C51CC01

A/T89C51CC01

Table 4. Timers SFRs (Continued) |

|

|

|

|

|

|

|

|

|||

Mnemonic |

Add |

Name |

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

T2CON |

C8h |

Timer/Counter 2 |

|

TF2 |

EXF2 |

RCLK |

TCLK |

EXEN2 |

TR2 |

C/T2# |

CP/RL2# |

control |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T2MOD |

C9h |

Timer/Counter 2 |

|

– |

– |

– |

– |

– |

– |

T2OE |

DCEN |

Mode |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Timer/Counter 2 |

|

|

|

|

|

|

|

|

|

RCAP2H |

CBh |

Reload/Capture High |

|

– |

– |

– |

– |

– |

– |

– |

– |

|

|

byte |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Timer/Counter 2 |

|

|

|

|

|

|

|

|

|

RCAP2L |

CAh |

Reload/Capture Low |

|

– |

– |

– |

– |

– |

– |

– |

– |

|

|

byte |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WDTRST |

A6h |

Watchdog Timer |

|

– |

– |

– |

– |

– |

– |

– |

– |

Reset |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WDTPRG |

A7h |

Watchdog Timer |

|

– |

– |

– |

– |

– |

S2 |

S1 |

S0 |

Program |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 5. Serial I/O Port SFRs |

|

|

|

|

|

|

|

|

|||

Mnemonic |

Add |

Name |

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

SCON |

98h |

Serial Control |

|

FE/SM0 |

SM1 |

SM2 |

REN |

TB8 |

RB8 |

TI |

RI |

|

|

|

|

|

|

|

|

|

|

|

|

SBUF |

99h |

Serial Data Buffer |

|

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

|

SADEN |

B9h |

Slave Address Mask |

|

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

|

SADDR |

A9h |

Slave Address |

|

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

|

Table 6. |

PCA SFRs |

|

|

|

|

|

|

|

|

|

Mnemonic |

Add |

Name |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

CCON |

D8h |

PCA Timer/Counter Control |

CF |

CR |

– |

CCF4 |

CCF3 |

CCF2 |

CCF1 |

CCF0 |

|

|

|

|

|

|

|

|

|

|

|

CMOD |

D9h |

PCA Timer/Counter Mode |

CIDL |

WDTE |

– |

– |

– |

CPS1 |

CPS0 |

ECF |

|

|

|

|

|

|

|

|

|

|

|

CL |

E9h |

PCA Timer/Counter Low byte |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

CH |

F9h |

PCA Timer/Counter High byte |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

CCAPM0 |

DAh |

PCA Timer/Counter Mode 0 |

|

ECOM0 |

CAPP0 |

CAPN0 |

MAT0 |

TOG0 |

PWM0 |

ECCF0 |

CCAPM1 |

DBh |

PCA Timer/Counter Mode 1 |

|

ECOM1 |

CAPP1 |

CAPN1 |

MAT1 |

TOG1 |

PWM1 |

ECCF1 |

CCAPM2 |

DCh |

PCA Timer/Counter Mode 2 |

– |

ECOM2 |

CAPP2 |

CAPN2 |

MAT2 |

TOG2 |

PWM2 |

ECCF2 |

CCAPM3 |

DDh |

PCA Timer/Counter Mode 3 |

|

ECOM3 |

CAPP3 |

CAPN3 |

MAT3 |

TOG3 |

PWM3 |

ECCF3 |

CCAPM4 |

DEh |

PCA Timer/Counter Mode 4 |

|

ECOM4 |

CAPP4 |

CAPN4 |

MAT4 |

TOG4 |

PWM4 |

ECCF4 |

|

|

|

|

|

|

|

|

|

|

|

CCAP0H |

FAh |

PCA Compare Capture Module 0 H |

CCAP0H7 |

CCAP0H6 |

CCAP0H5 |

CCAP0H4 |

CCAP0H3 |

CCAP0H2 |

CCAP0H1 |

CCAP0H0 |

CCAP1H |

FBh |

PCA Compare Capture Module 1 H |

CCAP1H7 |

CCAP1H6 |

CCAP1H5 |

CCAP1H4 |

CCAP1H3 |

CCAP1H2 |

CCAP1H1 |

CCAP1H0 |

CCAP2H |

FCh |

PCA Compare Capture Module 2 H |

CCAP2H7 |

CCAP2H6 |

CCAP2H5 |

CCAP2H4 |

CCAP2H3 |

CCAP2H2 |

CCAP2H1 |

CCAP2H0 |

CCAP3H |

FDh |

PCA Compare Capture Module 3 H |

CCAP3H7 |

CCAP3H6 |

CCAP3H5 |

CCAP3H4 |

CCAP3H3 |

CCAP3H2 |

CCAP3H1 |

CCAP3H0 |

CCAP4H |

FEh |

PCA Compare Capture Module 4 H |

CCAP4H7 |

CCAP4H6 |

CCAP4H5 |

CCAP4H4 |

CCAP4H3 |

CCAP4H2 |

CCAP4H1 |

CCAP4H0 |

|

|

|

|

|

|

|

|

|

|

|

9

4129N–CAN–03/08

Table 6. PCA SFRs (Continued)

Mnemonic |

Add |

Name |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

CCAP0L |

EAh |

PCA Compare Capture Module 0 L |

CCAP0L7 |

CCAP0L6 |

CCAP0L5 |

CCAP0L4 |

CCAP0L3 |

CCAP0L2 |

CCAP0L1 |

CCAP0L0 |

CCAP1L |

EBh |

PCA Compare Capture Module 1 L |

CCAP1L7 |

CCAP1L6 |

CCAP1L5 |

CCAP1L4 |

CCAP1L3 |

CCAP1L2 |

CCAP1L1 |

CCAP1L0 |

CCAP2L |

ECh |

PCA Compare Capture Module 2 L |

CCAP2L7 |

CCAP2L6 |

CCAP2L5 |

CCAP2L4 |

CCAP2L3 |

CCAP2L2 |

CCAP2L1 |

CCAP2L0 |

CCAP3L |

EDh |

PCA Compare Capture Module 3 L |

CCAP3L7 |

CCAP3L6 |

CCAP3L5 |

CCAP3L4 |

CCAP3L3 |

CCAP3L2 |

CCAP3L1 |

CCAP3L0 |

CCAP4L |

EEh |

PCA Compare Capture Module 4 L |

CCAP4L7 |

CCAP4L6 |

CCAP4L5 |

CCAP4L4 |

CCAP4L3 |

CCAP4L2 |

CCAP4L1 |

CCAP4L0 |

|

|

|

|

|

|

|

|

|

|

|

Table 7. Interrupt SFRs |

|

|

|

|

|

|

|

|

|||

Mnemonic |

Add |

Name |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

IEN0 |

A8h |

Interrupt Enable |

EA |

EC |

ET2 |

ES |

ET1 |

EX1 |

ET0 |

EX0 |

|

Control 0 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

IEN1 |

E8h |

Interrupt Enable |

– |

– |

– |

– |

– |

ETIM |

EADC |

ECAN |

|

Control 1 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

IPL0 |

B8h |

Interrupt Priority |

– |

PPC |

PT2 |

PS |

PT1 |

PX1 |

PT0 |

PX0 |

|

Control Low 0 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

IPH0 |

B7h |

Interrupt Priority |

– |

PPCH |

PT2H |

PSH |

PT1H |

PX1H |

PT0H |

PX0H |

|

Control High 0 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

IPL1 |

F8h |

Interrupt Priority |

– |

– |

– |

– |

– |

POVRL |

PADCL |

PCANL |

|

Control Low 1 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

IPH1 |

F7h |

Interrupt Priority |

– |

– |

– |

– |

– |

POVRH |

PADCH |

PCANH |

|

Control High1 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Table 8. ADC SFRs

Mnemonic |

Add |

Name |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

ADCON |

F3h |

ADC Control |

– |

PSIDLE |

ADEN |

ADEOC |

ADSST |

SCH2 |

SCH1 |

SCH0 |

|

|

|

|

|

|

|

|

|

|

|

ADCF |

F6h |

ADC Configuration |

CH7 |

CH6 |

CH5 |

CH4 |

CH3 |

CH2 |

CH1 |

CH0 |

|

|

|

|

|

|

|

|

|

|

|

ADCLK |

F2h |

ADC Clock |

– |

– |

– |

PRS4 |

PRS3 |

PRS2 |

PRS1 |

PRS0 |

|

|

|

|

|

|

|

|

|

|

|

ADDH |

F5h |

ADC Data High byte |

ADAT9 |

ADAT8 |

ADAT7 |

ADAT6 |

ADAT5 |

ADAT4 |

ADAT3 |

ADAT2 |

|

|

|

|

|

|

|

|

|

|

|

ADDL |

F4h |

ADC Data Low byte |

– |

– |

– |

– |

– |

– |

ADAT1 |

ADAT0 |

|

|

|

|

|

|

|

|

|

|

|

Table 9. CAN SFRs

Mnemonic |

Add |

Name |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

CANGCON |

ABh |

CAN General |

ABRQ |

OVRQ |

TTC |

SYNCTTC |

AUT– |

TEST |

ENA |

GRES |

|

Control |

BAUD |

||||||||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

CANGSTA |

AAh |

CAN General |

– |

OVFG |

– |

TBSY |

RBSY |

ENFG |

BOFF |

ERRP |

|

Status |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CANGIT |

9Bh |

CAN General |

CANIT |

– |

OVRTIM |

OVRBUF |

SERG |

CERG |

FERG |

AERG |

|

Interrupt |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CANBT1 |

B4h |

CAN Bit Timing 1 |

– |

BRP5 |

BRP4 |

BRP3 |

BRP2 |

BRP1 |

BRP0 |

– |

|

|

|

|

|

|

|

|

|

|

|

|

|

CANBT2 |

B5h |

CAN Bit Timing 2 |

– |

SJW1 |

SJW0 |

– |

PRS2 |

PRS1 |

PRS0 |

– |

|

|

|

|

|

|

|

|

|

|

|

|

|

CANBT3 |

B6h |

CAN Bit Timing 3 |

– |

PHS22 |

PHS21 |

PHS20 |

PHS12 |

PHS11 |

PHS10 |

SMP |

|

|

|

|

|

|

|

|

|

|

|

|

10 A/T89C51CC01

4129N–CAN–03/08

A/T89C51CC01

A/T89C51CC01

Table 9. CAN SFRs (Continued)

Mnemonic |

Add |

Name |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

CANEN1 |

CEh |

CAN Enable |

– |

ENCH14 |

ENCH13 |

ENCH12 |

ENCH11 |

ENCH10 |

ENCH9 |

ENCH8 |

|

Channel byte 1 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CANEN2 |

CFh |

CAN Enable |

ENCH7 |

ENCH6 |

ENCH5 |

ENCH4 |

ENCH3 |

ENCH2 |

ENCH1 |

ENCH0 |

|

Channel byte 2 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CANGIE |

C1h |

CAN General |

– |

– |

ENRX |

ENTX |

ENERCH |

ENBUF |

ENERG |

– |

|

Interrupt Enable |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Interrupt |

|

|

|

|

|

|

|

|

|

CANIE1 |

C2h |

Enable Channel |

– |

IECH14 |

IECH13 |

IECH12 |

IECH11 |

IECH10 |

IECH9 |

IECH8 |

|

|

|

byte 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Interrupt |

|

|

|

|

|

|

|

|

|

CANIE2 |

C3h |

Enable Channel |

IECH7 |

IECH6 |

IECH5 |

IECH4 |

IECH3 |

IECH2 |

IECH1 |

IECH0 |

|

|

|

byte 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Status |

|

|

|

|

|

|

|

|

|

CANSIT1 |

BAh |

Interrupt Channel |

– |

SIT14 |

SIT13 |

SIT12 |

SIT11 |

SIT10 |

SIT9 |

SIT8 |

|

|

|

byte1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Status |

|

|

|

|

|

|

|

|

|

CANSIT2 |

BBh |

Interrupt Channel |

SIT7 |

SIT6 |

SIT5 |

SIT4 |

SIT3 |

SIT2 |

SIT1 |

SIT0 |

|

|

|

byte2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CANTCON |

A1h |

CAN Timer |

TPRESC 7 |

TPRESC 6 |

TPRESC 5 |

TPRESC 4 |

TPRESC 3 |

TPRESC 2 |

TPRESC 1 |

TPRESC 0 |

|

Control |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CANTIMH |

ADh |

CAN Timer high |

CANTIM |

CANTIM |

CANTIM |

CANTIM |

CANTIM |

CANTIM |

CANTIM |

CANTIM |

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

||||

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

CANTIML |

ACh |

CAN Timer low |

CANTIM 7 |

CANTIM 6 |

CANTIM 5 |

CANTIM 4 |

CANTIM 3 |

CANTIM 2 |

CANTIM 1 |

CANTIM 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

CANSTMH |

AFh |

CAN Timer Stamp |

TIMSTMP |

TIMSTMP |

TIMSTMP |

TIMSTMP |

TIMSTMP |

TIMSTMP |

TIMSTMP |

TIMSTMP |

|

high |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|||

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

CANSTML |

AEh |

CAN Timer Stamp |

TIMSTMP |

TIMSTMP |

TIMSTMP |

TIMSTMP |

TIMSTMP |

TIMSTMP |

TIMSTMP |

TIMSTMP |

|

low |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|||

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

CANTTCH |

A5h |

CAN Timer TTC |

TIMTTC 15 |

TIMTTC 14 |

TIMTTC 13 |

TIMTTC 12 |

TIMTTC 11 |

TIMTTC 10 |

TIMTTC 9 |

TIMTTC 8 |

|

high |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CANTTCL |

A4h |

CAN Timer TTC |

TIMTTC |

TIMTTC |

TIMTTC |

TIMTTC |

TIMTTC |

TIMTTC |

TIMTTC |

TIMTTC |

|

low |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|||

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

CANTEC |

9Ch |

CAN Transmit |

TEC7 |

TEC6 |

TEC5 |

TEC4 |

TEC3 |

TEC2 |

TEC1 |

TEC0 |

|

Error Counter |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CANREC |

9Dh |

CAN Receive |

REC7 |

REC6 |

REC5 |

REC4 |

REC3 |

REC2 |

REC1 |

REC0 |

|

Error Counter |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CANPAGE |

B1h |

CAN Page |

CHNB3 |

CHNB2 |

CHNB1 |

CHNB0 |

AINC |

INDX2 |

INDX1 |

INDX0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

CANSTCH |

B2h |

CAN Status |

DLCW |

TXOK |

RXOK |

BERR |

SERR |

CERR |

FERR |

AERR |

|

Channel |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CANCONH |

B3h |

CAN Control |

CONCH1 |

CONCH0 |

RPLV |

IDE |

DLC3 |

DLC2 |

DLC1 |

DLC0 |

|

Channel |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CANMSG |

A3h |

CAN Message |

MSG7 |

MSG6 |

MSG5 |

MSG4 |

MSG3 |

MSG2 |

MSG1 |

MSG0 |

|

Data |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

11

4129N–CAN–03/08

Table 9. CAN SFRs (Continued)

Mnemonic |

Add |

Name |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Identifier Tag |

IDT10 |

IDT9 |

IDT8 |

IDT7 |

IDT6 |

IDT5 |

IDT4 |

IDT3 |

|

|

byte 1(Part A) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

CANIDT1 |

BCh |

|

|

|

|

|

|

|

|

|

|

|

CAN Identifier Tag |

IDT28 |

IDT27 |

IDT26 |

IDT25 |

IDT24 |

IDT23 |

IDT22 |

IDT21 |

|

|

byte 1(PartB) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Identifier Tag |

IDT2 |

IDT1 |

IDT0 |

– |

– |

– |

– |

– |

|

|

byte 2 (PartA) |

||||||||

CANIDT2 |

BDh |

|

|

|

|

|

|

|

|

|

CAN Identifier Tag |

|

|

|

|

|

|

|

|

||

|

|

IDT20 |

IDT19 |

IDT18 |

IDT17 |

IDT16 |

IDT15 |

IDT14 |

IDT13 |

|

|

|

byte 2 (PartB) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Identifier Tag |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

byte 3(PartA) |

||||||||

CANIDT3 |

BEh |

|

|

|

|

|

|

|

|

|

CAN Identifier Tag |

|

|

|

|

|

|

|

|

||

|

|

IDT12 |

IDT11 |

IDT10 |

IDT9 |

IDT8 |

IDT7 |

IDT6 |

IDT5 |

|

|

|

byte 3(PartB) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Identifier Tag |

– |

– |

– |

– |

– |

RTRTAG |

– |

RB0TAG |

|

|

byte 4(PartA) |

||||||||

|

|

|

|

|

|

|

|

|||

CANIDT4 |

BFh |

|

|

|

|

|

|

|

|

|

CAN Identifier Tag |

|

|

|

|

|

|

|

|

||

|

|

IDT4 |

IDT3 |

IDT2 |

IDT1 |

IDT0 |

– |

RB1TAG |

– |

|

|

|

byte 4(PartB) |

||||||||

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Identifier |

|

|

|

|

|

|

|

|

|

|

Mask byte |

IDMSK10 |

IDMSK9 |

IDMSK8 |

IDMSK7 |

IDMSK6 |

IDMSK5 |

IDMSK4 |

IDMSK3 |

|

|

1(PartA) |

||||||||

CANIDM1 |

C4h |

|

|

|

|

|

|

|

|

|

CAN Identifier |

|

|

|

|

|

|

|

|

||

|

|

IDMSK28 |

IDMSK27 |

IDMSK26 |

IDMSK25 |

IDMSK24 |

IDMSK23 |

IDMSK22 |

IDMSK21 |

|

|

|

Mask byte |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1(PartB) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Identifier |

|

|

|

|

|

|

|

|

|

|

Mask byte |

IDMSK2 |

IDMSK1 |

IDMSK0 |

– |

– |

– |

– |

– |

|

|

2(PartA) |

||||||||

CANIDM2 |

C5h |

|

|

|

|

|

|

|

|

|

CAN Identifier |

|

|

|

|

|

|

|

|

||

|

|

IDMSK20 |

IDMSK19 |

IDMSK18 |

IDMSK17 |

IDMSK16 |

IDMSK15 |

IDMSK14 |

IDMSK13 |

|

|

|

Mask byte |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

2(PartB) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Identifier |

|

|

|

|

|

|

|

|

|

|

Mask byte |

– |

– |

– |

– |

– |

– |

– |

– |

|

|

3(PartA) |

||||||||

CANIDM3 |

C6h |

|

|

|

|

|

|

|

|

|

CAN Identifier |

|

|

|

|

|

|

|

|

||

|

|

IDMSK12 |

IDMSK11 |

IDMSK10 |

IDMSK9 |

IDMSK8 |

IDMSK7 |

IDMSK6 |

IDMSK5 |

|

|

|

Mask byte |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

3(PartB) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN Identifier |

|

|

|

|

|

|

|

|

|

|

Mask byte |

– |

– |

– |

– |

– |

RTRMSK |

– |

IDEMSK |

|

|

4(PartA) |

||||||||

|

|

|

|

|

|

|

||||

CANIDM4 |

C7h |

|

|

|

|

|

|

|

|

|

CAN Identifier |

|

|

|

|

|

|

|

|

||

|

|

IDMSK4 |

IDMSK3 |

IDMSK2 |

IDMSK1 |

IDMSK0 |

– |

|

– |

|

|

|

Mask byte |

|

|||||||

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

4(PartB) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 10. |

Other SFRs |

|

|

|

|

|

|

|

|

|