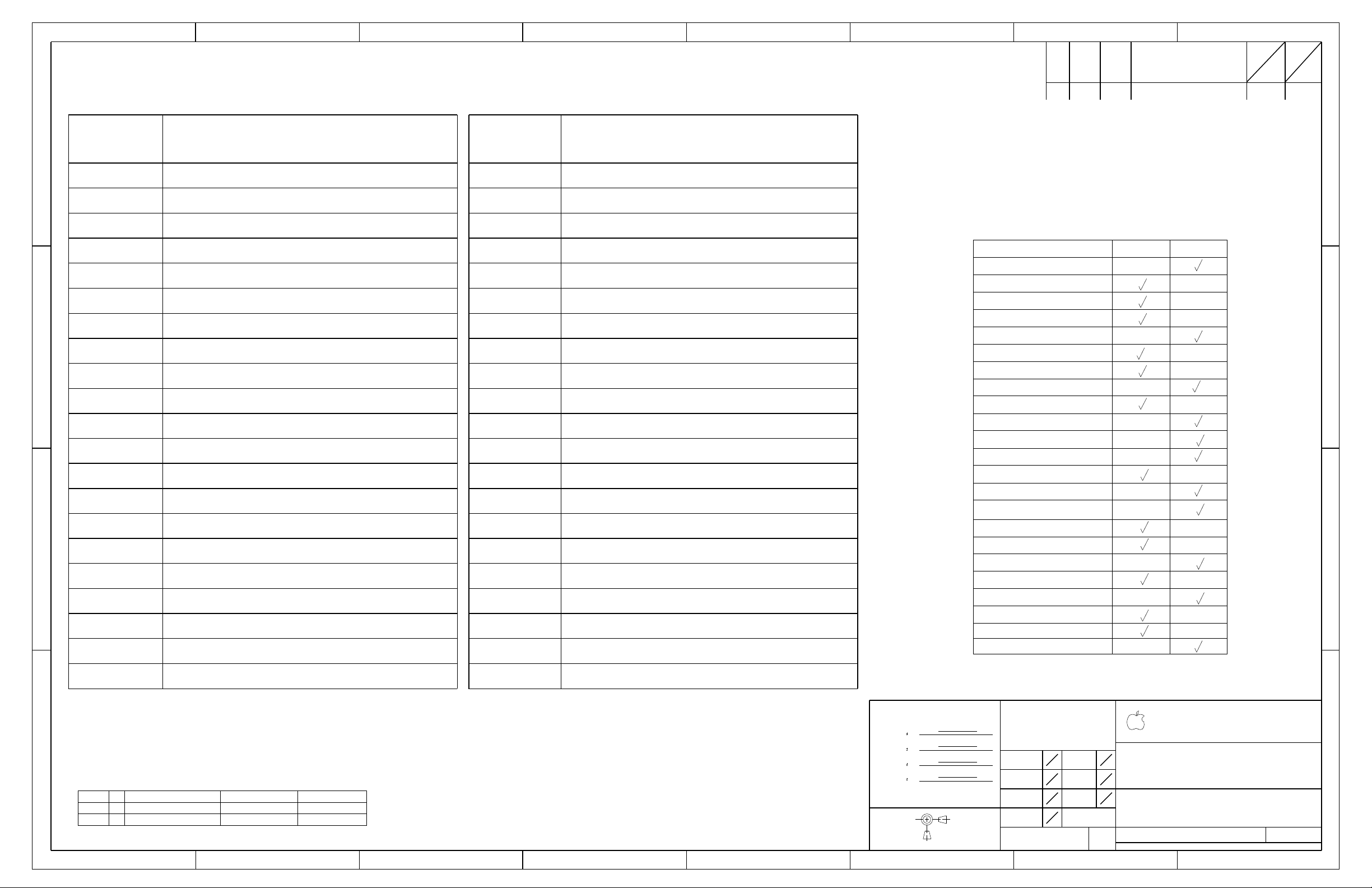

Page 1

ANGLES

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

DATE

APPD

ENG

DATE

APPD

CK

ECN

ZONE

REV

DO NOT SCALE DRAWING

X.XXX

X.XX

XX

DIMENSIONS ARE IN MILLIMETERS

THIRD ANGLE PROJECTION

D

SIZE

APPLICABLE

NOTED AS

MATERIAL/FINISH

NONE

SCALE

DESIGNER

MFG APPD

DESIGN CK

RELEASE

QA APPD

ENG APPD

DRAFTER

METRIC

OF

SHT

DRAWING NUMBER

TITLE

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

Apple Computer Inc.

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

DESCRIPTION OF CHANGE

TABLE_5_ITEM

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_5_ITEM

PMU (POWER MANAGEMENT UNIT)

12/21/2004

SCHEM,MLB,PB17"

SERIAL DEBUG (JOLLY ROGER, PWR/NMI/RESET)

LMU, LIGHT SENSOR, BOOTBANGER, SLEEP LED

SPIDEY - KBD,TPAD,HALL EFFECT,PWR BUTTON

DUAL-CHANNEL LVDS

GPU_SS

MARVELL GIGABIT ETHERNET PHY

STUFF

3.3V / 5V SYSTEM POWER SUPPLIES

CPU CORE VOLTAGE POWER SUPPLY

INTERNAL CONNECTORS - DVD,

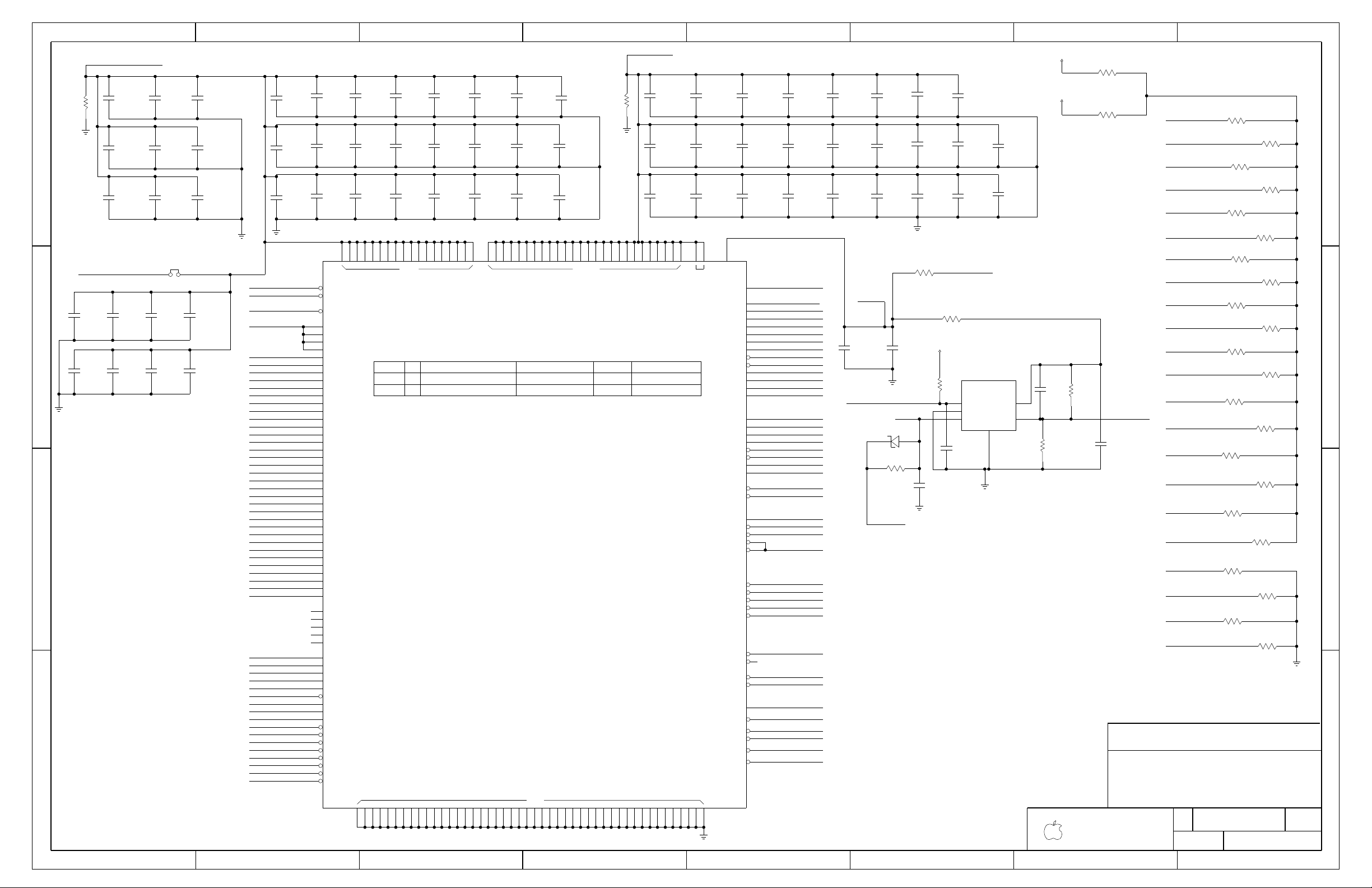

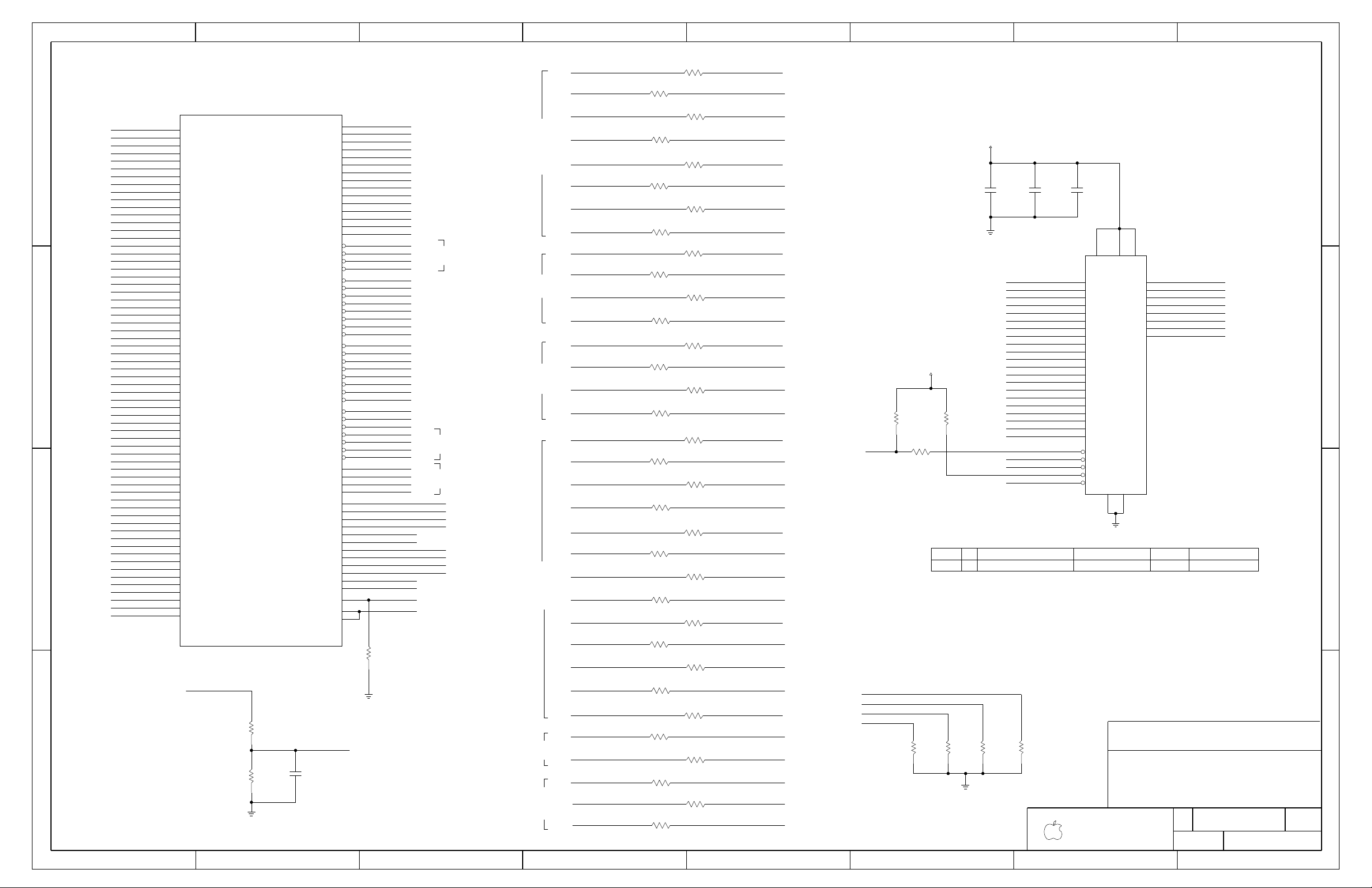

SYSTEM BLOCK DIAGRAM

23

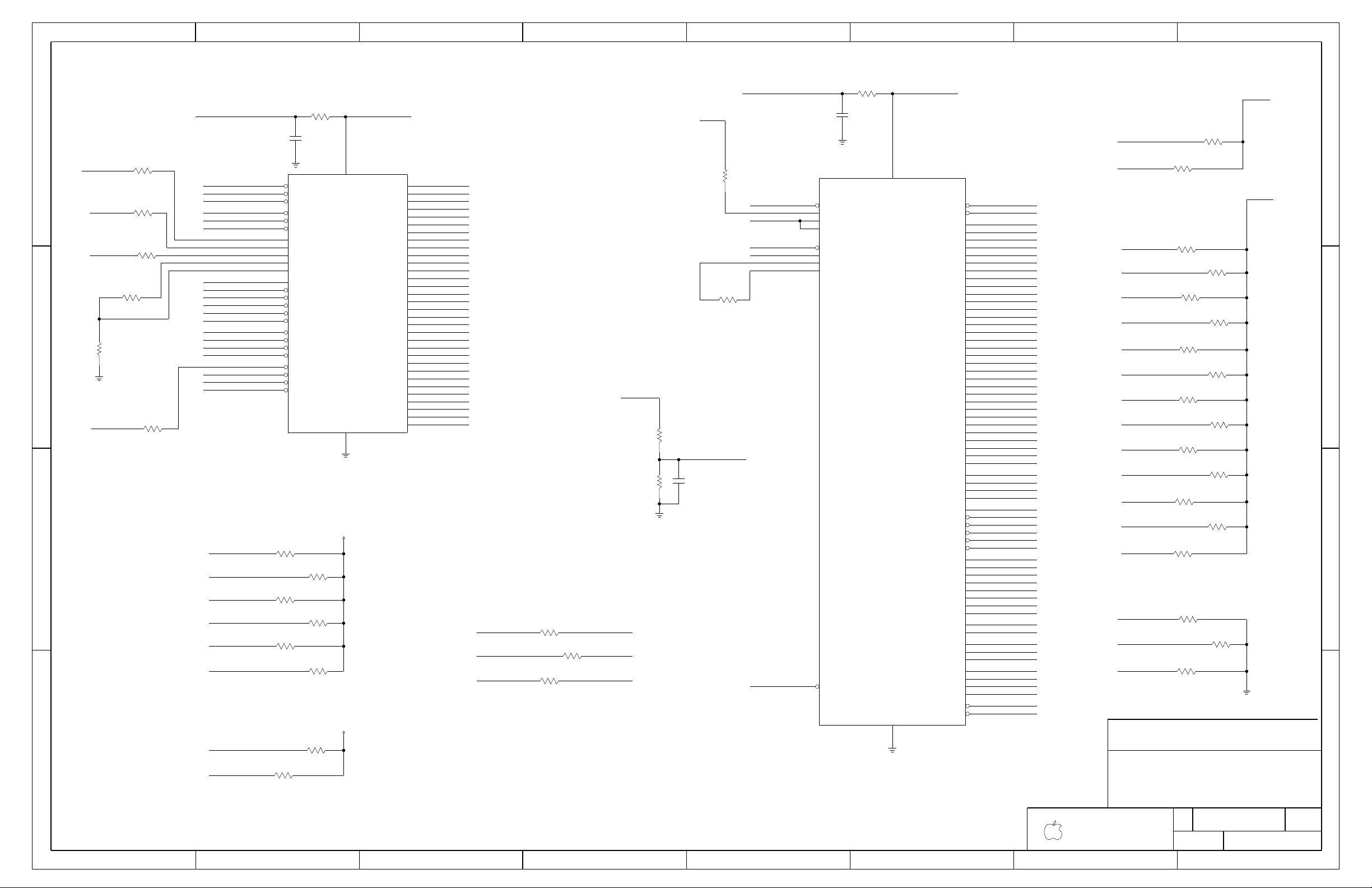

MPC7450 MAXBUS INTERFACE

200PIN DDR MEMORY SODIMM CONNECTORS

22

SCHEMATIC CREF AND NETLIST REPORTS

REVISION HISTORY (1 OF 1)

42-45

41

FIREWIRE A/B CONNECTORS, PORT POWER LIMITER

SIGNAL CONSTRAINTS (1 OF 3) - DIGITAL/CLK

5V_HD_LOGIC

INT_CLK

9

MPC7450 DATA

CARDSLOT, HARD DRIVE, LEFT USB/BLUETOOTH

6

8

10

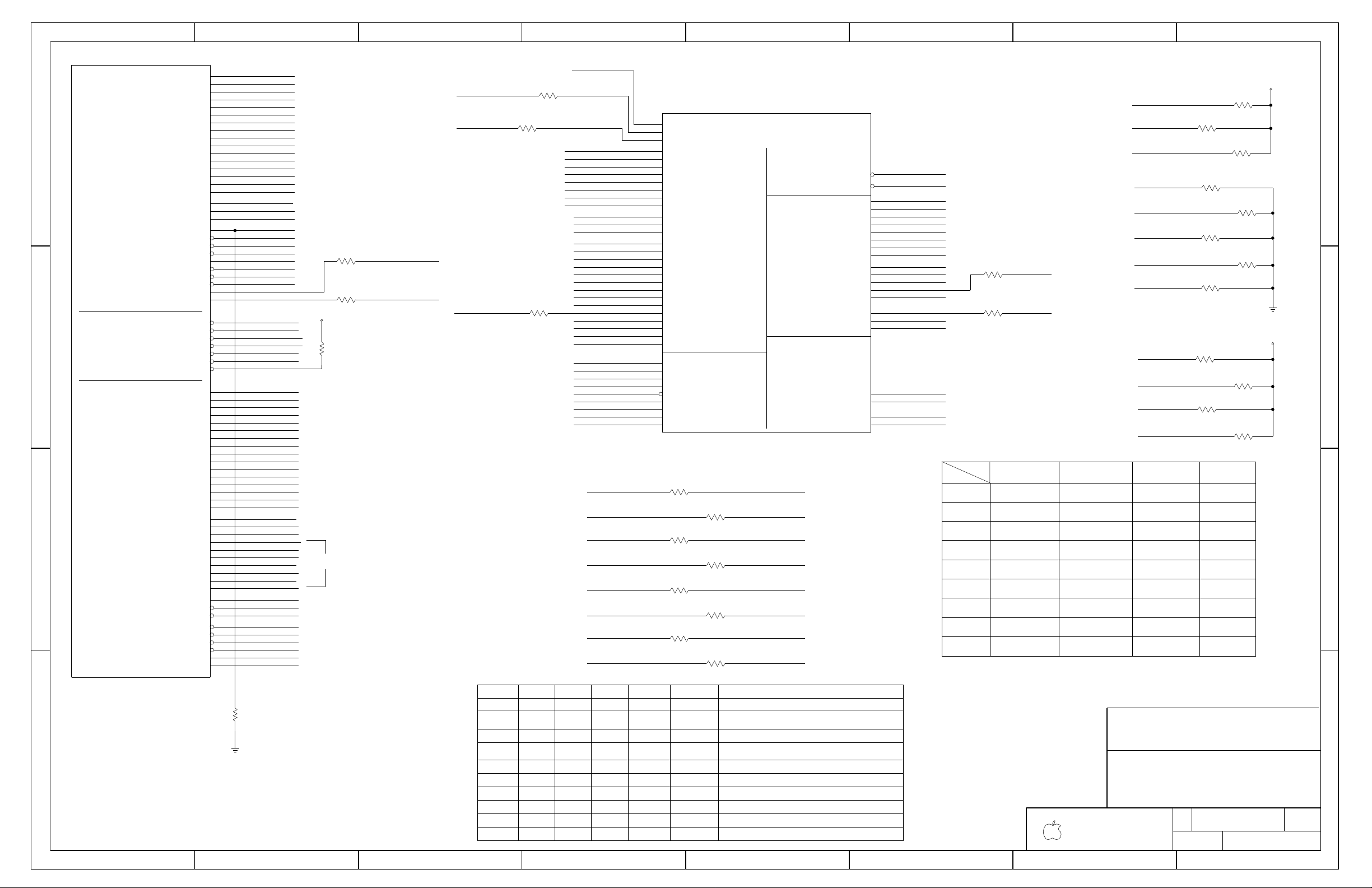

TITLE PAGE AND CONTENTS

24

28

NO_SSCG

SSCG

ATI_MEMIO_HI

BBANG

NEC_USB

EXT_TMDS

INT_TMDS

21

20

19

18

17

16

15

14

13

11

7

5

4

3

1

INTREPID AGP 4X/PCI

26

29

30

31

32

33

34

35

36

37

38

2

CPU PLL AND CONFIGURATION STRAPS

INTREPID MAXBUS AND BOOT STRAPS

M11 ANALOG, POWER, GND

SIL178 DUAL TMDS TRANSMITTER

M11 LVDS/TMDS/VGA/GPIO & GPU VCORE

M11 AGP & CLOCKS

INTREPID POWER RAILS

INTREPID DECOUPLING

CARDBUS CONTROLLER (PCI1510)

SIGNAL CONSTRAINTS (2 OF 3) - DIGITAL/DIFF

FIREWIRE A/B PHY

1.5V/ 1.8V / 2.5V SYSTEM POWER SUPPLIES

40

SIGNAL CONSTRAINTS (3 OF 3) - POWER NETS

FUNCTIONAL TEST POINTS

39

INTREPID ENET/FW/UATA/EIDE INTERFACES

D3_HOT

D3_COLD

USB 2.0

27

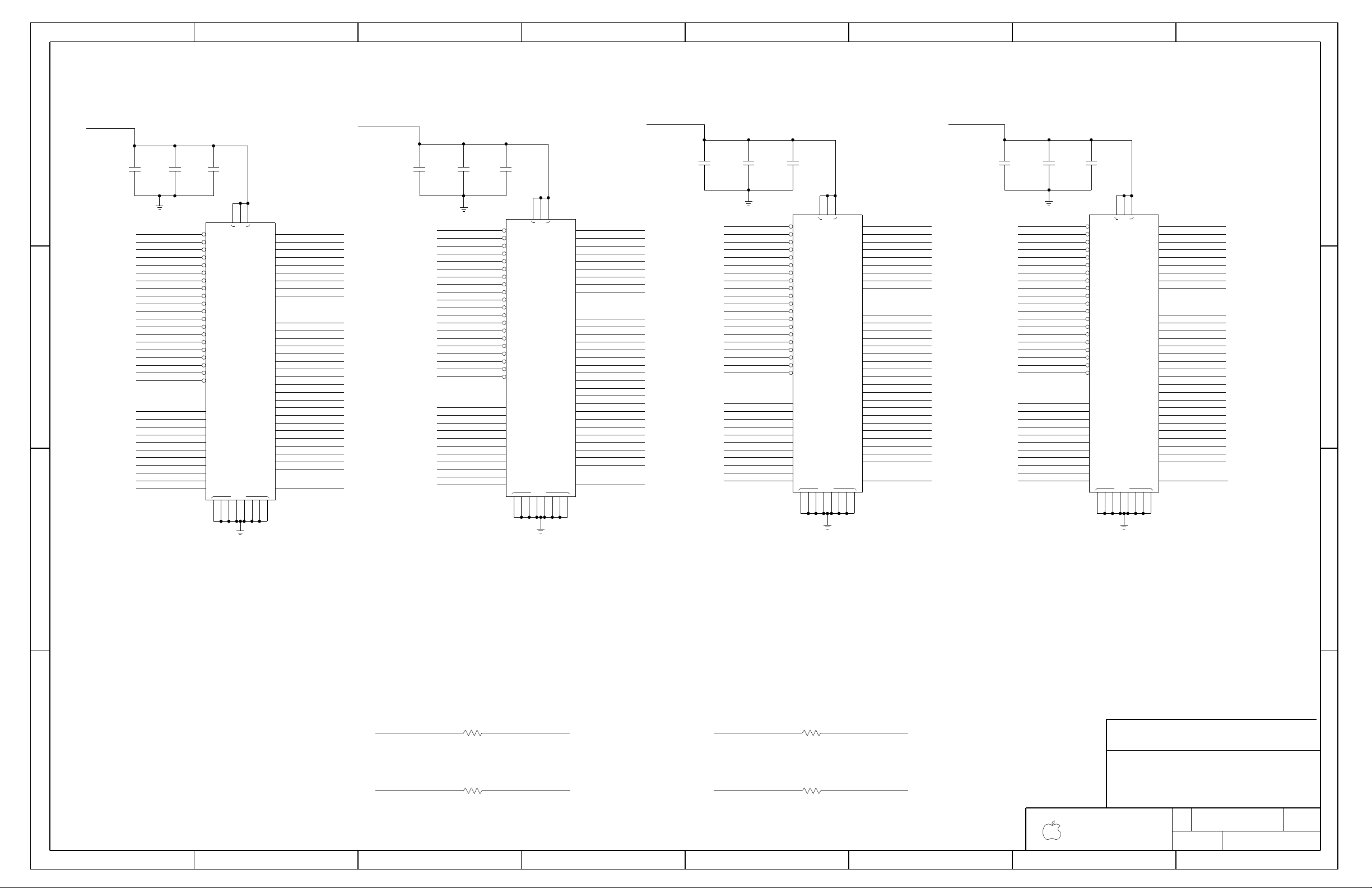

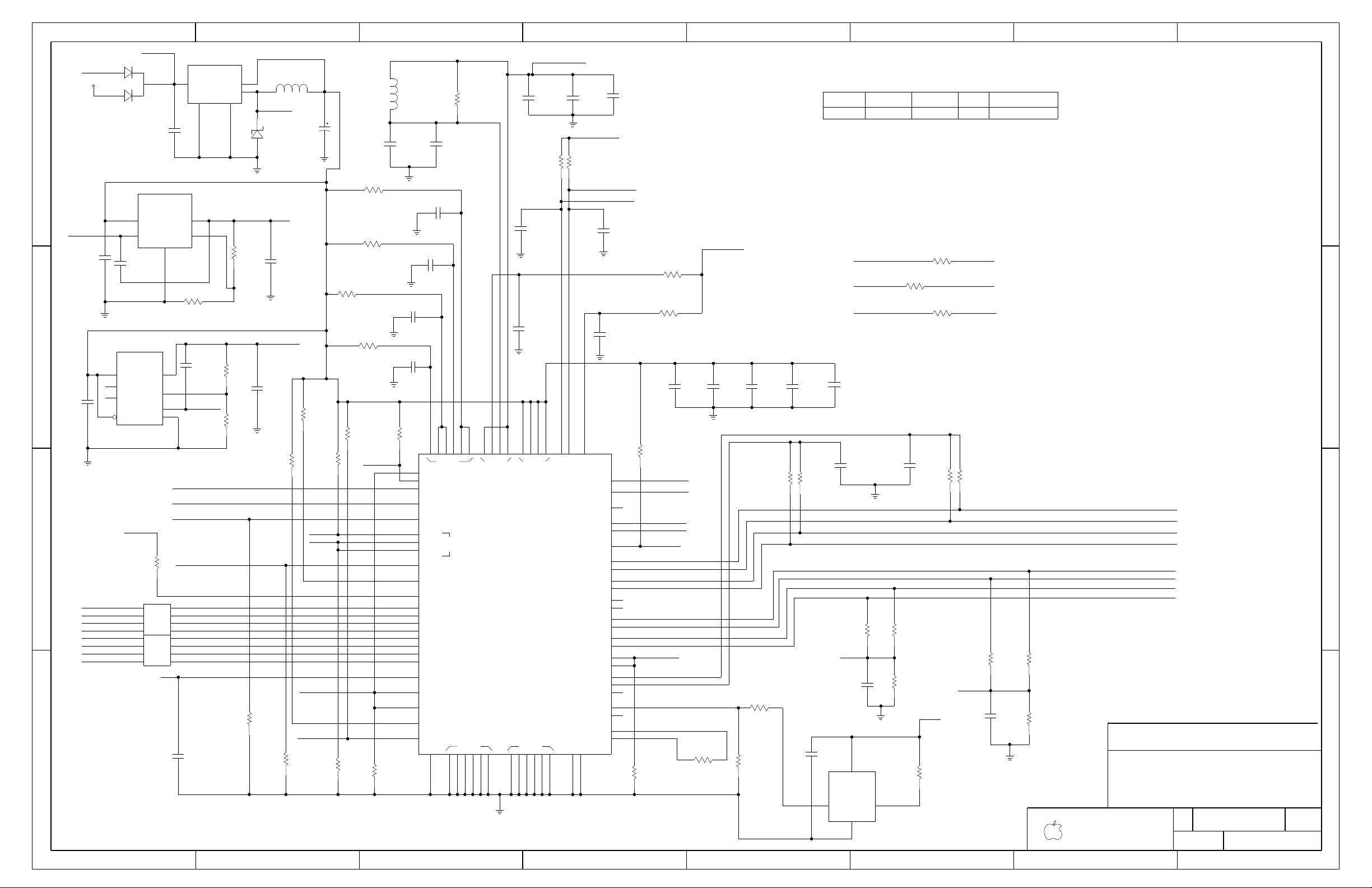

POWER BLOCK DIAGRAM

VCORE_OFFSET

ATI_MEMIO_LO

1_8V_MAXBUS

3V_HD_LOGIC

MMM

GPU_SWITCH

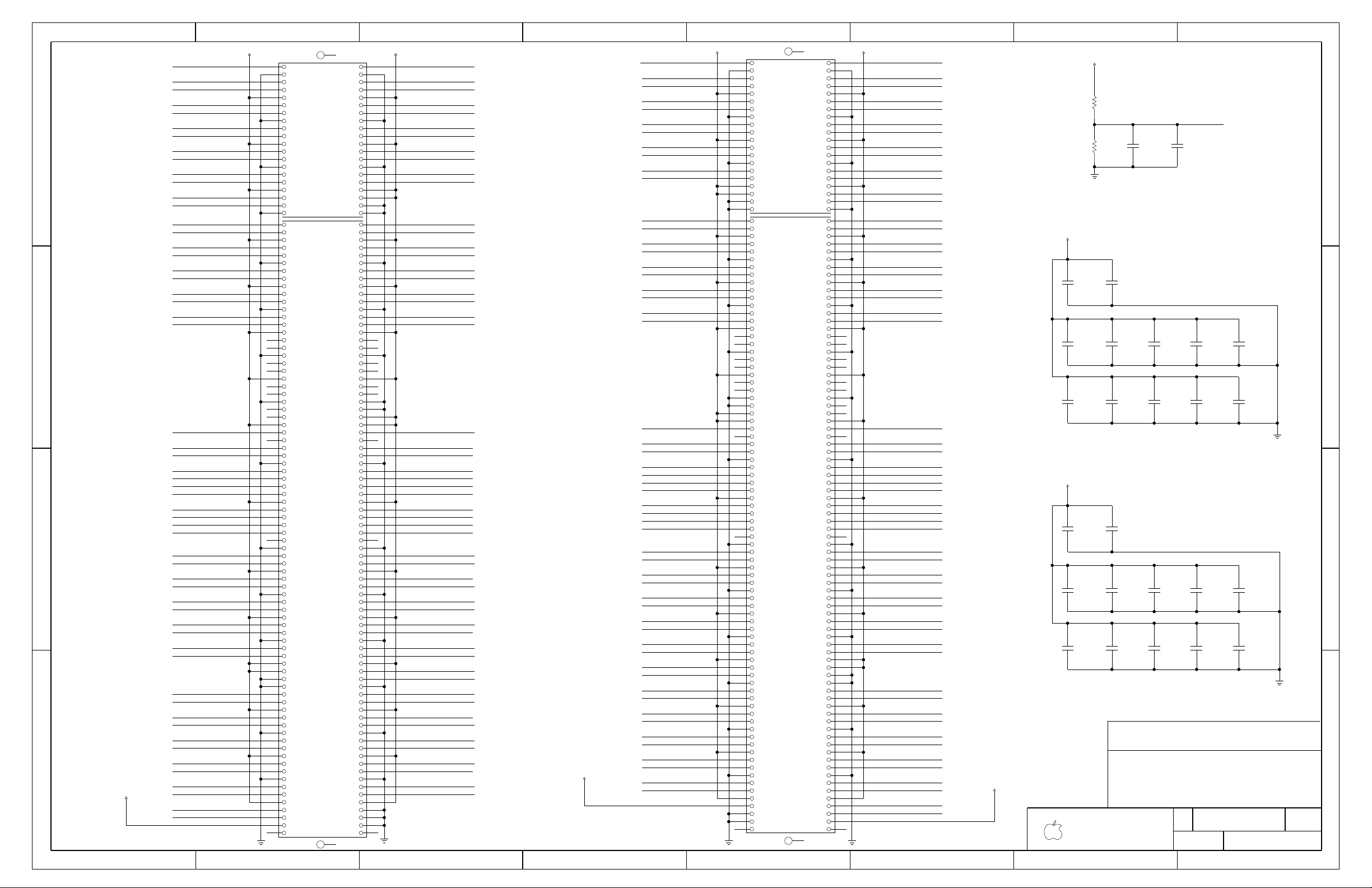

DDR MEMORY MUXES

12

MMM, BATTERY CURRENT SENSE

PCB NOTES AND HOLES

PAGEPAGE CONTENTSCONTENTS

NO STUFF

BOM OPTIONS

25

FAN CONTROLLER, MODEM, SOUND

VIDEO CONNECTORS - INVERTER, DVI, S-VIDEO

12.8V SYSTEM POWER SUPPLY / PMU POWER SUPPLY

BATTERY CHARGER AND CONNECTOR

NO_BBANG

INTREPID_USB

SERIAL_DEBUG

1_5V_MAXBUS

EXT_CLK

INTREPID GPIOS/SERIAL/USB INTERFACES/SSCG

INTREPID MEMORY INTERFACE / BOOT ROM

051-6694

1

SCH1

SCHEM,MLB,PB17

820-1688 PCB1

1

PCBF,MLB,PB17

SCHEM,MLB,PB17"

?

B

451

051-6694

B

PRODUCTION RELEASED

357142

12/21/04

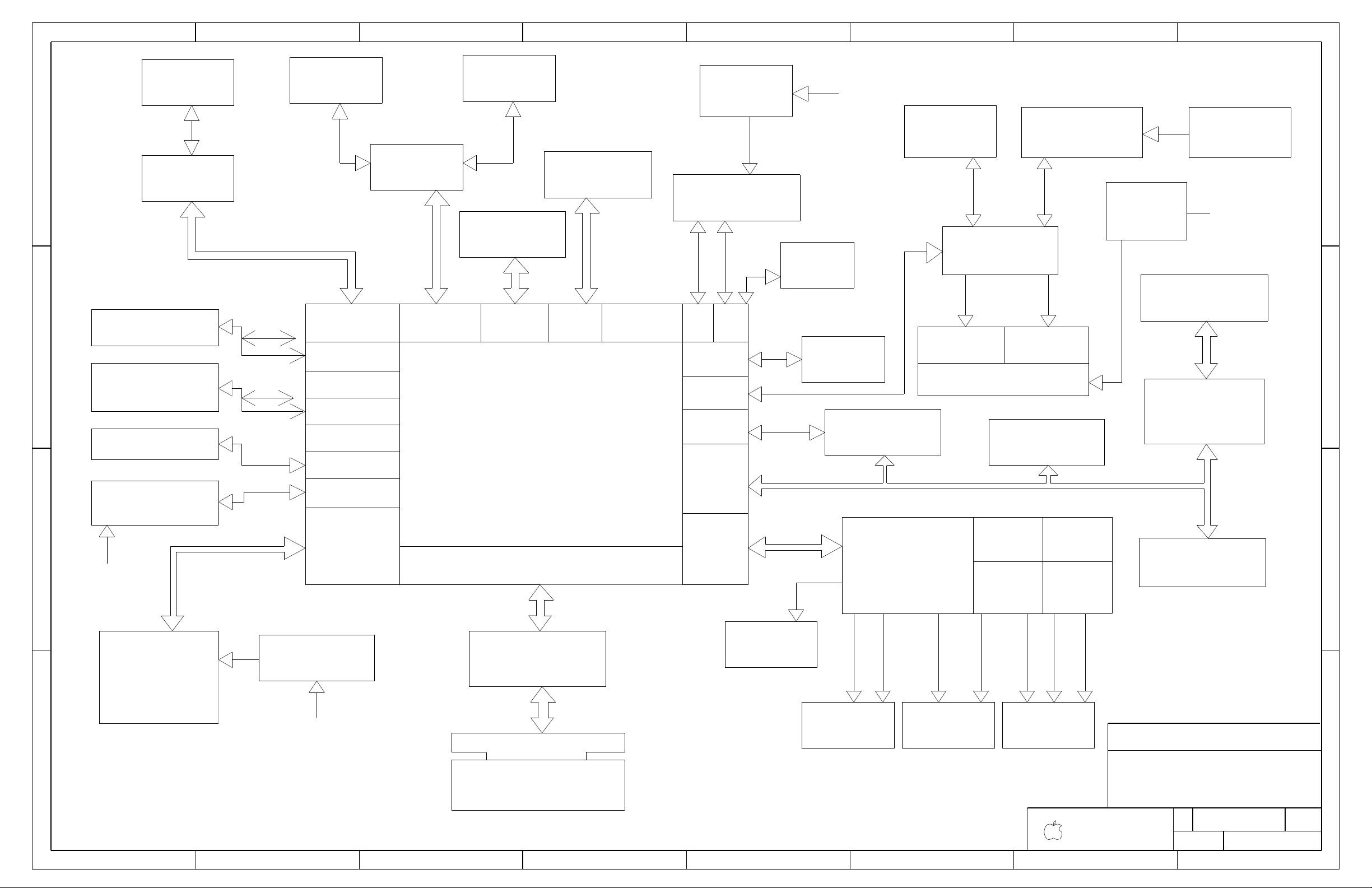

Page 2

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

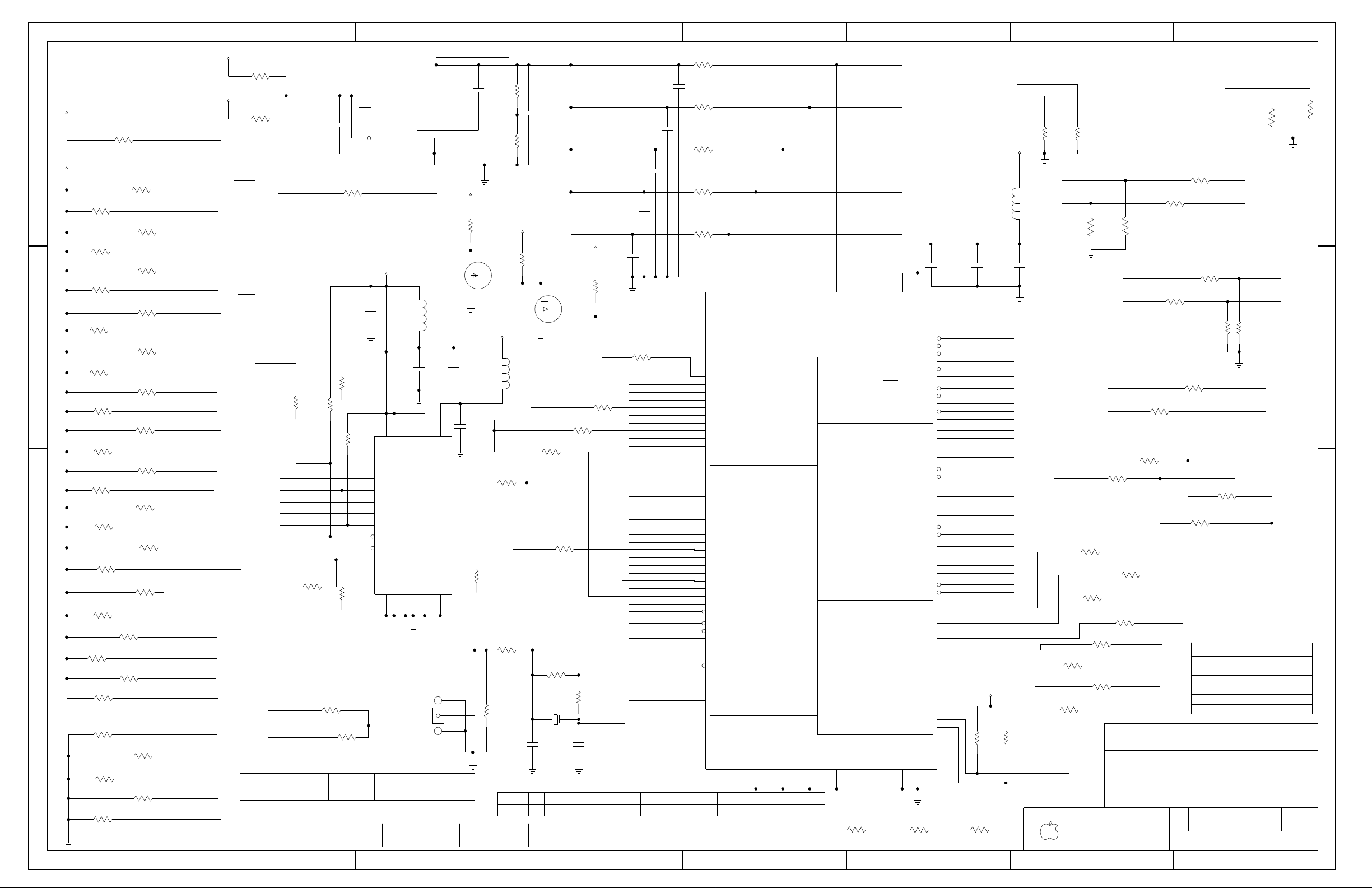

SYSTEM BLOCK DIAGRAM

J16

P.22

LVDS

(INTERNAL MEM)

COMPOSITE

S-VIDEO

EDID (I2C)

U43

66MHZ

32BITS

AGP BUS

1.5V/3.3V

P.28

EIDE

P.14

UATA 100

ULTRA ATA/100

J17

J7

Connector

LCD Panel S-Video

Connector

DVI-I

Connector

Inverter

Connector

J20/J23

U11/U12/U13/U14

P.14

USB PORT A

P.15

USB PORT B

P.15

USB PORT C

P.15

USB PORT D

P.15

USB PORT E

P.15

USB PORT F

P.15

MAXBUS

P.9

U42

PMU

64BIT DATA

32BIT ADDRESS

167MHZ

1.8V

MAXBUS

I2C

INTRPEID

J9

J3 (SHARE WITH LEFT USB)

J12

J3 (SHARE WITH BLUETOOTH)

ETHERNET

125MHZ

8BIT RX

8BIT TX

10/100/1000

3.3V

G/MII

4 DATA PAIRS

2 DATA PAIRS

@ 200MHz

100MHZ

8BIT TX/RX

3.3V

J13

Connector

P.14

CARDSLOT

P.14

FIREWIRE

P.14

800 MB/S

10/100/1000

NOT USED

LMU

P.26

I2C

I2S I2C

P.26

P.26

U52

P.27

CONTROLLER

USB 2.0

LIGHT SENSOR

KB LED

Keyboard

ConnectorConnector

TRACKPAD

J15

5V

SERIAL

U39

3.3V

SMBUS

J19

Connector

SUTRO (PWR)

U26

3.3V/5V

16/32 BITS

33MHZ

3.3V

33MHZ

32BITS

PCI BUS

TI PCI1510

CardBus

Controller

U48/J2/J4

(DDC TOO)

RGB

TMDS

2 DATA PAIRS

@ 400MHZ

P.15

P.14

(INTERNAL MEM)(INTERNAL MEM)

(INTERNAL MEM)

NOT USED

NOT USED

USB 2.0

P.26

J8

USB 2.0

MEMORY

CH. A

MEMORY

CH. C

MEMORY

CH. D

MEMORY

CH. B

P.15

SCCA

P.15

I2S I2C

Serial Debug

Connector

J5

U17

BOOT ROM

1M X 8

Fan

Circuit

Connector

TUBA (SOUND)

J14

Connector

OPTICAL DRIVE

J11

FireWire

PHY

U28

Connector

FW - B

J22

Connector

FW - A

J24

Connector

Ethernet

J18

U49

Ethernet

PHY

P.28

P.30

P.29

P.30

1394 OHCI

P.25

EIDE

P.32

Connector

Battery

J25

LED

SLEEP

Power Supply

& Charger

P.32-36

LMU

U36

PMU

P.31

P.24

I2C

P.32

CARDBUS

Connector

P.18

J10

P.24

P.10

P.18

Connector

AIRPOPT

J21

ATI M11

64MB

P.18-21

P.22

P.22 P.22

4X AGP

P.13

P.13

33MHZ

32BITS

PCI

P.14

BOOTROM

P.15

VIA/PMU

MEMORY BUS

2.5V

167MHZ

64BITS

2:1 DDR MUXES

P.10

DDR MEMORY

P.11

DDR SDRAM DIMM 0

DDR SDRAM DIMM 1

SO-DIMM Connector

P.12

P.7

Config

CPU PLL

APOLLO

CPU

(MPC7457)

P.5-6

P.26

Connector

Modem Board

P.25

BlueTooth

P.33

BACKUP BATTERY

RIGHT USB

P.25

LEFT USB

U44

P.25

INTREPID

UIDE

P.25

051-6694

2

B

45

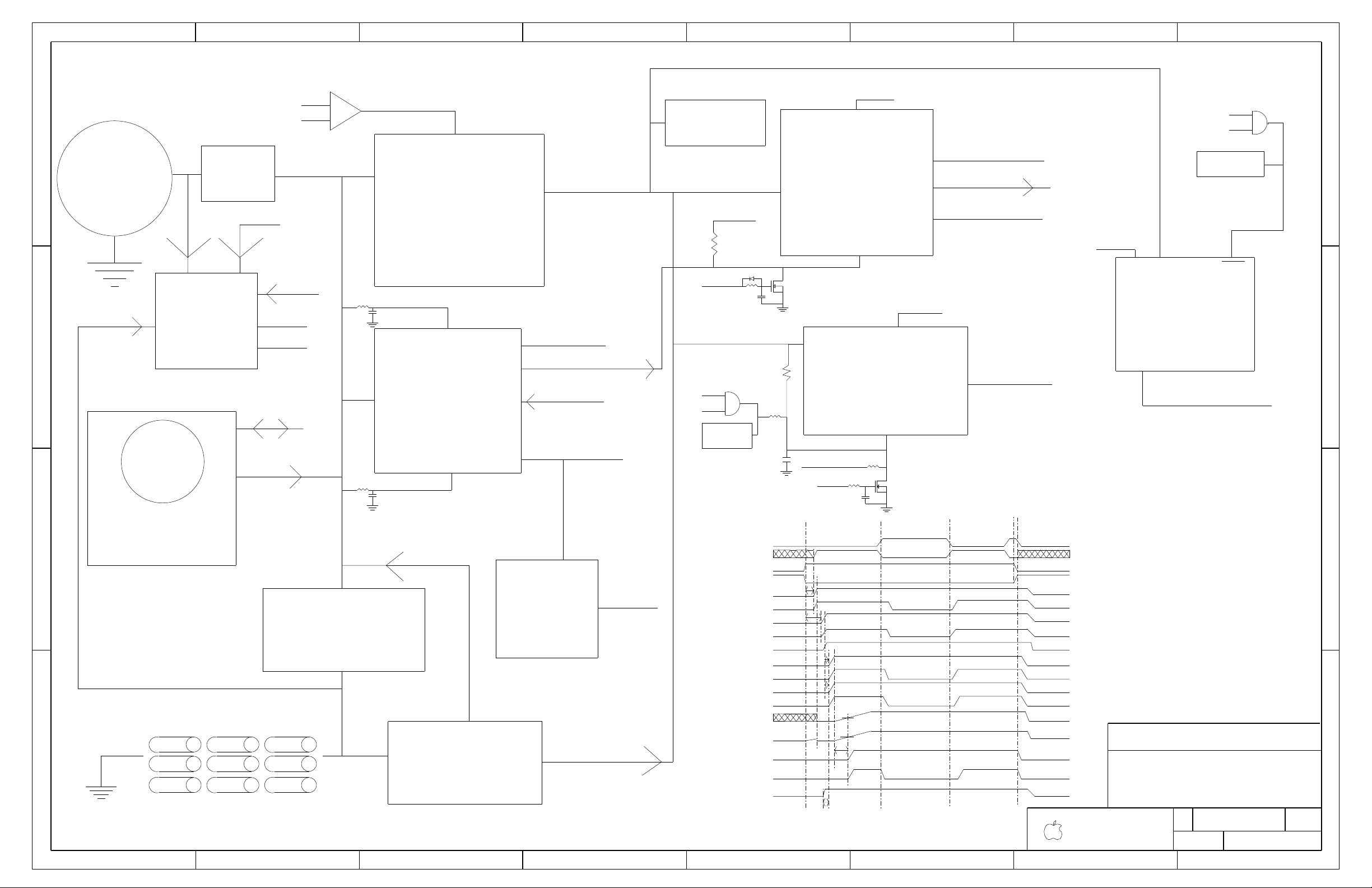

Page 3

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

BACKLIGHT

TURNS ON OUTPUT @ 2.4V

DCDC_EN_L WILL PULL ON1/ON2

BECOMES ’1’; MUCH LESS THAN THE

SLEEP

D3_HOT

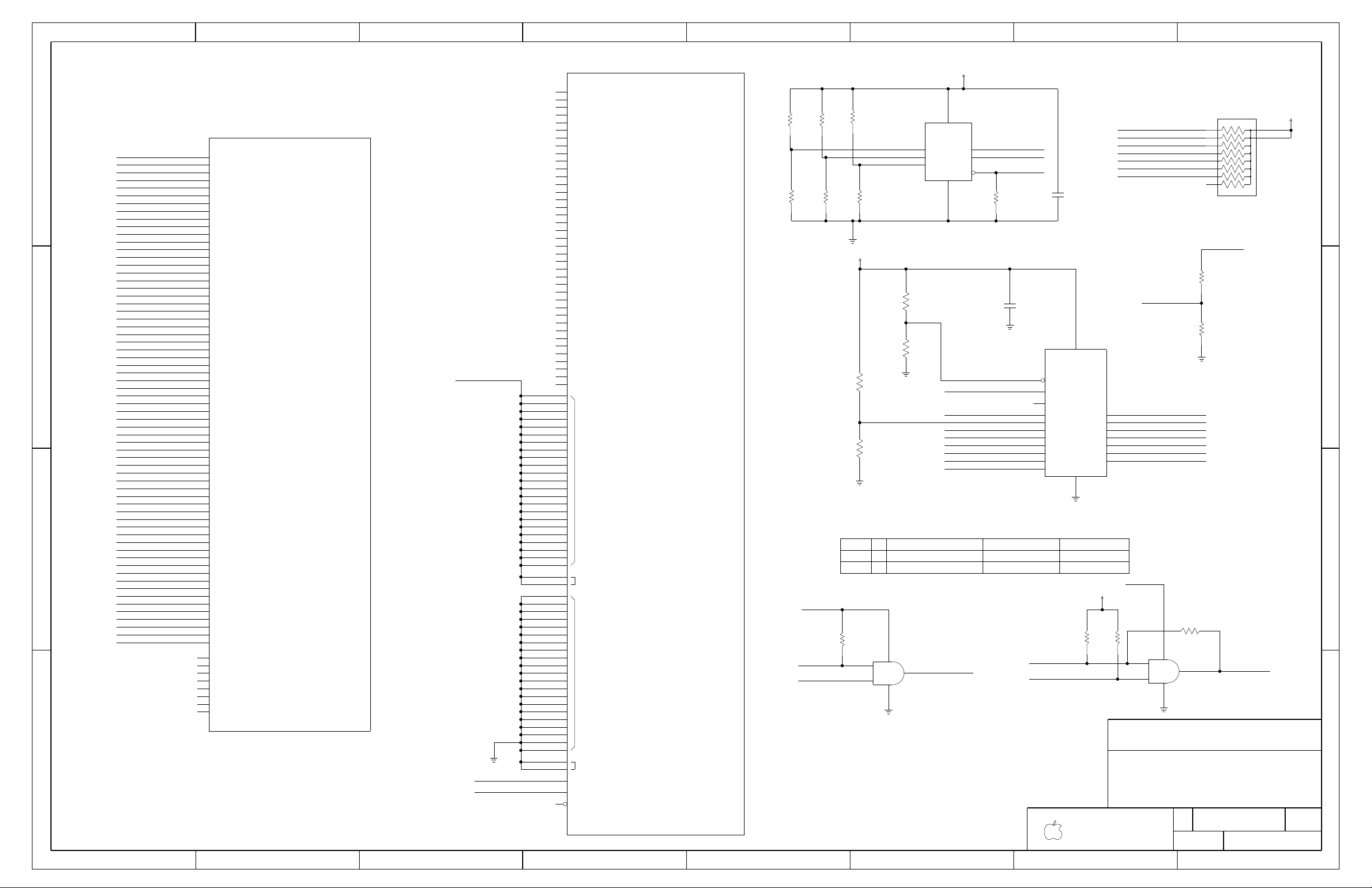

1_5V_2_5V_OK

D3_COLD

AC

ADAPTER

IN

PG 31

+BATT

MAIN 3V/5V

DC/DC

RC AT 1M*0.1UF @ 24V

NO INRUSH PROTECTION

+PBUS

PG 31

FEED-IN PATH

BATTERY VOLTAGE

3S 3P PRISMATIC CELLS

+BATT

PG 31

(MAX1772)

CHARGER

BATTERY

PG 32

& BOOST OUTPUT

BATTERY

BACKUP

+PBUS

SEQUENCING

MAXBUS

DCDC_EN

EXT_VCC

+1.2V/+1.0V

GPU_VCORE

RUN: RUNNING

SLEEP: STOPPED

SHUTDOWN: STOPPED

VCC

SHDN

DC/DC

(MAX1717)

PG 34

CPU_VCORE

(+1.4V/+1.5V)

SHUT-DOWNRUN

RUN

SHUT-DOWN

+1_8V_MAIN

(D3COLD)

GPU_VCORE

(D3HOT)

GPU_VCORE

(AT LTC1778 RUN/SS)

1_5V_2_5V_OK

1_5V_2_5V_OK

(MAX1715 OUTPUT)

+1_5V_SLEEP

+1_5V_MAIN

+2_5V_SLEEP

+2_5V_MAIN

3V_5V_OK

+3V_SLEEP

+3V_MAIN

+5V_SLEEP

+5V_MAIN

DCDC_EN_L

DCDC_EN

SLEEP_L_LS5

SLEEP

+3.3V_MAIN

RUN/SS - 3V

INTERNAL ZENER CLAMP TO 6V

RUN: RUNNING

SLEEP: RUNNING

SHUTDOWN: STOPPED

VCC

RUN/SS - 5V

TURNS ON AT >1V

<100UA ALLOWED

INTERNAL ZENER CLAMP TO 6V

PG 33

STBYMD

+4_6V_BU

+3V_PMU

+5V_MAIN

14V_PBUS

PG 30

LIMITER

RUN: RUNNING

SLEEP: RUNNING

SHUTDOWN: RUNNING

1625 NOT RUNNING

AC: 12.8V

PG 32

(LTC1625)

REGULATOR

BACKUP BATTERY

STARTS 2.0MSEC AFTER DCDC_EN_L BECOMES LOW

+PBUS (12.8V)

PG 31

AFTER PMU IS UP AND RUNNING

RC CHARGING AT INT_VCC (5V)

2.4V - ??? MS

DCDC_EN_L

D3_HOT

1_5V_2_5V_OK WILL NOT PULL LOW UNTIL

+5V_MAIN TURNS ON

DCDC_EN_L OR PMU_POWERUP_L

+5V_MAIN

(UNTIL DRAINED)

-

24V IS OUTPUT ONLY FROM

VCC

+5V_MAIN

LOW IN SHUTDOWN

DCDC_EN_L

TURNS ON AT >1V

<100UA ALLOWED

~13.5MS

2.6 MS

~11MS

~???MS

2.6 MS

1.9 MS

BACKUP BATTERY CIRCUIT CHARGES OFF +PBUS

AND PREVENTS +PBUS AND +24V_PBUS FROM DROPPING BELOW 6V

HOWEVER, 5V SHOULD TURN ON ~2.23MS AFTER

+

U21

+PBUS

12.8V CHARGES BACKUP BATTERY

WHEN ONLY BATTERY IS CONNECTED

PGOOD

RC AT 1M*0.047UF @ 24V

PGOOD

+5V_MAIN

VCC

+24V_PBUS

PG 32

LDO

+3V_PMU

INRUSH

1V20_REF

>~13.44V TURNS-ON

<~13.44V SHUTS-OFF

INVERTER

MAIN 2.5V/1.5V

DC/DC

(MAX1715)

PG 35

SHUTDOWN: STOPPED

SLEEP: RUNNING

RUN: RUNNING

ON1/ON2

+1.5V_MAIN

1_5V_2_5V_OK

+2.5V_MAIN

DDR POWER

MAP31 DDR CORE

INTREPID CORE

AGP I/O

+5V_MAIN

RUN/SS

INTERNAL 1.2UA CURRENT SOURCE

TURNS ON AS LOW AS 0.8V/TYP 1.5V

RUN: RUNNING

SLEEP: D3HOT/D3COLD

SHUTDOWN: STOPPED

PG 20

(LTC1778)

DC/DC

VCC

+PBUS (12.8V)

SLEEP

SHUTDOWN: STOPPED

SLEEP: STOPPED

RUN: RUNNING

PG 35

(LTC3411)

DC/DC

+1.8V_MAIN

MAXBUS

BROADCOM

+24V_PBUS

WHEN ONLY BATTERY IS CONNECTED

NO INRUSH PROTECTION

STARTS ~4.25MSEC AFTER DCDC_EN_L BECOMES LOW

SLEEP

~5.88MS TO START SWITCHER

1M & 0.1UF @14V, IT TAKES

SEQUENCING

GPU_VCORE

DCDC_EN

WHEN IT’S OPEN

WHEN IT’S CONNECTED TO GND

HOLDS BOTH RUN/SS AT GND

3V_5V_OK

+5V_MAIN

TURNS CONTROL TO RUN/SS

POWER BLOCK DIAGRAM

BUCK

NO AC: BATTERY VOLTAGE

RUN/SS

POWER SYSTEM ARCHITECTURE

MAP31 DDR I/O

(LTC3707)

CHARGER INPUT

3

B

45

051-6694

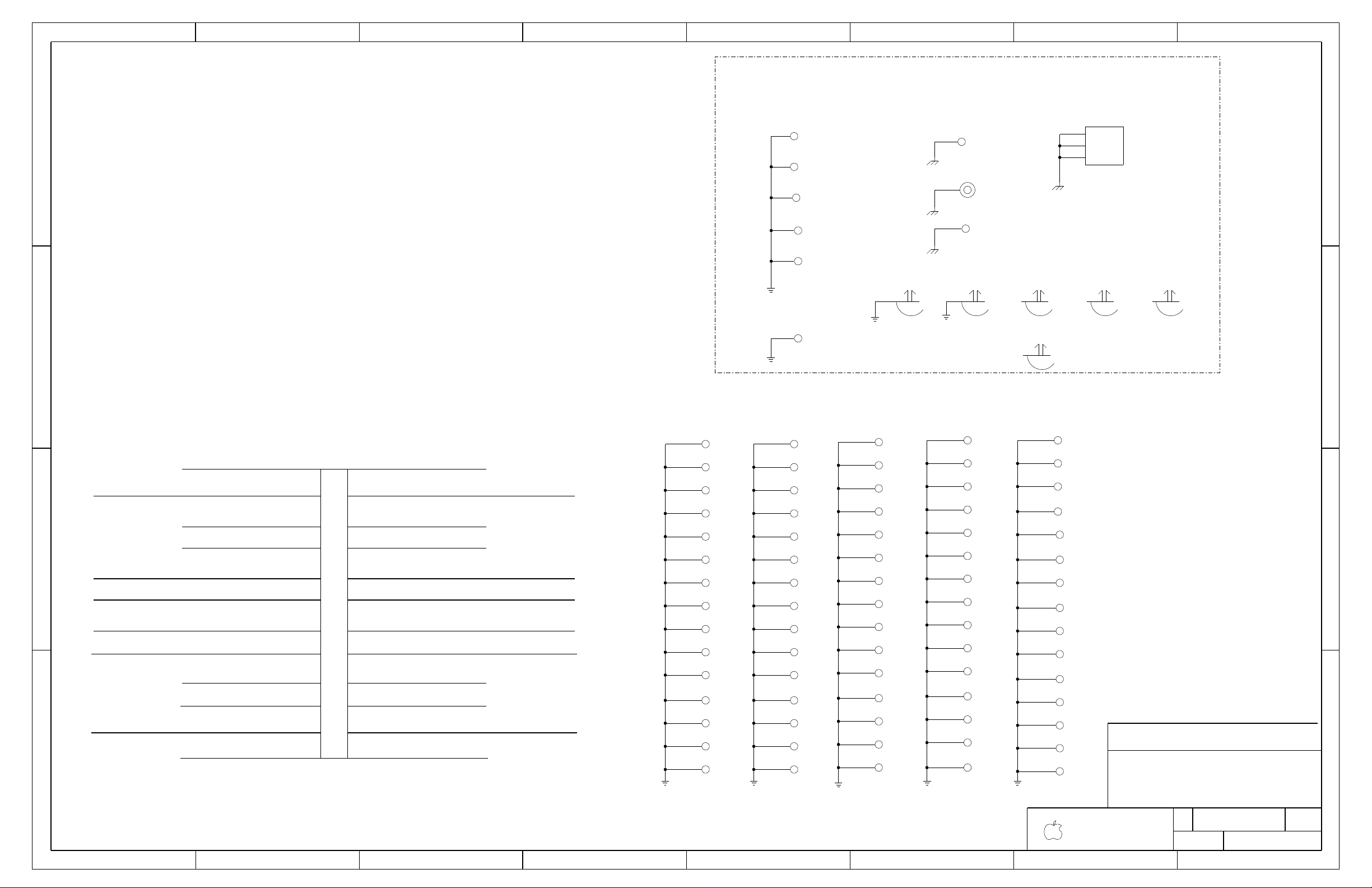

Page 4

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

BOARD INFORMATION

PCB SPECS

THICKNESS : 1.2 MM / 0.047 IN

1/2 OZ CU THICKNESS: 0.7 MILS

1.0 OZ CU THICKNESS: 1.4 MILS

IMPEDANCE : 50 OHMS +/- 10%

DIELECTRIC: FR-4

PREPREG (3MIL)

LAMINATE (4MIL)

PREPREG (3MIL)

LAMINATE (4MIL)

PREPREG (2MIL)

LAMINATE (3MIL)

PREPREG (2MIL)

LAMINATE (4MIL)

PREPREG (3MIL)

LAMINATE (4MIL)

PREPREG (3MIL)

SIGNAL (1/3 OZ + COPPER PLATING)

GROUND (1/2 OZ)

SIGNAL (1/2 OZ)

SIGNAL (1/2 OZ)

GROUND (1/2 OZ)

CUT POWER PLANE(1 OZ)

CUT POWER PLANE(1 OZ)

GROUND (1/2 OZ)

SIGNAL (1/2 OZ)

SIGNAL (1/2 OZ)

GROUND (1/2 OZ)

SIGNAL (1/3 OZ + COPPER PLATING)

BOARD STACK-UP AND CONSTRUCTION

SEE PCB CAD FILES FOR MORE SPECIFIC INFO.

PREPREG THICKNESS: 2-3 MILS

SIGNAL TRACE SPACING: 4 MILS

SIGNAL TRACE WIDTH: 4 MILS

LAYER COUNT: 12

20R10 TH VIA OR VIA IN PAD

12

11

9

10

8

7

6

5

4

3

2

1

GROUND VIAS

CONDUCTIVE MOUNTS

ASICS HEATSINK MOUNTS

I/O AREA INVERTER

CHASSIS MOUNTS

BOARD HOLES

SPEAKER CLIPS

ZT11

1

255R158

OMIT

ZT75

1

HOLE-VIA-20R10

ZT61

1

HOLE-VIA-20R10

ZT63

1

HOLE-VIA-20R10

ZT51

1

HOLE-VIA-20R10

ZT54

1

HOLE-VIA-20R10

ZT42

1

HOLE-VIA-20R10

ZT64

1

HOLE-VIA-20R10

ZT76

1

HOLE-VIA-20R10

ZT59

1

HOLE-VIA-20R10

ZT62

1

HOLE-VIA-20R10

ZT22

1

HOLE-VIA-20R10

ZT3

1

HOLE-VIA-20R10

ZT25

1

HOLE-VIA-20R10

ZT32

1

HOLE-VIA-20R10

ZT31

1

HOLE-VIA-20R10

ZT26

1

HOLE-VIA-20R10

ZT23

1

HOLE-VIA-20R10

ZT19

1

HOLE-VIA-20R10

ZT15

1

HOLE-VIA-20R10

ZT17

1

HOLE-VIA-20R10

ZT13

1

HOLE-VIA-20R10

ZT12

1

HOLE-VIA-20R10

ZT21

1

HOLE-VIA-20R10

ZT14

1

HOLE-VIA-20R10

ZT18

1

HOLE-VIA-20R10

ZT20

1

HOLE-VIA-20R10

ZT4

1

235R126

OMIT

ZT83

1

146R126

OMIT

ZT5

1

146R126

OMIT

SH1

1

2

3

SHLD-SM

OG-503040

CHGND1

SP6

1

SPKR_CLIP_P84

SP1

1

SPKR_CLIP_P84

SP3

1

SPKR_CLIP_P84

SP5

1

SPKR_CLIP_P84

SP2

1

SPKR_CLIP_P84

BS1

1

STDOFF-217ODX150IDX35H-TH

SP4

1

SPKR_CLIP_P84

ZT6

1

235R126

OMIT

ZT16

1

235R126

OMIT

CHGND6

CHGND2

ZT10

1

255R158

OMIT

CHGND5

ZT77

1

HOLE-VIA-20R10

ZT30

1

HOLE-VIA-20R10

ZT28

1

HOLE-VIA-20R10

ZT37

1

HOLE-VIA-20R10

ZT39

1

HOLE-VIA-20R10

ZT40

1

HOLE-VIA-20R10

ZT27

1

HOLE-VIA-20R10

ZT36

1

HOLE-VIA-20R10

ZT38

1

HOLE-VIA-20R10

ZT2

1

255R158

OMIT

ZT24

1

HOLE-VIA-20R10

ZT81

1

HOLE-VIA-20R10

ZT34

1

HOLE-VIA-20R10

ZT33

1

HOLE-VIA-20R10

ZT43

1

HOLE-VIA-20R10

ZT46

1

HOLE-VIA-20R10

ZT50

1

HOLE-VIA-20R10

ZT35

1

HOLE-VIA-20R10

ZT44

1

HOLE-VIA-20R10

ZT66

1

HOLE-VIA-20R10

ZT67

1

HOLE-VIA-20R10

ZT53

1

HOLE-VIA-20R10

ZT52

1

HOLE-VIA-20R10

ZT70

1

HOLE-VIA-20R10

ZT71

1

HOLE-VIA-20R10

ZT78

1

HOLE-VIA-20R10

ZT69

1

HOLE-VIA-20R10

ZT65

1

HOLE-VIA-20R10

ZT45

1

HOLE-VIA-20R10

ZT47

1

HOLE-VIA-20R10

ZT49

1

HOLE-VIA-20R10

ZT56

1

HOLE-VIA-20R10

ZT48

1

HOLE-VIA-20R10

ZT72

1

HOLE-VIA-20R10

ZT55

1

HOLE-VIA-20R10

ZT29

1

HOLE-VIA-20R10

ZT82

1

HOLE-VIA-20R10

ZT74

1

HOLE-VIA-20R10

ZT79

1

HOLE-VIA-20R10

ZT68

1

HOLE-VIA-20R10

ZT60

1

HOLE-VIA-20R10

ZT58

1

HOLE-VIA-20R10

ZT41

1

HOLE-VIA-20R10

ZT7

1

HOLE-VIA-20R10

ZT9

1

HOLE-VIA-20R10

ZT8

1

HOLE-VIA-20R10

ZT1

1

HOLE-VIA-20R10

ZT57

1

HOLE-VIA-20R10

ZT80

1

HOLE-VIA-20R10

ZT73

1

HOLE-VIA-20R10

45

4

051-6694

B

Page 5

QACK*

TEA*

A10

MCP*

A23

A28

A29

TRST*

PMON_OUT*

A7

SHD1*

HIT*

SHD0*

ARTRY*

AACK*

CI*

WT*

GBL*

TBST*

TS*

BG*

BR*

GND

VDD

A1

A2

A11

A5

A4

A3

A6

A8

A9

A12

A22

A21

A20

A19

A18

A17

A16

A15

A14

A13

A32

A31

A30

A27

A24

A25

AP1

AP4

AP2

AP3

AP0

A35

A34

A33

TT0

TT4

TSIZ1

TSIZ2

TSIZ0

TT1

TT2

TT3

DTI3

DTI2

TDI

TDO

TMS

TCK

A26

BMODE0*

PMON_IN*

BMODE1*

DTI1

A0

DTI0

LSSD_MODE*

TA*

L2_TSTCLK

L1_TSTCLK

EXT_QUAL

CHKS*

DX*

SRW0*

IARTRY0*

SRW1*

(1 OF 3)

HRESET*

SRESET*

TBEN

QREQ*

CKSTP_IN*

CKSTP_OUT*

SYSCLK

INT*

SMI*

PLL_CFG1

CLK_OUT

OVDD

PLL_CFG0

PLL_CFG3

DRDY*

DBG*

PLL_CFG2

PLL_CFG4

BVSEL

AVDD

OVDDSENSE

PG

EN

VIN

ADJ

VOUT

GND

TABLE_5_ITEM

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

CPU_VCORE DECOUPLING NETWORK

CPU_OVDD DECOUPLING NETWORK

MPC7447 MAXBUS

R2

PLCAE SHORT CLOSE TO CENTER OF CPU

POWER SUPPLY PAGE (PG 33)

MORE 0805 10UF CAPS ON VCORE

NC

NC

NC

NC

NC

NC

NC

PLACE BELOW CPU

IN FORMER L3 AREA

MPC7447 PULL-UPS

R1

VOUT = 0.59*(1+R1/R2)

PLACE RXXX AND RXXX CLOSE

TO UXX PIN 5 AND 6

470OHM FOR BOOT BANGER

470OHM FOR BOOT BANGER

R87

1 2

10K

5%

1/16W

MF

402

R139

1 2

10K

5%

1/16W

MF

402

R107

1 2

10K

5%

1/16W

MF

402

R59

1 2

470

5%

1/16W

MF

402

R97

1 2

10K

5%

1/16W

MF

402

R160

1 2

10K

5%

1/16W

MF

402

R57

1 2

1K

5%

1/16W

MF

402

R58

1 2

10K

5%

1/16W

MF

402

R129

1 2

10K

5%

1/16W

MF

402

C39

1

2

10V

0.1uF

20%

CERM

402

C203

1

2

0.1uF

CERM

402

10V

20%

C73

1

2

10V

402

20%

0.1uF

CERM

C74

1

2

402

CERM

10V

20%

0.1uF

C194

1

2

0.1uF

20%

CERM

402

10V

C40

1

2

CERM

10V

20%

0.1uF

402

C191

1

2

402

CERM

10V

20%

0.1uF

C152

1

2

402

CERM

10V

20%

0.1uF

C138

1

2

0.1uF

20%

10V

CERM

402

C113

1

2

0.1uF

20%

10V

CERM

402

C104

1

2

0.1uF

20%

10V

CERM

402

C115

1

2

402

CERM

10V

20%

0.1uF

C38

1

2

0.1uF

20%

10V

CERM

402

C224

1

2

CERM

0.1uF

20%

10V

402

C48

1

2

CERM

402

10V

20%

0.1uF

C90

1

2

10V

CERM

402

20%

0.1uF

C72

1

2

0.1uF

20%

CERM

402

10V

C107

1

2

402

CERM

10V

20%

0.1uF

R206

1

2

1/16W

5%

MF

402

470

C114

1

2

402

CERM

10V

20%

0.1uF

C154

1

2

0.1uF

20%

10V

CERM

402

C91

1

2

0.1uF

20%

10V

CERM

402

C168

1

2

402

CERM

10V

20%

0.1uF

C223

1

2

402

CERM

10V

20%

0.1uF

C112

1

2

0.1uF

20%

10V

CERM

402

R241

1

2

470

5%

1/16W

MF

402

R60

1 2

10K

5%

1/16W

MF

402

R61

1 2

470

5%

1/16W

MF

402

R148

1 2

10K

5%

1/16W

402

MF

R98

1 2

1K

5%

1/16W

MF

402

C25

10uF

20%

6.3V

CERM

805

C346

1

2

10uF

20%

6.3V

CERM

805

C342

805

CERM

6.3V

20%

10uF

C8

1

2

805

CERM

6.3V

20%

10uF

R120

1 2

10K

5%

1/16W

MF

402

R109

1 2

10K

5%

1/16W

MF

402

R106

1 2

402

NO STUFF

10

MF

1/16W

1%

C340

1

2

805

10V

20%

2.2uF

CERM

C12

1

2

2.2uF

20%

10V

CERM

805

R73

1 2

10K

5%

1/16W

MF

402

R72

1 2

10K

5%

1/16W

MF

402

R702

1 2

5%

1/16W

MF

603

1_5V_MAXBUS

0

R693

1 2

1_8V_MAXBUS

5%

1/16W

MF

603

0

+1_5V_SLEEP

+1_8V_SLEEP

R128

1 2

470

5%

1/16W

MF

402

C103

1

2

402

CERM

20%

0.1uF

10V

C149

1

2

0.1uF

20%

10V

CERM

402

C151

1

2

0.1uF

10V

CERM

402

20%

C202

1

2

402

CERM

10V

20%

0.1uF

C111

1

2

0.1uF

20%

10V

CERM

402

C110

1

2

0.1uF

20%

10V

CERM

402

C275

1

2

10V

402

CERM

20%

0.1uF

C257

1

2

402

CERM

10V

20%

0.1uF

C273

1

2

20%

0.1uF

10V

CERM

402

C41

1

2

0.1uF

20%

10V

CERM

402

C272

1

2

20%

402

10V

CERM

0.1uF

C46

1

2

0.1uF

20%

10V

CERM

402

R65

1 2

10K

5%

1/16W

MF

402

R130

1 2

10K

5%

1/16W

MF

402

R79

1 2

10K

5%

1/16W

MF

402

R108

1 2

10K

5%

1/16W

MF

402

C190

1

2

402

CERM

10V

20%

0.1uF

C150

1

2

CERM

10V

402

20%

0.1uF

C201

1

2

10V

402

CERM

20%

0.1uF

C193

1

2

0.1uF

20%

10V

CERM

402

C153

1

2

0.1uF

20%

10V

CERM

402

C344

1

2

20%

6.3V

CERM

10uF

805

C189

1

2

0.1uF

20%

10V

402

CERM

C105

1

2

402

CERM

10V

20%

0.1uF

C192

1

2

CERM

0.1uF

20%

10V

402

C47

1

2

402

CERM

10V

20%

0.1UF

C188

1

2

0.1UF

20%

10V

CERM

402

C169

1

2

402

CERM

10V

20%

0.1UF

C170

1

2

0.1UF

20%

10V

CERM

402

C155

1

2

402

CERM

10V

20%

0.1UF

C139

1

2

0.1UF

10V

20%

CERM

402

C92

1

2

402

CERM

10V

0.1UF

20%

C106

1

2

0.1UF

402

CERM

10V

20%

C195

1

2

10UF

20%

6.3V

CERM

805

C347

1

2

805

CERM

6.3V

20%

10UF

C258

1

2

10UF

20%

6.3V

CERM

805

C345

1

2

805

CERM

6.3V

20%

10UF

C156

1

2

805

CERM

6.3V

20%

10UF

C341

1

2

10UF

20%

6.3V

CERM

805

C225

1

2

805

CERM

6.3V

20%

10UF

C343

1

2

10UF

20%

6.3V

CERM

805

XW31

1 2

OMIT

SM

U43

E11

H1

D12

L3

G4

T2

F4

V1

J4

R2

K5

W2

C11

J2

K4

N4

J3

M5

P5

N3

T1

V2

U1

G3

N5

W1

B12

C4

G10

B11

F10

L2

D11

D1

C10

G2

R1

C1

E3

H6

F5

G7

N2

A8

M1

G9

F8

D2 B7

A12

J1

A3

B1

H2

M2

R3

G1

K1

P1

N1

D10

A11

E2

B5

H9

H11

H13

J6

J8

J10

J12

K7K3K9

C3

K11

K13

L6

L8

L10

L12

M4M7M9

M11D6M13

N7P3P9

P12R5R14

R17T7T10

D13

U3

U13

U17

V5

V8

V11

V15

E17F3G17

H4

H7

B2

D8

B6

D4

G8

B3

E8

C9

B4

M3N6P2P8P11R4R13

R16T6T9C2U2

U12

U16V4V7

V10

V14

C12D5F2H3J5K2L5

E18

G18

B8

C8

C7

D7

A7

D9

A9

G5

P4

E4

H5

F9

A2

B10

E10

A10

K6

E1

F11

C6

B9

A4

L1

F1

A5

L4

G6

F7

E7

E5

E6

F6

E9

C5

H8

K12

K14L7L9

L11

L13M8M10

M12

H10

H12J7J9

J11

J13K8K10

D3

BGA

OMIT

APOLL7_PM-R1.1

1.50GHZ-1.28V

CRITICAL

U6

53

2

4

1 6

CRITICAL

SOT23-6

FAN2558

C283

1

2

2.2UF

CERM1

20%

6.3V

603

C909

1

2

6.3V

CERM

402

10%

1UF

R280

1 2

402

MF

1/16W

1%

10

R276

1

2

0

1/10W

603

5%

MF

R282

1

2

118K

1/16W

1%

MF

402

R283

1

2

100K

1%

MF

402

1/16W

+3V_SLEEP

D35

12

NO STUFF

MBR0530

SM

R275

1 2

1/16W

MF

0

5%

402

C945

1

2

NO STUFF

0.1UF

CERM

20%

10V

402

C946

1

2

50V

10%

CERM

0.001UF

402

C137

1

2

0.1uF

20%

10V

402

CERM

C136

1

2

CERM

6.3V

20%

4.7UF

805

U431

CRITICAL337S3029

IC,A7PM,R1.3,1.67GHZ,1.28V

NO STUFF

45

B

5

051-6694

CRITICAL

1 U43

337S2955

IC,A7PM,R1.2.3,1.67GHZ,1.28V

?

CPU_PULLDOWN

CPU_SMI_L

CPU_HRESET_L

CPU_DTI<2>

JTAG_CPU_TCK

JTAG_CPU_TMS

CPU_VCORE_SLEEP

MPIC_CPU_INT_L

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

CPU_AVDD_VIN

CPU_AVDD_SHDN_L

CPU_SRESET_L

CPU_L1TSTCLK

VCORE_SHDN_L

JTAG_CPU_TCK

CPU_L2TSTCLK

CPU_SRWX_L

CPU_CHKSTP_OUT_L

JTAG_CPU_TDI

CPU_SMI_L

CPU_HRESET_L

CPU_PULLDOWN

CPU_EDTI

CPU_PULLUP

CPU_PMONIN_L

CPU_LSSD_MODE

CPU_SHD0_L

CPU_TBEN

CPU_SHD1_L

CPU_CHKS_L

MAXBUS_SLEEP

CPU_EMODE1_L

CPU_MCP_L

ADT7467_VCORE_MON

CPU_ADDR<1>

CPU_PLL_CFG<4>

CPU_PLL_CFG<1>

CPU_DBG_L

CPU_PLL_CFG<3>

CPU_DRDY_L

CPU_EDTI

CPU_DTI<1>

JTAG_CPU_TDI

JTAG_CPU_TMS

CPU_TBEN

CPU_MCP_L

CPU_CHKSTP_OUT_L

CPU_ADDR<18>

CPU_PLL_CFG<2>

CPU_ADDR<2>

CPU_ADDR<0>

CPU_CHKS_L

CPU_PULLDOWN

CPU_ADDR<16>

CPU_ADDR<21>

CPU_PMONIN_L

CPU_EMODE0_L

JTAG_CPU_TDO_TP

CPU_ARTRY_L

CPU_SHD0_L

CPU_HIT_L

CPU_SHD1_L

CPU_BR_L

CPU_BG_L

CPU_TS_L

CPU_ADDR<3>

CPU_ADDR<4>

CPU_ADDR<6>

CPU_ADDR<5>

CPU_ADDR<9>

CPU_ADDR<8>

CPU_ADDR<11>

CPU_ADDR<10>

CPU_ADDR<12>

CPU_ADDR<14>

CPU_ADDR<13>

CPU_ADDR<15>

CPU_ADDR<17>

CPU_ADDR<19>

CPU_ADDR<20>

CPU_ADDR<22>

CPU_ADDR<24>

CPU_ADDR<23>

CPU_ADDR<25>

CPU_ADDR<26>

CPU_ADDR<27>

CPU_ADDR<28>

CPU_ADDR<29>

CPU_ADDR<31>

CPU_ADDR<30>

CPU_TT<0>

CPU_TT<1>

CPU_TT<3>

CPU_TT<2>

CPU_TBST_L

CPU_TT<4>

CPU_TSIZ<0>

CPU_TSIZ<2>

CPU_TSIZ<1>

CPU_WT_L

CPU_GBL_L

CPU_CI_L

CPU_AACK_L

CPU_ADDR<7>

CPU_QACK_L

CPU_TA_L

SYSCLK_CPU

CPU_PULLDOWN

CPU_EMODE1_L

CPU_CLKOUT_SPN

CPU_LSSD_MODE

JTAG_CPU_TRST_L

CPU_L2TSTCLK

CPU_L1TSTCLK

CPU_PULLUP

CPU_SRWX_L

CPU_PULLUP

CPU_TEA_L

CPU_SRESET_L

CPU_AVDD

MPIC_CPU_INT_L

CPU_QREQ_L

CPU_PLL_CFG<0>

CPU_BUS_VSEL

CPU_DTI<0>

CPU_AVDD_ADJ

CPU_AVDD_VOUT

CPU_VCORE_SLEEP

MAXBUS_SLEEP

39

39

35

35

16

16

40

15

15

40

39

40

8

8

7

40

40

35

40

40

7

7

40

40

7

31

6

37

6

6

6

14

40

6

40

6

31

6

8

6

37

37

37

37

6

6

8

40

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

40

37

40

14

37

37

6

5

5

5

8

5

5

5

5

5

5

35

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

26

8

7

7

8

7

8

5

8

5

5

5

5

5

8

7

8

8

5

5

8

8

5

7

40

8

5

8

5

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

5

5

5

6

5

5

5

5

5

8

5

39

5

8

7

7

8

5

Page 6

D22

D3

D2

D1

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D28

D27

D23

D24

D25

D26

D29

D32

D31

D30

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D48

D47

D45

D46

D49

D51

D50

D52

D53

D54

D55

D58

D57

D56

D59

DP6

DP5

DP4

DP3

DP2

DP1

DP0

DP7

D63

D62

D61

D60

D0

(2 OF 3)

VDD

N/C_1

N/C_4

N/C_8

N/C_13

N/C_17

N/C_20

N/C_22

N/C_23

N/C_31

N/C_39

N/C_30

N/C_33

N/C_35

N/C_36

N/C_38

N/C_29

N/C_28

N/C_27

N/C_25

N/C_24

N/C_21

N/C_19

N/C_18

N/C_16

N/C_15

N/C_14

N/C_12

N/C_11

N/C_10

N/C_9

N/C_7

N/C_6

N/C_5

N/C_3

N/C_2

(3 OF 3)

N/C_26

N/C_32

N/C_34

N/C_37

SENSEVDD

GND

TEMP_CATHODE

TEMP_ANODE

SENSEGND

HPR*

Y

B

A

Y

B

A

SYM_VER2

WC*

VCC

VSS

SDA

SCL

NC1

NC2

NC3

VCC

RESET*

XTAL1

XTAL2

PB0

PD6

PD5

PD4

PD3

PD2

PD1

PD0

GND

PB1

PB2

PB3

PB4

PB5

PB6

PB7

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_5_ITEM

TABLE_5_ITEM

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

INPUTS ARE 3V TOLERANT

INPUTS ARE 3V TOLERANT

BOOT BANGER E2PROM

NC

WILL DISABLE THE CONTROLLER

UNSTUFFING RA AND STUFFING RB

MPC7447/BBANG

NC

BOOT BANGER

470OHM FOR BOOT BANGER

NC

RB

RA

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

BOOT BANGING SIGNAL DEFINITION

2/ PMU_HRESET_L (3V INPUT INTO LMU)

5/ JTAG_CPU_TDI (OPEN COLLECTOR OUTPUT - 470OHM PULLUP ON MLB)

6/ JTAG_CPU_TRST_L (OPEN COLLECTOR OUTPUT - 470OHM PULLUP ON MLB)

4/ JTAG_CPU_TMS (OPEN COLLECTOR OUTPUT - 470OHM PULLUP ON MLB)

1/ BBANG_HRESET_L (OPEN COLLECTOR OUTPUT - 10K PULLUP ON MLB)

3/ BBANG_JTAG_TCK (REGULAR OUTPUT)

NC

NC

NC

NC

NC

CRITICAL

1.50GHZ-1.28V

OMIT

BGA

APOLL7_PM-R1.1

U43

R15

W15

T13

P13

U14

W14

R12

T12

W12

V12

N11

N10

T14

R11

U11

W11

T11

R10

N9

P10

U10

R9

W10

V16

U9

V9

W5

U6

T5

U5

W7

R6

P7

V6

W16

P17

R19

V18

R18

V19

T19

U19

W19

U18

W17

T15

W18

T16

T18

T17

W3

V17

U4

U8

U7

R7

U15

P6

R8

W8

T8

P14

V13

W13

T3

W4

T4

W9

M6

V3

N8

W6

402

10K

1%

MF

1/16W

BBANG

R884

1

2

+3V_MAIN

+3V_MAIN

+3V_MAIN

CERM

20%

10V

BBANG

0.1UF

402

C638

1

2

402

BBANG

10K

5%

1/16W

MF

R532

1

2

MF

BBANG

5%

10K

1/16W

402

R533

1

2

CRITICAL

OMIT

APOLL7_PM-R1.1

BGA

1.50GHZ-1.28V

U43

A17

A19

B13

B16

B18

E12

E19

F13

F16

F18

G19

H18

J14

L14

M15

M17

M19

N14

N16

P15

P19

A6

A14

C15

D15

E15

F15

G15

H15

J15

K15

L15

C16

B14

D16

C17

D17

C18

D18

C19

D19

H16

J16

K16

C14

L16

J17

K17

L17

J18

K18

L18

J19

K19

L19

D14

E14

F14

G14

A15

B15

N13

G12

N12

G13

N18

N19

A13

A16

A18

B17

B19

C13

E13

E16

F12

F17

F19

G11

G16

H14

H17

H19

M14

M16

M18

N15

N17

P16

P18

SN74AUC1G08

SC70-5

BBANG

U4

1

2

3

5

4

SN74AUC1G08

BBANG

SC70-5

U2

1

2

3

5

4

BBANG

10K

5%

MF

1/16W

402

R62

1

2

NO_BBANG

0

5%

1/16W

MF

402

R6

1 2

BBANG

10K

5%

1/16W

MF

402

R40

1

2

+3V_MAIN

MF

BBANG

1/16W

5%

10K

402

R39

1

2

OMIT

SOI

32KX8_M24256B

U32

1

2

3

6

5

8

4

7

5%

MF

402

1/16W

10K

BBANG

R906

1

2

10K

5%

402

MF

1/16W

BBANG

R904

1

2

NO STUFF

1/16W

MF

10K

5%

402

R903

1

2

NO STUFF

5%

10K

1/16W

MF

402

R905

1

2

NO STUFF

1/16W

MF

10K

5%

402

R907

1

2

OMIT

ATTINY2313

SOI

U61

10

12

13

14

15

16

17

18

19

2

3

6

7

8

9

11

1

20

5

4

402

MF

1/16W

5%

470

BBANG

R86

1

2

200

NO_BBANG

5%

402

1/16W

MF

R85

1

2

SM

1/32W

25V

10K

5%

BBANG

RP6

5

10

1

2

3

4

6

7

8

9

402

CERM

0.1UF

BBANG

20%

10V

C938

1

2

402

5%

BBANG

10K

1/16W

MF

R885

1

2

10K

NO STUFF

402

1/16W

MF

5%

R886

1

2

10K

MF

1%

BBANG

1/16W

402

R882

1

2

U32

341S1661

BBANG

1

I2C EEPROM,PROGRAMMED W/ BANGER

MCU,PROGRAMMED W/ BANGER

341S1660

U61

BBANG

1

051-6694

45

6

B

CPU_DATA<18>

CPU_DATA<4>

CPU_DATA<6>

BB_EEPR_ADDR2

BB_EEPR_ADDR1

BB_EEPR_ADDR0

INT_I2C_CLK0

INT_I2C_DATA0

JTAG_CPU_TCK

BBANG_JTAG_TCK

BBANG_TCK_EN

MAXBUS_SLEEP

BBANG_HRESET_L

CPU_DATA<15>

CPU_DATA<16>

CPU_DATA<19>

CPU_DATA<20>

CPU_DATA<21>

CPU_DATA<22>

CPU_DATA<23>

CPU_DATA<24>

CPU_DATA<25>

CPU_DATA<26>

CPU_DATA<27>

CPU_DATA<28>

CPU_DATA<29>

CPU_DATA<30>

CPU_DATA<31>

CPU_DATA<32>

CPU_DATA<34>

CPU_DATA<35>

CPU_DATA<37>

CPU_DATA<38>

CPU_DATA<39>

CPU_DATA<41>

CPU_DATA<42>

CPU_DATA<43>

CPU_DATA<44>

CPU_DATA<45>

CPU_DATA<46>

CPU_DATA<47>

CPU_DATA<48>

CPU_DATA<49>

CPU_DATA<50>

CPU_DATA<51>

CPU_DATA<52>

CPU_DATA<53>

CPU_DATA<59>

CPU_DATA<60>

CPU_DATA<61>

CPU_DATA<63>

CPU_DATA<54>

CPU_DATA<55>

CPU_DATA<56>

CPU_DATA<57>

CPU_DATA<58>

CPU_DATA<3>

CPU_DATA<2>

CPU_DATA<1>

CPU_DATA<9>

CPU_DATA<10>

CPU_DATA<11>

CPU_DATA<13>

CPU_DATA<14>

CPU_DATA<33>

CPU_DATA<36>

CPU_DATA<62>

CPU_DATA<5>

CPU_DATA<7>

CPU_DATA<12>

CPU_DATA<17>

CPU_DATA<40>

CPU_THERM_DP

CPU_THERM_DM

EEPROM_WP_PD

BB_SCK

BB_MISO

BB_MOSI

INT_I2C_DATA0

INT_I2C_CLK0

BBANG_HRESET_L

PMU_CPU_HRESET_L

JTAG_CPU_TDI

JTAG_CPU_TRST_L

JTAG_CPU_TMS

ICT_TRST_L

ESP_EN_L

BFR_TDO

TP_BB_XTAL

CPU_VCORE_SLEEP

BB_RESET_L

BB_SCK

BB_MISO

BB_MOSI

BBANG_JTAG_TCK

ESP_EN_L

BFR_TDO

ICT_TRST_L

MAXBUS_SLEEP

JTAG_CPU_TRST_L

CPU_DATA<8>

CPU_DATA<0>

BBANG_JTAG_TCK

RESET_VREF

CPU_HRESET_L

MAXBUS_SLEEP

PMU_CPU_HRESET_L

5

5

5

6

6

6

7

7

7

6

6

8

6

6

8

8

11

11

15

11

11

5

15

15

13

13

16

13

13

5

35

16

5

5

16

8

37

37

23

23

5

35

6

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

37

8

8

8

8

8

8

8

8

8

8

8

23

23

6

6

5

6

5

39

35

6

8

8

7

35

6

37

8

8

40

40

40

6

39

40

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

8

37

37

37

37

37

37

37

37

37

37

37

26

26

6

6

6

40

40

40

31

40

40

40

6

6

6

40

6

6

6

6

6

6

6

39

40

37

37

6

40

39

31

Page 7

G

D

S

G

D

S

04

G

D

S

G

D

S

G

D

S

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

12.5X

13.0X

13.5X

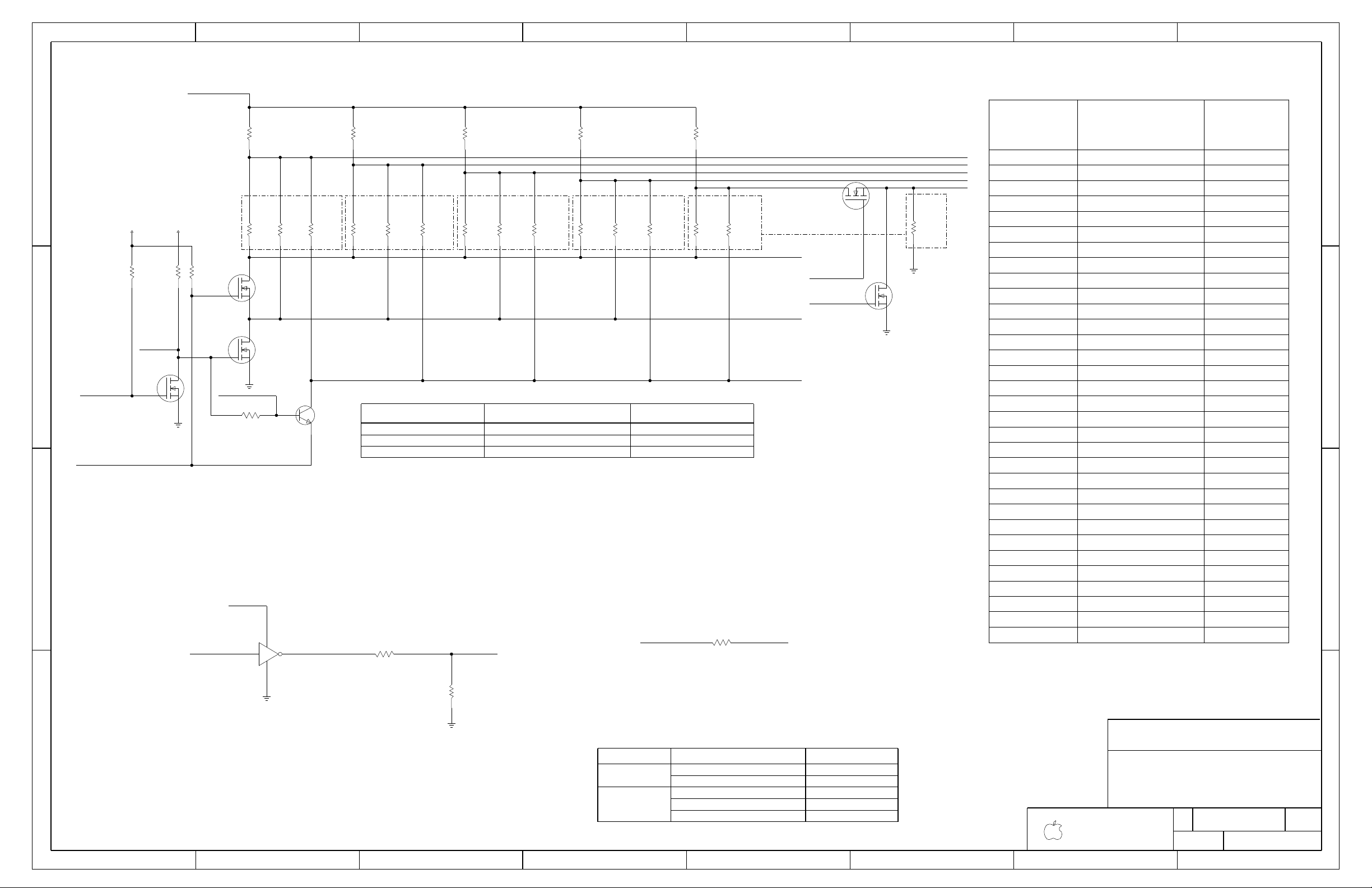

CPU PLL CONFIG CIRCUITRY

R00ER10ER01ER10DR00D

R01D

R10CR00CR01CR10BR00BR01BR10AR00AR01A

+5V_SLEEP NOW REQUIRED FOR PLL_STOP_L

PULLUP TO ENSURE THAT Vgs OF PASS

STATE ENCODING CPU_PLL_STOP_OC CPU_VCORE_HI_OC

SIGNAL

CPU_EMODE0_L

(PROCESSOR)

CPU_BUS_VSEL

(PROCESSOR)

CPU_HRESET_INV

LOW

CPU_HRESET_L

CPU_HRESET_L

HIGH

TIED

APPLICATION

60X BUS MODE

MAX BUS MODE

2.5V INTERFACE

1.8V INTERFACE

1.5V INTERFACE

(AT BUS FREQUENCY)

(MHZ)

PLL OFF

PLL BYPASS

267333

500 400

533667

833 667

733917

1000

800

867

1083

1167

933

10001250

1333 1067

11331417

1500 1200

1583 1267

1667 1333

1750 1400

1833 1467

1917 1533

2000

2083

2167

2250

2333

2500

2667

2833

3000

3333

3500

4000

4667

1600

1667

1733

1800

1867

2000

2133

2267

2400

2667

2800

3200

3733

1 1110 1E

1 0110 16

1 0100 14

1 0011 13

1 0010 12

1 0000 10

1 1101 1D

1 0001 11

1 1100 1C

0 1110 0E

1 0101 15

1 1111 1F

1 1011 1B

0 0000 00

1 1001 19

1 1000 18

1 1010 1A

0 0111 07

1 0111 17

0 0110 06

0 1100 0C

0 0001 01

0 0010 02

0 0101 05

0 1101 0D

0 1001 09

0 1011 0B

0 1010 0A

0 1000 08

0 0100 04

0 0011 03

0 1111 0F

E ABCD HEX

4 0123

CPU_PLL_CFG

STUFF PASS TRANSISTOR ONLY IF

R10E, R01E, OR PULLUP STUFFED

NEED TO CHARACTERIZE

INVERTER TO INVERT HRESET_L

DESKTOP HAD PROBLEM USING

INVERTED HRESET_L

MAXBUS VSEL

1.5V INTERFACE

1.8V INTERFACE

CPU CONFIGURATION

BUSTYPE SELECT

APOLLO ONLY SUPPORTS MAXBUS

(Bus-to-Core)

MULTIPLIER

133MHZ167MHZ

CORE FREQUENCY

APOLLO 7

CPU FREQUENCY CONFIGURATION

PLL DISABLE 1 X

HIGH SPEED 0 1

LOW SPEED 0 0

0.0X

1.0X

2.0X

3.0X

4.0X

5.0X

5.5X

6.0X

6.5X

7.0X

7.5X

8.0X

8.5X

9.0X

9.5X

10.0X

10.5X

11.0X

11.5X

12.0X

14.0X

15.0X

16.0X

17.0X

20.0X

21.0X

24.0X

28.0X

18.0X

CPU CONFIGURATION

TRANSISTOR ON CPU_PLL_CFG<4> IS MET.

402

MF

1/16W

5%

0

R23

1

2

0

5%

1/16W

MF

402

NO STUFF

R16

1

2

10K

5%

1/16W

MF

402

R9

1

2

10K

5%

1/16W

MF

402

R10

1

2

10K

5%

1/16W

MF

402

R11

1

2

5%

1/16W

MF

402

10K

R12

1

2

47K

5%

402

1/16W

MF

R3

1

2

10K

5%

1/16W

MF

402

R48

1

2

82K

5%

1/16W

MF

402

R33

1

2

0

5%

1/16W

MF

402

NO STUFF

R18

1

2

0

5%

1/16W

402

NO STUFF

MF

R17

1

2

10K

5%

1/16W

MF

402

R2

1

2

2N7002DW

SOT-363

Q2

3

5

4

SOT-363

2N7002DW

Q2

6

2

1

SC70-5

1_5V_MAXBUS

CRITICAL

SN74AUC1G04

U1

2

3

5

4

402

MF

1/16W

5%

0

NO STUFF

R27

1

2

2N7002DW

SOT-363

Q1

6

2

1

2N7002DW

SOT-363

Q1

3

5

4

+5V_SLEEP

1_5V_MAXBUS

22

5%

1/16W

MF

402

R4

21

402

MF

1/16W

5%

22

R149

21

1_8V_MAXBUS

10

5%

1/16W

MF

402

R5

1

2

2N7002

SM

Q3

3

1

2

2N3904

SM

Q4

1

3

2

249K

1%

1/16W

MF

402

R47

1 2

0

5%

1/16W

MF

402

NO STUFF

R19

1

2

+3V_SLEEP

402

MF

1/16W

5%

0

NO STUFF

R20

1

2

0

1/16W

5%

MF

402

NO STUFF

R21

1

2

0

5%

1/16W

MF

402

NO STUFF

R22

1

2

0

5%

1/16W

MF

402

NO STUFF

R24

1

2

0

5%

1/16W

MF

402

NO STUFF

R25

1

2

402

MF

1/16W

5%

0

NO STUFF

R26

1

2

0

5%

1/16W

MF

402

NO STUFF

R14

1

2

0

1/16W

5%

MF

402

NO STUFF

R13

1

2

402

MF

1/16W

5%

0

R15

1

2

051-6694

B

7

45

CPU_PLL_CFG<4>

CPU_PLL_CFG<2>

CPU_PLL_FS00

PLL_STOP_L

CPU_EMODE0_LCPU_HRESET_L

CPU_HRESET_L

CPU_HRESET_INV

MAXBUS_SLEEP

CPU_BUS_VSEL

CPU_PLL_STOP_OC

CPU_PLL_STOP_OC

CPU_PLL_STOP_BASE

CPU_VCORE_HI_OC

PLL_STOP_L

CPU_PLL_CFG<0>

MAXBUS_SLEEP

CPU_PLL_FS10

CPU_PLL_CFG<1>

CPU_PLL_CFG<3>

CPU_PLL_FS01

CPU_PLL_CFGEXT

5 5 6 6 7 7 8

8

5

5

15

15

6

6

16

16

7

7

35

7

7

31

35

5

5

7

5

40

40

39

5

31

31

35

7

5

39

5

5

Page 8

(PLL6)

VSSA_7

(PLL6)

VDD15A_7

D_42

D_41

D_40

D_39

D_38

D_44

D_43

D_45

D_46

D_47

D_48

D_52

D_51

D_50

D_49

D_53

D_55

D_54

D_56

D_57

D_58

D_60

D_59

D_62

D_61

D_63

DBG

DRDY

DTI_0

TEA

TA

DTI_2

DTI_1

D_1

D_0

D_2

D_6

D_5

D_4

D_3

D_7

D_11

D_10

D_9

D_8

D_12

D_14

D_13

D_15

D_16

D_17

D_22

D_21

D_20

D_19

D_18

D_23

D_24

D_25

D_26

D_27

D_32

D_31

D_30

D_29

D_28

D_34

D_33

D_35

D_36

D_37

BR

(1 OF 9)

MAXBUS

INTERFACE

TS

BG

A_0

A_1

A_2

A_3

A_4

A_5

A_9

A_6

A_7

A_8

A_10

A_14

A_13

A_12

A_11

A_20

A_16

A_17

A_18

A_19

A_15

A_27

A_22

A_21

A_30

A_29

A_28

A_26

A_25

A_24

A_23

TT_2

TT_1

TT_0

A_31

TBST

TSIZ_0

TSIZ_1

TSIZ_2

CI

GBL

TT_4

AACK

QREQ

ARTRY

TT_3

WT

HIT

ANALYZER_CLK

SUSPENDACK

SUSPENDREQ

QACK

STOPCPUCLK

CPU_FB_OUT

CPU_FB_IN

CPU_CLK

TBEN

ACS_REF

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

IT CANNOT BE CHANGED BY SOFTWARE

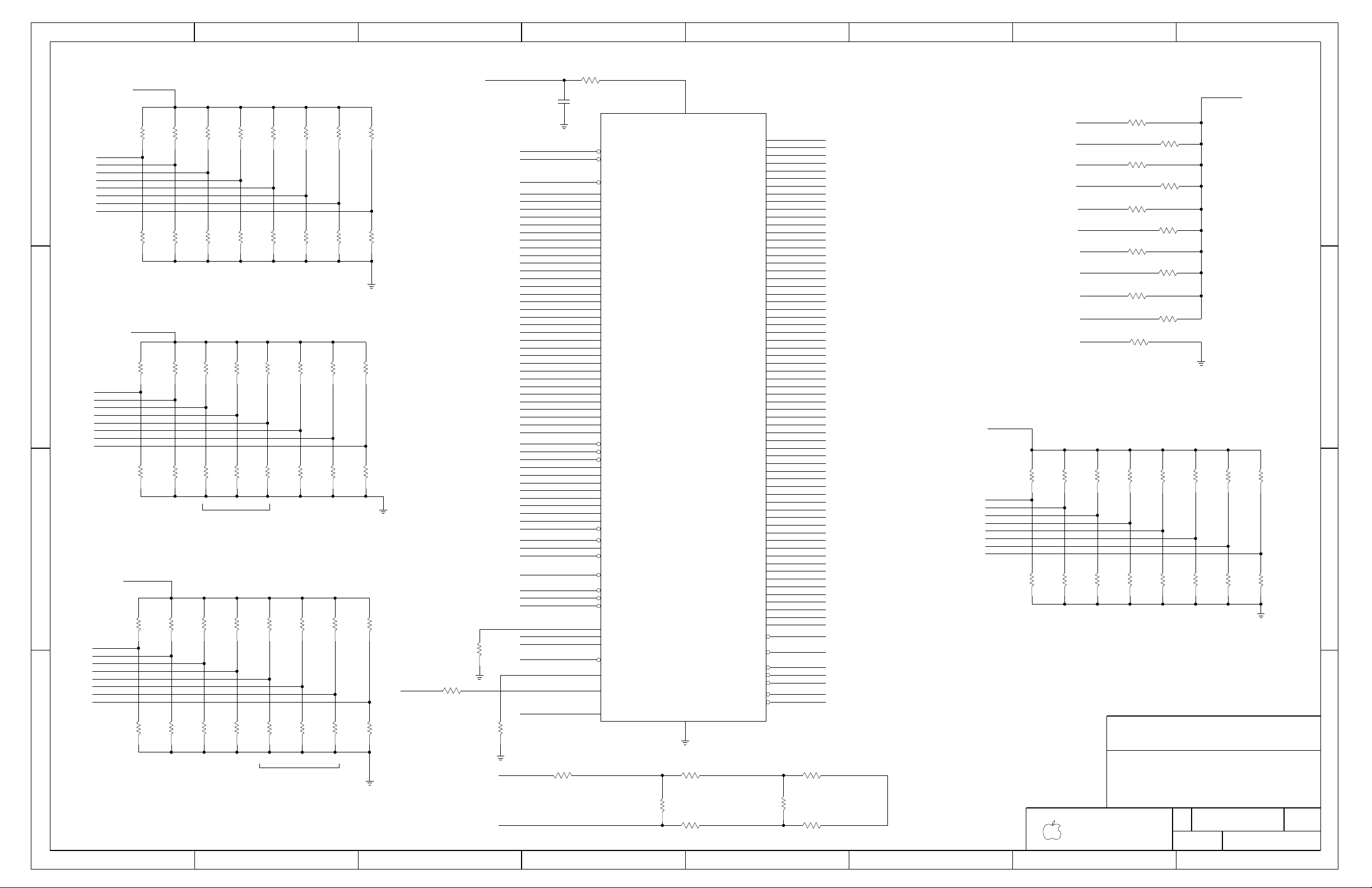

Intrepid MaxBus

THE FOLLOWING STRAP BITS CAN BE

3/ D44 - PLL4MODESEL_NXT<0> - SLEEP/WAKE CYCLE REQUIRED

011: 33.3 ohm

TI 1394b workaround

0: Normal 1394b

1: TI PHY workaround

SelPLL4ExtSrc

0: PLL5

1: External source

INTREPID OUTPUTS HIGH BY DEFAULT

0: Max Bus (G4)

Processor Bus Mode

1: 60x bus (G3)

FireWire PHY interface

0: Legacy interface

1: B-mode interface

PCI1_REQ0_L / PCI1_GNT0_L

0: REQ/GNT

1: GPIOs

PCI1_REQ2_L / PCI1_GNT2_L

0: REQ/GNT

1: GPIOs

1: GPIOs

PCI1_REQ1_L / PCI1_GNT1_L

0: REQ/GNT

Spare

Spare

Spare

BIT 56 TO 63

INTREPID BOOT STRAPS

MAXBUS PULL-UPS

IF A STRAP IS NOT LISTED, THEN

6/ D33 - ANALYZERCLK_EN_H - IMMEDIATE EFFECT

5/ D42 - PLL4MODESEL_NXT<2> - SLEEP/WAKE CYCLE REQUIRED

4/ D43 - PLL4MODESEL_NXT<1> - SLEEP/WAKE CYCLE REQUIRED

2/ D46 - SELPCI1SPREADCLK - SLEEP/WAKE CYCLE REQUIRED

1/ D47 - SELAGPSPREADCLK - SLEEP/WAKE CYCLE REQUIRED

CHANGED BY SOFTWARE:

INPUT

NO BUS KEEPER

NO BUS KEEPER - PU

NO BUS KEEPER - PU

INPUT - PU

INPUT - PD

NO BUS KEEPER - ?

Vin = Intrepid Vcore (1.5V)

Vout = MaxBus rail (1.8V)

NO BUS KEEPER - PU

INPUT - PU

NO BUS KEEPER - PU

NO BUS KEEPER - ?

NO BUS KEEPER - ?

NO BUS KEEPER - ?

NO BUS KEEPER - PU

FB BUFFER HAS 50 OHM OUTPUT IMPEDANCE

NO BUS KEEPER - PU

SHORT = 1" SHORTER THAN MATCHED LENGTH

BUF_REF_CLK_OUTEnable_h

1: Active

0: Inactive

Spare

000: 200 ohm

100: 200 ohm

010: 100 ohm

110: 66.6 ohm

001: 50 ohm

101: 40 ohm

111: 28.6 ohm

MaxBus output impedance

BIT2 BIT1 BIT0

Spare

BIT 48 TO 55

MODE C (2.0X) IS FOR CLOCK SLEW OPERATION

MODE A (2.5X) IS FOR STATIC OPERATION

PCI0 Source Clock

1: PLL4

0: PLL5 (NO SPREAD)

PCI1 Source Clock

1: PLL4

0: PLL5 (NO SPREAD)

InternalSpreadEn

0: Inactive

1: Active

Spare

Spare

100: 83.20MHZ

011: 99.84MHZ (1.5X)

010: 133.12MHZ (2.0X)

001: 149.76MHZ

000: 166.4MHZ (2.5X)

PLL4MODESEL_NXT[2:0]

BIT0BIT2 BIT1

BIT 40 TO 47

Spare

Spare

Spare

Spare

ExtPLL_SDwn_Pol

0: Active high

1: Active low

DDR_TPDEn_Pol

0: Active high

1: Active low

AnalyzerClk_En_h

0: Inactive

1: Active

DDR_TPDModeEnable_h

0: TDI input (JTAG)

1: TDI output

INTREPID BOOT STRAPS

LONG = 1" LONGER THAN MATCHED LENGTH

BIT 32 TO 39

NO BUS KEEPER

R137

1

2

402

MF

1/16W

1%

1K

C308

1

2

CERM

6.3V

20%

0.22UF

402

R227

1 2

5%

MF

402

1/16W

4.7

R144

1 2

0

5%

1/16W

MF

402

RP24

2 7

SM1

1/16W

5%

10K

R167

12

402

1/16W

MF

5%

0

R197

1

2

402

MF

1%

1/16W

511

R178

1

2

NO STUFF

402

MF

1/16W

10K

5%

R179

1

2

NO STUFF

402

MF

1/16W

5%

10K

R651

1

2

NO STUFF

402

MF

1/16W

5%

10K

R166

1

2

NO STUFF

402

MF

1/16W

5%

10K

R153

1

2

402

MF

1/16W

5%

10K

R123

1

2

NO STUFF

402

MF

1/16W

10K

5%

R135

1

2

NO STUFF

402

MF

1/16W

5%

10K

R674

1

2

402

MF

1/16W

5%

10K

R143

1

2

10K

5%

1/16W

MF

402

R673

1

2

MF

402

1/16W

5%

10K

R664

1

2

10K

5%

1/16W

MF

402

R657

1

2

NO STUFF

402

MF

1/16W

5%

10K

R639

1

2

402

1/16W

MF

5%

10K

R643

1

2

10K

5%

1/16W

MF

402

R642

1

2

NO STUFF

402

MF

1/16W

5%

10K

R136

1

2

402

1/16W

MF

5%

10K

R165

1

2

INT_CLK

402

MF

1/16W

5%

10K

R177

1

2

INT_CLK

402

MF

5%

1/16W

10K

R152

1

2

INT_CLK

402

MF

1/16W

5%

10K

R184

1

2

NO STUFF

402

MF

1/16W

5%

10K

R134

1

2

EXT_CLK

10K

5%

1/16W

MF

402

R164

1

2

NO STUFF

402

MF

1/16W

5%

10K

R142

1

2

NO STUFF

402

MF

1/16W

5%

10K

R122

1

2

NO STUFF

402

MF

1/16W

5%

10K

R666

1

2

EXT_CLK

10K

5%

1/16W

MF

402

R658

1

2

EXT_CLK

402

MF

1/16W

5%

10K

R675

1

2

EXT_CLK

10K

5%

1/16W

MF

402

R683

1

2

402

MF

1/16W

5%

10K

R644

1

2

INT_CLK

10K

5%

1/16W

MF

402

R665

1

2

402

MF

1/16W

5%

10K

R652

1

2

10K

5%

1/16W

MF

402

R640

1

2

402

MF

5%

1/16W

10K

R176

1

2

NO STUFF

402

MF

1/16W

5%

10K

R141

1

2

NO STUFF

402

MF

1/16W

5%

10K

R183

1

2

10K

5%

1/16W

MF

402

R162

1

2

NO STUFF

402

MF

1/16W

5%

10K

R151

1

2

NO STUFF

402

MF

1/16W

5%

10K

R163

1

2

402

MF

5%

1/16W

10K

R121

1

2

EXT_CLK

402

MF

1/16W

5%

10K

R676

1

2

10K

5%

1/16W

MF

402

R684

1

2

NO STUFF

402

MF

1/16W

5%

10K

R653

1

2

402

MF

1/16W

5%

10K

R667

1

2

10K

5%

1/16W

MF

402

R659

1

2

402

1/16W

MF

5%

10K

R668

1

2

NO STUFF

10K

5%

1/16W

MF

402

R641

1

2

INT_CLK

402

MF

1/16W

5%

10K

R133

1

2

EXT_CLK

MF

402

1/16W

5%

10K

R645

1

2

INT_CLK

402

MF

1/16W

5%

10K

R182

1

2

NO STUFF

10K

5%

1/16W

MF

402

R174

1

2

402

MF

5%

1/16W

10K

R150

1

2

NO STUFF

402

MF

5%

1/16W

10K

R131

1

2

NO STUFF

10K

5%

1/16W

MF

402

R132

1

2

NO STUFF

402

MF

1/16W

5%

10K

R175

1

2

NO STUFF

10K

5%

1/16W

MF

402

R161

1

2

NO STUFF

402

MF

1/16W

5%

10K

R140

1

2

NO STUFF

402

MF

1/16W

5%

10K

R685

1

2

402

MF

1/16W

5%

10K

R660

1

2

402

MF

1/16W

5%

10K

R678

1

2

NO STUFF

10K

5%

1/16W

MF

402

R647

1

2

1/16W

10K

5%

MF

402

R646

1

2

402

MF

1/16W

5%

10K

R677

1

2

402

MF

1/16W

5%

10K

R669

1

2

402

MF

1/16W

5%

10K

R654

1

2

402

MF

1/16W

5%

10K

U45

B29

H13

G8

H23

D24

D25

J22

B25

H22

G22

D22

B24

B23

E22

J21

G21

A27

E21

A24

D21

A23

H20

B22

H21

A22

E20

B21

E24

D20

A21

G23

B26

A26

D23

A25

E23

E26

E29

G26

J15

J24

H16 A30

G28

K25

D29

B30

D10

G12

B10

J13

A10

D12

E13

G13

B11

D13

A11

G14

E11

H14

E14

B12

G15

B13

H15

D14

B14

A12

G16

H11

E15

J16

D15

A14

A13

D16

E16

G17

B15

H17

B9

A15

B16

E17

A16

J18

H18

D17

G18

A17

B17

B8

E18

B18

D18

A18

A19

H19

B19

J19

A20

D19

A9

E19

G19

B20

G20

A8

E12

D11

A29

B31

G27

A32

AH9

AM8

AK9

E27

A31

A28

E28

B27

G24

H24

D26

E25

G25

B28

D27

J25

H26

H25

D28

CRITICAL

BGA

INTREPID-REV2.1

OMIT

R225

1

2

0

5%

1/16W

MF

402

NO STUFF

R215

1 2

402

MF

1/16W

5%

0

R208

1

2

0

5%

1/16W

MF

402

R207

1 2

402

MF

1/16W

5%

0

NO STUFF

R226

1 2

402

MF

1/16W

5%

0

R196

1 2

402

MF

1/16W

5%

0

NO STUFF

RP24

3 6

SM1

1/16W

5%

10K

RP23

1 8

SM1

1/16W

5%

10K

RP23

4 5

SM1

1/16W

5%

10K

RP23

2 7

SM1

5%

1/16W

10K

RP21

2 7

SM1

1/16W

5%

10K

RP21

1 8

SM1

1/16W

5%

10K

RP21

3 6

SM1

1/16W

5%

10K

RP21

4 5

SM1

1/16W

5%

10K

RP24

4 5

SM1

1/16W

5%

10K

RP23

3 6

SM1

1/16W

5%

10K

458

051-6694

B

CPU_ADDR<2>

CPU_DATA<36>

CPU_DATA<62>

CPU_DATA<63>

CPU_DATA<27>

CPU_DATA<24>

CPU_DATA<43>

CPU_ADDR<26>

CPU_ADDR<27>

CPU_DATA<47>

CPU_DATA<46>

MAXBUS_SLEEP

CPU_DATA<54>

CPU_DATA<52>

MAXBUS_SLEEP

CPU_CI_L

CPU_ADDR<31>

CPU_ADDR<29>

CPU_DATA<42>

CPU_DATA<44>

CPU_GBL_L

+1_5V_INTREPID_PLL7

INTREPID_ACS_REF

CPU_TBEN

CPU_CLK_EN

SYSCLK_LA_TP

INT_CPUFB_OUT

INT_SUSPEND_ACK_L

INT_SUSPEND_REQ_L

CPU_QACK_L

CPU_QREQ_L

CPU_ARTRY_L

CPU_HIT_L

CPU_AACK_L

CPU_WT_L

CPU_TT<3>

CPU_TT<4>

CPU_TT<2>

CPU_TT<0>

CPU_TT<1>

CPU_TBST_L

CPU_ADDR<30>

CPU_ADDR<28>

CPU_ADDR<25>

CPU_ADDR<23>

CPU_ADDR<24>

CPU_ADDR<21>

CPU_ADDR<22>

CPU_ADDR<20>

CPU_ADDR<18>

CPU_ADDR<19>

CPU_ADDR<17>

CPU_ADDR<13>

CPU_ADDR<14>

CPU_ADDR<11>

CPU_ADDR<9>

CPU_ADDR<7>

CPU_ADDR<5>

CPU_ADDR<4>

CPU_ADDR<3>

CPU_ADDR<0>

CPU_ADDR<1>

CPU_TS_L

CPU_BG_L

CPU_BR_L

CPU_DATA<1>

CPU_DATA<0>

CPU_DATA<3>

CPU_DATA<4>

CPU_DATA<2>

CPU_DATA<5>

CPU_DATA<6>

CPU_DATA<8>

CPU_DATA<9>

CPU_DATA<7>

CPU_DATA<10>

CPU_DATA<11>

CPU_DATA<13>

CPU_DATA<12>

CPU_DATA<14>

CPU_DATA<15>

CPU_DATA<16>

CPU_DATA<18>

CPU_DATA<17>

CPU_DATA<19>

CPU_DATA<21>

CPU_DATA<20>

CPU_DATA<22>

CPU_DATA<23>

CPU_DATA<26>

CPU_DATA<25>

CPU_DATA<28>

CPU_DATA<29>

CPU_DATA<31>

CPU_DATA<30>

CPU_DATA<32>

CPU_DATA<33>

CPU_DATA<34>

CPU_DATA<35>

CPU_DATA<36>

CPU_DATA<37>

CPU_DATA<39>

CPU_DATA<40>

CPU_DATA<42>

CPU_DATA<41>

CPU_DATA<43>

CPU_DATA<45>

CPU_DATA<44>

CPU_DATA<46>

CPU_DATA<47>

CPU_DATA<49>

CPU_DATA<50>

CPU_DATA<48>

CPU_DATA<51>

CPU_DATA<52>

CPU_DATA<54>

CPU_DATA<53>

CPU_DATA<55>

CPU_DATA<56>

CPU_DATA<57>

CPU_DATA<59>

CPU_DATA<58>

CPU_DATA<60>

CPU_DATA<62>

CPU_DATA<61>

CPU_DATA<63>

CPU_DBG_L

CPU_DRDY_L

CPU_DTI<0>

CPU_DTI<1>

CPU_DTI<2>

CPU_TA_L

CPU_TEA_L

+1_5V_INTREPID_PLL

CPU_DATA<55>

CPU_DATA<41>

CPU_DATA<40>

CPU_DATA<53>

CPU_DATA<51>

CPU_DATA<50>

CPU_DATA<49>

CPU_DATA<48>

INT_CPUFB_IN

INT_CPUFB_OUT_NORM

INT_CPUFB_IN_NORM

INT_CPUFB_LONG

CPU_DATA<61>

CPU_DATA<60>

CPU_DATA<59>

MAXBUS_SLEEP

CPU_DATA<58>

CPU_DATA<57>

CPU_DATA<56>

CPU_BR_L

CPU_ARTRY_L

CPU_DRDY_L

CPU_HIT_L

CPU_AACK_L

CPU_TEA_L

CPU_DBG_L

CPU_BG_L

MAXBUS_SLEEP

INT_CPUFB_IN

SYSCLK_CPU_UF

SYSCLK_CPU

INT_CPUFB_OUT

INT_CPUFB_OUT_SHORT

CPU_ADDR<8>

CPU_ADDR<10>

CPU_ADDR<16>

CPU_ADDR<15>

CPU_TS_L

CPU_TA_L

CPU_QREQ_L

CPU_DATA<38>

CPU_TSIZ<2>

CPU_TSIZ<1>

CPU_TSIZ<0>

CPU_DATA<39>

MAXBUS_SLEEP

CPU_DATA<45>

CPU_DATA<35>

CPU_DATA<37>

CPU_DATA<38>

CPU_DATA<34>

CPU_DATA<33>

CPU_DATA<32>

CPU_ADDR<6>

CPU_ADDR<12>

39

39

39

39

39

35

35

35

35

35

16

16

16

16

16

15

15

15

15

15

8

8

8

8

8

37

37

37

37

37

37

7

37

37

7

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

39

37

37

37

37

37

37

37

37

37

37

37

7

37

37

37

37

37

37

37

37

37

37

37

7

37

37

37

37

37

7

37

37

37

37

37

37

37

37

8

8

8

37

37

8

37

37

8

8

6

8

8

6

37

37

37

8

8

37

37

37

8

8

8

8

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

8

8

8

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

37

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

37

37

37

8

8

14

8

8

8

8

8

8

8

8

37

8

8

8

6

8

8

8

8

8

8

8

8

8

8

8

6

37

37

37

37

37

37

37

8

8

8

8

37

37

37

8

6

8

8

8

8

8

8

8

37

37

5

6

6

6

6

6

6

5

5

6

6

5

6

6

5

5

5

5

6

6

5

39

5

31

8

31

31

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

5

5

5

5

5

5

5

12

6

6

6

6

6

6

6

6

8

37

37

37