Page 1

WWW.AliSaler.Com

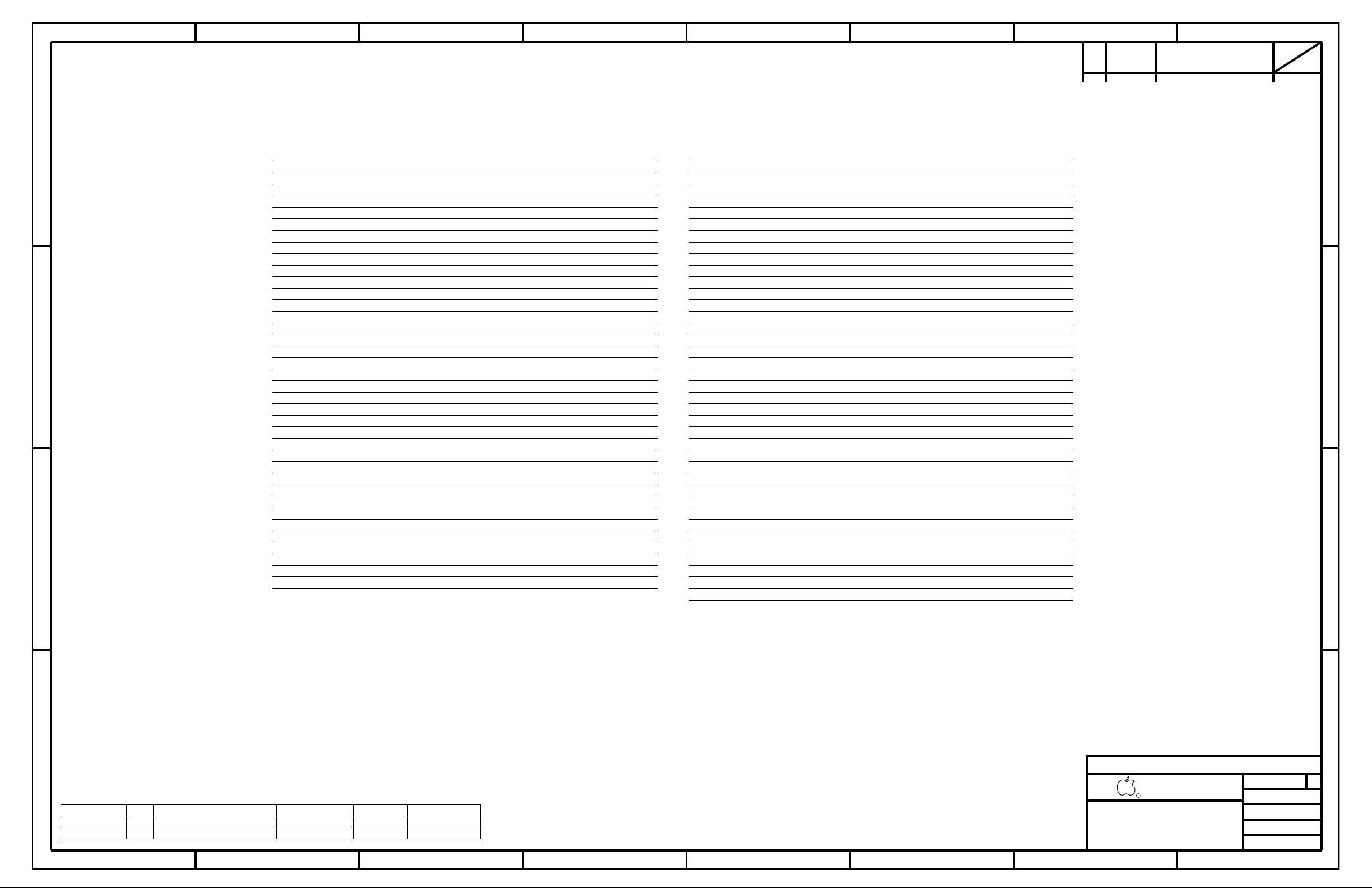

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

8

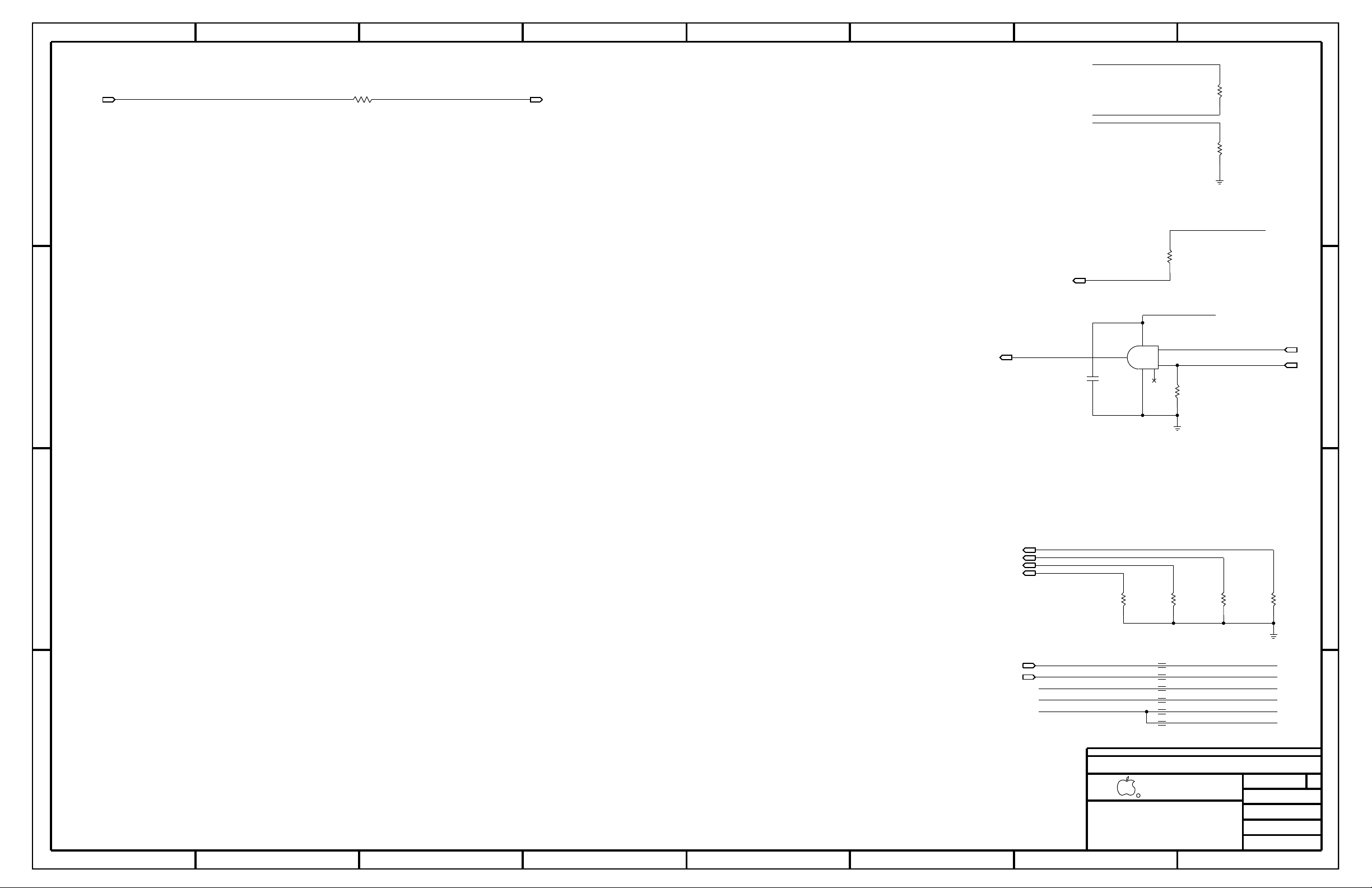

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

IV ALL RIGHTS RESERVED

II NOT TO REPRODUCE OR COPY IT

3

B

7

BRANCH

DRAWING NUMBER

SIZE

D

SHEET

R

DATE

D

A

C

PAGE

A

C

3456

D

B

87 6 5

4 21

12

APPD

CK

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

DRAWING TITLE

DESCRIPTION OF REVISION

REV ECN

REVISION

PROPRIETARY PROPERTY OF APPLE INC.

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_HEAD

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_HEAD

11/21/2014

PCB TO BE SILK-SCREENED WITH UL/CUL RECOGNITION MARK, MANUFACTURER’S UL FILE

NUMBER, UL PCB MATERIAL DESIGNATION, 130-C TEMP. RATING AND V-0 FLAME RATING.

PCB, UL RECOGNIZED, MIN. 130-C TEMP. RATING AND V-0 FLAME RATING PER UL 796 & UL 94.

PRODUCT SAFETY REQUIREMENTS:

Schematic / PCB #’s

J92 MLB NEWARK - DVT

ALIASES RESOLVED

1 OF 75

<PART_DESCRIPTION>

<SCH_NUM>

<ECODATE>

<ECN><REV>

<ECO_DESCRIPTION>

1 OF 130

<BRANCH>

<E4LABEL>

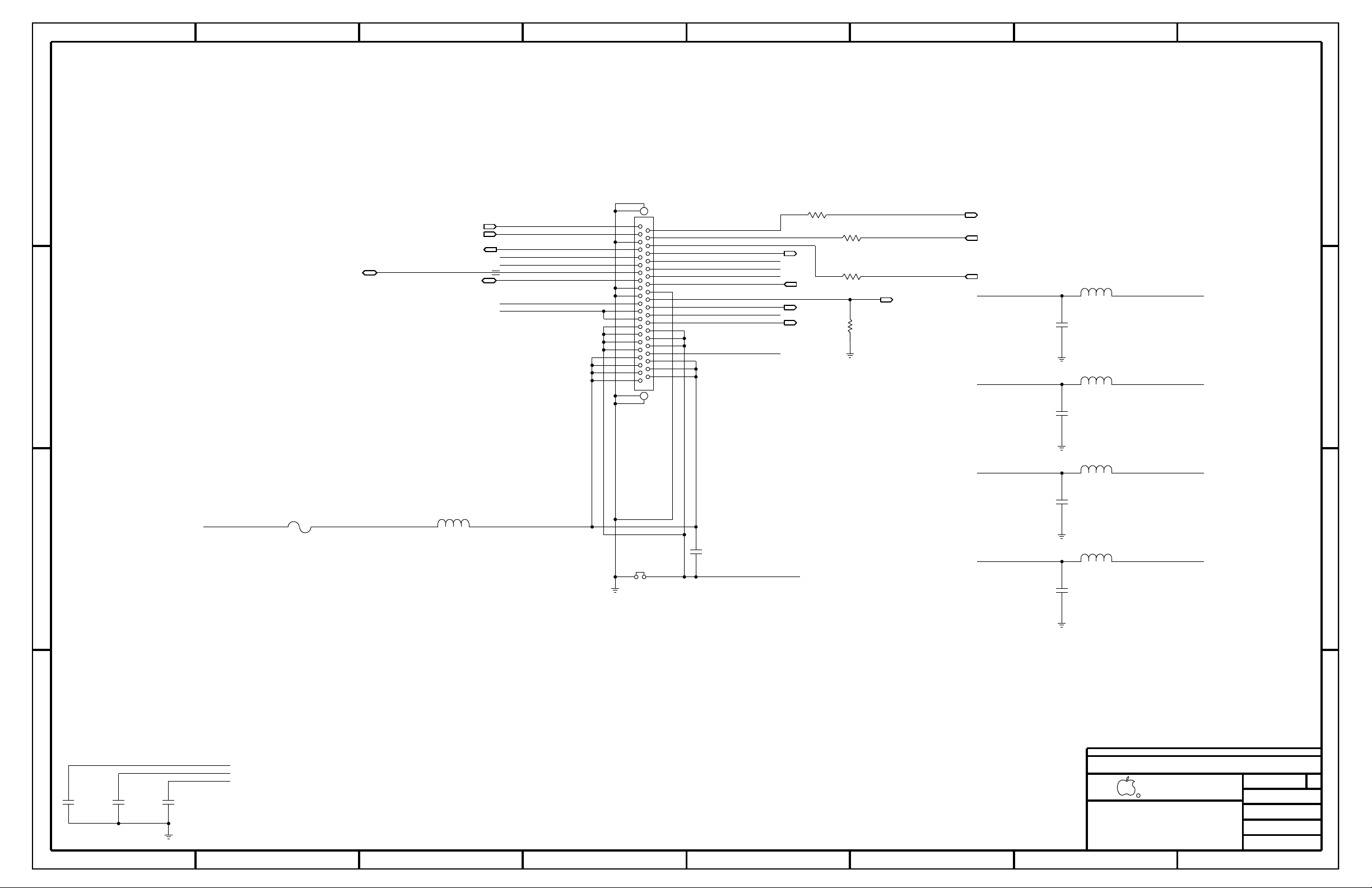

SPI+SWD Debug Connector

J92_DEVMLB

61

37

07/23/2013

Temperature Sensing

J92_DEVMLB

55

36

09/12/2013

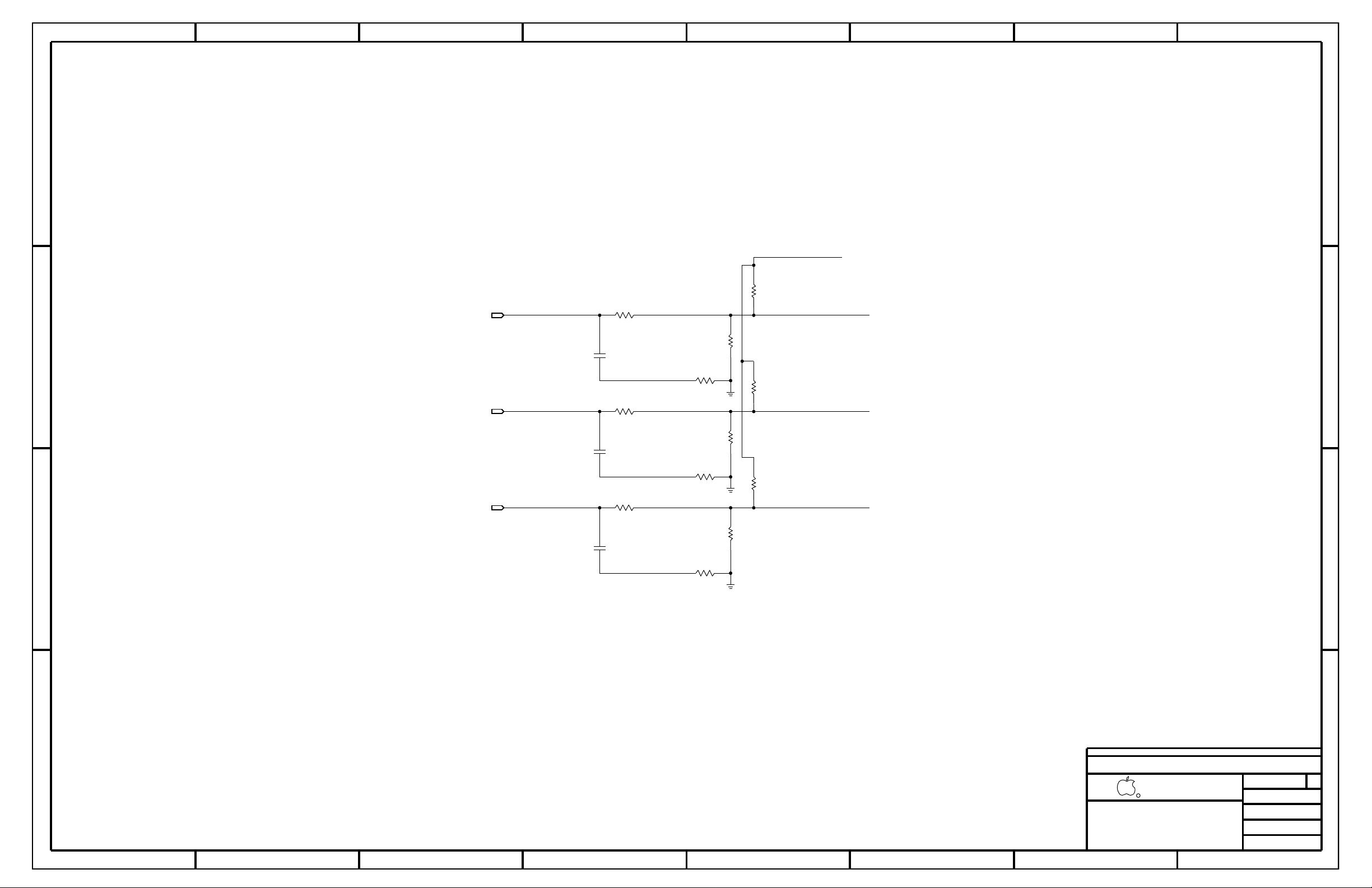

Voltage & Current Sensing

J92_DEVMLB

54

35

02/07/2014

SMBus Connections

J43_MLB

53

34

10/24/2012

SMC Project Support

J43_MLB

52

33

10/24/2012

SMC Shared Support

J92_DEVMLB

51

32

10/11/2013

SMC

J92_DEVMLB

50

31

10/11/2013

Keyboard & Trackpad Conn

J92_DEVMLB

48

30

03/26/2014

E85 FLEX CONNECTOR

DEV_MLB

47

29

04/17/2014

Host Port Micro

DEV_LIO

46

28

04/30/2014

High Speed MUXing

DEV_MLB

45

27

04/17/2014

Low Speed MUXing

J92_DEVMLB

44

26

07/08/2014

Camera 2 of 2

J92_DEVMLB

40

25

10/10/2013

Camera 1 of 2

J92_DEVMLB

39

24

07/24/2013

SSD Support

J92_DEVMLB

37

23

09/11/2013

WIFI/BT: MODULE

J72_MLB

35

22

11/13/2012

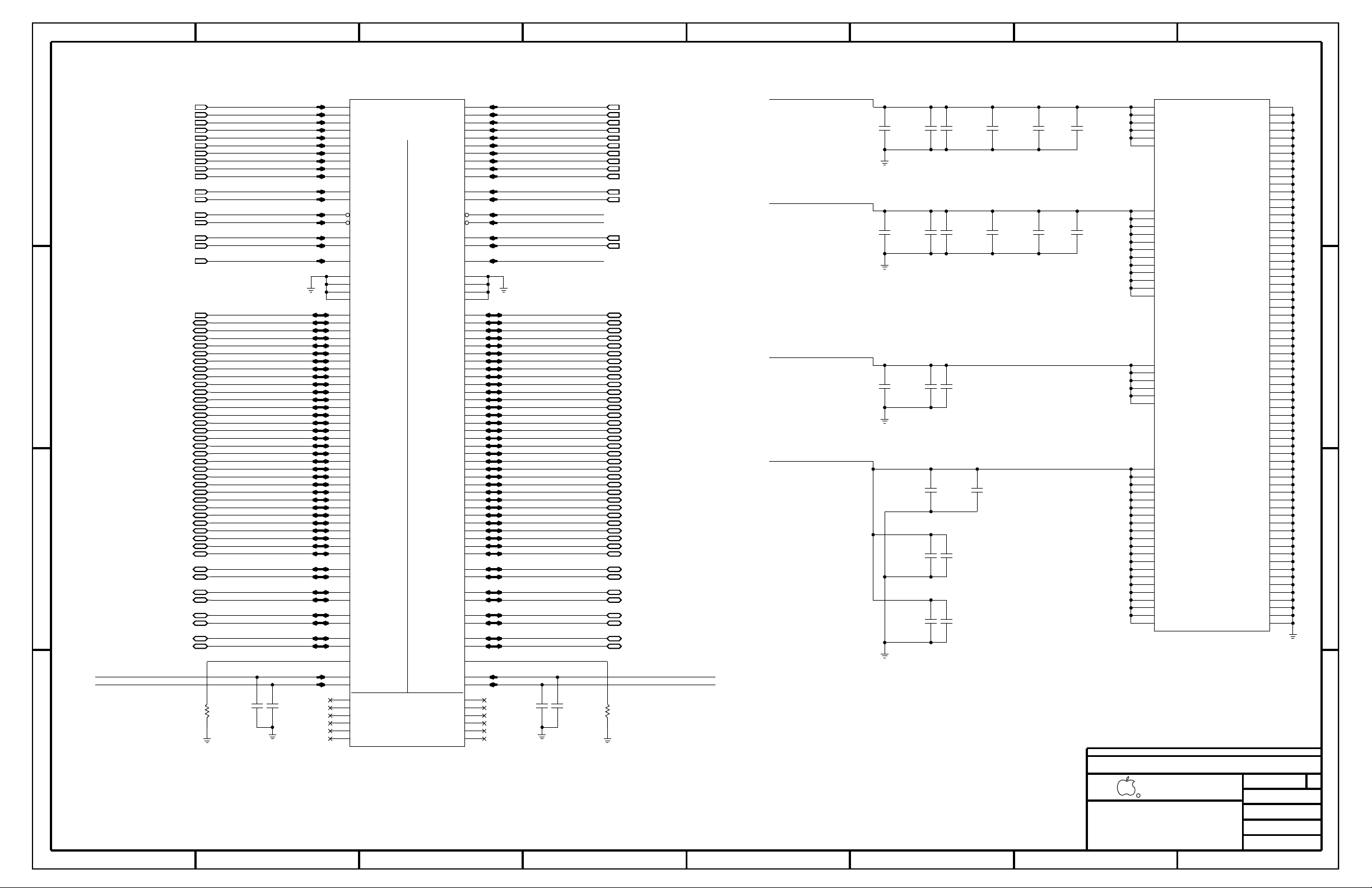

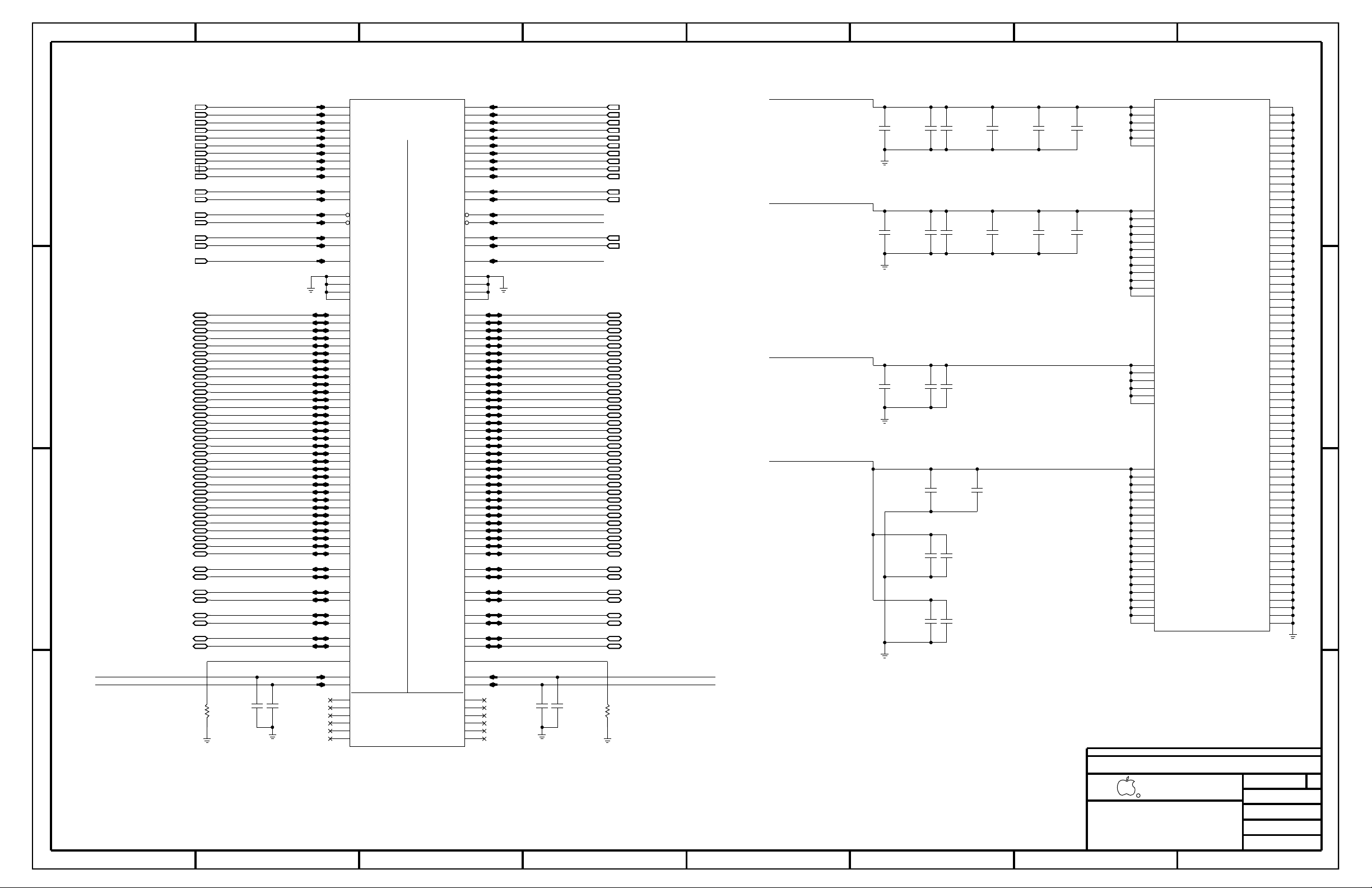

LPDDR3 DRAM Channel B (0-63)

(MASTER)

25

21

(MASTER)

LPDDR3 DRAM Channel A (0-63)

(MASTER)

23

20

(MASTER)

LPDDR3 VREF MARGINING

J92_DEVMLB

22

19

06/28/2013

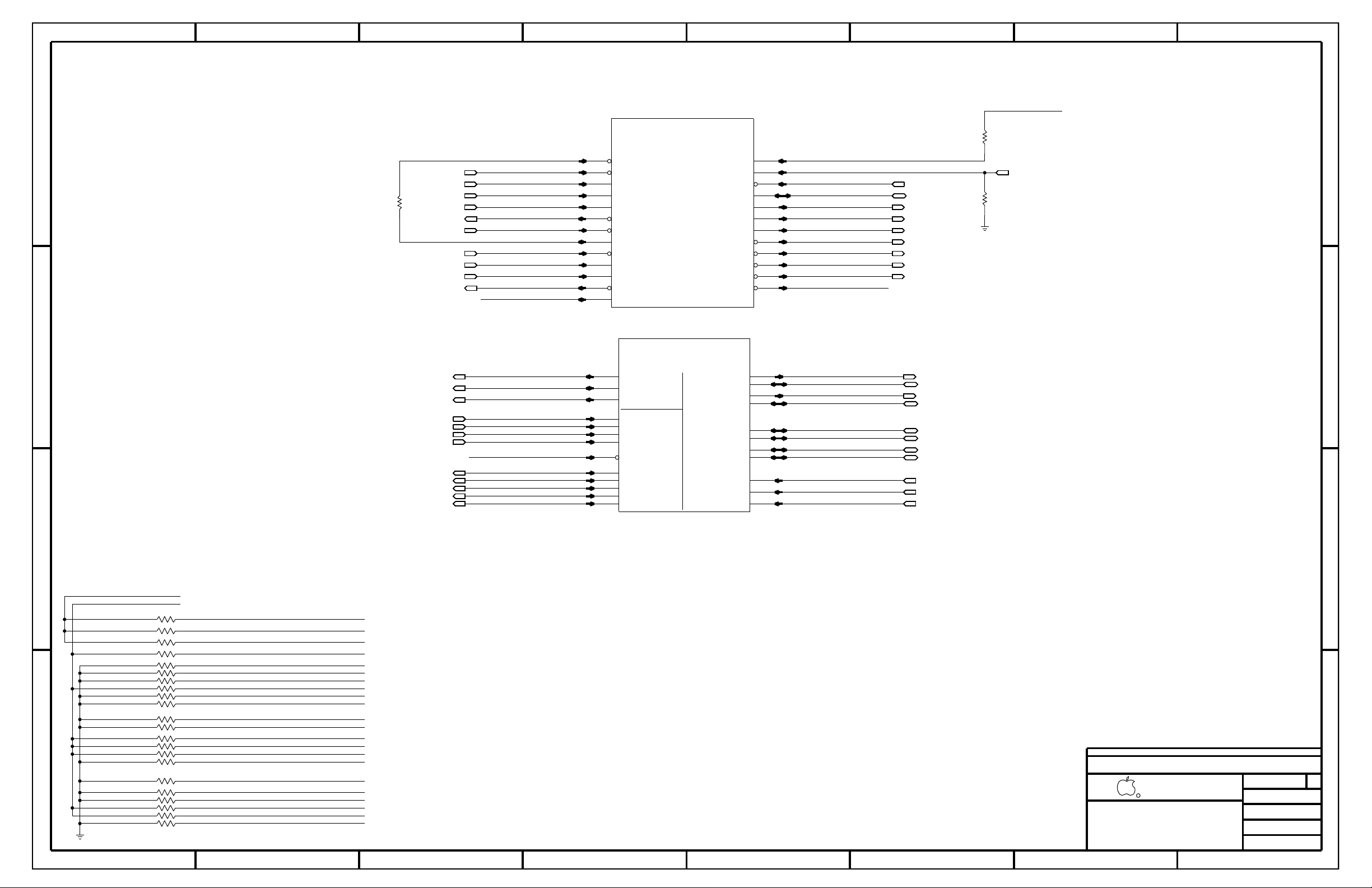

Project Chipset Support

J92_DEVMLB

20

18

08/01/2013

Chipset Support

J92_DEVMLB

19

17

06/28/2013

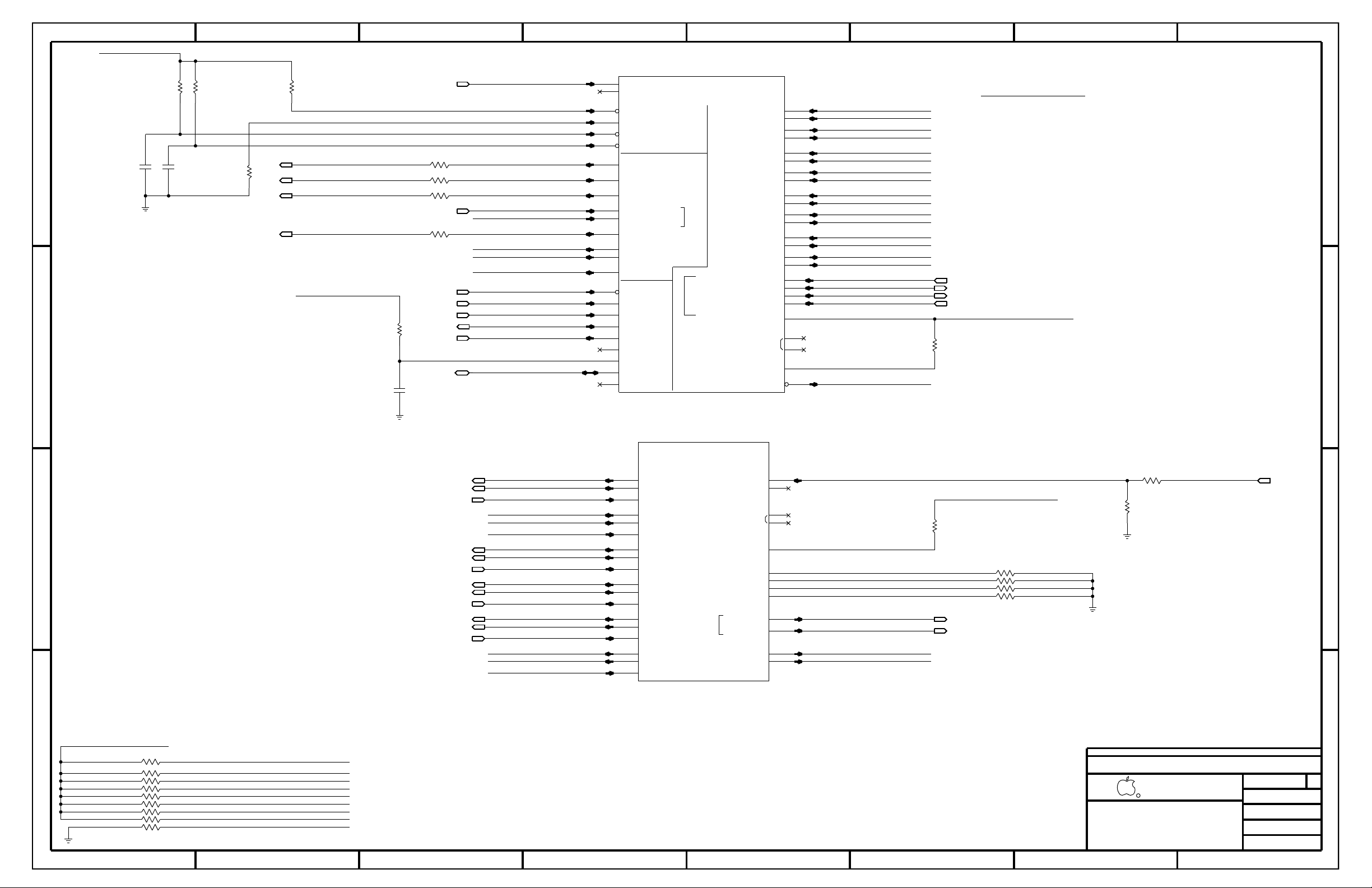

CPU/PCH Merged XDP

J92_DEVMLB

18

16

09/16/2013

PCH GPIO/MISC/LPIO

J92_DEVMLB

16

15

08/14/2013

PCH PCIe/USB/LPC/SPI/SMBus

J92_DEVMLB

15

14

06/28/2013

PCH PM/PCI/GFX

J92_WILL

14

13

04/10/2013

PCH Audio/JTAG/SATA/CLK

J92_WILL

13

12

04/10/2013

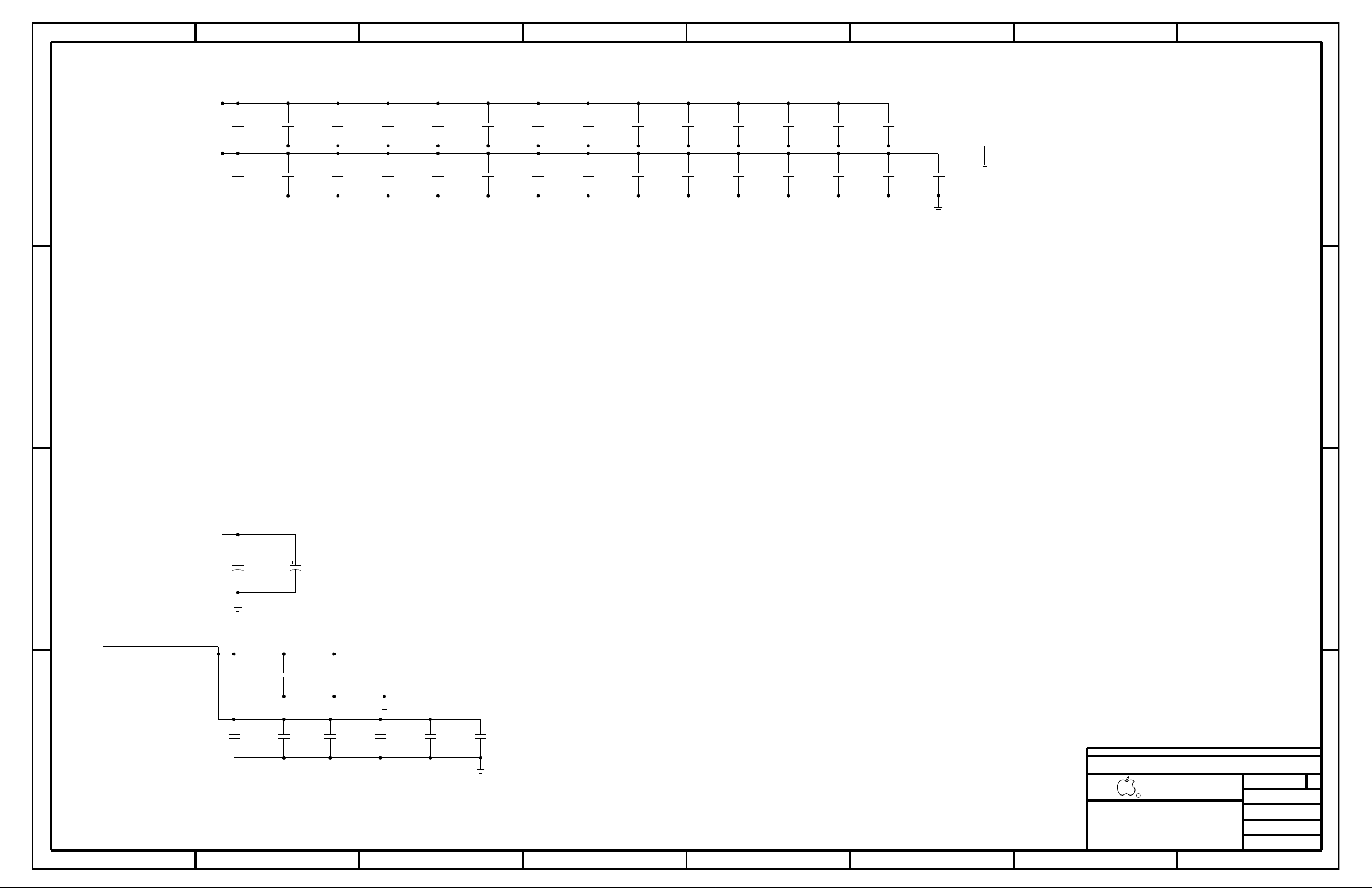

PCH Decoupling

J92_DEVMLB

12

11

09/23/2013

CPU Decoupling

J92_DEVMLB

10

10

10/01/2013

CPU/PCH GROUNDS

J92_WILL

9

9

04/10/2013

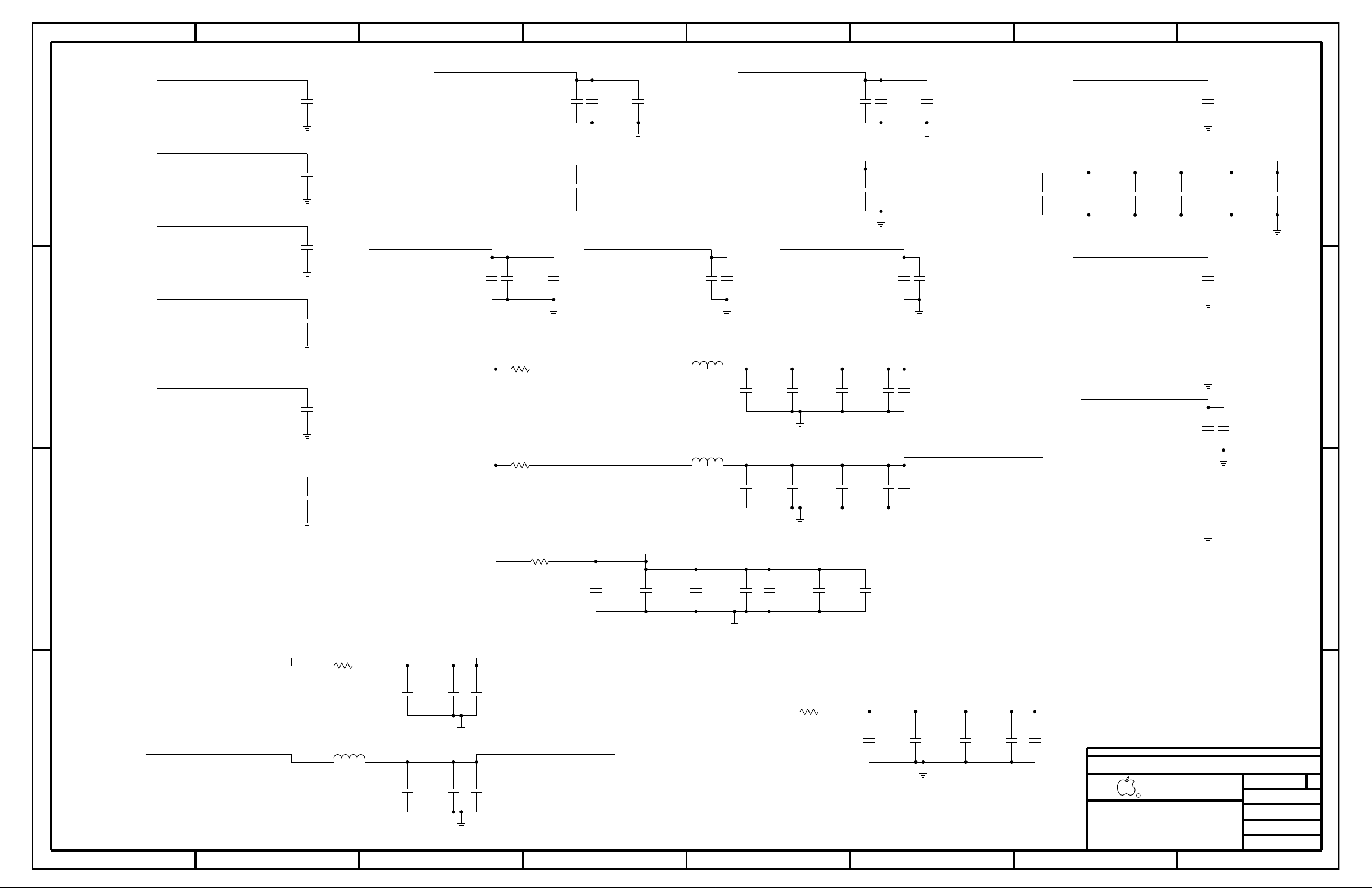

CPU/PCH POWER

J92_DEVMLB

8

8

10/01/2013

CPU DDR3/LPDDR3 Interfaces

J92_LS_MLB

7

7

07/17/2013

CPU Misc/JTAG/CFG/RSVD

J92_WILL

6

6

04/10/2013

CPU GFX/DC_TEST

J92_WILL

5

5

04/10/2013

PD PARTS

J43_MLB

4

4

10/24/2012

J92 BOM Variants

J43_MLB

3

3

10/24/2012

BOM Configuration

J43_MLB

2

2

10/24/2012

MASTER

130

MASTER

75

Debug Support

07/15/2013

120

J92_DEVMLB

74

Reference

04/08/2014

118

J92_DEVMLB

73

Project Specific Constraints

09/11/2013

117

J92_DEVMLB

72

SMC Constraints

08/01/2013

116

J92_DEVMLB

71

Camera Constraints

11/16/2011

115

MASTER

70

NAND CONSTRAINTS

05/07/2013

114

J92_LS_MLB

69

Memory Constraints

04/17/2014

113

DEV_MLB

68

PCH Constraints 2

04/17/2014

112

DEV_MLB

67

PCH Constraints 1

07/08/2014

111

J92_DEVMLB

66

CPU Constraints

10/24/2012

110

J43_MLB

65

PCB Rule Definitions

10/24/2012

105

J41_MLB

64

Project FCT/NC/Aliases

07/08/2014

104

J92_DEVMLB

63

Func Test / No Test

07/08/2014

103

J92_DEVMLB

62

J92 Signal Aliases

(MASTER)

102

(MASTER)

61

Memory Signal Swaps

10/24/2012

100

J43_MLB

60

Power Aliases

02/12/2014

89

J92_DEVMLB

59

SSD SR, Power, & Debug

10/07/2013

88

J92_SSD

58

SSD NAND Flash & ROM

10/10/2013

87

J92_DEVMLB

57

SSD Controller (4 of 4)

02/11/2014

86

J92_SSD

56

SSD Controller (3 of 4)

10/10/2013

85

J92_DEVMLB

55

SSD Controller (2 of 4)

02/11/2014

84

J92_SSD

54

SSD Controller (1 of 4)

09/25/2013

83

J92_DEVMLB

53

eDP Display Connector

09/20/2013

81

J92_DEVMLB

52

Power Control

07/24/2013

80

J92_DEVMLB

51

Power FETs

04/04/2014

78

J92_DEVMLB

50

Misc Power Supplies

10/01/2013

77

J92_DEVMLB

49

LCD Backlight Driver

04/04/2014

76

J92_DEVMLB

48

1.05V S0 Power Supply

04/17/2014

75

DEV_MLB

47

5V & 3.3V Power Supplies

04/04/2014

74

J92_DEVMLB

46

LPDDR3 Supply

04/17/2014

73

DEV_MLB

45

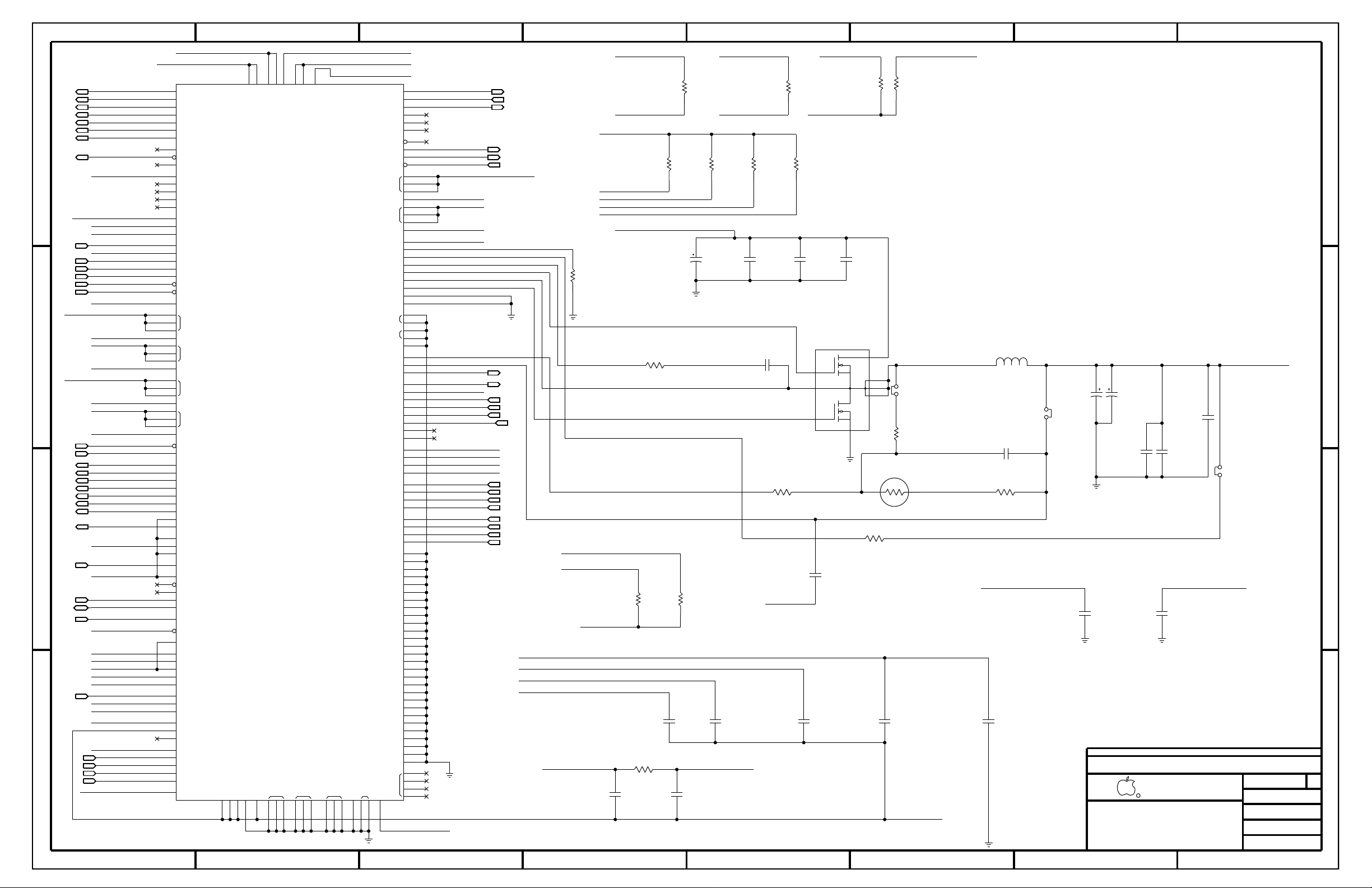

CPU VR12.5 VCC Power Stage

10/09/2012

72

J43_MLB

44

CPU VR12.6 VCC Regulator IC

04/04/2014

71

J92_DEVMLB

43

PBus Supply & Battery Charger

02/04/2013

70

J92_WILL

42

3.3V G3Hot Regulator

10/24/2012

69

J43_MLB

41

Battery Connector

04/17/2014

67

CARA_J92

40

AUDIO: CONNECTORS

09/19/2013

64

J92_DEVMLB

39

Audio:Right Speaker Amps

820-00045

PCBF,MLB-NEWARK,J92

PCB1 CRITICAL

1

SCHEM,MLB-NEWARK,J92

SCH

051-00107

CRITICAL

09/19/2013

63

J92_DEVMLB

38

Audio:Left Speaker Amps

Contents

(.csa)

Date

SyncPage

Table of Contents

MASTER

1

1

MASTER

Contents

Date

(.csa)

Page Sync

Page 2

WWW.AliSaler.Com

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5

4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

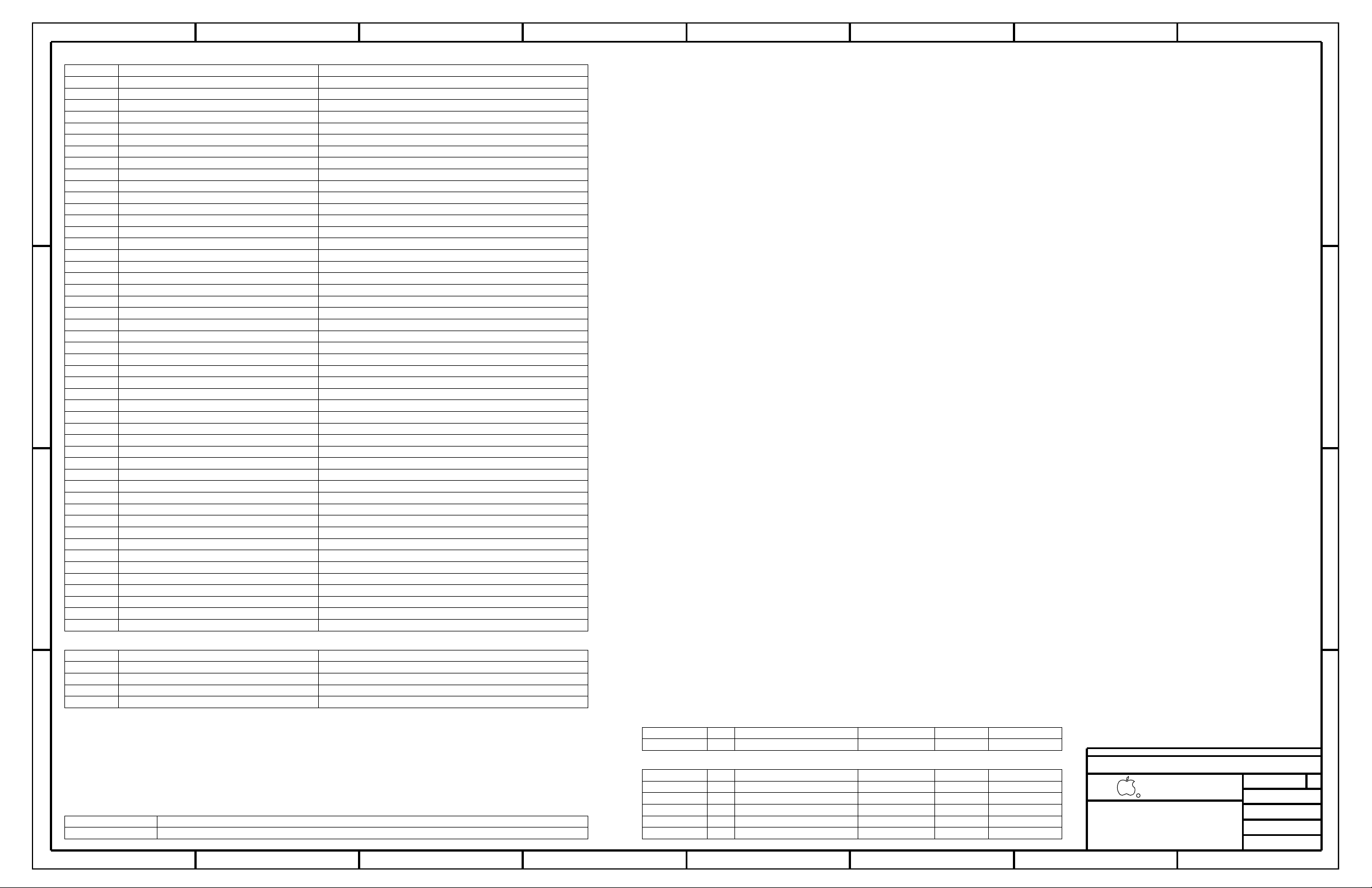

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_BOMGROUP_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_ALT_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

CPU DRAM SPD Straps

Programmable Parts

BOM Groups

CFG 2

8GB

HYNIX

Module Parts

1

MICRON

Alternate Parts

00

SAMSUNG

1

2GB

0

1

0

CFG 0

1

1

10

1

CFG 3

4GB QDP

1

4GB DDP

DRAM Parts

CFG 1

VENDOR

CPU DRAM CFG Chart

0

ELPIDA

0

SIZE

SSD POP Parts

0

RAMCFG0:H,RAMCFG1:H,RAMCFG2:H,RAMCFG3:H,DRAM_TYPE:ELPIDA_8GB

DRAM:ELP_8GB

DRAM:HYN_8GB

RAMCFG0:L,RAMCFG1:L,RAMCFG2:H,RAMCFG3:H,DRAM_TYPE:HYNIX_8GB

DRAM:ELP_2GB

RAMCFG0:H,RAMCFG1:H,RAMCFG2:L,RAMCFG3:L,DRAM_TYPE:ELPIDA_2GB

NXP alt for Diodes dual

376S1129

ALL

376S0855

338S00055

CRITICALSSD_CTRL

S1X:A2

1

IC,S1-X,CONTROLLER,A2,841(312)B,FCBGA

CRITICAL

S1X:A1

SSD_CTRL

1338S1288

IC,S1-X,CONTROLLER,A1,841(312)B,FCCSP

DRAM_TYPE:ELPIDA_4GB

CRITICAL

IC,SDRAM,LPDDR-1600,16GBIT,253B FBGA

333S0740 2

U2300,U2500

IC,SDRAM,LPDDR-1600,32GBIT,253B FBGA

333S0731 2

U2300,U2500

DRAM_TYPE:HYNIX_8GB

CRITICAL

IC,SDRAM,LPDDR-1600,16GBIT,253B FBGA

U2300,U2500

998-6454 2

DRAM_TYPE:ELPIDA_4GB_QDP

CRITICAL

IC,SDRAM,LPDDR-1600,8GBIT,253B FBGA

998-6453

U2300,U2500

2

DRAM_TYPE:ELPIDA_2GB

CRITICAL

2998-6486

U2300,U2500

DRAM_TYPE:HYNIX_2GB

CRITICAL

IC,SDRAM,LPDDR-1600,8GBIT,253B FBGA

IC,SDRAM,LPDDR-1600,16GBIT,253B FBGA

DRAM_TYPE:HYNIX_4GB_QDP

2

U2300,U2500

CRITICAL

333S00028

IC,SDRAM,LPDDR-1600,16GBIT,253B FBGA

DRAM_TYPE:HYNIX_4GB

2

U2300,U2500

CRITICAL

333S0730

Toshiba alt for Diodes dual

ALL

376S0855

376S00074

NXP alt for Diodes single

ALL

376S1089 376S1128

CRITICAL

2333S0741

IC,SDRAM,LPDDR-1600,32GBIT,253B FBGA

DRAM_TYPE:ELPIDA_8GB

U2300,U2500

J11/J13 MLB DYMAX ADHESIVE 29993-SC 0.4G

1 GLUE946-3892 CRITICAL

IC,CPU,BW,QGKZ,QS,E0,2/2,0.8,4.5W,.8,B1234

337S00054

CPU:0.8GHZ

1 U0500 CRITICAL

CRITICALU05001

CPU:1.1GHZ

337S00099

IC,CPU,BW,QH2Z,PRQ,F0,2/2,1.1,5W,.85,B1234

CRITICALU05001

CPU:1.2GHZ

337S00098

IC,CPU,BW,QH2V,PRQ,F0,2/2,1.2,5W,.9,B1234

RAMCFG0:H,RAMCFG1:H,RAMCFG2:L,RAMCFG3:H,DRAM_TYPE:ELPIDA_4GB

DRAM:ELP_4GB

DRAM:HYN_4GB_QDP

RAMCFG0:L,RAMCFG1:L,RAMCFG2:H,RAMCFG3:L,DRAM_TYPE:HYNIX_4GB_QDP

128S0334

Kemet alt to Sanyo

ALL

128S0393

ALL

138S0648138S0703

Murata alt to Taiyo Yuden

372S0186

NXP alt to Diodes

ALL

372S0185

376S1053

Diodes alt to Fairchild

376S0604

ALL

IC,SMC12-B1,40MHZ/50DMIPS MCU,7X7,168BGA

U5000 CRITICAL338S1231

SMC:BLANK

1

DRAM:ELP_4GB_QDP

RAMCFG0:H,RAMCFG1:H,RAMCFG2:H,RAMCFG3:L,DRAM_TYPE:ELPIDA_4GB_QDP

DRAM:HYN_4GB

RAMCFG0:L,RAMCFG1:L,RAMCFG2:L,RAMCFG3:H,DRAM_TYPE:HYNIX_4GB

DRAM:HYN_2GB

RAMCFG0:L,RAMCFG1:L,RAMCFG2:L,RAMCFG3:L,DRAM_TYPE:HYNIX_2GB

XDP

MLB_DEBUG:PROD

XDP_CONN,XDP,HPMBB:SSP0,HPMVBUS:VDET

MLB_DEBUG:PVT

333S0733

CRITICAL

1

S1X_DRAM:ELPIDA

SSD_DRAM

IC,LPDDR2,128MX32,1.2V,ELPIDA 28NM,312B

685-00004

SSDRAM:A1_HYN

U8400

1

CRITICAL

POP,MLB,S1X-A1,HYN-4GBIT,X261

685-00003

SSDRAM:A1_ELP

CRITICAL

1

U8400

POP,MLB,S1X-A1,ELP-4GBIT,X261

SSDRAM:A0_HYN

339S0244

U8400

CRITICAL

1

POP,S1-X CONTROLLER+4GBITS HYN,841B,FCBGA

SSDRAM:A0_ELP

339S0243

CRITICAL

U8400

1

POP,S1-X CONTROLLER+4GBITS ELP,841B,FCBGA

1 U0500 CRITICAL

CPU:1.3GHZ

337S00097

IC,CPU,BW,QH2R,PRQ,F0,2/2,1.3,5W,.9,B1234

SSD_DRAM

IC,LPDDR2,128MX32,1.2V,HYNIX 29NM,312B

S1X_DRAM:HYNIX

333S0694 1

CRITICAL

CRITICAL

1

870-00878

TAPE,CONDUCTIVE,SSD,REEL,X261

SSD_TAPE

IC,MCU,LPC11U37,128KB/12KB,TFBGA48

1 CRITICALU4600337S4638

HPM:BLANK

U6100

BOOTROM_MAC:BLANK

335S1010 CRITICAL1

64 MBIT SPI QUAD I/O FLASH,CSP,3.3V,QUAD IO

SSDROM_MAC:BLANK

CRITICALU88001335S0966

IC,SPI SERIAL FLASH,64M BITS,1.8V,WLCSP

LABEL,BARCODE,2D,1D,CONFIG,MLB,X261

825-7995

LABEL

1

138S0941

ALL

Samsung alt to Murata

138S0789

TFT alt to Cyntec

ALL

107S0251107S0249

ALL

NDK alt to TXC

197S0588197S0591

197S0588

ALL

Epson alt to TXC

197S0590

333S0700

Hynix CAM DRAM alt to Elpida

ALL

333S0704

339S0243 339S0244

Elpida SSD DRAM alt to Hynix

ALL

128S0631

NEC alt to Sanyo

ALL

128S0351

335S0948 335S0966

Winbond alt to Macronix

ALL

128S00008

ALL

128S0380

NEC alt to Sanyo

ALL

Sanyo alt to NEC

311S0426

311S00007

311S0271

Samsung alt to Murata

ALL

311S00008

311S00018

311S0409

Diodes alt to NXP

ALL

740S00004

740S0134

ALL

Kemet alt to Sanyo

Polytronics alt to Wayon

740S00005

740S0190

ALL

ALL

Sanyo alt to NEC

128S0296 128S0487

128S0487

ROHM alt to NEC

ALL

128S00012

AOS alt to Vishay

ALL

376S00007

376S1179

Kemet alt to Sanyo

ALL

128S0469

128S00025

376S1080

Diodes alt to OnSemi

ALL

376S0820

376S1194

Vishay alt to OnSemi

376S00036

ALL

ALL

333S0704

333S00016

Elpida new die CAM DRAM alt

333S0704

ALL

333S00030

Hynix new die CAM DRAM alt

XDP_CONN,XDP,HPMBB:SSP0,HPMVBUS:VDET

MLB_DEBUG:ENG

ALL

2.4G turbo CPU alt to 2.0G

337S00054337S00061

CPU:0.8GHZ

376S00037

Vishay alt to OnSemi

376S1193

ALL

128S0469

ALL

128S0374

NEC alt to Sanyo

SSDRAM:A1_ELP

ALL

Hynix SSD DRAM alt to Elpida

685-00003685-00004

U5000 CRITICAL

341S00031

SMC:PROG1

IC,SMC-B1,EXTERNAL (VXXXX) PROTO2A, J92

U61001

BOOTROM_WIN:BLANK

CRITICAL335S1009

64 MBIT SPI QUAD I/O FLASH,CSP,3.3V,QUAD IO

SSDROM:PROG

341S00091

U8800 CRITICAL1

S1-X SSD BOOTROM, UI64

SSDROM_WIN:BLANK

CRITICALU88001335S0948

IC,SPI SERIAL FLASH,64M BITS,1.8V,WLBGA

CRITICALU6100

BOOTROM:PROG

1

341S00191

EFI ROM,MLB (VXXX) DVT,X261

U61001335S1029 CRITICAL

BOOTROM_MIC:BLANK

64 MBIT SPI QUAD I/O FLASH,CSP,3.3V,QUAD IO

HPM:PROGU4600 CRITICAL1

341S00190

IC,HPM (VXXX) DVT,X261

CAM_FREQ:24M,CAM_XTAL:NO,EDP,RSMRST:SMC,PGOOD8:SLP_S4,SSD_LPSR:S3

MLB_MISC

ALTERNATE,COMMON,CCSAK,MLB_MISC,MLB_DEBUG:ENG,MLB_PROGPARTS,EQ:4CH

MLB_COMMON

SYNC_DATE=10/24/2012

SYNC_MASTER=J43_MLB

BOM Configuration

<BRANCH>

<SCH_NUM>

<E4LABEL>

2 OF 130

2 OF 75

www.qdzbwx.com

Page 3

WWW.AliSaler.Com

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5

4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

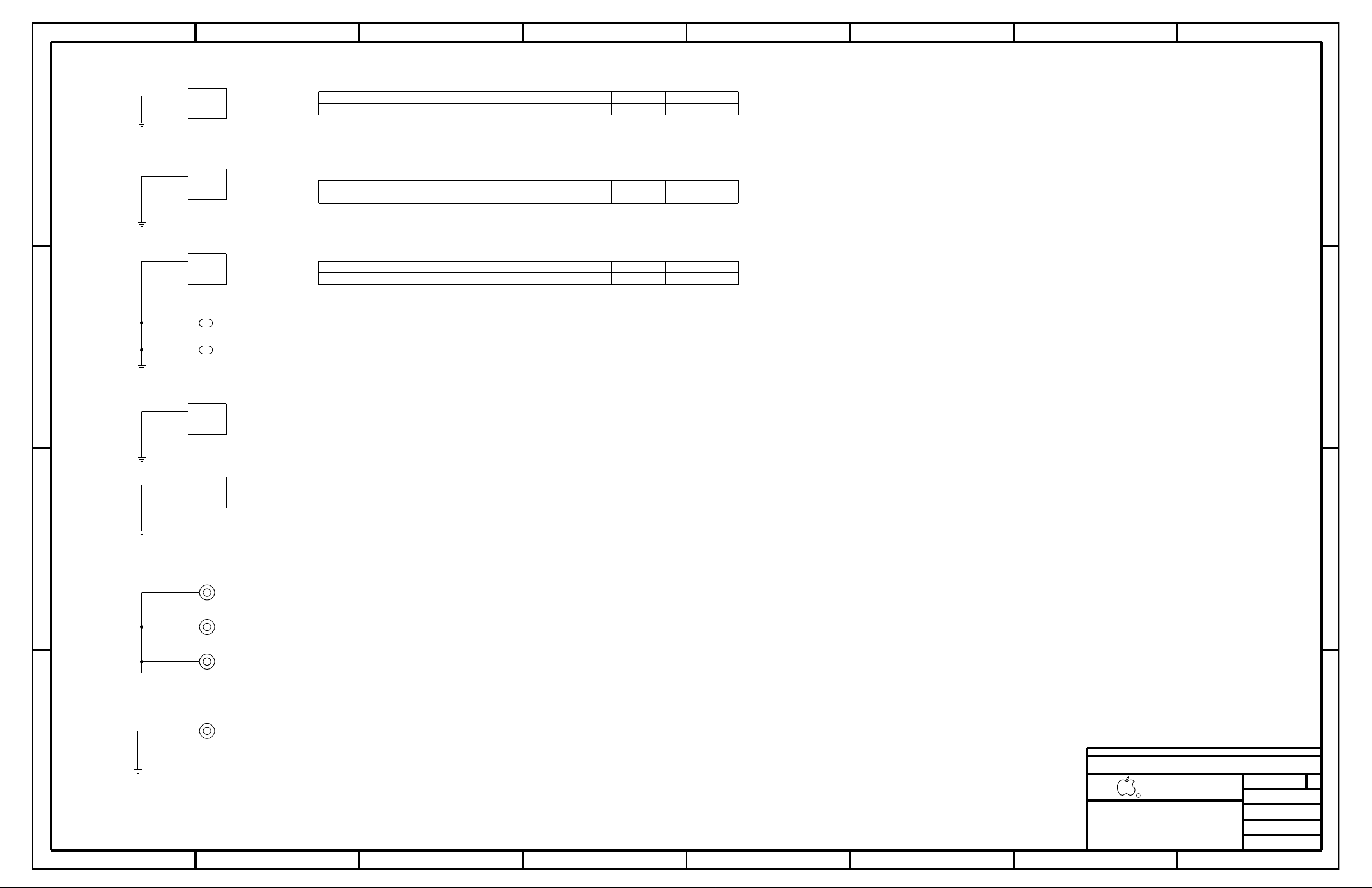

BOM OPTIONS

BOM NAME

BOM NUMBER

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

BOM OPTIONS

BOM NAME

BOM NUMBER

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

Partial & development BOMs

Common BOM

Top level BOM Variants

Programmable Parts

BOM Groups

ALTERNATE,CMN,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,NO CPU,EL 8GB,TOSH 256G,WIFI FCC,X261

939-00043

341S00198

WIFI ROM (PXXXX) DVT,WW2,X261

WIFI:ETSI

1 CRITICALU3580

BOOTROM:PROG,BT:PROG,SMC:PROG,SSDROM:PROG,HPM:PROG

MLB_PROGPARTS

341S00196

BT ROM (VXX) DVT,2MBIT,X261

CRITICALU35701 BT:PROG

341S00197

WIFI ROM (PXXXX) DVT,WW1,X261

WIFI:FCCU35801 CRITICAL

341S00199

WIFI ROM (PXXXX) DVT,WW3,X261

WIFI:APAC

U35801 CRITICAL

341S00200

WIFI ROM (PXXXX) DVT,IND,X261

WIFI:INDU35801 CRITICAL

685-00003

S1X:A2,S1X_DRAM:ELPIDA

POP,MLB,S1X-A2,ELP-4GBIT,X261

CMNPTS

CRITICAL

CMN1

685-00014

CMN PTS,PCBA,MLB-NEWARK,J92

685-00004

S1X:A2,S1X_DRAM:HYNIX

POP,MLB,S1X-A2,HYN-4GBIT,X261

685-00014

MLB_COMMON

CMN PTS,PCBA,MLB-NEWARK,J92

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,TOSH 256G,WIFI IND,J92

639-6614

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,TOSH 512G,WIFI IND,J92

639-6615

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,SAND 512G,WIFI IND,J92

639-6613

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,SAND 256G,WIFI IND,J92

639-6612

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,TOSH 512G,WIFI IND,J92

639-6611

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,TOSH 256G,WIFI IND,J92

639-6610

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,SAND 512G,WIFI IND,J92

639-6609

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,TOSH 512G,WIFI IND,J92

639-6607

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,TOSH 256G,WIFI IND,J92

639-6606

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,SAND 256G,WIFI IND,J92

639-6608

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,SAND 512G,WIFI IND,J92

639-6605

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,TOSH 512G,WIFI APAC,J92

639-6603

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:IND,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,SAND 256G,WIFI IND,J92

639-6604

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,TOSH 256G,WIFI APAC,J92

639-6602

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,SAND 512G,WIFI APAC,J92

639-6601

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,SAND 256G,WIFI APAC,J92

639-6600

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,TOSH 512G,WIFI APAC,J92

639-6599

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,SAND 512G,WIFI APAC,J92

639-6597

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,SAND 256G,WIFI APAC,J92

639-6596

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,TOSH 256G,WIFI APAC,J92

639-6598

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,TOSH 512G,WIFI APAC,J92

639-6595

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,TOSH 256G,WIFI APAC,J92

639-6594

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,SAND 512G,WIFI APAC,J92

639-6593

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:APAC,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,SAND 256G,WIFI APAC,J92

639-6592

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,TOSH 512G,WIFI ETSI,J92

639-6591

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,TOSH 256G,WIFI ETSI,J92

639-6590

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,SAND 512G,WIFI ETSI,J92

639-6589

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,SAND 256G,WIFI ETSI,J92

639-6588

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,TOSH 512G,WIFI ETSI,J92

639-6587

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,TOSH 256G,WIFI ETSI,J92

639-6586

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,SAND 512G,WIFI ETSI,J92

639-6585

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,SAND 256G,WIFI ETSI,J92

639-6584

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,TOSH 512G,WIFI ETSI,J92

639-6583

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,TOSH 256G,WIFI ETSI,J92

639-6582

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,TOSH 512G,WIFI FCC,J92

639-6579

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,SAND 512G,WIFI ETSI,J92

639-6581

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:ETSI,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,SAND 256G,WIFI ETSI,J92

639-6580

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,TOSH 256G,WIFI FCC,J92

639-6578

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,SAND 256G,WIFI FCC,J92

639-6576

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.3GHZ,EL 8GB,SAND 512G,WIFI FCC,J92

639-6577

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,TOSH 512G,WIFI FCC,J92

639-6575

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,SAND 512G,WIFI FCC,J92

639-6573

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,TOSH 256G,WIFI FCC,J92

639-6574

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.2GHZ,EL 8GB,SAND 256G,WIFI FCC,J92

639-6572

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:TOSH_512GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,TOSH 512G,WIFI FCC,J92

639-6571

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:SAND_512GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,SAND 512G,WIFI FCC,J92

639-6569

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:TOSH_256GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,TOSH 256G,WIFI FCC,J92

639-6570

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:ELP_8GB,NAND:SAND_256GB_1Y_128GBIT,WIFI:FCC,SSDRAM:A1_ELP

PCBA,MLB,1.1GHZ,EL 8GB,SAND 256G,WIFI FCC,J92

639-6568

SYNC_MASTER=J43_MLB

J92 BOM Variants

SYNC_DATE=10/24/2012

<BRANCH>

<SCH_NUM>

<E4LABEL>

3 OF 130

3 OF 75

Page 4

WWW.AliSaler.Com

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5

4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

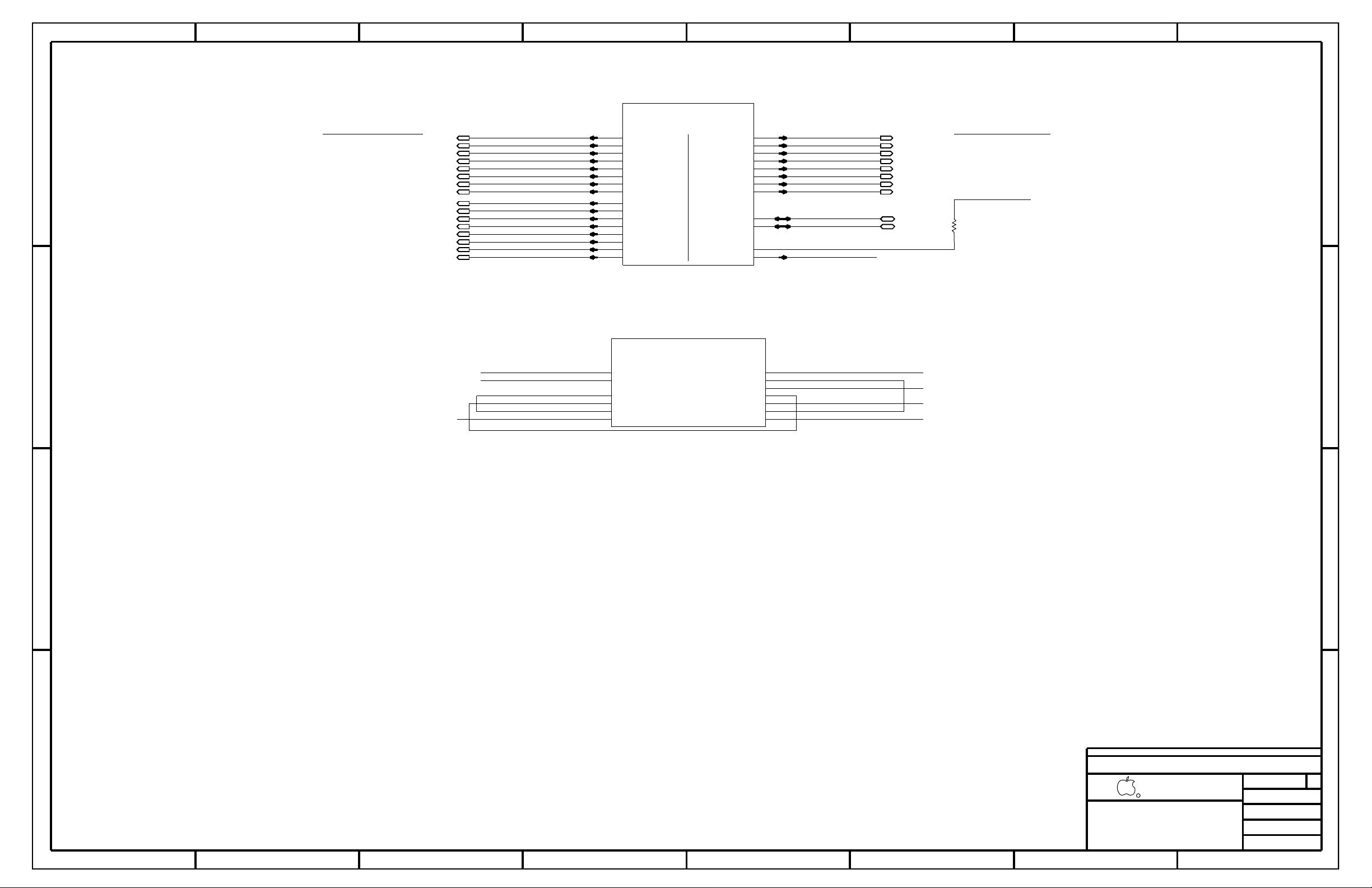

CPU EMI CAN

860-00060

SSD EMI FENCE & CAN

860-00889

860-00864

860-2930

WIFI EMI CAN

CPU Heat Spreader Bosses

DRAM EMI CAN & SLOTs

E85 BTB Connector Boss

4.5OD1.85ID-1.5H

Z0403

1

4.5OD1.85ID-1.5H

Z0404

1

4.5OD1.85ID-1.5H

Z0405

1

OMIT_TABLE

SM

SHLD-J92-EMI-CAN-WIFI

SH0400

1

OMIT_TABLE

SM

SHLD-J92-EMI-CAN-CPU

SH0401

1

OMIT_TABLE

SM

SHLD-CAN-EMI-DRAM-X261

SH0402

1

TH-NSP

SL-1.1X0.4-1.6X0.9-NSP

SL0400

1

TH-NSP

SL-1.1X0.4-1.6X0.9-NSP

SL0401

1

STDOFF-3.3X1.8R0.859H-SM

Z0406

1

SHLD-FENCE-SSD-TOP-X261

SM

SH0403

1

SHLD-CAN-EMI-SSD-BTM-X261

SM

SH0404

1

SH04001 CRITICAL806-7064

CAN,EMI,WIFI,X261

CRITICAL1

806-00400

CAN,EMI,DRAM,TALL,X261

SH0402

CRITICAL1 SH0401

CAN,EMI,CPU,X261

806-00112

PD PARTS

SYNC_DATE=10/24/2012

SYNC_MASTER=J43_MLB

<BRANCH>

<SCH_NUM>

<E4LABEL>

4 OF 130

4 OF 75

Page 5

WWW.AliSaler.Com

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

DDI1_TXN[0]

DDI1_TXN[1]

DDI1_TXN[2]

DDI1_TXN[3]

DDI1_TXP[0]

DDI1_TXP[1]

DDI1_TXP[2]

DDI1_TXP[3]

DDI2_TXN[0]

DDI2_TXN[1]

DDI2_TXN[2]

DDI2_TXN[3]

DDI2_TXP[0]

DDI2_TXP[1]

DDI2_TXP[2]

DDI2_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

EDP_RCOMP

EDP_TXN0

EDP_TXN1

EDP_TXN2

EDP_TXN3

EDP_TXP0

EDP_TXP1

EDP_TXP2

EDP_TXP3

DDI

(1 OF 20)

EDP

(18 OF 20)

DAISY_CHAIN_NCTF_A44

DAISY_CHAIN_NCTF_C43

DAISY_CHAIN_NCTF_C45

DAISY_CHAIN_NCTF_D2

DAISY_CHAIN_NCTF_D44

DAISY_CHAIN_NCTF_F1

DAISY_CHAIN_NCTF_F3

DAISY_CHAIN_NCTF_F43

DAISY_CHAIN_NCTF_F45

DAISY_CHAIN_NCTF_H2

DAISY_CHAIN_NCTF_H44

RSVD_CB11

RSVD_H15

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5

4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

(MUXed with HDMI

NO_TEST

Internal panel

eDP Port Assignment:

TBT Sink 0

TBT Sink 1

if necessary)

DDI Port Assignments:

NO_TEST

exist between both TP’s on each corner.

Other corner test signals connected in

Each corner of CPU has two testpoints.

MCP Daisy-Chain Strategy:

daisy-chain fashion. Continuity should

63

63

53 66

53 66

53

66

53 66

53 66

53 66

53 66

53 66

53 66

53 66

BGA

OMIT_TABLE

CRITICAL

BROADWELL-MOBILE-Y-B

U0500

AD25

AD26

AG25

AG26

AC25

AC26

AE25

AE26

AD22

AG22

AD21

AG21

AC22

AE22

AC21

AE21

AG16

AE17

Y21

AP41

AD17

AG18

AD18

AA17

AC17

AE18

AC18

W17

BROADWELL-MOBILE-Y-B

BGA

CRITICAL

OMIT_TABLE

U0500

A44

C43

C45

D2

D44

F1

F3

F43

F45

H2

H44

CB11

H15

1/20W

MF

1%

24.9

201

R0530

1

2

29 68

29 68

29

68

29 68

29 68

29 68

29 68

29 68

63

63

63

63

63

63

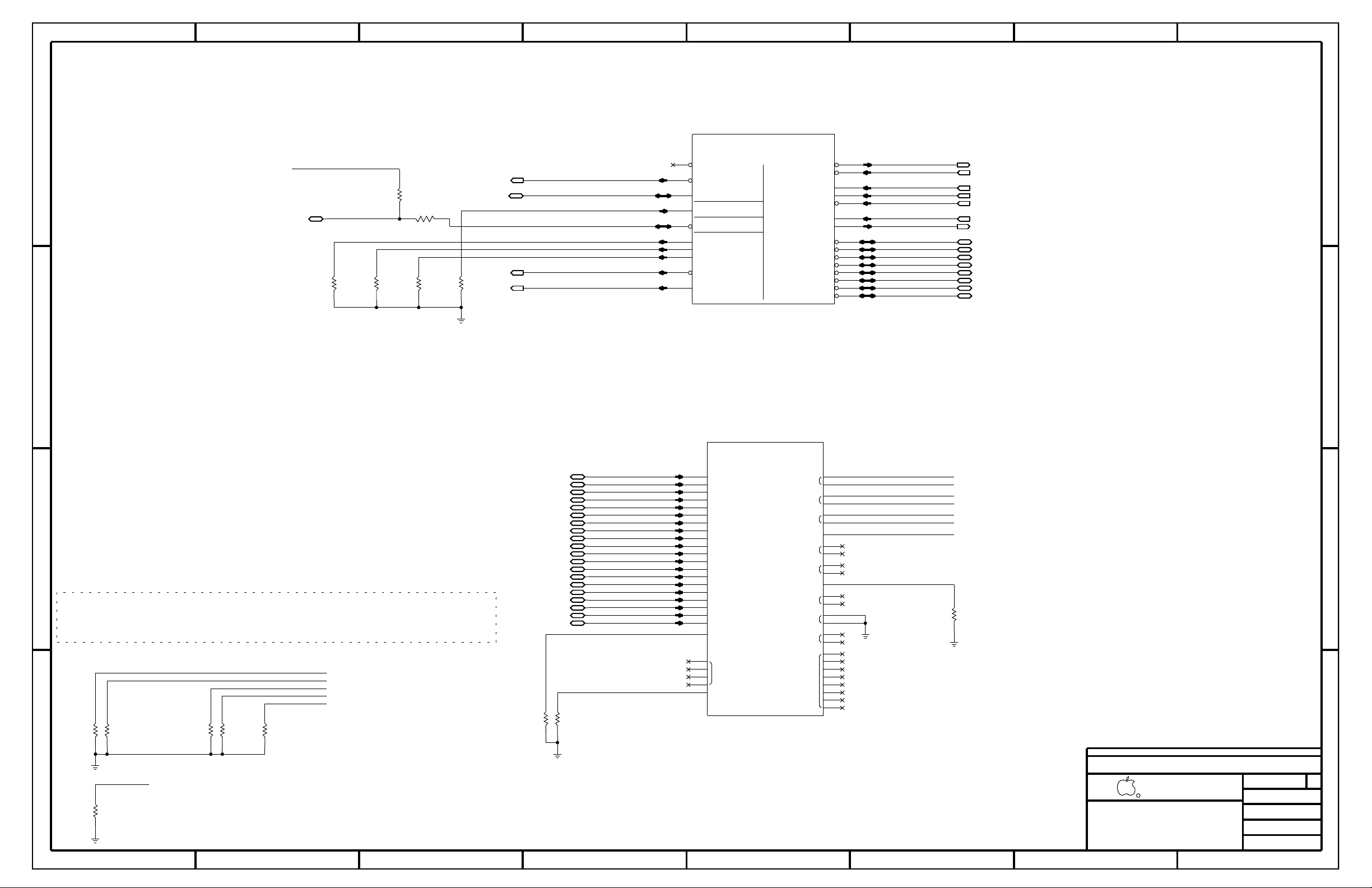

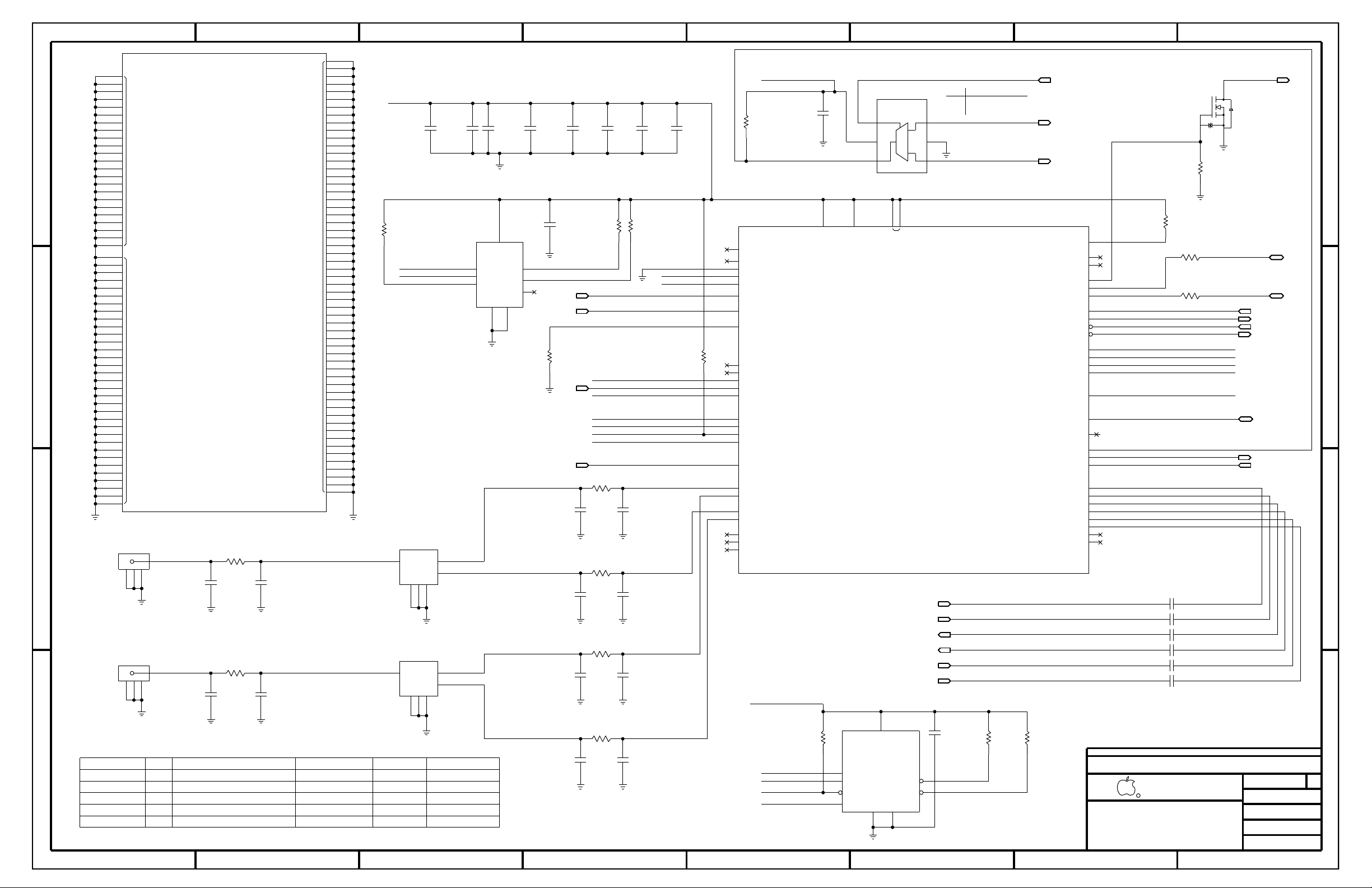

CPU GFX/DC_TEST

SYNC_DATE=04/10/2013SYNC_MASTER=J92_WILL

TP_MCP_DC_A44

TP_MCP_DC_H44

TP_ULX_SPARE1

DP_TBTSNK0_ML_C_N<1>

DP_TBTSNK0_ML_C_P<0>

TP_ULX_SSP_SPARE

DP_INT_ML_C_P<3>

DP_INT_ML_C_P<2>

DP_INT_ML_C_P<1>

DP_INT_ML_C_P<0>

DP_INT_ML_C_N<3>

DP_INT_ML_C_N<2>

DP_INT_ML_C_N<1>

DP_INT_ML_C_N<0>

MCP_EDP_RCOMP

TP_EDP_DISP_UTIL

DP_INT_AUXCH_C_P

DP_INT_AUXCH_C_N

NC_DP_TBTSNK1_ML_CP<3>

NC_DP_TBTSNK1_ML_CP<2>

NC_DP_TBTSNK1_ML_CP<1>

NC_DP_TBTSNK1_ML_CP<0>

NC_DP_TBTSNK1_ML_CN<3>

NC_DP_TBTSNK1_ML_CN<2>

NC_DP_TBTSNK1_ML_CN<1>

NC_DP_TBTSNK1_ML_CN<0>

DP_TBTSNK0_ML_C_P<3>

DP_TBTSNK0_ML_C_P<2>

DP_TBTSNK0_ML_C_P<1>

DP_TBTSNK0_ML_C_N<3>

DP_TBTSNK0_ML_C_N<2>

DP_TBTSNK0_ML_C_N<0>

PPVCOMP_S0_CPU

TRUE

MCP_DC_H2_F3

TRUE

MCP_DC_F43_F45

TP_MCP_DC_F1

TP_MCP_DC_D2

TP_MCP_DC_C45

MCP_DC_C43_D44

TRUE

<BRANCH>

<SCH_NUM>

5 OF 130

5 OF 75

<E4LABEL>

62

62

8

Page 6

WWW.AliSaler.Com

(2 OF 20)

MISC

JTAG

THERMAL

PWR

DDR3

PROC_TRST*

PROC_TDO

PROC_TDI

PROC_TCK

PROCPWRGD

PROCHOT*

PREQ*

PRDY*

PECI

BPM7*

BPM6*

BPM5*

BPM4*

BPM3*

BPM2*

BPM1*

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

PROC_TMS

BPM0*

CATERR*

PROC_DETECT*

SM_PG_CNTL1

SM_DRAMRST*

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

BI

BI

OUT

NC

BI

BI

BI

BI

BI

BI

BI

BI

OUT

IN

IN

IN

IN

IN

OUT

OUT

OUT

CFG[9]

CFG[8]

CFG[7]

CFG[5]

CFG[4]

CFG[3]

VSS

TD_IREF

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

PROC_OPI_RCOMP

CFG[19]

CFG[15]

CFG[14]

CFG[13]

CFG[12]

CFG[10]

CFG[6]

CFG[16]

CFG[17]

CFG[18]

CFG[11]

CFG[0]

CFG[1]

CFG[2]

CFG_RCOMP

(19 OF 20)

RESERVED

NC

NC

NC

NC

NC

NC

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5

4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

These can be placed close to J1800

CFG<4> :eDP ENABLE/DISABLE 1 = DISABLED 0 = ENABLED

TBD: Confirm w/ Intel which still apply for BDW-Y

and are only for debug access

CFG<0> :RESET SEQUENCE STALL 1 = NORMAL OPERATION 0 = STALL AFTER PCU PLL LOCK

CFG<10>:SAFE MODE BOOT 1 = NORMAL OPERATION 0 = POWER FEATURES NOT ACTIVE

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPD)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

CFG<9> :NO SVID-CAPABLE VR 1 = VR SUPPORTS SVID 0 = VR DOES NOT SUPPORT SVID

CFG<1> :PCH-LESS MODE 1 = NORMAL OPERATION 0 = PCH-LESS MODE

CFG<8> :ALLOW NOA ON LOCKED UNITS 1 = NORMAL OPERATION 0 = NOA ALWAYS UNLOCKED

.

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

CRITICAL

OMIT_TABLE

BROADWELL-MOBILE-Y-B

BGA

U0500

CM39

CN38

CK36

CM37

CN36

CR35

CN34

CR34

CH39

CK42

CU40

CR41

CF41

CM41

CU36

CU38

CN40

CR39

CH41

CG42

AB2

BL14

CV7

CP7

CT7

NOSTUFF

1K

5%

201

1/20W

MF

R0640

1

2

NOSTUFF

1K

5%

201

1/20W

MF

R0639

1

2

NOSTUFF

MF

1/20W

201

5%

1K

R0638

1

2

MF

1/20W

201

5%

1K

NOSTUFF

R0631

1

2

NOSTUFF

1K

5%

201

1/20W

MF

R0630

1

2

6

16 66

6

16 66

16 66

16

66

16 66

6

16 66

16 66

16

66

6

16 66

6

16 66

16 66

6

16 66

16 66

16

66

16 66

16 66

16 66

16 66

16 66

16 66

MF

1/20W

49.9

201

1%

R0681

1

2

31 32 44

66

62

5%

1/20W

MF

201

R0610

1

2

201

5%

MF

56

1/20W

R0611

12

32 66

31 64

66

PLACE_NEAR=U0500.CG42:12.7mm

10K

5%

1/20W

MF

201

R0620

1

2

16 66

16 66

16

66

16 66

16 66

16 66

16 66

16 66

16 66

16 66

12 16 66

16 66

16 66

16 66

16 66

PLACE_NEAR=U0500.CT7:12.7mm

100

1%

201

1/20W

MF

R0652

1

2

PLACE_NEAR=U0500.CP7:12.7mm

121

1%

201

1/20W

MF

R0651

1

2

PLACE_NEAR=U0500.CV7:12.7mm

MF

1/20W

201

200

1%

R0650

1

2

18

61

1%

49.9

1/20W

201

MF

R0680

1

2

OMIT_TABLE

BROADWELL-MOBILE-Y-B

CRITICAL

BGA

U0500

CV27

CT27

CP31

CN32

CV33

CU34

CT33

CP33

CR28

CN28

CR32

CU32

CP27

CU28

CV29

CT29

CM29

CU30

CN30

CV31

CR30

AB6

AJ22

AJ34

AK25

AL20

AL24

AP3

BJ40

BJ42

BT41

BT43

CK6

CL28

CL34

CL8

N18

P33

AA18

AL32

AL34

BJ14

BT15

CK13

Y18

W21

W33

Y33

Y34L40

AL26

AL28

1%

1/20W

201

MF

8.2K

R0685

1

2

1K

5%

201

1/20W

MF

EDP

R0634

1

2

SYNC_DATE=04/10/2013SYNC_MASTER=J92_WILL

CPU Misc/JTAG/CFG/RSVD

CPU_SM_RCOMP<0>

CPU_PWRGD

CPU_PROCHOT_R_L

CPU_SM_RCOMP<1>

CPU_SM_RCOMP<2>

CPU_CFG<1>

CPU_CFG<8>

CPU_CFG<10>

CPU_CFG<0>

CPU_CFG<4>

CPU_CFG_RCOMP

CPU_CFG<1>

CPU_CFG<0>

CPU_CFG<11>

CPU_CFG<18>

CPU_CFG<17>

CPU_CFG<16>

CPU_CFG<6>

CPU_CFG<10>

CPU_CFG<12>

CPU_CFG<13>

CPU_CFG<14>

CPU_CFG<15>

CPU_CFG<19>

CPU_CFG<4>

CPU_CFG<5>

CPU_CFG<7>

CPU_CFG<9>

PP1V05_S0

XDP_CPUPCH_TRST_L

XDP_CPU_TDO

XDP_CPU_TDI

XDP_CPU_TCK

XDP_CPU_PREQ_L

XDP_CPU_PRDY_L

XDP_BPM_L<7>

XDP_BPM_L<6>

XDP_BPM_L<5>

XDP_BPM_L<4>

XDP_BPM_L<3>

XDP_BPM_L<2>

XDP_BPM_L<1>

XDP_CPU_TMS

XDP_BPM_L<0>

CPU_PECI

CPU_CATERR_L

CPU_PROCHOT_L

TP_CPU_MEMVTT_PWR_EN_LSVDDQ

TP_CPU_MEM_RESET_L

TP_MCP_RSVD_Y18

TP_MCP_RSVD_AL32

TP_MCP_RSVD_BJ14

TP_MCP_RSVD_BT15

TP_MCP_RSVD_AA18

TP_MCP_RSVD_AL34

CPU_CFG<3>

MCP_RSVD_CK13

PCH_TD_IREF

CPU_OPI_RCOMP

CPU_CFG<8>

CPU_CFG<2>

CPU_CFG<9>

6 OF 75

6 OF 130

<E4LABEL>

<SCH_NUM>

<BRANCH>

66

66

66

66

6

16 66

6

16 66

6

16 66

6

16 66

6

16 66

8

11 15 16

17 32 44 46 51 60

64

6

16 66

Page 7

WWW.AliSaler.Com

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

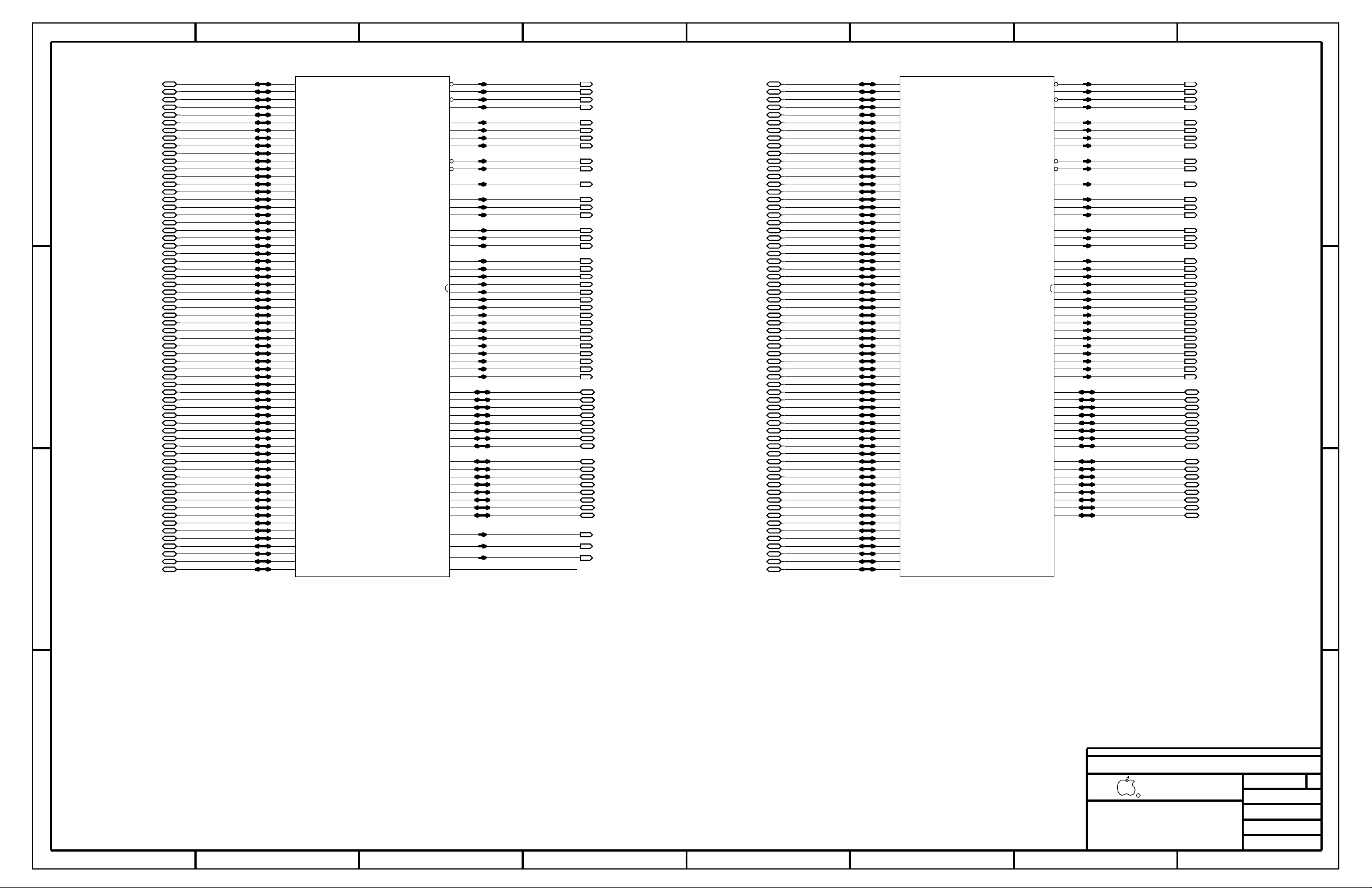

(3 OF 20)

MEMORY CHANNEL A

SA_CAA5

SA_CAA0

NOTUSED

SA_CAB5

SA_CAB8

SA_CAB9

SA_DQSN1

SA_DQSN0

SA_DQ5

SA_DQ6

SA_CAB3

SA_DQ9

SM_VREF_DQ1

SM_VCCDDQG

SA_ODT0

SA_CAB0

SA_CAA6

SA_CAA7

SA_CAA1

SA_DQSP7

SA_DQSP6

SA_DQSP5

SA_DQSP4

SA_DQSP3

SA_DQSP2

SA_DQSP1

SA_DQSP0

SA_DQSN7

SA_DQSN6

SA_DQSN5

SA_DQSN4

SA_DQSN3

SA_DQSN2

SA_DQ63

SA_DQ62

SA_DQ61

SA_DQ60

SA_DQ59

SA_DQ58

SA_DQ57

SA_DQ56

SA_DQ55

SA_DQ54

SA_DQ53

SA_DQ52

SA_DQ51

SA_DQ50

SA_DQ49

SA_DQ48

SA_DQ47

SA_DQ46

SA_DQ45

SA_DQ44

SA_DQ43

SA_DQ42

SA_DQ41

SA_DQ40

SA_DQ39

SA_DQ38

SA_DQ37

SA_DQ36

SA_DQ35

SA_DQ34

SA_DQ33

SA_DQ32

SA_DQ31

SA_DQ30

SA_DQ29

SA_DQ28

SA_DQ27

SA_DQ26

SA_DQ25

SA_DQ24

SA_DQ23

SA_DQ22

SA_DQ21

SA_DQ18

SA_DQ17

SA_DQ16

SA_DQ8

SA_DQ7

SA_CS1*

SA_CS0*

SA_CLK1

SA_CKE1

SA_CAA9

SA_CAB6

SA_CAA8

SA_DQ20

SA_DQ19 SA_CAB4

SM_VREF_DQ0

SM_VREF_CA

SA_CKE3

SA_CKE2

SA_CKE0

SA_CLK1*

SA_CAB2

SA_CAB7

SA_CAB1

SA_CLK0

SA_CLK0*

SA_DQ1

SA_DQ4

SA_DQ3

SA_DQ2

SA_DQ0

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_CAA3

SA_CAA4

SA_CAA2

(4 OF 20)

MEMORY CHANNEL B

SB_CAA2

SB_CAB5

SB_CAB7

SB_CAA1

SB_CAA3

SB_CAA4

SB_CAB1

SB_CAB2

SB_DQ2

SB_DQ1

SB_ODT0

SB_CAB0

SB_CAA6

SB_CAA7

SB_CAB8

SB_CAB9

SB_DQSP7

SB_DQSP6

SB_DQSP5

SB_DQSP4

SB_DQSP3

SB_DQSP2

SB_DQSP1

SB_DQSP0

SB_DQSN7

SB_DQSN6

SB_DQSN5

SB_DQSN4

SB_DQSN3

SB_DQSN2

SB_DQSN1

SB_DQSN0

SB_DQ63

SB_DQ62

SB_DQ61

SB_DQ60

SB_DQ59

SB_DQ58

SB_DQ57

SB_DQ56

SB_DQ55

SB_DQ54

SB_DQ53

SB_DQ52

SB_DQ51

SB_DQ50

SB_DQ49

SB_DQ48

SB_DQ47

SB_DQ46

SB_DQ45

SB_DQ44

SB_DQ43

SB_DQ42

SB_DQ41

SB_DQ40

SB_DQ39

SB_DQ38

SB_DQ37

SB_DQ36

SB_DQ35

SB_DQ34

SB_DQ33

SB_DQ32

SB_DQ31

SB_DQ28

SB_DQ27

SB_DQ26

SB_DQ25

SB_DQ24

SB_DQ21

SB_DQ20

SB_DQ19

SB_DQ18

SB_DQ17

SB_DQ15

SB_DQ14

SB_DQ13

SB_DQ12

SB_DQ11

SB_DQ10

SB_DQ9

SB_DQ8

SB_DQ4

SB_CS1*

SB_CS0*

SB_CK1*

SB_CK1

SB_CK0*

SB_CK0

SB_CAA9

SB_CAA5

SB_CAB6

SB_CAB4

SB_CAA8

SB_CKE3

SB_CKE2

SB_DQ16

SB_DQ30

SB_DQ29

SB_CKE0

SB_CKE1

SB_CAB3

SB_DQ6

SB_DQ22

SB_DQ23

SB_DQ3

SB_DQ0

SB_DQ5

SB_DQ7

SB_CAA0

NOTUSED

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5

4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

61 69

61 69

61

69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

20 61 69

61 69

61 69

61 69

61 69

61 69

61

61

20 61 69

20 69

20 69

20 69

20 69

20 69

20 69

20 69

20 69

61

20 61 69

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

20 61 69

61

61 69

61 69

61 69

61 69

61 69

20 61 69

61 69

61 69

20 69

20 69

21 64 69

21 64 69

21 69

21 69

21 69

21 64 69

21 69

21 69

21 64 69

21 64 69

21 61 69

61

61

61

61

21 61 69

61

61

61

61

61

61

61

61

61

61

61

61

61

21 61 69

61

61

61

61 64 69

61 69

61 69

61 69

61 69

61 69

21 61 69

61 69

61 69

61 64 69

61 69

61 69

61 69

21 61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

BROADWELL-MOBILE-Y-B

CRITICAL

OMIT_TABLE

BGA

U0500

CE10

CG8

CG6

CC12

CH3

CB9

CE6

CF11

CH5

CG12

CG10

CF9

CB3

CC8

CE4

CE2

CB5

CF5

CC2

CF3

CE12

CE8

CH11

CH9

CA12

CA10

CG2

CG4

CC6

CC4

CA4

CA2

CT17

CV17

CP10

CM10

CN12

CV13

CV10

CT10

CT25

CP25

CN22

CP23

CN14

CN24

CV25

CV23

CT23

CN20

CN18

CT21

CT19

CP19

CP21

CP15

CV19

CV21

BU2

BW2

BW6

BU4

BW4

BT3

BU6

BT5

CN16

BN2

BR2

BN6

BN4

BR6

BR4

BM5

BM3

BT11

BU10

CR16

BW12

BW10

BW8

BU8

BU12

BT9

BN8

BR8

BN12

BN10

CM13

BR12

BR10

BM11

BM9

CV15

CT13

CP13

CU16

CR12

CR24

CR20

BV3

BP3

BV9

BP9

CT15

CU12

CU24

CU20

BV5

BP5

BV11

BP11

CA6

CC14

AP13

AU14

AT13

BGA

BROADWELL-MOBILE-Y-B

OMIT_TABLE

CRITICAL

U0500

AR6

AT5

AT3

AY5

BA8

AW2

AY3

AU2

AU6

AU4

AR2

BA6

AW8

AW10

AW12

BA10

AY11

AU8

BA12

AY9

AR4

AT9

AW4

AW6

AP9

AP11

BA2

BA4

AR8

AP5

AR10

AT11

BK3

BK5

BC6

BE2

BE4

BE6

BC2

BC4

BE10

BC10

BE8

BC8

BG6

BF11

BC12

BE12

BF9

BJ12

BG12

BJ8

BJ10

BG8

BG10

BJ2

BK9

BK11

AM1

AH2

AJ3

AM5

AM3

AJ1

AJ5

AH4

BJ4

AG3

AG1

AD2

AE3

AE1

AG5

AD4

AE5

AM9

AM7

BJ6

AH8

AJ9

AM11

AJ7

AJ11

AH10

AE11

AG7

AE7

AE9

BG2

AG11

AG9

AD8

AD10

BG4

BF3

BF5

BH5

BD5

BD11

BH11

AK2

AF2

AK8

AF8

BH3

BD3

BD9

BH9

AK4

AF4

AK10

AF10

AU10

19

19

19

61 64 69

61

69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

20 61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

21 61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

61 69

SYNC_DATE=07/17/2013

SYNC_MASTER=J92_LS_MLB

CPU DDR3/LPDDR3 Interfaces

MEM_A_DQ<10>

MEM_A_DQ<11>

MEM_A_DQ<12>

MEM_A_DQ<15>

MEM_A_CAB<6>

MEM_B_DQ<6>

MEM_A_DQS_N<4>

MEM_A_DQS_P<6>

MEM_B_DQ<38>

MEM_B_DQ<39>

=MEM_A_BA<0>

MEM_B_DQ<40>

MEM_B_DQ<44>

MEM_B_DQ<36>

MEM_B_DQ<37>

MEM_A_CKE<1>

=MEM_B_A<8>

MEM_A_CLK_P<0>

MEM_B_DQ<10>

MEM_B_DQ<14>

MEM_B_DQ<12>

=MEM_A_A<5>

TP_LPDDR3_RSVD1

TP_LPDDR3_RSVD2

=MEM_A_A<2>

=MEM_A_A<1>

=MEM_A_A<0>

MEM_A_DQS_N<1>

MEM_A_DQS_N<0>

MEM_A_DQ<5>

MEM_A_DQ<6>

=MEM_A_RAS_L

MEM_A_DQ<9>

CPU_DIMMB_VREFDQ

TP_ULX_DDR_VCCDDQG

MEM_A_ODT<0>

=MEM_A_A<13>

MEM_A_CAA<6>

=MEM_A_A<11>

=MEM_A_A<9>

MEM_A_DQS_P<7>

MEM_A_DQS_P<5>

MEM_A_DQS_P<4>

MEM_A_DQS_P<3>

MEM_A_DQS_P<2>

MEM_A_DQS_P<1>

MEM_A_DQS_P<0>

MEM_A_DQS_N<7>

MEM_A_DQS_N<6>

MEM_A_DQS_N<5>

MEM_A_DQS_N<3>

MEM_A_DQS_N<2>

MEM_A_DQ<18>

MEM_A_DQ<17>

MEM_A_DQ<16>

MEM_A_DQ<8>

MEM_A_DQ<7>

MEM_A_CS_L<1>

MEM_A_CS_L<0>

MEM_A_CLK_P<1>

=MEM_A_A<14>

=MEM_A_A<15>

MEM_A_DQ<19>

CPU_DIMMA_VREFDQ

CPU_DIMM_VREFCA

MEM_A_CKE<3>

MEM_A_CKE<2>

MEM_A_CKE<0>

MEM_A_CLK_N<1>

=MEM_A_WE_L

=MEM_A_A<10>

=MEM_A_CAS_L

MEM_A_CLK_N<0>

MEM_A_DQ<1>

MEM_A_DQ<4>

MEM_A_DQ<3>

MEM_A_DQ<2>

MEM_A_DQ<0>

MEM_A_DQ<13>

MEM_A_DQ<14>

=MEM_A_A<8>

=MEM_A_A<7>

=MEM_A_A<6>

MEM_A_DQ<20>

MEM_A_DQ<21>

MEM_A_DQ<22>

MEM_A_DQ<23>

MEM_A_DQ<24>

MEM_A_DQ<25>

MEM_A_DQ<26>

MEM_A_DQ<27>

MEM_A_DQ<28>

MEM_A_DQ<29>

MEM_A_DQ<30>

MEM_A_DQ<31>

MEM_A_DQ<32>

MEM_A_DQ<33>

MEM_A_DQ<34>

MEM_A_DQ<35>

MEM_A_DQ<36>

MEM_A_DQ<37>

MEM_A_DQ<38>

MEM_A_DQ<39>

MEM_A_DQ<40>

MEM_A_DQ<41>

MEM_A_DQ<42>

MEM_A_DQ<43>

MEM_A_DQ<44>

MEM_A_DQ<45>

MEM_A_DQ<46>

MEM_A_DQ<47>

MEM_A_DQ<48>

MEM_A_DQ<49>

MEM_A_DQ<50>

MEM_A_DQ<51>

MEM_A_DQ<52>

MEM_A_DQ<53>

MEM_A_DQ<54>

MEM_A_DQ<55>

MEM_A_DQ<56>

MEM_A_DQ<57>

MEM_A_DQ<58>

MEM_A_DQ<59>

MEM_A_DQ<60>

MEM_A_DQ<61>

MEM_A_DQ<62>

MEM_A_DQ<63>

=MEM_B_A<6>

=MEM_B_A<2>

=MEM_B_A<10>

=MEM_B_A<9>

=MEM_B_CAS_L

=MEM_B_WE_L

MEM_B_DQ<1>

MEM_B_ODT<0>

=MEM_B_A<13>

MEM_B_CAA<6>

=MEM_B_A<11>

=MEM_B_A<1>

=MEM_B_A<0>

MEM_B_DQS_P<7>

MEM_B_DQS_P<6>

MEM_B_DQS_P<5>

MEM_B_DQS_P<4>

MEM_B_DQS_P<3>

MEM_B_DQS_P<2>

MEM_B_DQS_P<1>

MEM_B_DQS_P<0>

MEM_B_DQS_N<7>

MEM_B_DQS_N<6>

MEM_B_DQS_N<5>

MEM_B_DQS_N<4>

MEM_B_DQS_N<3>

MEM_B_DQS_N<2>

MEM_B_DQS_N<1>

MEM_B_DQS_N<0>

MEM_B_DQ<9>

MEM_B_CS_L<1>

MEM_B_CS_L<0>

MEM_B_CLK_N<1>

MEM_B_CLK_P<1>

MEM_B_CLK_N<0>

MEM_B_CLK_P<0>

=MEM_B_A<14>

=MEM_B_BA<2>

MEM_B_CAB<6>

=MEM_B_BA<0>

=MEM_B_A<15>

MEM_B_CKE<3>

MEM_B_CKE<2>

MEM_B_CKE<0>

=MEM_B_RAS_L

MEM_B_DQ<3>

MEM_B_DQ<0>

MEM_B_DQ<7>

=MEM_B_A<5>

TP_LPDDR3_RSVD4

TP_LPDDR3_RSVD3

MEM_B_DQ<24>

MEM_B_DQ<23>

MEM_B_DQ<22>

MEM_B_DQ<25>

MEM_B_DQ<30>

MEM_B_DQ<29>

MEM_B_DQ<28>

MEM_B_DQ<27>

MEM_B_DQ<26>

MEM_B_DQ<35>

MEM_B_DQ<34>

MEM_B_DQ<33>

MEM_B_DQ<32>

MEM_B_DQ<31>

MEM_B_DQ<45>

MEM_B_DQ<41>

MEM_B_DQ<47>

MEM_B_DQ<46>

MEM_B_DQ<63>

MEM_B_DQ<62>

MEM_B_DQ<61>

MEM_B_DQ<60>

MEM_B_DQ<59>

MEM_B_DQ<58>

MEM_B_DQ<57>

MEM_B_DQ<56>

MEM_B_DQ<55>

MEM_B_DQ<54>

MEM_B_DQ<53>

MEM_B_DQ<52>

MEM_B_DQ<51>

MEM_B_DQ<50>

MEM_B_CKE<1>

MEM_B_DQ<18>

MEM_B_DQ<15>

=MEM_A_BA<2>

MEM_B_DQ<13>

MEM_B_DQ<11>

MEM_B_DQ<8>

=MEM_B_A<7>

MEM_B_DQ<21>

MEM_B_DQ<20>

MEM_B_DQ<19>

MEM_B_DQ<2>

MEM_B_DQ<4>

MEM_B_DQ<5>

MEM_B_DQ<17>

MEM_B_DQ<16>

MEM_B_DQ<43>

MEM_B_DQ<42>

MEM_B_DQ<49>

MEM_B_DQ<48>

<BRANCH>

<SCH_NUM>

<E4LABEL>

7 OF 130

7 OF 75

64

Page 8

WWW.AliSaler.Com

OUT

IN

OUT

IN

OUT

BI

DCPSUS4

VCCOPIPLL

VCCHDAPLL

DCPSUS3

DCPRTC

VCC1_05

VCCUSB2PLL

VCCTS1_5

VCCSUS3_3_RTC

VCCSUS3_3

VCCSPI

VCCSDIO

VCCRTC

VCCHDA

VCCCLK7

VCCCLK5

VCCCLK3

VCCCLK2

VCCCLK1

VCC3_3

VCC1_05_USB

DCPSUSBYP

DCPSUS1

VCCACLKPLL

VCCCLK4

VCCTS3_3

VCCASW

VCCASW

DCPSUS2

VCCDSW3_3

VCCUSB3PHY

VCCUSB3PLL

VCCSUS3_3

VCCCLK6

VCCSATA3PLL

VCC1_05_PHY

VCCPCIEPHY

VCCSATAPHY

OPIICC

USB2

GPIO/LCC USB3MISC

CORE

RTC

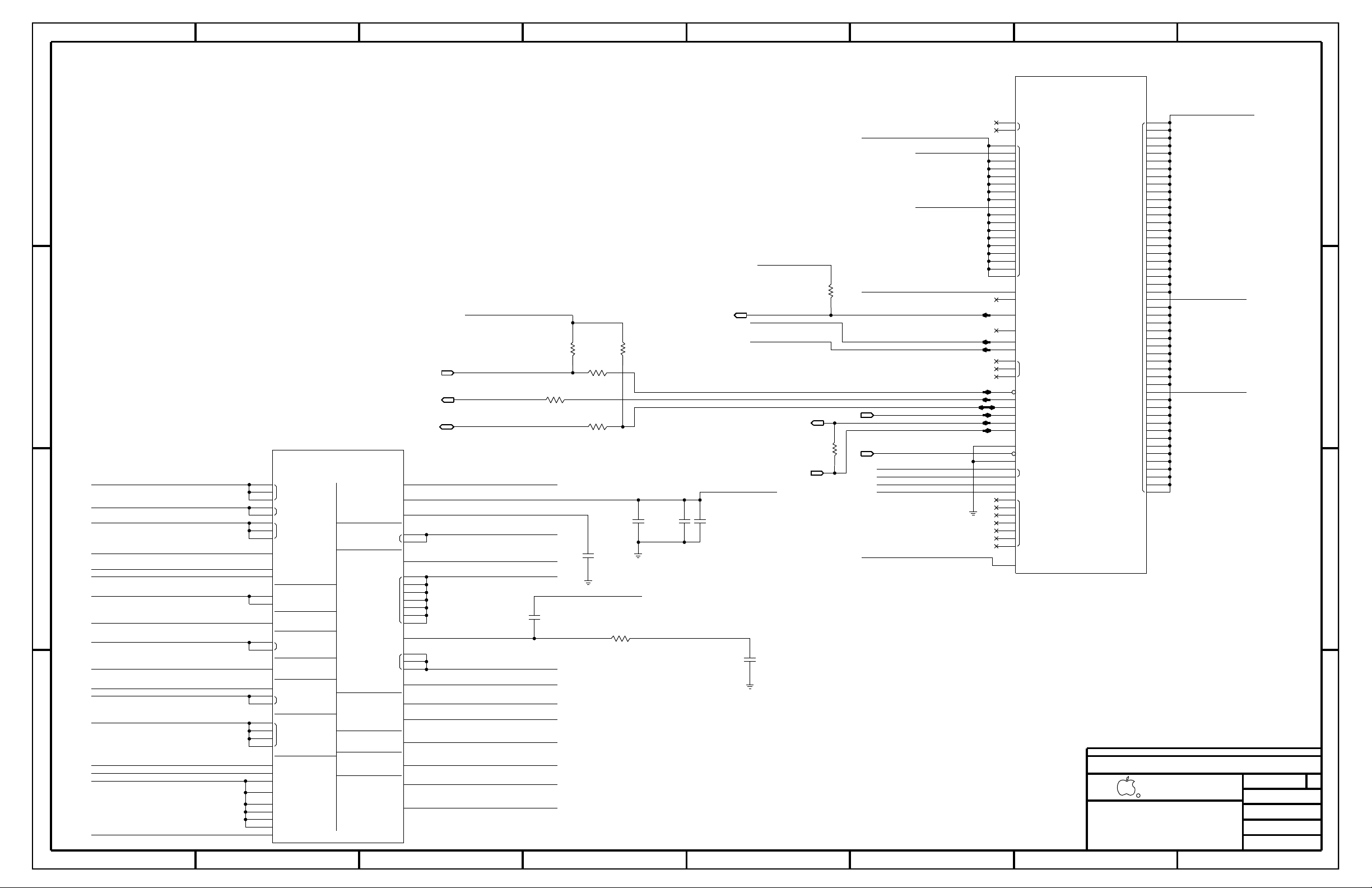

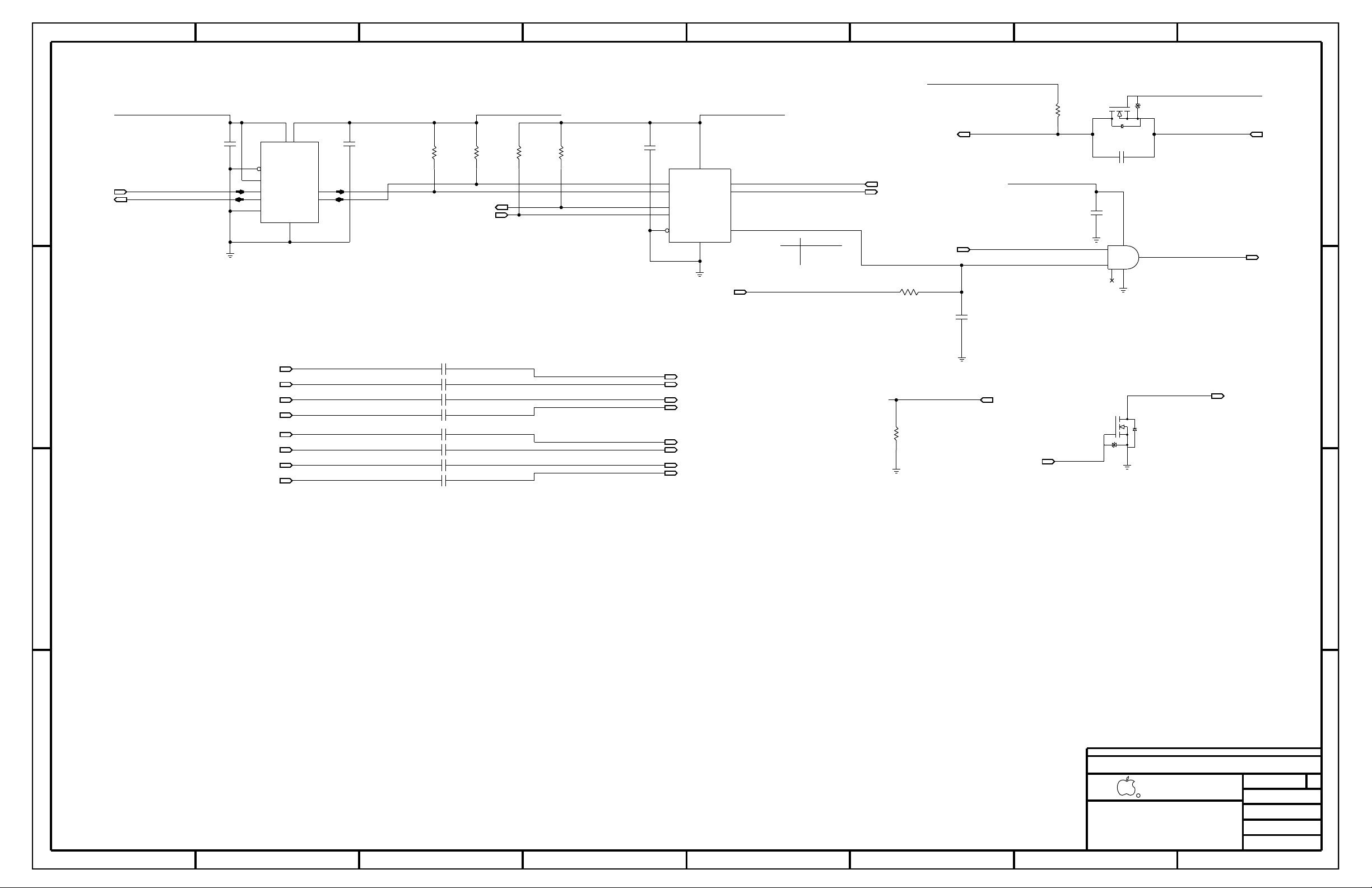

(13 OF 20)

SERIAL IO

SPI

HSIO

AZALIA/HDA

VRM/USB2/AZALIA

WPT LP POWER

SUS OSCILLATOR

THERMAL SENSOR

BRW ULX POWER

(12 OF 20)

RSVD

VCC

RSVD

VSS

IST_TRIGGER

RSVD

VCCST

VCC

VDDQ

VIDSCLK

VR_EN

VR_READY

RSVD

VIDALERT*

VIDSOUT

VCCST_PWRGD

IVR_ERROR

RSVD_TP

PWR_DEBUG*

VSS

VCC_SENSE

VCCIO_OUT

RSVD

VCOMP_OUT

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

IN

IN

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5

4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

LPT-LP current estimates from Lynx Point-LP PCH EDS, doc #503118, v1.0.

Max load: 300mA

???mA Max

R0800.2:

R0810.2:

R0802.2:

Max load: 300mA

32A Max

1.1A Max (LPDDR3: 1.2V)

1.4A Max (DDR3: 1.5-1.35V)

to avoid any extraneous connections.

NOTE: Aliases not used on CPU supply outputs

Note [1] current numbers from clarification email, from Srini, dated 9/10/2012 2:11pm.

HSW-ULT current estimates from Haswell Mobile ULT Processor EDS vol 1, doc #502406, v0.9.

6.3V

10%

0.47UF

CERM-X5R

0201

C0897

1

2

PLACE_NEAR=U0500.AG13:6.35mm

0

0201

MF

1/20W

5%

R0896

12

BYPASS=U0500.V15::6.35mm

0201

10V

X5R-CERM

10%

0.1UF

C0895

1

2

10V

X5R-CERM

0201

10%

0.1UF

BYPASS=U0500.AA15::6.35mm

C0892

1

2

X5R-CERM

BYPASS=U0500.AA15::6.35mm

10%

0.1UF

0201

10V

C0891

1

2

BYPASS=U0500.AA15::6.35mm

X5R

6.3V

0201

20%

1UF

C0890

1

2

201

5%

1/20W

MF

PLACE_NEAR=U0500.CH45:50.8mm

100

R0860

1

2

44 66

16 17

46

44

201

1/20W

MF

PLACE_NEAR=U0500.CE40:2.54mm

130

1%

R0802

1

2

201

1/20W

MF

PLACE_NEAR=R0810.1:2.54mm

75

1%

R0800

1

2

201

5%

1/20W

MF

PLACE_NEAR=U0500.CD43:38.1mm

43

R0810

12

5%

0

0201

1/20W

MF

R0811

12

0201

5%

0

1/20W

MF

R0812

12

44 66

44 66

44

66

CRITICAL

OMIT_TABLE

BGA

BROADWELL-MOBILE-Y-B

U0500

V15

U16

AG14

U30

T21

AG13

AJ45

AG45

AH36

AJ16

T31

T17

AE13

W22

Y22

T27

A26

A28

A30

AK35

AE15

N1

T1

W14

AK23

AK31

AJ28

AL37

AL39

AL30

AJ26

AA1

AB14

AA13

W1

AK29

AK19

AA45

AB38

W45

AA15

T33

N45

T45

A32

A24

T25

U18

AL14

AC15

AJ32

AB36

AK17

AE45

AC45

AD36

T35

OMIT_TABLE

CRITICAL

BROADWELL-MOBILE-Y-B

BGA

U0500

CL26

CK27

CK40

CK25

AK33

AL16

AL22

CJ16

CJ28

CJ32

CK19

CK21

CK31

CL14

CL22

CM27

CM33

CK23

CJ22

AV45

AY45

BB45

BD45

BF45

BH45

BK45

BM45

BP45

BT45

BV41

BV43

BV45

BW40

BW42

BW44

BY41

BY43

BY45

CA40

CA42

CA44

CB41

CB43

CB45

CD45

CF45

CM45

CN44

CR43

CR45

CU44

CV43

CV45

CY13

CY15

CY17

CY19

CY21

CY23

CY25

CY27

CY29

CY31

CY33

CY36

CY38

CY40

CY42

CY44

CH45

BM43

AJ20

BU14

AR40

AP1

AV1

BA14

BB1

BC14

BE14

BF1

BK1

BP1

BV1

CB1

CF1

CL1

CM3

CR1

CT3

CW1

CY3

CD43

CD41

CE40

CE42

CF43

CF39

CJ20

16

BYPASS=U0500.AG13::6.35mm

0201

X5R

6.3V

20%

1UF

C0896

1

2

201

5%

1/20W

MF

10K

R0850

1

2

44 62

CPU/PCH POWER

SYNC_DATE=10/01/2013

SYNC_MASTER=J92_DEVMLB

CPU_VIDSCLK_R

CPU_VIDSOUT_R

PPVOUT_S0_PCH_DCPRTC

MIN_LINE_WIDTH=0.2 mm

VOLTAGE=1.05V

MIN_NECK_WIDTH=0.2 mm

PPVRTC_G3H

VOLTAGE=1.05V

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.2 mm

PP1V05_S5_PCH_VCCDSW

MIN_NECK_WIDTH=0.1 mm

VOLTAGE=1.05V

MIN_LINE_WIDTH=0.2 mm

PP1V05_S5_PCH_VCCDSW_R

PP3V3_S5

PP3V3_S0

VOLTAGE=1.05V

PPVCOMP_S0_CPU

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.4 mm

MIN_LINE_WIDTH=0.4 mm

TP_PPVCCIO_S0_CPU

VOLTAGE=1.05V

MIN_NECK_WIDTH=0.2 mm

TP_MCP_DC_CY3

PP1V2_S3

TP_MCP_DC_CY44

MCP_DC_CV45

PPVCC_S0_CPU

CPU_VCCST_PWRGD

CPU_VIDALERT_R_L

PPVCC_S0_CPU

TP_MCP_DC_CW1

PP1V05_S0SW_PCH_USB3

PP1V05_S0SW_PCH_SATA

PP1V05_S0SW_PCH_PCIE

PP1V05_S0

CPU_VIDSOUT

PPVCC_S0_CPU

CPU_VIDALERT_L

CPU_PWR_DEBUG_L

PP1V05_S0

CPU_VCCSENSE_P

PP1V05_S0

PP1V05_S0SW_PCH_VCCSATA3PLL

PP3V3_SUS

PP1V05_S0SW_PCH_VCCUSB3PLL

PP1V05_SUS

PP1V05_S0

PP1V05_S0_PCH_VCC_ICC

PP1V05_S0_PCH_VCCACLKPLL

PP1V05_SUS

PP1V05_S0

PP3V3_S0

PP1V05_S0

PP1V05_S0

PP1V5_S0

PP3V3_S0

PP3V3_SUS

PP1V5_S0

PP1V05_S0_PCH_VCCAPLL_OPI

PP1V05_SUS

PP1V05_S0_PCH_VCCAPLL_OPI

TP_MCP_RSVD_CJ22

TP_MCP_RSVD_CK23

TP_IST_TRIGGER

TP_IVR_ERROR

CPU_VR_EN

CPU_VR_READY

CPU_VIDSCLK

PP3V3_SUS

PP3V3_S5

PP3V3_SUS

PP1V05_S0

PP1V05_SUS_PCH_VCCAOSCSUS

<BRANCH>

<SCH_NUM>

<E4LABEL>

8 OF 130

8 OF 75

12 13 46 60

8

11 13 15 16

17 22 33 37 46 47

51 59 60 73 75

8

11 12 13 15

17 18 23 24 29 32

33 34 35 36 40 46 47 53 60 73

75

5

10 19 20

21 46 52 59 60 69

64

8

10 35 45

60

8

10 35 45

60

11

51 60

11 51 60

11 51 60

6 8

11 15 16

17 32 44 46 51

60

8

10 35 45

60

6 8

11 15 16

17 32 44 46 51

60

6 8

11 15 16

17

32 44 46 51 60

11 12

8

11 14 15

18 27 28 29

46 51 60

11 14

8

11 12 16

46 48 51 60

6 8

11 15 16 17

32 44

46 51

60

11

11 12

8

11 12 16 46

48 51 60

6 8

11 15 16 17

32 44 46 51 60

8

11 12 13

15 17 18 23

24 29 32 33 34 35 36 40

46 47 53 60 73 75

6 8

11 15 16 17

32 44 46 51 60

6 8

11 15 16

17

32 44 46 51 60

8

11 17 40

46 60

8

11 12 13 15

17 18 23 24 29 32

33 34 35 36 40 46 47 53 60 73

75

8

11 14 15

18 27 28 29

46 51 60

8

11 17 40 46

60

8

11

8

11 12 16

46 48 51 60

8

11

8

11 14 15 18

27 28 29 46 51 60

8

11 13 15

16 17 22 33

37 46 47 51 59 60 73 75

8

11 14 15

18 27 28

29

46 51 60

6 8

11 15 16

17 32 44

46

51 60

11

Page 9

WWW.AliSaler.Com

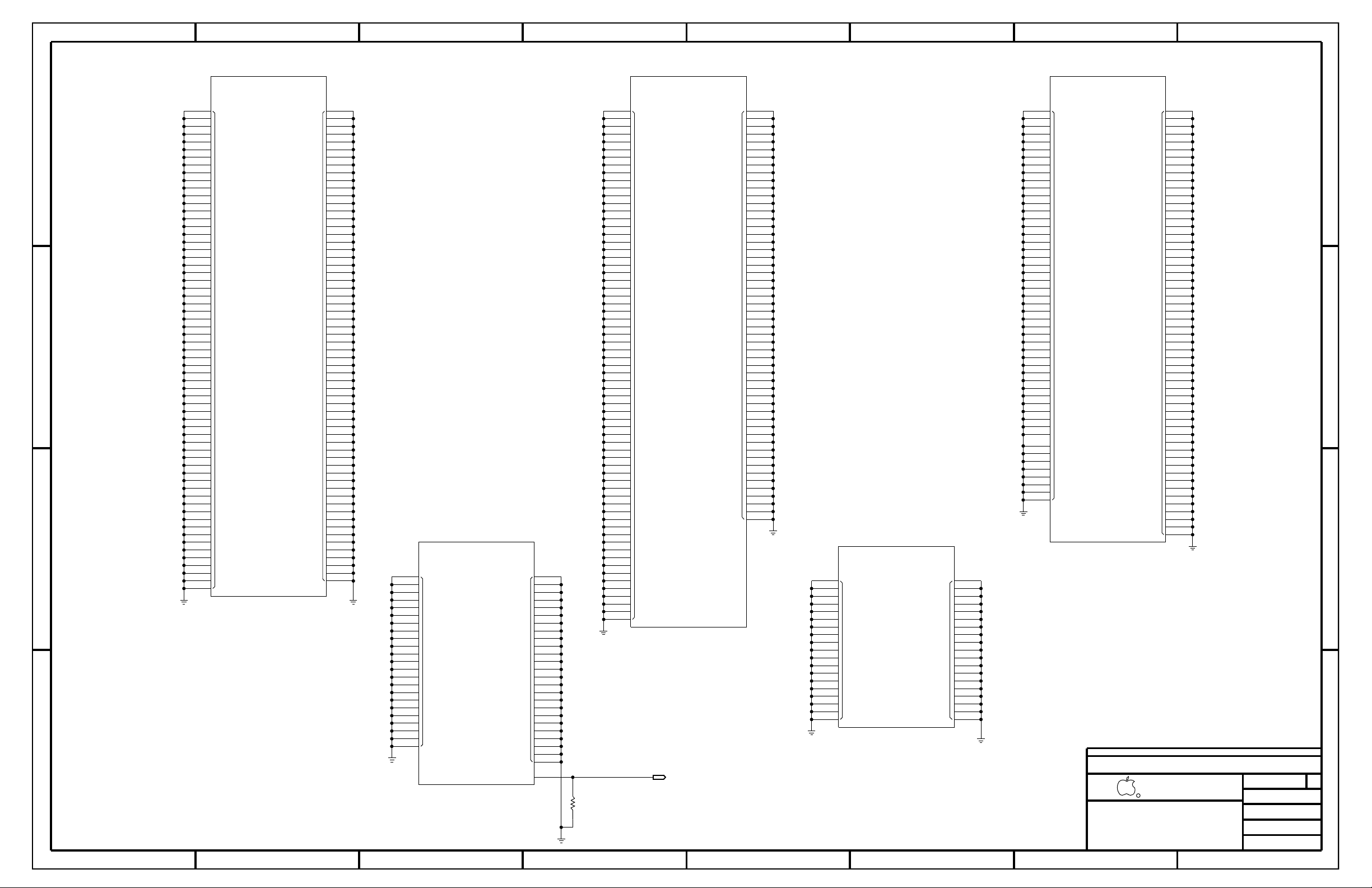

(14 OF 20)

VSS

VSS

(16 OF 20)

VSS

VSS_SENSE

VSS

OUT

(17 OF 20)

VSS VSS

(15 OF 20)

VSS

VSS

(20 OF 20)

VSS

VSS

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5

4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

BGA

OMIT_TABLE

CRITICAL

BROADWELL-MOBILE-Y-B

U0500

AH29

AH30

AH31

AH32

AH33

AH34

AH44

AH6

AJ18

AJ24

AJ30

AJ37

AJ39

AK12

AK21

AK27

AK6

AM13

AM17

AM19

AM21

AM23

AM25

AM27

AM29

AM31

AM35

AM45

AN10

AN12

AN14

AN2

AN4

AN40

AN42

AN44

AN6

AN8

AP15

AP39

AP43

AP7

AR42

AT1

AT15

AT39

AT45

AT7

AU44

AV13

AV15

AV39

AW44

AY1

AY13

AY15

AY39

AY7

BA44

BB11

BB13

BB15

BB3

BB39

BB5

BB7

BB9

BC44

BD1

BD13

BD15

BD39

BD7

BE40

BE42

BE44

BF13

BF15

BF39

BF7

BG14

BG44

BH1

BH13

BH15

BH39

BH41

BH43

BH7

BJ44

BK13

BK15

BK39

BK7

BL10

BL12

BL2

BL4

BL40

BL42

BL44

BL6

BL8

BM1

BM13

BM39

BM7

BN44

BP13

CH1

CH15

CJ18

CJ24

CJ30

CL24

CL5

CN1

CU1

CV3

CV39

CV41

CW12

CW14

CW16

CW18

CRITICAL

OMIT_TABLE

BGA

BROADWELL-MOBILE-Y-B

U0500

AC32

AJ13

AK15

AK44

AM33

AV7

CA14

CH7

E16E20

E24

E28

E32

E36

F5

G16

G20

G24

N16

N20

N24

N28

N32

P35

R10

R16

R18

R2

R20

R22

R24

R26

R28

R30

R4

R44

R6

R8

CH43

T15

U22

U24

U26

U28

U32

U34

V17

V2

V40

44 66

PLACE_NEAR=U0500.CH43:50.8mm

201

MF

1/20W

100

5%

R0960

1

2

BGA

CRITICAL

OMIT_TABLE

BROADWELL-MOBILE-Y-B

U0500

A42

A6

AA11

AF36

BN14

BR14

BW14

CE14

CG14

CJ34

CK29

CK33

CL30

CL32

D4

D42

H42

J1

J3

J43

J45

L38

T13

W30

W32

W34

W35

Y12

Y14

Y16

Y19

Y2

Y24

Y28

Y32

Y40

Y42

Y44

BGA

OMIT_TABLE

CRITICAL

BROADWELL-MOBILE-Y-B

U0500

AG39

AM39

AR14

AW14

BP39

BP7

BR44

BT1

BT13

BT39

BT7

BU40

BU42

BU44

BV13

BV15

BV39

BV7

BY1

BY11

BY13

BY15

BY3

BY39

BY5

BY7

BY9

C16

C20

C24

C28

C32

C36

CA8

CB13

CB15

CB39

CB7

CC10

CC40

CC42

CC44

CD1

CD11

CD13

CD15

CD3

CD39

CD5

CD7

CD9

CE44

CF13

CF15

CF7

CG44

CH13

CJ26

CK10

CK3

CK38

CK44

CL12

CM15

CM17

CM19

CM21

CM23

CM25

CM31

CM35

CM43

CN26

CN42

CN8

CP17

CP29

CP3

CR14

CR18

CR22

CR26

CR37

CR8

CT31

CU14

CU18

CU22

CU26

CU42

CU8

CV35

CV37

CW20

CW22

CW24

CW26

CW28

CW30

CW32

CW34

CW5

CW8

CY10

CY7

D10

G28

G32

H10

H36

J16

J20

J24

J28

J32

L16

L2

L20

L24

L28

L32

OMIT_TABLE

CRITICAL

BGA

BROADWELL-MOBILE-Y-B

U0500

A10

A16

A20

A36

A40

AA19

AA21

AA22

AA24

AA25

AA26

AA28

AA29

AA3

AA30

AA32

AA33

AA34

AA35

AA37

AA39

AA5

AA7

AB12

AB15

AB16

AB40

AB44

AB8

AC1

AC11

AC13

AC19

AC24

AC28

AC3

AC35

AC37

AC41

AC43

AC5

AC7

AC9

AD12

AD14

AD16

AD19

AD24

AD28

AD32

AD44

AD6

AE16

AE19

AE24

AE28

AE32

AE35

AE37

AF12

AF14

AF16

AF44

AF6

AG19

AG24

AG28

AG32

AG35

AG37

AH12

AH14

AH15

AH16

AH17

AH19

AH20

AH21

AH22

AH23

AH25

AH26

AH27

AH28

AR12

AU12

AV11

AV3

AV5

AV9

BM15

BP15

CN5

CR5

CU5

H4

T19

T23

T29

U14

U20

V44

W16

W18

W19

W24

W28

CPU/PCH GROUNDS

SYNC_DATE=04/10/2013SYNC_MASTER=J92_WILL

CPU_VCCSENSE_N

<BRANCH>

<SCH_NUM>