LG Display LC320WUE-SBR1 Specification

Global LCD Panel Exchange Center |

www.panelook.com |

LC320WUE

Engineering Specification

SPECIFICATION

FOR

APPROVAL

( |

) |

Preliminary Specification |

|

|

|

||

( |

) |

Final Specification |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Title |

|

32.0” WUXGA TFT LCD |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BUYER |

|

General |

|

SUPPLIER |

RAKEN |

|

|

|

|

|

|

*MODEL |

LC320WUE |

|

|

MODEL |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SUFFIX |

SBR1(ROHS Verified) |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

*When you obtain standard approval, |

|

please use the above model name without suffix

APPROVED BY

SIGNATURE

DATE

DATE

/

/

/

/

Please return 1 copy for your confirmation with your signature and comments.

SIGNATURE

APPROVED BY |

|

DATE |

|

|

|

/ Team Leader |

|

|

|

|

|

REVIEWED BY |

|

|

/ PM |

|

|

|

|

|

PREPARED BY |

|

|

/ Engineer |

|

|

|

|

|

LCM R&D Dept.

RAKEN Technology Co., Ltd

Ver. 0.1 |

1 /39 |

|

|

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

LC320WUE

Engineering Specification

|

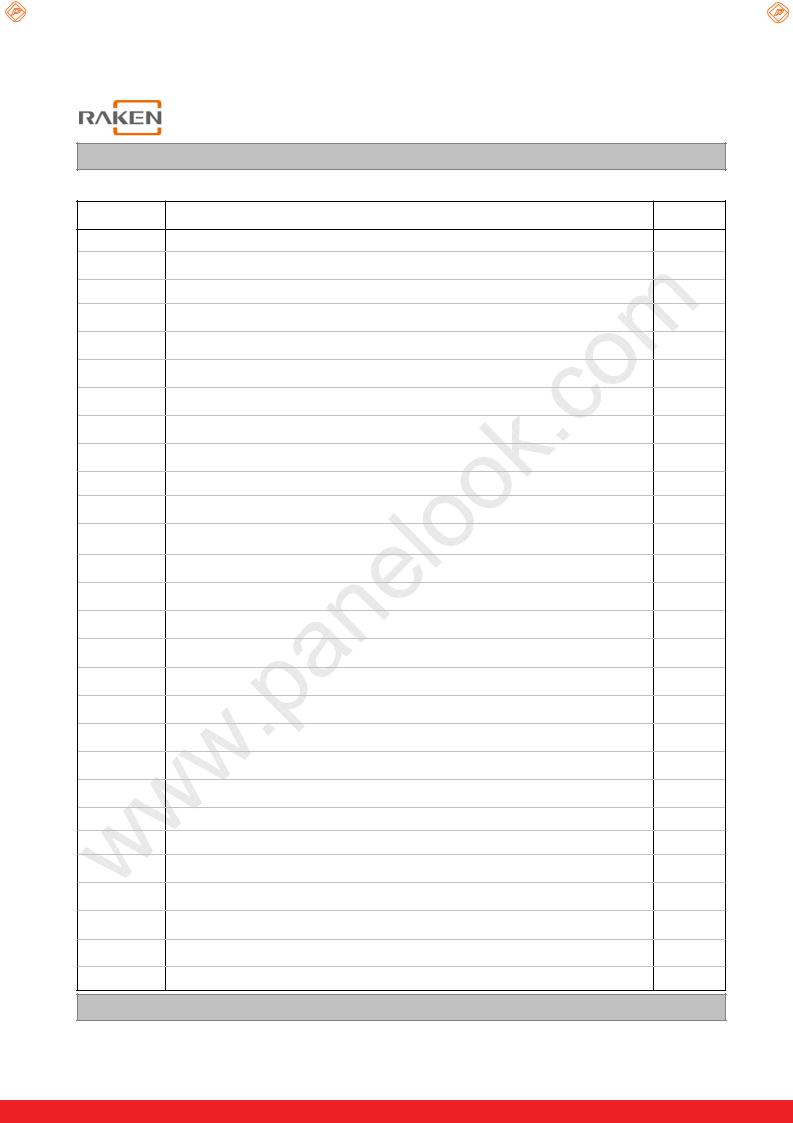

CONTENTS |

|

Number |

ITEM |

Page |

|

COVER |

1 |

|

CONTENTS |

2 |

|

RECORD OF REVISIONS |

3 |

1 |

GENERAL DESCRIPTION |

4 |

2 |

ABSOLUTE MAXIMUM RATINGS |

5 |

3 |

ELECTRICAL SPECIFICATIONS |

6 |

3-1 |

ELECTRICAL CHARACTERISTICS |

6 |

3-2 |

INTERFACE CONNECTIONS |

10 |

3-3 |

SIGNAL TIMING SPECIFICATIONS |

12 |

3-4 |

DATA MAPPING AND TIMING |

13 |

3-5 |

PANEL PIXEL STRUCTURE |

14 |

3-6 |

POWER SEQUENCE |

15 |

|

|

|

4 |

OPTICAL SPECIFICATIONS |

16 |

5 |

MECHANICAL CHARACTERISTICS |

20 |

6 |

RELIABILITY |

23 |

7 |

INTERNATIONAL STANDARDS |

24 |

7-1 |

SAFETY |

24 |

7-2 |

EMC |

24 |

8 |

PACKING |

25 |

8-1 |

DESIGNATION OF LOT MARK |

25 |

8-2 |

PACKING FORM |

25 |

9 |

PRECAUTIONS |

26 |

9-1 |

MOUTING PRECAUTIONS |

26 |

9-2 |

OPERATING PRECAUTIONS |

26 |

9-3 |

ELECTROSTATIC DISCHARGE CONTROL |

27 |

9-4 |

PRECAUTION FOR STRONG LIGHT EXPOSURE |

27 |

9-5 |

STORAGE |

27 |

9-6 |

HANDING PRECAUTION FOR PROTECTION FILM |

27 |

Ver. 0.1 |

|

2 /39 |

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

LC320WUE

Engineering Specification

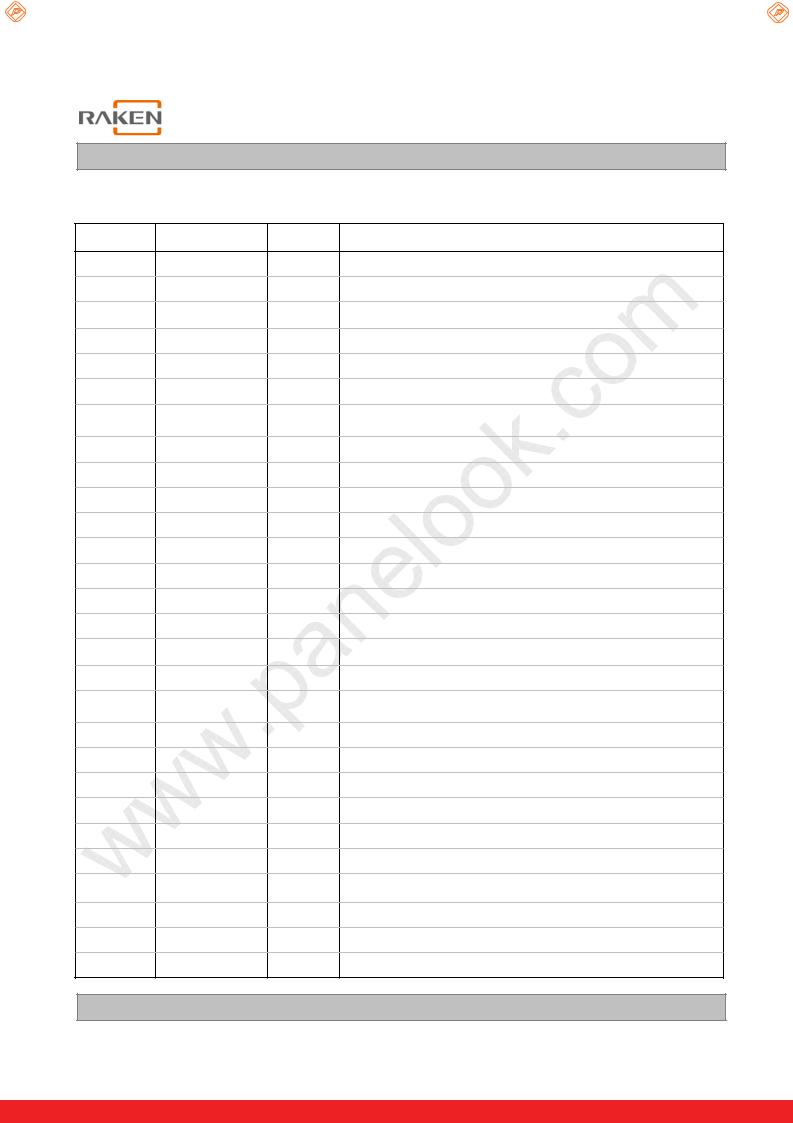

RECORD OF REVISIONS

Revision No. |

Revision Date |

Page |

Description |

0.1 |

Aug, 03, 2009 |

- |

Preliminary Specification |

Ver. 0.1 |

|

|

3 /39 |

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

LC320WUE

Engineering Specification

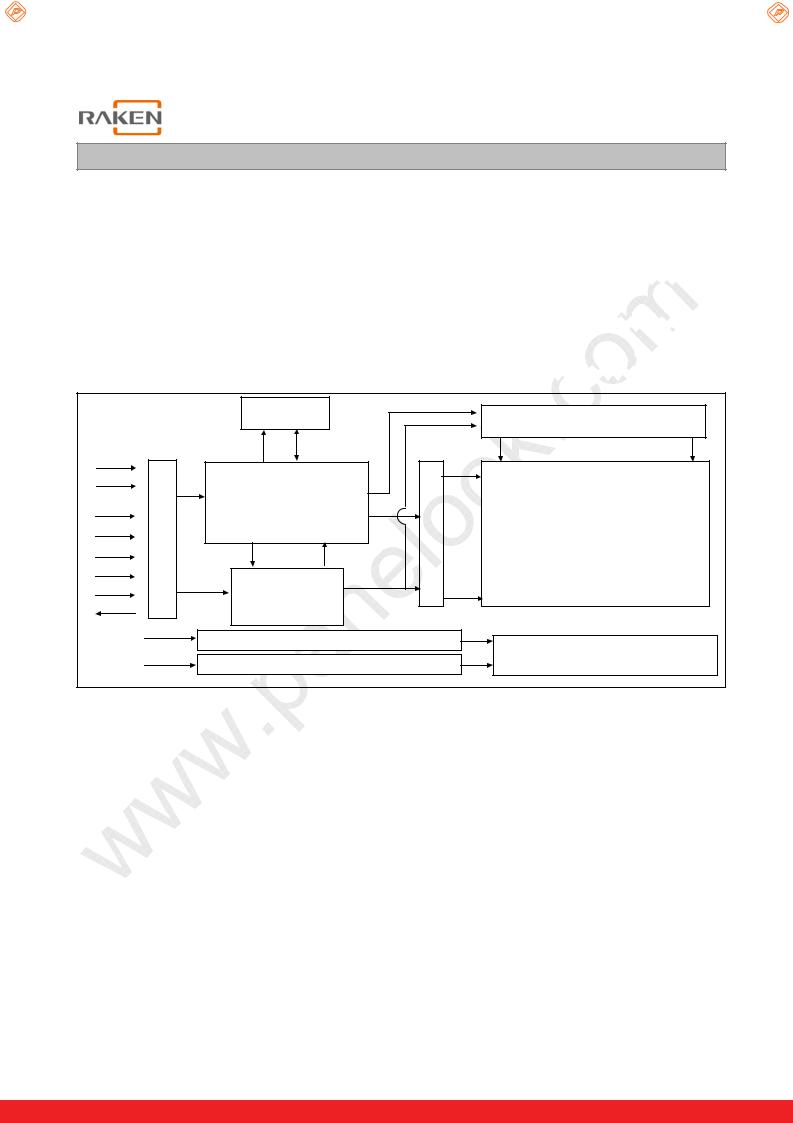

1. General Description

The LC320WUE is a Color Active Matrix Liquid Crystal Display with an integral External Electrode Fluorescent Lamp (EEFL) backlight system. The matrix employs a-Si Thin Film Transistor as the active element. It is a transmissive display type which is operating in the normally black mode. It has a 31.55 inch diagonally measured active display area with WUXGA resolution progressive mode (1080 vertical by 1920 horizontal pixel array).

Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arrayed in vertical stripes. Gray scale or the luminance of the sub-pixel color is determined with a 10-bit gray scale signal for each dot. Therefore, it can present a palette of more than 1.06B(true) colors.

It has been designed to apply the 10-bit 2-port LVDS interface.

It is intended to support LCD TV, PCTV where high brightness, super wide viewing angle, high color gamut, high color depth and fast response time are important.

color gamut, high color depth and fast response time are important.

|

|

|

Mini-LVDS(RGB) |

|

||

|

|

|

EEPROM |

|

Source Driver Circuit |

|

|

|

|

|

|

||

+12.0V |

|

SCL |

SDA |

|

S1 |

S1920 |

|

|

|

|

G1 |

|

|

LVDS |

|

|

|

Gate |

|

|

|

Timing Controller |

|

|

|||

2Port |

|

|

|

|||

CN1 |

[LVDS Rx + OPC + ODC |

|

|

|||

Reverse |

|

|

||||

Driver |

|

|

||||

(51pin) |

integrated] |

TFT - LCD Panel |

||||

LVDS Select |

|

|||||

|

|

|

||||

|

|

|

|

|||

Bit Select |

|

|

|

(1920 |

Ý RGB Ý 1080 pixels) |

|

|

|

|

Circuit |

|||

OPC Enable |

|

|

|

|

|

|

ExtVBR-B |

|

Power Circuit |

G1080 |

|

||

VBR-B out |

|

|

Block |

|

|

|

High Input |

|

CN2, 3pin, 18 Lamps/@135 mA |

|

|

|

|

High Input |

|

CN3, 3pin, 18 Lamps/@135mA |

|

Back light Assembly |

||

|

|

|

|

|||

General Features

|

Active Screen Size |

31.55 inches(801.31mm) diagonal |

|

|

Outline Dimension |

760 (H) x 450 (V) x 47.5 mm(D) (Typ.) |

|

|

Pixel Pitch |

0.36375 mm x 0.36375 mm |

|

|

Pixel Format |

1920 horiz. by 1080 vert. Pixels, RGB stripe arrangement |

|

|

|

|

|

|

Color Depth |

10-bit(D), 1.06 B colors |

|

|

Luminance, White |

500 cd/m2 (Center 1point ,Typ.) |

|

|

Viewing Angle (CR>10) |

Viewing angle free ( R/L 178 (Min.), U/D 178 (Min.)) |

|

|

Power Consumption |

Total 116.2 W (Typ.) (Logic=6.2 W, Back Light=110W with Inverter ,Control |

|

|

PCB) |

|

|

|

|

|

|

|

Weight |

5.7Kg(TBD) |

|

|

Display Mode |

Transmissive mode, Normally black |

|

|

Surface Treatment |

Hard coating(3H), Anti-glare treatment of the front polarizer (Haze 10%) |

|

|

|

|

|

|

Ver. 0.1 |

4 /39 |

|

|

|

|

|

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

LC320WUE

Engineering Specification

2. Absolute Maximum Ratings

The following items are maximum values which, if exceeded, may cause faulty operation or damage to the LCD Panel.

Table 1. ABSOLUTE MAXIMUM RATINGS

Parameter |

Symbol |

|

Value |

Unit |

Remark |

||

Min |

Max |

||||||

|

|

|

|

|

|||

Power Input |

LCD circuit |

VLCD |

-0.3 |

+14.0 |

V [DC] |

GY\G YG¶j |

|

Voltage |

|||||||

|

|

|

|

|

|

||

|

Operating |

|

|

|

|

GY\G YG¶j |

|

B/L Input voltage |

Voltage (one |

VOP |

700 |

1100 |

V[ RMS] |

Burst Dimming Duty |

|

|

side) |

|

|

|

|

100% |

|

Operating Temperature |

TOP |

0 |

+50 |

¶C |

|

||

Storage Temperature |

TST |

-20 |

+60 |

¶C |

Note 1 |

||

Operating Ambient Humidity |

HOP |

10 |

90 |

%RH |

|||

|

|||||||

Storage Humidity |

|

HST |

10 |

90 |

%RH |

|

|

Notes : 1. Temperature and relative humidity range are shown in the figure below. Wet bulb temperature should be Max 39 ¶C and no condensation of water.

2. Gravity mura can be guaranteed below 40 condition.

|

|

|

|

|

|

|

|

90% |

|

|

|

|

|

|

|

|

|

|

60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

60% |

|

|

|

Wet Bulb |

|

|

40 |

50 |

|

|

|

[(%)RH] |

Storage |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

Temperature [¶C] |

|

|

|

|

|

|

Humidity |

|

||

|

|

|

|

|

|

|

|

|

40% |

Operation |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

|

|

|

|

|

|

|

|

|

0 |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10% |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-20 |

0 |

10 |

20 |

30 |

40 |

50 |

60 |

70 |

80 |

|

|

|

|

Dry Bulb Temperature [¶C] |

|

|

|

|

|

||||

Ver. 0.1 |

5 /39 |

|

|

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

LC320WUE

Engineering Specification

3. Electrical Specifications

It requires two kind of power inputs.

One is employed to power for the LCD circuit. The other Is used for the EEFL backlight circuit.

3-1. Electrical Characteristics

Table 2. DC ELECTRICAL CHARACTERISTICS

Parameter |

Symbol |

|

Value |

|

Unit |

Note |

|

Min |

Typ |

Max |

|||||

|

|

|

|

||||

Circuit : |

|

|

|

|

|

|

|

Power Input Voltage |

VLCD |

10.8 |

12.0 |

13.2 |

VDC |

|

|

Power Input Current |

ILCD |

- |

500 |

650 |

mA |

1 |

|

- |

690 |

900 |

mA |

2 |

|||

|

|

||||||

Power Consumption |

PLCD |

- |

6.2 |

8.1 |

Watt |

1 |

|

Rush current |

IRUSH |

- |

- |

3.0 |

A |

3 |

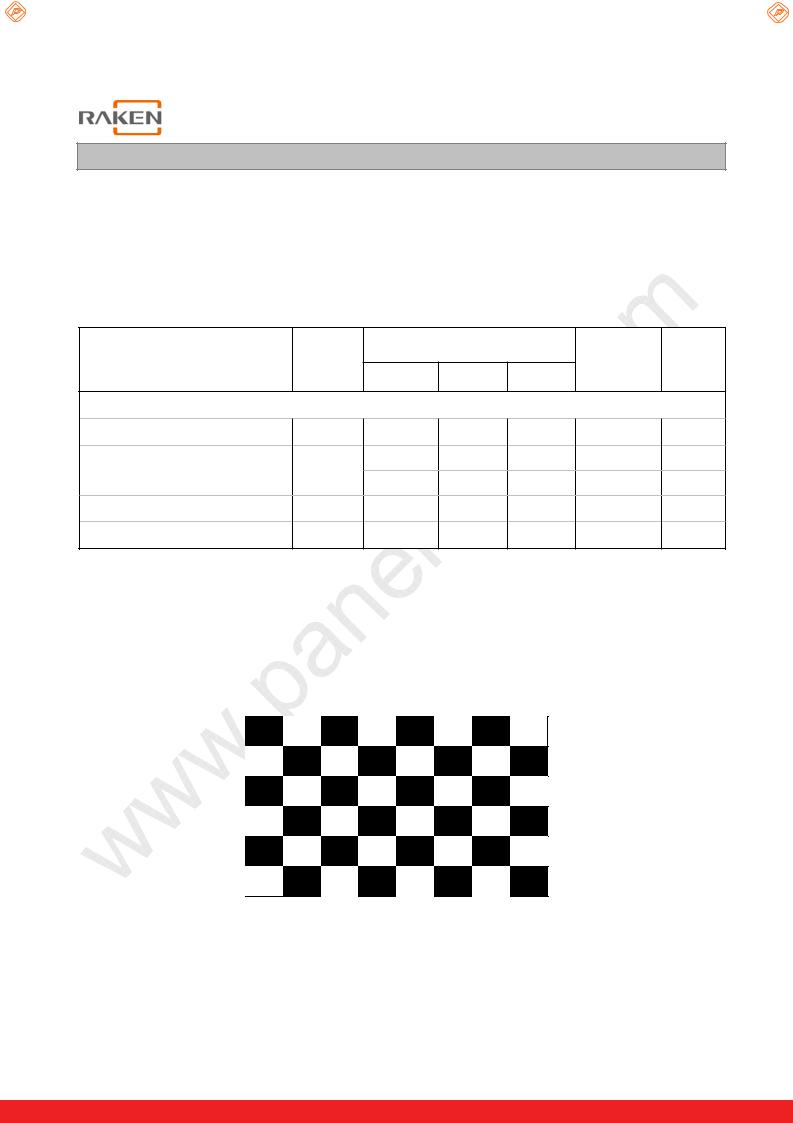

Notes : 1. The specified current and power consumption are under the VLCD=12.0V, 25 2¶C, fV=60Hz condition whereas mosaic pattern(8 x 6) is displayed and fV is the frame frequency.

2.The current is specified at the maximum current pattern.

3.The duration of rush current is about 2ms and rising time of power input is 0.5ms (min.).

White : 1023Gray |

Black : 0Gray |

Mosaic Pattern(8 x 6) |

Ver. 0.1 |

6 /39 |

|

|

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

|

|

|

|

|

|

|

|

|

|

|

LC420WUE |

|

|

|

Product Specification |

|

|

|

|||||

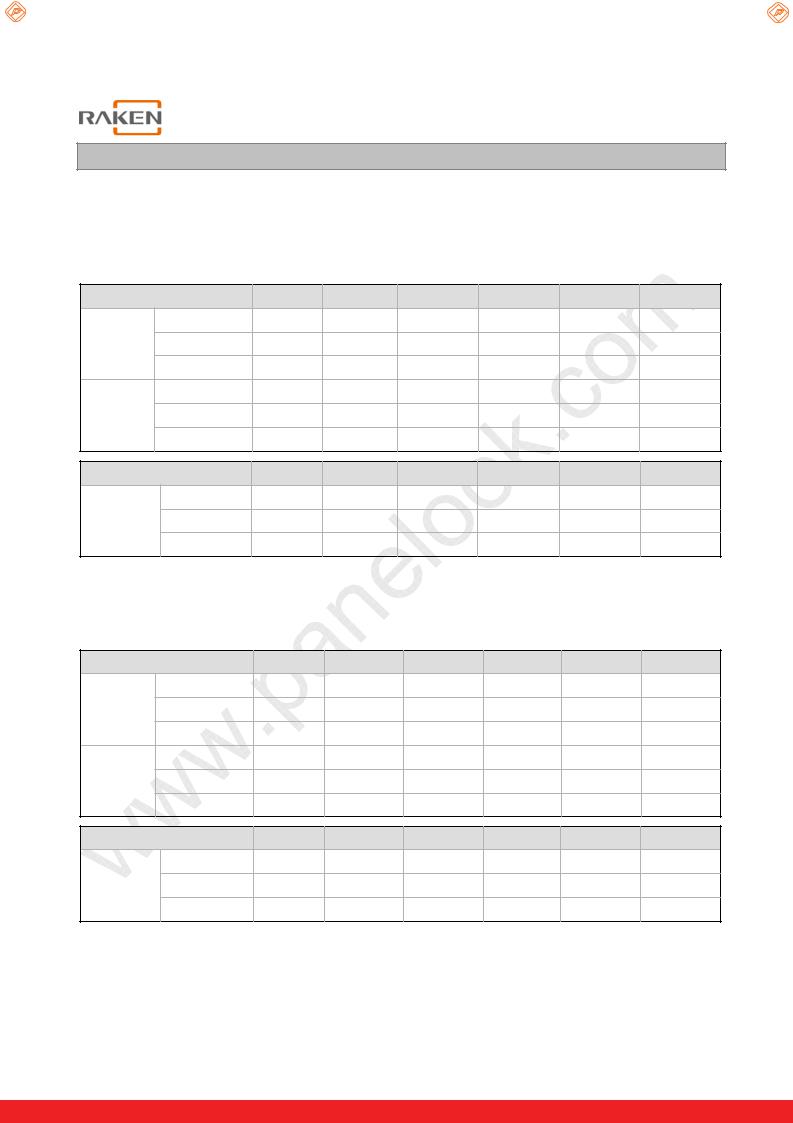

Table 3. ELECTRICAL CHARACTERISTICS for IPB& Lamp (Continue) |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

|

|

Values |

|

Unit |

Notes |

||

|

|

|

|

|

|

|

|

||||

|

|

Min |

|

Typ |

|

|

Max |

||||

|

|

|

|

|

|

|

|

|

|||

|

Backlight Assembly : |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Operating Voltage |

|

VBL |

800 |

950 |

|

|

1100 |

VRMS |

1, 2 |

|

|

(one side,fBL=62KHz, IBL= 135mArms)) |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||

|

Operating Current (one side) |

|

IBL |

130 |

135 |

|

|

140 |

mARMS |

1 |

|

|

Established Starting |

0 |

VS |

- |

- |

|

|

1225 |

VRMS |

1, 3 |

|

|

Voltage (one side) |

25 |

- |

- |

|

|

1020 |

||||

|

|

|

|

|

|

||||||

|

Operating Frequency |

|

fBL |

43 |

45 |

|

|

47 |

kHz |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Striking Time |

|

S TIME |

- |

- |

|

|

2.0 |

sec |

3 |

|

|

Power Consumption |

|

PBL |

|

67 |

|

|

74 |

Watt |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Burst Dimming Duty |

|

PWM duty |

20 |

|

|

|

|

100 |

% |

9 |

|

Burst Dimming Frequency |

|

1/T |

98 |

- |

|

|

182 |

Hz |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

|

|

Values |

|

Unit |

Notes |

||

|

|

|

|

|

|

|

|

||||

|

|

Min |

|

Typ |

|

|

Max |

||||

|

|

|

|

|

|

|

|

|

|||

|

Lamp : APPENDIX |

|

|

|

|

|

|

|

|

|

|

|

Lamp Voltage (one side) |

|

VLAMP |

820 |

|

1035 |

|

|

1075 |

VRMS |

2 |

|

Lamp Current (one side) |

|

ILAMP |

3 |

|

7.5 |

|

|

8 |

mARMS |

|

|

Discharge Stabilization Time |

|

TS |

- |

|

- |

|

|

3 |

Min |

5 |

|

Lamp Frequency |

|

f LAMP |

40 |

|

65 |

|

|

80 |

KHz |

|

|

Lamp Temperature |

|

TLAMP |

|

|

|

|

|

130 |

C |

|

|

Established Starting |

0 |

VS |

|

|

|

|

|

1225 |

VRMS |

3 |

|

Voltage (one side) |

25 |

VS |

|

|

|

|

|

1020 |

||

|

|

|

|

|

|

|

|

||||

|

Life Time |

|

|

50,000 |

|

|

|

|

|

Hrs |

7 |

Notes : The design of the inverter must have specifications for the lamp in LCD Assembly. The electrical characteristics of inverter are based on High-High Driving type.

The performance of the lamps in LCM, for example life time or brightness, is extremely influenced by the characteristics of the DC-AC inverter. So, all the parameters of an inverter should be carefully designed so as not to produce too much leakage current from high-voltage output of the inverter. When you design or order the inverter, please make sure unwanted lighting caused by the mismatch of the lamp and the inverter (no lighting, flicker, etc) has never been occurred. When you confirm it,

the LCD– Assembly should be operated in the same condition as installed in your instrument.

the LCD– Assembly should be operated in the same condition as installed in your instrument.

Do not attach a conductive tape to lamp connecting wire.

Do not attach a conductive tape to lamp connecting wire.

If you attach conductive tape to the lamp wire, not only luminance level can be lower than typical one

but also inverter operate abnormally on account of leakage current which is generated between lamp wire and conductive tape.

1.Specified values are defined for a Backlight Assembly.( IBL : 18 lamp, 7.5mA/Lamp)

2.Operating voltage is measured at 25 2¶C(after 2hr.aging). The variance range for operating voltage is 10%.

3.The established starting voltage [ VS ] should be applied to the lamps for more than Striking time (S TIME)

for start-up. Inverter open voltage must be more than established starting voltage. Otherwise, the lamps may not be turned on. The used lamp current is typical value.

Ver. 0.1 |

7 /33 |

|

|

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

LC320WUE

Engineering Specification

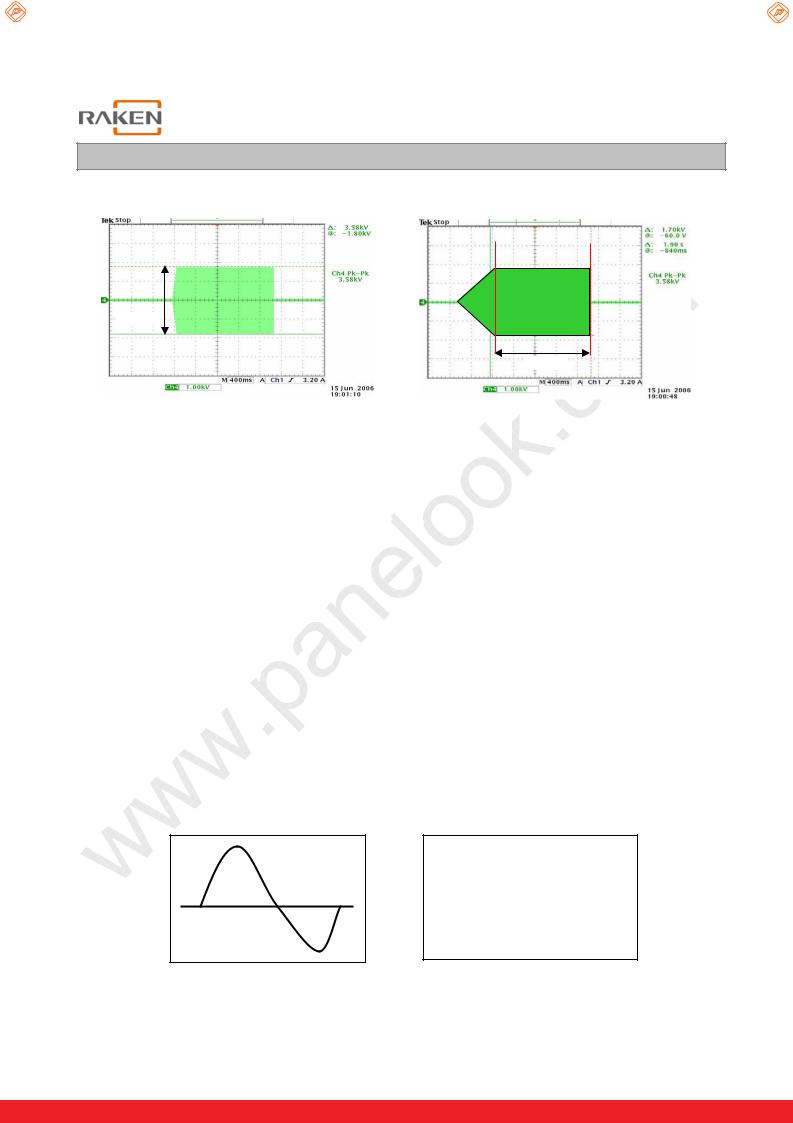

} T

S TIME

Vs = (Vpk-pk) / [ 2*root(2)]

4.Lamp frequency may produce interference with horizontal synchronous frequency. As a result, the may

cause beat on the display. Therefore, lamp frequency shall be away as much as possible from the horizontal synchronous frequency and its harmonics range in order

order to prevent interference.

to prevent interference.

5.The brightness of the lamp after lighted for 5minutes is defined as 100%.

TS is the time required for the brightness of the center of the lamp to be not less than 95% at typical current. The screen of LCD module may be partially dark by the time the brightness of lamp is stable after turn on.

6.Maximum level of power consumption is measured at initial turn on.

Typical level of power consumption is measured after 2hrs aging at 25 2¶C.

7.The life time is determined as the time at which brightness of the lamp is 50% compared to that of initial value at the typical lamp current on condition of continuous operating at 25 2¶C, based on duty 100%.

8.The output of the inverter must have symmetrical(negative and positive) voltage and current waveform (Unsymmetrical ratio is less than 10%). Please do not use the inverter which has not only unsymmetrical voltage and current but also spike wave.

Requirements for a system inverter design, which is intended to achieve better display performance, power efficiency and more reliable lamp characteristics.

It can help increase the lamp lifetime and reduce leakage current.

a.The asymmetry rate of the inverter waveform should be less than 10%.

b.The distortion rate of the waveform should be within ˲2 ·10%.

*Inverter output waveform had better be more similar to ideal sine wave.

* Asymmetry rate:

I p

| I p – I –p | / Iop x 100%

* Distortion rate

I -p

I p (or I –p) / Iop

Ver. 0.1 |

8 /39 |

|

|

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

LC320WUE

Engineering Specification

9. The reference method of burst dimming duty ratio.

It is recommended to use synchronous V-sync frequency to prevent waterfall (Vsync x 2 =Burst Frequency)

{

A

PWM

Output of Inverter to Lamp

PWM duty={ A/T } * 100

Point A : rising time 90% of Iout point . Point B : falling starting point .

I out duty = { a/T } * 100 PWM Frequency = 1/T

+3.3V TTL

I-out

90%

Point A |

a |

Point B |

|

We recommend not to be much different between PWM duty and Iout duty .

different between PWM duty and Iout duty .

Dimming current output rising and falling time may produce humming and inverter trans’ sound noise. Burst dimming duty should be 100% for more than 1second after turn on.

Equipment

Oscilloscope :TDS3054B(Tektronix)

Current Probe : P6022 AC (Tektronix)

High Voltage Probe: P5100(Tektronix)

10. The Cable between the backlight connector and its inverter power supply should be connected directly with a minimized length. The longer cable between the backlight and the inverter may cause the lower  luminance of lamp and may require more higher starting voltage ( Vs ).

luminance of lamp and may require more higher starting voltage ( Vs ).

11.The operating current must be measured as near as backlight assembly input.

12.The operating current unbalance between left and right must be under 10% of Typical current

Left(Master) current – Right(Slave) Current |

10% of typical current |

Ver. 0.1 |

9 /39 |

|

|

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

LC320WUE

Engineering Specification

3-2. Interface Connections

This LCD module employs two kinds of interface connection, a 51-pin connector is used for the module electronics and two 3-pin Balance PCB connectors are used for the integral backlight system.

3-2-1. LCD Module

- LCD Connector(CN1): FI-R51S-HF(manufactured by JAE) or KN25-51P-0.5SH(manufactured by Hirose) - Mating Connector : FI-R51HL(JAE) or compatible

Table 4. MODULE CONNECTOR(CN1) PIN CONFIGURATION

No |

Symbol |

Description |

No |

Symbol |

Description |

|

|

|

|

|

|

|

|

1 |

GND |

Ground |

27 |

Bit Select |

‘H’ or NC= 10bit(D) , ‘L’ = 8bit |

|

2 |

NC |

No Connection |

28 |

R2AN |

SECOND LVDS Receiver Signal (A-) |

|

3 |

NC |

No Connection |

29 |

R2AP |

SECOND LVDS Receiver Signal (A+) |

|

4 |

NC |

No Connection |

30 |

R2BN |

SECOND LVDS Receiver Signal (B-) |

|

5 |

NC |

No Connection |

31 |

R2BP |

SECOND LVDS Receiver Signal (B+) |

|

6 |

NC |

No Connection |

32 |

R2CN |

SECOND LVDS Receiver Signal (C-) |

|

7 |

LVDS Select |

‘H’ =JEIDA , ‘L’ or NC = VESA |

33 |

R2CP |

SECOND LVDS Receiver Signal (C+) |

|

8 |

VBR_EXT |

Vbr Input (For OPC) |

34 |

GND |

Ground |

|

9 |

OPC_OUT |

Vbr Output (For OPC) |

35 |

R2CLKN |

SECOND LVDS Receiver Clock Signal(-) |

|

10 |

OPC Enable |

H : OPC Enable / L : OPC Disable |

36 |

R2CLKP |

SECOND LVDS Receiver Clock Signal(+) |

|

11 |

GND |

Ground |

37 |

GND |

Ground |

|

12 |

R1AN |

FIRST LVDS Receiver Signal (A-) |

38 |

R2DN |

SECOND LVDS Receiver Signal (D-) |

|

13 |

R1AP |

FIRST LVDS Receiver Signal (A+) |

39 |

R2DP |

SECOND LVDS Receiver Signal (D+) |

|

14 |

R1BN |

FIRST LVDS Receiver Signal (B-) |

40 |

R2EN |

SECOND LVDS Receiver Signal (E-) |

|

15 |

R1BP |

FIRST LVDS Receiver Signal (B+) |

41 |

R2EP |

SECOND LVDS Receiver Signal (E+) |

|

16 |

R1CN |

FIRST LVDS Receiver Signal (C-) |

42 |

Reserved |

No connection or GND |

|

17 |

R1CP |

FIRST LVDS Receiver Signal (C+) |

43 |

Reserved |

No connection or GND |

|

18 |

GND |

Ground |

44 |

GND |

Ground |

|

19 |

R1CLKN |

FIRST LVDS Receiver Clock Signal(-) |

45 |

GND |

Ground |

|

20 |

R1CLKP |

FIRST LVDS Receiver Clock |

46 |

GND |

Ground |

|

Signal(+) |

||||||

|

|

|

|

|

||

21 |

GND |

Ground |

47 |

NC |

No connection |

|

22 |

R1DN |

FIRST LVDS Receiver Signal (D-) |

48 |

VLCD |

Power Supply +12.0V |

|

23 |

R1DP |

FIRST LVDS Receiver Signal (D+) |

49 |

VLCD |

Power Supply +12.0V |

|

24 |

R1EN |

FIRST LVDS Receiver Signal (E-) |

50 |

VLCD |

Power Supply +12.0V |

|

25 |

R1EP |

FIRST LVDS Receiver Signal (E+) |

51 |

VLCD |

Power Supply +12.0V |

|

26 |

Reserved |

No connection or GND |

- |

- |

- |

Notes : 1. |

All GND(ground) pins should be connected together to the LCD module’s metal frame. |

2. |

All VLCD (power input) pins should be connected together. |

3. |

All Input levels of LVDS signals are based on the EIA 644 Standard. |

4. |

Specific pins(pin No. #2~#6) are used for internal data process of the LCD module. |

|

If not used, these pins are no connection. |

5.LVDS pin (pin No. #24,25,40,41) are used for 10Bit(D) of the LCD module. If used for 8Bit(R), these pins are no connection.

6.Specific pin No. #44 is used for “No signal detection” of system signal interface.

It should be GND for NSB(No Signal Black) during the system interface signal is not. If this pin is “H”, LCD Module displays AGP(Auto Generation Pattern).

Ver. 0.1 |

10 /39 |

|

|

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

|

|

|

|

|

|

|

|

|

|

LC320WUE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Engineering Specification |

|

|||

|

3-2-2. Backlight Module |

|

|

|

|

|

|

|||

[ Master ] |

|

|

|

|

|

[ Slave ] |

|

|||

|

1) Balance Connector |

|

|

|

1) Balance Connector |

|

||||

|

: 65002WS-03 (manufactured by YEONHO) |

: 65002WS-03 (manufactured by YEONHO) |

||||||||

|

2) Mating Connector |

|

|

|

2) Mating Connector |

|

||||

|

: 65002HS-03 (manufactured by YEONHO) |

: 65002HS-03 (manufactured by YEONHO) |

||||||||

Table 5. BACKLIGHT CONNECTOR PIN CONFIGURATION(CN2,CN3) |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

No |

Symbol |

|

Master |

|

|

Slave |

|

Note |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

H_Input |

|

High_Input |

|

|

High_Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

H_Input |

|

High_Input |

|

|

High_Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

FB |

|

|

NC |

|

|

NC |

|

|

|

|

|

|

|

|

|

|

|

||

|

Rear view of LCM |

|

|

|

|

|

||||

3 |

2 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

|

3 |

|

|

|

|

Master |

|

|

|

Slave |

|

|

|

|

Ver. 0.1 |

11 /39 |

|

|

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Global LCD Panel Exchange Center |

www.panelook.com |

LC320WUE

Engineering Specification

3-3. Signal Timing Specifications

Table 6 shows the signal timing required at the input of the LVDS transmitter. All of the interface signal timing should be satisfied with the following specification for normal operation.

Table 6. TIMING TABLE for NTSC (DE Only Mode)

|

ITEM |

Symbol |

Min |

Typ |

Max |

Unit |

Note |

|

Display Period |

tHV |

- |

960 |

- |

tclk |

|

Horizontal |

Blank |

tHB |

100 |

140 |

240 |

tclk |

|

|

Total |

tHP |

1060 |

1100 |

1200 |

tclk |

2200/2 |

|

Display Period |

tVV |

- |

1080 |

- |

Lines |

|

Vertical |

Blank |

tVB |

11 |

45 |

69 |

Lines |

|

|

Total |

tVP |

1091 |

1125 |

1149 |

Lines |

|

|

ITEM |

Symbol |

Min |

Typ |

Max |

Unit |

Note |

|

DCLK |

fCLK |

70 |

74.25 |

77 |

MHz |

148.5/2 |

Frequency |

Horizontal |

fH |

65 |

67.5 |

70 |

KHz |

|

|

Vertical |

fV |

57 |

60 |

63 |

Hz |

|

Table 7 shows the signal timing required at the input of the LVDS transmitter. All of the interface signal timing should be satisfied with the following specification for normal operation.

Table 7. TIMING TABLE for PAL (DE Only Mode)

|

ITEM |

Symbol |

Min |

Typ |

Max |

Unit |

Note |

|

Display Period |

tHV |

- |

960 |

- |

tclk |

|

Horizontal |

Blank |

tHB |

100 |

140 |

240 |

tclk |

|

|

Total |

tHP |

1060 |

1100 |

1200 |

tclk |

2200/2 |

|

Display Period |

tVV |

- |

1080 |

- |

Lines |

|

Vertical |

Blank |

tVB |

228 |

270 |

300 |

Lines |

|

|

Total |

tVP |

1308 |

1350 |

1380 |

Lines |

|

|

ITEM |

Symbol |

Min |

Typ |

Max |

Unit |

Note |

|

DCLK |

fCLK |

70 |

74.25 |

77 |

MHz |

148.5/2 |

Frequency |

Horizontal |

fH |

65 |

67.5 |

70 |

KHz |

|

|

Vertical |

fV |

47 |

50 |

53 |

Hz |

|

Note : The Input of HSYNC & VSYNC signal does not have an effect on normal operation(DE Only Mode).

The performance of the electro-optical characteristics may be influenced by variance of the vertical refresh rate.

Ver. 0.1 |

12 /39 |

|

|

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

Loading...

Loading...