FUJITSU MB90473, MB90474, MB90477, MB90478 DATA SHEET

|

|

|

|

|

|

FUJITSU SEMICONDUCTOR |

|

DS07-13712-4E |

|

|

DATA SHEET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16-Bit Proprietary Microcontroller

CMOS

F2MC-16LX MB90470 Series

MB90473/474/477/478/F474L/F474H

■ DESCRIPTIONS

The FUJITSU MB90470 Series is a 16-bit general-purpose microcontroller designed for consumer products and other process control applications requiring high-speed and real-time processing.

The F2MC-16LX CPU core instruction set retains the AT architecture of the F2MC*1 family, with additional instructions for use with high-level languages, expanded addressing mode, enhanced multiply and divide instructions, and full bit processing. Also included is a built-in 32-bit accumulator for long-word processing.

Peripheral resources built into the MB90470 series include 8/16-bit PPG, expanded I/O serial interface, UART, 10-bit A/D converter, 16-bit input-output timer, 8/16-bit up-counter, PWC timer, I2C*2 interface, DTP/external interrupt, chip select, and 16-bit reload timer.

*1 : F2MC is an abbreviation for FUJITSU Flexible Microcontroller, and is a registered trademark of FUJITSU, Ltd.

*2 : I2C license :

This product includes licensing of Philips I2C patents if used by the customer in an I2C system subject to the I2C standard specifications established by Philips.

■ PACKAGES

100-pin plastic QFP |

100-pin plastic LQFP |

(FPT-100P-M06) |

(FPT-100P-M05) |

MB90470 Series

■FEATURES

•Clocks

Minimum instruction execution time :

50.0ns at 5 MHz base oscillation with 4 × multiplier (internal operation at 20 MHz/3.3 V ± 0.3 V)

62.5ns at 4 MHz base oscillation with 4 × multiplier (internal operation at 16 MHz/3.0 V ± 0.3 V) Uses PLL clock multiplier.

•Maximum memory size

16Mbytes

•Instruction set optimized for control applications

Handles bit, byte, word, long-word data

23standard addressing modes

32-bit accumulator for enhanced high-precision calculation Signed multiply-divide and expanded RETI instructions

•Instruction system compatible with high-level language (C) multitasking

System stack pointer

Instruction set correlation and barrel shift instructions

•Non-multi bus or multi-bus compatible

•Program patch function (for two address pointers)

•Improved execution speed

4-byte queue

•Powerful interrupt functions

8external interrupt functions with 8-level programmable priority

•Data transfer functions ( DMA or Extended intelligent I/O service)

16channels maximum

µDMA maximum assured operation frequency : 16 MHz

Extended intelligent I/O service maximum assured operation frequency : 20 MHz

•Built-in ROM

Flash versions : 256 KB, Mask ROM versions : 128 KB/256 KB

•Built-in RAM

10KB/16 KB

•General purpose ports

84ports maximum

(includes 16 ports with input pull-up resistance setting, 14 ports with output open drain setting)

•A/D converter

RC sequential comparator type, 8 channels

10-bit resolution, conversion time 4.65 µs (at 20 MHz operation)

•I2C interface

1channel

•PG

1channel

•UART

1channel

•I/O expansion serial interface (SIO)

2channels

•8/16-bit up/down timer

1channel

•16-bit PWC

3channels (including 2-channel input comparison function)

(Continued)

2

MB90470 Series

(Continued)

•16-bit reload timer

1 channel (8-bit × 2-channel, 16-bit × 1-channel mode switching function provided)

•16-bit input-output timer

2-channel input capture, 6-channel output compare, 1-channel free run timer

•2 built-in clock generator systems

•Low power modes

Stop, sleep, CPU intermittent mode, watch mode, etc.

•Package options

QFP100/LQFP100

•Process

CMOS technology

•Supply voltage

Can operate on 3 V single supply systems (with 5 V interface provided by some pins with 3/5 V dual-supply capability)

3

MB90470 Series

■ PRODUCT LINEUP

Parameter |

Part number |

MB90F474L |

|

MB90F474H |

MB90473 |

MB90474 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROM capacity |

|

FLASH 256 KB |

|

FLASH 256 KB |

MASKROM |

MASKROM |

|

|

128 KB |

256 KB |

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

RAM capacity |

|

16 KB |

|

16 KB |

10 KB |

16 KB |

|

|

|

|

|

|

|

|

|

Basic instructions |

|

: 351 |

|

|

|

|

Instruction bit length |

|

: 8-bit, 16-bit |

|

|

CPU functions |

|

Instruction length |

|

: 1 byte to 7 bytes |

|

|

|

|

Data bit length |

|

: 1-bit, 8-bit, 16-bit |

|

|

|

|

Minimum instruction execution time |

: 62.5 ns (with 16 MHz machine clock) |

|||

General purpose input/output ports : 84 Max

Ports

General purpose input/output ports (CMOS output)

General purpose input/output ports (built-in pull-up resistance)

General purpose input/output ports (N-ch open drain)

UART |

|

Stop-start synchronized : 1 channel |

|

|

||

8/16-bit PPG timer |

8-bit 6-channel/16-bit 3-channel |

|

|

|||

|

|

|

|

|||

8/16-bit up-down counter/timer |

Two 8-bit up-down counters with 6 event input pins |

|

||||

Two 8-bit reload/compare registers |

|

|

||||

|

|

|

|

|||

|

|

|

|

|

|

|

16-bit |

16-bit free-run timer |

Channel : 1 |

|

|

|

|

Overflow interrupt |

|

|

|

|||

|

|

|

|

|||

input/ |

|

|

|

|

|

|

Output compare (OCU) |

Channels : 6 |

|

|

|

||

out- |

|

|

|

|||

Pin input source : from compare register match signal |

|

|||||

put |

|

|

||||

|

|

|

|

|

||

|

Channels : 2 |

|

|

|

||

timers |

Input capture (ICU) |

|

|

|

||

Register rewritten from pin input (rising/falling/both edges) |

|

|||||

|

|

|

||||

|

|

|

|

|

|

|

DTP/external interrupt circuit |

External interrupt pins : 8 channels (set to edge or level correlation) |

|||||

|

|

|

|

|

||

I/O expansion serial interface |

2-channel, built-in |

|

|

|

||

|

|

|

|

|

||

I2C interface |

1-channel, built-in |

|

|

|

||

|

|

18-bit counter |

|

|

|

|

Time base timer |

Interrupt cycle : 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms |

|

||||

|

|

(minimum times, at base oscillator frequency 4 MHz) |

|

|||

|

|

|

|

|||

|

|

Conversion accuracy : 8/10-bit switchable |

|

|||

|

|

Single conversion mode (converts selected channel 1 time only) |

||||

A/D converter |

Scan conversion mode |

|

|

|||

(converts multiple consecutive channels, programmable up to 8 channels) |

||||||

|

|

|||||

|

|

Continuous conversion mode (converts selected channels continuously) |

||||

|

|

Stop conversion mode (converts selected channel, stops and repeats) |

||||

|

|

|

|

|||

Watchdog timer |

Reset interval : 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms |

|

||||

(minimum times, at base oscillator frequency 4 MHz) |

|

|||||

|

|

|

||||

|

|

|

||||

Low power (standby) modes |

Sleep, stop, CPU intermittent, watch mode |

|

||||

|

|

|

|

|

||

Process |

CMOS |

|

|

|

||

|

|

|

|

|

|

|

|

|

Flash model, low |

Flash model, high |

|

|

|

Notes |

|

voltage version |

voltage version |

Mask version |

Mask version |

|

|

(f = 10 MHz or |

|||||

|

|

(f = 20 MHz) |

|

|

||

|

|

less at VCC = 2.4 V) |

|

|

||

|

|

|

|

|

||

|

|

|

|

|

||

Emulator dedicated power supply |

|

|

|

|

||

(Continued)

4

MB90470 Series

(Continued)

|

|

Part number |

MB90477 |

MB90478 |

|

MB90V470B |

|

Parameter |

|

||||||

|

|

|

|

||||

|

|

|

|

|

|

|

|

ROM capacity |

MASKROM |

MASKROM |

|

|

|||

256 KB |

256 KB |

|

|||||

|

|

|

|

|

|||

|

|

|

|

|

|||

RAM capacity |

8 KB |

8 KB |

|

16 KB |

|||

|

|

|

|

|

|

|

|

|

|

|

Basic instructions |

|

: 351 |

|

|

|

|

|

|

: 8-bit, 16-bit |

|||

|

|

|

Instruction bit length |

|

|||

|

|

|

|

: 1 byte to 7 bytes |

|||

CPU functions |

Instruction length |

|

|||||

|

: 1-bit, 8-bit, 16-bit |

||||||

|

|

|

Data bit length |

|

|||

|

|

|

|

: 50 ns (with 20 MHz |

|||

|

|

|

Minimum instruction execution time |

||||

|

|

|

machine clock) |

||||

|

|

|

|

|

|||

|

|

|

|

|

|

||

|

|

|

General purpose input/output ports : 84 Max |

|

|

||

Ports |

|

General purpose input/output ports (CMOS output) |

|

||||

|

General purpose input/output ports (built-in pull-up resistance) |

||||||

|

|

|

|||||

|

|

|

General purpose input/output ports (N-ch open drain) |

|

|||

|

|

|

|

|

|||

UART |

|

Stop-start synchronized : 1 channel |

|

|

|||

|

|

|

|

||||

8/16-bit PPG timer |

8-bit 6-channel/16-bit 3-channel |

|

|

||||

|

|

|

|

|

|||

8/16-bit up-down counter/timer |

Two 8-bit up-down counters with 6 event input pins |

|

|||||

Two 8-bit reload/compare registers |

|

|

|||||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

16-bit free-run timer |

Channel : 1 |

|

|

|

|

16-bit |

|

Overflow interrupt |

|

|

|

||

|

|

|

|

|

|||

|

|

|

|

|

|

||

input/ |

|

Output compare (OCU) |

Channels : 6 |

|

|

|

|

output |

|

Pin input source : from compare register match signal |

|

||||

timers |

|

|

|

|

|

|

|

|

Input capture (ICU) |

Channels : 2 |

|

|

|

||

|

|

|

|

|

|||

|

|

Register rewritten from pin input (rising/falling/both edges) |

|||||

|

|

|

|||||

|

|

|

|

|

|||

DTP/external interrupt circuit |

External interrupt pins : 8 channels (set to edge or level correlation) |

||||||

|

|

|

|

|

|||

I/O expansion serial interface |

2-channel, built-in |

|

|

|

|||

|

|

|

|

|

|||

I2C interface |

1-channel, built-in |

|

|

|

|||

|

|

|

18-bit counter |

|

|

|

|

Time base timer |

Interrupt cycle : 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms |

|

|||||

|

|

|

(minimum times, at base oscillator frequency 4 MHz) |

|

|||

|

|

|

|

|

|

||

|

|

|

Conversion accuracy : 8/10-bit switchable |

|

|

||

|

|

|

Single conversion mode (converts selected channel 1 time only) |

||||

A/D converter |

Scan conversion mode |

|

|

|

|||

(converts multiple consecutive channels, programmable up to 8 channels) |

|||||||

|

|

|

|||||

|

|

|

Continuous conversion mode (converts selected channels continuously) |

||||

|

|

|

Stop conversion mode (converts selected channel, stops and repeats) |

||||

|

|

|

|

||||

Watchdog timer |

Reset interval : 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms |

||||||

(minimum times, at base oscillator frequency 4 MHz) |

|

||||||

|

|

|

|

||||

|

|

|

|

||||

Low power (standby) modes |

Sleep, stop, CPU intermittent, watch mode |

|

|

||||

|

|

|

|

|

|

||

Process |

|

CMOS |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Mask version without |

|

EVA function |

|

Notes |

|

Mask version |

I2C |

|

|||

|

|

User pin |

|||||

|

|

|

|

built-in interface |

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|||

Emulator dedicated power supply |

|

|

|

Included |

|||

|

|

|

|

|

|

|

|

5

MB90470 Series

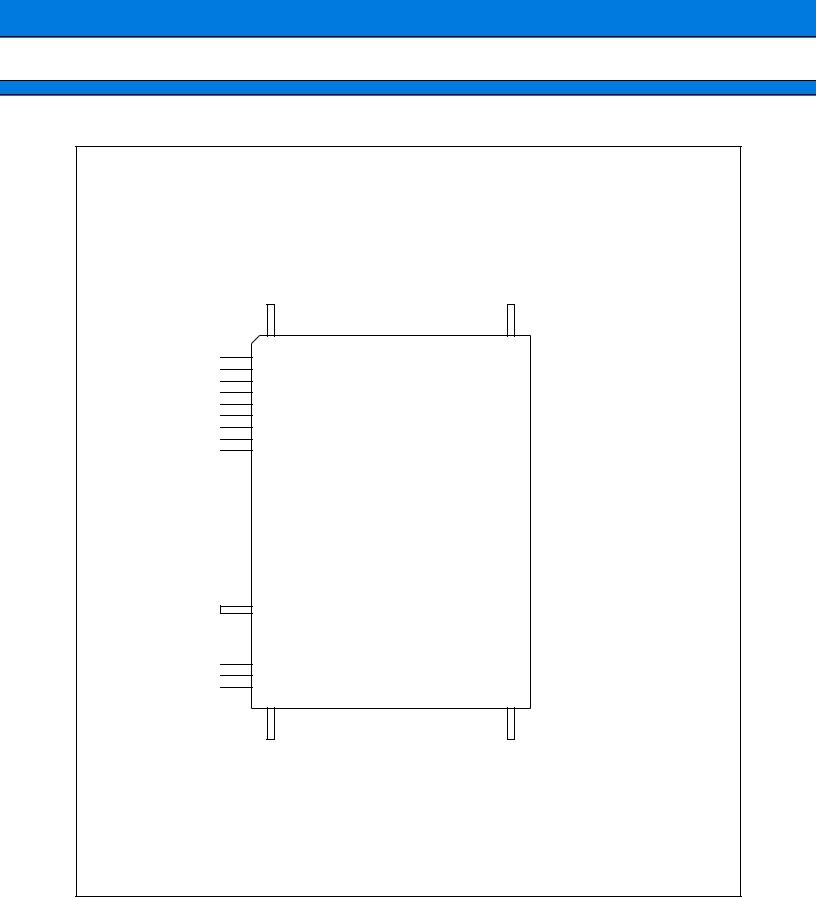

■ PIN ASSIGNMENTS

(TOP VIEW)

P20/A16

P21/A17

P22/A18

P23/A19

P24/A20/PPG0

P25/A21/PPG1

P26/A22/PPG2

P26/A22/PPG2

P27/A23/PPG3

P27/A23/PPG3

P30/A00/AIN0

P31/A01/BIN0

VSS

VSS

P32/A02/ZIN0

P33/A03/AIN1

P34/A04/BIN1

P34/A04/BIN1

P35/A05/ZIN1  P36/A06/PWC0

P36/A06/PWC0

P37/A07/PWC1

P40/A08/SIN2

P40/A08/SIN2

P41/A09/SOT2  P42/A10/SCK2

P42/A10/SCK2

P43/A11/MT00

P44/A12/MT01

P44/A12/MT01

VCC5

P45/A13/EXTC

P46/A14/OUT4

P46/A14/OUT4

P47/A15/OUT5

P47/A15/OUT5

P70/SIN0

P71/SOT0

P72/SCK0

P73/TIN0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

100 P17/AD15/D15

P74/TOT0 31

P16/AD14/D14 |

P15/AD13/D13 |

P14/AD12/D12 |

P13/AD11/D11 |

P12/AD10/D10 |

P11/AD09/D09 |

P10/AD08/D08 |

P07/AD07/D07 |

P06/AD06/D06 |

P05/AD05/D05 |

P04/AD04/D04 |

P03/AD03/D03 |

P02/AD02/D02 |

P01/AD01/D01 |

P00/AD00/D00 |

VCC3 |

X1 X0 |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

99 |

98 |

97 |

96 |

95 |

94 |

93 |

92 |

91 |

90 |

89 |

88 |

87 |

86 |

85 |

84 |

83 |

82 |

|||||||||||||||||||

32 |

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

41 |

42 |

43 |

44 |

45 |

46 |

47 |

48 |

49 |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P75/PWC2 |

P76/SCL |

P77/SDA |

AVCC |

AVRH |

AVSS |

P60/AN0 |

P61/AN1 |

P62/AN2 |

P63/AN3 |

Vss |

P64/AN4 |

P65/AN5 |

P66/AN6 |

P67/AN7 |

P80/IRQ0 |

P81/IRQ1 |

MD0 |

|||||||||||||||||||

81 VSS

MD1 50

80 |

|

X0A |

79 |

|

X1A |

|

||

78 |

|

P57/CLK |

|

||

77 |

|

RST |

|

||

76 |

|

P56/RDY |

|

||

75 |

|

P55/HAK |

|

||

74 |

|

P54/HRQ |

|

||

73 |

|

P53/WRH |

|

||

72 |

|

P52/WRL |

|

||

71 |

|

P51/RD |

|

||

70 |

|

P50/ALE |

|

||

69 |

|

PA3/OUT3 |

|

||

68 |

|

PA2/OUT2 |

|

||

67 |

|

PA1/OUT1 |

|

||

66 |

|

PA0/OUT0 |

|

||

65 |

|

P97/IN1 |

|

||

64 |

|

P96/IN0 |

|

||

63 |

|

P95/PPG5 |

|

||

62 |

|

P94/PPG4 |

|

||

61 |

|

P93/FRCK/ADTG/CS3 |

|

||

60 |

|

P92/SCK1/CS2 |

|

||

|

||

59 |

|

P91/SOT1/CS1 |

|

||

58 |

|

P90/SIN1/CS0 |

|

||

|

||

57 |

|

P87/IRQ7 |

|

||

|

||

56 |

|

P86/IRQ6 |

|

||

|

||

55 |

|

P85/IRQ5 |

|

||

|

||

54 |

|

P84/IRQ4 |

|

||

53 |

|

P83/IRQ3 |

|

||

|

||

52 |

|

P82/IRQ2 |

|

||

|

||

51 |

|

MD2 |

|

||

|

(FPT-100P-M06)

6

MB90470 Series

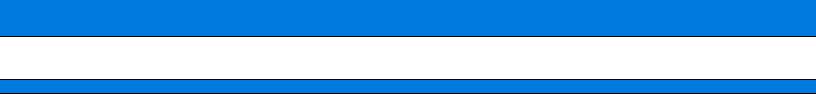

(TOP VIEW)

P22/A18

P23/A19

P24/A20/PPG0

P25/A21/PPG1

P26/A22/PPG2

P27/A23/PPG3

P30/A00/AIN0

P31/A01/BIN0

VSS

P32/A02/ZIN0

P33/A03/AIN1

P34/A04/BIN1

P35/A05/ZIN1

P36/A06/PWC0

P37/A07/PWC1

P40/A08/SIN2

P41/A09/SOT2

P42/A10/SCK2

P43/A11/MT00

P44/A12/MT01 VCC5 P45/A13/EXTC P46/A14/OUT4 P47/A15/OUT5 P70/SIN0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

P21/A17 |

P20/A16 |

P17/AD15/D15 |

P16/AD14/D13 |

P15/AD13/D13 |

P14/AD12/D12 |

P13/AD11/D11 |

P12/AD10/D10 |

P11/AD09/D09 |

P10/AD08/D08 |

P07/AD07/D07 |

P06/AD06/D06 |

P05/AD05/D05 |

P04/AD04/D04 |

P03/AD03/D03 |

P02/AD02/D02 |

P01/AD01/D01 |

P00/AD00/D00 |

VCC3 |

X1 |

X0 |

VSS |

X0A |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 |

99 |

98 |

97 |

96 |

95 |

94 |

93 |

92 |

91 |

90 |

89 |

88 |

87 |

86 |

85 |

84 |

83 |

82 |

81 |

80 |

79 |

78 |

||||||||||||||||||||||||||||

26 |

27 |

28 |

29 |

30 |

31 |

32 |

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

41 |

42 |

43 |

44 |

45 |

46 |

|

47 |

48 |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P71/SOT0 |

P72/SCK0 |

P73/TIN0 |

P74/TOT0 |

P75/PWC2 |

P76/SCL |

P77/SDA |

AVCC |

AVRH |

AVSS |

P60/AN0 |

P61/AN1 |

|

P62/AN2 |

|

P63/AN3 |

VSS |

|

P64/AN4 |

P65/AN5 |

P66/AN6 |

P67/AN7 |

P80/IRQ0 |

P81/IRQ1 |

MD0 |

MD1 |

||||||||||||||||||||

X1A |

P57/CLK |

|

|

|

|

|

|

|

77 |

76 |

|

49 |

50 |

||

|

|

|

|

|

|

|

|

MD2 |

P82/IRQ2 |

||

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

RST

P56/RDY

P55/HAK

P54/HRQ

P53/WRH

P52/WRL

P51/RD

P50/ALE

PA3/OUT3

PA2/OUT2

PA1/OUT1

PA0/OUT0

P97/IN1

P96/IN0

P95/PPG5

P94/PPG4

P93/FRCK/ADTG/CS3

P92/SCK1/CS2

P91/SOT1/CS1

P90/SIN1/CS0

P87/IRQ7

P86/IRQ6

P85/IRQ5

P84/IRQ4

P83/IRQ3

(FPT-100P-M05)

7

MB90470 Series

■ PIN DESCRIPTION

Pin no. |

Pin name |

Circuit |

Description |

||||

LQFP |

QFP |

type |

|||||

|

|

|

|

||||

|

|

|

|

|

|

||

80 |

82 |

|

X0 |

A |

Oscillator pin |

||

|

|

|

|

|

|

||

81 |

83 |

|

X1 |

A |

Oscillator pin |

||

|

|

|

|

|

|

||

78 |

80 |

|

X0A |

A |

32 kHz oscillator pin |

||

|

|

|

|

|

|

||

77 |

79 |

|

X1A |

A |

32 kHz oscillator pin |

||

|

|

|

|

|

|

|

|

75 |

77 |

|

|

|

B |

Reset input pin |

|

RST |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

General purpose input/output ports. Set the pull-up resistance |

|

|

|

P00 to P07 |

|

setting register (RDR0) to add pull-up resistance (RD00-RD07 |

|||

|

|

|

|

|

C |

= “1” ) . (Not valid when set for output) |

|

|

|

|

|

|

|

||

83 to 90 |

85 to 92 |

|

|

|

In multiplex mode, these pins function as external address/ |

||

AD00 to AD07 |

(CMOS) |

||||||

|

|

|

|

|

|

data bus lower input/output pins. |

|

|

|

D00 to D07 |

|

In non-multiplex mode, these pins function as external data |

|||

|

|

|

bus lower output pins. |

||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

General purpose input/output ports. Set the pull-up resistance |

|

|

|

P10 to P17 |

|

setting register (RDR1) to add pull-up resistance (RD10-RD17 |

|||

|

93 to |

|

|

|

C |

= “1” ) . (Not valid when set for output) |

|

|

|

|

|

|

|||

91 to 98 |

|

|

|

In multiplex mode, these pins function as external address/ |

|||

100 |

AD08 to AD15 |

(CMOS) |

|||||

|

data bus higher input/output pins. |

||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

D08 to D15 |

|

In non-multiplex mode, these pins function as external data |

|||

|

|

|

bus higher output pins. |

||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

General purpose input/output ports. In external bus mode, pins |

|

|

|

P20 to P23 |

|

for which the corresponding bit in the external address output |

|||

|

|

|

control register (HACR) is “1” function as the general purpose |

||||

|

|

|

|

|

|

||

99 |

|

|

|

|

|

input/output ports. |

|

|

|

|

|

|

|

||

100 |

1 to 4 |

|

|

|

E |

In multiplex mode, pins for which the corresponding bit in the |

|

1 |

A16 to A19 |

(CMOS/H) |

external address output control register (HACR) is “0” function |

||||

|

|||||||

2 |

|

|

|

|

|

as the upper address output pins (A16 to A19) . |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

In non-multiplex mode, pins for which the corresponding bit in |

|

|

|

A16 to A19 |

|

the external address output control register (HACR) is “0” |

|||

|

|

|

|

|

|

function as the upper address output pins (A16 to A19) . |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

General purpose input/output ports. In external bus mode, pins |

|

|

|

P24 to P27 |

|

for which the corresponding bit in the external address output |

|||

|

|

|

control register (HACR) is “1” function as the general purpose |

||||

|

|

|

|

|

|

||

|

|

|

|

|

|

input/output ports. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

In multiplex mode, pins for which the corresponding bit in the |

|

3 to 6 |

5 to 8 |

A20 to A23 |

external address output control register (HACR) is “0” function |

||||

(CMOS/H) |

|||||||

|

|

|

|

|

as the upper address output pins (A20 to A23) . |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

In non-multiplex mode, pins for which the corresponding bit in |

|

|

|

A20 to A23 |

|

the external address output control register (HACR) is “0” |

|||

|

|

|

|

|

|

function as the upper address output pins (A20 to A23) . |

|

|

|

|

|

|

|||

|

|

PPG0 to PPG3 |

|

PPG timer output pins. |

|||

|

|

|

|

|

|

|

|

(Continued)

LQFP : FPT-100P-M05 package QFP : FPT-100P-M06 package

8

MB90470 Series

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin no. |

Pin name |

Circuit |

Description |

|

|

|

|

|

|

|||

|

LQFP |

QFP |

type |

|

||

|

|

|

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

P30 |

|

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

7 |

9 |

A00 |

E |

In non-multibus bus mode, this pin functions as an external |

|

|

(CMOS/H) |

address pin. |

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

AIN0 |

|

8/16-bit up-down timer input pin. (ch0) |

|

|

|

|

|

|

|

|

|

|

|

P31 |

|

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

8 |

10 |

A01 |

E |

In non-multibus bus mode, this pin functions as an external |

|

|

(CMOS/H) |

address pin. |

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

BIN0 |

|

8/16-bit up-down timer input pin. (ch0) |

|

|

|

|

|

|

|

|

|

|

|

P32 |

|

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

10 |

12 |

A02 |

E |

In non-multibus bus mode, this pin functions as an external |

|

|

(CMOS/H) |

address pin. |

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

ZIN0 |

|

8/16-bit up-down timer input pin. (ch0) |

|

|

|

|

|

|

|

|

|

|

|

P33 |

|

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

11 |

13 |

A03 |

E |

In non-multibus bus mode, this pin functions as an external |

|

|

(CMOS/H) |

address pin. |

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

AIN1 |

|

8/16-bit up-down timer input pin. (ch1) |

|

|

|

|

|

|

|

|

|

|

|

P34 |

|

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

12 |

14 |

A04 |

E |

In non-multibus bus mode, this pin functions as an external |

|

|

(CMOS/H) |

address pin. |

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

BIN1 |

|

8/16-bit up-down timer input pin. (ch1) |

|

|

|

|

|

|

|

|

|

|

|

P35 |

|

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

13 |

15 |

A05 |

E |

In non-multibus bus mode, this pin functions as an external |

|

|

(CMOS/H) |

address pin. |

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

ZIN1 |

|

8/16-bit up-down timer input pin. (ch1) |

|

|

|

|

|

|

|

|

|

|

|

P36, P37 |

|

General purpose input/output ports. |

|

|

|

|

|

|

|

|

|

14 |

16 |

A06, A07 |

E |

In non-multibus bus mode, this pin functions as an external |

|

|

15 |

17 |

(CMOS/H) |

address pin. |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

PWC0, PWC1 |

|

Functions as PWC input pin. |

|

|

|

|

|

|

|

|

|

|

|

P40 |

|

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

16 |

18 |

A08 |

G |

In non-multibus bus mode, this pin functions as an external |

|

|

(CMOS/H) |

address pin. |

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

SIN2 |

|

Single serial I/O input pin |

|

|

|

|

|

|

|

|

|

|

|

P41 |

|

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

17 |

19 |

A09 |

F |

In non-multibus bus mode, this pin functions as an external |

|

|

(CMOS) |

address pin. |

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

SOT2 |

|

Single serial I/O output pin |

|

|

|

|

|

|

|

|

(Continued)

LQFP : FPT-100P-M05 package QFP : FPT-100P-M06 package

9

MB90470 Series

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin no. |

Pin name |

Circuit |

|

|

|

|

|

|

Description |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

LQFP |

QFP |

type |

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

P42 |

|

General purpose input/output port. |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

18 |

20 |

|

A10 |

G |

In non-multibus bus mode, this pin functions as an external |

|

||||||||||||||

|

|

(CMOS/H) |

address pin. |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

SCK2 |

|

Single serial I/O clock input/output pin |

|

|||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

P43, P44 |

|

General purpose input/output ports. |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

19 |

21 |

A11, A12 |

F |

In non-multibus bus mode, this pin functions as an external |

|

|||||||||||||||

|

20 |

22 |

(CMOS) |

address pin. |

|

||||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

MT00, MT01 |

|

PG input pins |

|

|||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

P45 |

|

General purpose input/output ports. |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

22 |

24 |

|

A13 |

G |

In non-multibus bus mode, this pin functions as an external |

|

||||||||||||||

|

|

(CMOS/H) |

address pin. |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

EXTC |

|

PG input pin |

|

|||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

P46, P47 |

|

General purpose input/output ports. |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

23 |

25 |

A14, A15 |

F |

In non-multibus bus mode, this pin functions as an external |

|

|||||||||||||||

|

24 |

26 |

(CMOS) |

address pin. |

|

||||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

OUT4/OUT5 |

|

Output compare event output pins |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

P50 |

|

General purpose input/output port. In external bus mode, this |

|

||||||||||||||

|

|

|

|

D |

pin functions as the ALE pin |

|

|||||||||||||||

|

68 |

70 |

|

|

|

|

|

|

|||||||||||||

|

|

ALE |

(CMOS) |

In external bus mode, this pin functions as the address load |

|

||||||||||||||||

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

enable signal (ALE) pin |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

P51 |

|

General purpose input/output port. In external bus mode, this |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

69 |

71 |

D |

pin functions as the RD pin. |

|

||||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

(CMOS) |

In external bus mode, this pin functions as the read strobe |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

RD |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

output (RD) pin. |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

General purpose input/output port. In external bus mode, this |

|

|||||||||||

|

|

|

|

P52 |

|

pin functions as the |

WRL |

pin when the WRE bit in the EPCR |

|

||||||||||||

|

|

|

|

|

|

|

|

D |

register is set to “1”. |

|

|||||||||||

|

70 |

72 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

In external bus mode, this pin functions as the lower data write |

|

||||||||||||||

|

|

|

|

|

|

(CMOS) |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

strobe output |

(WRL) |

pin. When the WRE bit in the EPCR |

|

|||||||||

|

|

|

|

WRL |

|

||||||||||||||||

|

|

|

|

|

register is set to “0”,this pin functions as a general purpose |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

input/output port. |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

General purpose input/output port. In external bus mode with |

|

|||||||||||

|

|

|

|

P53 |

|

16-bit bus width, this pin functions as the |

WRH |

pin when the |

|

||||||||||||

|

|

|

|

|

|

|

|

D |

WRE bit in the EPCR register is set to “1”. |

|

|||||||||||

|

71 |

73 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

In external bus mode with 16-bit bus width, this pin functions |

|

||||||||||||||

|

|

|

|

|

|

(CMOS) |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

as the higher data write strobe output |

(WRH) |

pin. When the |

|

|||||||||

|

|

|

|

WRH |

|

||||||||||||||||

|

|

|

|

|

WRE bit in the EPCR register is set to “0”,this pin functions as |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

a general purpose input/output port. |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Continued)

LQFP : FPT-100P-M05 package QFP : FPT-100P-M06 package

10

MB90470 Series

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin no. |

Pin name |

Circuit |

|

|

|

Description |

|

||||

|

LQFP |

QFP |

type |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

General purpose input/output port. In external bus mode, this |

|

||||

|

|

|

|

P54 |

|

pin functions as the HRQ pin when the HDE bit in the EPCR |

|

|||||

|

72 |

74 |

|

|

|

D |

register is set to “1”. |

|

||||

|

|

|

|

(CMOS) |

In external bus mode, this pin functions as the hold request |

|

||||||

|

|

|

|

|

|

|

||||||

|

|

|

HRQ |

|

input (HRQ) pin. When the HDE bit in the EPCR register is set |

|

||||||

|

|

|

|

|

|

|

to “0”,this pin functions as a general purpose input/output port. |

|

||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

General purpose input/output port. In external bus mode, this |

|

||||

|

|

|

|

P55 |

|

pin functions as the |

HAK |

pin when the HDE bit in the EPCR |

|

|||

|

|

|

|

|

|

D |

register is set to “1”. |

|

||||

|

73 |

75 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

In external bus mode, this pin functions as the hold acknowl- |

|

|||||||

|

|

|

|

(CMOS) |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

edge output (HAK) pin. When the HDE bit in the EPCR register |

|

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

HAK |

|

|||||||

|

|

|

|

|

is set to “0”,this pin functions as a general purpose input/output |

|

||||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

port. |

|

||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

General purpose input/output port. In external bus mode, this |

|

||||

|

|

|

|

P56 |

|

pin functions as the DRY pin when the RYE bit in the EPCR |

|

|||||

|

74 |

76 |

|

|

|

D |

register is set to “1”. |

|

||||

|

|

|

|

(CMOS) |

In external bus mode, this pin functions as the external ready |

|

||||||

|

|

|

|

|

|

|

||||||

|

|

|

RDY |

|

input (RDY) pin. When the RYE bit in the EPCR register is set |

|

||||||

|

|

|

|

|

|

|

to “0”,this pin functions as a general purpose input/output port. |

|

||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

General purpose input/output port. In external bus mode, this |

|

||||

|

|

|

|

P57 |

|

pin functions as the CLK pin when the CKE bit in the EPCR |

|

|||||

|

|

|

|

|

|

D |

register is set to “1”. |

|

||||

|

76 |

78 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

In external bus mode, this pin functions as the machine cycle |

|

|||||||

|

|

|

|

(CMOS) |

|

|||||||

|

|

|

|

|

|

clock output (CLK) pin. When the CKE bit in the EPCR register |

|

|||||

|

|

|

|

CLK |

|

|

||||||

|

|

|

|

|

is set to “0”,this pin functions as a general purpose input/output |

|

||||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

port. |

|

||||

|

|

|

|

|

|

|

||||||

|

36 to 39 |

38 to 41 |

P60 to P63 |

H |

General purpose input/output ports. |

|

||||||

|

AN0 to AN3 |

(CMOS) |

Analog input pins. |

|

||||||||

|

|

|

|

|||||||||

|

|

|

|

|

|

|

||||||

|

41 to 44 |

43 to 46 |

P64 to P67 |

H |

General purpose input/output ports. |

|

||||||

|

AN4 to AN7 |

(CMOS) |

Analog input pins. |

|

||||||||

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|||||

|

25 |

27 |

|

P70 |

G |

General purpose input/output port. |

|

|||||

|

SIN0 |

(CMOS/H) |

UART data input pin. |

|

||||||||

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|||||

|

26 |

28 |

|

P71 |

F |

General purpose input/output port. |

|

|||||

|

SOT0 |

(CMOS) |

UART data output pin. |

|

||||||||

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|||||

|

27 |

29 |

|

P72 |

G |

General purpose input/output port. |

|

|||||

|

SCK0 |

(CMOS/H) |

UART clock input pin. |

|

||||||||

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|||||

|

28 |

30 |

|

P73 |

G |

General purpose input/output port. |

|

|||||

|

TIN0 |

(CMOS/H) |

16-bit reload timer event input pin. |

|

||||||||

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|||||

|

29 |

31 |

|

P74 |

F |

General purpose input/output port. |

|

|||||

|

TOT0 |

(CMOS) |

16-bit reload timer output pin. |

|

||||||||

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

(Continued)

LQFP : FPT-100P-M05 package QFP : FPT-100P-M06 package

11

MB90470 Series

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin no. |

Pin name |

Circuit |

|

Description |

|

|

|

|

|

|

|

|||

|

LQFP |

QFP |

type |

|

|

||

|

|

|

|

|

|||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

30 |

32 |

P75 |

G |

General purpose input/output port. |

|

|

|

PWC2 |

(CMOS/H) |

PWC input pin. |

|

|||

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

P76 |

I |

General purpose input/output port. |

|

|

|

31 |

33 |

|

|

|

|

|

|

|

2 |

2 |

|

|||

|

SCL |

(NMOS/H) |

|

||||

|

|

|

I C interface data input/output pin. During I C interface |

|

|||

|

|

|

|

|

operation, the port output should be set to High-Z level. |

|

|

|

|

|

|

|

|

|

|

|

|

|

P77 |

I |

General purpose input/output port. |

|

|

|

32 |

34 |

|

|

|

|

|

|

|

2 |

2 |

|

|||

|

SDA |

(NMOS/H) |

|

||||

|

|

|

I |

C interface clock input/output pin. During I C interface |

|

||

|

|

|

|

|

operation, the port output should be set to High-Z level. |

|

|

|

|

|

|

|

|

|

|

|

45 |

47 |

P80, P81 |

E |

General purpose input/output ports. |

|

|

|

46 |

48 |

IRQ0, IRQ1 |

(CMOS/H) |

External interrupt input pins. |

|

|

|

|

|

|

|

|

|

|

|

50 to 55 |

52 to 57 |

P82 to P87 |

E |

General purpose input/output ports. |

|

|

|

IRQ2 to IRQ7 |

(CMOS/H) |

External interrupt input pins. |

|

|||

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

P90 |

E |

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

|

|

56 |

58 |

SIN1 |

Single serial I/O data input pin. |

|

||

|

(CMOS/H) |

|

|||||

|

|

|

CS0 |

|

Chip select 0. |

|

|

|

|

|

|

|

|

|

|

|

|

|

P91 |

D |

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

|

|

57 |

59 |

SOT1 |

Single serial I/O data output pin. |

|

||

|

(CMOS) |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

CS1 |

|

Chip select 1. |

|

|

|

|

|

|

|

|

|

|

|

|

|

P92 |

E |

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

|

|

58 |

60 |

SCK1 |

Single serial I/O clock input/output pin. |

|

||

|

(CMOS/H) |

|

|||||

|

|

|

CS2 |

|

Chip select 2. |

|

|

|

|

|

|

|

|

|

|

|

|

|

P93 |

|

General purpose input/output port. |

|

|

|

|

|

|

|

|

|

|

|

|

|

FRCK |

|

In free run timer operation, this pin functions as the external |

|

|

|

|

|

E |

clock input pin. |

|

||

|

59 |

61 |

|

|

|||

|

ADTG |

(CMOS/H) |

In A/D converter operation, this pin functions as the external |

|

|||

|

|

|

|

||||

|

|

|

|

trigger input pin. |

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

CS3 |

|

Chip select 3. |

|

|

|

|

|

|

|

|

|

|

|

60 |

62 |

P94 |

D |

General purpose input/output port. |

|

|

|

PPG4 |

(CMOS) |

PPG timer output pin. |

|

|||

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

61 |

63 |

P95 |

D |

General purpose input/output port. |

|

|

|

PPG5 |

(CMOS) |

PPG timer output pin. |

|

|||

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

62 |

64 |

P96 |

E |

General purpose input/output port. |

|

|

|

IN0 |

(CMOS/H) |

Functions as input capture ch 0 trigger input. |

|

|||

|

|

|

|

||||

|

|

|

|

|

|

|

|

(Continued)

LQFP : FPT-100P-M05 package QFP : FPT-100P-M06 package

12

MB90470 Series

(Continued)

Pin no. |

Pin name |

Circuit |

Description |

||

|

|

||||

LQFP |

QFP |

type |

|||

|

|

||||

|

|

|

|||

|

|

|

|

|

|

63 |

65 |

P97 |

E |

General purpose input/output port. |

|

IN1 |

(CMOS/H) |

Functions as input capture ch 1 trigger input. |

|||

|

|

||||

|

|

|

|

|

|

64 to 67 |

66 to 69 |

PA0 to PA3 |

D |

General purpose input/output ports. |

|

OUT0 to OUT3 |

(CMOS) |

Output compare event output pins. |

|||

|

|

||||

|

|

|

|

|

|

33 |

35 |

AVCC |

|

A/D converter power supply pin. |

|

|

|

|

|

|

|

34 |

36 |

AVRH |

|

A/D converter external reference power pin. |

|

|

|

|

|

|

|

35 |

37 |

AVSS |

|

A/D converter power supply pin. |

|

|

|

|

|

|

|

47 to 49 |

49 to 51 |

MD0 to MD2 |

J |

Input pins for specifying operating mode. |

|

(CMOS/H) |

|||||

|

|

|

|

|

|

82 |

84 |

VCC3 |

|

3.3 V ± 0.3 V power supply pin (VCC3) . |

|

|

|

|

|

|

|

21 |

23 |

VCC5 |

|

3.3 V ± 0.3 V/5.0 V ± 0.5 V dual power supply pin (VCC5) . |

|

|

|

|

|

|

|

9 |

11 |

|

|

|

|

40 |

42 |

VSS |

Power supply input pins (GND) . |

||

79 |

81 |

|

|

|

|

|

|

|

|

|

|

LQFP : FPT-100P-M05 package QFP : FPT-100P-M06 package

Notes : • For use as a 3.3 V single supply device, apply the same voltage to the VCC3 and VCC5 power supply pins.

•For use with a dual power supply, apply the respective voltages to the VCC3 and VCC5 power supply pins.

•In use with a dual power supply, a total of 32 pins (P20/A16 to P27/A23/PPG3, P30/A00/AIN0 to P37/ A07/PWC1, P40/A08/SIN2 to P47/A15/OUT5 and P70/SIN0 to P77/SDA) can be used in a 5 V interface. Note that all other pins must be used in 3 V interface.

•In use with a dual power supply, it is not possible to turn on only the 5 V or the 3 V power supply independently. Always turn on both power supplies simultaneously. (It is recommended that the 3 V power to the MB90470 series be turned on first.)

13

MB90470 Series

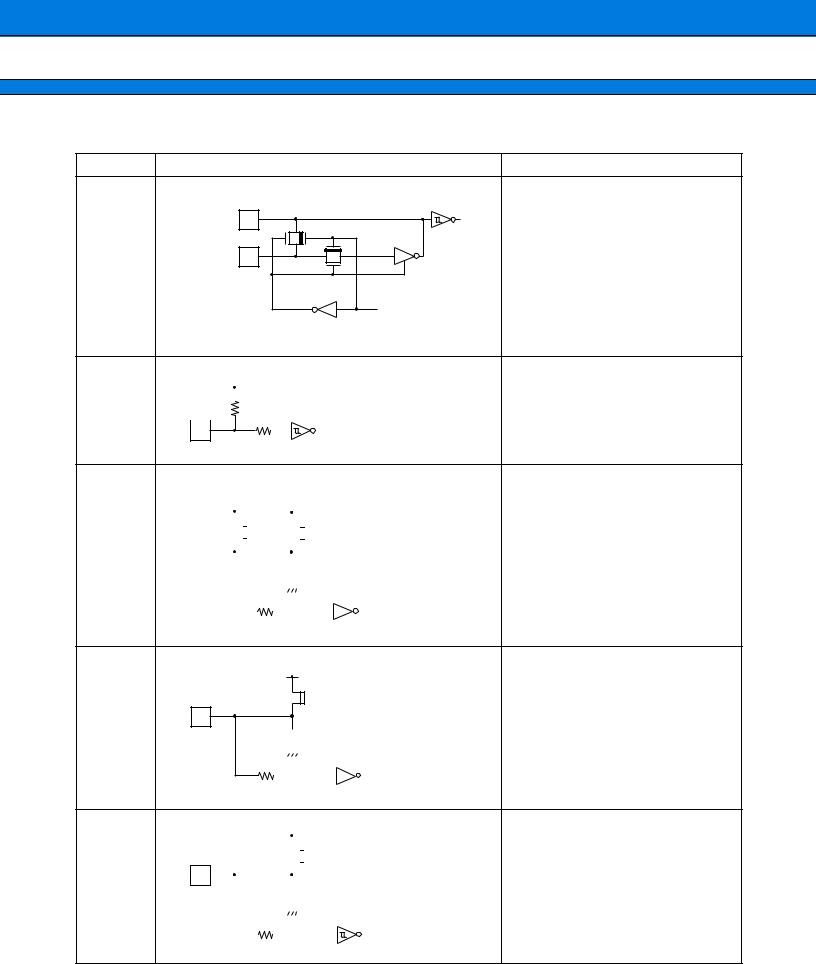

■ I/O CIRCUIT TYPES |

|

|

|

Type |

Circuit |

Remarks |

|

X1, X1A |

|

|

|

|

|

Oscillator feedback resistance : |

|

X0, X0A |

|

X1,X0 |

1 MΩ approx. |

A |

|

X1A,X0A |

10 MΩ approx. |

|

|

||

|

|

Includes standby control |

|

|

|

Standby control |

|

|

|

signal |

|

B |

|

|

|

|

Hysteresis with pull-up resistance |

||

|

|

|

|||||

|

|

HYS |

Input resistance 50 kΩ approx. |

||||

|

|

|

|

|

|

||

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CTL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Includes input pull-up resistance control |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CMOS level input/output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Resistance : 50 kΩ approx. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CMOS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

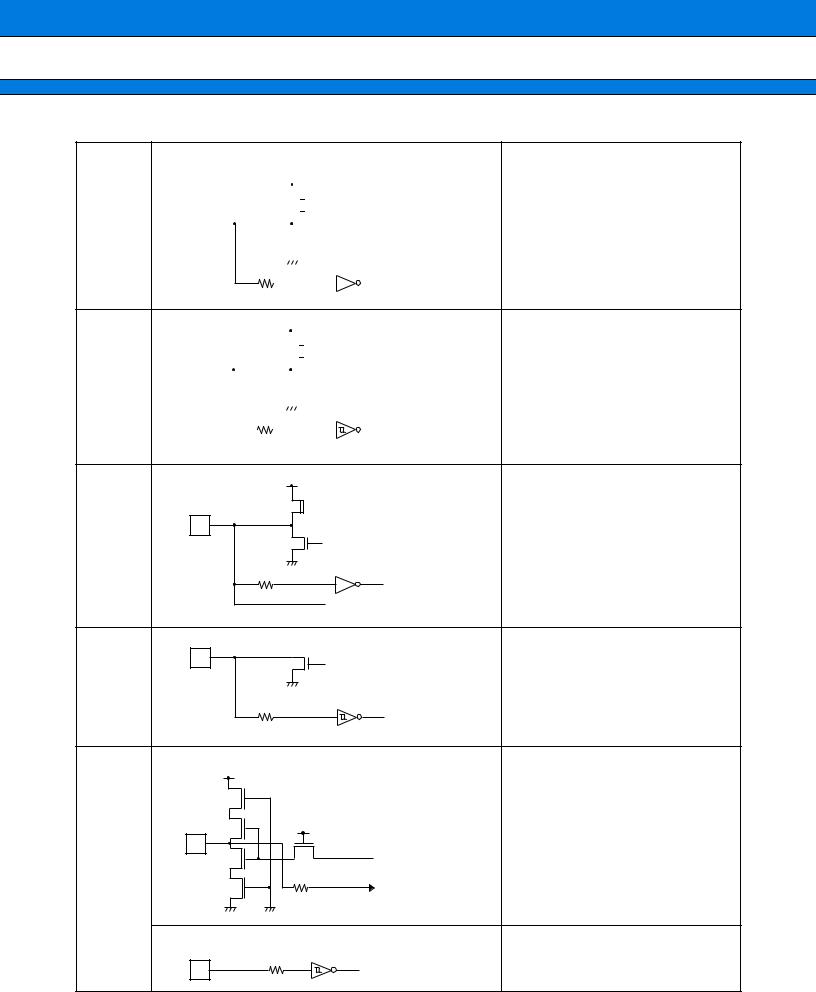

D |

|

|

|

|

CMOS level input/output |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CMOS

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hysteresis input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

CMOS level input/output |

||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CMOS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

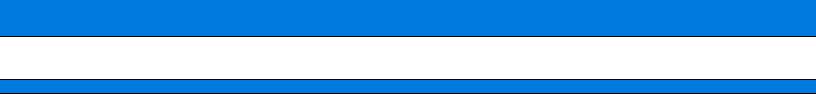

(Continued)

14

MB90470 Series

(Continued)

Type |

|

|

|

|

Circuit |

Remarks |

|||

|

|

|

|

|

|

|

|

Open drain |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F |

|

|

|

|

|

|

|

control signal |

CMOS level input/output |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

CMOS |

Includes open drain control |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Open drain |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

control signal |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CMOS level output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hysteresis input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Includes open drain control |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HYS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|