FUJITSU MB90233, MB90234, MB90P234, MB90W234 DATA SHEET

MB90W234ZFV

|

FUJITSU SEMICONDUCTOR |

|

DS07-13504-2E |

|

|

|

DATA SHEET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16-bit Proprietary Microcontroller

CMOS

F2MC-16F MB90230 Series

MB90233/234/P234/W234

■ DESCRIPTION

The MB90230 series is a member of general-purpose, 16-bit microcontrollers designed for those applications which require high-speed realtimeprocessing, proving to be suitable for various industrial machines, camera and video devices, OA equipment, and for process control. The CPU used in this series is the F2MC*-16F. The instruction set for the F2MC-16F CPU core is designed to be optimized for controller applications while inheriting the AT architecture of the F2MC-16/16H series, allowing a wide range of control tasks to be processed efficiently at high speed.

The peripheral resources integrated in the MB90230 series include: the UART (clock asynchronous/synchronous transfer) × 1 channel, the extended serial I/O interface × 1 channel, the A/D converter (8/10-bit precision) × 8 channels, the D/A converter (8-bit precision) × 2 channels, the level comparator × 1 channel, the external interrupt input × 4 lines, the 8-bit PPG timer (PWM/single-shot function) × 1 channel, the 8-bit PWM controller × 6 channels, the 16-bit free run timer × 1 channel, the input capture unit × 4 channels, the output compare unit × 6 channels, and the serial E2PROM interface.

*: F2MC stands for FUJITSU Flexible Microcontroller.

■FEATURES

F2MC-16F CPU block

•Minimum execution time: 62.5 ns (at machine clock frequency of 16 MHz)

•Instruction set optimized for controllers

Various data types supported (bit, byte, word, and long-word) Extended addressing modes: 23 types

High coding efficiency

Higher-precision operation enhanced by a 32-bit accumulator Signed multiplication and division instructions

(Continued)

■ PACKAGE

100-pin Plastic LQFP |

100-pin Ceramic LQFP |

(FPT-100P-M05) |

(FPT-100C-C01) |

MB90230 Series

(Continued)

•Enhanced instructions applicable to high-level language (C) and multitasking System stack pointer

Enhanced pointer-indirect instructions Barrel shift instructions

•Increased execution speed: 8-byte instruction queue

•8-level, 32-factor powerful interrupt service functions

•Automatic transfer function independent of the CPU (EI2OS)

•General-purpose ports: Up to 84 lines

Ports with input pull-up resistor available: 24 lines Ports with output open-drain available: 9 lines

Peripheral blocks

• ROM:48 Kbytes (MB90233)

96 Kbytes (MB90234)

EPROM: 96 Kbytes (MB90W234)

One-time PROM: 96 Kbytes (MB90P234)

• RAM: 2 Kbytes (MB90233)

3 Kbytes (MB90234/W234/P234)

•PWM control circuit: (simple 8 bits): 6 channels

•Serial interface UART: 1 channel

Extended serial I/O interface Switchable I/O port: 1 channel

Communication prescaler (Source clock generator for the UART, serial I/O interface, CKOT, and level comparator): 1 channel

•Serial E2PROM interface: 1 channel

•A/D converter with 8/10-bit resolution: input 8 channels

•Level comparator: 1 channel 4-bit D/A converter integrated

•D/A converter with 8-bit resolution: 2 channels 8-bit PPG timer: 1 channel

•Input/output timer

16-bit free run timer: 1 channel

16-bit output compare unit: 6 channels

16-bit input capture unit: 4 channels

•18-bit timebase timer

•Watchdog timer function

•Standby modes Sleep mode Stop mode

2

MB90230 Series

■ PRODUCT LINEUP

Part number |

MB90233 |

|

NB90234 |

|

MB90P234 |

|

MB90W234 |

|

MB90V230 |

Parameter |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

Classification |

Mask ROM products |

|

One-time PROM |

|

EPROM model |

|

Evaluation |

||

|

|

model |

|

|

model |

||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

ROM size |

48 Kbytes |

|

96 Kbytes |

|

96 Kbytes |

|

96 Kbytes |

|

— |

|

|

|

|

|

|

|

|

|

|

RAM size |

2 Kbytes |

|

3 Kbytes |

|

3 Kbytes |

|

3 Kbytes |

|

4 Kbytes |

|

|

|

|

|

|

|

|

|

|

CPU functions |

|

Number of instructions: 420 |

|

|

|

||||

|

|

Instruction bit length: 8 or 16 bits |

|

|

|

||||

|

|

Instruction length: 1 to 7 bytes |

|

|

|

||||

|

|

Data bit length: 1, 4, 8, 16, or 32 bits |

|

|

|

||||

|

|

Minimum execution time: 62.5 ns at 16 MHz (internal) |

|

||||||

|

|

|

|

|

|

|

|

|

|

Ports |

|

Up to 84 lines |

|

|

|

|

|

|

|

|

|

I/O ports (CMOS): 51 |

|

|

|

||||

|

|

I/O ports (CMOS) with pull-up resistor available: 24 |

|

||||||

|

|

I/O ports (open-drain): 9 |

|

|

|

||||

|

|

|

|

|

|||||

UART |

|

|

Number of channels: 1 (switchable I/O) |

|

|||||

|

Clock synchronous communication (2404 to 38460 bps, full-duplex double buffering) |

||||||||

|

Clock asynchronous communication (500K to 5M bps, full-duplex double buffering) |

||||||||

|

|

|

|

|

|

|

|

||

Serial interface |

|

|

|

Number of channels: 1 |

|

|

|

||

|

|

|

Internal or external clock mode |

|

|||||

|

Clock synchronous transfer (62.5 kHz to 1 MHz, “LSB first” or “MSB first” transfer) |

||||||||

|

|

|

|

|

|||||

A/D converter |

|

|

Resolution: 10 or 8 bits, Number of input lines: 4 |

|

|||||

|

Single conversion mode (conversion for a specified input channel) |

||||||||

|

Scan conversion mode (continuous conversion for specified consecutive channels) |

||||||||

|

Continuous conversion mode (repeated conversion for a specified channel) |

||||||||

|

|

|

Stop conversion mode (periodical conversion) |

|

|||||

|

|

|

|

|

|||||

D/A converter |

|

|

Resolution: 8 bits, Number of output pins: 2 |

|

|||||

|

|

|

|

|

|

|

|

|

|

Level |

|

|

Comparison to internal D/A converter (4-bit resolution) |

|

|||||

comparator |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

PWM |

|

|

|

Number of channels: 6 |

|

|

|

||

|

|

8-bit PWM control circuit (operation of 1×φ, 2×φ, 16×φ, 32×φ) |

|

||||||

|

|

|

|

|

|||||

PPG timer |

|

|

Number of channels: 1 channel with 8-bit resolution |

|

|||||

|

PWM function: Continuous output of pulse synchronous to trigger |

||||||||

|

|

|

Single-shot function: Output of single pulse by trigger |

|

|||||

|

|

|

|

|

|

|

|

||

Serial E2PROM |

|

|

|

Number of channels: 1 |

|

|

|

||

interface |

|

|

|

Instruction code (NS type) |

|

||||

|

Variable address length: 8 to 11 bits (with address increment function) |

||||||||

|

|

|

Variable data length: 8 or 16 bits |

|

|||||

|

|

|

|

|

|

|

|

||

Timer |

|

|

|

Number of channels: 6 |

|

|

|

||

|

16-bit reload timer operation (operation clock cycle of 0.25 µs to 1.05 s) |

||||||||

|

|

|

|

|

|

|

|

||

Free run timer |

|

|

|

Number of channels: 1 |

|

|

|

||

|

|

|

16-bit input capture unit: 4 channels |

|

|||||

|

|

|

16-bit output compare unit: 6 channels |

|

|||||

|

|

|

|

|

|

|

|

|

|

External interrupt |

|

|

|

Number of input pins: 4 |

|

||||

input |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Standby mode |

|

|

|

Stop mode and sleep mode |

|

||||

|

|

|

|

|

|

|

|||

Package |

|

|

FPT-100P-M05 |

|

FPT-100C-C01 |

|

PGA256-A02 |

||

|

|

|

|

|

|

|

|

|

|

3

MB90230 Series

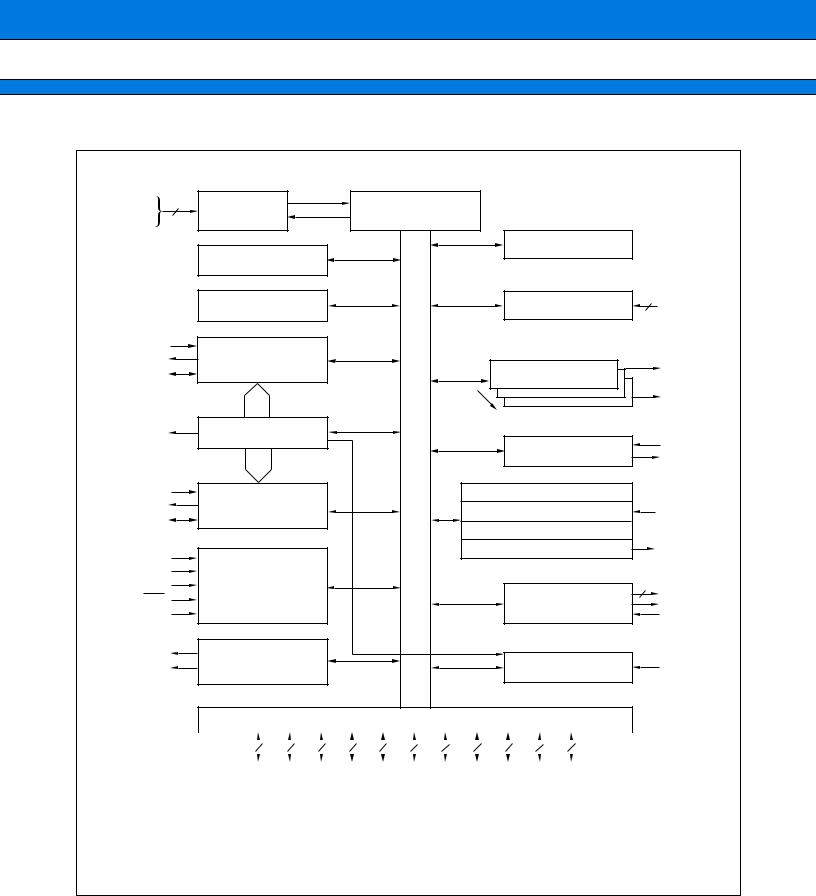

■ PIN ASSIGNMENT

(TOP VIEW)

|

|

|

|

|

P21/A01 |

P20/A00 |

P17/D15 |

P16/D14 |

P15/D13 |

P14/D12 |

P13/D11 |

P12/D10 |

P11/D09 |

P10/D08 |

P07/D07 |

P06/D06 |

P05/D05 |

P04/D04 |

P03/D03 |

P02/D02 |

P01/D01 |

P00/D00 |

VCC |

X1 |

X0 |

VSS |

P57 |

|

P56/RD |

|

P55/WRL |

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 |

99 |

98 |

97 |

96 |

95 |

94 |

93 |

92 |

91 |

90 |

89 |

88 |

87 |

86 |

85 |

84 |

83 |

82 |

81 |

80 |

79 |

78 |

77 |

|

76 |

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||

|

P22/A02 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

75 |

|

|

|

RST |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P23/A03 |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74 |

|

|

|

P54/WRH |

|||||

|

P24/A04 |

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

73 |

|

|

|

P53/HRQ |

|||||

|

P25/A05 |

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

72 |

|

|

|

P52/HAK |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P26/A06 |

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

71 |

|

|

|

P51/RDY |

|||||

|

P27/A07 |

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

70 |

|

|

|

P50/CLK |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P30/A08 |

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

69 |

|

|

|

PA5/SCK2 |

|||||

|

P31/A09 |

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

68 |

|

|

|

PA4/SOT2 |

|||||

|

|

VSS |

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

67 |

|

|

|

PA3/SIN2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P32/A10 |

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

66 |

|

|

|

PA2/SCK1 |

|||||

|

P33/A11 |

|

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

65 |

|

|

|

PA1/SOT1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P34/A12 |

|

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64 |

|

|

|

PA0/SIN1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P35/A13 |

|

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

63 |

|

|

|

P96/SCK0 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P36/A14 |

|

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

62 |

|

|

|

P95/SOT0 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P37/A15 |

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

61 |

|

|

|

P94/SIN0 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

PWM0/P40/A16 |

|

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

|

|

|

P93/IN3/CKOT |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

PWM1/P41/A17 |

|

|

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

59 |

|

|

|

P92/IN2 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

PWM2/P42/A18 |

|

|

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

58 |

|

|

|

P91/IN1 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

PWM3/P43/A19 |

|

|

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

|

|

|

P90/IN0 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

PWM4/P44/A20 |

|

|

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

56 |

|

|

|

P87/OUT5 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

VCC |

|

|

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

55 |

|

|

|

P86/OUT4 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

PWM5/P45/A21 |

|

|

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

54 |

|

|

|

P85/OUT3 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

TRG/P46/A22 |

|

|

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

53 |

|

|

|

P84/OUT2 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

PPG/P47/A23 |

|

|

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

|

|

|

P83/OUT1/INT3 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

|

|

|

P82/OUT0/INT2 |

||||

|

ATG/P70 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

26 |

27 |

28 |

29 |

30 |

31 |

32 |

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

41 |

42 |

43 |

44 |

45 |

46 |

47 |

48 |

49 |

|

50 |

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P71/EDI |

P72/EDO |

P73/ESK |

P74/ECS |

P75/DA0 |

P76/DA1 |

AVCC |

AVRH |

AVRL |

AVSS |

P60/AN0 |

P61/AN1 |

P62/AN2 |

|

P63/AN3 |

VSS |

|

P64/AN4 |

|

P65/AN5 |

|

P66/AN6 |

|

P67/AN7/CMP |

|

P80/INT0 |

P81/INT1 |

|

MD0 |

MD1 |

|

MD2 |

|

HST |

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||

(FPT-100P-M05) (FPT-100C-C01)

4

MB90230 Series

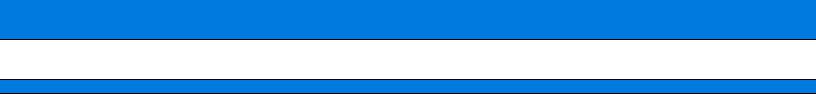

■ PIN DESCRIPTION

Pin no. |

Pin name |

Circuit |

|

Function |

type |

|

|||

|

|

|

|

|

|

|

|

|

|

80 |

X0 |

A |

|

Oscillator pins |

|

|

|

|

|

81 |

X1 |

|

|

|

|

|

|

|

|

82 |

VCC |

— |

|

Power supply pin |

|

|

|

|

|

83 to 90 |

P00 to P07 |

G |

|

General-purpose I/O port |

|

|

|

|

An input pull-up resistor can be added to the port by setting the |

|

|

|

|

pull-up resistor setting register. |

|

|

|

|

These pins serve as D00 to D07 pins in bus modes other than the |

|

|

|

|

single-chip mode. |

|

|

|

|

|

|

D00 to D07 |

|

|

I/O pins for the lower eight bits of the external data bus. |

|

|

|

|

These pins are enabled in an external-bus enabled mode. |

|

|

|

|

|

91 to 98 |

P10 to P17 |

G |

|

General-purpose I/O port |

|

|

|

|

An input pull-up resistor can be added to the port by setting the pull-up |

|

|

|

|

resistor setting register. |

|

|

|

|

These pins are enabled in the single-chip mode with the external-bus |

|

|

|

|

enabled and the 8-bit data bus specified. |

|

|

|

|

|

|

D08 to D15 |

|

|

I/O pins for the upper eight bits of the external data bus |

|

|

|

|

These pins are enabled in an external-bus enabled mode with the 16- |

|

|

|

|

bit data bus specified. |

|

|

|

|

|

99, 100 |

P20 to P27 |

G |

|

General-purpose I/O port |

1 to 6 |

|

|

|

An input pull-up resistor can be added to the port by setting the |

|

|

|

|

pull-up resistor setting register. |

|

|

|

|

These pins are enabled in the single-chip mode. |

|

|

|

|

|

|

A00 to A07 |

|

|

I/O pins for the lower eight bits of the external data bus |

|

|

|

|

These pins are enabled in an external-bus enabled mode. |

|

|

|

|

|

7, 8 |

P30, P31 |

E |

|

General-purpose I/O port |

|

|

|

|

This port is enabled in the single-chip mode or when the middle |

|

|

|

|

address control register setting is “port.” |

|

|

|

|

|

|

A08, A09 |

|

|

I/O pins for the middle eight bits of the external data bus |

|

|

|

|

These pins are enabled in an external-bus enabled mode when the |

|

|

|

|

middle address control register setting is “address.” |

|

|

|

|

|

9 |

VSS |

— |

|

Power supply pin |

|

|

|

|

|

10 to 15 |

P32 to P37 |

E |

|

General-purpose I/O port |

|

|

|

|

This port is enabled in the single-chip mode or when the middle |

|

|

|

|

address control register setting is “port.” |

|

|

|

|

|

|

A10 to A15 |

|

|

I/O pins for the middle eight bits of the external data bus |

|

|

|

|

These pins are enabled in an external-bus enabled mode when the |

|

|

|

|

middle address control register setting is “address.” |

|

|

|

|

|

|

|

|

|

(Continued) |

5

MB90230 Series

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin no. |

Pin name |

Circuit |

|

Function |

|

|

type |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

P40 |

E |

|

General-purpose I/O port |

|

|

|

|

|

|

This port is enabled in the single-chip mode or when the upper |

|

|

|

|

|

|

address control register setting is “port.” |

|

|

|

|

|

|

|

|

|

|

A16 |

|

|

Output pin for external address A16 |

|

|

|

|

|

|

This pin is enabled in the external-bus enabled mode with the upper |

|

|

|

|

|

|

address control register set to “address.” |

|

|

|

|

|

|

|

|

|

|

PWM0 |

|

|

This pin serves as the output pin for 8-bit PWM0 |

|

|

|

|

|

|

The pin is enabled for output by the control status register. |

|

|

|

|

|

|

|

|

|

17 |

P41 |

E |

|

General-purpose I/O port |

|

|

|

|

|

|

This port is enabled in the single-chip mode or when the upper |

|

|

|

|

|

|

address control register setting is “port.” |

|

|

|

|

|

|

|

|

|

|

A17 |

|

|

Output pin for external address A17 |

|

|

|

|

|

|

This pin is enabled in the external-bus enabled mode with the upper |

|

|

|

|

|

|

address control register set to “address.” |

|

|

|

|

|

|

|

|

|

|

PWM1 |

|

|

This pin serves as the output pin for 8-bit PWM1. |

|

|

|

|

|

|

The pin is enabled for output by the control status register. |

|

|

|

|

|

|

|

|

|

18 |

P42 |

E |

|

General-purpose I/O port |

|

|

|

|

|

|

This port is enabled in the single-chip mode or when the upper |

|

|

|

|

|

|

address control register setting is “port.” |

|

|

|

|

|

|

|

|

|

|

A18 |

|

|

Output pin for external address A18 |

|

|

|

|

|

|

This pin is enabled in the external-bus enabled mode with the upper |

|

|

|

|

|

|

address control register set to “address.” |

|

|

|

|

|

|

|

|

|

|

PWM2 |

|

|

This pin serves as the output pin for 8-bit PWM2. |

|

|

|

|

|

|

This pin is enabled for output by the control status register. |

|

|

|

|

|

|

|

|

|

19 |

P43 |

E |

|

General-purpose I/O port |

|

|

|

|

|

|

This port is enabled in the single-chip mode or when the upper |

|

|

|

|

|

|

address control register setting is “port.” |

|

|

|

|

|

|

|

|

|

|

A19 |

|

|

Output pin for external address A19 |

|

|

|

|

|

|

This pin is enabled in the external-bus enabled mode with the upper |

|

|

|

|

|

|

address control register set to “address.” |

|

|

|

|

|

|

|

|

|

|

PWM3 |

|

|

This pin serves as the output pin for 8-bit PWM3. |

|

|

|

|

|

|

This pin is enabled for output by the control status register. |

|

|

|

|

|

|

|

|

|

20 |

P44 |

E |

|

General-purpose I/O port |

|

|

|

|

|

|

This port is enabled in the single-chip mode or when the upper |

|

|

|

|

|

|

address control register setting is “port.” |

|

|

|

|

|

|

|

|

|

|

A20 |

|

|

Output pin for external address A20 |

|

|

|

|

|

|

This pin is enabled in the external-bus enabled mode with the upper |

|

|

|

|

|

|

address control register set to “address.” |

|

|

|

|

|

|

|

|

|

|

PWM4 |

|

|

This pin serves as the output pin for 8-bit PWM4. |

|

|

|

|

|

|

The pin is enabled for output by the control status register. |

|

|

|

|

|

|

|

|

|

21 |

VCC |

— |

|

Power supply pin |

|

|

|

|

|

|

|

|

(Continued)

6

MB90230 Series

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin no. |

|

Pin name |

Circuit |

Function |

|

|

|

|

type |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22 |

|

P45 |

E |

General-purpose I/O port |

|

|

|

|

|

|

|

|

This port is enabled in the single-chip mode or when the upper |

|

|

|

|

|

|

|

address control register setting is “port.” |

|

|

|

|

|

|

|

|

|

|

|

|

A21 |

|

Output pin for external address A21 |

|

|

|

|

|

|

|

|

This pin is enabled in the external-bus enabled mode with the upper |

|

|

|

|

|

|

|

address control register set to “address.” |

|

|

|

|

|

|

|

|

|

|

|

|

PWM5 |

|

This pin serves as the output pin for 8-bit PWM5. |

|

|

|

|

|

|

|

|

The pin is enabled for output by the control status register. |

|

|

|

|

|

|

|

|

|

|

23 |

|

P46 |

L*1 |

General-purpose I/O port |

|

|

|

|

|

|

|

|

This port is enabled in the single-chip mode or when the upper |

|

|

|

|

|

|

|

address control register setting is “port.” |

|

|

|

|

|

|

|

|

|

|

|

|

A22 |

|

Output pin for external address A22 |

|

|

|

|

|

|

|

|

This pin is enabled in the external-bus enabled mode with the upper |

|

|

|

|

|

|

|

address control register set to “address.” |

|

|

|

|

|

|

|

|

|

|

|

|

TRG |

|

This pin serves as the external trigger pin for the 8-bit PPG timer |

|

|

|

|

|

|

|

|

The pin is enabled for triggering by the control status register. |

|

|

|

|

|

|

|

|

|

|

24 |

|

P47 |

E |

General-purpose I/O port |

|

|

|

|

|

|

|

|

This port is enabled in the single-chip mode or when the upper |

|

|

|

|

|

|

|

address control register setting is “port.” |

|

|

|

|

|

|

|

|

|

|

|

|

A23 |

|

Output pin for external address A23 |

|

|

|

|

|

|

|

|

This pin is enabled in the external-bus enabled mode with the upper |

|

|

|

|

|

|

|

address control register set to “address.” |

|

|

|

|

|

|

|

|

|

|

|

|

PPG |

|

This pin serves as the output pin for the 8-bit PPG timer. |

|

|

|

|

|

|

|

|

The pin is enabled for output by the control status register. |

|

|

|

|

|

|

|

|

|

|

25 |

|

P70 |

L*1 |

General-purpose I/O port |

|

|

|

|

|

|

|

|

External trigger input pin for the A/D converter |

|

|

|

|

ATG |

|

|||

|

|

|

|

|

|

This pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

26 |

|

P71 |

F |

General-purpose I/O port |

|

|

|

|

|

|

|

|

|

|

|

|

|

EDI |

|

Data input pin for the serial EEPROM interface |

|

|

|

|

|

|

|

|

This pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

27 |

|

P72 |

E |

General-purpose I/O port |

|

|

|

|

|

|

|

|

|

|

|

|

|

EDO |

|

Data output pin for the serial EEPROM interface |

|

|

|

|

|

|

|

|

This pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

28 |

|

P73 |

E |

General-purpose I/O port |

|

|

|

|

|

|

|

|

|

|

|

|

|

ESK |

|

Clock output pin for the serial EEPROM interface |

|

|

|

|

|

|

|

|

This pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

29 |

|

P74 |

E |

General-purpose I/O port |

|

|

|

|

|

|

|

|

|

|

|

|

|

ECS |

|

Chip select signal output pin for the serial EEPROM interface |

|

|

|

|

|

|

|

|

This pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Continued) |

|

7

MB90230 Series

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin no. |

Pin name |

Circuit |

|

Function |

|

|

type |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

30, 31 |

P75, P76 |

K |

|

General-purpose I/O port |

|

|

|

|

|

|

|

|

|

|

DA0 |

|

|

This pin serves as the D/A converter output pin. |

|

|

|

DA1 |

|

|

The pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

32 |

AVCC |

— |

|

A/D converter power supply pin |

|

|

|

|

|

|

|

|

|

33 |

AVRH |

— |

|

“H” reference power supply pin for the A/D converter |

|

|

|

|

|

|

|

|

|

34 |

AVRL |

— |

|

“L” reference power supply pin for the A/D converter |

|

|

|

|

|

|

|

|

|

35 |

AVSS |

— |

|

A/D converter power pin (GND) |

|

|

|

|

|

|

|

|

|

36 to 39 |

P60 to P63 |

J |

|

General-purpose I/O port |

|

|

|

|

|

|

This port is enabled when the analog input enable register setting is |

|

|

|

|

|

|

“port.” |

|

|

|

|

|

|

|

|

|

|

AN0 to AN3 |

|

|

A/D converter analog input pins |

|

|

|

|

|

|

These pins are enabled when the analog input enable register setting |

|

|

|

|

|

|

is “analog input.” |

|

|

|

|

|

|

|

|

|

40 |

VSS |

— |

|

Power pin (GND) |

|

|

|

|

|

|

|

|

|

41 to 43 |

P64 to P66 |

J |

|

General-purpose I/O port |

|

|

|

|

|

|

This port is enabled when the analog input enable register setting is |

|

|

|

|

|

|

“port.” |

|

|

|

|

|

|

|

|

|

|

AN4 to AN6 |

|

|

A/D converter analog input pins |

|

|

|

|

|

|

These pins are enabled when the analog input enable register setting |

|

|

|

|

|

|

is “analog input.” |

|

|

|

|

|

|

|

|

|

44 |

P67 |

J |

|

General-purpose I/O port |

|

|

|

|

|

|

This port is enabled when the analog input enable register setting is |

|

|

|

|

|

|

“port.” |

|

|

|

|

|

|

|

|

|

|

AN7 |

|

|

A/D converter analog input pin |

|

|

|

|

|

|

This pin is enabled when the analog input enable register setting is |

|

|

|

|

|

|

“analog input.” |

|

|

|

|

|

|

|

|

|

|

CMP |

|

|

Comparator input pin |

|

|

|

|

|

|

|

|

|

45 |

P80 |

L*2 |

|

General-purpose I/O port |

|

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

|

|

|

|

|

INT0 |

|

|

External interrupt request input 0 |

|

|

|

|

|

|

Since this pin serves for interrupt request as required when external |

|

|

|

|

|

|

interrupt is enabled, other outputs must be off unless used |

|

|

|

|

|

|

intentionally. |

|

|

|

|

|

|

|

|

|

46 |

P81 |

L*2 |

|

General-purpose I/O port |

|

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

|

|

|

|

|

INT1 |

|

|

External interrupt request input 1 |

|

|

|

|

|

|

Since this pin serves for interrupt request as required when external |

|

|

|

|

|

|

interrupt is enabled, other outputs must be off unless used |

|

|

|

|

|

|

intentionally. |

|

|

|

|

|

|

|

|

|

47 |

MD0 |

C |

|

Mode pin |

|

|

|

|

|

|

This pin must be fixed to VCC or VSS. |

|

|

|

|

|

|

|

|

|

48 |

MD1 |

C |

|

Mode pin |

|

|

|

|

|

|

This pin must be fixed to VCC or VSS. |

|

|

|

|

|

|

|

|

|

|

|

|

|

(Continued) |

|

8

MB90230 Series

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin no. |

|

Pin name |

Circuit |

Function |

|

|

|

|

type |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

49 |

|

MD2 |

C |

Mode pin |

|

|

|

|

|

|

|

|

This pin must be fixed to VSS. |

|

|

|

|

|

|

|

|

|

|

50 |

|

|

|

D |

Hardware standby input pin |

|

|

HST |

||||||

|

|

|

|

|

|

|

|

|

51, 52 |

|

P82, P83 |

L*2 |

General-purpose I/O port |

|

|

|

|

|

OUT0, |

|

Output compare output pins |

|

|

|

|

|

OUT1 |

|

These pins function when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

|

|

|

INT2, |

|

External interrupt request inputs 2 and 3. |

|

|

|

|

|

INT3 |

|

Since these pins serve for interrupt request as required when external |

|

|

|

|

|

|

|

|

interrupt is enabled, other outputs must be off unless used |

|

|

|

|

|

|

|

intentionally. |

|

|

|

|

|

|

|

||

|

53 to 56 |

P84 to P87 |

E |

General-purpose I/O port |

|

||

|

|

|

|

|

|

This pin is always enabled. |

|

|

|

|

|

|

|

|

|

|

|

|

OUT2 to OUT5 |

|

Output compare output pins |

|

|

|

|

|

|

|

|

These pins function when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

57 to 59 |

|

P90 to P92 |

L*1 |

General-purpose I/O port |

|

|

|

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

|

|

|

|

|

|

|

IN0 to IN2 |

|

Input capture edge input pins |

|

|

|

|

|

|

|

|

These pins function when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

60 |

|

P93 |

L*1 |

General-purpose I/O port |

|

|

|

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

|

|

|

|

|

|

|

IN3 |

|

Input capture edge input pin |

|

|

|

|

|

|

|

|

This pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

|

|

CKOT |

|

Prescaler output pin |

|

|

|

|

|

|

|

|

This pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

61 |

|

P94 |

I |

General-purpose I/O port |

|

|

|

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

|

|

The port serves as an open-drain output depending on the open-drain |

|

|

|

|

|

|

|

setting register. |

|

|

|

|

|

|

|

|

|

|

|

|

SIN0 |

|

Serial data input pin for the UART |

|

|

|

|

|

|

|

|

This pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

62 |

|

P95 |

H |

General-purpose I/O port |

|

|

|

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

|

|

The port serves as an open-drain output depending on the open-drain |

|

|

|

|

|

|

|

setting register. |

|

|

|

|

|

|

|

|

|

|

|

|

SOT0 |

|

Serial data output pin for the UART |

|

|

|

|

|

|

|

|

This pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

63 |

|

P96 |

I |

General-purpose I/O port |

|

|

|

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

|

|

The port serves as an open-drain output depending on the open-drain |

|

|

|

|

|

|

|

setting register. |

|

|

|

|

|

|

|

|

|

|

|

|

SCK0 |

|

UART clock output pin |

|

|

|

|

|

|

|

|

This pin functions when enabled by the control status register. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Continued) |

|

9

MB90230 Series

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin no. |

Pin name |

Circuit |

Function |

|

|

type |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

64 |

PA0 |

I |

General-purpose I/O port |

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

The port serves as an open-drain output depending on the open-drain |

|

|

|

|

|

setting register. |

|

|

|

|

|

|

|

|

|

SIN1 |

|

Serial data input pin for the extended serial I/O interface |

|

|

|

|

|

This pin functions when enabled by the control status register and by |

|

|

|

|

|

the serial port switching register. |

|

|

|

|

|

|

|

|

65 |

PA1 |

H |

General-purpose I/O port |

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

The port serves as an open-drain output depending on the open-drain |

|

|

|

|

|

setting register. |

|

|

|

|

|

|

|

|

|

SOT1 |

|

Serial data output pin for the extended serial I/O interface |

|

|

|

|

|

This pin functions when enabled by the control status register and by |

|

|

|

|

|

the serial port switching register. |

|

|

|

|

|

|

|

|

66 |

PA2 |

I |

General-purpose I/O port |

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

The port serves as an open-drain output depending on the open-drain |

|

|

|

|

|

setting register. |

|

|

|

|

|

|

|

|

|

SCK1 |

|

Clock output pin for the extended serial I/O interface |

|

|

|

|

|

This pin functions when enabled by the control status register and by |

|

|

|

|

|

the serial port switching register. |

|

|

|

|

|

|

|

|

67 |

PA3 |

I |

General-purpose I/O port |

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

The port serves as an open-drain output depending on the open-drain |

|

|

|

|

|

setting register. |

|

|

|

|

|

|

|

|

|

SIN2 |

|

Serial data input pin for the extended serial I/O interface |

|

|

|

|

|

This pin functions when enabled by the control status register and by |

|

|

|

|

|

the serial port switching register. |

|

|

|

|

|

|

|

|

68 |

PA4 |

H |

General-purpose I/O port |

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

The port serves as an open-drain output depending on the open-drain |

|

|

|

|

|

setting register. |

|

|

|

|

|

|

|

|

|

SOT2 |

|

Serial data output pin for the extended serial I/O interface |

|

|

|

|

|

This pin functions when enabled by the control status register and by |

|

|

|

|

|

the serial port switching register. |

|

|

|

|

|

|

|

|

69 |

PA5 |

I |

General-purpose I/O port |

|

|

|

|

|

This port is always enabled. |

|

|

|

|

|

The port serves as an open-drain output depending on the open-drain |

|

|

|

|

|

setting register. |

|

|

|

|

|

|

|

|

|

SCK2 |

|

Clock output pin for the extended serial I/O interface |

|

|

|

|

|

This pin functions when enabled by the control status register and by |

|

|

|

|

|

the serial port switching register. |

|

|

|

|

|

The pin is a general-purpose I/O port. |

|

|

|

|

|

|

|

|

|

|

|

(Continued) |

|

10

MB90230 Series

(Continued)

Pin no. |

|

|

Pin name |

Circuit |

|

Function |

||||

|

|

type |

|

|||||||

|

|

|

|

|