8

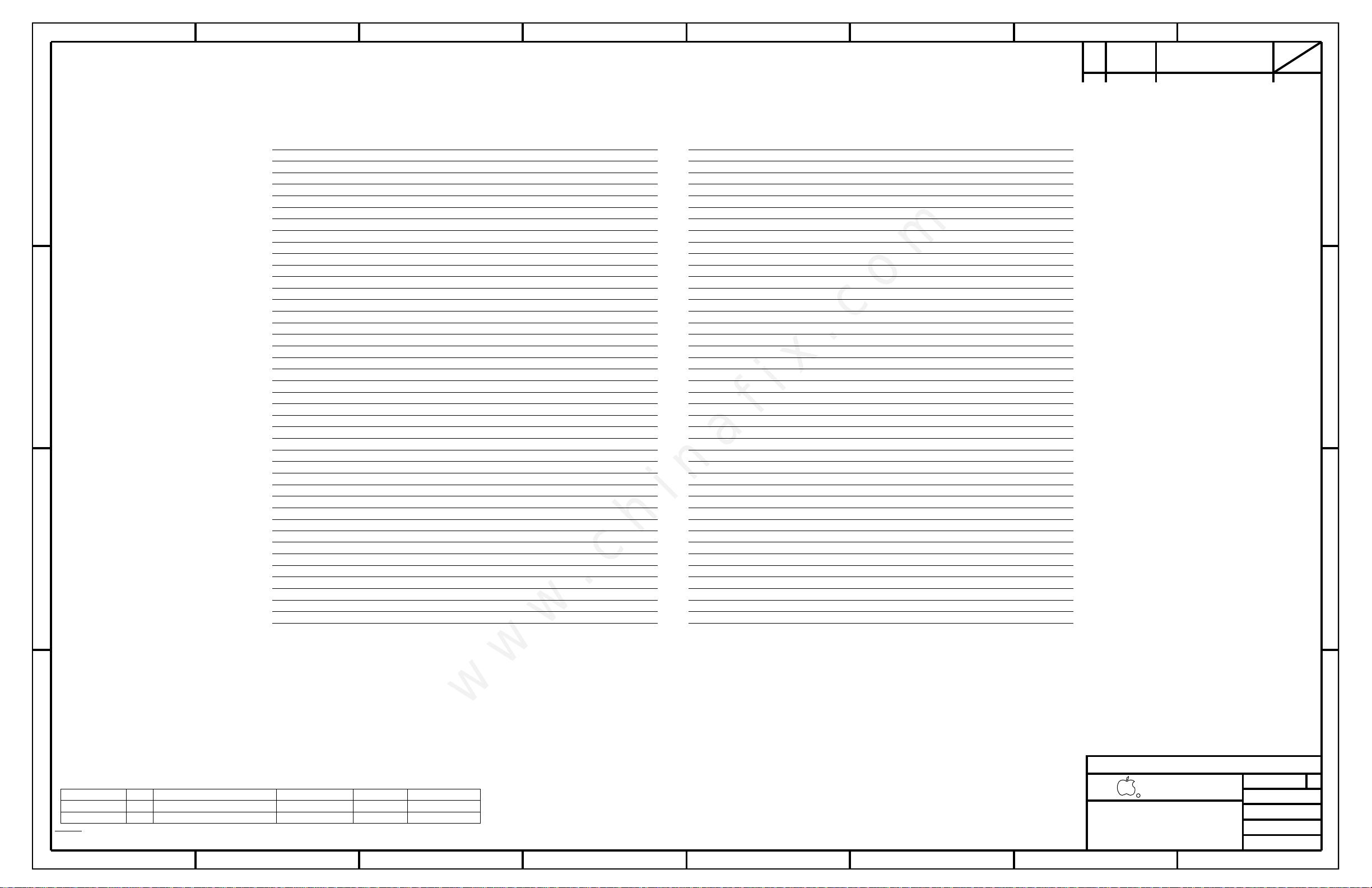

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

D

C

B

7

SCHEM,MLB,X425

08/06/2014 PROTO1A

Sync

Date

MASTER

05/30/2014

10/31/2012

10/31/2012

02/18/2014

12/18/2012

12/18/2012

12/18/2012

12/18/2012

12/18/2012

12/18/2012

12/18/2012

12/18/2012

02/18/2014

12/18/2012

12/18/2012

12/18/2012

10/31/2012

12/18/2012

01/14/2013

07/01/2014

01/14/2014

10/31/2012

10/31/2012

10/31/2012

10/31/2012

10/31/2012

01/14/2013

01/14/2013

06/24/2014

06/24/2014

06/24/2014

11/16/2012

01/15/2014

02/18/2014

06/24/2014

06/24/2014

10/31/2012

02/18/2014

05/30/2014

01/15/2014

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

(.csa)

Page Page

TABLE_TABLEOFCONTENTS_HEAD TABLE_TABLEOFCONTENTS_HEAD

1

TABLE_TABLEOFCONTENTS_ITEM

2

TABLE_TABLEOFCONTENTS_ITEM

3

TABLE_TABLEOFCONTENTS_ITEM

4

TABLE_TABLEOFCONTENTS_ITEM

5

TABLE_TABLEOFCONTENTS_ITEM

6

TABLE_TABLEOFCONTENTS_ITEM

7

TABLE_TABLEOFCONTENTS_ITEM

8

TABLE_TABLEOFCONTENTS_ITEM

9

TABLE_TABLEOFCONTENTS_ITEM

10

TABLE_TABLEOFCONTENTS_ITEM

11

TABLE_TABLEOFCONTENTS_ITEM

12

TABLE_TABLEOFCONTENTS_ITEM

13

TABLE_TABLEOFCONTENTS_ITEM

14

TABLE_TABLEOFCONTENTS_ITEM

15

TABLE_TABLEOFCONTENTS_ITEM

16

TABLE_TABLEOFCONTENTS_ITEM

17

TABLE_TABLEOFCONTENTS_ITEM

18

TABLE_TABLEOFCONTENTS_ITEM

19

TABLE_TABLEOFCONTENTS_ITEM

20

TABLE_TABLEOFCONTENTS_ITEM

21

TABLE_TABLEOFCONTENTS_ITEM

22

TABLE_TABLEOFCONTENTS_ITEM

23

TABLE_TABLEOFCONTENTS_ITEM

24

TABLE_TABLEOFCONTENTS_ITEM

25

TABLE_TABLEOFCONTENTS_ITEM

26

TABLE_TABLEOFCONTENTS_ITEM

27

TABLE_TABLEOFCONTENTS_ITEM

28

TABLE_TABLEOFCONTENTS_ITEM

29

TABLE_TABLEOFCONTENTS_ITEM

30

TABLE_TABLEOFCONTENTS_ITEM

31

TABLE_TABLEOFCONTENTS_ITEM

32

TABLE_TABLEOFCONTENTS_ITEM

33

TABLE_TABLEOFCONTENTS_ITEM

34

TABLE_TABLEOFCONTENTS_ITEM

35

TABLE_TABLEOFCONTENTS_ITEM

36

TABLE_TABLEOFCONTENTS_ITEM

37

TABLE_TABLEOFCONTENTS_ITEM

38

TABLE_TABLEOFCONTENTS_ITEM

39

TABLE_TABLEOFCONTENTS_ITEM

40

TABLE_TABLEOFCONTENTS_ITEM

41

TABLE_TABLEOFCONTENTS_ITEM

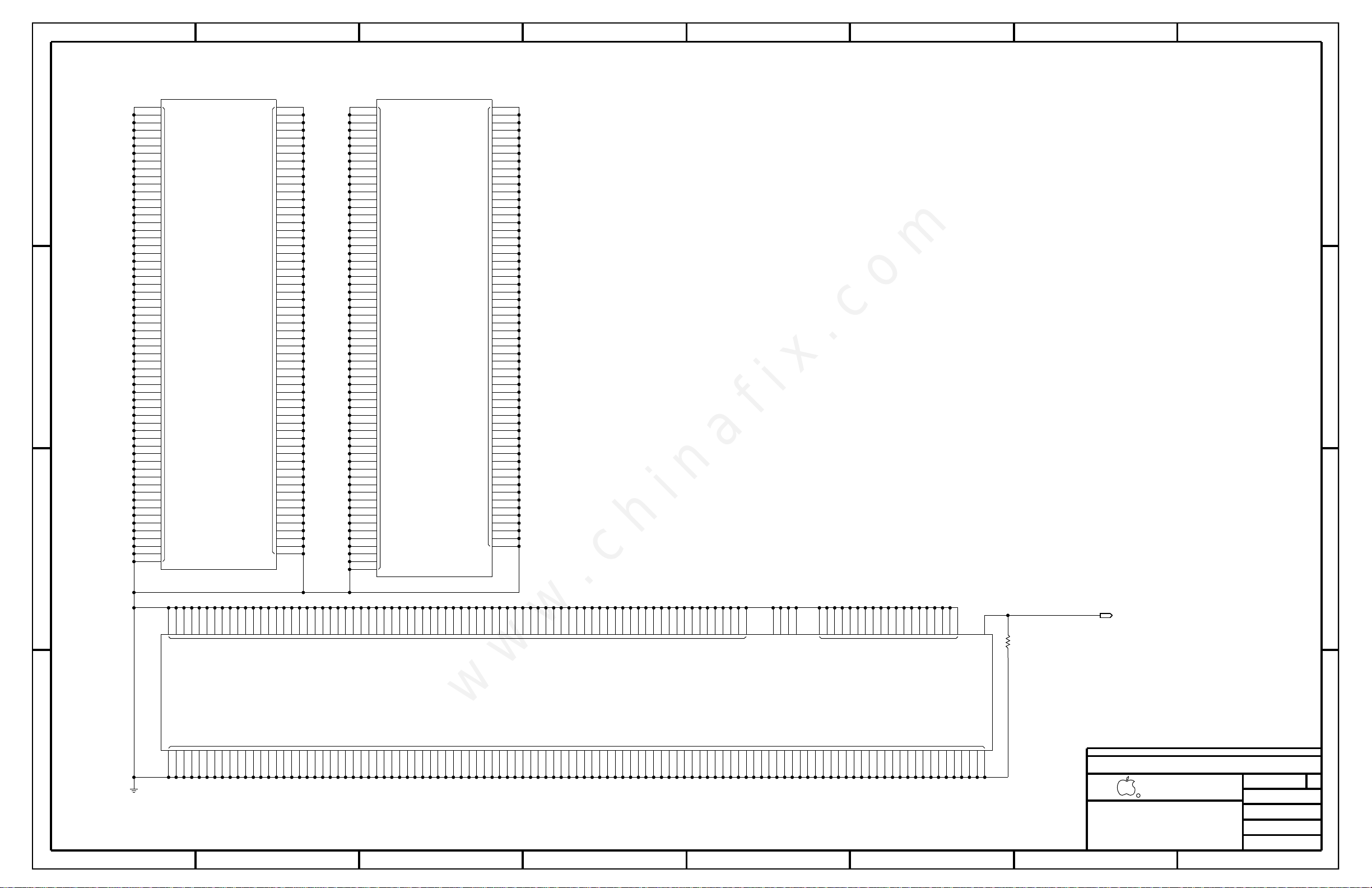

1

Table of Contents

2

BOM Configuration

3

BOM Configuration

4

PD Parts

5

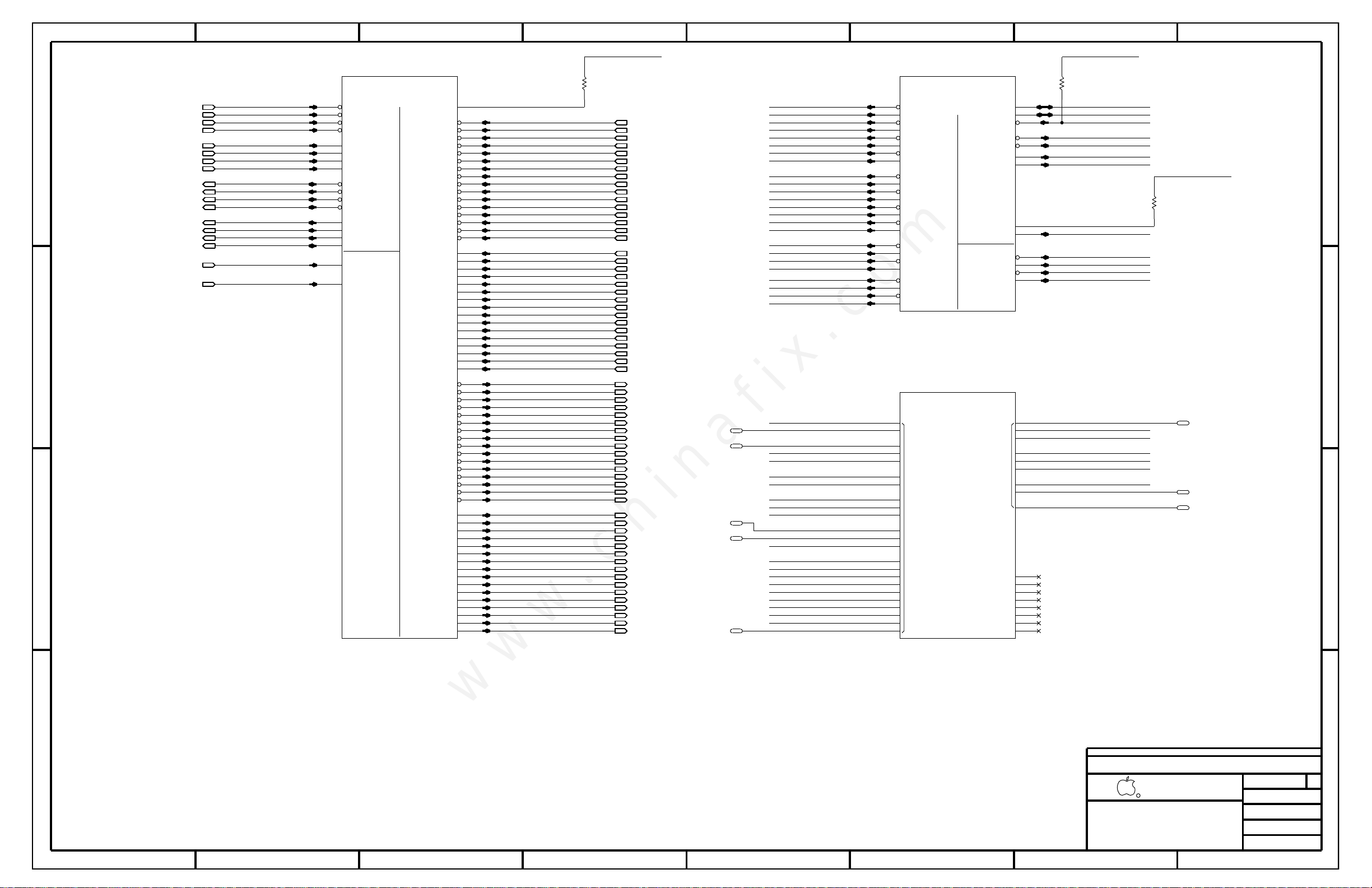

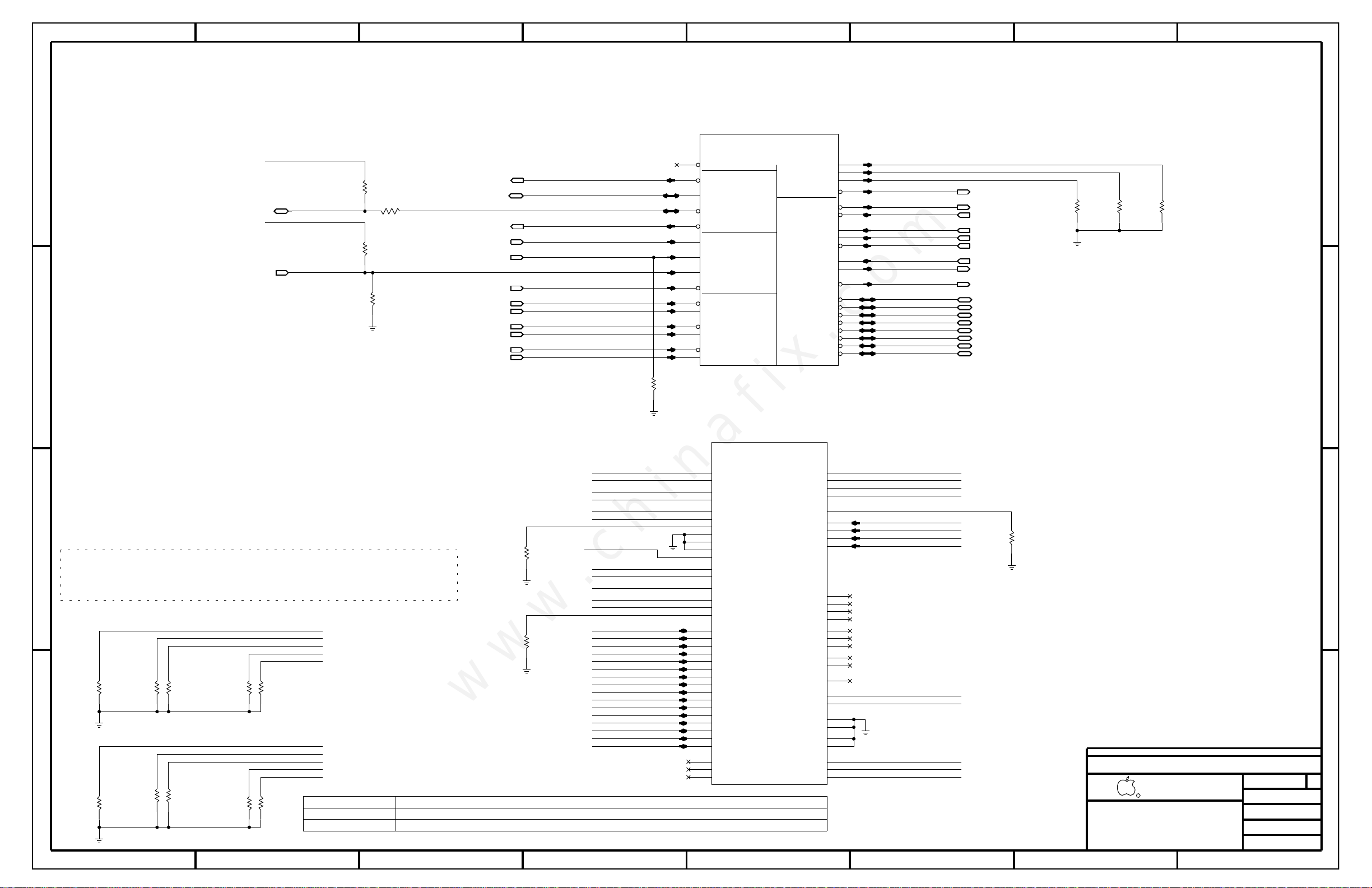

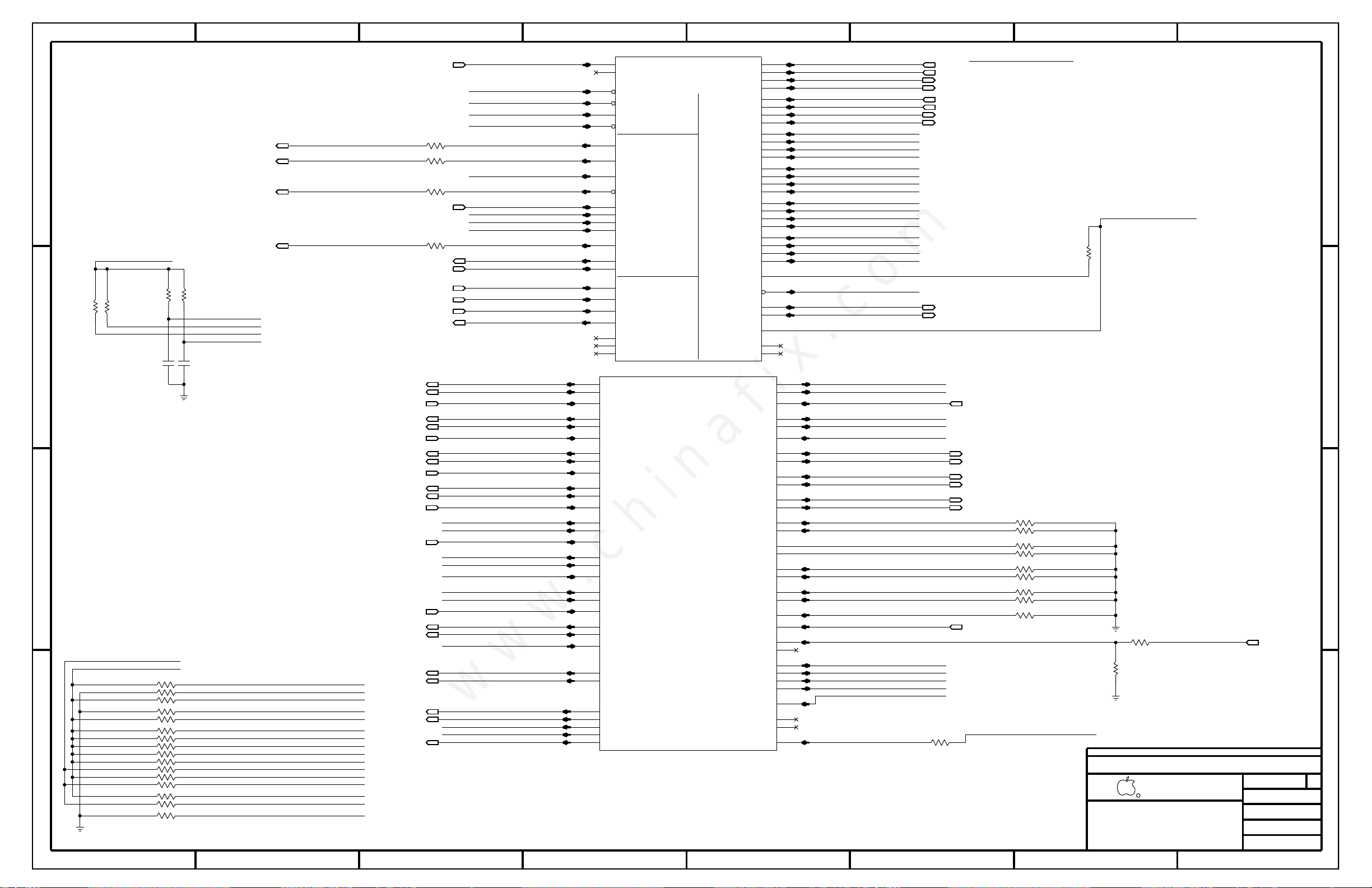

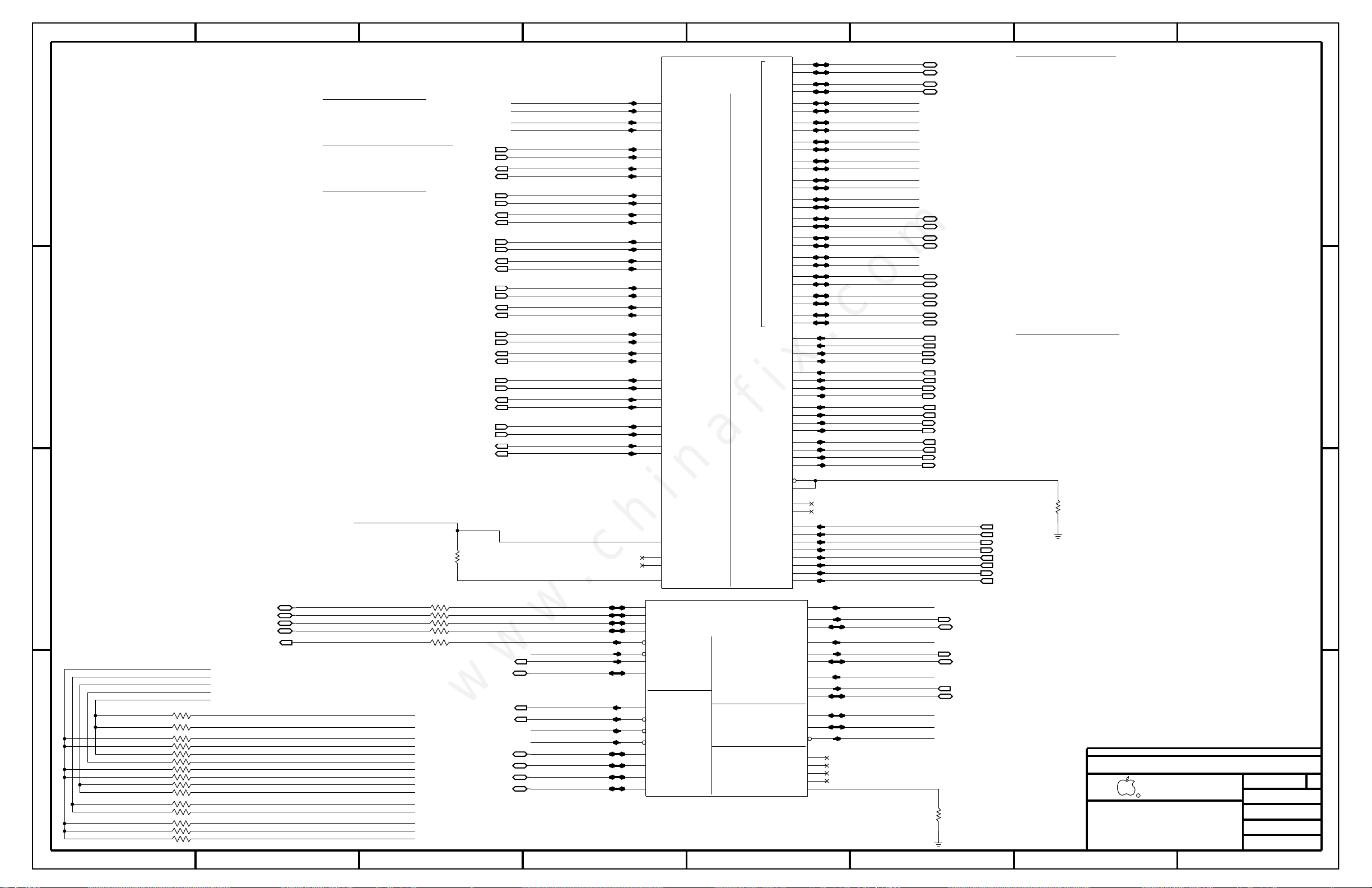

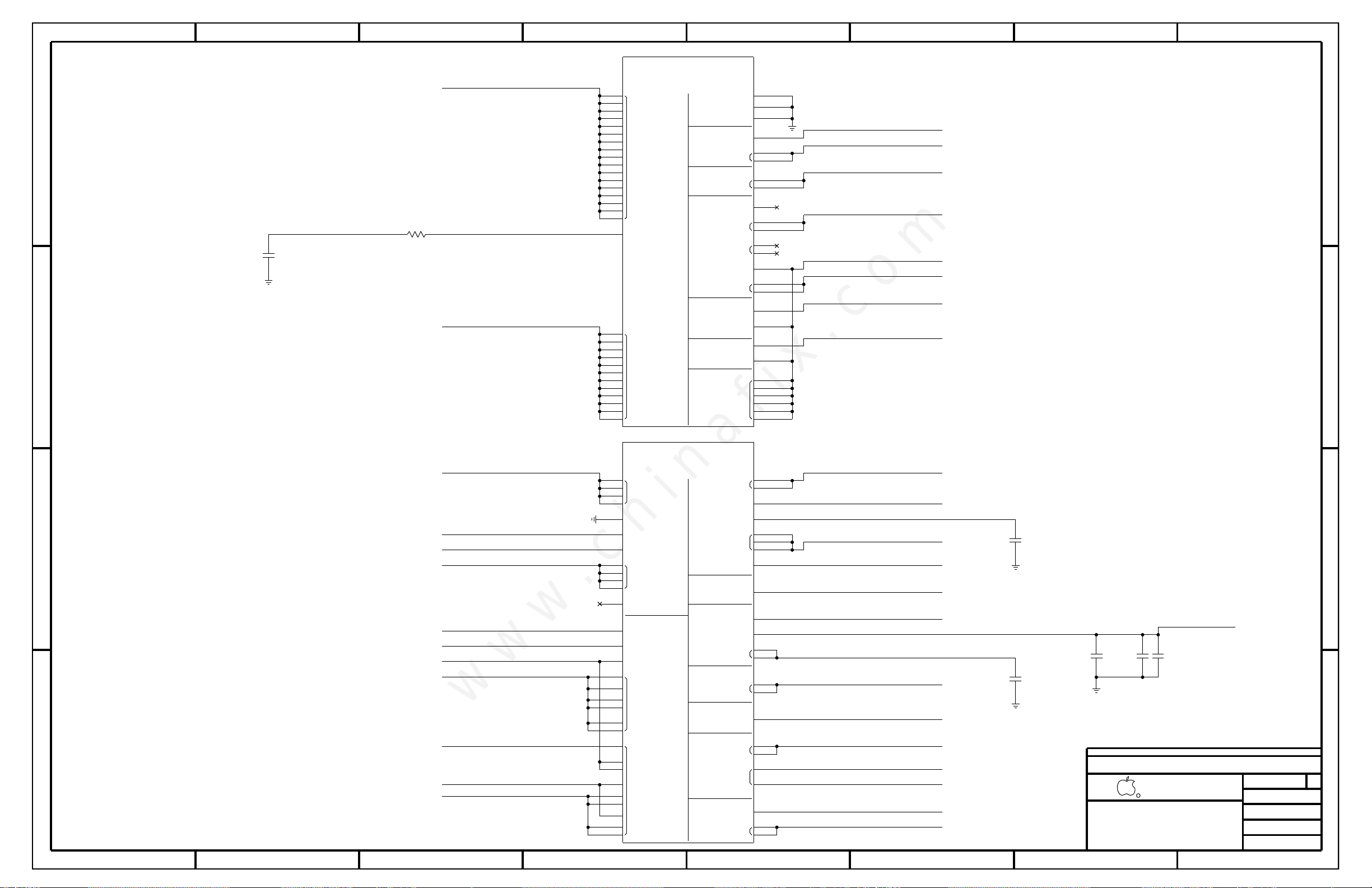

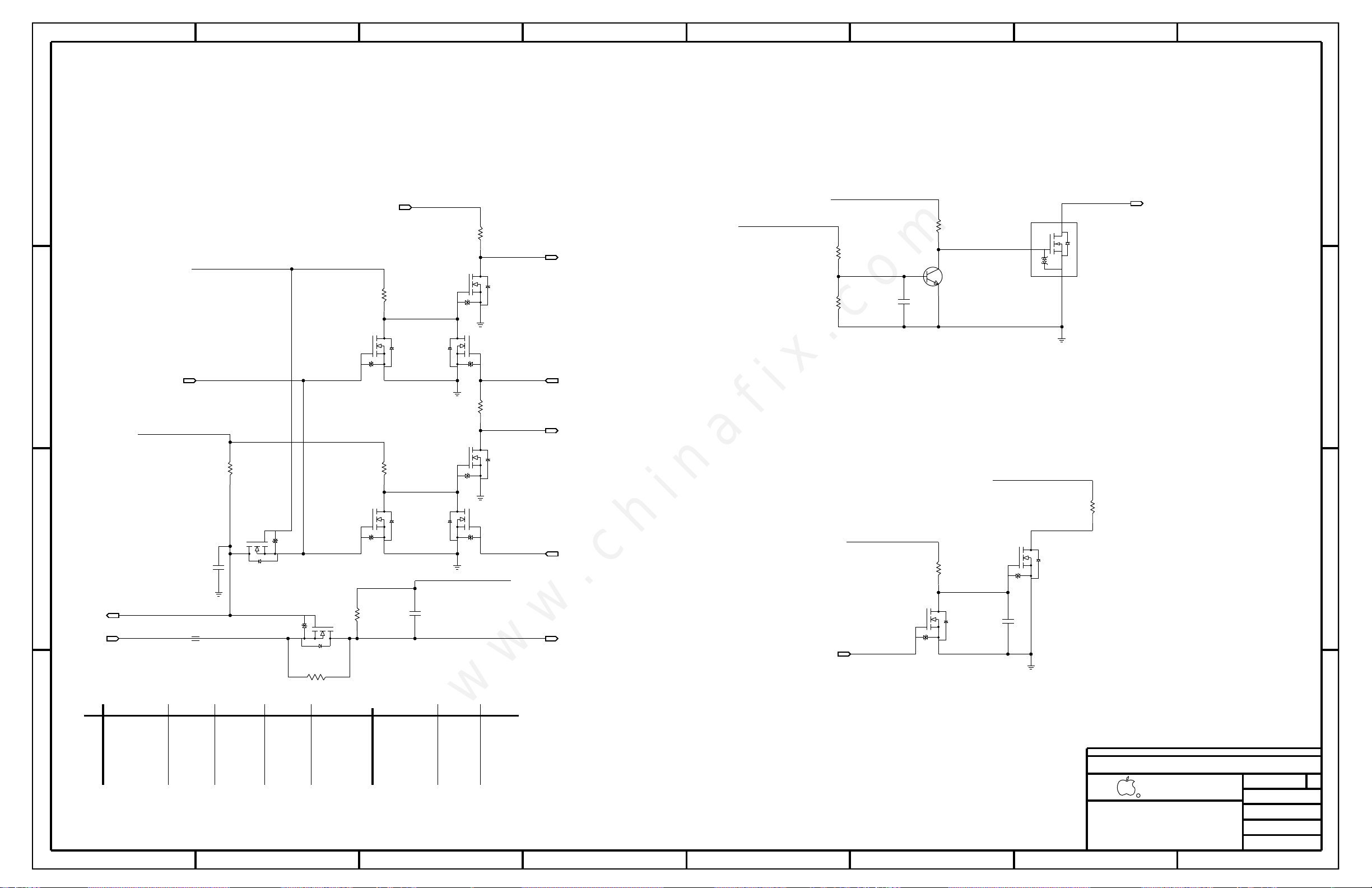

CPU DMI/PEG/FDI/RSVD

6

CPU Clock/Misc/JTAG/CFG

7

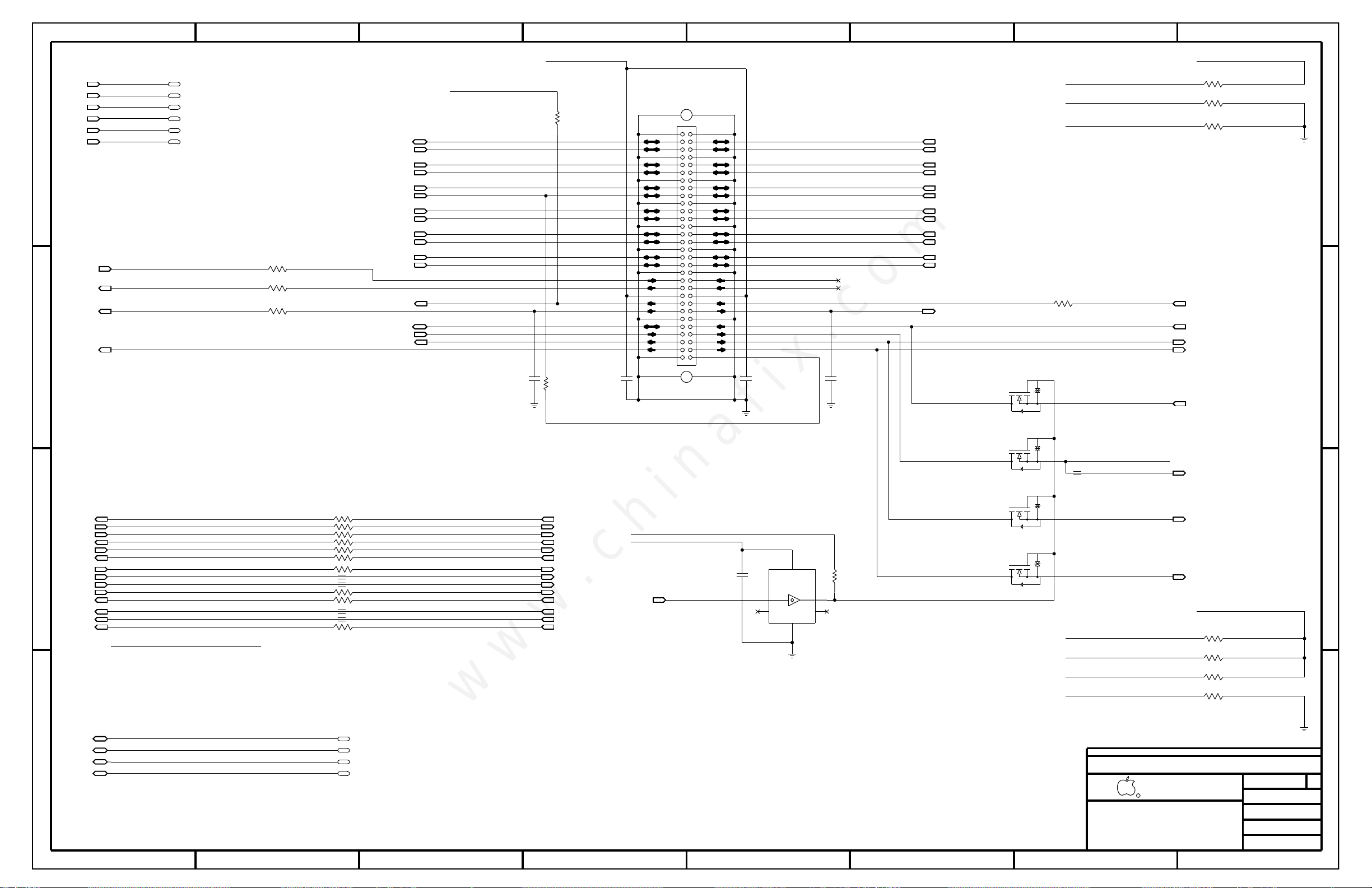

CPU DDR3 Interfaces

8

CPU Power

9

CPU Ground

10

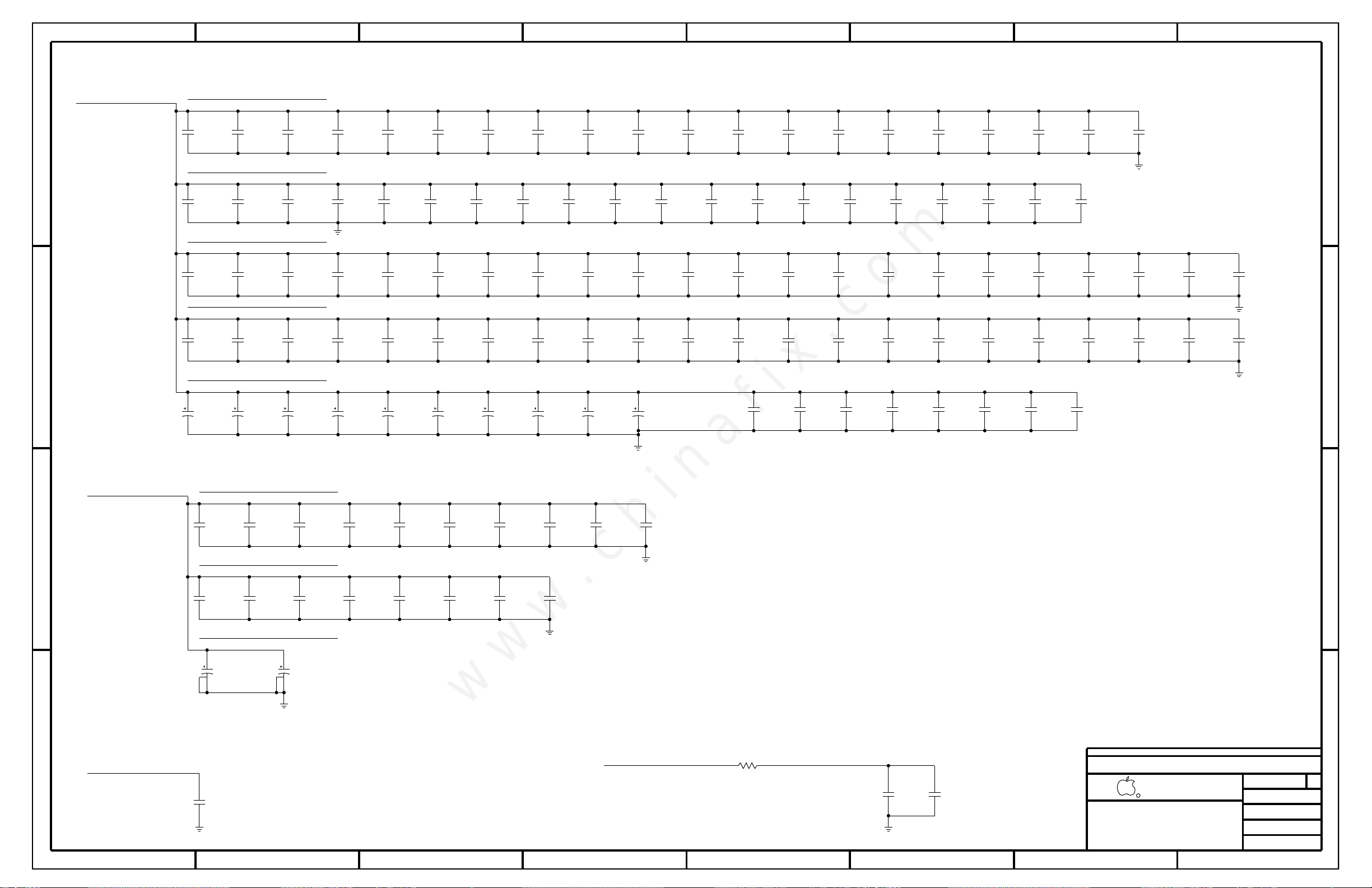

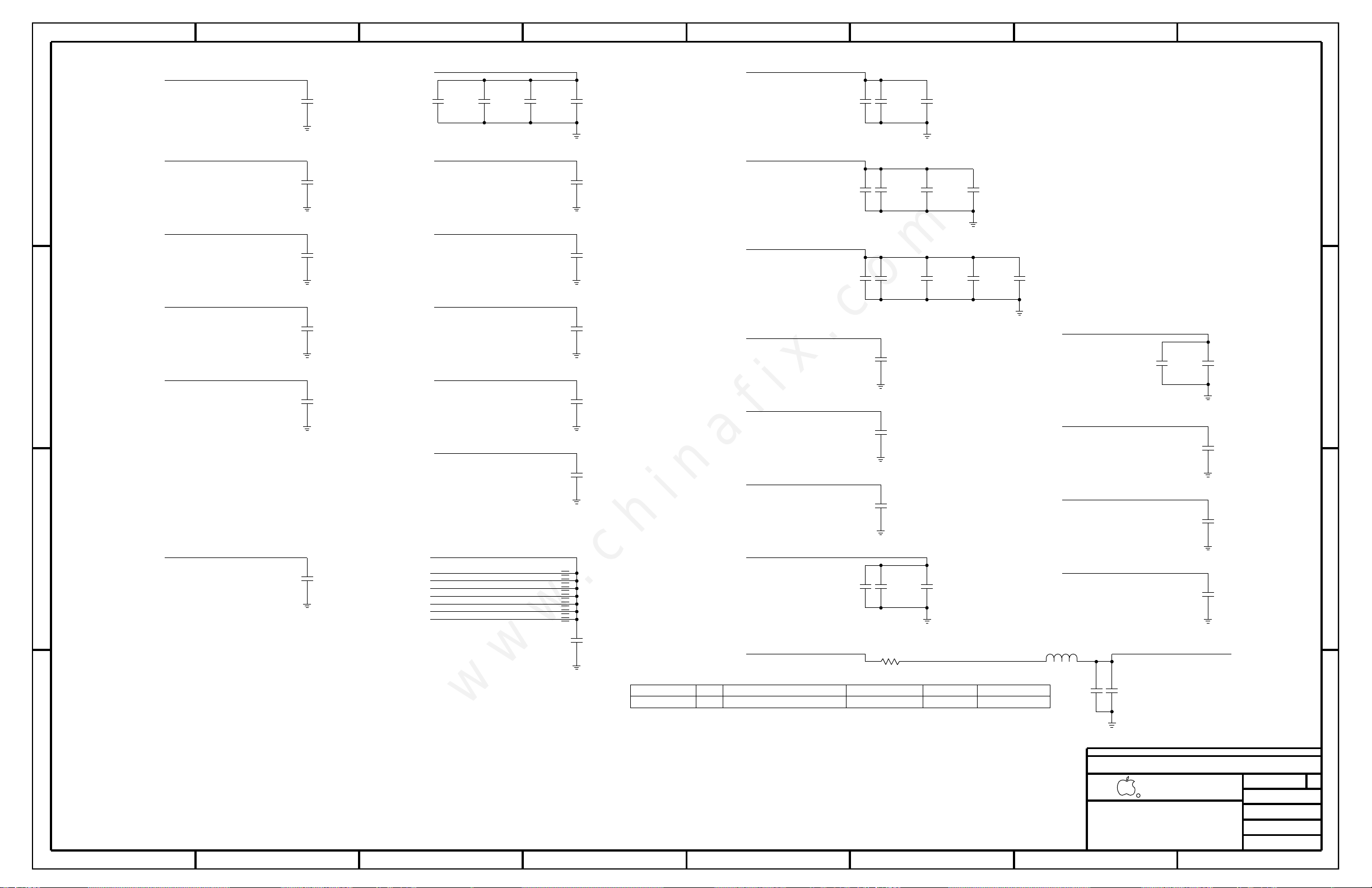

CPU Decoupling

11

PCH RTC/HDA/JTAG/SATA/CLK

12

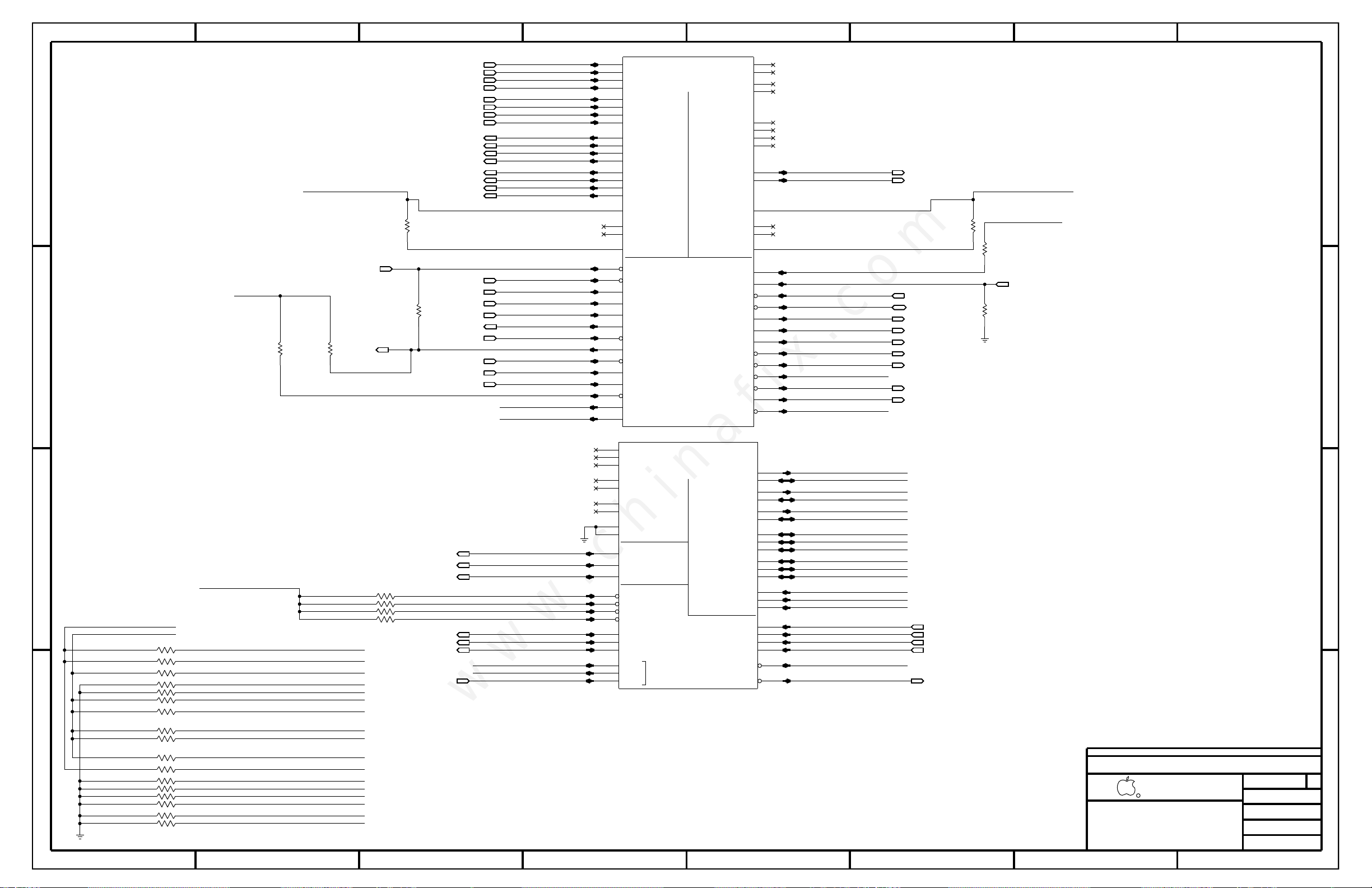

PCH DMI/FDI/PM/GFX/PCI

13

PCH PCI-E/USB

14

PCH GPIO/MISC/NCTF

15

PCH Power

16

PCH Grounds

17

PCH DECOUPLING

18

CPU & PCH XDP

19

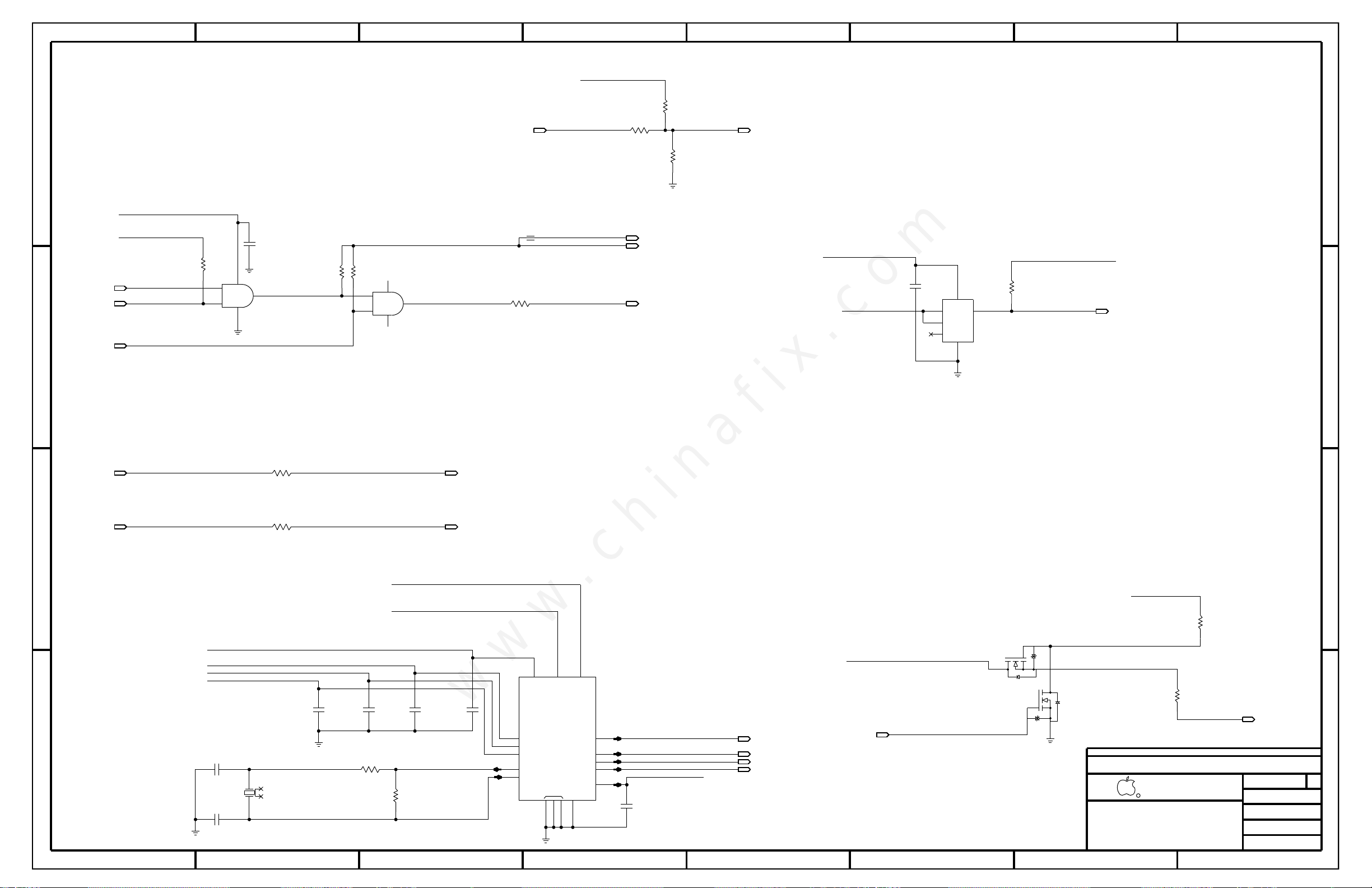

Chipset Support

20

Project Chipset Support

21

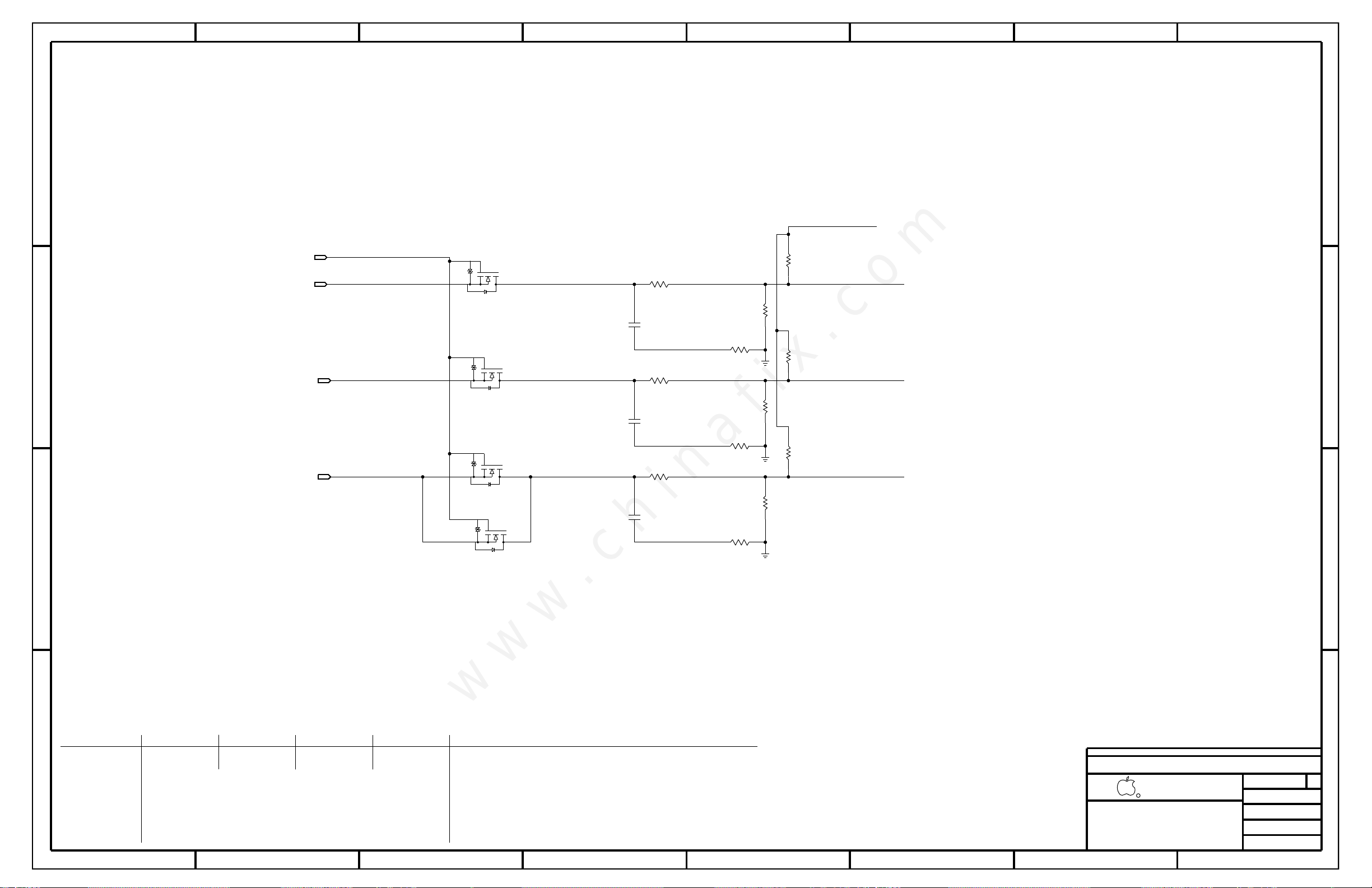

CPU Memory S3 Support

22

DDR3 VREF MARGINING

23

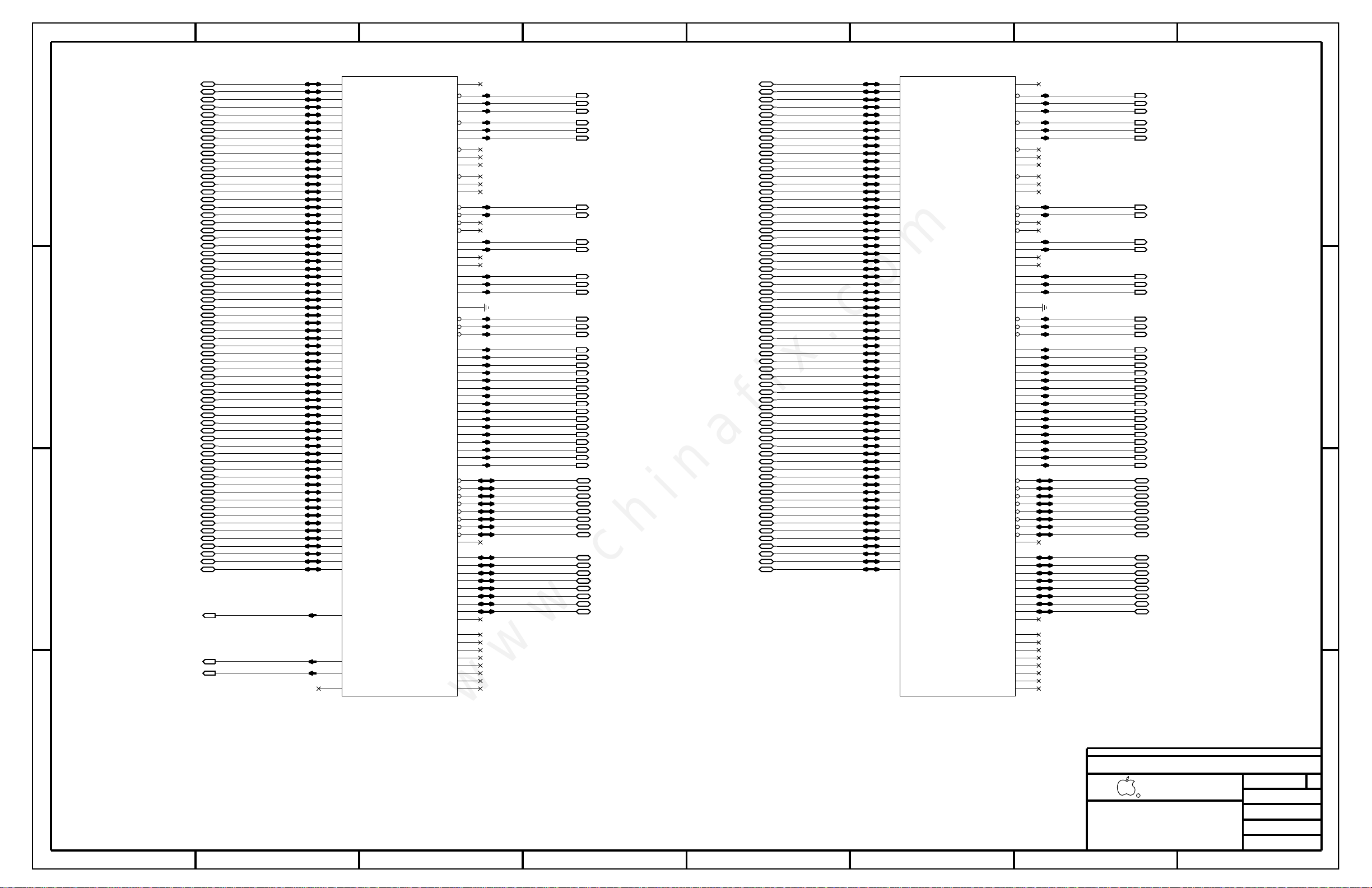

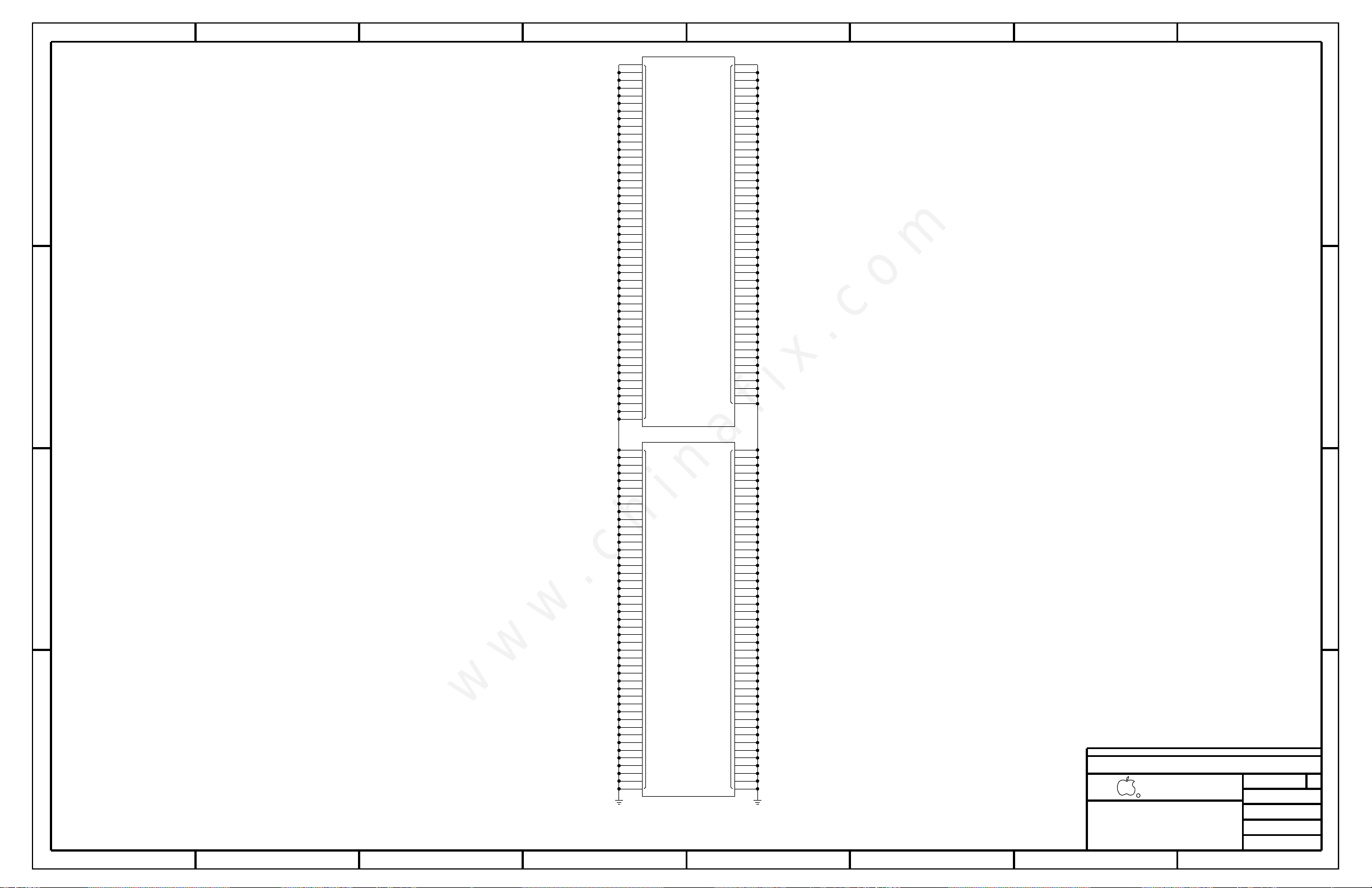

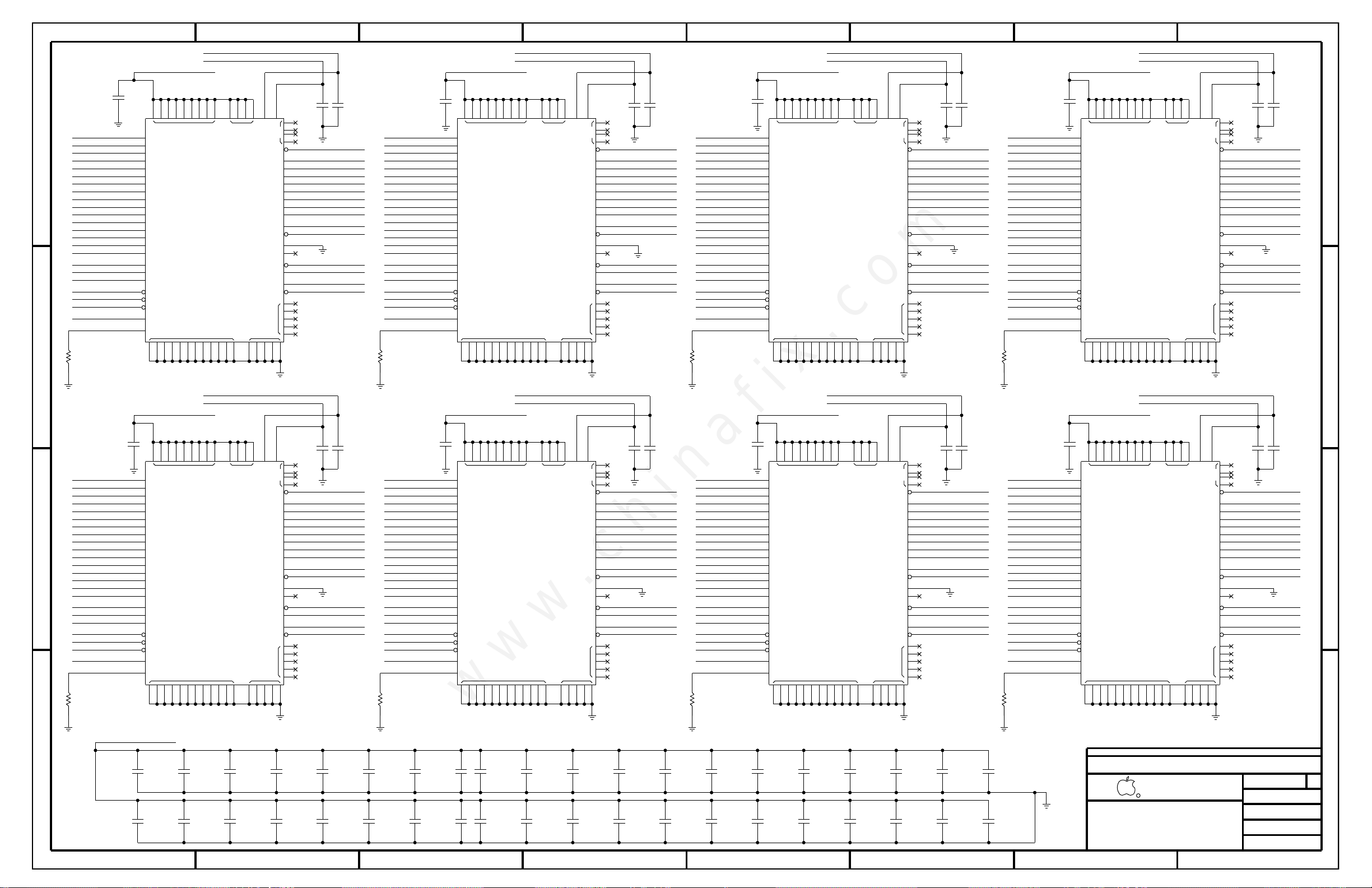

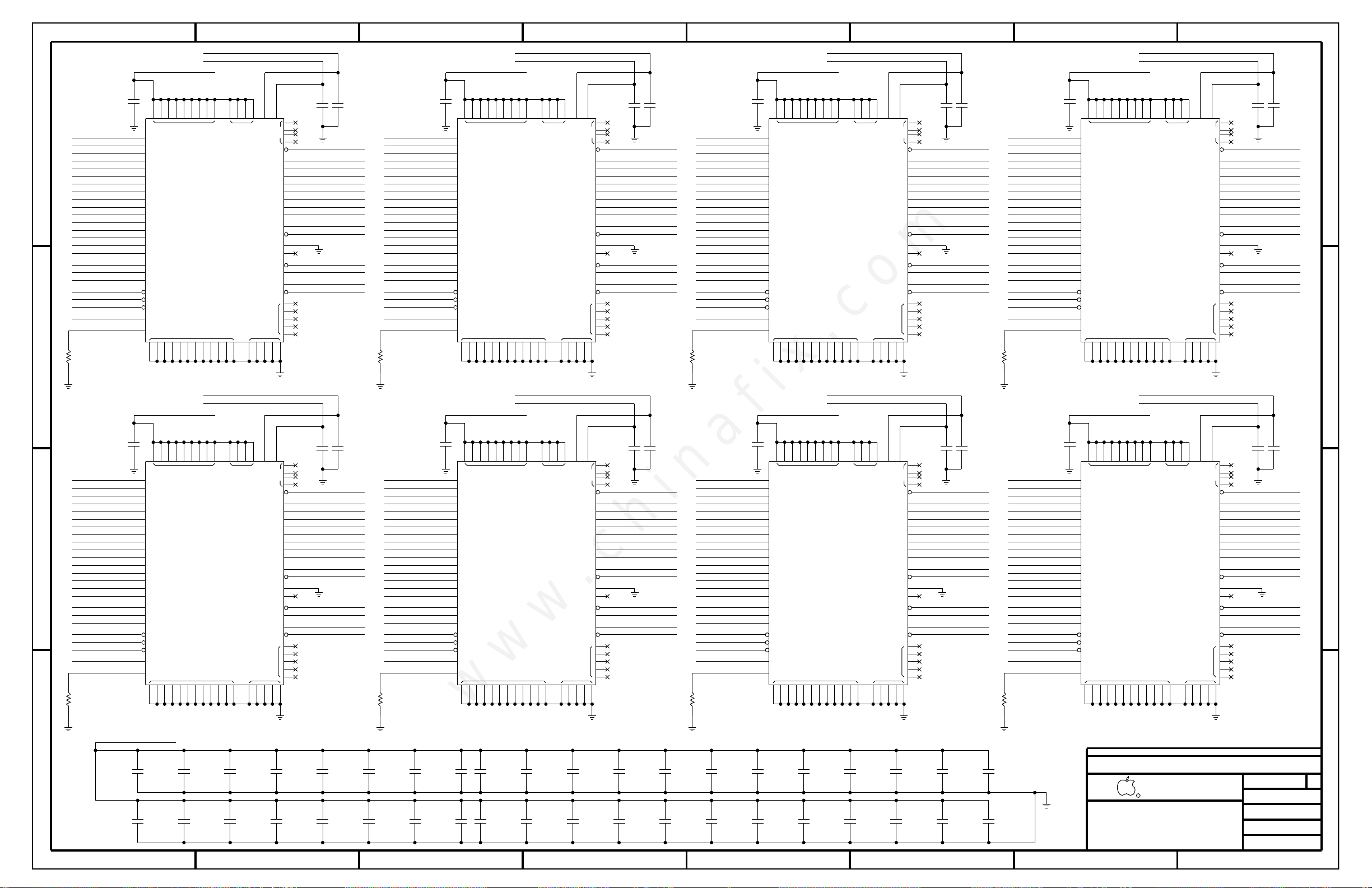

DDR3 SDRAM Bank A (1 OF 2)

24

DDR3 SDRAM Bank A (2 OF 2)

25

DDR3 SDRAM Bank B (1 OF 2)

26

DDR3 SDRAM Bank B (2 OF 2)

27

DDR3 Termination

28

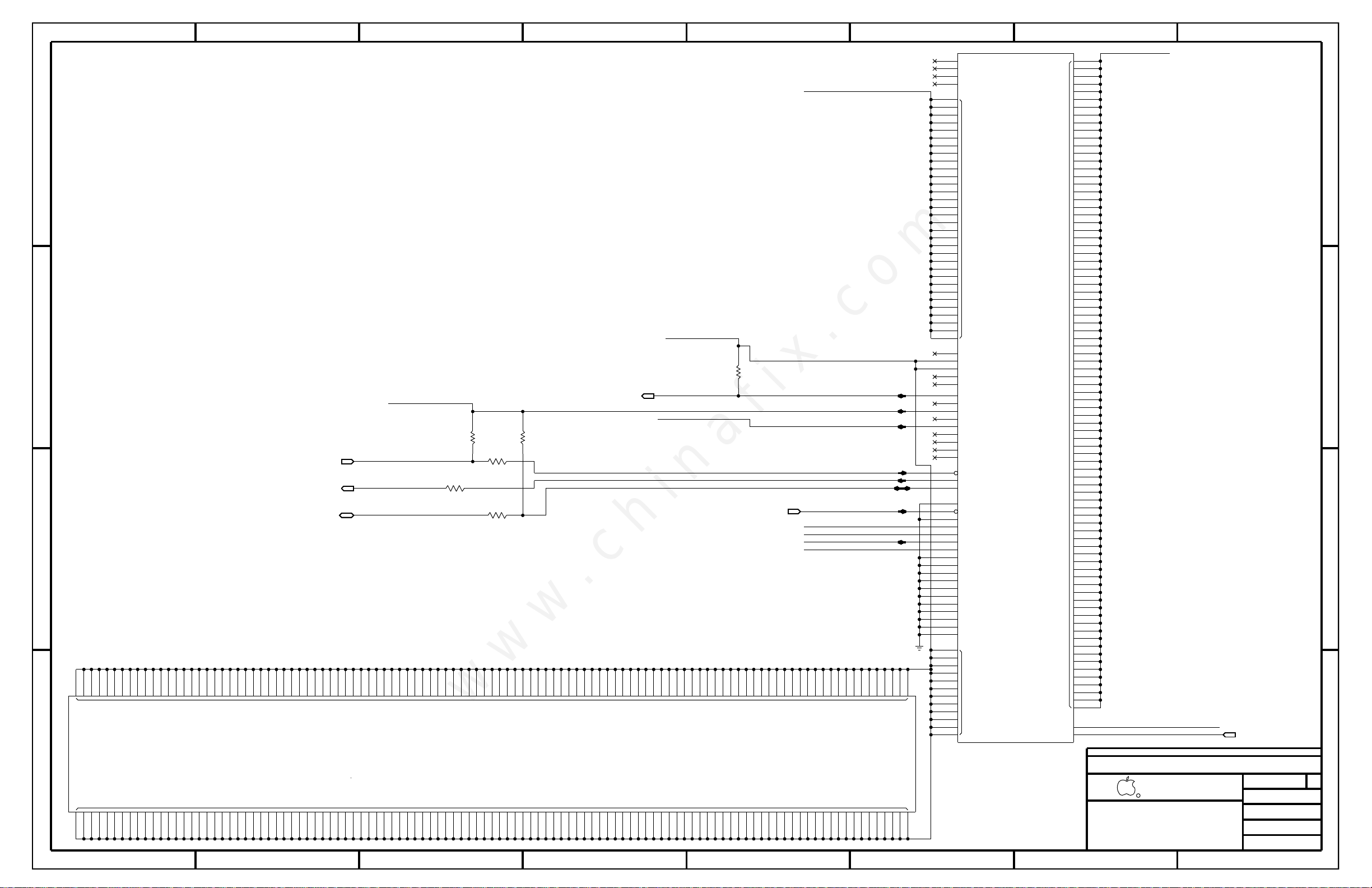

Thunderbolt Host (1 of 2)

29

Thunderbolt Host (2 of 2)

30

Thunderbolt Mobile Support

32

Thunderbolt Connector A

33

Thunderbolt Connector B

34

DDC Crossbar

35

X87 CONNECTOR

37

SSD Connector

39

Camera 1 of 2

40

Camera 2 of 2

46

USB 3.0 CONNECTORS

48

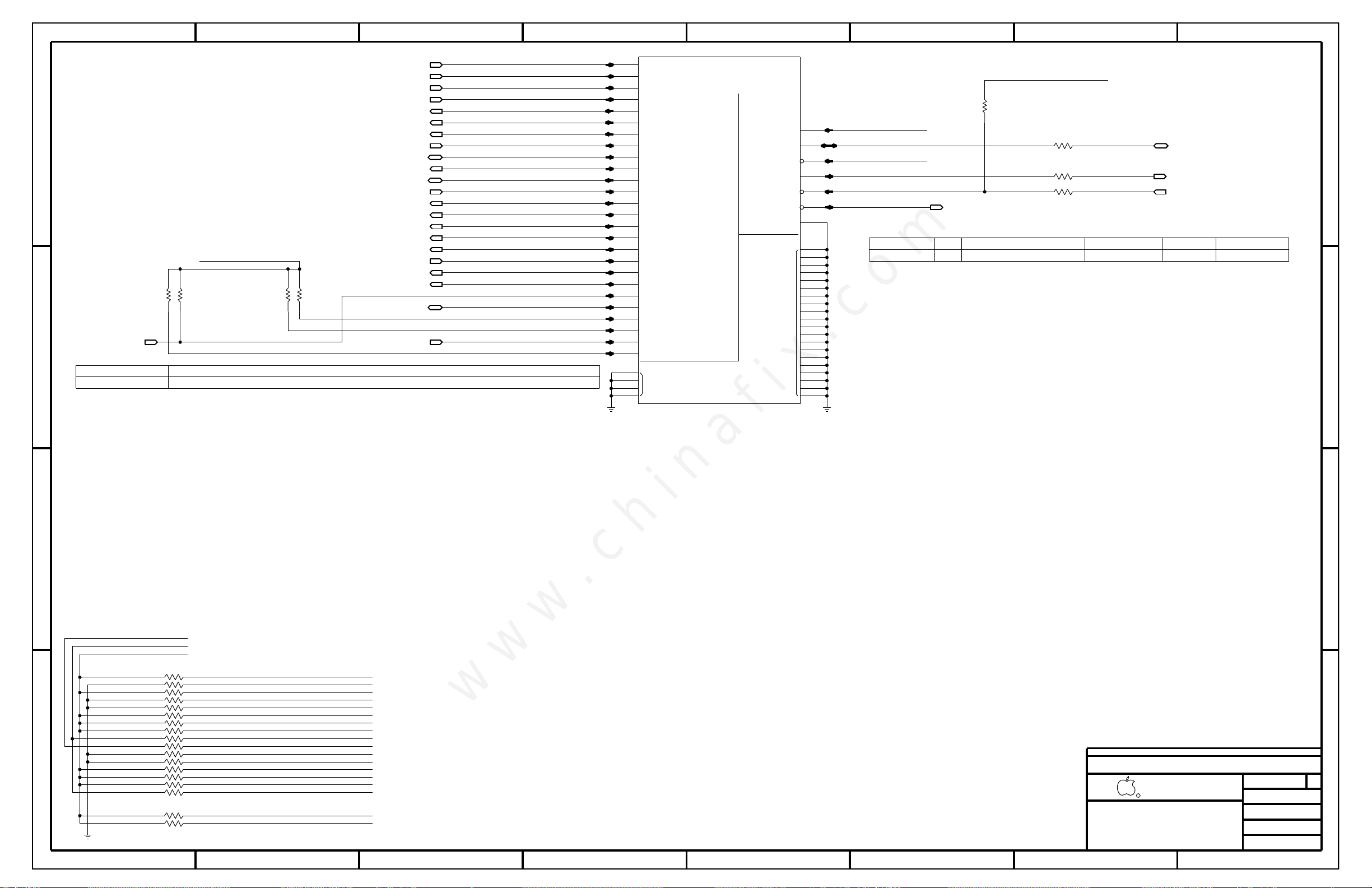

KEYBOARD/TRACKPAD (1 OF 2)

49

KEYBOARD/TRACKPAD (2 OF 2)

50

SMC

Contents

MASTER

CLEAN_X305

J15_MLB

J15_MLB

CLEAN_X305_PEG

J15_REFERENCE

J15_REFERENCE

J15_REFERENCE

J15_REFERENCE

J15_REFERENCE

J15_REFERENCE

J15_REFERENCE

J15_REFERENCE

CLEAN_X305_PEG

J15_REFERENCE

J15_REFERENCE

J15_REFERENCE

J15_MLB

J15_REFERENCE

J15_REFERENCE

CLEAN_X305G

CLEAN_X305

J15_MLB

J15_MLB

J15_MLB

J15_MLB

J15_MLB

T29_RR

T29_RR

CLEAN_X305

CLEAN_X305

CLEAN_X305

J15_REFERENCE

CLEAN_X305

CLEAN_X305_PEG

CLEAN_X305

CLEAN_X305

J15_MLB

CLEAN_X305_PEG

CLEAN_X305

CLEAN_X305

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

(.csa)

51

SMC Shared Support

52

SMC Project Support

53

SMBus Connections

54

High Side Voltage and Current Sensing

55

Load Side Voltage and Current Sensing

56

Debug Sensors

58

Thermal Sensors

60

Fan Connectors

61

SPI Debug Connector

62

AUDIO:CODEC, ANALOG

63

AUDIO:CODEC, DIGITAL

64

AUDIO: SPEAKER AMP

65

AUDIO: JACK

66

AUDIO: JACK TRANSLATORS

70

DC-In & Battery Connectors

71

PBus Supply & Battery Charger

72

CPU VR12.5 VCC Regulator IC

73

CPU VR12.5 VCC Power Stage

74

1.35V DDR3L SUPPLY

75

5V / 3.3V Power Supply

76

1V05V POWER SUPPLY

77

LCD/KBD Backlight Driver

78

Misc Power Supplies

79

X249 Boost Power Supply

80

Power FETs

81

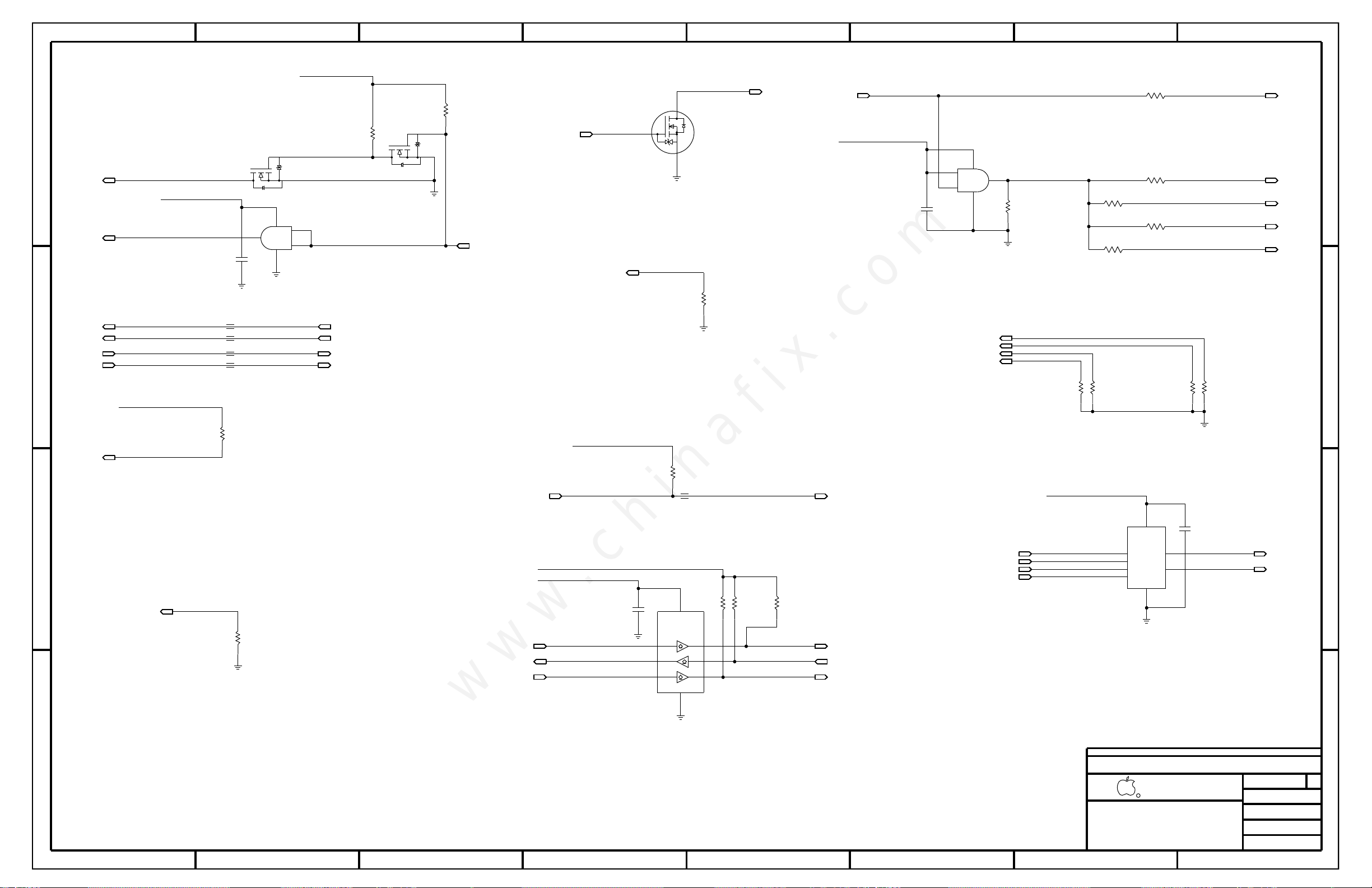

Power Control 1/ENABLE

83

eDP Display Connector

95

RIO Connectors

100

Power Aliases

102

Signal Aliases

104

Functional Test Points

105

NC & No Test

110

PCB Rule Definitions

111

CPU Constraints

112

PCH Constraints 1

113

PCH Constraints 2

114

Memory Constraints

115

Thunderbolt Constraints

116

Camera Constraints

117

SMC Constraints

118

Project Specific Constraints

Contents

3456

REV ECN

DESCRIPTION OF REVISION

12

CK

APPD

DATE

<ECODATE>

D

C

B

Sync

CLEAN_X305

CLEAN_X305

CHANG_J45

CLEAN_X305_PEG

CLEAN_X305_PEG

CLEAN_X305

CHANG_J45

J15_MLB

CLEAN_X305_PEG

JOE_J45

JOE_J45

JOE_J45

CLEAN_X305

CLEAN_X305

CLEAN_X305_PEG

CLEAN_X305

CLEAN_X305_PEG

J15_MLB

CLEAN_X305

CLEAN_X305_PEG

CLEAN_X305_PEG

CLEAN_X305_PEG

CLEAN_X305

CLEAN_X305

CLEAN_X305_PEG

CLEAN_X305

CLEAN_X305_PEG

CLEAN_X305G

CLEAN_X305

J15_MLB

J15_MLB

J15_MLB

SIDLE_J45

CLEAN_X305_PEG

SIDLE_J45

CLEAN_X305_PEG

SIDLE_J45

SIDLE_J45

SIDLE_J45

SIDLE_J45

SIDLE_J45

Date

06/24/2014

05/30/2014

11/26/2012

02/18/2014

02/18/2014

01/14/2014

11/26/2012

10/31/2012

02/18/2014

07/30/2013

07/30/2013

07/30/2013

06/24/2014

06/24/2014

02/18/2014

01/15/2014

02/24/2014

10/31/2012

01/15/2014

02/18/2014

02/18/2014

02/19/2014

01/15/2014

05/30/2014

02/18/2014

05/30/2014

02/18/2014

01/14/2014

05/30/2014

10/31/2012

10/31/2012

10/31/2012

12/10/2012

02/18/2014

12/10/2012

02/18/2014

12/10/2012

12/10/2012

12/10/2012

12/10/2012

12/10/2012

<ECN><REV>

<ECO_DESCRIPTION>

A

ALIASES RESOLVED

Schematic / PCB #’s

PART NUMBER

051-00330

820-00138

DRAWING

TITLE=MLB

ABBREV=ABBREV

LAST_MODIFIED=Wed Aug 6 13:00:04 2014

QTY

8 7 6 5 4 2 1

DESCRIPTION

SCHEM,MLB,X305

PCBF,MLB,X305

REFERENCE DES

SCH1

PCB1

CRITICAL

CRITICAL

CRITICAL

BOM OPTION

w w w . c h i n a f i x . c o m

DRAWING TITLE

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

3

<PART_DESCRIPTION>

Apple Inc.

DRAWING NUMBER

<SCH_NUM>

REVISION

<E4LABEL>

BRANCH

<BRANCH>

PAGE

1 OF 118

SHEET

1 OF 82

SIZE

A

D

8 7 6 5 4 3

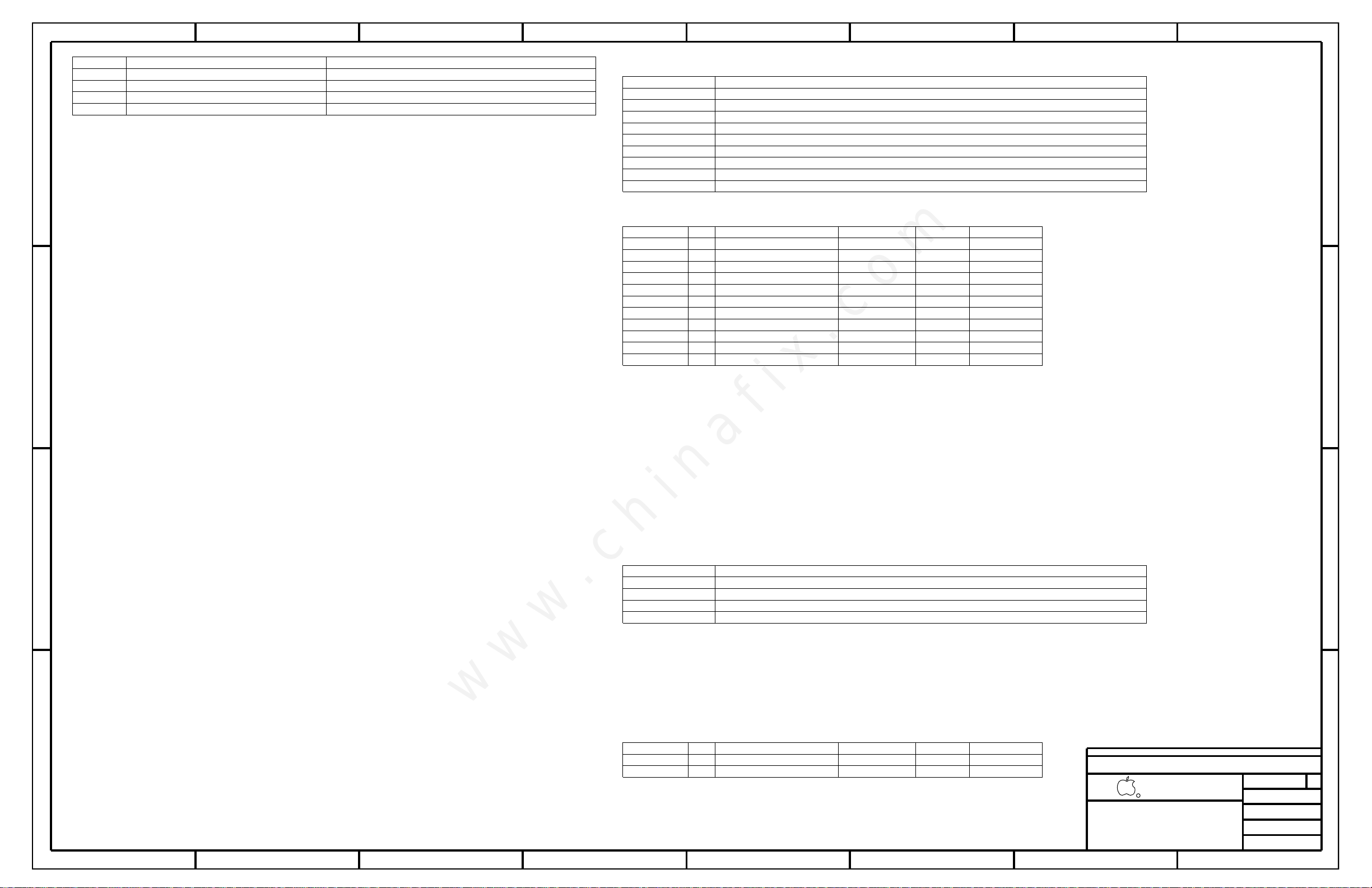

BOM Variants

BOM NUMBER

685-00039

985-00043

639-00534

639-00535

BOM NAME

COMMON PARTS,MLB,X425

DEV,MLB,X425

PCBA,MLB,CTO,16G-HYN,X425

PCBA,MLB,CTO,16G-MIC,X425

BASE_BOM,DEVEL_BOM,CPU_CRW:CTO,RAM:HYNIX_1866

BASE_BOM,DEVEL_BOM,CPU_CRW:CTO,RAM:MICRON_1866

BOM OPTIONS

X425_COMMON

X425_DEVEL:ENG

D

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

X425 BOM Groups

BOM GROUP

X425_COMMON

X425_COMMON1

X425_COMMON2

X425_PVT

X425_PROGPARTS

X425_DEVEL:ENG

X425_DEVEL:DVT

X425_DEVEL:PVT

XDP_DEBUG

BOM OPTIONS

ALTERNATE,COMMON,X425_COMMON1,X425_COMMON2,X425_PROGPARTS

CPUMEM:S0,TBTHV:P15V,SKIP_5V3V3:AUDIBLE,CPUPEG:X8X8,S2_PWR:S0,SMC_SUSACK:YES

EDP:YES,XDP,SSD_PWR_EN:GPIO,CAM_WAKE:NO,SAMCONN,APCLKRQ:ISOL,DDRREG_PGD:N,CRW_SPRT,WLAN_SW:SIL

BKLT:PROD,SENSOR_NONPROD:N

SMC_PROG:BASE,BOOTROM_PROG:PROTO1A,TBTROM:PROG

ALTERNATE,XDP_DEBUG,S0PGOOD_ISL,SENSOR_NONPROD:Y,SENSOR_NONPROD_R,BKLT:ENG,DBGLED,X249:BOOST

ALTERNATE,XDP_DEBUG,BKLT:PROD,SENSOR_NONPROD:N,DBGLED

XDP_DEBUG

XDP_CONN,XDP_PCH

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

12

D

Module Parts

PART NUMBER

337S00057

337S00058

337S00059

337S4542

QTY

1

1

1

1

1

1

333S0700

333S0802

333S0719

C

333S0802 CRITICAL

333S0719 CRITICAL

1

16

16

32

32

DESCRIPTION

CRW,SR1ZW,PRQ,C0,2.2,47W,4+3E,1.2,6M,BGA

CRW,SR1ZX,PRQ,C0,2.5,47W,4+3E,1.2,6M,BGA

CRW,SR1ZY,PRQ,C0,2.8,47W,4+3E,1.2,6M,BGA

IC,QEWV,LPT-M,HM87,C2,SR199,PRQ,FCBGA

IC,TBT,FR-4C,A0,PRQ,CIO,SR1JC,FCBGA288

IC,BCM15700A2,S2 PCIE CMRA,8X8,208FCBGA

IC,SDRAM,4GBIT,DDR3L-1600,GEMMA,96B FBGA

IC,SDRAM,25NM,512MX8,DDR3L-1866,78B FBGA

IC,SDRAM,4GBIT,DDR3-1866,V80A,78B,FBGA

IC,SDRAM,25NM,512MX8,DDR3L-1866,78B FBGA

IC,SDRAM,4GBIT,DDR3-1866,V80A,78B,FBGA

REFERENCE DES

U0500

U0500

U0500

U1100

U2800

U3900

U4000

U2300,U2310,U2320,U2330,U2340,U2350,U2360,U2370,U2500,U2510,U2520,U2530,U2540,U2550,U2560,U2570

U2300,U2310,U2320,U2330,U2340,U2350,U2360,U2370,U2500,U2510,U2520,U2530,U2540,U2550,U2560,U2570

U2300,U2310,U2320,U2330,U2340,U2350,U2360,U2370,U2400,U2410,U2420,U2430,U2440,U2450,U2460,U2470,U2500,U2510,U2520,U2530,U2540,U2550,U2560,U2570,U2600,U2610,U2620,U2630,U2640,U2650,U2660,U2670

U2300,U2310,U2320,U2330,U2340,U2350,U2360,U2370,U2400,U2410,U2420,U2430,U2440,U2450,U2460,U2470,U2500,U2510,U2520,U2530,U2540,U2550,U2560,U2570,U2600,U2610,U2620,U2630,U2640,U2650,U2660,U2670

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL338S1247

CRITICAL338S1264

CRITICAL

CRITICAL

CRITICAL

BOM OPTION

CPU_CRW:BETTER

CPU_CRW:BEST

CPU_CRW:CTO

HYNIX_1866_S

MICRON_1866_S

HYNIX_1866

MICRON_1866

C

B

DRAM SPD Straps

BOM GROUP

RAM:HYNIX_1866_S

RAM:MICRON_1866_S

RAM:HYNIX_1866

RAM:MICRON_1866

BOM OPTIONS

HYNIX_1866_S,RAMCFG3:L,RAMCFG2:H,RAMCFG1:L,RAMCFG0:L

MICRON_1866_S,RAMCFG3:L,RAMCFG2:H,RAMCFG1:H,RAMCFG0:L

HYNIX_1866,RAMCFG3:H,RAMCFG2:H,RAMCFG1:L,RAMCFG0:L

MICRON_1866,RAMCFG3:H,RAMCFG2:H,RAMCFG1:H,RAMCFG0:L

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

B

w w w . c h i n a f i x . c o m

COMMON/DEVEL BOM

A

PART NUMBER

685-00039

985-00043

QTY

1

1

DESCRIPTION

COMMON PARTS,MLB,X425

DEV,MLB,X425

6 3

REFERENCE DES

BASE

DEVEL

CRITICAL

CRITICAL

CRITICAL

BOM OPTION

BASE_BOM

DEVEL_BOM

SYNC_MASTER=CLEAN_X305

PAGE TITLE

BOM Configuration

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=05/30/2014

DRAWING NUMBER

<SCH_NUM>

REVISION

<E4LABEL>

BRANCH

<BRANCH>

PAGE

2 OF 118

SHEET

2 OF 82

124578

SIZE

A

D

8 7 6 5 4 3

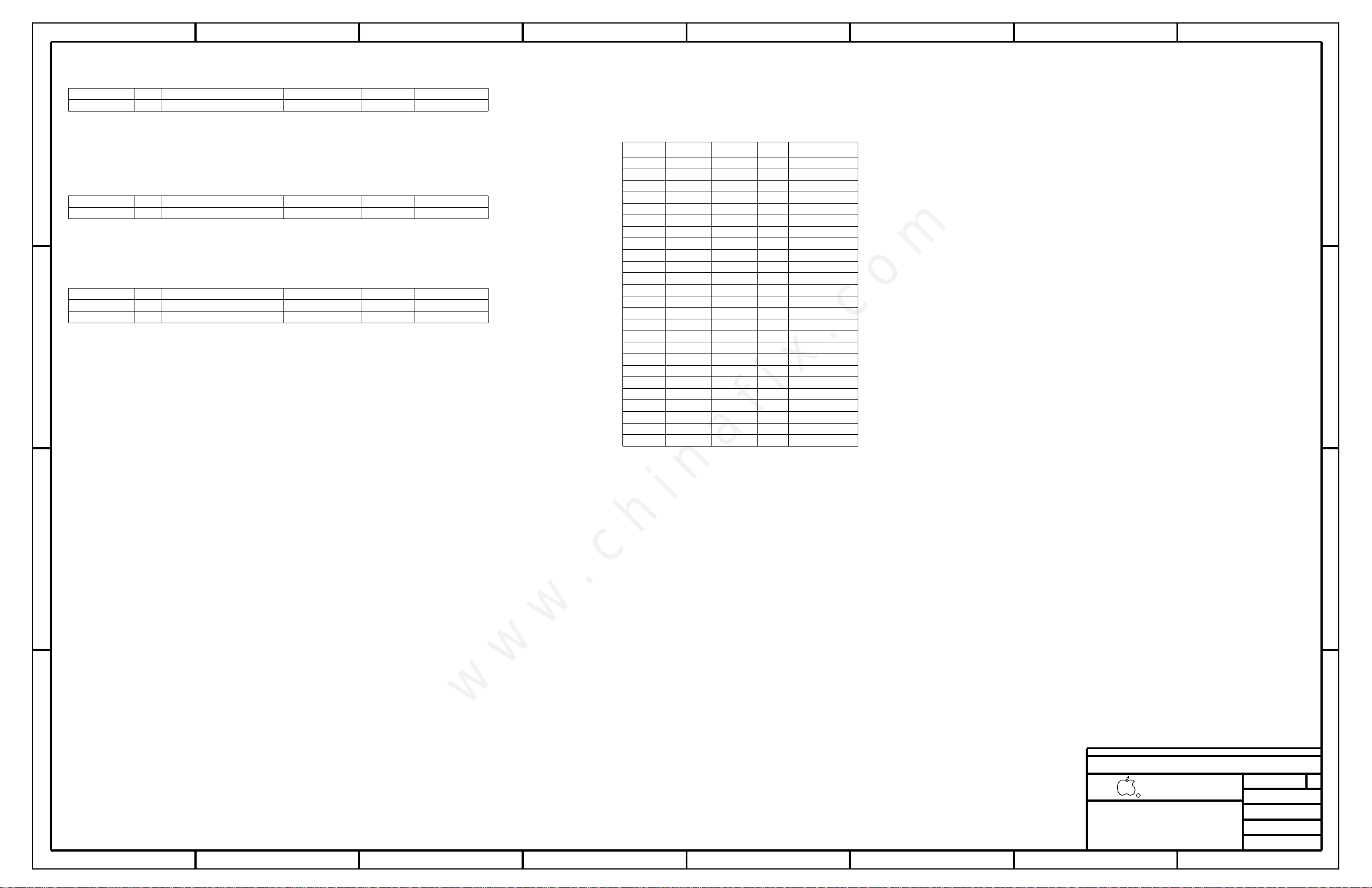

Programmables - All builds

335S0915

341S00133

IC,SERIAL SPI FLASH ROM,4MBIT,50MHZ,USON

1

T29,FALCON RIDGE(VXXXX)PROTO 1A,X425

1

U2890

U2890

CRITICAL

CRITICAL

12

TBTROM:BLANK

TBTROM:PROG

D

C

SMC

338S1214

341S00125

EFI ROM

335S00007

335S00006

341S00131

IC,SMC-B1,40MHZ/50DMIPS,SCPL FW,157BGA

1

IC,SMC-B1,EXT (V2.24A31) PROTO 1A,X425

1

IC,SERIAL FLASH,64MB,3V,WSON,6X5MM

1

IC,SERIAL FLASH,64MB,3V,WSON,6X5MM

1

IC,EFI ROM (VXXXX) PROTO 1A,X425

1

U5000

U5000

U6100

U6100

U6100

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

SMC_PROG:BLANK

SMC_PROG:BASE

BOOTROM_BLANK:WIN

BOOTROM_BLANK:MAC

BOOTROM_PROG:PROTO1A

Alternate Parts

PART NUMBER

376S1053 376S0604

128S0311 128S0329

138S0739 138S0706

197S0478

371S0713 371S0558

155S0667

376S1217 376S0855

376S1089

138S0803

138S0732 138S0715

128S0364 128S0264

311S0649 311S0541

376S00014

740S00003

377S0155

377S0184

ALTERNATE FOR

PART NUMBER

197S0480197S0481

197S0479

152S1645152S0461

376S0820376S1080

155S00008

376S0855376S1129

376S1128

128S0376128S0371

138S0639

138S0674138S0843

138S0811138S0846

127S0162127S0164

333S0700333S0704

376S0761

740S0135

377S00011

377S00011

BOM OPTION

REF DES

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

COMMENTS:

Diodes alt to Fairchild

NEC alt to Sanyo

Samsung alt to Murata

Epson Alt to NDK

NDK Alt to Epson

DDS alt to STALL

Cyntec alt to Vishay

Diodes alt to On Semi

Panasonic alt to TDK

Toshiba alt to Diodes

NXP alt to Diodes

NXP alt to Diodes

Kemet alt to Sanyo

Samsung alt to Murata

Samsung alt to Murata

Samsung alt to Murata

Rohm alt to Vishay

Rohm alt to Vishay

Kemet alt to Sanyo

ELPIDA to HYNIX

ON alt to Toshiba

Toshiba alt to Vishay

AEM alt to Tyco

On Semi alt to Infineon

Infineon alt to Infineon

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

D

C

B

B

w w w . c h i n a f i x . c o m

A

SYNC_MASTER=J15_MLB

PAGE TITLE

BOM Configuration

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

6 3

SYNC_DATE=10/31/2012

DRAWING NUMBER

<SCH_NUM>

REVISION

<E4LABEL>

BRANCH

<BRANCH>

PAGE

3 OF 118

SHEET

3 OF 82

124578

SIZE

A

D

8 7 6 5 4 3

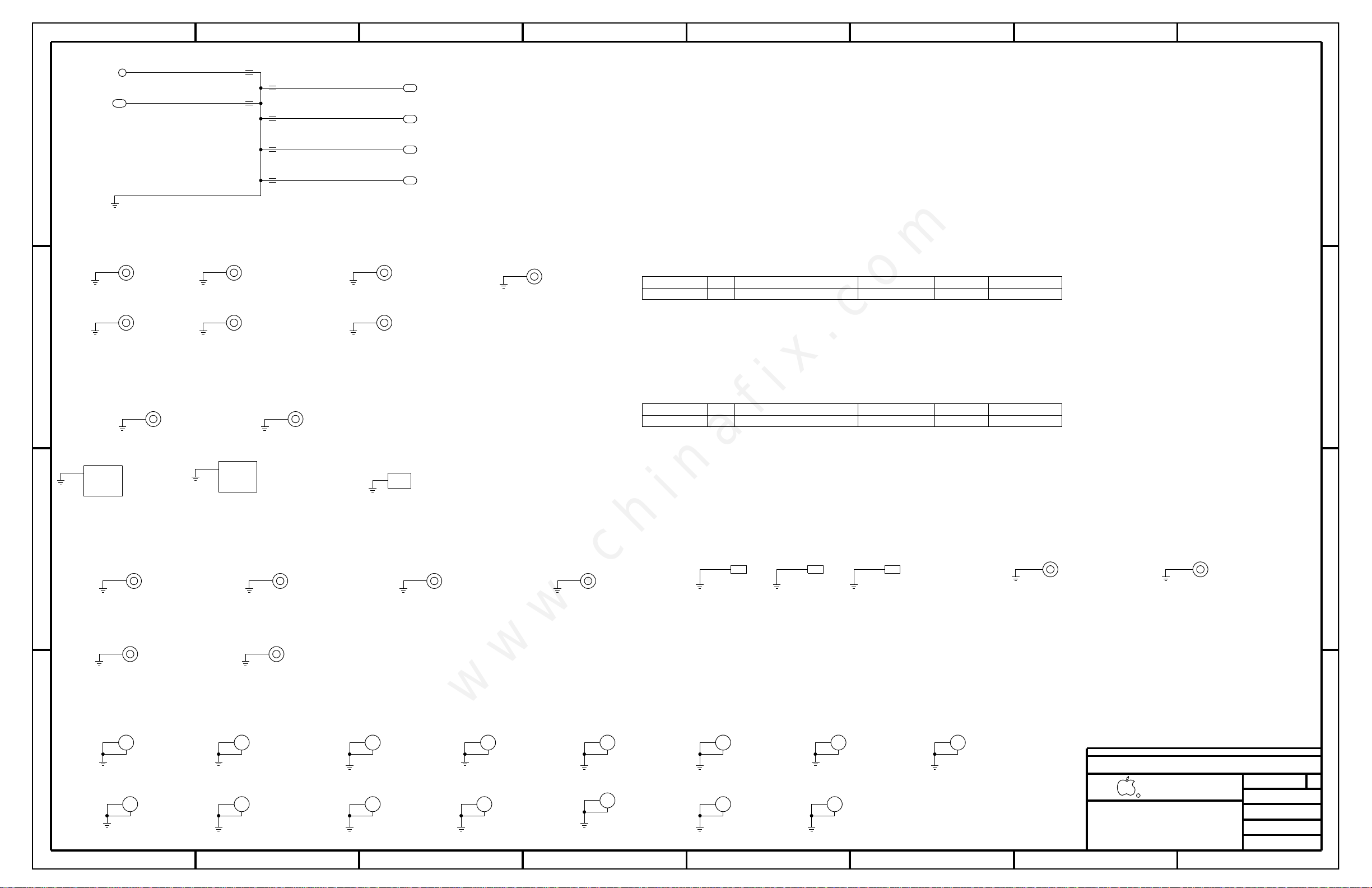

12

ZT0415

2.8R2.3

ZT0450

TH-NSP

SL-2.3X3.9-2.9X4.5

D

|

|

|

|

|

|

|

|

|

|

|

|

-----------------------

SH0427

5.0OD1.85ID-2.35H-SM

1

SH0429

5.0OD1.85ID-2.35H-SM

1

C

1

GND

1

GND

MAKE_BASE=TRUE

X425 THERMAL MODULE STANDOFF

860-00173

Frame Holes

SH0426

5.0OD1.85ID-2.35H-SM

1

SH0428

5.0OD1.85ID-2.35H-SM

1

-----------------------

GND

GND

GND

GND

ZT0470

TH-NSP

1

SL-1.1X0.45-1.4x0.75

ZT0471

TH-NSP

1

SL-1.1X0.45-1.4x0.75

ZT0472

TH-NSP

1

SL-1.1X0.45-1.4x0.75

ZT0473

TH-NSP

1

SL-1.1X0.45-1.4x0.75

860-00184

|

|

|

|

|

|

|

|

|

|

|

|

OMIT_TABLE

SH0425

STDOFF-4.5OD1.8H-SM

1

OMIT_TABLE

SH0423

STDOFF-4.5OD1.8H-SM

1

-----------------------

|

|

|

|

|

|

|

|

|

|

|

|

-----------------------

860-00167

SH0424

4.5OD1.9H-SM-X304

1

|

|

|

|

|

|

|

|

|

|

|

|

PART NUMBER

860-00184

QTY

2

DESCRIPTION

STANDOFF,THERMAL/FAN,W/O MYLAR,X305

REFERENCE DES

SH0423,SH0425

CRITICAL

CRITICAL

BOM OPTION

D

C

5.0OD2.9ID-2.38H

806-9391

1

SH0450

SM

SHLD-MLB-USB-J45

B

POGO-2.3OD-5.5H-SM-LOW-FORCE

POGO-2.3OD-5.5H-SM-LOW-FORCE

SH0431

1

SH0434

1

817-00335

SH0446

1

SM

SM

817-00336

5.0OD2.9ID-2.38H-FD2

806-00452

1

SH0451

SM

SHLD-FENCE-MLB-T29-X305

X425 POGO PINS

POGO-2.3OD-5.5H-SM-LOW-FORCE

POGO-2.3OD-5.5H-SM-LOW-FORCE

SH0432

1

SH0435

1

SH0445

1

SM

SM

APN 806-2247

BR0401

MLB-MTG-BRKT-J5

TH

1

POGO-2.3OD-5.5H-SM-LOW-FORCE

SH0433

SM

1

w w w . c h i n a f i x . c o m

POGO-2.3OD-5.5H-SM-LOW-FORCE

SH0437

SM

1

X425 StAND OFF

860-1448

PART NUMBER

946-3819

QTY

1

DESCRIPTION

D2 MLB DYMAX ADHESIVE SEE-CURE 29993-SC

SMT GND TEST PONTS

ZT0490

2.1SM2.0MM-CIR

SMT-PAD-NSP

1

ZT0491

2.1SM2.0MM-CIR

SMT-PAD-NSP

1

REFERENCE DES

EDGE_BOND

ZT0492

2.1SM2.0MM-CIR

SMT-PAD-NSP

1

CRITICAL

CRITICAL

BOM OPTION

RIO FLEX BRACKET BOSS (860-00166)

SH0480

3.5OD1.85ID-2.0H

1

SH0481

3.5OD1.85ID-2.0H

1

B

SH0440

2.9OD1.2ID-1.35H-SM

A

1

2

SH0441

2.9OD1.2ID-1.35H-SM

1

2

SH0443

2.9OD1.2ID-1.35H-SM

1

2

SH0444

2.9OD1.2ID-1.35H-SM

1

2

SH0460

2.9OD1.2ID-1.35H-SM

1

2

SH0461

2.9OD1.2ID-1.35H-SM

1

2

SH0462

2.9OD1.2ID-1.35H-SM

1

2

SH0465

2.9OD1.2ID-1.35H-SM

1

2

SH0466

2.9OD1.2ID-1.35H-SM

1

2

SH0467

2.9OD1.2ID-1.35H-SM

1

2

SH0470

2.9OD1.2ID-1.35H-SM

1

2

SH0471

2.9OD1.2ID-1.35H-SM

1

2

SH0472

2.9OD1.2ID-1.35H-SM

1

2

SH0473

2.9OD1.2ID-1.35H-SM

1

2

2.9OD1.2ID-1.35H-SM

6 3

SH0474

1

2

SYNC_MASTER=J15_MLB

PAGE TITLE

PD Parts

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=10/31/2012

DRAWING NUMBER

<SCH_NUM>

REVISION

<E4LABEL>

BRANCH

<BRANCH>

PAGE

4 OF 118

SHEET

4 OF 82

124578

SIZE

A

D

8 7 6 5 4 3

12

PPVCOMP_S0_CPU

OMIT_TABLE

U0500

HASWELL

BGA

DMI_S2N_N<0>

12 75

IN

DMI_S2N_N<1>

12 73 75

IN

DMI_S2N_N<2>

12 73 75

IN

DMI_S2N_N<3>

12 73 75

IN

DMI_S2N_P<0>

12 75

D

IN

12 73 75

IN

12 73 75

IN

12 73 75

IN

12 75

OUT

12 73 75

OUT

12 73 75

OUT

12 73 75

OUT

12 75

OUT

12 73 75

OUT

12 73 75

OUT

12 73 75

OUT

12 75

IN

12 75

IN

DMI_S2N_P<1>

DMI_S2N_P<2>

DMI_S2N_P<3>

DMI_N2S_N<0>

DMI_N2S_N<1>

DMI_N2S_N<2>

DMI_N2S_N<3>

DMI_N2S_P<0>

DMI_N2S_P<1>

DMI_N2S_P<2>

DMI_N2S_P<3>

FDI_CSYNC

FDI_INT

AB2

AB3

AC3

AC1

AB1

AB4

AC4

AC2

AF2

AF4

AG4

AG2

AF1

AF3

AG3

AG1

F11

F12

DMI_RX0*

DMI_RX1*

DMI_RX2*

DMI_RX3*

DMI_RX0

DMI_RX1

DMI_RX2

DMI_RX3

DMI_TX0*

DMI_TX1*

DMI_TX2*

DMI_TX3*

DMI_TX0

DMI_TX1

DMI_TX2

DMI_TX3

FDI_CSYNC

DISP_INT

C

B

SYM 1 OF 12

PEG_RCOMP

PEG_RX0*

PEG_RX1*

PEG_RX2*

PEG_RX3*

PEG_RX4*

PEG_RX5*

PEG_RX6*

PEG_RX7*

DMI

PEG_RX8*

PEG_RX9*

PEG_RX10*

PEG_RX11*

PEG_RX12*

PEG_RX13*

PEG_RX14*

PEG_RX15*

PEG_RX0

PEG_RX1

FDI

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX0*

PEG_TX1*

PEG_TX2*

PEG_TX3*

PEG_TX4*

PEG_TX5*

PEG_TX6*

PEG_TX7*

PEG_TX8*

PCI EXPRESS BASED INTERFACE SIGNALS

PEG_TX9*

PEG_TX10*

PEG_TX11*

PEG_TX12*

PEG_TX13*

PEG_TX14*

PEG_TX15*

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

AH6

E10

C10

B10

E9

D9

B9

L5

L2

M4

L4

M2

V5

V4

V1

Y3

Y2

F10

D10

A10

F9

C9

A9

M5

L1

M3

L3

M1

Y5

V3

V2

Y4

Y1

B6

C5

E6

D4

G4

E3

J5

G3

J3

J2

T6

R6

R2

R4

T4

T1

C6

B5

D6

E4

G5

E2

J6

G2

J4

J1

T5

R5

R1

R3

T3

T2

CPU_PEG_RCOMP

75

PCIE_SSD_D2R_N<0>

PCIE_SSD_D2R_N<1>

PCIE_SSD_D2R_N<2>

PCIE_SSD_D2R_N<3>

=PEG_D2R_N<4>

=PEG_D2R_N<5>

=PEG_D2R_N<6>

=PEG_D2R_N<7>

PCIE_TBT_D2R_N<0>

PCIE_TBT_D2R_N<1>

PCIE_TBT_D2R_N<2>

PCIE_TBT_D2R_N<3>

TP_PEG_D2RN<12>

TP_PEG_D2RN<13>

TP_PEG_D2RN<14>

TP_PEG_D2RN<15>

PCIE_SSD_D2R_P<0>

PCIE_SSD_D2R_P<1>

PCIE_SSD_D2R_P<2>

PCIE_SSD_D2R_P<3>

=PEG_D2R_P<4>

=PEG_D2R_P<5>

=PEG_D2R_P<6>

=PEG_D2R_P<7>

PCIE_TBT_D2R_P<0>

PCIE_TBT_D2R_P<1>

PCIE_TBT_D2R_P<2>

PCIE_TBT_D2R_P<3>

TP_PEG_D2RP<12>

TP_PEG_D2RP<13>

TP_PEG_D2RP<14>

TP_PEG_D2RP<15>

PCIE_SSD_R2D_C_N<0>

PCIE_SSD_R2D_C_N<1>

PCIE_SSD_R2D_C_N<2>

PCIE_SSD_R2D_C_N<3>

=PEG_R2D_C_N<4>

=PEG_R2D_C_N<5>

=PEG_R2D_C_N<6>

=PEG_R2D_C_N<7>

PCIE_TBT_R2D_C_N<0>

PCIE_TBT_R2D_C_N<1>

PCIE_TBT_R2D_C_N<2>

PCIE_TBT_R2D_C_N<3>

TP_PEG_R2D_CN<12>

TP_PEG_R2D_CN<13>

TP_PEG_R2D_CN<14>

TP_PEG_R2D_CN<15>

PCIE_SSD_R2D_C_P<0>

PCIE_SSD_R2D_C_P<1>

PCIE_SSD_R2D_C_P<2>

PCIE_SSD_R2D_C_P<3>

=PEG_R2D_C_P<4>

=PEG_R2D_C_P<5>

=PEG_R2D_C_P<6>

=PEG_R2D_C_P<7>

PCIE_TBT_R2D_C_P<0>

PCIE_TBT_R2D_C_P<1>

PCIE_TBT_R2D_C_P<2>

PCIE_TBT_R2D_C_P<3>

TP_PEG_R2D_CP<12>

TP_PEG_R2D_CP<13>

TP_PEG_R2D_CP<14>

TP_PEG_R2D_CP<15>

1

R0510

24.9

1%

1/16W

MF-LF

402

2

35 71 75

IN

35 71 75

IN

35 71 75

IN

35 71 75

IN

71

IN

71

IN

71

IN

71

IN

28 71 75

IN

28 71 75

IN

28 71 75

IN

28 71 75

IN

71

IN

71

IN

71

IN

71

IN

35 71 75

IN

35 71 75

IN

35 71 75

IN

35 71 75

IN

71

IN

71

IN

71

IN

71

IN

28 71 75

IN

28 71 75

IN

28 71 75

IN

28 71 75

IN

71

IN

71

IN

71

IN

71

IN

35 71 75

OUT

35 71 75

OUT

35 71 75

OUT

35 71 75

OUT

71

OUT

71

OUT

71

OUT

71

OUT

28 71 75

OUT

28 71 75

OUT

28 71 75

OUT

28 71 75

OUT

71

OUT

71

OUT

71

OUT

71

OUT

35 71 75

OUT

35 71 75

OUT

35 71 75

OUT

35 71 75

OUT

71

OUT

71

OUT

71

OUT

71

OUT

28 71 75

OUT

28 71 75

OUT

28 71 75

OUT

28 71 75

OUT

71

OUT

71

OUT

71

OUT

71

OUT

5 8

OMIT_TABLE

U0500

HASWELL

BGA

DP_TBTSNK0_ML_C_N<0>

28 71 75

DP_TBTSNK0_ML_C_P<0>

28 71 75

DP_TBTSNK0_ML_C_N<1>

28 71 75

DP_TBTSNK0_ML_C_P<1>

28 71 75

DP_TBTSNK0_ML_C_N<2>

28 71 75

DP_TBTSNK0_ML_C_P<2>

28 71 75

DP_TBTSNK0_ML_C_N<3>

28 71 75

DP_TBTSNK0_ML_C_P<3>

28 71 75

DP_TBTSNK1_ML_C_N<0>

28 71 75

DP_TBTSNK1_ML_C_P<0>

28 71 75

DP_TBTSNK1_ML_C_N<1>

28 71 75

DP_TBTSNK1_ML_C_P<1>

28 71 75

DP_TBTSNK1_ML_C_N<2>

28 71 75

DP_TBTSNK1_ML_C_P<2>

28 71 75

DP_TBTSNK1_ML_C_N<3>

28 71 75

DP_TBTSNK1_ML_C_P<3>

28 71 75

TP_DP_IG_D_MLN<2>

71

TP_DP_IG_D_MLP<2>

71

HDMI_CLK_N

69 71 72 75

HDMI_CLK_P

69 71 72 75

TP_DP_IG_D_MLN<0>

71

TP_DP_IG_D_MLP<0>

71

TP_DP_IG_D_MLN<1>

71

TP_DP_IG_D_MLP<1>

71

Port D pins out of order

to match Intel symbol.

C25

D25

A25

B25

C24

D24

A24

B24

C21

D21

A21

B21

C20

D20

A20

B20

C16

D16

A16

B16

C17

D17

A17

B17

DDIB_TXN0

DDIB_TXP0

DDIB_TXN1

DDIB_TXP1

DDIB_TXN2

DDIB_TXP2

DDIB_TXN3

DDIB_TXP3

DDIC_TXN0

DDIC_TXP0

DDIC_TXN1

DDIC_TXP1

DDIC_TXN2

DDIC_TXP2

DDIC_TXN3

DDIC_TXP3

DDID_TXN2

DDID_TXP2

DDID_TXN3

DDID_TXP3

DDID_TXN0

DDID_TXP0

DDID_TXN1

DDID_TXP1

SYM 10 OF 12

EDP_AUXN

EDP_AUXP

EDP_HPD

EDP_TXN0

EDP

EDP_TXN1

EDP_TXP0

EDP_TXP1

EDP_RCOMP

EDP_DISP_UTIL

DIGITAL DISPLAY INTERFACES

FDI_TXN0

FDI_TXP0

FDI

FDI_TXN1

FDI_TXP1

F15

F14

E14

C14

A12

D14

B12

AG6

E12

C12

D12

A14

B14

OMIT_TABLE

U0500

HASWELL

TP0500

TP0510

TP0520

TP0530

TP0521

TP

TP-P6

TP

TP-P6

TP

TP-P6

TP

TP-P6

TP

TP-P6

BGA

CPU_DC_A3_B3

5

CPU_DC_A4

1

CPU_DC_A51

1

CPU_DC_A52_B52

5

CPU_DC_A53_B53

5

CPU_DC_B2_C3

5

CPU_DC_A3_B3

5 5

CPU_DC_A52_B52

5

CPU_DC_A53_B53

5

CPU_DC_B54_C54

5

1

CPU_DC_BC1

CPU_DC_BC54

1

CPU_DC_BD1_BE1

5

CPU_DC_BD54_BE54

5

CPU_DC_BD1_BE1

5

CPU_DC_BE2_BF2

5

CPU_DC_BE3_BF3

5

CPU_DC_BE52_BF52

5

CPU_DC_BE53_BF53

5

CPU_DC_BD54_BE54

5

CPU_DC_BE2_BF2

5

CPU_DC_BE3_BF3

5

CPU_DC_BF4

1

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

A51

A52

A53

B52

B53

B54

BC1

BC54

BD1

BD54

BE1

BE2

BE3

BE52

BE53

BE54

BF2

BF3

BF4

A3

A4

B2

B3

SYM 12 OF 12

RESERVED

DAISY_CHAIN_NCTF

DAISY_CHAIN_NCTF

RSVD132

RSVD133

RSVD134

RSVD135

RSVD136

RSVD137

RSVD138

RSVD139

NO_TESTNO_TEST

BF51

BF52

BF53

C1

C2

C3

C54

D1

D54

CPU Daisy-Chain Strategy:

Each corner of CPU has two testpoints.

Other corner test signals connected in

daisy-chain fashion. Continuity should

exist between both TP’s on each corner.

AN35

AN37

AF9

AE9

G14

G17

AD45

AG45

PPVCCIO_S0_CPU

1

R0531

10k

5%

1/16W

MF-LF

402

2

DP_INT_AUXCH_C_N

DP_INT_AUXCH_C_P

DP_IG_A_HPD_L

DP_INT_ML_C_N<0>

DP_INT_ML_C_N<1>

DP_INT_ML_C_P<0>

DP_INT_ML_C_P<1>

CPU_EDP_RCOMP

75

TP_EDP_DISP_UTIL

DP_INT_ML_C_N<2>

DP_INT_ML_C_P<2>

DP_INT_ML_C_N<3>

DP_INT_ML_C_P<3>

CPU_DC_BF51

CPU_DC_BE52_BF52

TRUE

CPU_DC_BE53_BF53

TRUE

CPU_DC_C1_C2

TRUE

CPU_DC_C1_C2

TRUE

CPU_DC_B2_C3

TRUE

CPU_DC_B54_C54

TRUE

CPU_DC_D1

CPU_DC_D54

NC

NC

NC

NC

NC

NC

NC

NC

6 8

10 18 58

68 71 75

68 71 75

20

68 71 75

68 71 75

68 71 75

68 71 75

PPVCOMP_S0_CPU

1

R0530

24.9

1%

1/16W

MF-LF

402

2

68 71 75

68 71 75

68 71 75

68 71 75

5

5

5

5

5

1

TP

TP-P6

1

TP

TP-P6

1

TP

TP-P6

D

5 8

C

TP0531

TP0501

TP0511

B

w w w . c h i n a f i x . c o m

A

SYNC_MASTER=CLEAN_X305_PEG

PAGE TITLE

CPU DMI/PEG/FDI/RSVD

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

6 3

SYNC_DATE=02/18/2014

DRAWING NUMBER

<SCH_NUM>

REVISION

<E4LABEL>

BRANCH

<BRANCH>

PAGE

5 OF 118

SHEET

5 OF 82

124578

SIZE

A

D

8 7 6 5 4 3

12

OMIT_TABLE

D

PPVCCIO_S0_CPU

5 8

10 18 58

1

R0601

62

5%

1/16W

MF-LF

402

2

R0603

56

1%

1/16W

MF-LF

402

3.32K

1/16W

MF-LF

2 1

5%

1/16W

MF-LF

402

1

2

1

1%

402

2

CPU_PROCHOT_L

41 42 58 75

BI

PP1V35_S3RS0_CPUDDR

8

10 21 66 67 70 82

R0620

PLACE_NEAR=R0621.2:1mm

PM_MEM_PWRGD

12 21 75

IN

PLACE_NEAR=U0500.AP48:51.562mm

1.82K

R0621

C

CPU_CATERR_L

41 75

OUT

CPU_PECI

14 42 75

BI

CPU_PROCHOT_R_L

PM_THRMTRIP_L

14 42 75

OUT

PM_SYNC

12 75

IN

CPU_PWRGD

14 18 75

IN

CPU_RESET_L

14

IN

CPU_CLK135M_DPLLREF_N

11 75

IN

CPU_CLK135M_DPLLREF_P

11 75

IN

CPU_CLK135M_DPLLSS_N

11 75

IN

CPU_CLK135M_DPLLSS_P

11 75

IN

DMI_CLK100M_CPU_N

11 75

IN

DMI_CLK100M_CPU_P

11 75

IN

PLACE_NEAR=U0500.F50:157mm

R0611

10K

1/16W

MF-LF

1

5%

402

2

C51

NC

PROC_DETECT*

G50

CATERR*

G51

PECI

E50

PROCHOT*

D53

THERMTRIP*

D52

PM_SYNC

F50

PWRGOOD

AP48

SM_DRAMPWROK

L54

PLTRSTIN*

AC6

DPLL_REF_CLKN

AE6

DPLL_REF_CLKP

V6

SSC_DPLL_REF_CLKN

Y6

SSC_DPLL_REF_CLKP

AB6

BCLKN

AA6

BCLKP

U0500

HASWELL

BGA

SYM 2 OF 12

THERMAL

PWR

CLOCK

DDR3

JTAG

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST*

(IPU)

PRDY*

(IPU)

PREQ*

(IPD)

(IPU)

(IPU)

TRST*

(IPU)

DBR*

(IPU)

BPM0*

(IPU)

BPM1*

(IPU)

BPM2*

(IPU)

BPM3*

(IPU)

BPM4*

(IPU)

BPM5*

BPM6*

(IPU)

BPM7*

(IPU)

TCK

TMS

TDI

TDO

BB51

BB53

BB52

BE51

N53

N52

N54

M51

M53

N49

M49

F53

R51

R50

P49

N50

R49

P53

U51

P51

CPU_SM_RCOMP<0>

75

CPU_SM_RCOMP<1>

75

75

CPU_SM_RCOMP<2>

CPU_MEM_RESET_L

XDP_CPU_PRDY_L

XDP_CPU_PREQ_L

XDP_CPU_TCK

XDP_CPU_TMS

XDP_CPUPCH_TRST_L

XDP_CPU_TDI

XDP_CPU_TDO

XDP_DBRESET_L

XDP_BPM_L<0>

XDP_BPM_L<1>

XDP_BPM_L<2>

XDP_BPM_L<3>

XDP_BPM_L<4>

XDP_BPM_L<5>

XDP_BPM_L<6>

XDP_BPM_L<7>

PLACE_NEAR=U0500.BB52:12.7mm

21

OUT

18 72 75

OUT

18 72 75

IN

18 72 75

IN

18 72 75

IN

18 72 75

IN

18 72 75

IN

18 72 75

OUT

18 19 75

OUT

18 75

BI

18 75

BI

18 75

BI

18 75

BI

18 75

BI

18 75

BI

18 75

BI

18 75

BI

PLACE_NEAR=U0500.BB53:12.7mm

PLACE_NEAR=U0500.BB51:12.7mm

1

R0614

100

1%

1/16W

MF-LF

402

2

1

R0613

75

1%

1/16W

MF-LF

402

2

1

R0612

100

1%

1/16W

MF-LF

402

2

D

C

B

CFG [7] :PEG DEFER TRAINING 1 = (DEFAULT) IMMEDIATELY AFTER xxRESETB 0 = WAIT FOR BIOS

CFG [6:5] :PCIE BIFURCATION 11 = 1 X16 (DEFAULT) 10 = 2 X8 01 = RSVD 00 = X8, X4, X4

CFG [4] :eDP ENABLE/DISABLE 1 = DISABLED 0 = ENABLED

CFG [3] :PCIE x4 LANE REVERSAL 1 = NORMAL OPERATION 0 = LANES REVERSED

CFG [2] :PCIE x16 LANE REVERSAL 1 = NORMAL OPERATION 0 = LANES REVERSED

These can be placed close to

J1800 and only for debug access

NOSTUFF

R0649

1/16W

MF-LF

NOSTUFF

1

1K

5%

402

R0648

1/16W

2

MF-LF

NOSTUFF

1

1

R0643

1K

1K

5%

5%

1/16W

MF-LF

402

402

2

2

NOSTUFF

R0641

1/16W

MF-LF

A

NOSTUFF

R0647

1/16W

MF-LF

1

1K

5%

402

2

CPUCFG6_PD

R0646

1/16W

MF-LF

1K

402

5%

1

2

CPUCFG5_PD

1

R0645

1K

5%

1/16W

MF-LF

402

2

EDP:YES

R0644

1/16W

MF-LF

1K

5%

402

1K

5%

402

1

2

1

2

CPU_CFG<16>

CPU_CFG<9>

CPU_CFG<3>

CPU_CFG<1>

CPU_CFG<0>

NOSTUFF

1

R0640

1K

5%

1/16W

MF-LF

402

2

CPU_CFG<7>

CPU_CFG<6>

CPU_CFG<5>

CPU_CFG<4>

CPU_CFG<2>

NOSTUFF

1

R0642

1K

5%

1/16W

MF-LF

402

2

6

18 75

6

18 75

6

18 72 75

6

18 75

6

18 75

6

18 75

6

18 75

6

18 75

6

18 75

6

18 75

BOM GROUP

CPUPEG:X8X8

CPUPEG:X8X4X4

To use PEG X16 configuration, simply remove CPUPEG:X8X8 and CPUPEG:X8X4X4 from BOMs.

OMIT_TABLE

U0500

HASWELL

BGA

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

SYM 11 OF 12

RESERVED

CFG_RCOMP

(IPU)

(IPU)

RSVD_TP17

RSVD_TP18

TP_CPU_RSVD_TP23

TP_CPU_RSVD_TP24

TP_CPU_RSVD_TP25

TP_CPU_RSVD_TP26

TP_CPU_RSVD_TP27

TP_CPU_RSVD_TP28

CPU_TESTLO_F21

1

R0680

49.9

1/16W

MF-LF

1%

402

2

PPVCC_S0_CPU

8

10 46 59 70 72

TP_CPU_RSVD_TP35

TP_CPU_RSVD_TP36

TP_CPU_RSVD_TP37

TP_CPU_RSVD_TP38

TP_CPU_RSVD_TP39

CPU_TESTLO_F20

1

R0685

49.9

1%

1/16W

MF-LF

402

2

w w w . c h i n a f i x . c o m

CPU_CFG<0>

6

18 75

CPU_CFG<1>

6

18 75

CPU_CFG<2>

6

18 75

CPU_CFG<3>

6

18 72 75

CPU_CFG<4>

6

18 75

CPU_CFG<5>

6

18 75

CPU_CFG<6>

6

18 75

CPU_CFG<7>

6

18 75

CPU_CFG<8>

18 75

CPU_CFG<9>

6

18 75

CPU_CFG<10>

18 75

CPU_CFG<11>

18 75

CPU_CFG<12>

18 75

CPU_CFG<13>

18 75

CPU_CFG<14>

18 75

CPU_CFG<15>

18 75

BE4

RSVD_TP23

BD3

RSVD_TP24

F6

RSVD_TP25

G6

RSVD_TP26

G21

RSVD_TP27

G24

RSVD_TP28

F21

TESTLO_F21

G19

VSS_G19

F51

VSS_F51

F52

VSS_F52

F22

VCC_F22

L52

RSVD_TP35

L53

RSVD_TP36

L51

RSVD_TP37

F24

RSVD_TP38

F25

RSVD_TP39

F20

TESTLO_F20

AG49

CFG0

AD49

CFG1

AC49

CFG2

AE49

CFG3

Y50

CFG4

AB49

CFG5

V51

CFG6

W51

CFG7

Y49

CFG8

Y54

CFG9

Y53

CFG10

W53

CFG11

U53

CFG12

V54

CFG13

R53

CFG14

R52

CFG15

L49

RSVD50

RSVD51

E5

RSVD52

NC

NC

NC

BOM OPTIONS

CPUCFG5_PD

CPUCFG6_PD,CPUCFG5_PD

RSVD_TP1

RSVD_TP2

RSVD_TP3

RSVD_TP4

CFG16

CFG18

CFG17

CFG19

RSVD92

RSVD93

RSVD94

RSVD95

RSVD9

RSVD10

RSVD11

RSVD41

RSVD42

RSVD16

VSS_H54

VSS_H53

VSS_H51

VSS_H52

RSVD47

RSVD48

RSVD49

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

F1

E1

A5

A6

R54

Y52

V53

Y51

V52

B50

AH49

AM48

AU27

AU26

BD4

BC4

AL6

F8

F16

G12

G10

H54

H53

H51

H52

N51L50

G53

H50

TP_CPU_RSVD_TP1

TP_CPU_RSVD_TP2

TP_CPU_RSVD_TP3

TP_CPU_RSVD_TP4

CPU_CFG_RCOMP

CPU_CFG<16>

CPU_CFG<18>

CPU_CFG<17>

CPU_CFG<19>

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

TP_CPU_RSVD_TP17

TP_CPU_RSVD_TP18

TP_CPU_RSVD_TP47

TP_CPU_RSVD_TP48

TP_CPU_RSVD_TP49

6

18 75

18 75

18 75

18 75

1

R0690

49.9

1%

1/16W

MF-LF

402

2

6 3

SYNC_MASTER=J15_REFERENCE

PAGE TITLE

CPU Clock/Misc/JTAG/CFG

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=12/18/2012

DRAWING NUMBER

REVISION

BRANCH

PAGE

SHEET

124578

<SCH_NUM>

<E4LABEL>

<BRANCH>

6 OF 118

6 OF 82

SIZE

B

A

D

8 7 6 5 4 3

12

OMIT_TABLE

MEM_A_DQ<0>

23 24 78

BI

MEM_A_DQ<1>

23 24 78

BI

MEM_A_DQ<2>

23 24 78

BI

MEM_A_DQ<3>

23 24 78

BI

MEM_A_DQ<4>

23 24 78

BI

MEM_A_DQ<5>

23 24 78

BI

MEM_A_DQ<6>

23 24 78

BI

MEM_A_DQ<7>

23 24 78

BI

MEM_A_DQ<8>

23 24 78

D

C

B

BI

MEM_A_DQ<9>

23 24 78

BI

MEM_A_DQ<10>

23 24 78

BI

MEM_A_DQ<11>

23 24 78

BI

MEM_A_DQ<12>

23 24 78

BI

MEM_A_DQ<13>

23 24 78

BI

MEM_A_DQ<14>

23 24 78

BI

MEM_A_DQ<15>

23 24 78

BI

MEM_A_DQ<16>

23 24 78

BI

MEM_A_DQ<17>

23 24 78

BI

MEM_A_DQ<18>

23 24 78

BI

MEM_A_DQ<19>

23 24 78

BI

MEM_A_DQ<20>

23 24 78

BI

MEM_A_DQ<21>

23 24 78

BI

MEM_A_DQ<22>

23 24 78

BI

MEM_A_DQ<23>

23 24 78

BI

MEM_A_DQ<24>

23 24 78

BI

MEM_A_DQ<25>

23 24 78

BI

MEM_A_DQ<26>

23 24 78

BI

MEM_A_DQ<27>

23 24 78

BI

MEM_A_DQ<28>

23 24 78

BI

MEM_A_DQ<29>

23 24 78

BI

MEM_A_DQ<30>

23 24 78

BI

MEM_A_DQ<31>

23 24 78

BI

MEM_A_DQ<32>

23 24 78

BI

MEM_A_DQ<33>

23 24 78

BI

MEM_A_DQ<34>

23 24 78

BI

MEM_A_DQ<35>

23 24 78

BI

MEM_A_DQ<36>

23 24 78

BI

MEM_A_DQ<37>

23 24 78

BI

MEM_A_DQ<38>

23 24 78

BI

MEM_A_DQ<39>

23 24 78

BI

MEM_A_DQ<40>

23 24 78

BI

MEM_A_DQ<41>

23 24 78

BI

MEM_A_DQ<42>

23 24 78

BI

MEM_A_DQ<43>

23 24 78

BI

MEM_A_DQ<44>

23 24 78

BI

MEM_A_DQ<45>

23 24 78

BI

MEM_A_DQ<46>

23 24 78

BI

MEM_A_DQ<47>

23 24 78

BI

MEM_A_DQ<48>

23 24 78

BI

MEM_A_DQ<49>

23 24 78

BI

MEM_A_DQ<50>

23 24 78

BI

MEM_A_DQ<51>

23 24 78

BI

MEM_A_DQ<52>

23 24 78

BI

MEM_A_DQ<53>

23 24 78

BI

MEM_A_DQ<54>

23 24 78

BI

MEM_A_DQ<55>

23 24 78

BI

MEM_A_DQ<56>

23 24 78

BI

MEM_A_DQ<57>

23 24 78

BI

MEM_A_DQ<58>

23 24 78

BI

MEM_A_DQ<59>

23 24 78

BI

MEM_A_DQ<60>

23 24 78

BI

MEM_A_DQ<61>

23 24 78

BI

MEM_A_DQ<62>

23 24 78

BI

MEM_A_DQ<63>

23 24 78

BI

CPU_DIMM_VREFCA

22

OUT

CPU_DIMMA_VREFDQ

22 75

OUT

CPU_DIMMB_VREFDQ

22 75

OUT

AH54

SA_DQ0

AH52

SA_DQ1

AK51

SA_DQ2

AK54

SA_DQ3

AH53

SA_DQ4

AH51

SA_DQ5

AK52

SA_DQ6

AK53

SA_DQ7

AN54

SA_DQ8

AN52

SA_DQ9

AR51

SA_DQ10

AR53

SA_DQ11

AN53

SA_DQ12

AN51

SA_DQ13

AR52

SA_DQ14

AR54

SA_DQ15

AV52

SA_DQ16

AV53

SA_DQ17

AY52

SA_DQ18

AY51

SA_DQ19

AV51

SA_DQ20

AV54

SA_DQ21

AY54

SA_DQ22

AY53

SA_DQ23

AY47

SA_DQ24

AY49

SA_DQ25

BA47

SA_DQ26

BA45

SA_DQ27

AY45

SA_DQ28

AY43

SA_DQ29

BA49

SA_DQ30

BA43

SA_DQ31

BF14

SA_DQ32

BC14

SA_DQ33

BC11

SA_DQ34

BF11

SA_DQ35

BE14

SA_DQ36

BD14

SA_DQ37

BD11

SA_DQ38

BE11

SA_DQ39

BC9

SA_DQ40

BE9

SA_DQ41

BE6

SA_DQ42

BC6

SA_DQ43

BD9

SA_DQ44

BF9

SA_DQ45

BE5

SA_DQ46

BD6

SA_DQ47

BB4

SA_DQ48

BC2

SA_DQ49

AW3

SA_DQ50

AW2

SA_DQ51

BB3

SA_DQ52

BB2

SA_DQ53

AW4

SA_DQ54

AW1

SA_DQ55

AU3

SA_DQ56

AU1

SA_DQ57

AR1

SA_DQ58

AR4

SA_DQ59

AU2

SA_DQ60

AU4

SA_DQ61

AR2

SA_DQ62

AR3

SA_DQ63

AM6

SM_VREF

AR6

SA_DIMM_VREFDQ

AN6

SB_DIMM_VREFDQ

BC53

NC

RSVD25

U0500

HASWELL

BGA

SYM 3 OF 12

MEMORY CHANNEL A

VSS_BC21

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

RSVD160

SA_CKN0

SA_CKP0

SA_CKE0

SA_CKN1

SA_CKP1

SA_CKE1

SA_CKN2

SA_CKP2

SA_CKE2

SA_CKN3

SA_CKP3

SA_CKE3

SA_CS0*

SA_CS1*

SA_CS2*

SA_CS3*

SA_ODT0

SA_ODT1

SA_ODT2

SA_ODT3

SA_BS0

SA_BS1

SA_BS2

SA_RAS*

SA_WE*

SA_CAS*

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

RSVD161

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

RSVD162

RSVD163

RSVD164

RSVD165

RSVD166

RSVD167

RSVD168

RSVD169

RSVD170

BD31

BE25

BF25

BE34

BD25

BC25

BF34

BE23

BF23

BC34

BD23

BC23

BD34

BE16

BC17

BE17

BD16

BC16

BF16

BF17

BD17

BC20

BD21

BD32

MEM_A_CLK_N<0>

MEM_A_CLK_P<0>

MEM_A_CKE<0>

MEM_A_CLK_N<1>

MEM_A_CLK_P<1>

MEM_A_CKE<1>

NC

NC

NC

NC

NC

NC

MEM_A_CS_L<0>

MEM_A_CS_L<1>

NC

NC

MEM_A_ODT<0>

MEM_A_ODT<1>

NC

NC

MEM_A_BA<0>

MEM_A_BA<1>

MEM_A_BA<2>

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

23 27 78

23 27 78

23 27 78

24 27 78

24 27 78

24 27 78

23 27 78

24 27 78

23 27 78

24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

BC21

BF20

BF21

BE21

BD28

BD27

BF28

BE28

BF32

BC27

BF27

BC28

BE27

BC32

BD20

BF31

BC31

BE20

BE32

BE31

AJ52

AP53

AW52

AY46

BD12

BE7

BA3

AT2

AW39

AJ53

AP52

AW53

BA46

BE12

BD7

BA2

AT3

AW40

BA40

AY40

BA39

AY39

AV40

AU40

AV39

AU39

MEM_A_RAS_L

MEM_A_WE_L

MEM_A_CAS_L

MEM_A_A<0>

MEM_A_A<1>

MEM_A_A<2>

MEM_A_A<3>

MEM_A_A<4>

MEM_A_A<5>

MEM_A_A<6>

MEM_A_A<7>

MEM_A_A<8>

MEM_A_A<9>

MEM_A_A<10>

MEM_A_A<11>

MEM_A_A<12>

MEM_A_A<13>

MEM_A_A<14>

MEM_A_A<15>

MEM_A_DQS_N<0>

MEM_A_DQS_N<1>

MEM_A_DQS_N<2>

MEM_A_DQS_N<3>

MEM_A_DQS_N<4>

MEM_A_DQS_N<5>

MEM_A_DQS_N<6>

MEM_A_DQS_N<7>

NC

MEM_A_DQS_P<0>

MEM_A_DQS_P<1>

MEM_A_DQS_P<2>

MEM_A_DQS_P<3>

MEM_A_DQS_P<4>

MEM_A_DQS_P<5>

MEM_A_DQS_P<6>

MEM_A_DQS_P<7>

NC

NC

NC NC

NC

NC

NC

NC

NC

NC

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 27 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

23 24 78

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

25 26 78

BI

MEM_B_DQ<0>

MEM_B_DQ<1>

MEM_B_DQ<2>

MEM_B_DQ<3>

MEM_B_DQ<4>

MEM_B_DQ<5>

MEM_B_DQ<6>

MEM_B_DQ<7>

MEM_B_DQ<8>

MEM_B_DQ<9>

MEM_B_DQ<10>

MEM_B_DQ<11>

MEM_B_DQ<12>

MEM_B_DQ<13>

MEM_B_DQ<14>

MEM_B_DQ<15>

MEM_B_DQ<16>

MEM_B_DQ<17>

MEM_B_DQ<18>

MEM_B_DQ<19>

MEM_B_DQ<20>

MEM_B_DQ<21>

MEM_B_DQ<22>

MEM_B_DQ<23>

MEM_B_DQ<24>

MEM_B_DQ<25>

MEM_B_DQ<26>

MEM_B_DQ<27>

MEM_B_DQ<28>

MEM_B_DQ<29>

MEM_B_DQ<30>

MEM_B_DQ<31>

MEM_B_DQ<32>

MEM_B_DQ<33>

MEM_B_DQ<34>

MEM_B_DQ<35>

MEM_B_DQ<36>

MEM_B_DQ<37>

MEM_B_DQ<38>

MEM_B_DQ<39>

MEM_B_DQ<40>

MEM_B_DQ<41>

MEM_B_DQ<42>

MEM_B_DQ<43>

MEM_B_DQ<44>

MEM_B_DQ<45>

MEM_B_DQ<46>

MEM_B_DQ<47>

MEM_B_DQ<48>

MEM_B_DQ<49>

MEM_B_DQ<50>

MEM_B_DQ<51>

MEM_B_DQ<52>

MEM_B_DQ<53>

MEM_B_DQ<54>

MEM_B_DQ<55>

MEM_B_DQ<56>

MEM_B_DQ<57>

MEM_B_DQ<58>

MEM_B_DQ<59>

MEM_B_DQ<60>

MEM_B_DQ<61>

MEM_B_DQ<62>

MEM_B_DQ<63>

AC54

AC52

AE51

AE54

AC53

AC51

AE52

AE53

AU47

AU49

AV43

AV45

AU43

AU45

AV47

AV49

BC49

BE49

BD47

BC47

BD49

BD50

BE47

BF47

BE44

BD44

BC42

BF42

BF44

BC44

BD42

BE42

BA16

AU16

BA15

AV15

AY16

AV16

AY15

AU15

AU12

AY12

BA10

AU10

AV12

BA12

AY10

AV10

AU8

BA8

AV6

BA6

AV8

AY8

AU6

AY6

AM2

AM3

AK1

AK4

AM1

AM4

AK2

AK3

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ15

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

OMIT_TABLE

U0500

HASWELL

BGA

SYM 4 OF 12

MEMORY CHANNEL B

RSVD171

SB_CKN0

SB_CKP0

SB_CKE0

SB_CKN1

SB_CKP1

SB_CKE1

SB_CKN2

SB_CKP2

SB_CKE2

SB_CKN3

SB_CKP3

SB_CKE3SB_DQ14

SB_CS0*SB_DQ16

SB_CS1*SB_DQ17

SB_CS2*SB_DQ18

SB_CS3*SB_DQ19

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_BS0

SB_BS1

SB_BS2

VSS_AU30

SB_RAS*

SB_WE*

SB_CAS*

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

RSVD172

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

RSVD173

RSVD174

RSVD175

RSVD176

RSVD177

RSVD178

RSVD179

RSVD180

RSVD181

AY36

AW27

AV27

AU36

AW26

AV26

AU35

BA26

AY26

AV35

BA27

AY27

AV36

BA20

AY19

AU19

AW20

AY20

BA19

AV19

AW19

AY23

BA23

BA36

AU30

AV23

AW23

AV20

BA30

AW30

AY30

AV30

AW32

AY32

AT30

AV32

BA32

AU32

AU23

AY35

AW35

AU20

AW36

BA35

AD52

AU46

BD48

BD43

AW16

AW10

AW8

AL2

BE38

AD53

AV46

BE48

BE43

AW15

AW12

AW6

AL3

BD38

BF39

BE39

BF37

BE37

BD39

BC39

BC37

BD37

NCNC

MEM_B_CLK_N<0>

MEM_B_CLK_P<0>

MEM_B_CKE<0>

MEM_B_CLK_N<1>

MEM_B_CLK_P<1>

MEM_B_CKE<1>

NC

NC

NC

NC

NC

NC

MEM_B_CS_L<0>

MEM_B_CS_L<1>

NC

NC

MEM_B_ODT<0>

MEM_B_ODT<1>

NC

NC

MEM_B_BA<0>

MEM_B_BA<1>

MEM_B_BA<2>

MEM_B_RAS_L

MEM_B_WE_L

MEM_B_CAS_L

MEM_B_A<0>

MEM_B_A<1>

MEM_B_A<2>

MEM_B_A<3>

MEM_B_A<4>

MEM_B_A<5>

MEM_B_A<6>

MEM_B_A<7>

MEM_B_A<8>

MEM_B_A<9>

MEM_B_A<10>

MEM_B_A<11>

MEM_B_A<12>

MEM_B_A<13>

MEM_B_A<14>

MEM_B_A<15>

MEM_B_DQS_N<0>

MEM_B_DQS_N<1>

MEM_B_DQS_N<2>

MEM_B_DQS_N<3>

MEM_B_DQS_N<4>

MEM_B_DQS_N<5>

MEM_B_DQS_N<6>

MEM_B_DQS_N<7>

NC

MEM_B_DQS_P<0>

MEM_B_DQS_P<1>

MEM_B_DQS_P<2>

MEM_B_DQS_P<3>

MEM_B_DQS_P<4>

MEM_B_DQS_P<5>

MEM_B_DQS_P<6>

MEM_B_DQS_P<7>

NC

NC

NC

NC

NC

NC

NC

NC

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

25 27 78

25 27 78

25 27 78

26 27 78

26 27 78

26 27 78

25 27 78

26 27 78

25 27 78

26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 27 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

25 26 78

D

C

B

w w w . c h i n a f i x . c o m

A

6 3

SYNC_MASTER=J15_REFERENCE

PAGE TITLE

CPU DDR3 Interfaces

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=12/18/2012

DRAWING NUMBER

<SCH_NUM>

<SCH_NUM>

REVISION

<E4LABEL>

<E4LABEL>

BRANCH

<BRANCH>

<BRANCH>

PAGE

7 OF 1187 OF 118

SHEET

7 OF 827 OF 82

124578

SIZE

A

D

D

C

B

A

H37

H36

H34

H33

BGA

U0500

HASWELL

SYM 6 OF 12

OMIT_TABLE

AB8

AC46

AB46

AB45

8 7 6 5 4 3

PP1V35_S3RS0_CPUDDR

6

10 21 66 67 70 82

PPVCC_S0_CPU

6 8

10 46 59 70 72

1

R0860

H38

POWER

AC47

H39

AC8

H40

AC9

H42

AD46

H43

AD8

H45

AE46

H46

AE47

AE8

AF8

H9H8H48

AG46

J10

AG8

J14

AH46

J19

AH47

J24

AH8

J29

AJ45

J33

AJ46

J36

AK46

J37

AK47

J38

AK8

J39

AL45

J40

AL46

J42

AL8

NOTE: Aliases not used on CPU supply outputs

to avoid any extraneous connections.

Max load: 300mA

58 75

IN

58 75

OUT

58 75

BI

K45

K44

K43

K40

K38

J9J8J48

J46

J45

J43

AM9

AM8

AL9

AM46

AM47

AN10

AN12

AN13

AN14

AN15

AN16

PPVCCIO_S0_CPU

5 6

10 18 58

MIN_LINE_WIDTH=0.4 mm

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=1.05V

CPU_VIDALERT_L

CPU_VIDSCLK

CPU_VIDSOUT

L39

L38

L37

K9K8K48

K46

AN25

AN24

AN23

AN21

AN20

AN19

AN17

L40

AN26

L42

AN27

R0800

L44

L43

AN30

AN29

PLACE_NEAR=U0500.C50:50.8mm

PLACE_SIDE=BOTTOM

CPU_VCCSENSE_P

58 75

OUT

PPVCOMP_S0_CPU

5

1

75

1%

1/16W

MF-LF

402

R0810

2

1/16W

R0811

0

5%

1/16W

MF-LF

402

L47

L46

MF-LF

21

R0812

1/16W

MF-LF

M40

M39

M38

M37

L8

w w w . c h i n a f i x . c o m

AN41

AN40

AN39

AN38

AN36

AN34

AN32

1

R0802

110

1%

1/16W

MF-LF

402

2

43

21

5%

402

0

21

5%

402

M45

M44

M43

M42

VCCVCC

AN8

AN46

AN45

AN44

AN43

AN42

R0802.2:

R0810.2:

R0800.2:

N37

M9M8M46

AN9

AP10

N38

AP12

Max load: 300mA

PLACE_NEAR=U0500.J50:2.54mm

PLACE_NEAR=U0500.J53:38mm

PLACE_NEAR=R0810.1:2.54mm

N46

N44

N43

N42

N40

N39

AP20

AP19

AP18

AP17

AP16

AP15

AP14

AP13

MIN_LINE_WIDTH=0.4 mm

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=1.05V

P8

P46

P45

N9N8N47

AP24

AP23

AP22

AP21

R46

AP25

AP26

AP27

R9R8R47

AP29

T45

AP30

T46

AP31

U46

AP32

1/16W

MF-LF

U47

AP33

100

U8

AP34

5%

402

2

CPU_VIDALERT_R_L

CPU_VIDSCLK_R

CPU_VIDSOUT_R

CPU_PWR_DEBUG

18

IN

TP_CPU_RSVD_TP75

TP_CPU_RSVD_TP76

TP_CPU_IVR_ERROR

TP_CPU_RSVD_TP78

Y8

Y46

Y45

W8

W47

W46

V8

V46

V45

U9

AP35

AP36

AP37

AP38

AP39

AP40

AP41

AP42

AP43

AP44

A27

AP46

A28

AP47

A31

AP8

A32

AP9

A34

AR35

B27

AR37

B28

AR39

B31

AR41

B32

AR43

B34

AR45

B36

AR46

B38

H30

B39

H31

6 3

B42

H32

12

PPVCC_S0_CPU

VCC

FC_D5

FC_D3

B43

B45

B46

B48

C27

C28

C31

C32

C34

C36

C38

C39

C42

C43

C45

C46

C48

D27

D28

D31

D32

D34

D36

D38

D39

D42

D43

D45

D46

D48

E27

E28

E31

E32

E34

E36

E38

E39

E42

E43

E45

E46

E48

F27

F28

F31

F32

F34

F36

F38

F39

F42

F43

F45

F46

F48

G27

G29

G31

G32

G34

G36

G38

G39

G42

G43

G45

G46

G48

H11

H12

H13

H14

H16

H17

H18

H19

H20

H21

H23

H24

H25

H26

H27

H29

D5

D3

Connections are required

for BDW CPU support.

PP1V05_S0_CPU_VCCST

CPU_VCCST_PWRGD

SYNC_MASTER=J15_REFERENCE

PAGE TITLE

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

J17

AR29

AR31

AR33

AT13

AT19

AT23

AT27

AT32

AT36

AV37

AW22

AW25

AW29

AW33

AY18

BB21

BB22

BB26

BB27

BB30

BB31

BB34

BB36

BD22

BD26

BD30

BD33

BE18

BE22

BE26

BE30

BE33

AN31

AN22

AN18

AN33

AR49

AM49

AN49

AJ49

AG50

AK49

AJ50

AP49

AB50

AP50

AD50

AM50

AA46

AA47

J21

J26

J31

C50

AH9

D51

F17

AK6

J12

J53

J52

J50

B51

F19

E52

V49

U49

W49

V50

A36

A38

A39

A42

A43

A45

A46

A48

AA8

AA9

L6

M6

W9

RSVD64

RSVD65

RSVD66

RSVD67

VDDQ

RSVD68

VCC_L6

VCC_M6

RSVD69

RSVD70

VCC_SENSE

RSVD71

VCCIO_OUT

FC_F17

VCOMP_OUT

RSVD72

RSVD73

RSVD79(VSS)

RSVD74

VIDALERT*

VIDSCLK

VIDSOUT

VSS_B51

PWR_DEBUG*

VSS_E52

RSVD75

RSVD76

IVR_ERROR

IST_TRIGGER

VSS_V50(RSVD)

VSS_AN49(RSVD)

VSS_AJ49(RSVD)

VSS_AG50(RSVD)

VSS_AK49(RSVD)

VSS_AJ50(RSVD)

VSS_AP49(RSVD)

VSS_AB50(RSVD)

VSS_AP50(RSVD)

VSS_AD50(RSVD)

VSS_AM50(RSVD)

VCC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

U0500

HASWELL

BGA

SYM 5 OF 12

OMIT_TABLE

6 8

10 46 59 70 72

CPU Power

Apple Inc.

10 19

19

IN

SYNC_DATE=12/18/2012

DRAWING NUMBER

<SCH_NUM>

REVISION

<E4LABEL>

BRANCH

<BRANCH>

PAGE

8 OF 118

SHEET

8 OF 82

SIZE

D

C

B

A

D

124578

8 7 6 5 4 3

12

OMIT_TABLE

A11

A15

A19

A22

A26

D

C

B

A30

A33

A37

A40

A44

AA1

AA2

AA3

AA4

AA48

AA5

AA7

AB5

AB51

AB52

AB53

AB54

AB7

AB9

AC48

AC5

AC50

AC7

AD48

AD51

AD54

AD7

AD9

AE1

AE2

AE3

AE4

AE48

AE5

AE50

AE7

AF5

AF6

AF7

AG48

AG5

AG51

AG52

AG53

AG54

AG7

AG9

AH1

AH2

AH3

AH4

AH48

AH5

AH50

AH7

U0500

HASWELL

BGA

SYM 7 OF 12

GROUND

AJ48

AJ51

AJ54

AK48

AK5

AK50

AK7

AK9

AL1

AL4

AL48

AL5

AL7

AM5

AM51

AM52

AM53

AM54

AM7

AN1

AN2

AN3

AN4

AN48

AN5

AN50

AN7

AP51

AP54

AP7

VSSVSS

AR12

AR14

AR16

AR18

AR20

AR24

AR26

AR48

AR5

AR50

AR7

AR8

AR9

AT1

AT10

AT12

AT15

AT16

AT18

AT20

AT22

AT25

AT26

AT29

AT33

AT35

AT37

AT39

AT4

AT40

AT42

AT43

AT45

AT46

AT47

AT49

AT5

AT50

AT51

AT52

AT53

AT54

AT6

AT8

AT9

AU13

AU18

AU22

AU25

AU29

AU33

AU37

AU42

AU5

AU9

AV1

AV13

AV18

AV2

AV22

AV25

AV29

AV3

AV33

AV4

AV42

AV5

AV50

AV9

AW13

AW18

AW37

AW42

AW43

AW45

AW46

AW47

AW49

AW5

AW50

AW51

AW54

AW9

AY13

AY22

AY25

AY29

AY33

AY37

AY42

OMIT_TABLE

U0500

HASWELL

BGA

SYM 8 OF 12

GROUND

VSS VSS

AY50

AY9

B11

B15

B19

B22

B26

B30

B33

B37

B40

B44

B49

B8

BA13

BA18

BA22

BA25

BA29

BA33

BA37

BA4

BA42

BA5

BA50

BA51

BA52

BA53

BA9

BB10

BB11

BB12

BB14

BB15

BB16

BB17

BB18

BB20

BB23

BB25

BB28

BB32

BB33

BB37

BB38

BB39

BB41

BB42

BB43

BB44

BB46

BB47

BB48

BB49

BB5

BB6

BB7

BB9

D

C

B

CPU_VCCSENSE_N

Y9Y7Y48

W7

W54

W52

W50

W48

V9V7V48

U7U6U54

U52

U50

U5

U48

C33

VSS

C37

U4U3U2U1T48

C40

C44

C49

C52

C8

D15

D11

D19

D22

D26

D30

D33

C4

D37

D40

D44

D49

D8

E11

E15

E16

E17

E19

G18

AR22

AB48

VSS_P9(RSVD)

VSS_G18(RSVD)

VSS_AB48(RSVD)

VSS_AR22(RSVD)

E25

E24

E22

E21

E20

E26

E30

A49

E33

E37

E40

B4A8A50

E44

BA1

E49

BA54

E51

BB1

E53

BB54

E8

BD2

F2

BF49

BD53

VSS_NCTF

F3

F26

BF5

F30

BF50

F33

BF6

F37

C53

G1

F54

E54

D2

F5

F4

F49

F44

F40

G11

G13

R7

R48P9P7P6P54

P52

P50

P5

P48

P4P3P2

P1

N7

N48

M7

M54

M52

M50

M48

L9L7L48

K7

K6K5K4

K3

K2K1J7

J54

J51

J49

J44

H7

H49

H44

G9G8G7

G54

G52

G49

G44

G40

G37

G33

G30

G26

G25

G23

G20

VSS

BGA

U0500

HASWELL

OMIT_TABLE

SYM 9 OF 12

w w w . c h i n a f i x . c o m

A

C30

C26

C22

C19

C15

C11

BC10

BC12

BC15

BC18

BC22

BC26

BC3

BC30

BC33

BC36

BC38

BC41

BC43

BC46

BC48

BC5

BC50

BC52

BC7

BD10

BD15

BD18

BD36

BD41

BD46

BD5

BD51

BE10

BE15

BE36

BE41

BE46

BF10

BF12

BF15

BF18

BF22

BF26

BF30