UC1860

UC2860

UC3860

Resonant Mode Power Supply Controller

FEATURES

• 3MHz VFO Linear over 100:1 Range

• 5MHz Error Amplifier with Controlled

Output Swing

• Programmable One Shot Timer—

Down to 100ns

• Precision 5V Reference

• Dual 2A Peak Totem Pole Outputs

• Programmable Output Sequence

• Programmab le Under Volta ge Locko ut

• Very Low Start Up Current

• Programmable Fault Management &

Restart Delay

• Uncommitted Comparator

DESCRIPTIO N

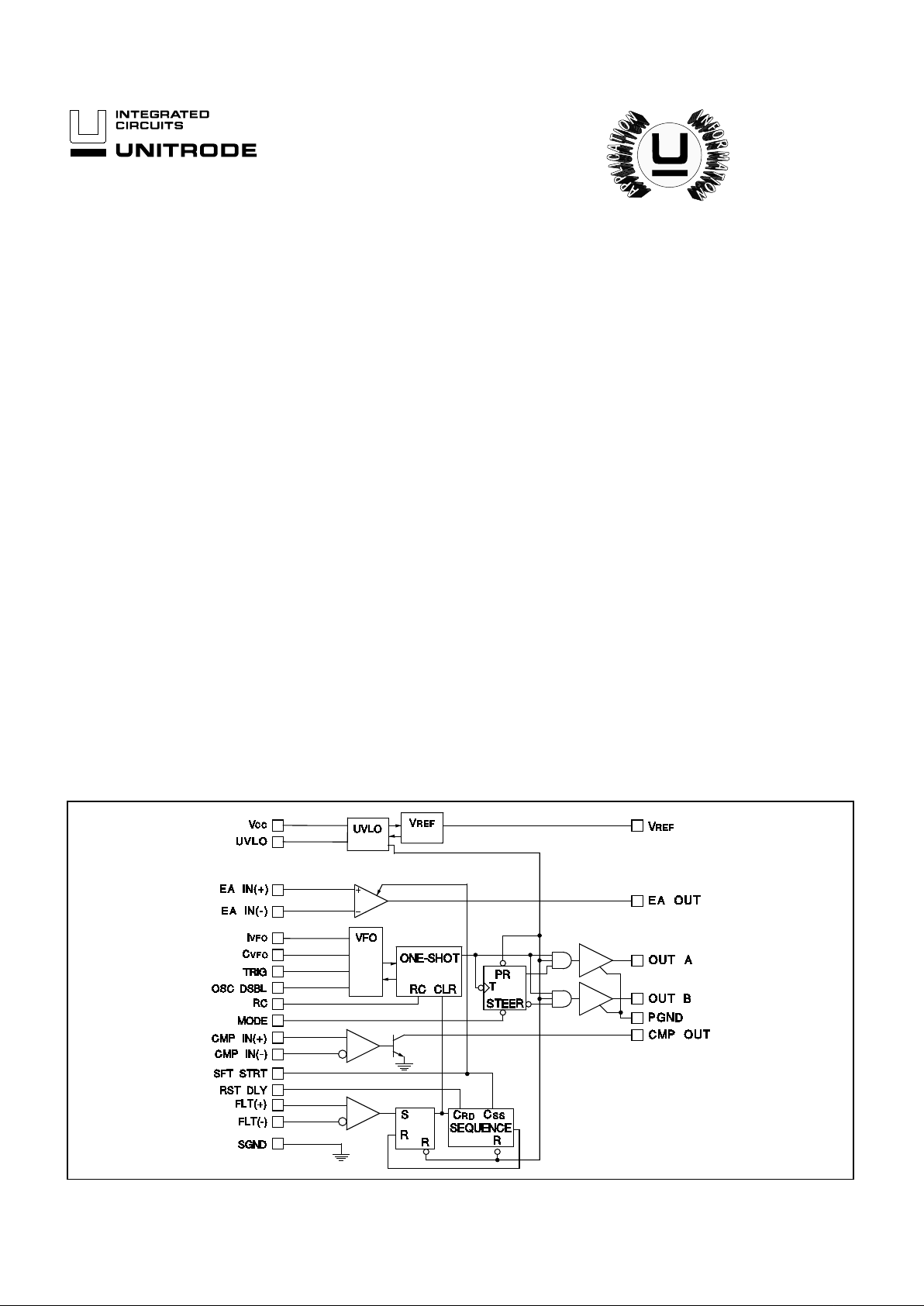

The UC1860 family of control ICs is a versatile system for resonant mode

power supply control. This device easily implements frequency modulate d

fixed-on-time control schemes as well as a number of other power supply

control schemes with its various dedicated and programmable features.

The UC1860 includes a precision voltage reference, a wide-bandwidth error amplifier, a variable frequency oscillator operable to beyond 3MHz, an

oscillator-triggere d one-shot, dual high-current totem-pole output drivers,

and a programmable toggle flip-flop. The output mode is easily programmed for various sequences such as A, off, B, off; A & B, off; or A, B,

off. The error amplifier contai ns precision output clamps that allow programming of minimum and maximum frequency.

The device also co ntain s an u ncommitted compa rator, a fast comparator

for fault sensing, progra mmable soft start circuitry, and a programmable

restart delay. Hic-up style response to faults is easily achieved. In addition, the UC18 60 contains prog rammable under voltage lockout circuitry

that forces the output stages low and minimizes supply current during

start-up conditions.

BLOCK DIAGRAM

ABSOLUTE MAXI MUM RATING S

Supply Voltage ( pin 19) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20V

Output Current , Sourc e or Sink (pins 17 & 20)

DC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.8A

Pulse (0.5µs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.0A

Power Ground Voltag e. . . . . . . . . . . . . . . . . . . . . . . . . . . . ±0.2V

Inputs (pins 1, 2, 3, 4, 8, 9, 11, 12,

13, 14, 21, 22, 23 & 24). . . . . . . . . . . . . . . . . . . . . . -0. 4 t o 6V

Error Amp Output Curr ent , Source or Sink (pin 5). . . . . . . . 2mA

I

VFO Current (pin 7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2mA

Compara to r Output Cur ren t (pin 15) . . . . . . . . . . . . . . . . . . 5mA

Compara to r Output Volt age (pin 15) . . . . . . . . . . . . . . . . . . 15V

Soft Start or Restart Delay Sink Curre nt (pins 22 & 23) . . . 5mA

Power Dissipation at T

A = 50°C (DIP) . . . . . . . . . . . . . . . 1.25W

Power Dissipation at T

A = 50°C (PLCC) . . . . . . . . . . . . . . . . 1W

Lead Temp era ture (Solder in g, 10 seconds) . . . . . . . . . . . 300°C

Note: All voltages are with respect to signal gro und an d a ll

currents are posit ive int o the spec ified t ermina l.

Pin numbers refer to the DI P.

Refer to Packag ing Sect ion of Databoo k fo r therma l

limitations and cons id era tion s of packa ges.

10/93

UC1860

UC2860

UC3860

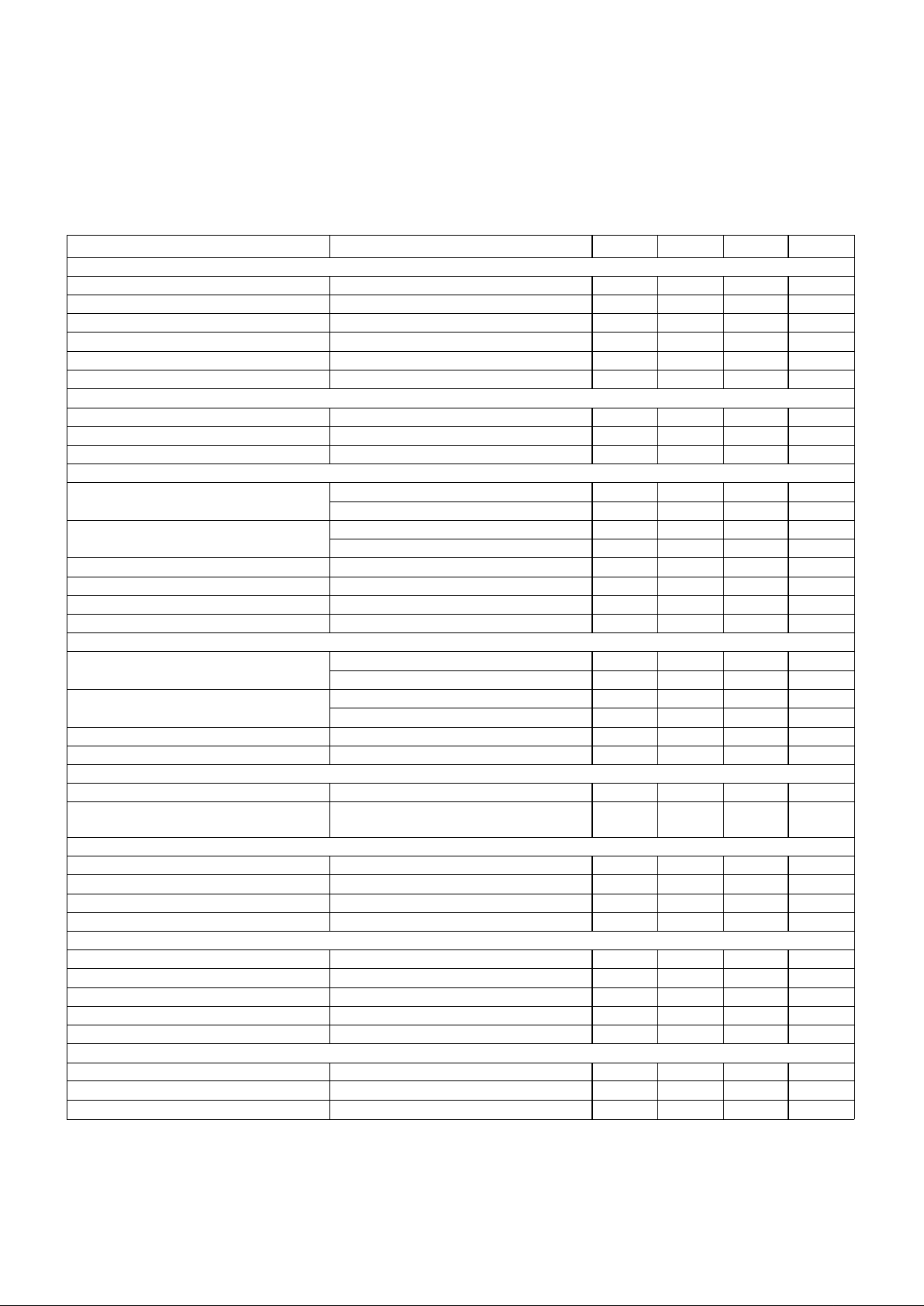

ELECTRICAL CHARACTERISTICS:

PARAMETER CONDITIONS MIN TYP MAX UNITS

Reference Sec tio n

Output Volt age T

A = 25°C, IO = 0 4.95 5.00 5.05 V

I

O = 0, Over Temp 4.93 5.07 V

Line Regulatio n 10 ≤ V

CC ≤ 20V 2 15 mV

Load Regulation 0≤ I

O ≤ 10mA 2 25 mV

Output Noise Voltage* 10Hz ≤ f ≤ 10kHz 50 µV

RMS

Short Circuit Current VREF = 0V -150 -1 5 mA

Error Amplifier Section

Input Offs et Vo lta g e 2.8 ≤ V

CM ≤ 4.5V 1 8 mV

Input Bias Cur ren t 50 500 nA

Open Loop Gain dV

O = 1.5V 60 80 dB

PSRR 10 ≤ V

CC ≤ 20V 70 100 dB

Output Low ( V

O-VIVFO) -0.1 ≤ IO ≤ 0.1mA -8 0 8 mV

Output High (V

O-VIVFO ) -0.5 ≤ IO ≤ 0.5mA 1.9 2 2.1 V

Unity Gain Bandwidth* R

IN = 2k 4 5 MHz

Oscillato r Sect io n

Nominal Frequency* 1.0 1.5 2.0 MHz

dF/dI

OSC* 100 ≤ IVFO ≤ 500µA 2 3 4 GHz/A

*Guarant e e d by des ign but not 100% test ed.

Unless otherwise stat ed, all specif icat ions app ly for -55 °C ≤ TA ≤ 125°C for the

UC1860, -25°C ≤ T

A ≤ 85°C for the UC2860, 0 ≤ TA ≤ 70°C for the UC3860, VCC =

12V, C

VFO = 330pF, IVFO = 0.5mA, C = 330pF, and R = 2.7k, T A = TJ.

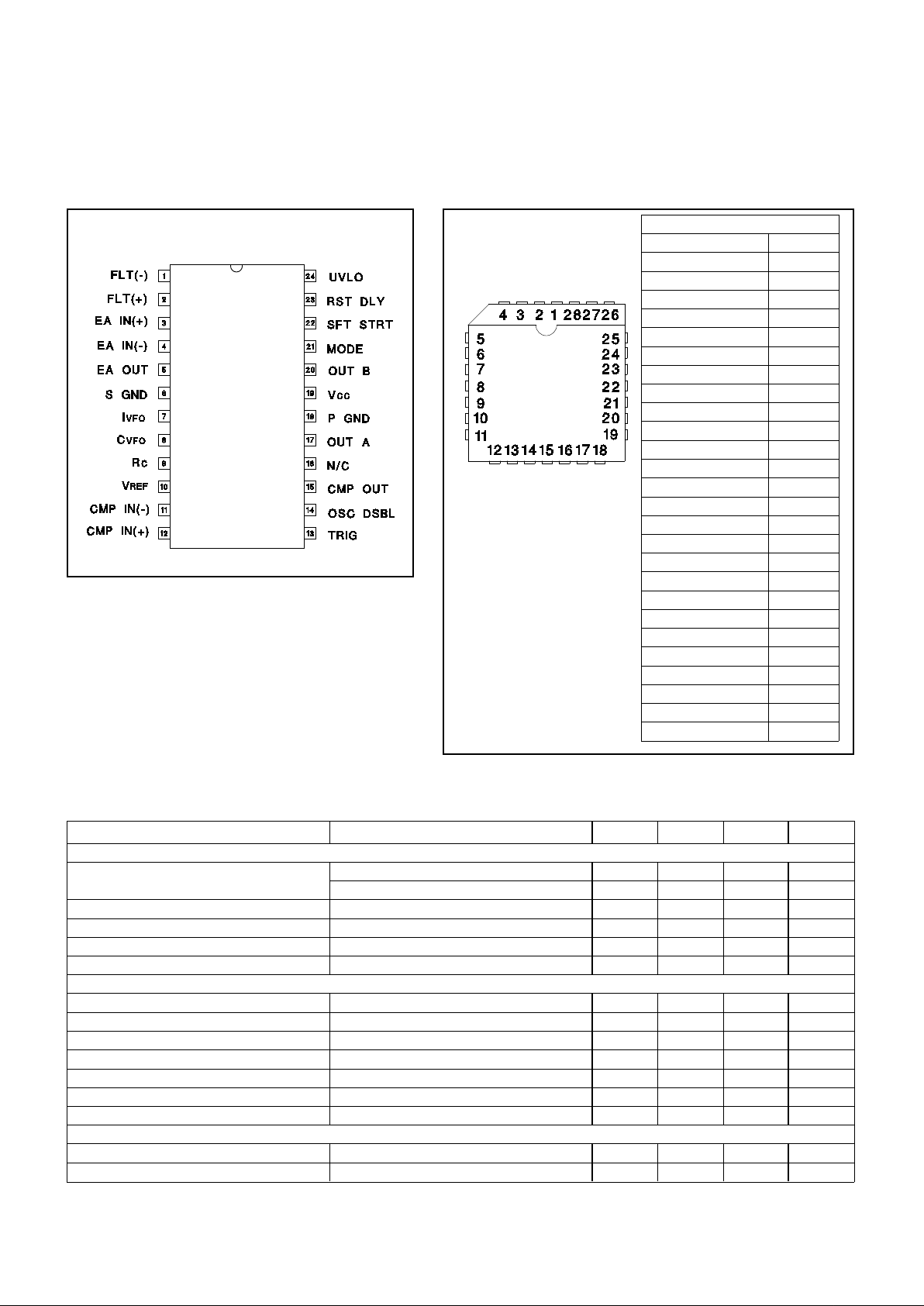

DIL - 24 (TOP VIEW)

J or N Package

PLCC-28, LCC-28

(TOP VIEW)

Q or L Package

PIN PACKAGE FUNCTION

FUNCTION PIN

S GND 1

I

VFO 2

C

VFO 3

RC 4

V

REF 5

CMP IN (-) 6

CMP IN (+) 7

TRIG 8

OSC DSBL 9

CMP OUT 10

N/C 11, 12

OUT A 13

PGND 14

N/C 15

V

CC 16

OUT B 17

N/C 18, 19

MODE 20

SFT STRT 21

RST DLY 22

UVLO 23

FLT (-) 24

FLT (+) 25

EA IN (+) 26

EA IN (-) 27

EA OUT 28

CONNECTION DIAGRAM

2

UC1860

UC2860

UC3860

ELECTRICAL CHARACTERISTICS:

PARAMETER CONDITIONS MIN TYP MAX UNITS

Oscillato r Sect io n (c ont’d)

Trig in Threshold 1.0 1.4 1.8 V

Trig in Open Circuit Volta ge 0.7 0.9 1.1 V

Trig in Delta (V

TH-VOC) 0.3 0.5 0.7 V

Trig in Input Resistance dV T

RIG = VOC to VTH 51225kΩ

Minimum Trig in Pulse Width* 3 10 ns

Osc. Disable Threshold 1.0 1.4 1.8 V

One Shot Ti m er

On Time* 150 200 250 ns

Clamp Frequency* I

VFO = 1.5m A 2.8 3.7 4.6 MHz

Dead Time* I

VFO =1.5mA 35 70 100 ns

Output Stage

Output Low Saturation 20mA 0.2 0.4 V

200mA 0.5 2.2 V

Output High Saturation -20mA 1.5 2.0 V

-200mA 1.7 2.5 V

Rise/Fall Time* C

LOAD = 1nF 1530ns

UVLO Low Satur at i on 20mA 0.8 1.5 V

Output M ode Low Input 0.4 V

Output Mode High Inpu t 2.0 V

Under Voltage Lockout Sectio n

V

CC Comparator Threshold On 16 17.3 18.5 V

Off 9.5 10.5 12 V

UVLO Comparat or Threshold On 3.6 4.2 4.8 V

Hysteresis 0.2 0.4 0.6 V

UVLO Input Resist ance UVLO = 4/V

CC = 8 102350kΩ

V

REF Comparator Threshold VCC = UVLO = VREF 4.5 4.9 V

Supply Current

I

CC VCC = 12V, VOSC DSBL = 3V 30 40 mA

I

START UVLO pin open

V

CC

= VCC (on) -0.3V

0.3 0.5 mA

Fault Compar ator

Input Offs et Vo lta g e −0.3 ≤ V

CM ≤ 3V 2 10 mV

Input Bias Cur ren t V

CM = 0V 100 200 µA

Input Offs et Cu rr ent V

CM = 0V 10 3 0 µA

Propagation De lay To Out put * ±50mV input 100 150 ns

Uncommitted Comparator

Input Offs et Vo lta g e -0.3 ≤ V

CM ≤ 3V 2 10 mV

Input Bias Cur ren t V

CM = 0V 100 200 µA

Input Offs et Cu rr ent V

CM = 0V 10 3 0 µA

Output Low Volt age I

O = 2mA 0.3 0.5 V

Propagation De lay To Sat * ±50mV input, 2.5k load to 5V 50 100 ns

Soft Start/Resta rt Co ntrol Sect ion

Saturation Volta ge (2 pins) I

SINK = 100µA0.20.5V

Charge Current (2 pins) 2 5 10 µA

Restart Delay Threshold 2.8 3.0 3.2 V

*Guarant e e d by des ign but not 100% test ed.

Unless otherw ise stated, all speci fications app ly for -55°C ≤ TA ≤ 125°C for the

UC1860, -25° ≤ TA ≤ 85°C for the UC2860, 0 ≤ TA ≤ 70°C for the UC 3860 , V CC =

12V, CVFO = 330pF, IVFO = 0.5mA, C = 330pF, and R = 2.7k, TA = TJ.

3

UC1860

UC2860

UC3860

ERROR AMPLIFI ER

The error amplifier is a high gain, low offset, high bandwidth design with precise limits on its output swing. The band w id th of the

amplifier is externally determined by the resistance seen at the

inverting input. Unity gain bandwidt h is appr oxim ately:

Frequency ( 0dB) = 1/(2π * RIN (-) * C

COMP

)

The input common mode range of the amplifier is from 2.8 to

4.5V. As long as one pin is within this range, the other can go as

low as zero.

The output swing with respect to the l

VFO pin is limited from zero

to 2V. Note that pulling Sf t Strt (soft start) low will lower the reference of the upper clamp. The lower clamp, however, will

dominate should the upper clamp reference drop below the

lower reference.

UNDER VOLTAGE LOCKOUT SECTION

The under voltage lockout consists of three comparators that

monitor V

CC, UVLO and VREF. The VREF comparator makes

sure that the reference voltage is sufficiently high before operation begins. When the UVLO comparator is low, the outputs

are driven low, the fault latch is reset, the soft start pin is discharged, and the togg le flip-flop is loaded fo r ou tput A.

The V

CC comparator is used for off- line applications by leaving

the UVLO pin open. In this application the supply current is

typical ly less than 0. 3m A during star t-up.

The UVLO comparator is used for DC to DC applications or to

gate the chip on and off. To utilize its hyster et ic t hre shold b y an

external resistive divider, the internal impedance of the pin

must be accounted for. To run from a 5V external supply,

UVLO, V

CC, and VREF are tied together.

ICC vs VCC

4

UC1860

UC2860

UC3860

VARIABLE FREQUENCY OSCILLATOR

The VFO block is controlled throug h 4 pins: C

VFO, lVFO,

Osc Dsbl (oscil lator disa ble), and Trig (trigger input). Oscillator frequency is approximately:

Frequency = I

VFO

/(C

VFO

* 1V)

With a fixed capacitor and low voltage applied to Trig and

Osc Dsbl, frequency i s linearly modulated by varying the

current into the l

VFO pin.

The Trig and Osc Dsbl inputs are used to modify VFO operation. If Osc Dsbl is held high, the oscillator will complete the current cycle but wait until Osc Dsbl is re turned

low to initiate a new cycle. If a pulse is applied to Trig during a cycle, the oscillator will immediately initiate a new

cycle. Osc Dsbl has priority over Trig, but if a trigger pulse

is received while Osc Dsbl is high, the VFO will remember

the trigger pulse and start a new cycle as soon as Osc

Dsbl goes low .

Normally low trig ger pulses are used to synchronize the

oscillator to a faster clock. Normally high trigger pulses

can also be used to synchronize to a slower clock.

ONE SHOT TIMER

The one shot timer performs three functions and is programmed by the RC pin. The first function is to control

output driver pulse width. Seco ndly, it clocks the toggle

flip-flop. Thirdly, it establishes the maximum allowable frequency for the V FO. One shot operation is initiated at the

beginning of each oscillator cycle. The RC pin, programmed by an external resistor and capacitor to ground,

is charged to approximately 4.3V and then allowed to discharge. The lowe r threshold is approximately 80% of the

peak. On time is approximately:

t(on) = 0.2 * R * C.

After crossing the lower threshol d, the re sistor continues

to discharge the ca pacitor to ap proximately 3V, where it

waits for the next oscillator cycle.

Maximum Frequen cy vs R

On Time vs R

VFO Frequency vs I

VFO

5

UC1860

UC2860

UC3860

FAULT MANAGEMENT SECTION

During UVLO, the fault management section is initialized.

The latch is reset, and both Sft Strt (soft start) and Rst Dly

(restart delay) are pulled low. When Sft Strt is low, it lowers the upper clamp of the error amplifier. As Sft Strt increases in voltage, the upper clamp increases from a

value equal to the lower clamp until it is 2V more positive.

A capacitor to ground fro m the S ft Strt pin will control the

start rate.

UNCOMMITTED COMPARAT OR

The uncommitted comparator, biased from the reference

voltage, operates independently from the rest of the chip.

The open collector output is cap able of sinking 2mA. The

inputs are valid in the common mode range of -0.3 to

3.0V. As long as one of the inputs is within this range, the

other can be as high as 5V.

The high speed fault comparator will work over the input

common mode range of -0.3 to 3.0V. When a fault is

sensed, the one shot is immediately terminated, Sft Strt i s

pulled low, and Rst Dly is allowed to go high. Three

modes of fault dispo sition can easi ly be implemented. If

Rst Dly is externally held low, then a detected fault will

shut the chip down permanently. If the Rst Dly pin is left

open, a fault will simply cause an interruption of operation. If a capaci tor is connected from Rst Dly to ground,

then hic-up operation is implemented. The hic-up time is:

t (off) = 600 kohm * C(Rst Dly).

Input Bias Current Input Voltage

6

UC1860

UC2860

UC3860

OPEN LOOP LABORATORY TEST FIXTURE

The open loop laboratory test fixture is desi gned t o allow

familiarization with the operating characteristics of the

UC3860. Note the pin numbers apply to the DlP.

To get started, preset all the options as follows:

Adjust the error amplifier variable resistor pot (R1)

so the wiper is at a high potential.

Open the l

VFO resistor switch (S1).

Throw the Trig switch (S 2) to ground.

Throw the Osc Dsbl switch (S3) to ground.

Throw the uncommitted comparat or switch (S4) to

ground.

Throw the UVLO switch (S5) to the resistive divider.

Throw the Out Mode switch (S6) to ground.

Open the restart delay switch (S7).

Throw the fault switch (S8)to ground.

In this configura tion, the chip w ill operate for Vcc greater

than 12V. Adjustment of the following controls allows examination of specific features.

R1 adjusts the output of the error amp. Notice the voltage

at pin 5 is limited from 0 to 2V above the voltage at pin 7.

S1 changes the error amp output to VFO gain. With S1

open, the maximum frequency is determined by the error

amp output. With S1 closed, the one shot will set the

maximum frequency.

S2 demonstrates the trigger. An external trigger signal

may be applied. When the switch is set to the resistive divider, the chip will operate in consecutive mode (ie: A,B,

off,...)

S3 allows input of an external logic sig nal to disable the

oscillator.

S4 demonstrates the uncommitted comparator. When set

to output A, the comparator will accelerate the discharge

of pin 9, shortening the output pulse.

S5 shorted to ground will disable the chip and the outputs

will be low. If the switch is open, the V

CC start and stop

thresholds are 17 and 10V. Switched to the re sistive divider , the thresholds are approximately 12 and 10V.

S6 sets the mode of the toggle flip-flop. When grounded,

the outputs operate alternately. Switched to 5V, the outputs switch in unison . (Note: I f S6 and S2 are set for unison operation and triggered consecutive outputs, the chip

will free run at the maximum frequency determined by the

one shot.)

S7 open allows the chip to restart immediately after a

fault sense has been removed. When grounded, it causes

the chip to latch off indefinitely. This state can be reset by

UVLO, V

CC, or opening the switch. Connected to IµF pro-

grams a hic-up delay time of 600 ms.

S8 allows the simul ation of a fault s tate. When flipped to

the RC network, the comparator monitors scaled average

voltage of output B. Adjusting frequency will cause the

comparator to sense a ’fault’ and the chip will enter fault

sequence.

7

UC1860

UC2860

UC3860

OUTPUT STAGE

The two totem pole output stages can be programmed by

Mode to operate alternately or in unison. When Mode is

low the outputs alternate. Duri ng UVLO, the outputs are

low.

Extreme care need s to be exe rcised in the appli cation of

these outputs. Each output can source and sink transient

currents of 2A or more and is designed for high values of

dl/dt. This dictates the use of a ground plane, shielded interconnect cables, Schottky diode clamps from the output

pins to Pwr Gnd (power grou nd), and some series resistance to provide damping. Pwr Gnd should not exceed

±0.2V from signal ground.

BYPASS NOTE

The reference should be bypassed with a 0.1µF ceramic

capacitor from the V

REF pin directly to the ground plane

near the Signal Ground pin. The timing capacitors on

C

VFO and RC should be treated likewise. VCC, however,

should be bypassed with a ceramic capacitor from the

V

CC pin to the section of gro und plane that is connected

to Power Ground. Any re quired bulk reservoir capacitor

should paral lel this one. The two ground plane sections

can then be joined at a single point to optimize noise rejection and minimize DC drops.

Output Saturatio n Volt age vs Lo ad Current

Output Saturatio n Volt age vs Lo ad CurrentOutput Rise & Fall Time vs Load Capaci tan ce

UNITRODE INTEGRATED CIRCUITS

7 CONTINENTAL BLVD. • MERRIMACK, NH 03054

TEL. 603-424-2410 • FAX 603-424-3460

8

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERSTOOD T O

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1999, Texas Instruments Incorporated

Loading...

Loading...