6/98

FEATURES

• Programmable Output Turn On

Delay; Zero Delay Available

• Compatible with Voltage Mode or

Current Mode Topologies

• Practical Operation at Switching

Frequencies to 300kHz

• Four 100mA Totem Pole Outputs

• 10MHz Error Amplifier

• Pin Programmable Undervoltage

Lockout

• Low Startup Current - 150µA

• Soft Start Control

• Outputs Active Low During UVLO

Phase Shift Resonant Controller

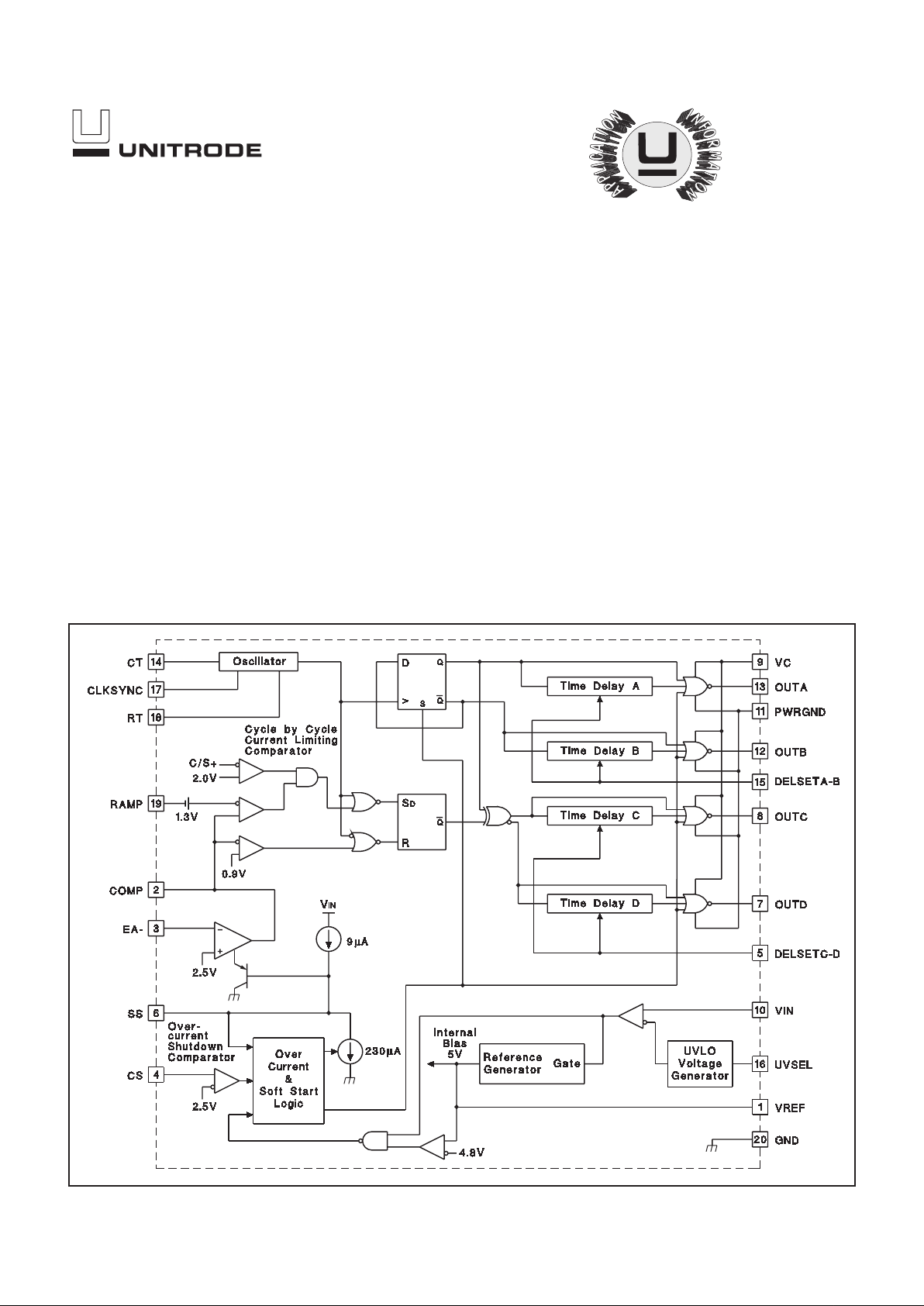

BLOCK DIAGRAM

UDG-94070-1

UC1879

UC2879

UC3879

DESCRIPTION

The UC3879 controls a bridge power stage by phase shifting the switching

of one half-bridge with respect to the other. This allows constant frequency

pulse width modulation in combination with resonant, zero-voltage switching

for high efficiency performance. The UC3879 can be configured to provide

control in either voltage mode or current mode operation, with overcurrent

shutdown for fast fault protection.

Independently programmable time delays provide dead-time at the turn-on

of each output stage, allowing time for each resonant switching interval.

With the oscillator capable of operating in excess of 600kHz, overall output

switching frequencies to 300kHz are practical. In addition to the standard

free running mode, with the CLKSYNC pin, the user may configure the

UC3879 to accept an external clock synchronization signal. Alternatively, up

to three units can be locked together with the operational frequency determined by the fastest device.

Protective features include an undervoltage lockout and overcurrent protection. Additional features include a 10MHz error amplifier, a 5V precision reference, and soft start. The UC3879 is available in 20 pin N, J, DW, and Q

and 28 pin L packages.

2

UC1879

UC2879

UC3879

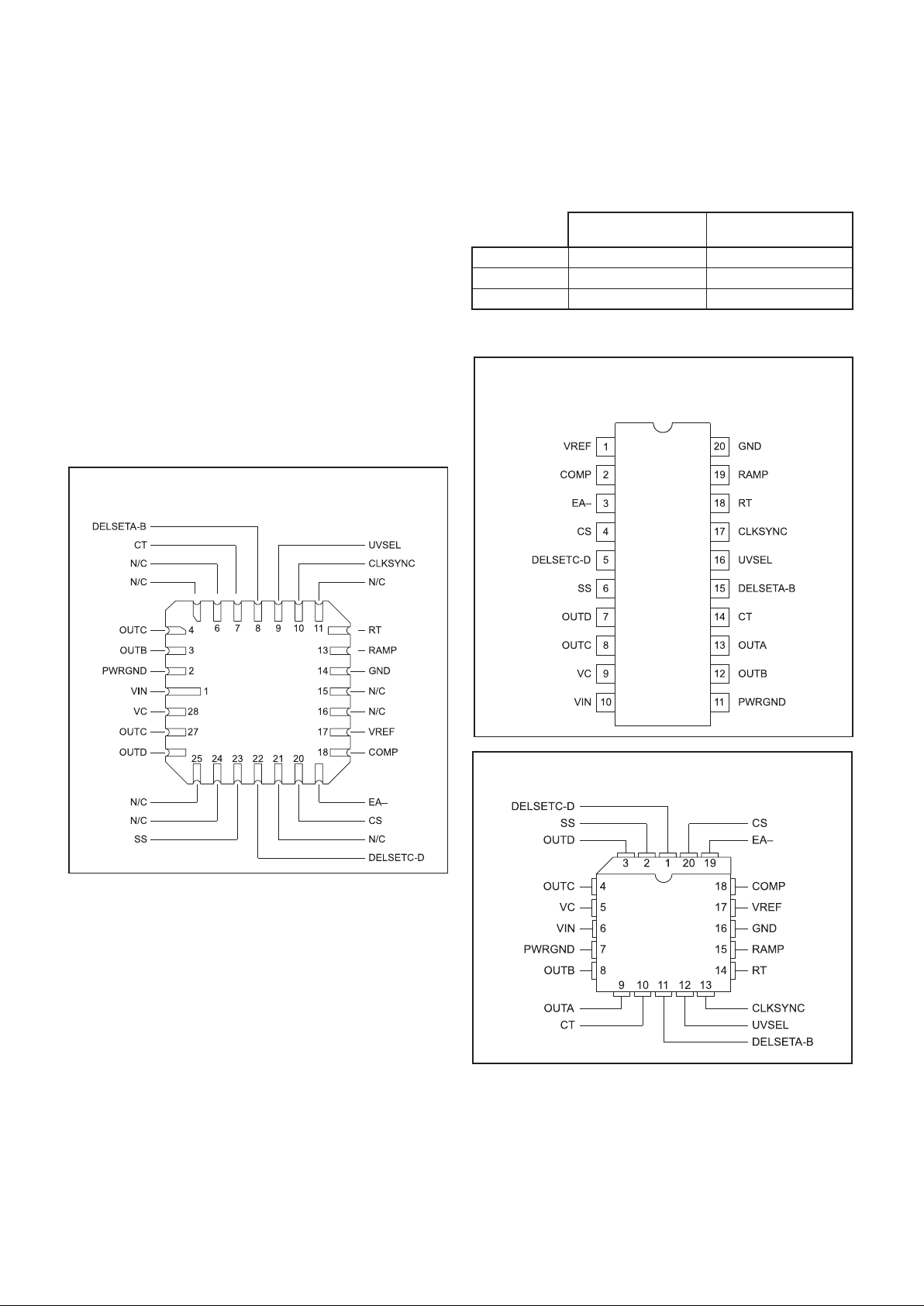

CONNECTION DIAGRAMS

DIL-20, SOIC-20 (Top View)

JorNPackage,DWPackage

ABSOLUTE MAXIMUM RATINGS

Supply Voltage (VC, VIN) ..........................20V

Output Current, Source or Sink, DC.................20mA

Analog I/0s

(Pins 1, 2, 3, 4, 5, 6, 14, 15, 17, 18, 19) ......−0.3 to 5.3V

(Pin 16) ...............................−.03V to VIN

Storage Temperature Range .............−65°C to +150°C

Junction Temperature...................−55°C to +150°C

Lead Temperature (Soldering, 10 sec.) ............ +300°C

Notes: Pin references are to 20 pin DIL and SOIC packages.

All voltages are with respect to ground unless otherwise stated.

Currents are positive into, negative out of the specified terminal. Consult Packaging Section of Databook for thermal limitations and considerations of packages.

PLCC-20 (Top View)

Q Package

Table I. Product Selection Guide

TEMPERATURE

RANGE

AVAILABLE

PACKAGES

UCC1879 – 55°C to +125°C J, L

UCC2879 – 40°C to +85°C N, DW, Q, J, L

UCC3879 0°C to +70°C N, DW, Q

CLCC-28 (Top View)

L Package

3

UC1879

UC2879

UC3879

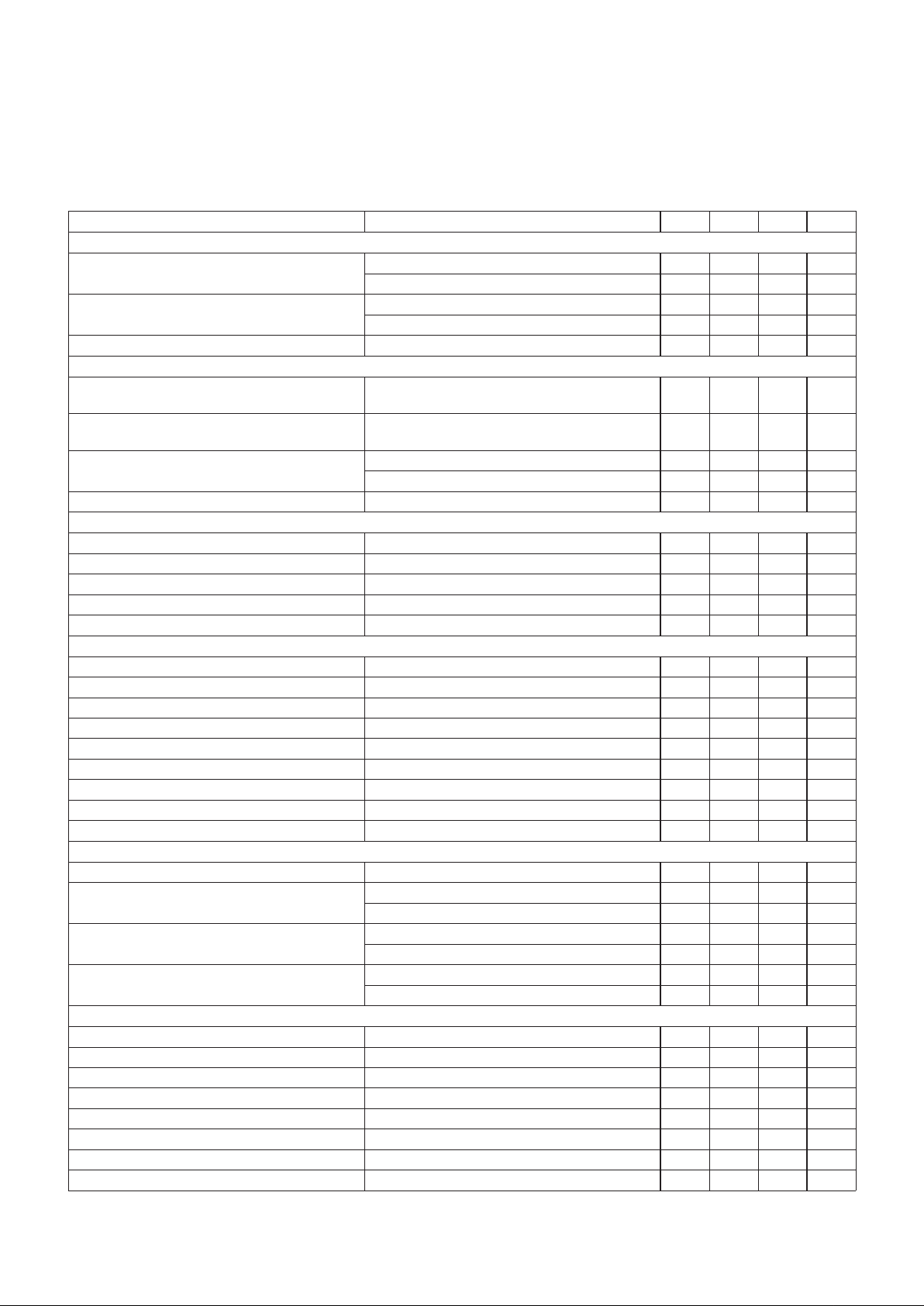

ELECTRICAL CHARACTERISTICS

Unless specified; VC = VIN = V

UVSEL

=12V, CT = 470pF, RT = 9.53k, RDELSETA-B =

R

DELSEC-D

= 4.8k, C

DELSETA-B=CDELSETC-D

= 0.01µF, TA=TJ.

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Undervoltage Lockout

Start Threshold V

UVSEL

= VIN 9 10.75 12.5 V

V

UVSEL

= Open 12.5 15.25 16.5 V

UVLO Hysteresis V

UVSEL

= VIN 1.15 1.75 2.15 V

V

UVSEL

= Open 5.2 6 7.4 V

Input Bias, UVSEL Pin V

UVSEL

=VIN=8V 30 µA

Supply Current

I

VIN

Startup VIN = V

UVSEL

= 8V, VC = 18V, I

DELSETA-B

=

I

DELSETC-D

=0

150 600 µA

IVCStartup VIN = V

UVSEL

= 8V, VC = 18V, I

DELSETA-B

=

I

DELSETC-D

=0

10 100 µA

I

VIN

Operating UC3879, UC2879 23 33 mA

UC1879 23 36 mA

I

VC

Operating 48mA

Voltage Reference

Output Voltage T

J

= +25°C 4.92 5 5.08 V

Line Regulation 11V < VIN < 18V 1 10 mV

Load Regulation I

VREF

= –10mA 5 20 mV

Total Variation Line, Load, Temperature 4.875 5.125 V

Short Circuit Current VREF = 0V, T

J

=25°C –60 –15 mA

Error Amplifier

Error Amplifier Input Voltage 2.4 2.5 2.6 V

Input Bias Current 0.6 3 µA

AVOL 1V < V

COMP

<4V 60 90 dB

PSRR 11V < VIN < 18V 85 100 dB

Output Sink Current V

COMP

= 1V 1 2.5 mA

Output Source Current V

COMP

=4V −1.3 −0.5 mA

Output Voltage High I

COMP

= –0.5mA 4 4.7 5 V

Output Voltage Low I

COMP

= 1mA 0 0.5 1 V

Slew Rate TA= +25°C 6 11 V/µs

PWM Comparator

RAMP Offset Voltage T

J

=25°C, Note 3 1.1 1.25 1.4 V

PWM Phase Shift, V

COMP>VRAMPpeak+VRAMPoffset

98 99.7 102 %

T

DELSETA-B

,

T

DELSETC-D

= 0, Note 1 V

COMP

< Zero Phase Shift Voltage 0 0.3 2 %

Output Skew, V

COMP

>VRAMPpeak +VRAMPoffset 10 ns

T

DELSETA-B

,

T

DELSETC-D

= 0, Note 1 V

COMP

< Zero Phase Shift Voltage 10 ns

Ramp to Output Delay, T

DELSETA-B

=0,

T

DELSETC-D

=0

UC3879, UC2879 115 250 ns

UC1879 115 300 ns

Oscillator

Initial Accuracy T

A

=25°C 180 200 220 kHz

Voltage Stability 11V < VIN < 18V 1 2 %

Total Variation Line, Temperature 160 200 240 kHz

CLKSYNC Threshold 2.3 2.5 2.7 V

Clock Out High 2.8 4 V

Clock Out Low 0.5 1 1.5 V

Clock Out Pulse Width 400 600 ns

Ramp Valley Voltage 0.2 0.4 V

Loading...

Loading...