Motorola MC10E197FNR2, MC10E197FN Datasheet

SEMICONDUCTOR TECHNICAL DATA

2–1

REV 2

Motorola, Inc. 1996

12/93

The MC10E197 is an integrated data separator designed for use in

high speed hard disk drive applications. With data rate capabilities of up

to 50Mb/s the device is ideally suited for today’s and future

state-of-the-art hard disk designs.

The E197 is typically driven by a pulse detector which reads the

magnetic information from the storage disk and changes it into ECL

pulses. The device is capable of operating on both 2:7 and 1:7 RLL

coding schemes. Note that the E197 does not do any decoding but rather

prepares the disk data for decoding by another device.

For applications with higher data rate needs, such as tape drive

systems, the device accepts an external VCO. The frequency capability

of the integrated VCO is the factor which limits the device to 50Mb/s.

A special anti-equivocation circuit has been employed to ensure timely

lock-up when the arriving data and VCO edges are coincident.

Unlike the majority of the devices in the ECLinPS family, the E197 is

available in only 10H compatible ECL. The device is available in the

standard 28-lead PLCC.

Since the E197 contains both analog and digital circuitry, separate

supply and ground pins have been provided to minimize noise coupling

inside the device. The device can operate on either standard negative

ECL supplies or, as is more common, on positive voltage supplies.

• 2:7 and 1:7 RLL Format Compatible

• Fully Integrated VCO for 50Mb/s Operation

• External VCO Input for Higher Operating Frequency

• Anti-equivocation Circuitry to Ensure PLL Lock

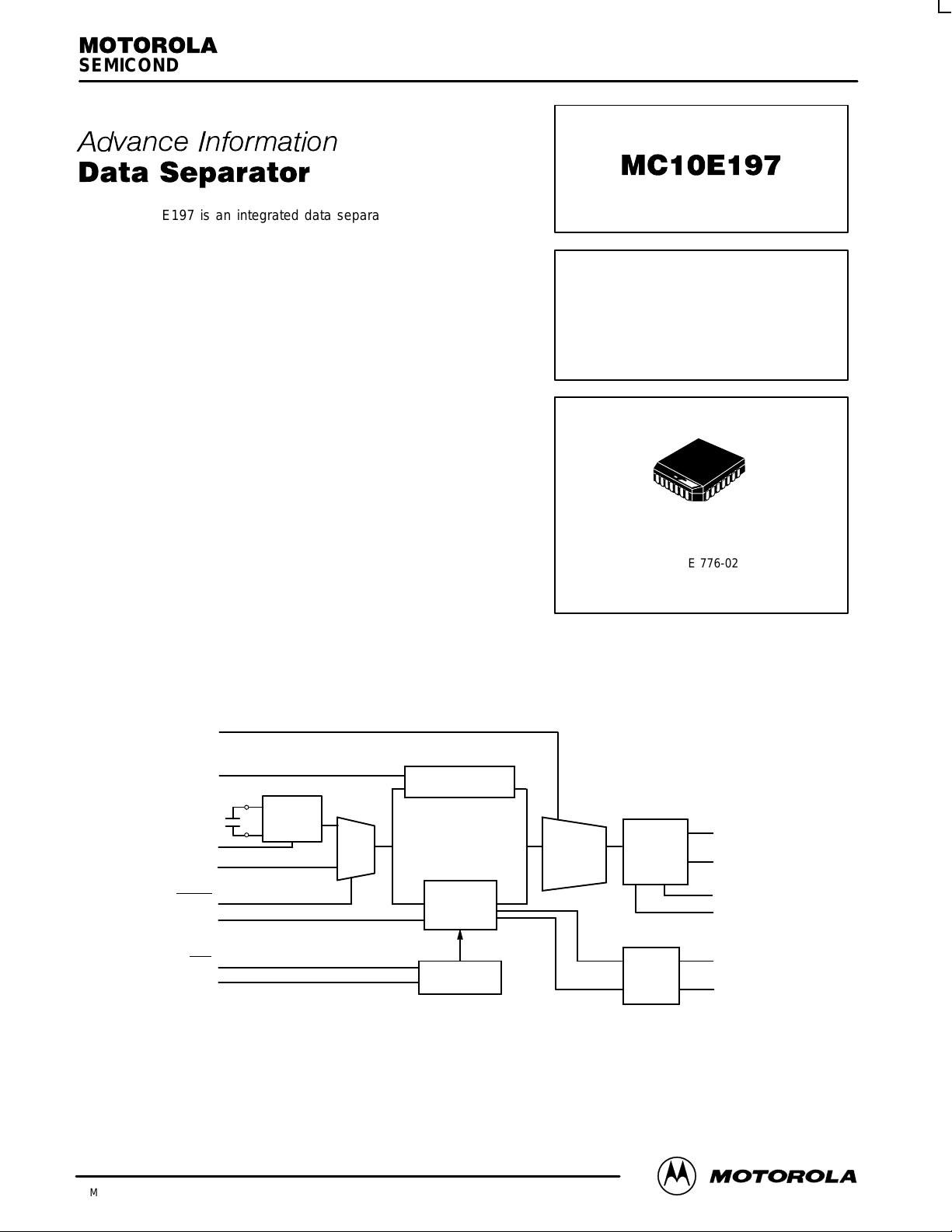

INTERNAL

VCO

DATA

PHASE

DETECTOR

ACQUISITION

CIRCUITRY

CHARGE

PUMP

CURRENT-

SOURCES

PHASE

DETECTOR

MUX

PHASE FREQUENCY

DETECTOR

LOGIC DIAGRAM

RDEN

REFCLK

VCOIN

EXTVCO

ENVCO

RAWD

ACQ

TYPE

CAP1

CAP2

PUMPUP

PUMPDN

RSETUP

RSETDN

RDATA

RDCLK

VCO

MUX

CLOCK &

DATA

BUFFER

This document contains information on a new product. Specifications and information herein are subject to

change without notice.

DATA SEPARATOR

FN SUFFIX

PLASTIC PACKAGE

CASE 776-02

MC10E197

MOTOROLA ECLinPS and ECLinPS Lite

DL140 — Rev 4

2–2

CAP1

CAP2

VCOIN

V

RSETUP

PUMPDN

RAWD

RAWD

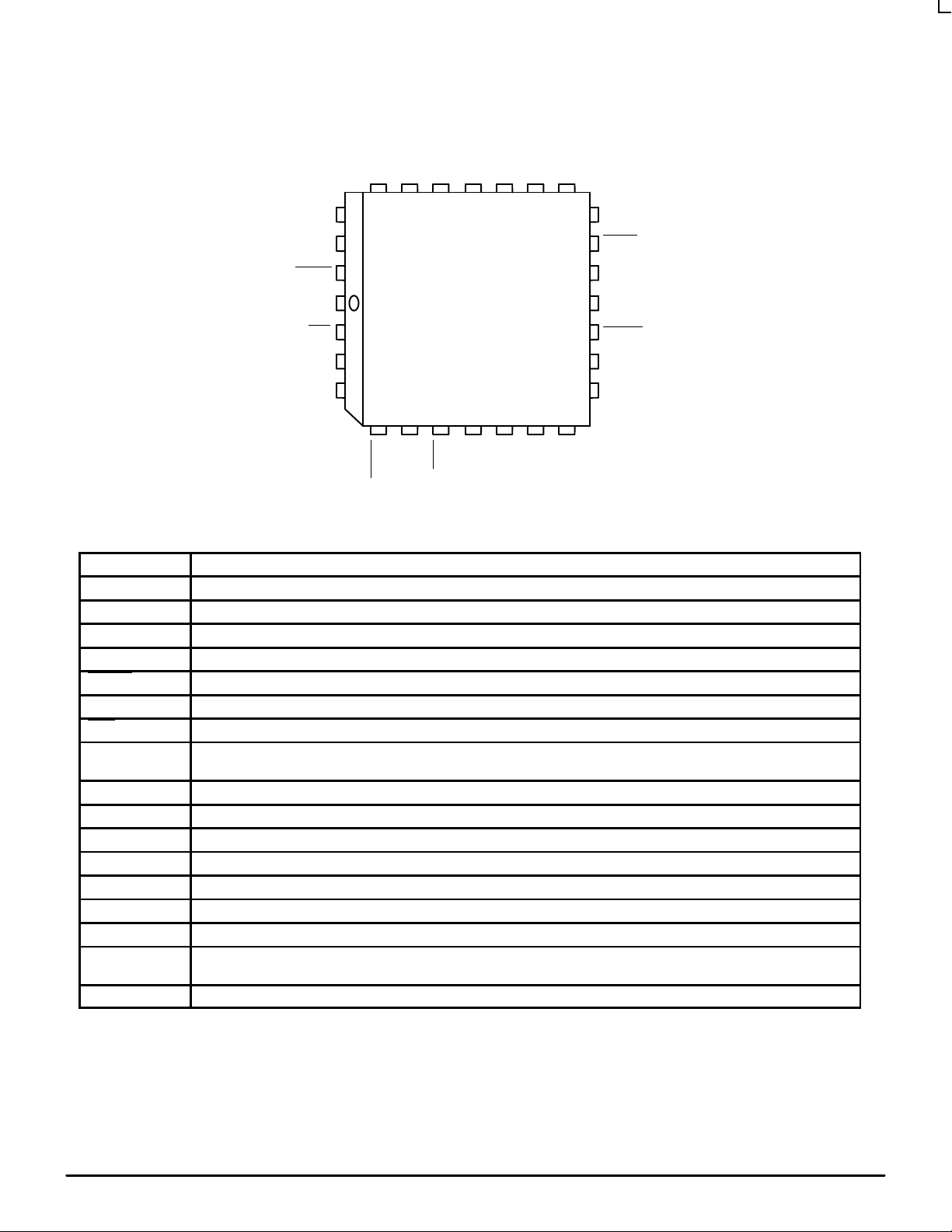

Pinout: 28-Lead PLCC (Top View)

25 24 23 22 21 20 19

18

17

16

15

14

13

12

5 6 7 8 9 10 11

26

27

28

2

3

4

RDCLK

RDCLK

V

CC

RSDATA

RSDATA

PUMPUP

RSETDN

TEST

EXTVCO

ENVCO

V

EE

ACQ

TYPE

RDEN

NC

RFFCLK

RFFCLK

CCO1

V

CCO0

V

CCVCO

V

CCVCO

1

PIN DESCRIPTIONS

REFCLK Reference clock equivalent to one clock cycle per decoding window.

RDEN Enable data synchronizer when HIGH. When LOW enable the phase/frequency detector steered by REFCLK.

RAWD Data Input to Synchronizer logic.

VCOIN VCO control voltage input

CAP1/CAP2 VCO frequency controlling capacitor inputs

ENVCO VCO select pin. LOW selects the internal VCO and HIGH selects the external VCO input. Pin floats LOW when left open.

EXTVCO External VCO pin selected when ENVCO is HIGH

ACQ Acquisition circuitry select pin. This pin must be driven HIGH at the end of the data sync field for some sync field types.

TYPE Selects between the two types of commonly used sync fields. When LOW it selects a sync field interspersed with 3 zeroes

(2:7 RLL code). When HIGH it selects a sync field interspersed with 2 zeroes (1:7 RLL code).

TEST Input included to initialize the clock flip-flop for test purposes only. Pin should be left open (LOW) in actual application.

PUMPUP Open collector charge pump output for the signal pump

PUMPDN Open collector charge pump output for the reference pump

RSETUP Current setting resistor for the signal pump

RSETDN Current setting resistor for the reference pump

RDATA Synchronized data output

RDCLK Synchronized clock output

VCC, V

CCO

,

V

CCVCO

Most positive supply rails. Digital and analog supplies are independent on chip

VEE, V

EEVCO

Most negative supply rails. Digital and analog supplies are independent on chip

MC10E197

2–3 MOTOROLAECLinPS and ECLinPS Lite

DL140 — Rev 4

DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = GND or VCC = 4.75V to 5.25V; VEE = GND)

0°C 25°C 85°C

Symbol Characteristic min typ max min typ max min typ max Unit Condition

I

IH

Input HIGH Current 150 150 150 µA 1

I

IL

Input LOW Current 0.5 0.5 0.5 µA 1

I

EE

Power Supply Current 90 150 180 90 150 180 90 150 180 mA

I

SET

Charge Pump Bias Current 0.5 5 0.5 5 0.5 5 mA 2

I

OUT

Charge Pump Output 1 1 1 µA 3

Leakage Current

V

ACT

PUMPUP/PUMPDN VCC– 2.5 V

CCVCC

– 2.5 V

CCVCC

– 2.5 V

CC

V

Active Voltage Range

10H LOGIC LEVELS

DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = V

CCO

+ V

CCO1

= V

CCVCO

= GND)

0°C 25°C 85°C

Symbol Characteristic min typ max min typ max min typ max Unit Condition

V

OH

Output HIGH Voltage –1020 – 840 – 980 – 810 – 910 –720 mV

V

OL

Output LOW Voltage –1950 –1630 –1950 –1630 –1950 –1595 mV

V

IH

Input HIGH Voltage –1170 –840 –1130 – 810 –1060 –720 mV

V

IL

Input LOW Voltage –1950 –1480 –1950 –1480 –1950 –1445 mV

POSITIVE EMITTER COUPLED LOGIC LEVELS

DC CHARACTERISTICS (VEE = V

EEVCO

= GND; VCC = V

CCO1

= V

CCVCO

= +5 volts*)

0°C 25°C 85°C

Symbol Characteristic min typ max min typ max min typ max Unit Condition

V

OH

Output HIGH Voltage 3980 4160 4020 4190 4090 4280 mV

V

OL

Output LOW Voltage 3050 3370 3050 3370 3050 3405 mV

V

IH

Input HIGH Voltage 3830 4160 3870 4190 3940 4280 mV

V

IL

Input LOW Voltage 3050 3520 3050 3050 3050 3555 mV

1. *VOH and VOL levels will vary 1:1 with V

CC

AC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = GND or VCC = 4.75V to 5.25V; VEE = GND)

0°C 25°C 85°C

Symbol Characteristic min max min max min max Unit Condition

t

s

Time from RDATA Valid to

Rising Edge of RDCLK

T

VCO

– 550 T

VCO

– 500 T

VCO

– 500 ps 4,7

t

H

Time from Rising Edge of

RDCLK to RDATA invalid

T

VCO

T

VCO

T

VCO

ps 4,7

t

SKEW

Skew Between RDATA and

RDATA

300 300 300 ps

f

VCO

Frequency of the VCO 150 150 150 MHz 5

Tuning Ratio 1.53 1.87 1.53 1.87 1.53 1.87 6

1. Applies to the input current for each input except VCOIN

2. For a nominal set current of 3.72mA, the resistor values for RSETUP and RSETDN should be 130Ω(0.1%). Assuming no variation between

these two resistors, the current match between the PUMPUP and PUMPDN output signals should be within ±3%. I

SET

is calculated as (VEE+

1.3v – VBE)/R; where R is RSETUP or RSETDN and a nominal value for VBE is 0.85 volts.

3. Output leakage current of the PUMPUP or PUMPDN output signals when at a LOW level.

4. T

VCO

is the period of the VCO.

5. The VCO frequency determined with VCOIN = VEE + 0.5 volts and using a 10pF tuning capacitor.

6. The tuning ratio is defined as the ratio of f

VCOMAX

to F

VCOMIN

where f

VCOMAX

is measured at VCOIN = 1.3V + VEE and f

VCOMAX

is measured

at VCOIN = 2.6V + VEE.

MC10E197

MOTOROLA ECLinPS and ECLinPS Lite

DL140 — Rev 4

2–4

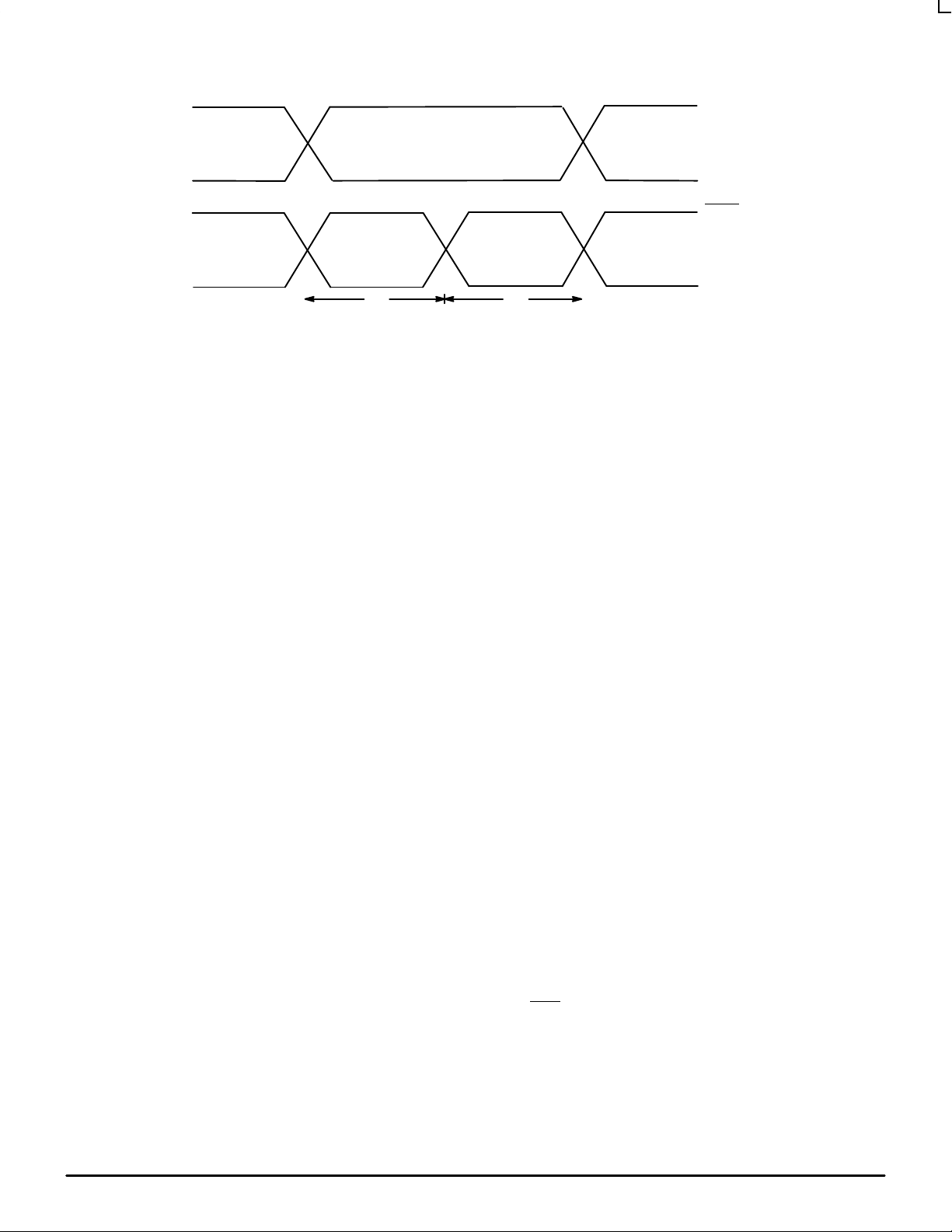

RDATA

RDATA

RDCLK

RDCLK

t

S

t

H

SETUP AND HOLD TIMING DIAGRAMS

APPLICATIONS INFORMATION

General Operation

Operation

The E197 is a phase-locked loop circuit consisting of an

internal VCO, a Data Phase detector with associated

acquisition circuitry, and a Phase/Frequency detector (Figure

1). In addition, an enable pin(ENVCO) is provided to disable

the internal VCO and enable the external VCO input. Hence,

the user has the option of supplying the VCO signal.

The E197 contains two phase detectors: a data phase

detector for synchronizing to the non-periodic pulses in the

read data stream during the data read mode of operation, and

a phase/ frequency detector for frequency (and phase) locking

to an external reference clock during the “idle” mode of

operation. The read enable (RDEN) pin muxes between these

two detectors.

Data Read Mode

The data pins (RAWD) are enabled when the RDEN pin is

placed at a logic high level, thus enabling the Data Phase

detector (Figure1) and initiating the data read mode. In this

mode, the loop is servoed by the timing information taken from

the positive edges of the input data pulses. This phase

detector samples positive edges from the RAWD signal and

generates both a pump up and pump down pulse from any

edge of the input data pulse. The leading edge of the pump up

pulse is time modulated by the leading edge of the data signal,

whereas the rising edge of the pump up pulse is generated

synchronous to the VCO clock. The falling edge of the pump

down pulse is synchronous to the falling edge of the VCO

clock and the rising edge of the pump down signal is

synchronous to the rising edge of the VCO clock. Since both

edges of the VCO are used the internal clock a duty cycle of

50%. This pulse width modulation technique is used to

generate the servoing signal which drives the VCO. The pump

down signal is a reference pulse which is included to provide

an evenly balanced differential system, thereby allowing the

synthesis of a VCO input control signal after appropriate signal

processing by the loop filter.

By using suitable external filter circuitry, a control signal for

input into the VCO can be generated by inverting the pump

down signal, summing the inverted signal with the pump up

signal and averaging the result. The polarity of this control

signal is defined as zero when the data edges lead the clock

by a half clock cycle. If the data edges are advanced with

respect to the zero polarity data/VCO edge relationship, the

control signal is defined to have a negative polarity; whereas

if the VCO is advanced with respect to the zero polarity

data/VCO edge relationship, the control signal is defined to

have a positive polarity . If there is no data edge present at the

RAWD input, the corresponding pump up and pump down

outputs are not generated and the resulting control output is

zero.

Acquisition Circuitry

The acquisition circuitry is provided to assist the data phase

detector in phase locking to the sync field that precedes the

data. For the case in which lock-up is attempted when the data

edges are coincident with the VCO edges, the pump down

signal may enter an indeterminate state for an unacceptably

long period due to the violation of internal set up and hold

times. After an initial pump down pulse, the circuit blocks

successive pump down pulses, and inserts extra pump up

pulses, during portions of the sync field that are known to

contain zeros. Thus, the data phase detector is forced to have

a nonzero output during the lock-up period, and the restoring

force ensures correction of the loop within an acceptable time.

Hence, this circuitry provides a quasi-deterministic pump

down output signal, under the condition of coincident data and

VCO edges, allowing lock-up to occur with excessive delays.

The ACQ

line is provided to disable (disable = HIGH) the

acquisition circuit during the data portion of a sector block.

Typically, this circuit is enabled at the beginning of the sync

field by a one-shot timer to ensure a timely lock-up.

The TYPE line allows the choice between two sync field

preamble types; transitions interspersed with two zeros

between transitions. These types of sync fields are used with

the 1:7 and 2:7 coding schemes, respectively.

MC10E197

2–5 MOTOROLAECLinPS and ECLinPS Lite

DL140 — Rev 4

Idle Mode

In the absence of data or when the drive is writing to the disk,

PLL servoing is accomplished by pulling the read enable line

(RDEN) low and providing a reference clock via the REFCLK

pins. The condition whereby RDEN is low selects the

Phase/Frequency detector (Figure 1) and the 10E197 is said

to be operating in the “idle mode”. In order to function as a

frequency detector the input waveform must be periodic. The

pump up and pump down pulses from the Phase/Frequency

detector will have the same frequency , phase and pulse width

only when the two clocks that are being compared have their

positive edges aligned and are of the same frequency.

As with the data phase detector, by using suitable external

filter circuitry, a VCO input control signal can be generated by

inverting the pump down signal, summing the inverted signal

with the pump up signal and averaging the result. The polarity

of this control signal is defined as zero when all positive edges

of both clocks are coincident. For the case in which the

frequencies of the two clocks are the same but the clock edges

of the reference clock are slightly advanced with respect to the

VCO clock, the control clock is defined to have a positive

polarity. A control signal with negative polarity occurs when

the edges of the reference clock are delayed with respect to

those of the VCO. If the frequencies of the two clocks are

different, the clock with the most edges per unit time will initiate

the most pulses and the polarity of the detector will reflect the

frequency error. Thus, when the reference clock is high in

frequency than the VCO clock the polarity of the control signal

is positive; whereas a control signal with negative polarity

occurs when the frequency of the reference clock is lower than

the VCO clock.

Phase-Lock Loop Theory

Introduction

Phase lock loop (PLL) circuits are fundamentally feedback

systems used to synchronize the frequency of an oscillator to

an incoming signal. In addition to frequency synchronization,

the PLL circuitry is designed to minimize the phase difference

between the system input and output signals. A block diagram

of a feedback control system is shown in Figure 1.

where:

A(s) is the product of the feed-forward transfer functions.

Figure 1. Feedback System

Xi(s) Xo(s)

A(s)

β

(s)

+

–

Xe(s)

R

β(s) is the product of the feedback transfer functions.

The transfer function for this closed loop system is

Xo(s)

Xi(s)

=

A(s)

1 + A(s)β(s)

Typically, phase lock loops are modeled as feedback

systems connected in a unity feedback configuration (β(s)=1)

with a phase detector, a VCO (voltage controlled oscillator),

and a loop filter in the feed-forward path, A(s). Figure 2

illustrates a phase lock loop as a feedback control system in

block diagram form.

F

i

F

o

PHASE

DETECTOR

K

f

V

CO

K

o

s

Figure 2. Phase Lock Loop Block Diagram

The closed loop transfer function is:

Xo(s)

Xi(s)

=

K

φ

K

o

s

F(s)

K

o

s

1 + K

φ

F(s)

where:

Kφ= the phase detector gain.

Ko= the VCO gain. Since the VCO introduces a

pole at the origin of the s-plane, Ko is divided

by s.

F(s) = the transfer function of the loop filter.

The 10E197 is designed to implement the phase detector

and VCO functions in a unity feedback loop, while allowing the

user to select the desired filter function.

Gain Constants

As mentioned, each of the three sections in the phase lock

loop block diagram has an associated open loop gain

constant. Further, the gain constant of the filter circuitry is

composed of the product of three gain constants, one for each

filter subsection. The open loop gain constant of the

feed-forward path is given by

Kol = Kφ * Ko * K1 * Kl * K

d

eqt. 1

and obtained by performing a root locus analysis.

Phase Detector Gain Constant

The gain of the phase detector is a function of the operating

mode and the data pattern. The 10E197 provides data

LOOP FILTER

F(s)

Loading...

Loading...