Transcend TS2GCF100I-P, TS1GCF100I, TS4GCF100I-P, TS8GCF100I-P, TS512MCF100I-P DATASHEET

...

T

1

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

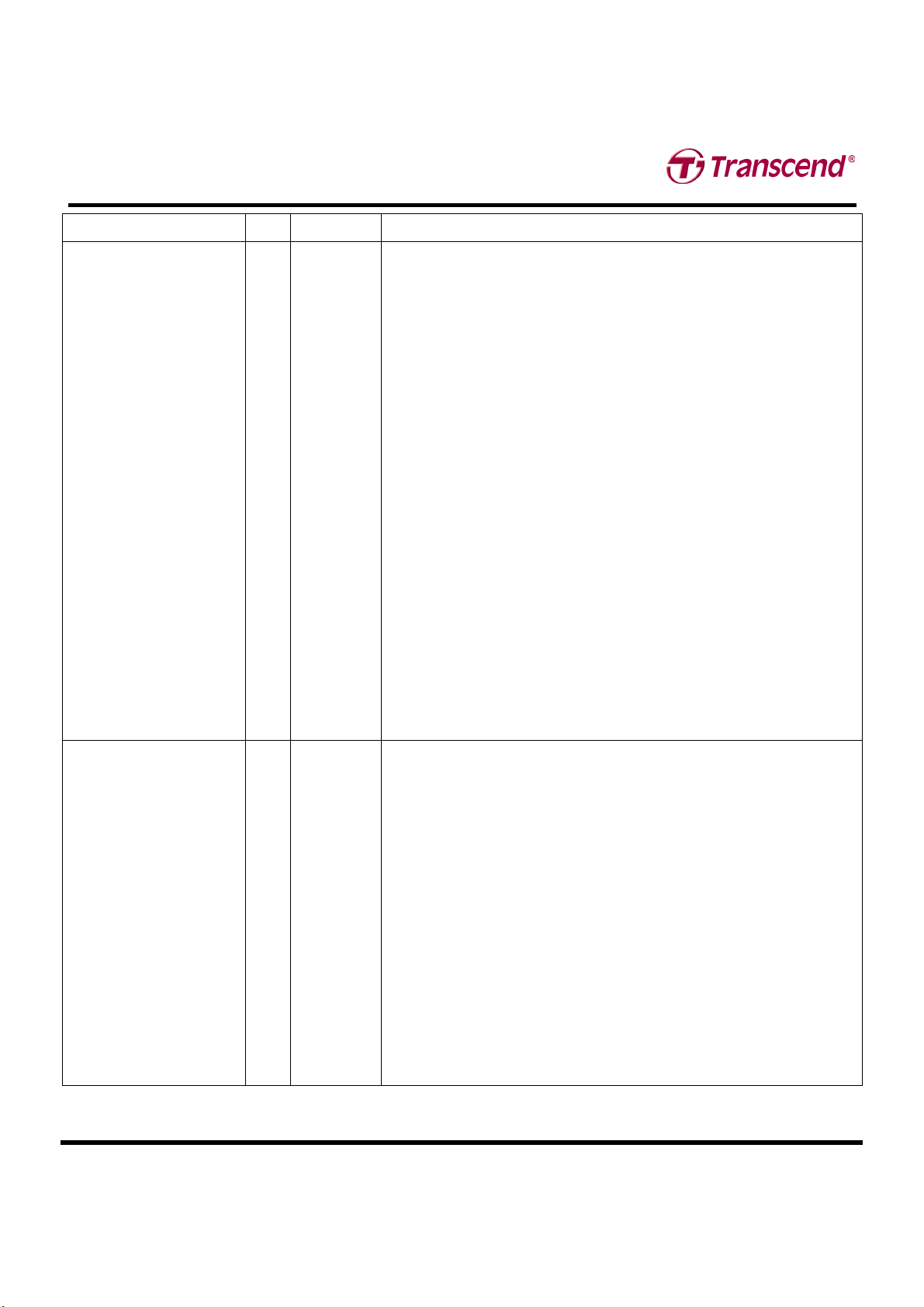

Description

The Transcend CF100I is a High Speed industrial

Compact Flash Card with high quality Flash Memory

assembled on a printed circuit board.

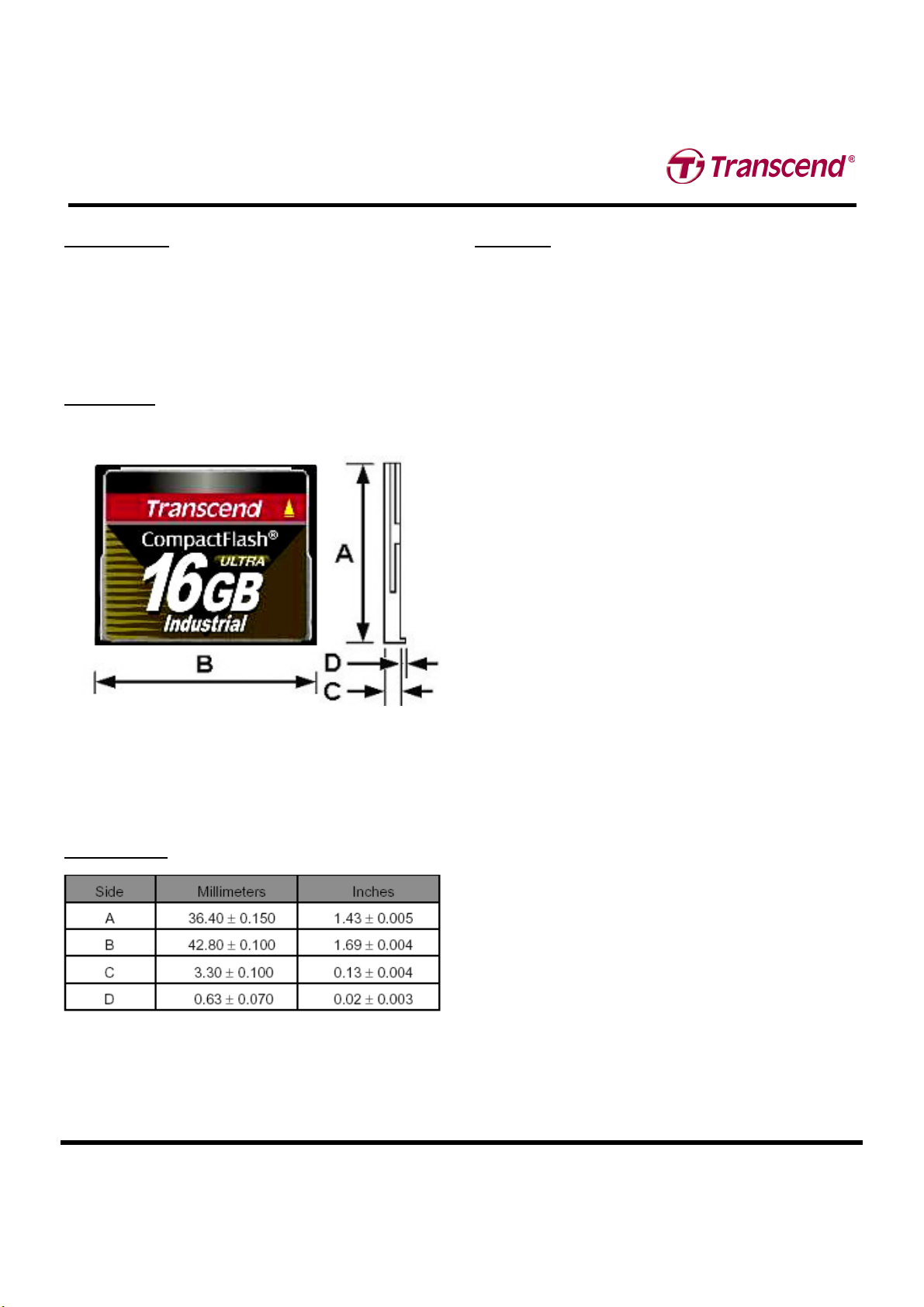

Placement

Features

•

CompactFlash Specification Version 4.1 Complaint

•

RoHS compliant products

•

Single Power Supply: 3.3V±5% or 5V±10%

•

Operating Temperature: -40oC to 85oC

•

Storage Temperature: -55oC to 100oC

•

Operating Humidity (Non condensation): 0% to 95%

•

Storage Humidity (Non condensation): 0% to 95%

•

Operation Modes:

•

True IDE Mode supports:

PC Card Memory Mode

PC Card IO Mode

True IDE Mode

Ultra DMA Mode 0 to Ultra DMA Mode 4

Multi-Word DMA Mode 0 to Multi-Word DMA Mode 4

PIO Mode 0 to PIO Mode 6

Dimensions

(Series of –P Only support PIO Mode 0 to PIO Mode

4, please see Order Information)

•

True IDE Mode: Fixed Disk (Standard)

•

PC Card Mode: Fixed Disk (Standard)

•

Durability of Connector: 10,000 times

•

MTBF: 4,000,000 hours

•

Support Wear-Leveling to extend product life

•

Support S.M.A.R.T (Self-defined)

•

Support Security Command

•

Compliant to CompactFlash, PCMCIA, and ATA

standards

•

Mechanical Shock Test: 1500G

•

Vibration Test: 20G (Peak-to-Peak)

20Hz to 2000Hz (Frequency)

Transcend Information Inc.

V1.2

T

2

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

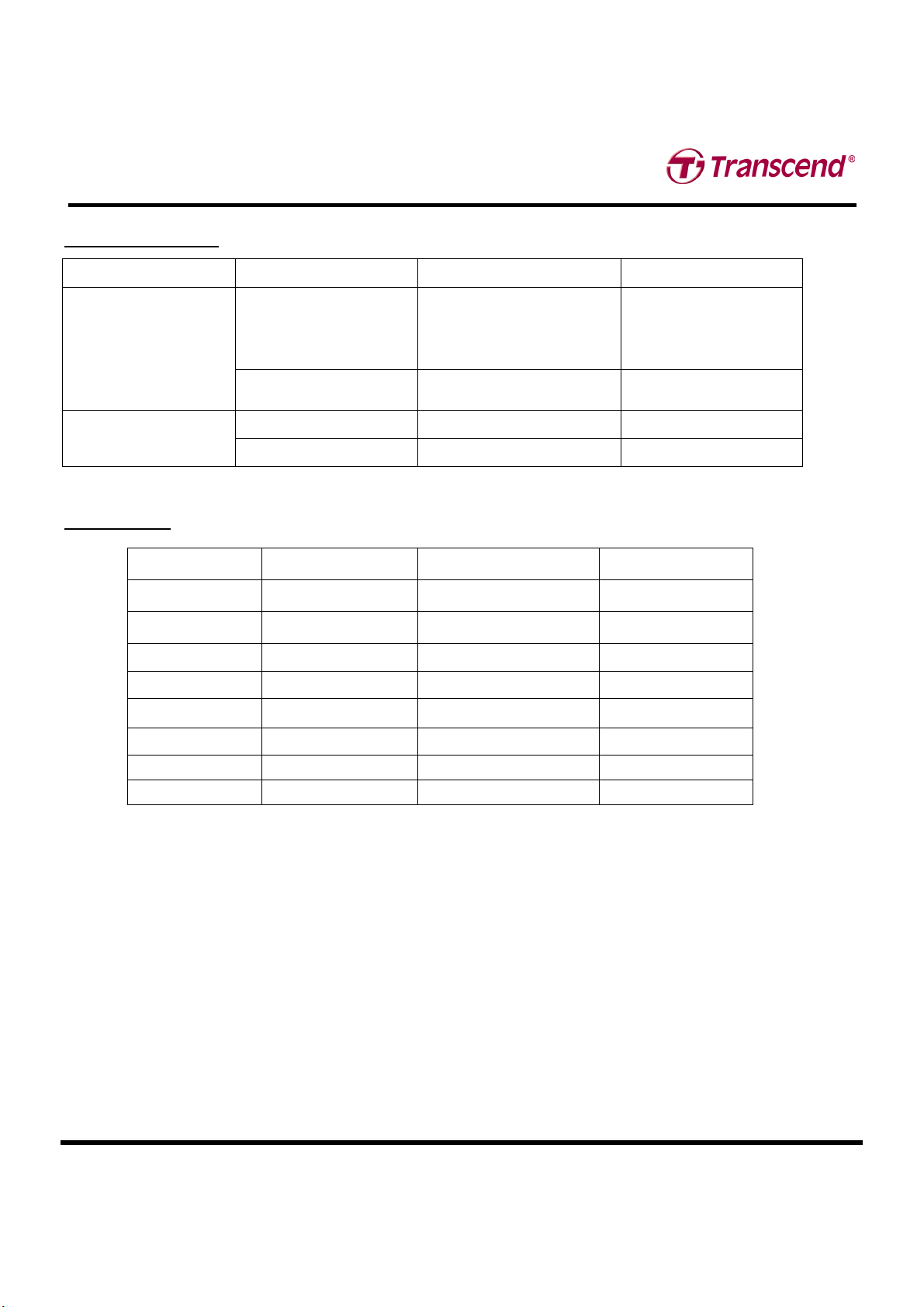

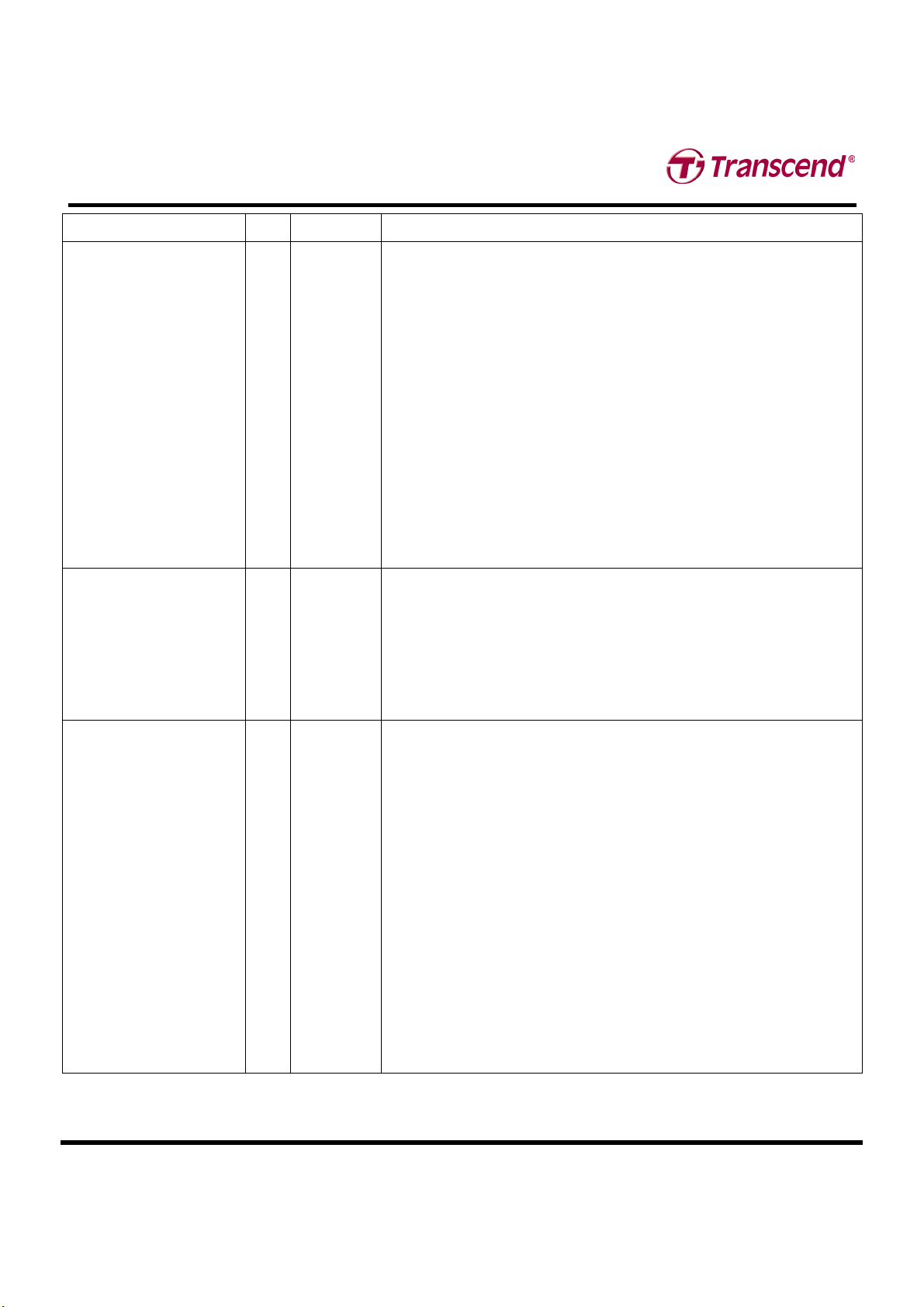

Order information

Part Number Interface Transfer Mode

Ultra DMA mode 0~4

TS128M~16GCF100I

TS128M~16GCF100I-P

C.H.S. Table

Capacity C H S

128MB 246 16 63

256MB 493 16 63

512MB 987 16 63

True IDE mode

PC Card mode (PCMCIA) 80ns, 100ns, 120ns, 250ns Fixed Disk (Standard)

True IDE mode PIO Mode 0 ~ 4 Fixed Disk (Standard)

PC Card mode (PCMCIA) 250ns Fixed Disk (Standard)

Multi-Word DMA Mode 0~4

PIO Mode 0 ~ 6

Fixed Disk (Standard)

1GB 1974 16 63

2GB 3949 16 63

4GB 7899 16 63

8GB 15798 16 63

16GB 33149 15 63

Transcend Information Inc.

V1.2

T

3

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

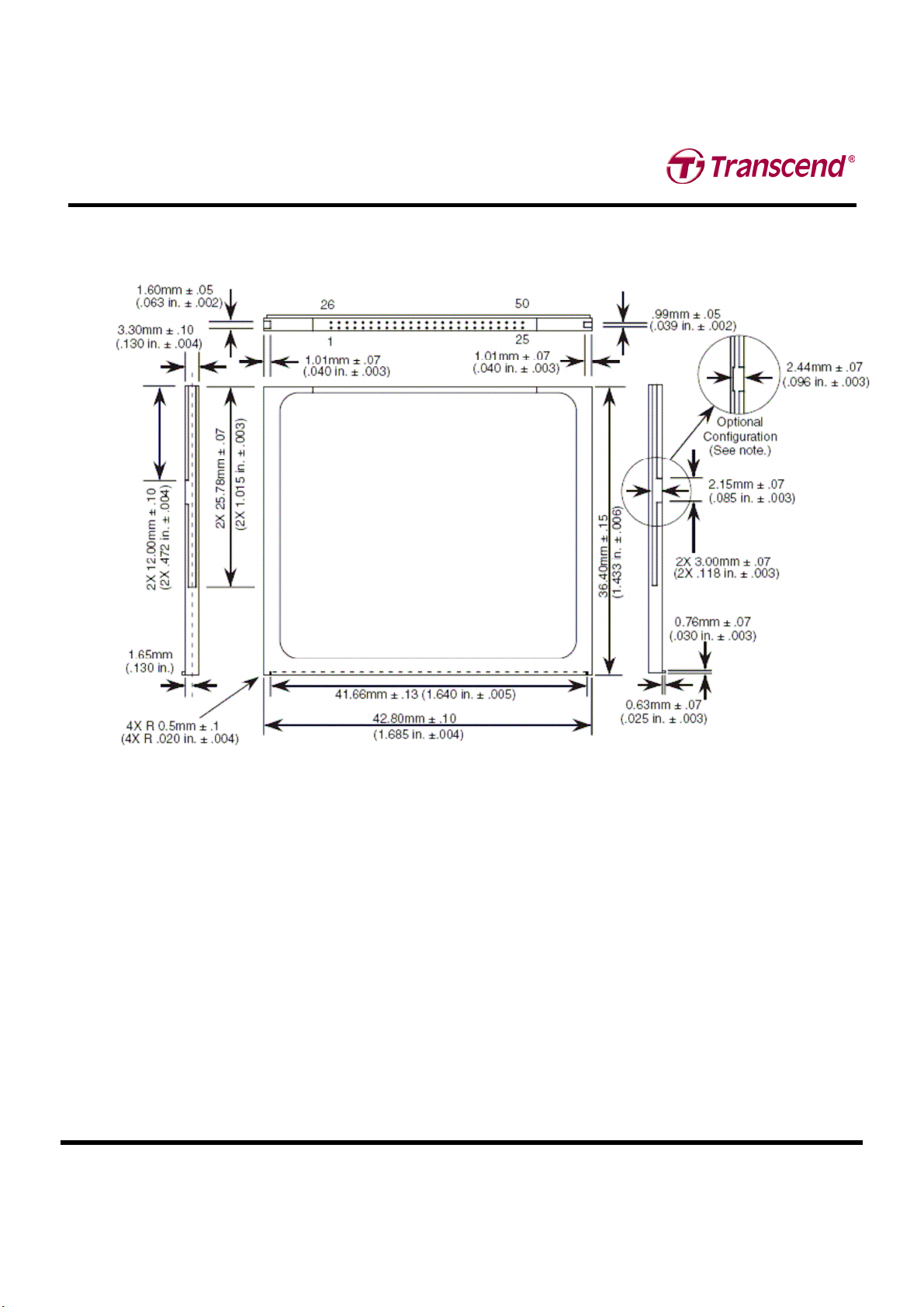

Transcend

Transcend Information Inc.

V1.2

T

4

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

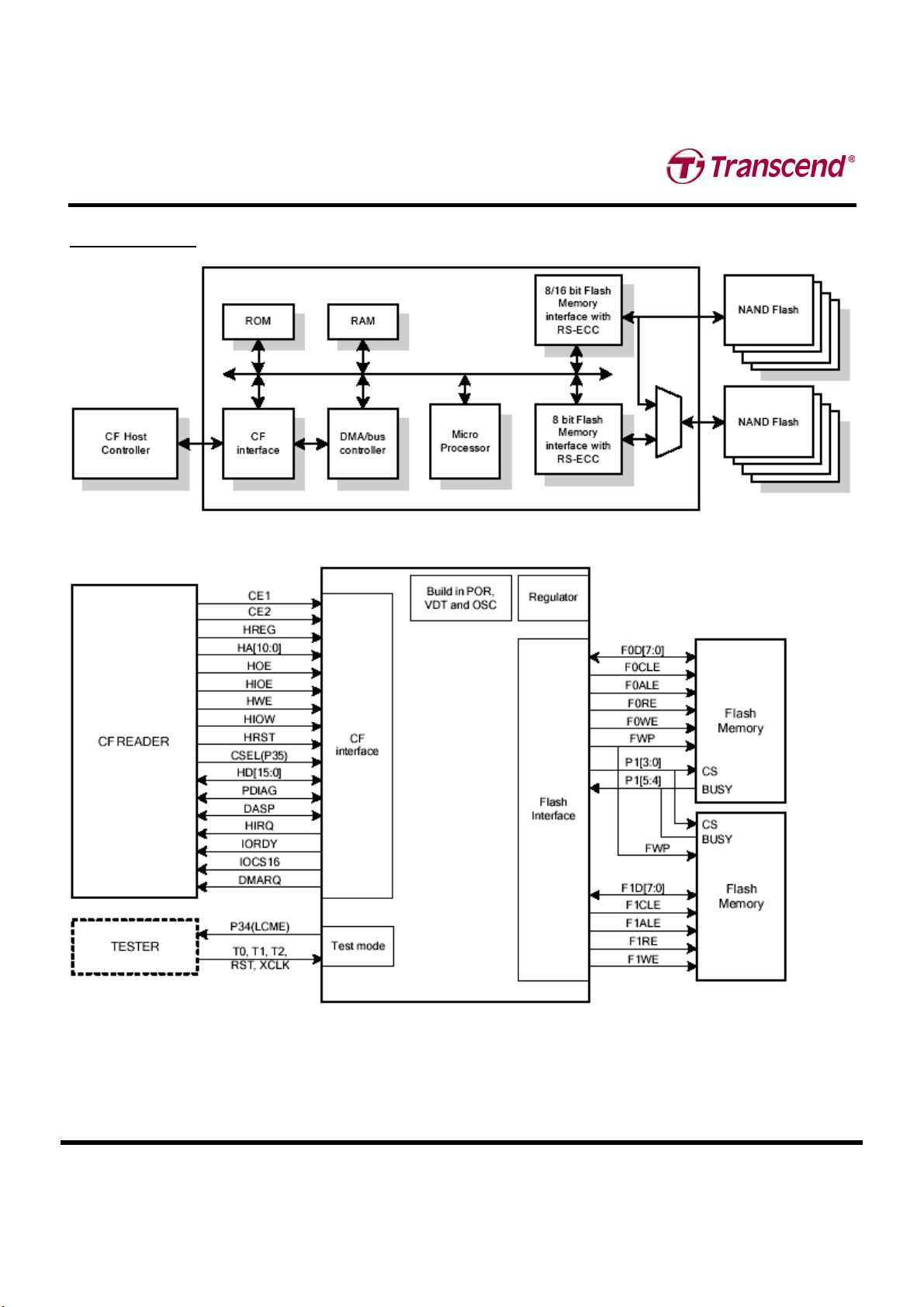

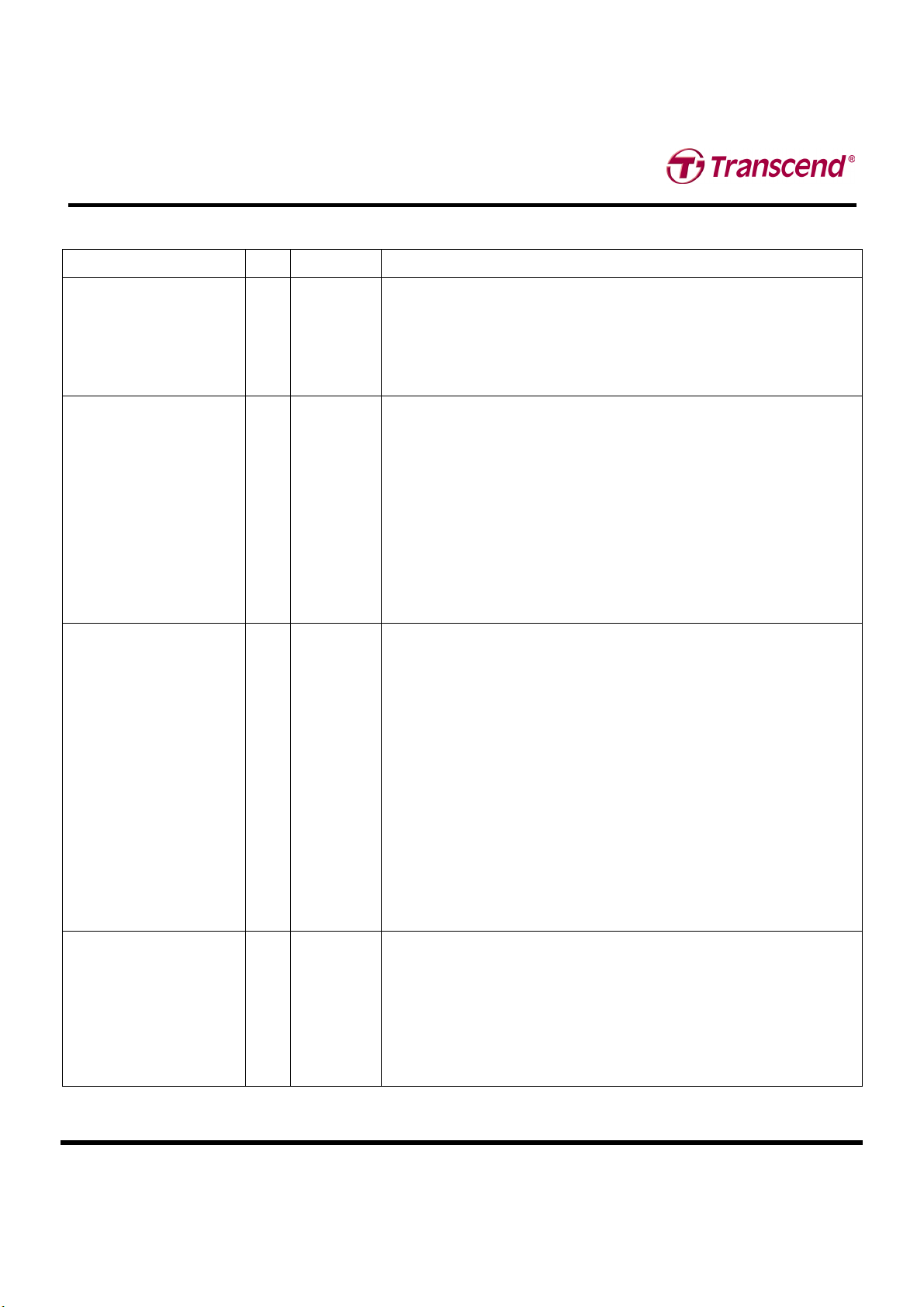

Block Diagram

Transcend Information Inc.

V1.2

T

5

r

a

n

s

c

e

n

d

I

T

r

a

n

s

c

e

T

r

a

n

(

T

(

T

(

T

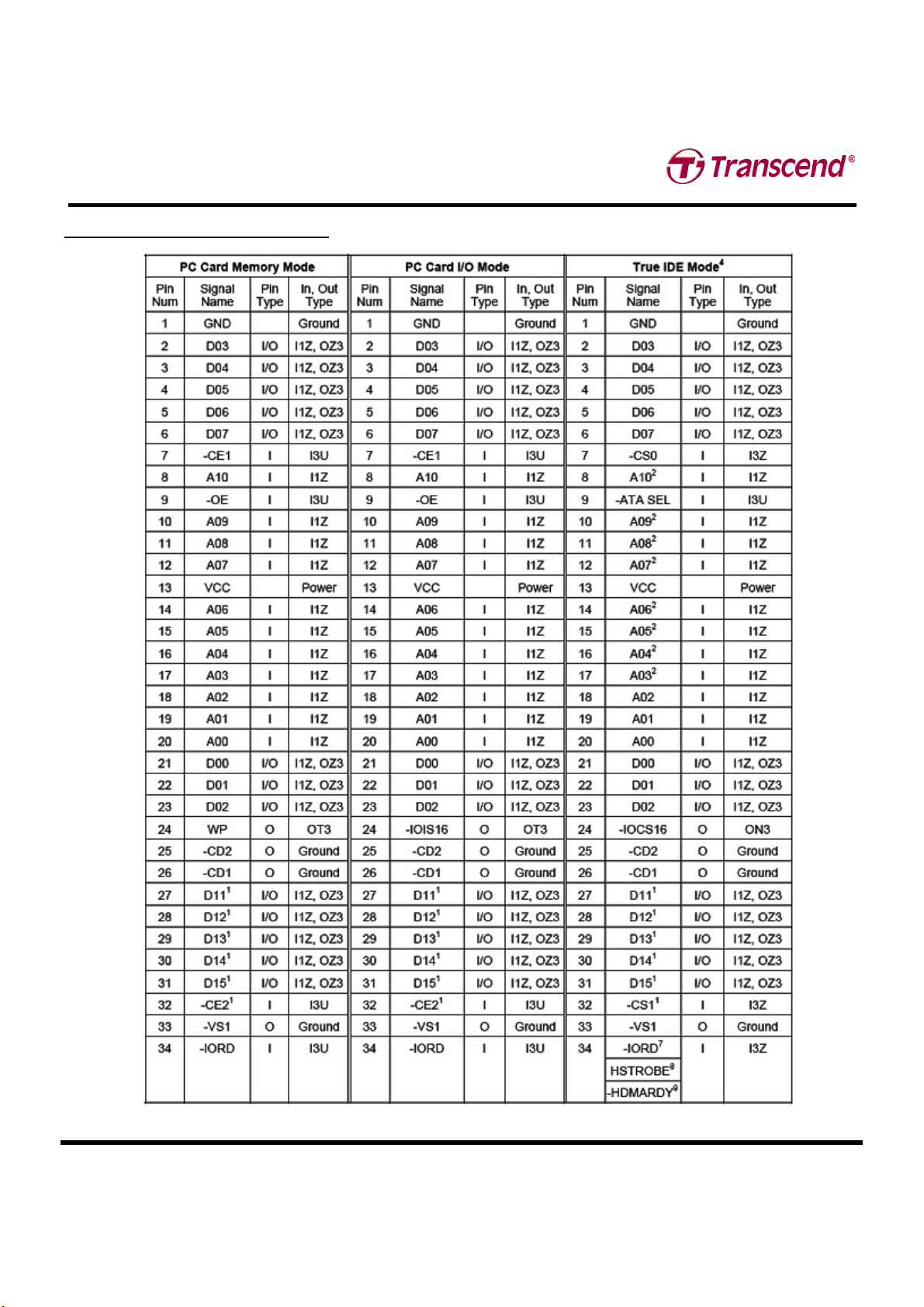

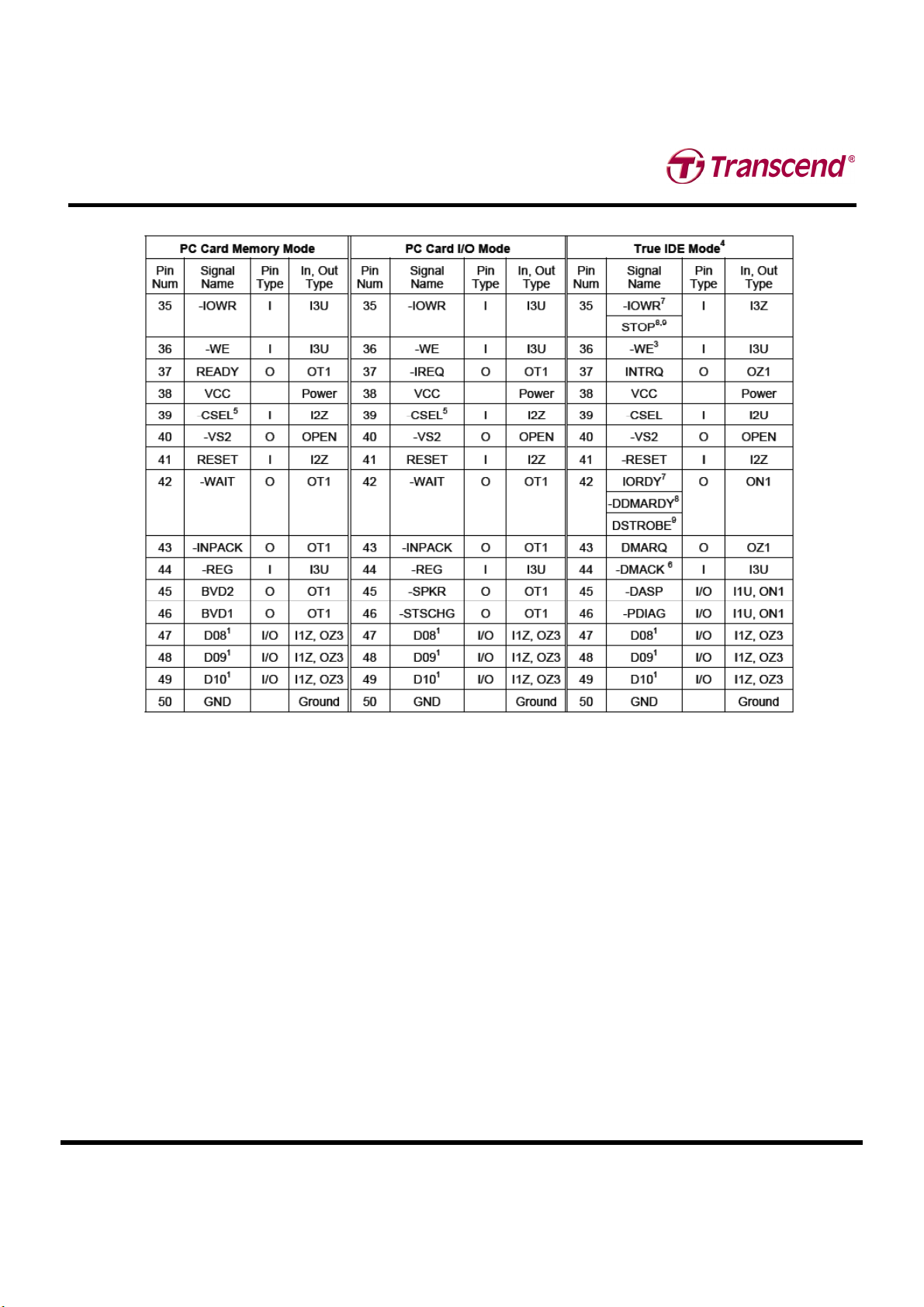

Pin Assignments and Pin Type

s

S

S

S

c

1

1

1

e

n

2

2

2

n

8

8

8

d

d

M

M

M

n

I

n

I

n

~

~

~

d

d

d

u

s

t

r

i

a

l

C

F

C

a

r

d

u

s

t

r

i

a

l

C

F

u

s

t

r

i

a

l

1

6

G

C

G

G

C

C

F

F

F

1

6

1

6

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Transcend Information Inc.

V1.2

T

6

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Note: 1) These signals are required only for 16 bit accesses and not required when installed in 8 bit

systems. Devices should allow for 3-state signals not to consume current.

2) The signal should be grounded by the host.

3) The signal should be tied to VCC by the host.

4) The mode is required for CompactFlash Storage Cards.

5) The -CSEL signal is ignored by the card in PC Card modes. However, because it is not

pulled upon the card in these modes, it should not be left floating by the host in PC Card

modes. In these modes, the pin should be connected by the host to PC Card A25 or

grounded by the host.

6) If DMA operations are not used, the signal should be held high or tied to VCC by the host. For

proper operation in older hosts: while DMA operations are not active, the card shall ignore

this signal,including a floating condition

7) Signal usage in True IDE Mode except when Ultra DMA mode protocol is active.

8) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA W rite is active.

9) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Read is active.

10) Signal usage in PC Card I/O and Memory Mode when Ultra DMA mode protocol DMA Write is active.

11) Signal usage in PC Card I/O and Memory Mode when Ultra DMA mode protocol DMA Read is active.

12) Signal usage in PC Card I/O and Memory Mode when Ultra DMA protocol is active.

Transcend Information Inc.

V1.2

T

7

select the following:

registers within the CompactFlash Storage Card,

configuration control and status

READY and Write

Present signal in

CompactFlash Storage

r

a

n

T

r

a

n

T

r

a

n

(

T

(

(

Signal Description

s

T

T

s

s

c

c

S

S

S

c

e

e

1

1

1

e

n

n

n

2

2

2

d

8

8

8

d

d

M

M

M

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

I

n

d

u

s

t

r

i

a

l

C

F

I

n

d

u

s

t

r

i

a

l

~

1

6

G

C

~

1

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Signal Name

A10 – A00

(PC Card Memory Mode)

A10 – A00

(PC Card I/O Mode)

A02 - A00

(True IDE Mode)

BVD1

(PC Card Memory Mode)

-STSCHG

(PC Card I/O Mode)

Status Changed

-PDIAG

(True IDE Mode)

BVD2

(PC Card Memory Mode)

-SPKR

(PC Card I/O Mode)

-DASP

(True IDE Mode)

Dir.

I

I

I/O

I/O

Pin

8,10,11,12,

14,15,16,17,

18,19,20

18,19,20

46 This signal is asserted high, as BVD1 is not supported.

45 This signal is asserted high, as BVD2 is not supported.

These address lines along with the -REG signal are used to

The I/O port address registers within the CompactFlash Storage Card , the

memory mapped port address

a byte in the card's information structure and its

registers.

This signal is the same as the PC Card Memory Mode signal.

In True IDE Mode, only A[02:00] are used to select the one of eight registers

in the Task File, the remaining address lines should be grounded by the

host.

This signal is asserted low to alert the host to changes in the

Protect states, while the I/O interface is configured. Its use is controlled by the

Card Config and Status Register.

In the True IDE Mode, this input / output is the Pass Diagnostic signal in the

Master / Slave handshake protocol.

This line is the Binary Audio output from the card. If the Card does not support

the Binary Audio function, this line should be held negated.

In the True IDE Mode, this input/output is the Disk Active/Slave

the Master/Slave handshake protocol.

Description

-CD1, -CD2

(PC Card Memory Mode)

-CD1, -CD2

(PC Card I/O Mode)

-CD1, -CD2

(True IDE Mode)

Transcend Information Inc.

O

26,25 These Card Detect pins are connected to ground on the

Card. They are used by the host to determine that the CompactFlash Storage

Card is fully inserted into its socket.

This signal is the same for all modes.

This signal is the same for all modes.

V1.2

T

8

the host to PC

e host to PC

a Master or a

the host

Byte of the Word. D08 is the LSB

der

r

a

n

T

r

a

n

T

r

a

n

(

(

Signal Name

-CE1, -CE2

(PC Card Memory Mode)

Card Enable

-CE1, -CE2

(PC Card I/O Mode)

Card Enable

-CS0, -CS1

(True IDE Mode)

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

T

S

1

2

8

M

~

1

6

G

C

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

Dir.

I

~

Pin

7,32

6

1

6

F

G

C

F

G

C

F

These input signals are used both to select the card and to indicate to the card

whether a byte or a word operation is being performed. -CE2 always accesses

the odd byte of the word.-CE1 accesses the even byte or the Odd byte of the

word depending on A0 and -CE2. A multiplexing scheme based on A0,-CE1,

-CE2 allows 8 bit hosts to access all data on D0-D7. See Table 27, Table 29,

Table 31, Table 35, Table 36 and Table 37.

This signal is the same as the PC Card Memory Mode signal.

In the True IDE Mode, -CS0 is the address range select for the task file

registers while -CS1 is used to select the Alternate Status Register and the

Device Control Register.

While –DMACK is asserted, -CS0 and –CS1 shall be held negated and the

width of the transfers shall be 16 bits.

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Description

-CSEL

(PC Card Memory Mode)

-CSEL

(PC Card I/O Mode)

-CSEL

(True IDE Mode)

D15 - D00

(PC Card Memory Mode)

D15 - D00

(PC Card I/O Mode)

D15 - D00

(True IDE Mode)

GND

(PC Card Memory Mode)

GND

(PC Card I/O Mode)

GND

(True IDE Mode)

I

I/O

--

39 This signal is not used for this mode, but should be connected by

31,30,29,28,

27,49,48,47,

6,5,4,3,2,

23, 22, 21

1,50 Ground.

Card A25 or grounded by the host.

This signal is not used for this mode, but should be connected by th

Card A25 or grounded by the host.

This internally pulled up signal is used to configure this device as

Slave when configured in the True IDE Mode.

When this pin is grounded, this device is configured as a Master.

When the pin is open, this device is configured as a Slave.

These lines carry the Data, Commands and Status information between

and the controller. D00 is the LSB of the Even

of the Odd Byte of the Word.

This signal is the same as the PC Card Memory Mode signal.

In True IDE Mode, all Task File operations occur in byte mode on the low or

bus D[7:0] while all data transfers are 16 bit using D[15:0].

This signal is the same for all modes.

This signal is the same for all modes.

Transcend Information Inc.

V1.2

9

of

transfers between host

device when it is ready to transfer data to

handshake manner with

held negated and

output signal is not

report

this does not prevent proper operation in any

gates I/O data onto

Card when the card is configured to use

signal has the same

in

this signal is the

T

T

T

Signal Name

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

Dir.

~

Pin

6

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Description

-INPACK

(PC Card Memory Mode)

-INPACK

(PC Card I/O Mode)

Input Acknowledge

DMARQ

(True IDE Mode)

O

43 This signal is not used in this mode.

The Input Acknowledge signal is asserted by the CompactFlash Storage Card

when the card is selected and responding to an I/O read cycle at the address

that is on the address bus. This signal is used by the host to control the enable

any input data buffers between the CompactFlash Storage Card and the CPU.

This signal is a DMA Request that is used for DMA data

and device. It shall be asserted by the

or from the host. For Multiword DMA transfers, the direction of data transfer is

controlled by -IORD and -IOWR. This signal is used in a

-DMACK, i.e., the device shall wait until the host asserts -DMACK before

negating DMARQ, and reasserting DMARQ if there is more data to transfer.

DMARQ shall not be driven when the device is not selected.

While a DMA operation is in progress, -CS0 and –CS1 shall be

the width of the transfers shall be 16 bits.

If there is no hardware support for DMA mode in the host, this

used and should not be connected at the host. In this case, the BIOS must

that DMA mode is not supported by the host so that device drivers will not

attempt DMA mode.

A host that does not support DMA mode and implements both PCMCIA and

True-IDE modes of operation need not alter the PCMCIA mode connections

while in True-IDE mode as long as

mode.

-IORD

(PC Card Memory Mode)

-IORD

(PC Card I/O Mode)

-IORD

(True IDE Mode – Except

Ultra DMA Protocol Active)

-HDMARDY

(True IDE Mode – In Ultra

DMA Protocol DMA Read)

HSTROBE

(True IDE Mode – In Ultra

DMA Protocol DMA Write)

Transcend Information Inc.

I

34 This signal is not used in this mode.

This is an I/O Read strobe generated by the host. This signal

the bus from the CompactFlash Storage

the I/O interface.

In True IDE Mode, while Ultra DMA mode is not active, this

function as in PC Card I/O Mode.

In True IDE Mode when Ultra DMA mode DMA Read is active, this signal is

asserted by the host to indicate that the host is read to receive Ultra DMA databursts. The host may negate -HDMARDY to pause an Ultra DMA transfer.

In True IDE Mode when Ultra DMA mode DMA Write is active,

data out strobe generated by the host. Both the rising and falling edge of

HSTROBE cause data to be latched by the device. The host may stop

generating HSTROBE edges to pause an Ultra DMA data-out burst.

V1.2

T

10

assertion of this

is

continuous assertion of RESET from the application

Interrupt Request. This line is

r

a

n

T

T

Signal Name

-IOWR

(PC Card Memory Mode)

-IOWR

(PC Card I/O Mode)

-IOWR

(True IDE Mode – Except

Ultra DMA Protocol Active)

STOP

(True IDE Mode – Ultra DMA

Protocol Active)

-OE

(PC Card Memory Mode)

-OE

(PC Card I/O Mode)

-ATA SEL

(True IDE Mode)

READY

(PC Card Memory Mode)

-IREQ

(PC Card I/O Mode)

INTRQ

(True IDE Mode)

s

r

a

n

s

r

a

n

s

(

T

(

T

(

T

c

c

S

S

S

c

e

e

e

1

1

1

Dir.

n

2

2

I

I

O

n

n

2

d

8

8

8

d

d

M

M

M

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

I

n

d

u

s

t

r

i

a

l

C

F

I

n

d

u

s

t

r

i

a

l

~

1

6

G

C

~

~

Pin

35

9

37

1

6

1

6

F

G

C

F

G

C

F

This signal is not used in this mode.

The I/O Write strobe pulse is used to clock I/O data on the Card Data bus into

the CompactFlash Storage Card controller registers when the CompactFlash

Storage Card is configured to use the I/O interface.

The clocking shall occur on the negative to positive edge of the signal (trailing

edge).

In True IDE Mode, while Ultra DMA mode protocol is not active, this signal has

the same function as in PC Card I/O Mode. When Ultra DMA mode protocol is

supported, this signal must be negated before entering Ultra DMA mode

protocol.

In True IDE Mode, while Ultra DMA mode protocol is active, the

signal causes the termination of the Ultra DMA burst.

This is an Output Enable strobe generated by the host interface. It is used to

read data from the CompactFlash Storage Card in Memory Mode and to read

the CIS and configuration registers.

In PC Card I/O Mode, this signal is used to read the CIS and configuration

registers.

To enable True IDE Mode this input should be grounded by the host.

In Memory Mode, this signal is set high when the CompactFlash Storage Card

ready to accept a new data transfer operation and is held low when the card is

busy.

At power up and at Reset, the READY signal is held low (busy) until the

CompactFlash Storage Card has completed its power up or reset function. No

access of any type should be made to the CompactFlash Storage Card during

this time.

Note, however, that when a card is powered up and used with RESET

continuously disconnected or asserted, the Reset function of the RESET pin is

disabled. Consequently, the

of power shall not cause the READY signal to remain continuously in the busy

state.

I/O Operation – After the CompactFlash Storage Card Card has been

configured for I/O operation, this signal is used as strobed low to generate a pulse mode interrupt or held low for a level mode

interrupt.

In True IDE Mode signal is the active high Interrupt Request to the host.

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Description

Transcend Information Inc.

V1.2

T

11

High for Common Memory,

I/O address is on

DMACK signal,

RESET pin is high with the

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Signal Name

-REG

(PC Card Memory Mode)

Attribute Memory Select

-REG

(PC Card I/O Mode)

-DMACK

(True IDE Mode)

RESET

(PC Card Memory Mode)

RESET

(PC Card I/O Mode)

-RESET

(True IDE Mode)

Dir.

I

I

Pin

44

This is a DMA Acknowledge signal that is asserted by the host in response to

41 The CompactFlash Storage Card is Reset when the

This signal is used during Memory Cycles to distinguish between Common

Memory and Register (Attribute) Memory accesses.

Low for Attribute Memory.

The signal shall also be active (low) during I/O Cycles when the

the Bus.

DMARQ to initiate DMA transfers.

While DMA operations are not active, the card shall ignore the including a floating condition.

If DMA operation is not supported by a True IDE Mode only host, this signal

should be driven high or connected to VCC by the host.

A host that does not support DMA mode and implements both PCMCIA and

True-IDE modes of operation need not alter the PCMCIA mode connections

while in True-IDE mode as long as this does not prevent proper operation all

modes.

following important exception:

The host may leave the RESET pin open or keep it continually high from the

application of power without causing a continuous Reset of the card. Under

either of these conditions, the card shall emerge from power-up having

completed an initial Reset.

The CompactFlash Storage Card is also Reset when the Soft Reset bit in the

Card Configuration Option Register is set.

This signal is the same as the PC Card Memory Mode signal.

In the True IDE Mode, this input pin is the active low hardware reset from the

host.

Description

VCC

(PC Card Memory Mode)

VCC

(PC Card I/O Mode)

VCC

(True IDE Mode)

Transcend Information Inc.

--

13,38 +5 V, +3.3 V power.

This signal is the same for all modes.

This signal is the same for all modes.

V1.2

T

12

VS2 is

Card to signal the

this signal is the

write data to the

configured in the

to VCC

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Signal Name

-VS1

-VS2

(PC Card Memory Mode)

-VS1

-VS2

(PC Card I/O Mode)

-VS1

-VS2

(True IDE Mode)

-WAIT

(PC Card Memory Mode)

-WAIT

(PC Card I/O Mode)

IORDY

(True IDE Mode – Except

Ultra DMA Mode)

-DDMARDY

(True IDE Mode – Ultra DMA

Write Mode)

DSTROBE

(True IDE Mode – Ultra

DMA Read Mode)

Dir.

O

O

Pin

33

40

42 The -WAIT signal is driven low by the CompactFlash Storage

Voltage Sense Signals. -VS1 is grounded on the Card and sensed by the Host

so that the CompactFlash Storage Card CIS can be read at 3.3 volts and reserved by PCMCIA for a secondary voltage and is not connected on the Card.

This signal is the same for all modes.

This signal is the same for all modes.

host to delay completion of a memory or I/O cycle that is in progress.

This signal is the same as the PC Card Memory Mode signal.

In True IDE Mode, except in Ultra DMA modes, this output signal may be used

as IORDY.

In True IDE Mode, when Ultra DMA mode DMA Write is active, this signal is

asserted by the host to indicate that the device is read to receive Ultra DMA

data-in bursts. The device may negate -DDMARDY to pause an Ultra DMA

transfer.

In True IDE Mode, when Ultra DMA mode DMA Write is active,

data out strobe generated by the device. Both the rising and falling edge of

DSTROBE cause data to be latched by the host. The device may stop

generating DSTROBE edges to pause an Ultra DMA data-out burst.

Description

-WE

(PC Card Memory Mode)

-WE

(PC Card I/O Mode)

-WE

(True IDE Mode)

Transcend Information Inc.

I

36 This is a signal driven by the host and used for strobing memory

registers of the CompactFlash Storage Card when the card is

memory interface mode. It is also used for writing the configuration registers.

In PC Card I/O Mode, this signal is used for writing the configuration registers.

In True IDE Mode, this input signal is not used and should be connected

by the host.

V1.2

T

13

does not have a write protect

IOIS16) function. A

performed at

device is expecting

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

WP

(PC Card Memory Mode)

Write Protect

-IOIS16

(PC Card I/O Mode)

-IOCS16

(True IDE Mode)

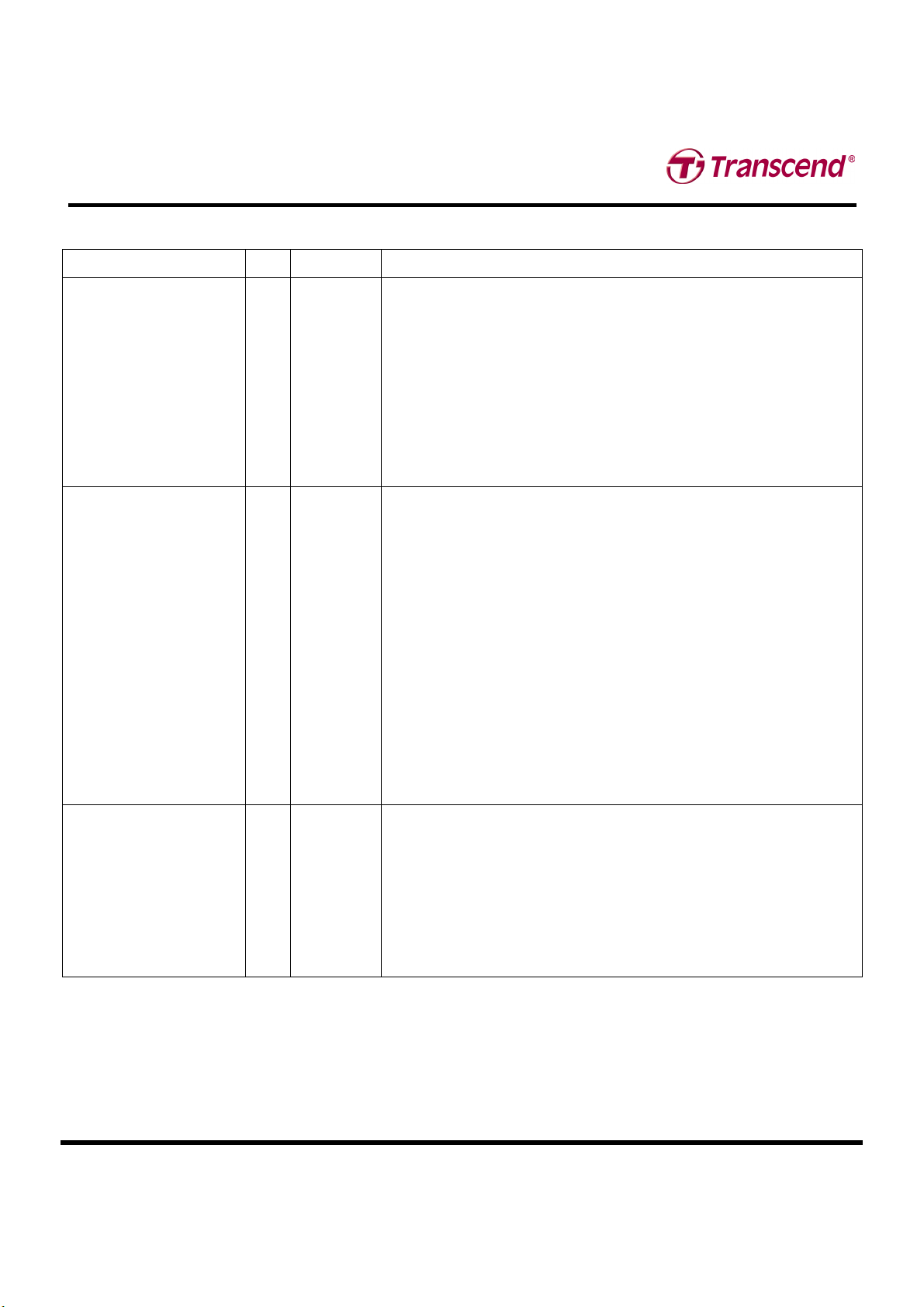

Electrical Specification

The following tables indicate all D.C. Characteristics for the CompactFlash Storage Card. Unless

otherwise stated, conditions are:

Vcc = 5V ±10%

Vcc = 3.3V ± 5%

O

6

~

1

6

24

F

G

C

F

G

C

F

Memory Mode – The CompactFlash Storage Card

switch. This signal is held low after the completion of the reset initialization

sequence.

I/O Operation – When the CompactFlash Storage Card is configured for I/O

Operation Pin 24 is used for the -I/O Selected is 16 Bit Port (Low signal indicates that a 16 bit or odd byte only operation can be

the addressed port.

In True IDE Mode this output signal is asserted low when this

a word data transfer cycle.

C

1

1

1

C

F

C

0

0

I

)

0

0

I

)

0

0

I

)

a

r

d

a

r

d

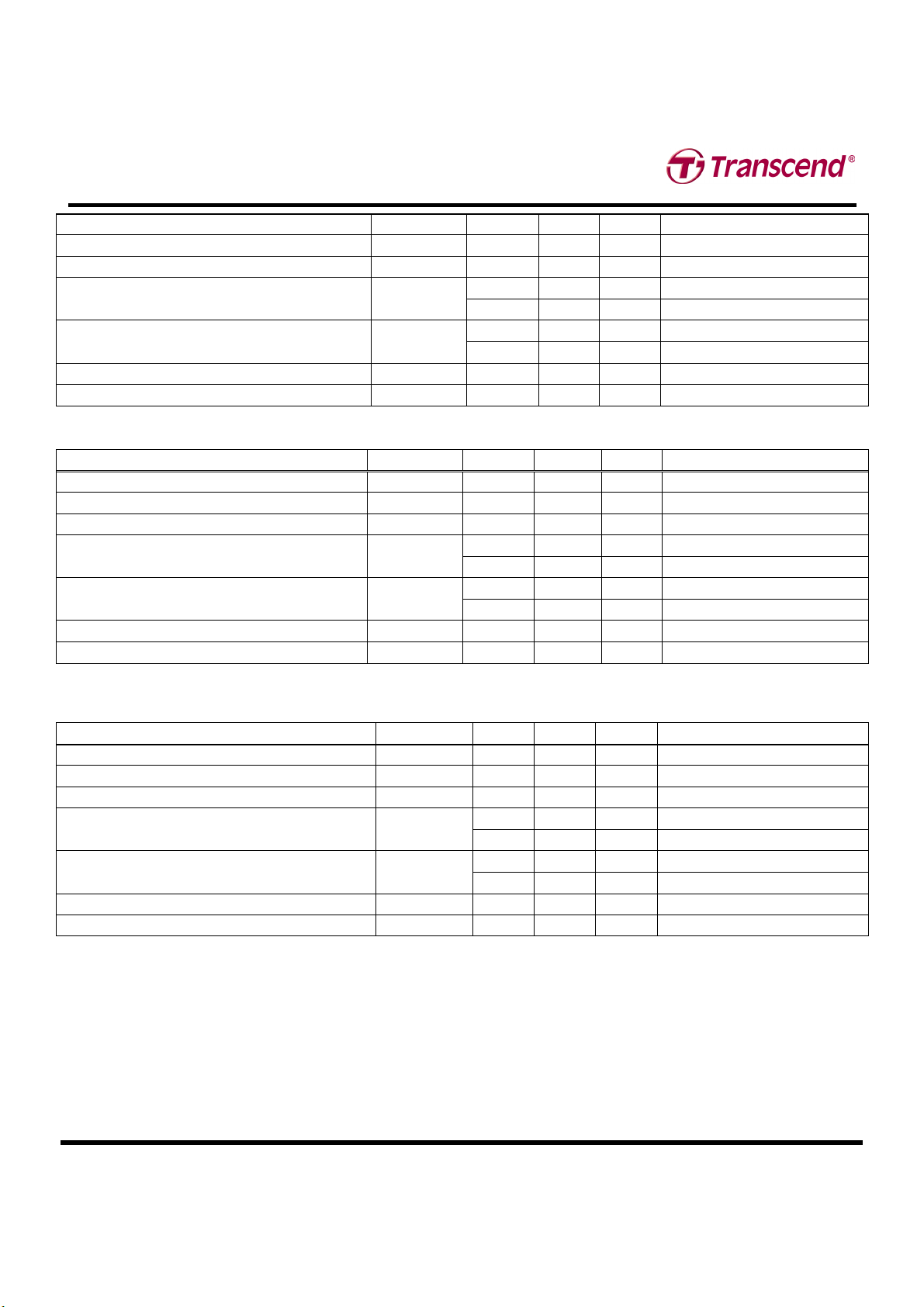

Absolute Maximum Conditions

Input Power

Input Leakage Current

Input Characteristics

CompactFlash interface I/O at 5.0V

Transcend Information Inc.

Parameter Symbol Min. Max. Unit Remark

V1.2

T

14

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

Supply Voltage VCC 4.5 5.5 V

High level output voltage VOH VCC-0.8

Low level output voltage VOL 0.8 V

High level input voltage VIH

Low level input voltage VIL

Pull up resistance2 RPU 50. 73 kOhm

Pull down resistance RPD 50 97 kOhm

CompactFlash interface I/O at 3.3V

Parameter Symbol Min. Max. Unit Remark

Supply Voltage VCC 3.135 3.465 V

High level output voltage VOH VCC-0.8

Low level output voltage VOL 0.8 V

High level input voltage VIH

Low level input voltage VIL

Pull up resistance2 RPU 52.7 141 kOhm

Pull down resistance RPD 47.5 172 kOhm

The I/O pins other than CompactFlash interface

Parameter Symbol Min. Max. Unit Remark

Supply Voltage VCC 3.135 3.465

High level output voltage VOH 2.4 V

Low level output voltage VOL 0.4 V

High level input voltage VIH

Low level input voltage VIL

Pull up resistance RPU 40 kOhm

Pull down resistance RPD 40 kOhm

1. Include CE1, CE2, HREG, HOE. HIOE, HWE, HIOW pins.

2. Include CE1, CE2, HREG, HOE. HIOE, HWE, HIOW, CSEL, PDIAG, DASP pins.

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

C

F

C

0

0

I

)

0

0

I

)

0

0

I

)

4.0 V Non-schmitt trigger

2.92 V Schmitt trigger1

2.4 V Non-schmitt trigger

2.05 V Schmitt trigger1

2.0 V Non-schmitt trigger

1.4 2.0 V Schmitt trigger

0.8 1.2 V Schmitt trigger

a

r

d

a

r

d

V

0.8 V Non-schmitt trigger

1.70 V Schmitt trigger1

V

0.6 V Non-schmitt trigger

1.25 V Schmitt trigger1

V

0.8 V Non-schmitt trigger

Transcend Information Inc.

V1.2

T

15

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

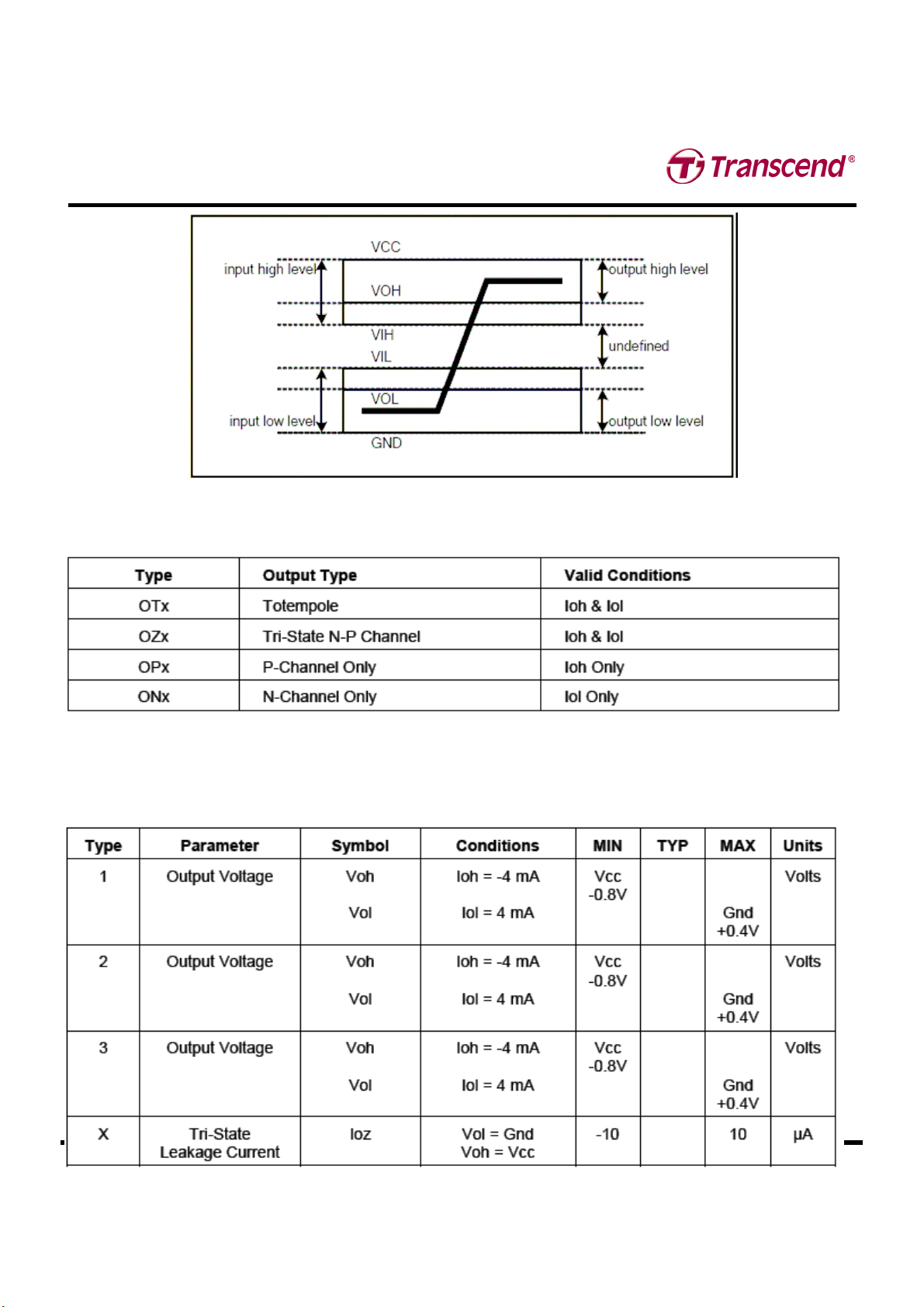

Output Drive Type

Output Drive Characteristics

Transcend Information Inc.

V1.2

T

16

r

a

n

T

r

a

n

T

r

a

n

(

T

(

T

(

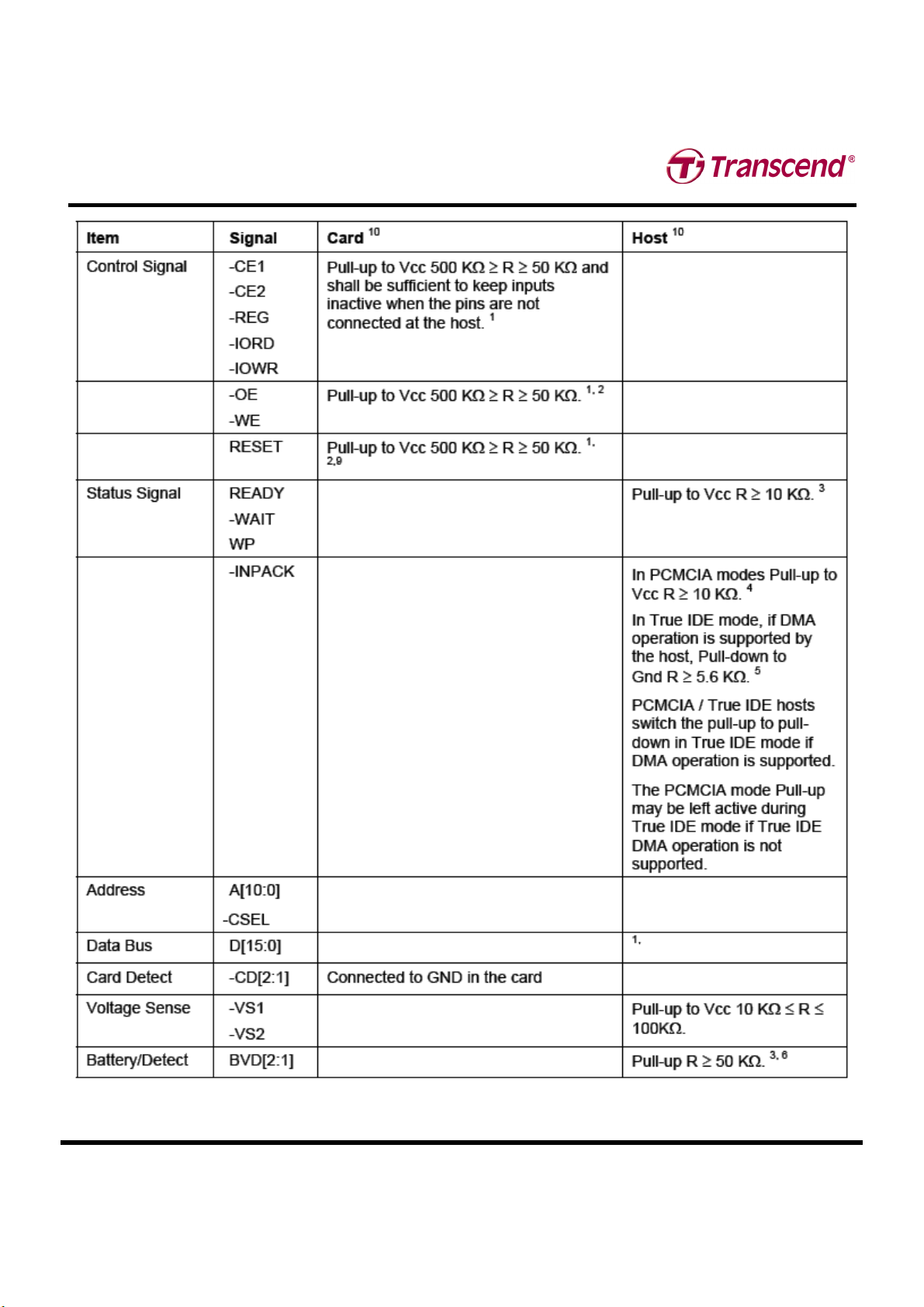

Signal Interface

s

s

T

s

c

c

S

S

S

c

e

e

1

1

1

e

n

n

n

2

2

2

d

8

8

8

d

d

M

M

M

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

I

n

d

u

s

t

r

i

a

l

C

F

I

n

d

u

s

t

r

i

a

l

~

1

6

G

C

~

1

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Transcend Information Inc.

V1.2

T

17

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Notes: 1) Control Signals: each card shall present a load to the socket no larger than 50 pF

low state and 150 μ A high state, including pull-resistor. The socket shall be able to drive at least the following

load

10

while meeting all AC timing requirements: (the number of sockets wired in parallel) multiplied by (50 pF

with DC current 700 μ A low state and 150 μ A high state per socket).

2) Resistor is optional.

3) Status Signals: the socket shall present a load to the card no larger than 50 pF

state and 100 μ A high state, including pull-up resistor. The card shall be able to drive at least the following load

10

while meeting all AC timing requirements: 50 pF at a DC current of 400 μ A low state and 100 μ A high state.

4) Status Signals: the socket shall present a load to the card no larger than 50 pF

state and 100 μ A high state, including pull-up resistor. The card shall be able to drive at least the following load

10

while meeting all AC timing requirements: 50 pF at a DC current of 400 μ A low state and 100 μ A high state.

5) Status Signals: the socket shall present a load to the card no larger than 50 pF

state and 100 μ A high state, including pull-up resistor. The card shall be able to drive at least the following load

10

while meeting all AC timing requirements: 50 pF at a DC current of 400 μ A low state and 1100 μ A high state.

6) BVD2 was not defined in the JEIDA 3.0 release. Systems fully supporting JEIDA release 3 SRAM cards shall

pull-up pin 45 (BVD2) to avoid sensing their batteries as “Low.”

7) Address Signals: each card shall present a load of no more than 100pF

150μA high state. The host shall be able to drive at least the following load

requirements: (the number of sockets wired in parallel) multiplied by (100pF with DC current 450μ A low state

and 150μ A high state per socket).

8) Data Signals: the host and each card shall present a load no larger than 50pF

150μ A high state. The host and each card shall be able to drive at least the following load

AC timing requirements: 100pF with DC current 1.6mA low state and 300μ A high state. This permits the host to

wire two sockets in parallel without derating the card access speeds.

9) Reset Signal: This signal is pulled up to prevent the input from floating when a CFA to PCMCIA adapter is used

in a PCMCIA revision 1 host. However, to minimize DC current drain through the pull-up resistor in normal

operation the pull-up should be turned off once the Reset signal has been actively driven low by the host.

Consequently, the input is specified as an I2Z because the resistor is not necessarily detectable in the input

current leakage test.

10) Host and card restrictions for CF Advanced Timing Modes and Ultra DMA modes: Additional Requirements for

CF Advanced Timing Modes and Ultra DMA Electrical Requirements for additional required limitations on the

implementation of CF Advanced Timing modes and Ultra DMA modes respectively.

Additional Requirements for CF Advanced Timing Modes

The CF Advanced Timing modes include PCMCIA I/O and Memory modes that are 100ns or faster and True

IDE PIO Modes 5,6 and Multiword DMA Modes 3,4.

When operating in CF Advanced timing modes, the host shall conform to the following requirements:

1) Only one CF device shall be attached to the CF Bus.

2) The host shall not present a load of more than 40pF to the device for all signals, including any cabling.

3) The maximum cable length is 0.15 m (6 in). The cable length is measured from the card connector to the host

controller. 0.46 m (18 in) cables are not supported.

4) The -WAIT and IORDY signals shall be ignored by the host.

Devices supporting CF Advanced timing modes shall also support slower timing modes, to ensure operability with

systems that do not support CF Advanced timing modes

10

at a DC current of 700 μ A

10

at a DC current of 400 μ A low

10

at a DC current of 400 μ A low

10

at a DC current of 400 μ A low

10

at a DC current of 450μ A low state and

while meeting all AC timing

10

10

at a DC current of 450μ A and

10

while meeting all

Transcend Information Inc.

V1.2

T

18

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

T

r

a

n

s

c

e

n

d

I

n

d

(

T

S

1

2

8

M

~

(

T

S

1

2

(

T

S

Ultra DMA Electrical Requirements

Host and Card signal capacitance limits for Ultra DMA operation

The host interface signal capacitance at the host connector shall be a maximum of 25 pF for each signal as measured at

1 MHz. The card interface signal capacitance at the card connector shall be a maximum of 20 pF for each signal as

measured at 1 MHz.

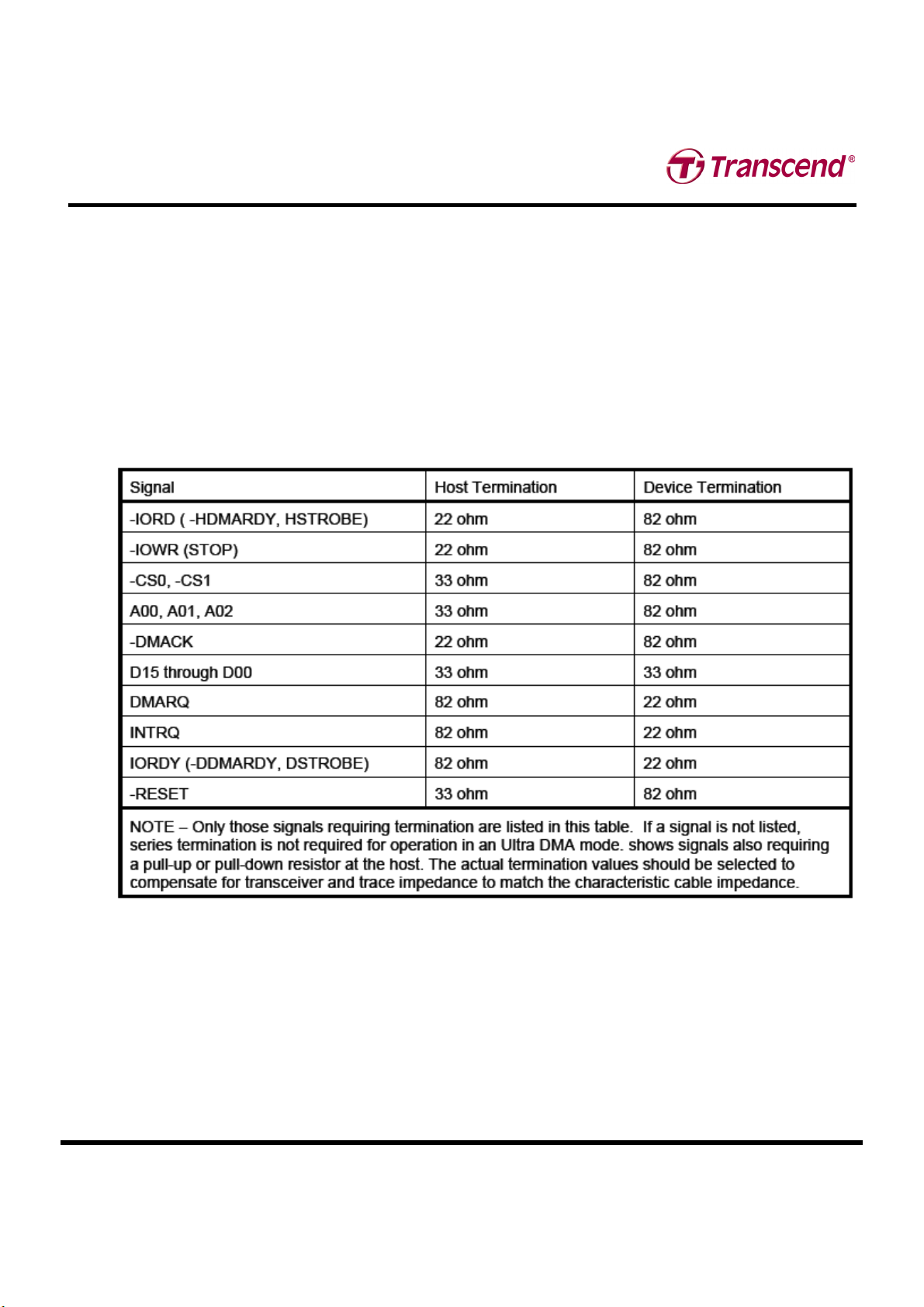

Series termination required for Ultra DMA operation

Series termination resistors are required at both the host and the card for operation in any of the Ultra DMA modes. Table

13 describes typical values for series termination at the host and the device.

8

1

2

8

M

M

~

~

r

u

s

t

1

6

G

1

6

G

1

6

G

C

i

a

l

r

i

a

l

C

F

1

C

F

1

C

F

C

C

1

0

0

F

0

F

F

0

0

0

C

a

r

d

C

C

I

)

I

)

I

)

a

r

d

a

r

d

Transcend Information Inc.

Table: Typical Series Termination for Ultra DMA

V1.2

T

19

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Printed Circuit Board (PCB) Trace Requirements for Ultra DMA

On any PCB for a host or device supporting Ultra DMA:

The longest D[15:00] trace shall be no more than 0.5" longer than either STROBE trace as measured from the

IC pin to the connector.

The shortest D[15:00] trace shall be no more than 0.5" shorter than either STROBE trace as measured from

the IC pin to the connector.

Ultra DMA Mode Cabling Requirement

Operation in Ultra DMA mode requires a crosstalk suppressing cable. The cable shall have a grounded line

between each signal line.

For True IDE mode operation using a cable with IDE (ATA) type 40 pin connectors it is recommended that the

host sense the cable type using the method described in the ANSI INCITS 361-2002 AT Attachment - 6

standard, to prevent use of Ultra DMA with a 40 conductor cable.

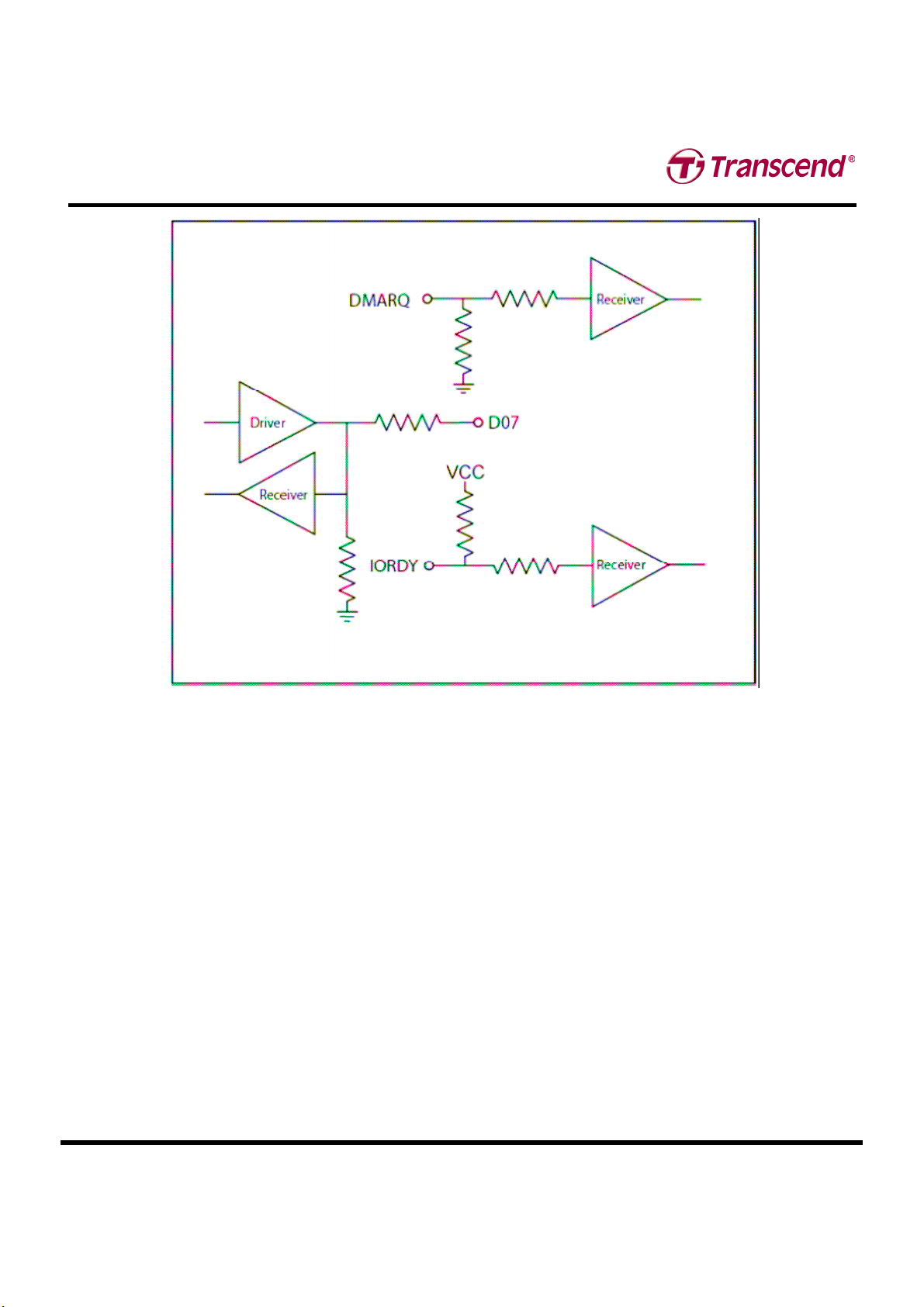

Table: Ultra DMA Termination with Pull-up or Pull down Example

Transcend Information Inc.

V1.2

T

20

r

a

n

s

c

e

n

d

I

n

d

u

T

r

a

n

s

c

e

n

d

I

8

8

8

d

M

M

M

n

I

n

T

r

a

n

s

c

e

n

(

T

S

1

S

S

1

1

2

2

2

(

T

(

T

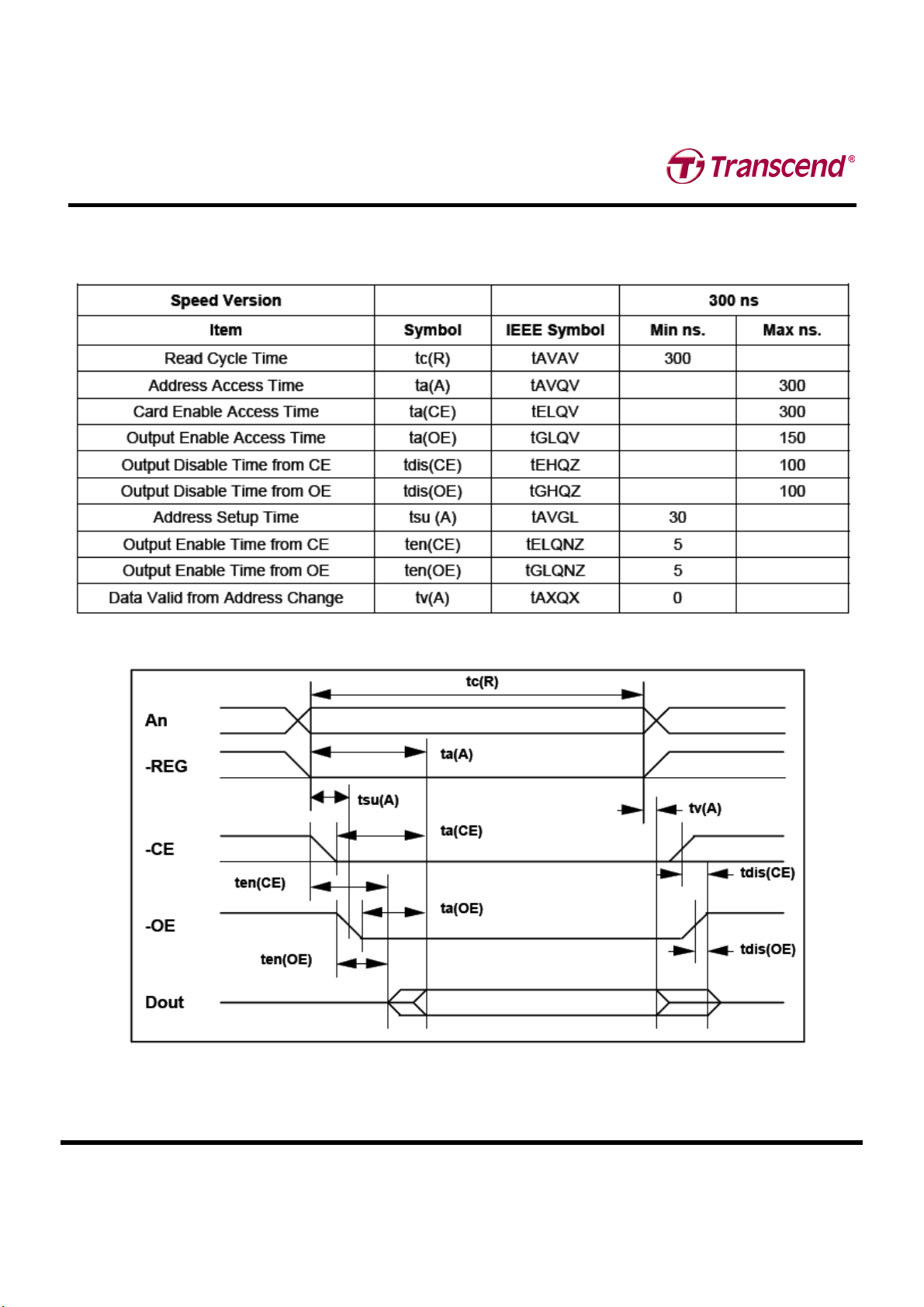

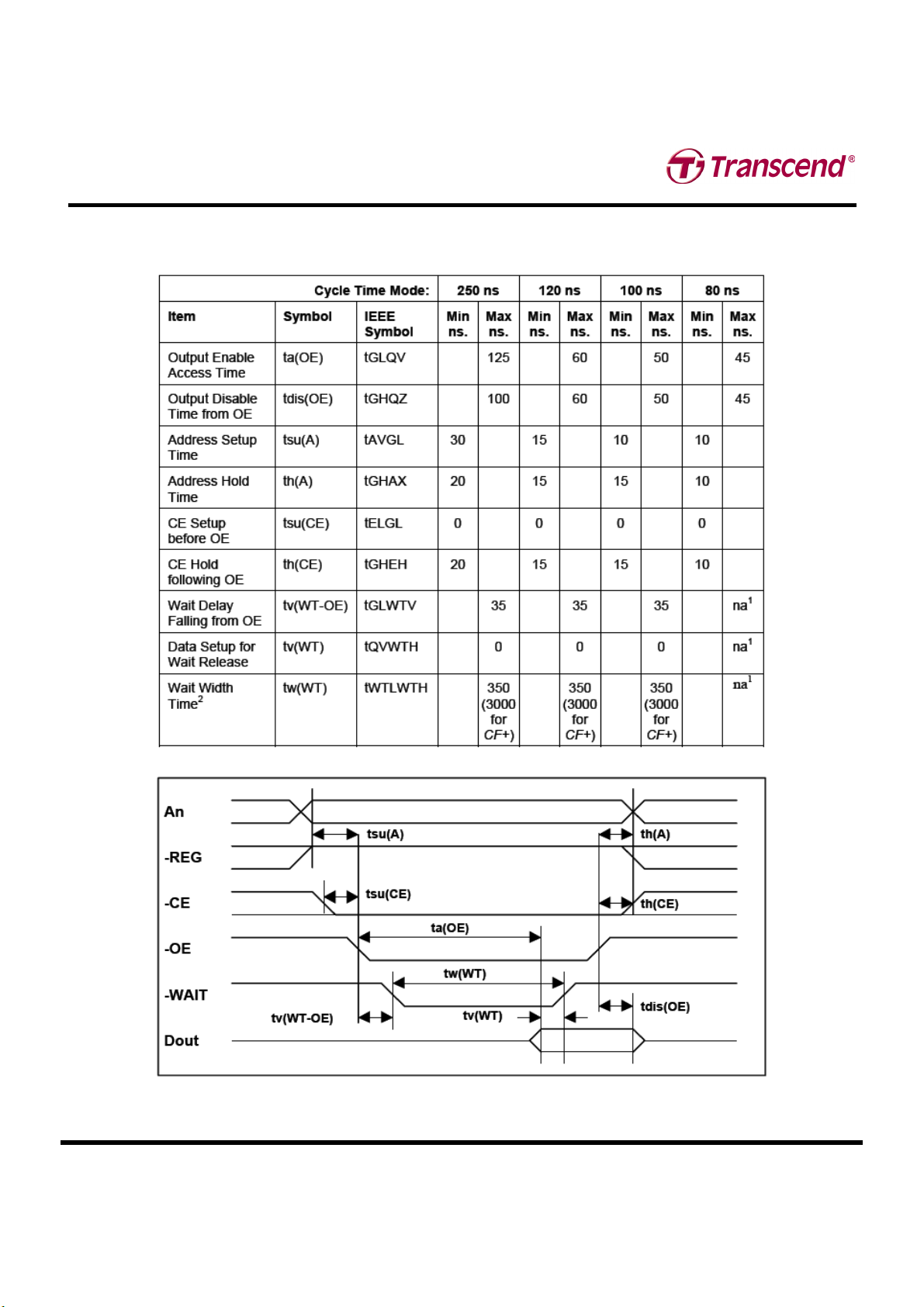

Attribute Memory Read Timing Specification

s

d

u

s

d

u

s

~

1

6

~

1

6

~

1

6

t

t

t

G

G

G

r

i

a

l

C

F

C

a

r

d

r

i

a

l

C

F

r

i

a

l

C

F

C

F

C

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Transcend Information Inc.

V1.2

T

21

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

C

a

r

d

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

C

F

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

(

T

S

1

2

8

M

~

1

6

G

C

(

T

S

1

2

8

M

~

1

(

T

S

1

2

8

M

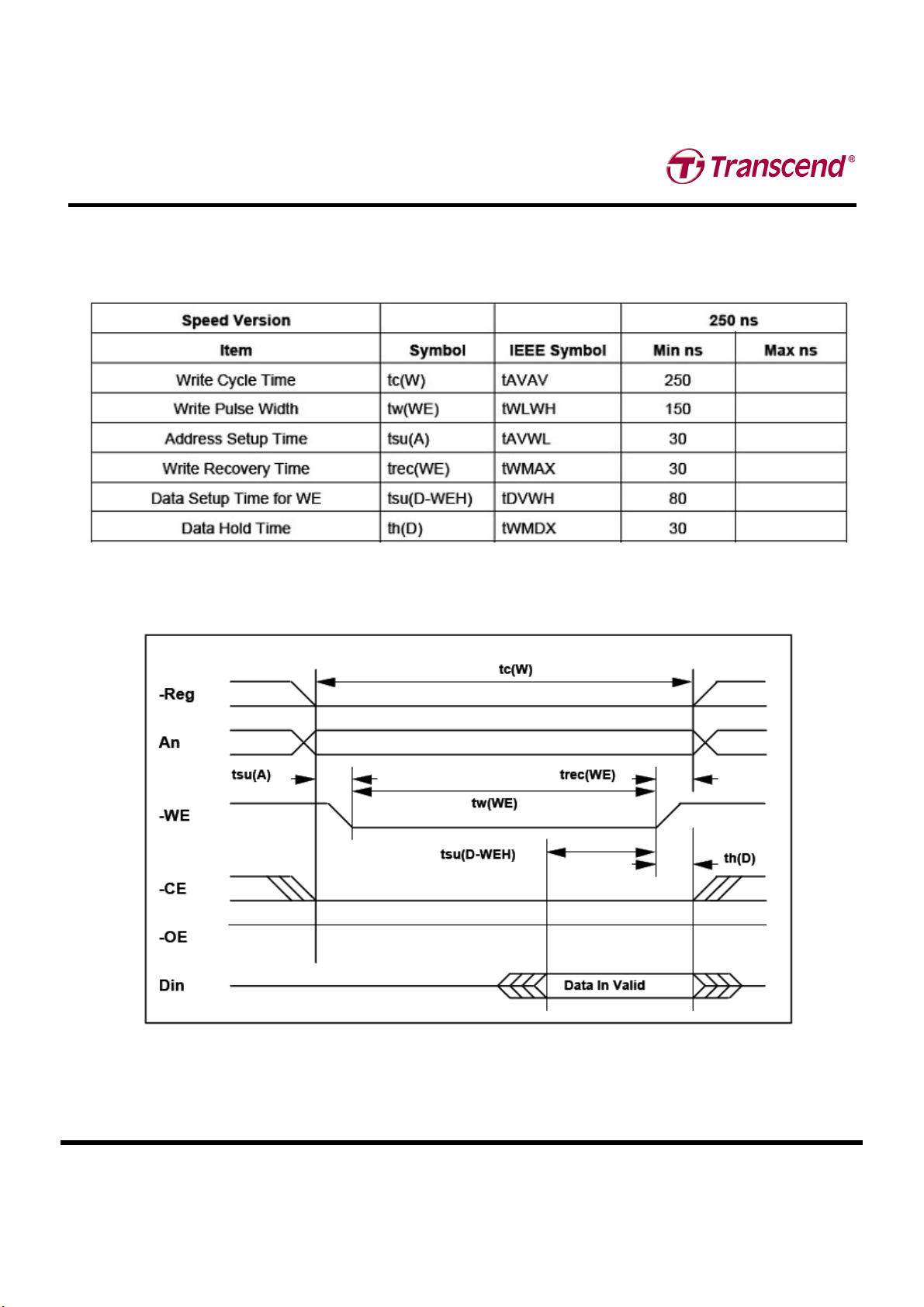

Configuration Register (Attribute Memory) Write Timing Specification

6

~

1

6

G

G

C

C

F

F

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Transcend Information Inc.

V1.2

T

22

r

a

n

s

c

e

n

d

I

n

d

u

s

t

r

i

a

l

T

r

a

n

s

c

e

n

d

I

n

d

u

s

t

T

r

a

n

s

c

e

n

d

I

n

d

(

T

S

1

2

8

M

~

(

T

S

1

2

1

2

8

8

(

T

S

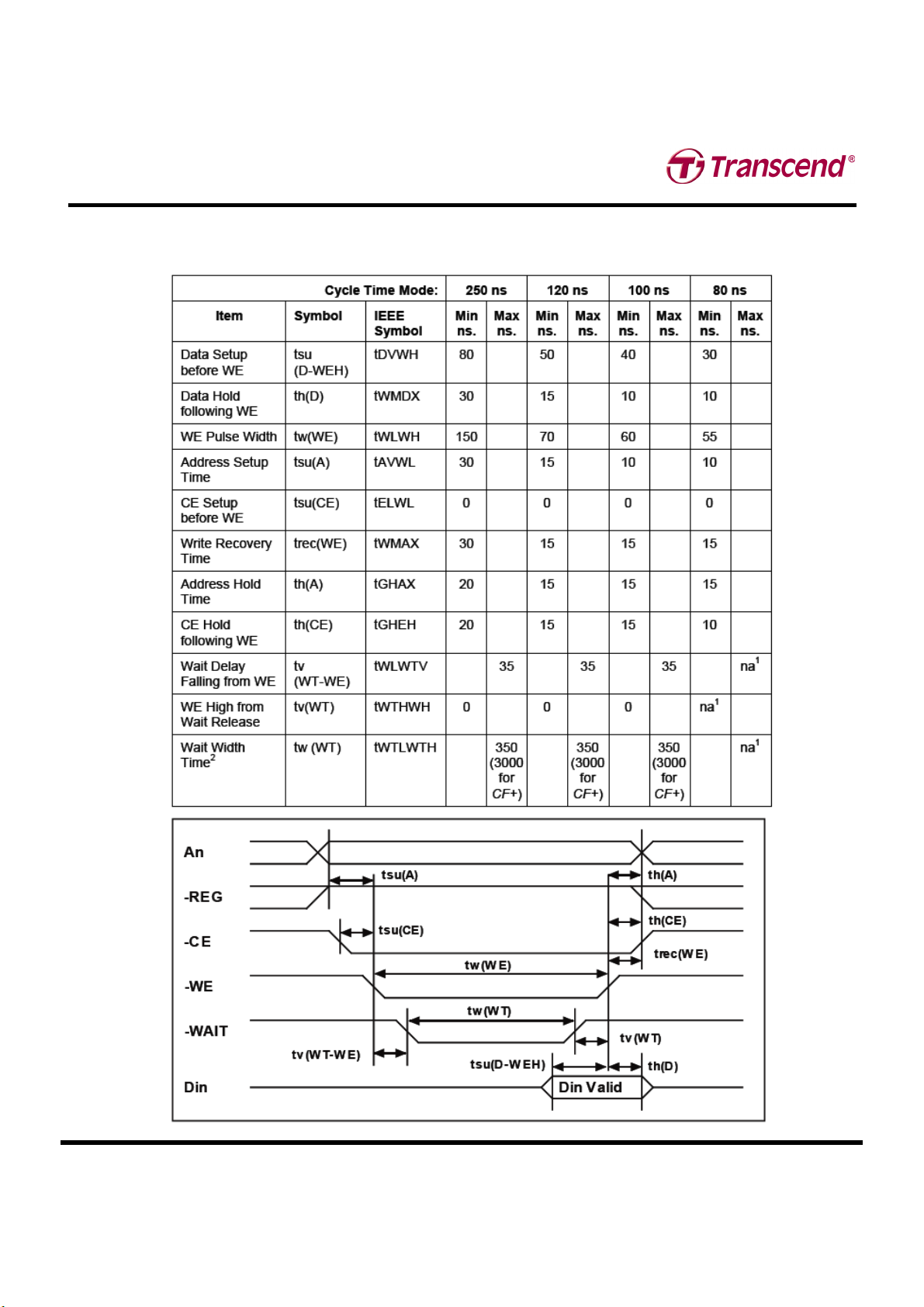

Common Memory Read Timing Specification

M

M

~

~

r

u

s

t

1

6

G

1

6

G

1

6

G

C

i

a

l

i

C

C

C

a

F

F

F

C

l

C

1

1

1

r

0

0

F

0

F

F

0

0

0

C

a

r

d

C

C

I

)

I

)

I

)

a

r

d

a

r

d

Transcend Information Inc.

V1.2

T

23

r

a

n

s

c

e

n

d

I

n

d

u

T

r

a

n

s

c

e

n

d

I

8

8

8

d

M

M

M

n

I

n

T

r

a

n

s

c

e

n

(

T

S

1

S

S

1

1

2

2

2

(

T

(

T

Common Memory Write Timing Specification

s

d

u

s

d

u

s

~

1

6

~

1

6

~

1

6

t

t

t

G

G

G

r

i

a

l

C

F

C

a

r

d

r

i

a

l

C

F

r

i

a

l

C

F

C

F

C

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Transcend Information Inc.

V1.2

T

24

r

a

n

s

c

e

n

d

I

n

d

u

s

T

r

a

n

s

c

e

n

d

I

n

T

r

a

n

s

c

e

n

d

(

T

S

1

2

S

1

1

2

2

8

8

8

(

T

S

(

T

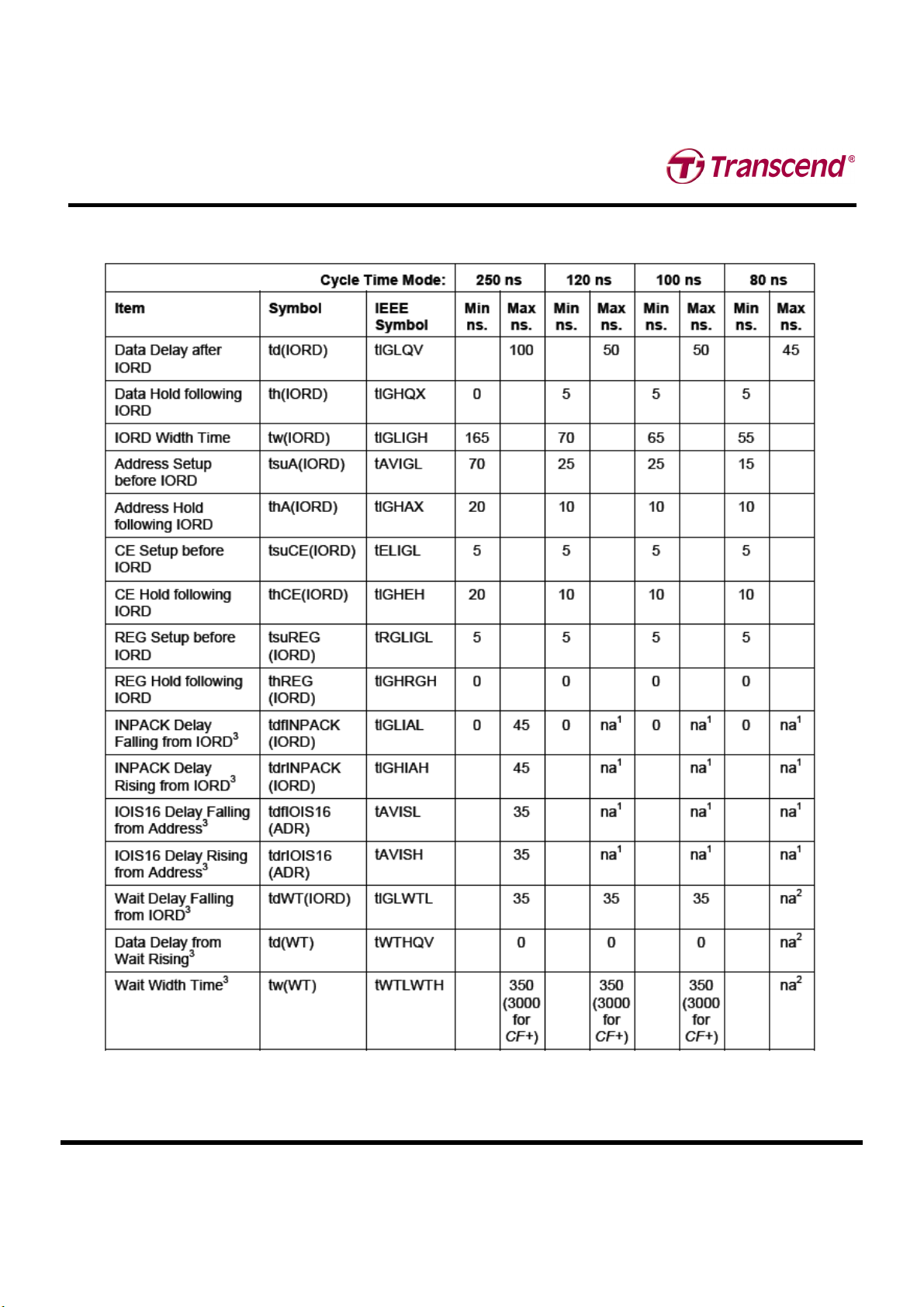

I/O Input (Read) Timing Specification

M

M

M

d

I

n

~

~

~

d

t

u

s

t

u

s

t

1

6

G

1

6

G

1

6

G

r

i

a

l

C

F

C

a

r

d

r

i

a

l

C

F

r

i

a

l

C

F

C

F

C

F

C

1

1

1

0

0

0

F

0

0

0

C

C

I

I

I

)

)

)

a

r

d

a

r

d

Transcend Information Inc.

V1.2

Loading...

Loading...