TOSHIBA TC74VHC595F, TC74VHC595FN, TC74VHC595FT, TC74VHC595FK Technical data

TC74VHC595F/FN/FT/FK

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74VHC595F,TC74VHC595FN,TC74VHC595FT,TC74VHC595FK

8-Bit Shift Register/Latch (3-state)

The TC74VHC595 is an advanced high speed 8-BIT SHIFT REGISTER/LATCH fabricated with silicon gate C2MOS technology.

It achieves the high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

The TC74VHC595 contains an 8-bit static shift register which feeds an 8-bit storage register.

Shift operation is accomplished on the positive going transition of the SCK input. The output register is loaded with the contents of the shift register on the positive going transition of the RCK input. Since RCK and SCK signal are independent, parallel outputs can be held stable during the shift operation. And, since the parallel outputs are 3-state, it can be directly connected to 8-bit bus. This register can be used in serial-to-parallel conversion, data receivers, etc.

An input protection circuit ensures that 0 to 5.5 V can be applied to the input pins without regard to the supply voltage. This device can be used to interface 5 V to 3 V systems and two supply systems such as battery back up. This circuit prevents device destruction due to mismatched supply and input voltages.

Features

•High speed: fmax = 185 MHz (typ.) at VCC = 5 V

•Low power dissipation: ICC = 4 μA (max) at Ta = 25°C

•High noise immunity: VNIH = VNIL = 28% VCC (min)

•Power down protection is provided on all inputs.

•Balanced propagation delays: tpLH − tpHL

•Wide operating voltage range: VCC (opr) = 2 V to 5.5 V

•Low noise: VOLP = 1.0 V (max)

•Pin and function compatible with 74ALS595

Note: xxxFN (JEDEC SOP) is not available in Japan.

TC74VHC595F

TC74VHC595FN

TC74VHC595FT

TC74VHC595FK

Weight |

|

SOP16-P-300-1.27A |

: 0.18 g (typ.) |

SOL16-P-150-1.27 |

: 0.13 g (typ.) |

TSSOP16-P-0044-0.65A |

: 0.06 g (typ.) |

VSSOP16-P-0030-0.50 |

: 0.02 g (typ.) |

1 |

2007-10-01 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TC74VHC595F/FN/FT/FK |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin Assignment |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IEC Logic Symbol |

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(13) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QB |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

VCC |

|

G |

(12) |

|

EN3 |

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RCK |

|

C2 |

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

QC |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

QA |

|

|

|

|

|

(10) |

|

|

SRG8 |

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCLR |

|

(11) |

|

R |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

QD |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

SI |

|

SCK |

|

|

|

C/1 |

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

QE |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

|

|

|

|

|

|

|

|

(14) |

|

|

|

|

|

|

|

|

(15) |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G |

|

|

|

|

SI |

|

|

1D |

|

2D |

3 |

QA |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(1) |

||||||||||

|

|

|

|

|

|

QF |

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

RCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QB |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(2) |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QC |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(3) |

||

|

|

|

|

|

|

QG |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

SCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QD |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(4) |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QE |

||

|

|

|

|

|

|

QH |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(5) |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCLR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QF |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(6) |

||

|

|

|

|

|

GND |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

QH’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QG |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(7) |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2D |

3 |

QH |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(9) |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(top view) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QH’ |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Truth Table |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Inputs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Function |

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

SI |

|

|

SCK |

|

|

SCLR |

|

|

RCK |

|

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

X |

|

|

X |

|

|

|

X |

|

|

X |

|

H |

QA thru QH outputs disable |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

X |

|

|

X |

|

|

|

X |

|

|

X |

|

L |

QA thru QH outputs enable |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

X |

|

|

X |

|

|

|

L |

|

|

X |

|

X |

Shift register is cleared. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

L |

|

|

|

|

|

|

|

|

H |

|

|

X |

|

X |

|

First stage of S.R. becomes “L”. Other stages store the data of previous stage, |

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

respectively. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

H |

|

|

|

|

|

|

|

|

H |

|

|

X |

|

X |

|

First stage of S.R. becomes “H”. Other stages store the data of previous stage, |

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

respectively. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

X |

|

|

|

|

|

|

|

|

H |

|

|

X |

|

X |

State of S.R. is not changed. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

X |

|

|

X |

|

|

|

X |

|

|

|

|

|

|

X |

S.R. data is stored into storage register. |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

X |

|

|

X |

|

|

|

X |

|

|

|

|

|

|

X |

Storage register stage is not changed. |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X: Don’t care

2 |

2007-10-01 |

TC74VHC595F/FN/FT/FK

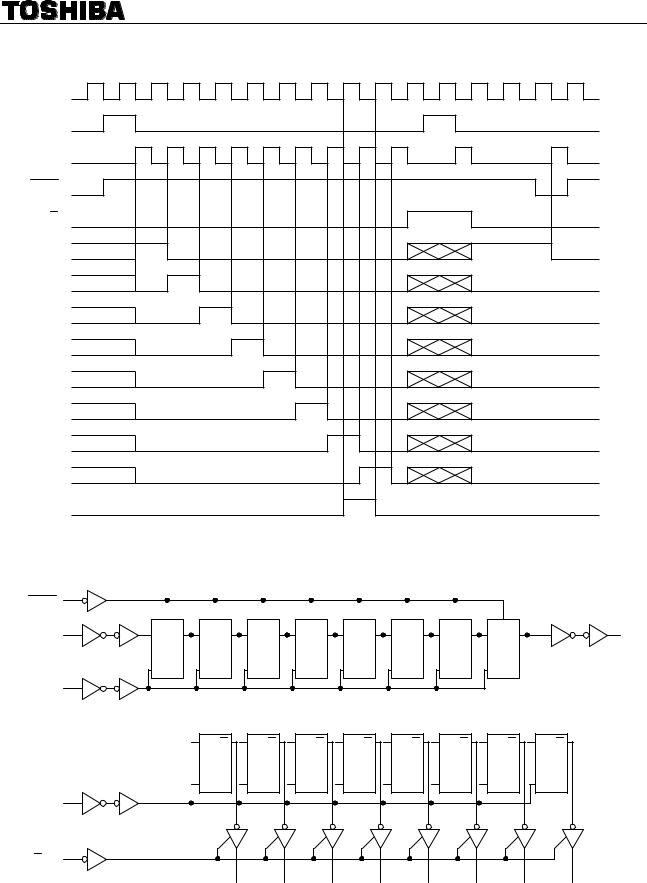

Timing Chart

SCK

SI

RCK

SCLR

G

QA

QB

QC

QD

QE

QF

QG

QH

QH’

System Diagram

10

SCLR |

|

|

|

|

|

|

|

|

|

14 |

R |

R |

R |

R |

DR |

R |

R |

R |

QH’ |

SI |

D Q |

D Q |

D Q |

D Q |

D Q |

D Q |

D Q |

D Q |

9 |

|

|

|

|

|

|

|

|

|

|

11 |

SCK |

SCK |

SCK |

SCK |

SCK |

SCK |

SCK |

SCK |

|

|

|

|

|

|

|

|

|

|

|

SCK |

|

|

|

|

|

|

|

|

|

D Q |

D Q |

D Q |

D Q |

D Q |

D Q |

D Q |

D Q |

RCK |

RCK |

RCK |

RCK |

RCK |

RCK |

RCK |

RCK |

12 |

|

|

|

|

|

|

|

RCK |

|

|

|

|

|

|

|

13 |

|

|

|

|

|

|

|

G |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

15 |

|||||||

QA |

QB |

QC |

QD |

QE |

QF |

QG |

QH |

3 |

2007-10-01 |

|

|

|

TC74VHC595F/FN/FT/FK |

Absolute Maximum Ratings (Note) |

|

|

|

Characteristics |

Symbol |

Rating |

Unit |

Supply voltage range |

VCC |

−0.5 to 7.0 |

V |

DC input voltage |

VIN |

−0.5 to 7.0 |

V |

DC output voltage |

VOUT |

−0.5 to VCC + 0.5 |

V |

Input diode current |

IIK |

−20 |

mA |

Output diode current |

IOK |

±20 |

mA |

DC output current |

IOUT |

±25 |

mA |

DC VCC/ground current |

ICC |

±75 |

mA |

Power dissipation |

PD |

180 |

mW |

Storage temperature |

Tstg |

−65 to 150 |

°C |

Note: |

Exceeding any of the absolute maximum ratings, even briefly, lead to deterioration in IC performance or |

|

even destruction. |

|

Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the |

|

significant change in temperature, etc.) may cause this product to decrease in the reliability significantly |

|

even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute |

|

maximum ratings and the operating ranges. |

|

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook |

|

(“Handling Precautions”/“Derating Concept and Methods”) and individual reliability data (i.e. reliability test |

|

report and estimated failure rate, etc). |

Operating Ranges (Note)

|

Characteristics |

Symbol |

Rating |

Unit |

|

|

|

|

|

||

Supply voltage |

VCC |

2.0 to 5.5 |

V |

||

Input voltage |

VIN |

0 to 5.5 |

V |

||

Output voltage |

VOUT |

0 to VCC |

V |

||

Operating temperature |

Topr |

−40 to 85 |

°C |

||

Input rise and fall time |

dt/dv |

0 to 100 (VCC = 3.3 ± 0.3 V) |

ns/V |

||

0 to 20 (VCC = 5 ± 0.5 V) |

|||||

|

|

|

|

||

Note: |

The operating ranges must be maintained to ensure the normal operation of the device. |

||||

|

Unused inputs must be tied to either VCC or GND. |

|

|||

4 |

2007-10-01 |

Loading...

Loading...