TOSHIBA TC55V8512J-12, TC55V8512FT-12, TC55V8512J-15, TC55V8512FT-15 Technical data

TC55V8512FT-12

TC55V8512J/FT-12,-15

TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

524,288-WORD BY 8-BIT CMOS STATIC RAM

DESCRIPTION

The TC55V8512J/FT is a 4,194,304-bit high-speed static random access memory (SRAM) organized as 524,288 words by 8 bits. Fabricated using CMOS technology and advanced circuit techniques to provide high speed, it operates from a single 3.3 V power supply. Chip enable (CE ) can be used to place the device in a low-power mode, and output enable ( OE ) provides fast memory access. This device is well suited to cache memory applications where high-speed access and high-speed storage are required. All inputs and outputs are directly LVTTL compatible. The TC55V8512J/FT is available in plastic 36-pin SOJ and 44-pin TSOP with 400mil width for high density surface assembly.

FEATURES

• Fast access time (the following are maximum values) |

• |

Single power supply voltage of 3.3 V ± 0.3 V |

|||||||||

|

TC55V8512J/FT-12:12 ns |

|

|

|

|

• |

Fully static operation |

|

|||

|

TC55V8512J/FT-15:15 ns |

|

|

|

|

• All inputs and outputs are LVTTL compatible |

|||||

• Low-power dissipation |

|

|

|

|

|

|

• |

Output buffer control using |

OE |

||

(the following are maximum values) |

|

|

• |

Package: |

|

||||||

|

|

|

|

|

|

|

|

|

|

SOJ36-P-400-1.27 (J) |

(Weight: 1.35 g typ) |

|

Cycle Time |

12 |

15 |

|

20 |

25 |

ns |

|

|

||

|

|

|

|

TSOP II44-P-400-0.80 (FT) |

(Weight: 0.45 g typ) |

||||||

|

|

|

|

|

|

|

|

|

|

||

|

Operation (max) |

170 |

140 |

|

130 |

110 |

mA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Standby:4 mA |

(both |

devices) |

|

|

|

|

|

|

||

PIN ASSIGNMENT (TOP VIEW) |

|

|

PIN NAMES |

||||||||||

36 PIN SOJ |

|

|

44 PIN TSOP |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

|

|

|

|

A0 to A18 |

Address Inputs |

|||

|

|

|

|

1 |

44 |

NC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

NC |

2 |

43 |

NC |

|

I/O1 to I/O8 |

Data Inputs/Outputs |

|||

|

|

|

|

A17 |

3 |

42 |

NC |

|

|

|

|

|

|

|

|

|

|

A3 |

4 |

41 |

A4 |

|

|

|

|

|

Chip Enable Input |

A17 |

1 |

36 |

|

|

|

CE |

|||||||

NC |

A2 |

5 |

40 |

A5 |

|

|

|||||||

|

|

|

|

|

|

||||||||

A3 |

2 |

35 |

A4 |

A1 |

6 |

39 |

A6 |

|

|

|

|

|

|

|

|

WE |

Write Enable Input |

||||||||||

A2 |

3 |

34 |

A5 |

A0 |

7 |

38 |

A7 |

|

|

||||

A1 |

4 |

33 |

A6 |

CE |

8 |

37 |

OE |

|

|

|

|

|

Output Enable Input |

A0 |

5 |

32 |

A7 |

I/O1 |

9 |

36 |

I/O8 |

|

|

OE |

|||

CE |

6 |

31 |

OE |

I/O2 |

10 |

35 |

I/O7 |

|

|

|

|

|

|

|

|

|

|

|

Power (+3.3 V) |

||||||||

I/O1 |

7 |

30 |

I/O8 |

VDD |

11 |

34 |

GND |

|

VDD |

||||

I/O2 |

8 |

29 |

I/O7 |

GND |

12 |

33 |

VDD |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

VDD |

9 |

28 |

GND |

I/O3 |

13 |

32 |

I/O6 |

|

GND |

Ground |

|||

GND |

10 |

27 |

VDD |

I/O4 |

14 |

31 |

I/O5 |

|

|||||

|

|

|

|

|

|

||||||||

I/O3 |

11 |

26 |

I/O6 |

WE |

15 |

30 |

A8 |

|

|

NC |

No Connection |

||

I/O4 |

12 |

25 |

I/O5 |

A16 |

16 |

29 |

A9 |

|

|

||||

|

|

|

|

|

|

||||||||

WE |

13 |

24 |

A8 |

A15 |

17 |

28 |

A10 |

|

|

NU |

Not Usable (Input) |

||

A16 |

14 |

23 |

A9 |

A14 |

18 |

27 |

A11 |

|

|

||||

A15 |

15 |

22 |

A10 |

A13 |

19 |

26 |

A12 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

A14 |

16 |

21 |

A11 |

A18 |

20 |

25 |

NU |

|

|

|

|

|

|

A13 |

17 |

20 |

A12 |

NC |

21 |

24 |

NC |

|

|

|

|

|

|

A18 |

18 |

19 |

NU |

NC |

22 |

23 |

NC |

|

|

|

|

|

|

|

(TC55V8512J) |

|

|

(TC55V8512FT) |

|

|

|

|

|

|

|

||

2001-12-19 1/10

TC55V8512J/FT-12,-15

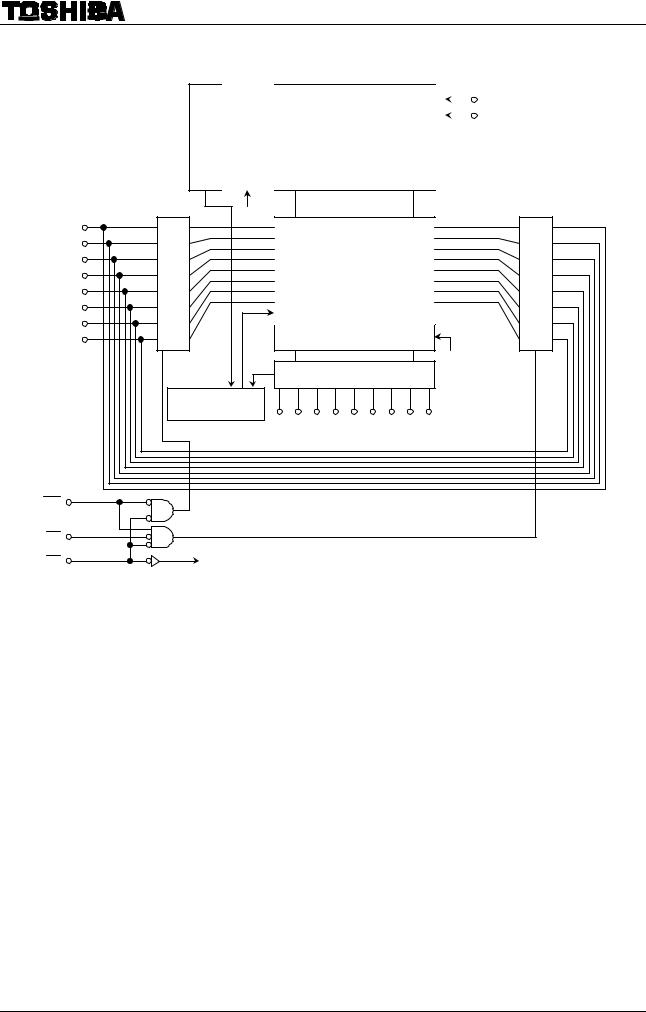

BLOCK DIAGRAM

A0

A1

A4

A8

A9

A12

A14

A15

A16

A17

ROW ADDRESS BUFFER |

|

ROW DECODER |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

VDD |

|

|

|

|

MEMORY CELL ARRAY |

|

|

GND |

|

|

||

|

|

|

|

512 × 1,024 × 8 |

|

|

|

(4,194,304) |

|

|

|

|

|

|

|

|

|

|

CE |

|

|

I/O1 |

|

|

|

|

|

I/O2 |

|

|

|

|

|

I/O3 |

|

|

SENSE AMP |

|

|

I/O4 |

|

|

|

||

DATAINPUT |

BUFFER |

DATAOUTPUT |

BUFFER |

||

I/O5 |

|||||

I/O5 |

|||||

I/O7 |

|||||

|

|

|

|

||

I/O8 |

|

|

COLUMN DECODER |

|

|

|

|

|

CE |

|

|

|

|

|

COLUMN ADDRESS BUFFER |

|

|

|

|

|

CLOCK |

|

|

|

|

|

GENERATOR |

|

|

|

|

|

A2 A3 A5 A6 A7 A10 A11A13 A18 |

|

|

WE |

|

|

|

|

|

OE |

|

|

|

|

|

CE |

|

|

CE |

|

MAXIMUM RATINGS

SYMBOL |

RATING |

VALUE |

UNIT |

|

|

|

|

VDD |

Power Supply Voltage |

−0.5 to 4.6 |

V |

VIN |

Input Terminal Voltage |

−0.5* to 4.6 |

V |

VI/O |

Input/Output Terminal Voltage |

−0.5* to VDD + 0.5** |

V |

PD |

Power Dissipation |

1.4 |

W |

Tsolder |

Soldering Temperature (10s) |

260 |

°C |

Tstg |

Storage Temperature |

−65 to 150 |

°C |

Topr |

Operating Temperature |

−10 to 85 |

°C |

*: −1.5 V with a pulse width of 20% tRC min (4 ns max)

**: VDD + 1.5 V with a pulse width of 20% tRC min (4 ns max)

DC RECOMMENDED OPERATING CONDITIONS (Ta = 0° to 70°C)

SYMBOL |

PARAMETER |

MIN |

TYP |

MAX |

UNIT |

|

|

|

|

|

|

VDD |

Power Supply Voltage |

3.0 |

3.3 |

3.6 |

V |

VIH |

Input High Voltage |

2.0 |

|

VDD + 0.3** |

V |

VIL |

Input Low Voltage |

−0.3* |

|

0.8 |

V |

*: −1.0 V with a pulse width of 20% tRC min (4 ns max)

**: VDD + 1.0 V with a pulse width of 20% tRC min (4 ns max)

2001-12-19 2/10

TC55V8512J/FT-12,-15

DC CHARACTERISTICS (Ta = 0° to 70°C, VDD = 3.3 V ± 0.3 V)

SYMBOL |

PARAMETER |

|

|

|

|

TEST CONDITION |

MIN |

TYP |

MAX |

UNIT |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IIL |

Input Leakage Current |

VIN = 0 to VDD |

|

|

|

−1 |

|

1 |

µA |

|||||

|

(Except NU pin) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Leakage |

|

|

|

= VIH or |

|

= VIL or |

|

= VIH, |

|

|

|

|

|

ILO |

CE |

WE |

OE |

−1 |

|

1 |

µA |

|||||||

Current |

VOUT = 0 to VDD |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|||||||

II (NU) |

Input Current |

VIN = 0 to 0.8 V |

|

|

|

−1 |

|

20 |

µA |

|||||

(NU pin) |

VIN = 0 to 0.2 V |

|

|

|

−1 |

|

1 |

|||||||

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

VOH |

Output High Voltage |

IOH = −2 mA |

|

|

|

2.4 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

IOH = −100 µA |

|

|

|

VDD − 0.2 |

|

|

V |

|||||||

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOL |

Output Low Voltage |

IOL = 2 mA |

|

|

|

|

|

0.4 |

||||||

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

IOL = 100 µA |

|

|

|

|

|

0.2 |

|

|||||||

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tcycle = 12 ns |

|

|

170 |

|

|

|

|

|

|

= VIL, IOUT = 0 mA, |

|

|

|

|

|

|

|

||

IDDO |

Operating Current |

CE |

|

|

tcycle = 15 ns |

|

|

140 |

mA |

|||||

|

OE |

= VIH, |

|

|

|

|

|

|

||||||

|

|

tcycle = 20 ns |

|

|

130 |

|||||||||

|

|

Other Input = VIH/VIL |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

tcycle = 25 ns |

|

|

110 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||||

IDDS1 |

|

|

|

= VIH, Other Input = VIH or VIL |

|

|

50 |

|

||||||

Standby Current |

CE |

mA |

||||||||||||

IDDS2 |

|

|

= VDD − 0.2 V, Other Input = VDD − 0.2 V or 0.2 V |

|

|

4 |

||||||||

|

|

CE |

|

|||||||||||

CAPACITANCE (Ta = 25°C, f = 1 .0 MHz)

SYMBOL |

PARAMETER |

TEST CONDITION |

MAX |

UNIT |

|

|

|

|

|

CIN |

Input Capacitance |

VIN = GND |

6 |

pF |

CI/O |

Input/Output Capacitance |

VI/O = GND |

8 |

pF |

Note: This parameter is periodically sampled and is not 100% tested. |

|

|

||

OPERATING MODE

|

|

|

|

|

|

|

|

|

|

|

|

MODE |

CE |

OE |

|

WE |

I/O1 to I/O8 |

POWER |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

Read |

|

L |

|

L |

|

H |

Output |

IDDO |

|||

Write |

|

L |

* |

|

|

L |

Input |

IDDO |

|||

Outputs Disable |

|

L |

|

H |

|

H |

High Impedance |

IDDO |

|||

Standby |

|

H |

* |

|

* |

|

High Impedance |

IDDS |

|||

* : Don’t care |

|

|

|

|

|

|

|

|

|

|

|

Note: The NU pin must be left unconnected or tied to GND or a voltage level of less than 0.8 V.

You must not apply a voltage of more than 0.8 V to the NU.

2001-12-19 3/10

Loading...

Loading...