TOSHIBA TC74AC112P, TC74AC112F, TC74AC112FN Technical data

TC74AC112P/F/FN

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74AC112P,TC74AC112F,TC74AC112FN

Dual J-K Flip Flop with Preset and Clear

The TC74AC112 is an advanced high speed CMOS DUAL J-K FLIP FLOP fabricated with silicon gate and double-layer metal wiring C2MOS technology.

It achieves the high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

In accordance with the logic level given J and K input this device changes state on negative going transition of the clock pulse. CLEAR and PRESET are independent of the clock and accomplished by a low logic level on the corresponding input.

All inputs are equipped with protection circuits against static discharge or transient excess voltage.

Features

•High speed: fmax = 170 MHz (typ.) at VCC = 5 V

•Low power dissipation: ICC = 4 μA (max) at Ta = 25°C

•High noise immunity: VNIH = VNIL = 28% VCC (min)

•Symmetrical output impedance: |IOH| = IOL = 24 mA (min)

Capability of driving 50 Ω transmission lines.

•Balanced propagation delays: tpLH − tpHL

•Wide operating voltage range: VCC (opr) = 2 to 5.5 V

•Pin and function compatible with 74F112

Pin Assignment

Note: xxxFN (JEDEC SOP) is not available in Japan.

TC74AC112P

TC74AC112F

TC74AC112FN

Weight |

|

DIP16-P-300-2.54A |

: 1.00 g (typ.) |

SOP16-P-300-1.27A |

: 0.18 g (typ.) |

SOL16-P-150-1.27 |

: 0.13 g (typ.) |

1 |

2007-10-01 |

TC74AC112P/F/FN

IEC Logic Symbol

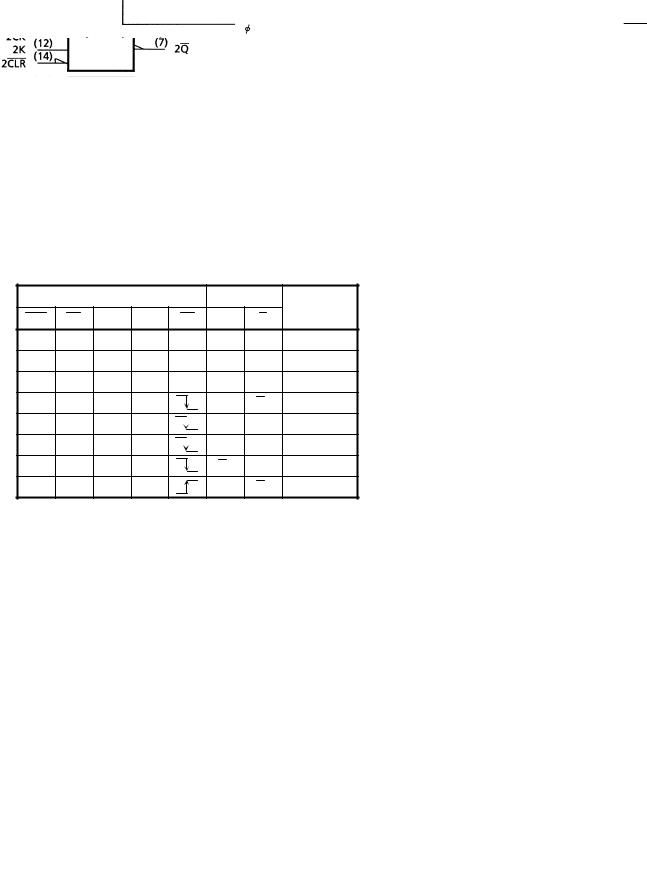

Truth Table

|

|

Inputs |

|

|

Outputs |

Function |

||

CLR |

PR |

J |

K |

CK |

Q |

Q |

||

|

||||||||

L |

H |

X |

X |

X |

L |

H |

Clear |

|

H |

L |

X |

X |

X |

H |

L |

Preset |

|

L |

L |

X |

X |

X |

H |

H |

|

|

H |

H |

L |

L |

|

Qn |

Qn |

No Change |

|

H |

H |

L |

H |

|

L |

H |

|

|

H |

H |

H |

L |

|

H |

L |

|

|

H |

H |

H |

H |

|

Qn |

Qn |

Toggle |

|

H |

H |

X |

X |

|

Qn |

Qn |

No Change |

|

X: Don’t care

System Diagram

2 |

2007-10-01 |

TC74AC112P/F/FN

Absolute Maximum Ratings (Note 1)

Characteristics |

Symbol |

Rating |

Unit |

|

|

|

|

Supply voltage range |

VCC |

−0.5 to 7.0 |

V |

DC input voltage |

VIN |

−0.5 to VCC + 0.5 |

V |

DC output voltage |

VOUT |

−0.5 to VCC + 0.5 |

V |

Input diode current |

IIK |

±20 |

mA |

Output diode current |

IOK |

±50 |

mA |

DC output current |

IOUT |

±50 |

mA |

DC VCC/ground current |

ICC |

±100 |

mA |

Power dissipation |

PD |

500 (DIP) (Note 2)/180 (SOP) |

mW |

Storage temperature |

Tstg |

−65 to 150 |

°C |

Note 1: Exceeding any of the absolute maximum ratings, even briefly, lead to deterioration in IC performance or even destruction.

Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings and the operating ranges.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook (“Handling Precautions”/Derating Concept and Methods) and individual reliability data (i.e. reliability test report and estimated failure rate, etc).

Note 2: 500 mW in the range of Ta = −40 to 65°C. From Ta = 65 to 85°C a derating factor of −10 mW/°C should be applied up to 300 mW.

Operating Ranges (Note)

|

Characteristics |

Symbol |

Rating |

Unit |

|

|

|

|

|

|

|

Supply voltage |

VCC |

2.0 to 5.5 |

V |

|

|

Input voltage |

VIN |

0 to VCC |

V |

|

|

Output voltage |

VOUT |

0 to VCC |

V |

|

|

Operating temperature |

Topr |

−40 to 85 |

°C |

|

|

Input rise and fall time |

dt/dV |

0 to 100 (VCC = 3.3 ± 0.3 V) |

ns/V |

|

|

0 to 20 (VCC = 5 ± 0.5 V) |

|

||||

|

|

|

|

|

|

Note: |

The operating ranges must be maintained to ensure the normal operation of the device. |

||||

|

Unused inputs must be tied to either VCC or GND. |

|

|

||

3 |

2007-10-01 |

Loading...

Loading...