ROHM BR24E16FV, BR24E16FJ, BR24E16F, BR24E16, BR24E08F Datasheet

...

BR24C08 / BR24C08F / BR24C08FJ / BR24C08FV / BR24C16/ BR24C16F / Memory Ics BR24C16FJ / BR24C16FV / BR24E16 / BR24E16F / BR24E16FJ / BR24E16FV

I2C BUS compatible serial EEPROM

BR24C08 / BR24C08F / BR24C08FJ / BR24C08FV / BR24C16 / BR24C16F / BR24C16FJ / BR24C16FV / BR24E16 / BR24E16F / BR24E16FJ / BR24E16FV /

The BR24C08, BR24C16 and BR24E16 series are 2-wire (I2C BUS type) serial EEPROMs which are electrically programmable.

I2C BUS is a registered trademark of Philips.

zFeatures

1)1k x 8 bits serial EEPROM. (BR24C08 / F / FJ / FV) 2k x 8 bits serial EEPROM.

(BR24C16 / F / FJ / FV, BR24E16 / F / FJ / FV)

2)Two wire serial interface.

(2Byte Address : BR24E16)

3)Operating voltage range : 2.7V 5.5V

4)Low current consumption

Active (at 5V) : 2.0mA (Typ.)

Standby (at 5V) : 1.0 A (Typ.)

5) Auto erase and auto complete functions can be used during write operations.

zAbsolute maximum ratings (Ta=25° C)

6)Page write function : 16byte

7)DATA security

Write protect feature

Inhibit to WRITE at low Vcc

8)Noise filters at SCL and SDA pins.

9)Address can be incremented automatically during read operations.

10)Compact packages.

11)Rewriting possible up to 100,000 times.

12)Data can be stored for ten years without corruption.

|

Parameter |

Symbol |

Limits |

|

Unit |

|

|

|

|

|

|

Supply voltage |

VCC |

− 0.3~+ 6.5 |

|

V |

|

|

|

|

|

|

|

|

|

|

300(SSOP− B8) |

1 |

|

|

|

|

|

|

|

Power dissipation |

Pd |

450(SOP8, SOP− J8) |

2 |

mW |

|

|

|

|

|

|

|

|

|

|

800(DIP8) |

3 |

|

|

|

|

|

|

|

Storage temperature range |

Tstg |

− 65~+ 125 |

|

° C |

|

|

|

|

|

|

|

Operating temperature range |

Topr |

− 40~+ 85 |

|

° C |

|

|

|

|

|

|

|

Terminal voltage |

− |

− 0.3~VCC+ 0.3 |

|

V |

|

|

|

|

|

|

|

1 |

Reduced by 3.0mW for each increase in Ta of 1° C over 25° C. |

|

|

||

2 |

Reduced by 3.5mW for each increase in Ta of 1° C over 25° C. |

|

|

||

3 |

Reduced by 5.0mW for each increase in Ta of 1° C over 25° C. |

|

|

||

zRecommended operating conditions (Ta=25° C)

|

Parameter |

Symbol |

Limits |

Unit |

|

|

|

|

|

|

|

|

|

|

Power supply voltage |

VCC |

2.7~5.5 |

V |

||

|

|

|

|

|

|

|

|

Input voltage |

VIN |

0~VCC |

V |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BR24C08 / BR24C08F / BR24C08FJ / BR24C08FV / BR24C16/ BR24C16F / Memory Ics BR24C16FJ / BR24C16FV / BR24E16 / BR24E16F / BR24E16FJ / BR24E16FV

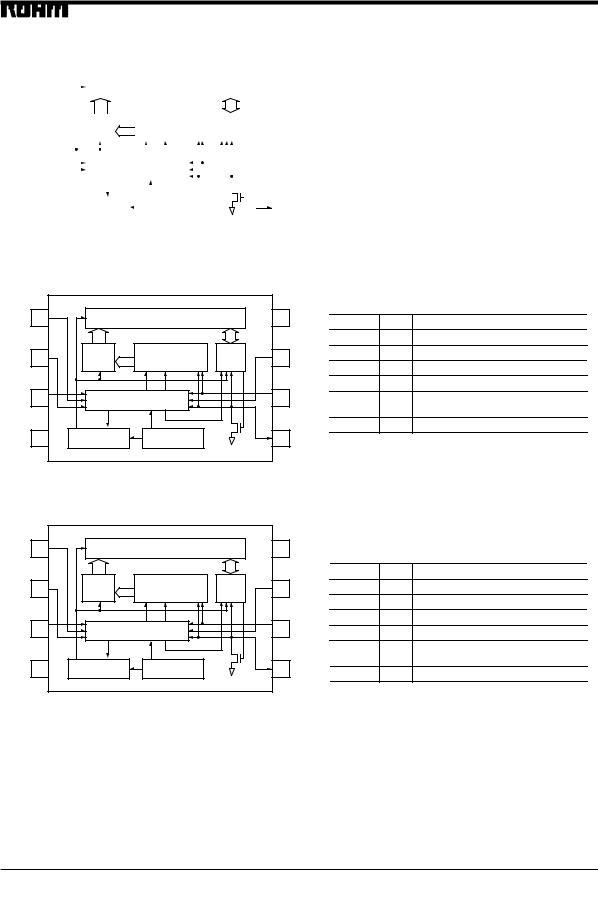

zBlock diagram

BR24C08 / F / FJ / FV

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

A0 |

|

1 |

|

|

|

|

|

|

|

8kbits EEPROM ARRAY |

|

|

|

|

|

|

8 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

10bits |

|

|

|

|

|

|

|

|

8bits |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

A1 |

|

|

|

|

|

|

ADDRESS |

|

|

|

|

SLAVE·WORD |

|

|

DATA |

|

|

|

|

|

|||||||||

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

7 |

WP |

||||||||||||||

|

|

|

|

|

DECODER |

10bits |

ADDRESS REGISTER |

|

REGISTER |

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

START |

|

|

STOP |

|

|

|

|

|

|

|

|

|

|

|

|

||||

A2 |

|

3 |

|

|

|

|

|

|

CONTROL LOGIC |

|

|

|

|

|

|

|

|

|

|

6 |

SCL |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ACK |

|

|

|

|

|

|

|

|

SDA |

||

GND |

4 |

|

HIGH VOLTAGE GEN. |

|

|

|

VCC LEVEL DETECT |

|

|

|

|

|

|

|

|

5 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin name |

I / O |

Function |

|

|

|

|

|

|

|

VCC |

− |

Power supply |

|

|

GND |

− |

Ground (0V) |

|

|

|

|

|

|

|

A0, A1 |

− |

Out of use. Please connect to GND. |

|

|

|

|

|

|

|

A2 |

I |

Slave address set |

|

|

|

|

|

|

|

SCL |

I |

Serial clock input |

|

|

|

|

|

|

|

SDA |

I / O |

Slave and word address, |

|

|

serial data input, serial data output |

||||

|

|

|

||

|

|

|

|

|

WP |

I |

Wite protect pin |

|

|

|

|

|

|

An open drain output requires a pull-up resistor.

BR24C16 / F / FJ / FV |

|

|

|

|

|

|

|

|

|

||

A0 |

1 |

|

16kbits EEPROM ARRAY |

|

8 |

VCC |

Pin name |

I / O |

Function |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

11bits |

|

|

8bits |

|

|

VCC |

− |

Power supply |

|

|

|

|

|

|

|

|

|

|

|||

A1 |

2 |

ADDRESS |

|

SLAVE·WORD |

DATA |

7 |

WP |

GND |

− |

Ground (0V) |

|

DECODER |

11bits ADDRESS REGISTER |

REGISTER |

|

|

|

|

|||||

|

|

|

|

A0, A1, A2 |

I |

Out of use. Please connect to GND. |

|

||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

START |

STOP |

|

|

|

SCL |

I |

Serial clock input |

|

A2 |

3 |

CONTROL LOGIC |

|

6 |

SCL |

SDA |

I / O |

Slave and word address, |

|

||

|

|

|

|

|

|

|

|

serial data input, serial data output |

|||

|

|

|

|

ACK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WP |

I |

Wite protect pin |

|

GND |

4 |

HIGH VOLTAGE GEN. |

VCC LEVEL DETECT |

|

5 |

SDA |

An open drain output requires a pull-up resistor. |

|

|||

BR24E16 / F / FJ / FV |

|

|

|

|

|

|

|

|

|

||

A0 |

1 |

|

16kbits EEPROM ARRAY |

|

8 |

VCC |

|

|

|

|

|

|

|

11bits |

|

|

8bits |

|

|

Pin name |

I / O |

Function |

|

|

|

|

|

|

|

|

|

|

|||

A1 |

2 |

ADDRESS |

|

SLAVE·WORD |

DATA |

7 |

WP |

VCC |

− |

Power supply |

|

DECODER |

11bits ADDRESS REGISTER |

REGISTER |

|

||||||||

|

|

|

|

|

− |

|

|

||||

|

|

|

|

|

|

|

|

GND |

Ground (0V) |

|

|

|

|

|

START |

STOP |

|

|

|

A0, A1, A2 |

I |

Slave address set |

|

A2 |

3 |

CONTROL LOGIC |

|

6 |

SCL |

SCL |

I |

Serial clock input |

|

||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

ACK |

|

|

|

SDA |

I / O |

Slave and word address, |

|

|

|

|

|

|

|

|

|

serial data input, serial data output |

|||

|

|

|

|

|

|

|

|

|

|

|

|

GND |

4 |

HIGH VOLTAGE GEN. |

VCC LEVEL DETECT |

|

5 |

SDA |

WP |

I |

Wite protect pin |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

An open drain output requires a pull-up resistor. |

|

||

BR24C08 / BR24C08F / BR24C08FJ / BR24C08FV / BR24C16/ BR24C16F / Memory Ics BR24C16FJ / BR24C16FV / BR24E16 / BR24E16F / BR24E16FJ / BR24E16FV

zElectrical characteristics

DC characteristics (Unless otherwise noted, Ta=− 40 85° C, VCC=2.7 5.5V)

Parameter |

Symbol |

Min. |

Typ. |

Max. |

Unit |

Conditions |

|

|

|

|

|

|

|

|

|

"HIGH" input voltage |

VIH |

0.7VCC |

− |

− |

V |

− |

|

|

|

|

|

|

|

|

|

"LOW" input voltage |

VIL |

− |

|

− |

0.3VCC |

V |

− |

|

|

|

|

|

|

|

|

"LOW" output voltage |

VOL |

− |

|

− |

0.4 |

V |

IOL= 3.0mA(SDA) |

|

|

|

|

|

|

|

|

Input leakage current |

ILI |

− |

1 |

− |

1 |

µ A |

VIN= 0V~VCC |

|

|

|

|

|

|

|

|

Output leakage current |

ILO |

− |

1 |

− |

1 |

µ A |

VOUT= 0V~VCC |

|

|

|

|

|

|

|

|

operating current |

ICC |

− |

|

− |

3.0 |

mA |

VCC= 5.5V, fSCL= 400kHz |

|

|

|

|

|

|

|

|

Standby current |

ISB |

− |

|

− |

3.0 |

µ A |

VCC= 5.5V, SDA SCL= VCC |

|

A0, A1, A2= GND, WP= GND |

||||||

|

|

|

|

|

|

|

|

This product is not designed for protection against radioactive rays.

This product is not designed for protection against radioactive rays.

Operating timing characteristics (Unless otherwise noted, Ta=− 40 85° C, VCC=2.7 5.5V)

Parameter |

Symbol |

Vcc= 5V± 10% |

Vcc= 3V± |

10% |

Unit |

|||||

Min. |

Typ. |

Max. |

Min. |

Typ. |

Max. |

|||||

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

SCL frequency |

fSCL |

− |

− |

400 |

− |

− |

|

100 |

kHz |

|

|

|

|

|

|

|

|

|

|

|

|

Dataclock "HIGH" time |

tHIGH |

0.6 |

− |

− |

4.0 |

− |

|

− |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

Dataclock "LOW" time |

tLOW |

1.2 |

− |

− |

4.7 |

− |

|

− |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

SDA / SCL rise time |

tR |

− |

− |

0.3 |

− |

− |

|

1.0 |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

SDA / SCL fall time |

tF |

− |

− |

0.3 |

− |

− |

|

0.3 |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

Start condition hold time |

tHD : STA |

0.6 |

− |

− |

4.0 |

− |

|

− |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

Start condition setup time |

tSU : STA |

0.6 |

− |

− |

4.7 |

− |

|

− |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

Input data hold time |

tHD : DAT |

0 |

− |

− |

0 |

− |

|

− |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

Input data setup time |

tSU : DAT |

100 |

− |

− |

250 |

− |

|

− |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

Output data delay time |

tPD |

0.1 |

− |

0.9 |

0.2 |

− |

|

3.5 |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

Output data hold time |

tDH |

0.1 |

− |

− |

0.2 |

− |

|

− |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

Stop condition setup time |

tSU : STO |

0.6 |

− |

− |

4.7 |

− |

|

− |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

Bus open time before start or transfer |

tBUF |

1.2 |

− |

− |

4.7 |

− |

|

− |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

Internal write cycle time |

tWR |

− |

− |

10 |

− |

− |

|

10 |

ms |

|

|

|

|

|

|

|

|

|

|

|

|

Noise erase valid time (SDA/SCL pins) |

tI |

− |

− |

0.05 |

− |

− |

|

0.1 |

µ s |

|

|

|

|

|

|

|

|

|

|

|

|

BR24C08 / BR24C08F / BR24C08FJ / BR24C08FV / BR24C16/ BR24C16F / Memory Ics BR24C16FJ / BR24C16FV / BR24E16 / BR24E16F / BR24E16FJ / BR24E16FV

zTiming charts

|

tR |

tF |

tHIGH |

SCL |

|

|

|

tHD : STA |

tSU : DAT |

tLOW |

tHD : DAT |

SDA |

|

|

|

(IN) |

|

|

|

tBUF |

|

tPD |

tDH |

|

|

||

SDA |

|

|

|

(OUT) |

|

|

|

SCL |

|

|

tSU : STA |

tHD : STA |

tSU : STO |

SDA |

|

|

|

START BIT |

STOP BIT |

Data is read on the rising edge of SCL.

Data is output in synchronization with the falling edge of SCL.

Fig.1 Synchronized data input / output timing

SCL |

|

|

|

SDA |

D0 |

ACK |

|

|

Write data (n) |

|

tWR |

|

|

STOP CONDITION |

START CONDITION |

Fig.2 Write cycle timing

zCircuit operation

(1)Start condition (recognition of start bit)

Before executing any command, when SCL is HIGH, a start condition (start bit) is required to cause SDA to fall from HIGH to LOW. This IC is designed to constantly detect whether there is a start condition (start bit) for the SDA and SCL line, and no commands will be executed unless this condition is satisfied.

(See Fig.1 for the synchronized data input / output timing.)

(2)Stop condition (recognition of stop bit)

To stop any command, a stop condition (stop bit) is required. A stop condition is achieved when SDA goes from LOW to HIGH while SCL is HIGH. This enables commands to be completed.

(See Fig.1 for the synchronized data input / output timing.)

(3)Precautions concerning write commands

In the WRITE mode, the transferred data is not written to the memory unless the stop bit is executed.

Loading...

Loading...