Page 1

Multi-Channel High

Speed Counter

(Catalog Number 1746-HSCE2)

User Manual

Page 2

Important User Information

Because of the variety of uses for the products described in this

publication, those responsible for the application and use of these

products must satisfy themselves that all necessary steps have been

taken to assure that each application and use meets all performance

and safety requirements, including any applicable laws, regulations,

codes and standards. In no event will Rockwell Automation be

responsible or liable for indirect or consequential damage resulting

from the use or application of these products.

Any illustrations, charts, sample programs, and layout examples

shown in this publication are intended solely for purposes of

example. Since there are many variables and requirements associated

with any particular installation, Rockwell Automation does not assume

responsibility or liability (to include intellectual property liability) for

actual use based upon the examples shown in this publication.

Allen-Bradley publication SGI-1.1, Safety Guidelines for the

Application, Installation and Maintenance of Solid-State Control

(available from your local Rockwell Automation office), describes

some important differences between solid-state equipment and

electromechanical devices that should be taken into consideration

when applying products such as those described in this publication.

Reproduction of the contents of this copyrighted publication, in whole

or part, without written permission of Rockwell Automation, is

prohibited.

Throughout this publication, notes may be used to make you aware of

safety considerations. The following annotations and their

accompanying statements help you to identify a potential hazard,

avoid a potential hazard, and recognize the consequences of a

potential hazard:

WARNING

Identifies information about practices or

circumstances that can cause an explosion in a

hazardous environment, which may lead to personal

injury or death, property damage, or economic loss.

!

ATTENTION

Identifies information about practices or

circumstances that can lead to personal injury or

death, property damage, or economic loss.

!

IMPORTANT

Identifies information that is critical for successful

application and understanding of the product.

Allen-Bradley and SLC are trademarks of Rockwell Automation.

Page 3

Module Overview

Table of Contents

Preface

Who Should Use This Manual . . . . . . . . . . . . . . . . . . . . . . P-1

Purpose of This Manual. . . . . . . . . . . . . . . . . . . . . . . . . . . P-1

Related Documentation . . . . . . . . . . . . . . . . . . . . . . . . P-2

Conventions Used In This Manual . . . . . . . . . . . . . . . . . . . P-3

Your Questions or Comments on the Manual . . . . . . . . . . . P-3

Chapter 1

Multi-Channel High-Speed Counter Module Overview . . . . 1-1

Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Operating Class. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Class 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Class 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Class 1 vs. Class 4 Comparison . . . . . . . . . . . . . . . . . . . 1-4

Hardware Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Jumpers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Module Operation

Chapter 2

Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Input Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Pulse/External Direction. . . . . . . . . . . . . . . . . . . . . . . . 2-2

Pulse/Internal Direction . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Up and Down Pulses . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

X1 Quadrature Encoder . . . . . . . . . . . . . . . . . . . . . . . . 2-4

X2 Quadrature Encoder . . . . . . . . . . . . . . . . . . . . . . . . 2-4

X4 Quadrature Encoder . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Input Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Gate/Preset Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

No Preset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Soft Preset Only. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Store/Continue. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Store/Hold/Resume . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Store/Preset/Hold/Resume . . . . . . . . . . . . . . . . . . . . . . 2-7

Store/Preset/Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Gate and Preset Limitations . . . . . . . . . . . . . . . . . . . . . 2-8

Gate and Preset Considerations . . . . . . . . . . . . . . . . . . 2-8

Summary of Available Counter Configurations . . . . . . . . . . 2-8

i Publication 1746-UM002B-EN-P - August 2004

Page 4

Table of Contents ii

Installation and Wiring

Counter Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Linear Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Ring Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Rate Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Output Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Range Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

Count Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

Rate Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Counter Input Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Class 1 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

Class 4 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

Input Word Bit Values . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

Output State Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

Counter Status Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

Chapter 3

Compliance to European Union Directives . . . . . . . . . . . . . 3-1

EMC Directive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Low Voltage Directive . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Prevent Electrostatic Discharge . . . . . . . . . . . . . . . . . . . . . 3-2

Setting the Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Installing the Module. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

Important Wiring Considerations . . . . . . . . . . . . . . . . . . . . 3-4

Considerations for Reducing Noise . . . . . . . . . . . . . . . . 3-5

Electronic Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Auto Reset Operation. . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Input and Output Connections . . . . . . . . . . . . . . . . . . . . . 3-7

Removing the Terminal Block . . . . . . . . . . . . . . . . . . . 3-7

Encoder Wiring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

Differential Encoder Wiring . . . . . . . . . . . . . . . . . . . . . 3-8

Single-Ended Encoder Wiring (Open Collector). . . . . . . 3-9

Single-Ended Wiring (Discrete Devices) . . . . . . . . . . . . 3-10

Configuration and Programming

Publication 1746-UM002B-EN-P - August 2004

Chapter 4

Selecting Operating Class . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Power-up Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Module Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Programming Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Data Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Page 5

Table of Contents iii

Module Setup Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Programming Block Identification Bit . . . . . . . . . . . . . . 4-6

TRMT: Transmit Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

DEBUG: Debug Mode Selection Bit . . . . . . . . . . . . . . . 4-6

INT: Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

RVF: Rate Value Format . . . . . . . . . . . . . . . . . . . . . . . . 4-7

PRA: Program Range Allocation . . . . . . . . . . . . . . . . . . 4-7

Op Mode: Operating Mode . . . . . . . . . . . . . . . . . . . . . 4-8

Range Allocation Values. . . . . . . . . . . . . . . . . . . . . . . . 4-8

Range Allocation Examples . . . . . . . . . . . . . . . . . . . . . 4-9

Counter Configuration Block . . . . . . . . . . . . . . . . . . . . . . . 4-10

Programming Block Identification Bit . . . . . . . . . . . . . . 4-11

TRMT: Transmit Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

DEBUG: Debug Mode Selection Bit . . . . . . . . . . . . . . . 4-11

PGMn: Program Counter Number Bits . . . . . . . . . . . . . 4-12

CType: Counter Type Bit . . . . . . . . . . . . . . . . . . . . . . . 4-12

Input Config: Input Configuration Bits . . . . . . . . . . . . . 4-12

G/P Mode: Gate/Preset Mode Bits . . . . . . . . . . . . . . . . 4-13

Minimum/Maximum Count Value Block. . . . . . . . . . . . . . . 4-13

Programming Block Identification Bit . . . . . . . . . . . . . . 4-14

TRMT: Transmit Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

DEBUG: Debug Mode Selection Bit . . . . . . . . . . . . . . . 4-14

AUTO PRESET: Automatic Preset Bit. . . . . . . . . . . . . . . 4-14

CNTR No.: Counter Number Bits . . . . . . . . . . . . . . . . . 4-15

Preset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

Minimum/Maximum Count Value Words . . . . . . . . . . . 4-15

Counter Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

Minimum/Maximum Rate Value Block . . . . . . . . . . . . . . . . 4-16

Programming Block Identification Bit . . . . . . . . . . . . . . 4-17

TRMT: Transmit Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

DEBUG: Debug Mode Selection Bit . . . . . . . . . . . . . . . 4-17

CNTR No.: Counter Number Bits . . . . . . . . . . . . . . . . . 4-18

Minimum/Maximum Rate Value Words . . . . . . . . . . . . . 4-18

Operating Class . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

Program Ranges Block . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19

Programming Block Identification Bit . . . . . . . . . . . . . . 4-20

TRMT: Transmit Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

DEBUG: Debug Mode Selection Bit . . . . . . . . . . . . . . . 4-20

CNTR No.: Counter Number Bits . . . . . . . . . . . . . . . . . 4-21

Rtype: Range Type. . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

Range No.: Range Number Bits. . . . . . . . . . . . . . . . . . . 4-21

Range Start Value, Range Stop Value . . . . . . . . . . . . . . 4-22

Output State: Output State Byte . . . . . . . . . . . . . . . . . . 4-22

Publication 1746-UM002B-EN-P - August 2004

Page 6

Table of Contents iv

Start Up, Operation,

Troubleshooting, and Debug Mode

Counter Control Block. . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-23

Transmit Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

Programming Block Identification Bit . . . . . . . . . . . . . . 4-24

Control Words . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

ENn: Enable Counter (n) Bit. . . . . . . . . . . . . . . . . . . . . 4-24

SPn: Soft Preset Only (n) Bit . . . . . . . . . . . . . . . . . . . . 4-25

IDn: Internal Direction (n) Bit . . . . . . . . . . . . . . . . . . . 4-25

C/R(n): Count or Rate Value Bit . . . . . . . . . . . . . . . . . . 4-26

P(n): Program Counter (n) Bit . . . . . . . . . . . . . . . . . . . 4-26

Output ON (OR) Mask . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

Output Enable Mask . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

Enable Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-27

Determining Actual Output State . . . . . . . . . . . . . . . . . 4-27

Programming Block Default Values . . . . . . . . . . . . . . . . . . 4-28

Class 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

Class 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-30

Chapter 5

Start Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Normal Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Module Diagnostic Errors . . . . . . . . . . . . . . . . . . . . . . . 5-2

Module Programming Errors. . . . . . . . . . . . . . . . . . . . . 5-3

Application Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Debug Mode Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Activating Debug Mode . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Application Examples

Publication 1746-UM002B-EN-P - August 2004

Chapter 6

Example 1 - Direct Addressing. . . . . . . . . . . . . . . . . . . . . . 6-2

Data Table for N10 File (hexidecimal). . . . . . . . . . . . . . 6-7

Data Table for N11 File (decimal). . . . . . . . . . . . . . . . . 6-7

Example 2 - Indirect Addressing . . . . . . . . . . . . . . . . . . . . 6-7

Data Table for N10 File (hexidecimal). . . . . . . . . . . . . . 6-10

Data Table for N11 File (decimal). . . . . . . . . . . . . . . . . 6-10

Example 3 - Block Transfers . . . . . . . . . . . . . . . . . . . . . . . 6-10

Data Table for N10 File (hexidecimal). . . . . . . . . . . . . . 6-14

Data Table for N11 File (decimal). . . . . . . . . . . . . . . . . 6-14

Example 4 - Using Soft Presets. . . . . . . . . . . . . . . . . . . . . . 6-14

Ladder File 9 - HSCE2 Initialization Routine . . . . . . . . . 6-17

Data Table for N10 File (hexidecimal). . . . . . . . . . . . . . 6-18

Data Table for N11 File (decimal). . . . . . . . . . . . . . . . . 6-18

Example 5 - Change Presets Dynamically . . . . . . . . . . . . . . 6-18

Data Table for N10 File (hexidecimal). . . . . . . . . . . . . . 6-22

Data Table for N11 File (decimal). . . . . . . . . . . . . . . . . 6-22

Page 7

Specifications

Connecting a Differential Encoder

Module Programming Quick

Reference

Table of Contents v

Example 6 - Retentive Counters . . . . . . . . . . . . . . . . . . . . . 6-23

Data Table for N10 File (hexidecimal). . . . . . . . . . . . . . 6-25

Data Table for N11 File (decimal). . . . . . . . . . . . . . . . . 6-25

Appendix A

General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Inputs A, B, and Z . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

Outputs (sourcing) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

On-State Current Derating . . . . . . . . . . . . . . . . . . . . . . A-3

Throughput and Timing . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

Appendix B

Appendix C

Frequently Asked Questions

Comparing 1746-HSCE2 to

1746-HSCE

Appendix D

Appendix E

Glossary

Index

Publication 1746-UM002B-EN-P - August 2004

Page 8

Table of Contents vi

Publication 1746-UM002B-EN-P - August 2004

Page 9

Summary of Changes

The information below summarizes the changes to this manual since

the last printing.

To help you find new information and updated information in this

release of the manual, we have included change bars as shown to the

right of this paragraph.

New Information

The table below lists sections that include new information.

For this new information See page(s)

Note on limitations of rate value calculation at input frequencies

below 60 Hz.

Clarified operation of Module Fault (MFLT) bit 2-17

Updated resistor information in single-ended wiring diagrams 3-9 and 3-10

Clarified programming cycle 4-2

Modifications to the COP instruction example for reading and writing

floating point data

Corrected bit identification in Output State Byte 4-22

Example showing how to activate debug mode 5-10

Corrected bit identification table for Program Ranges Block C-2

2-11

4-4

1 Publication 1746-UM002B-EN-P - August 2004

Page 10

2 Summary of Changes

Publication 1746-UM002B-EN-P - August 2004

Page 11

Preface

Read this preface to familiarize yourself with the rest of the manual.

This preface covers the following topics:

• who should use this manual

• how to use this manual

• related publications

• conventions used in this manual

• Rockwell Automation support

Who Should Use This Manual

Purpose of This Manual

Use this manual if you are responsible for designing, installing,

programming, or troubleshooting control systems that use

Allen-Bradley small logic controllers.

You should have a basic understanding of SLC 500™ products. You

should understand programmable controllers and be able to interpret

the ladder logic instructions required to control your application. If

you do not, contact your local Rockwell Automation representative for

information on available training courses before using this product.

As much as possible, we organized this manual to explain, in

a task-by-task manner, how to install, configure, program,

operate and troubleshoot an SLC 500-based system using the

1746-HSCE2 module.

1 Publication 1746-UM002B-EN-P - August 2004

Page 12

2 Preface

Related Documentation

The table below provides a listing of publications that contain

important information about SLC™ products.

For Read this document Document number

A reference manual containing status file data, instruction

set, and troubleshooting information

A description of how to install and use your Modular

SLC 500 programmable controller

An overview of the SLC 500™ family of products SLC 500 Systems Selection Guide 1747-SG001

In-depth information on grounding and wiring

Allen-Bradley programmable controllers

SLC 500™ Instruction Set Reference

Manual

SLC 500™ Modular Hardware Style

User Manual

Allen-Bradley Programmable Controller

Grounding and Wiring Guidelines

1747-RM001

1747-UM011

1770-4.1

A description of important differences between solid-state

programmable controller products and hard-wired

electromechanical devices

An article on wire sizes and types for grounding electrical

equipment

A glossary of industrial automation terms and

abbreviations

If you would like a manual, you can:

• view and download a free electronic version from the internet at

www.rockwellautomation.com/literature

• purchase a printed manual by contacting your local

Allen-Bradley distributor or Rockwell Automation sales office

Application Considerations for

Solid-State Controls

National Electrical Code Published by the National Fire

Allen-Bradley Industrial Automation

Glossary

SGI-1.1

Protection Association of Boston,

MA

AG-7.1

Publication 1746-UM002B-EN-P - August 2004

Page 13

Preface 3

Conventions Used In This Manual

Your Questions or Comments on the Manual

The following conventions are used throughout this manual:

• Bulleted lists (like this one) provide information, not procedural

steps.

• Numbered lists provide sequential steps or hierarchical

information.

• Italic type is used for emphasis.

• Text in this font indicates words or phrases you should type.

If you find a problem with this manual, please notify us. If you have

any suggestions for how this manual could be made more useful to

you, please contact us at the address below:

Rockwell Automation

Automation Control and Information Group

Technical Communication, Dept. A602V

P.O. Box 2086

Milwaukee, WI 53201-2086

Publication 1746-UM002B-EN-P - August 2004

Page 14

4 Preface

Publication 1746-UM002B-EN-P - August 2004

Page 15

Module Overview

This chapter contains the following:

• multi-channel high-speed counter module overview

• operating class

• hardware features

Chapter

1

Multi-Channel High-Speed Counter Module Overview

The 1746-HSCE2 is an intelligent counter module with its own

microprocessor and I/O that is capable of reacting to high-speed input

signals without the intervention of the SLC processor. The module is

compatible with the SLC 500 family and can be used in a remote

chassis with the SLC Remote I/O Adapter Module (1747-ASB).

Counters

The module is able to count in either direction. A maximum of four

pulse counters are available (or 2 quadrature counters). Each counter

can count to +/- 8,388,607 as a ring or linear counter. In addition to

providing a count value, the module provides a rate value up to

+/-1 MHz, dependent on the type of input. The rate value is the input

frequency (in Hertz) to the counter. When the count value is

increasing, the rate value is positive. When the count value is

decreasing, the rate value is negative.

Counters can also be preset to any value between the minimum and

maximum values. The conditions that preset the count value and

generate capture values are configured by the gate/preset modes. The

four counters can have different gate/preset modes.

1 Publication 1746-UM002B-EN-P - August 2004

Page 16

1-2 Module Overview

Inputs

The module features six high-speed differential inputs labeled ±A1,

±B1, ±Z1, ±A2, ±B2, and ±Z2. It supports quadrature encoders with

ABZ inputs and/or up to six discrete switches. In addition, x1, x2, and

x4 counting configurations are provided to fully use the capabilities of

high resolution quadrature encoders. The inputs can be wired for

single-ended or differential use. Inputs are opto-isolated from the

backplane.

Outputs

Eight outputs are available, four real (dc sourcing) and four virtual

bits. The virtual outputs are available to the processor only. The real

outputs are protected from overloads by a self-resetting fuse. The

outputs can be controlled by any or all of the counters and/or directly

controlled by the user’s program.

Up to 16 dynamically configurable ranges are available, using rates or

counts to control outputs. The ranges, programmed with range start

and range stop values, can overlap. If the count or rate is within more

than one range, the output patterns of those ranges are combined

(logically ORed) to determine the actual status of the output. When an

output is enabled by more than one counter and/or with the user

program, its output state is determined by logically ORing the

programmed setpoints of all those counters and the user program.

Operation

Module operation is controlled by user-programmed settings in the

following six module programming blocks.

• Module Setup Block

• Counter Configuration Block

• Minimum/Maximum Count Value Block

• Minimum/Maximum Rate Value Block

• Program Ranges Block

• Counter Control Block

Publication 1746-UM002B-EN-P - August 2004

Page 17

Module Overview 1-3

Most programming parameters, except those in the Module Setup and

Counter Configuration blocks, are dynamic and can be changed

without halting counter operation. The table below lists the static and

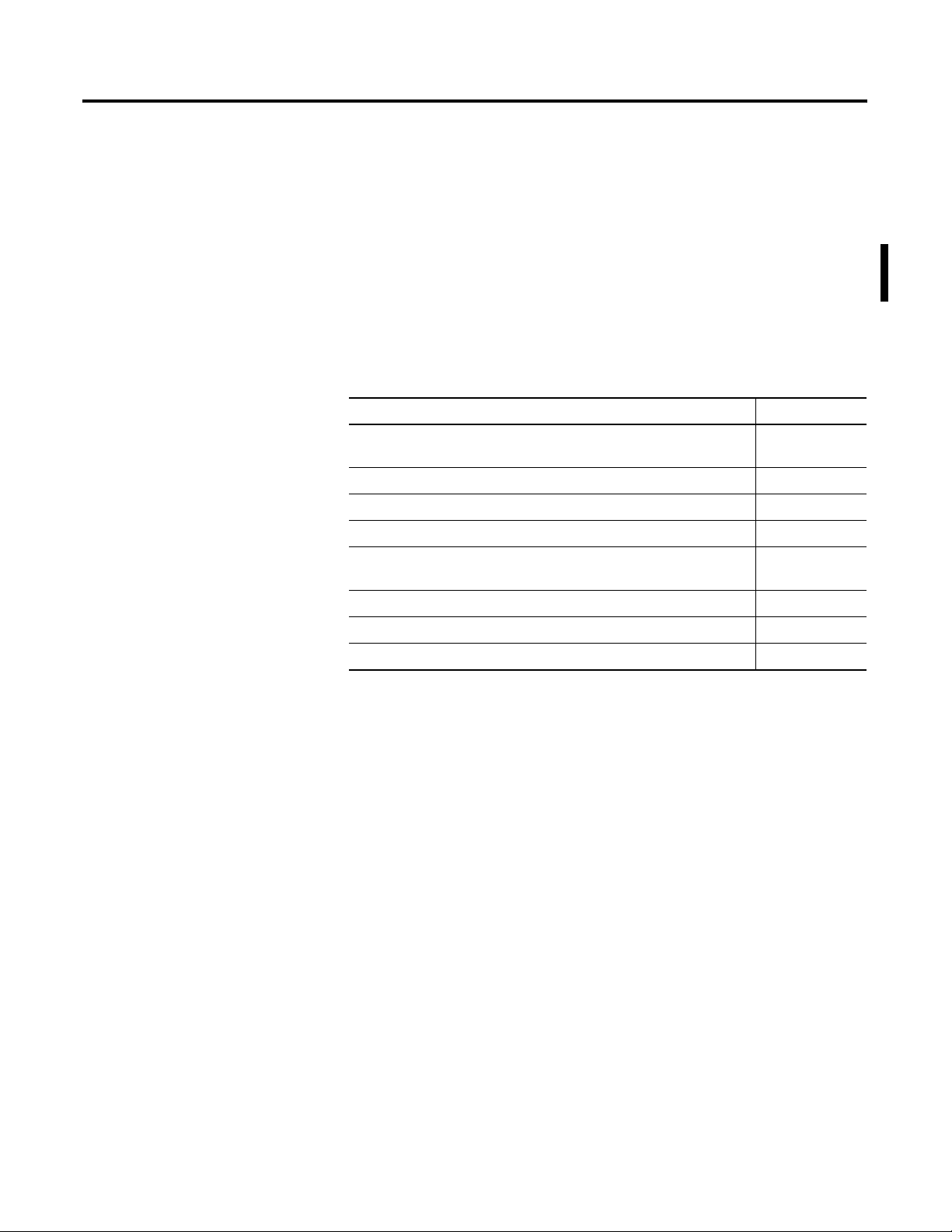

dynamic parameters by programming block.

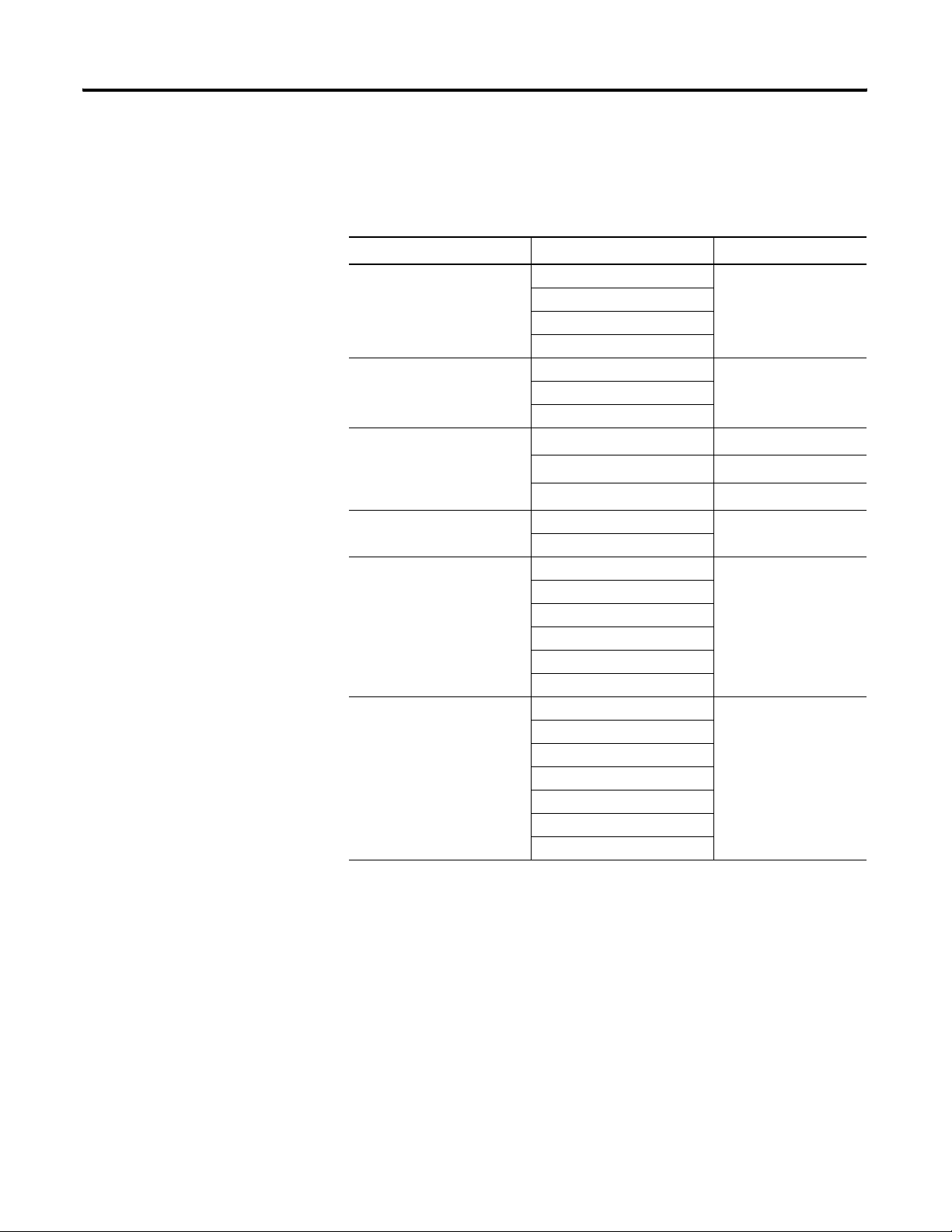

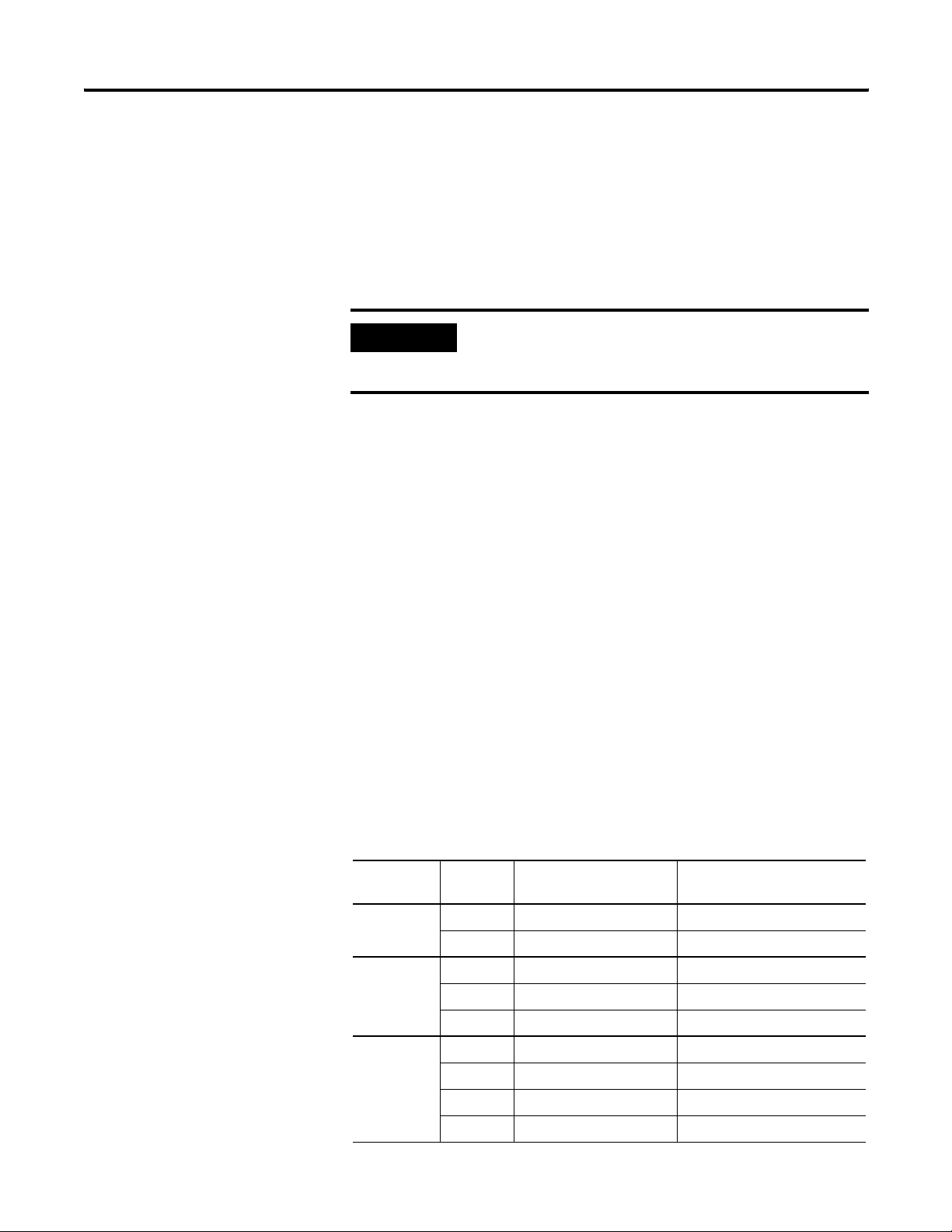

Programming Block Parameter

Ty pe

(1)

Operating Mode

Module Setup

Range Allocation

Interrupt Enable

Static

Rate Value Format

Counter Type

Counter Configuration

Input Configuration

Static

(2)

Gate/Preset Mode

Minimum Count

Min./Max. Count Value

Maximum Count

Preset Value

Min./Max. Rate Value Minimum Rate

Maximum Rate

(2)

Static

(2)

Static

Dynamic

Dynamic

Counter Number

Range Type

Program Range

Range Number

Start Value

Dynamic

Stop Value

Output Image

Enabled

Soft Preset Only

Internal Direction

Counter Control

Output ON Mask

Dynamic

Output OFF Mask

Count or Rate Value

Range Enable Mask

(1) STATIC = the associated counter must be disabled to set this parameter.

DYNAMIC = this parameter may be changed while the associated counter is running.

(2) Only the selected counter must be disabled.

(3) Under specific conditions, this parameter is dynamic. See page 4-15 for more information.

(3)

Publication 1746-UM002B-EN-P - August 2004

Page 18

1-4 Module Overview

Operating Class

Module operation differs slightly based on the operating class. The

operating class is selected via the module ID code.

Class 1

Class 1 operation is compatible with all SLC 500 processors. In Class 1

operation, the module uses 8 input and 8 output words and has an

associated ID code of 3511. A maximum of four 16-bit counters are

available in this operating class.

Class 4

Class 4 operation is compatible with SLC 5/03 and above systems. In

Class 4 operation, the module uses 23 input and 8 output words and

has an associated ID code of 15912. A maximum of four 24-bit

counters are available in this class.

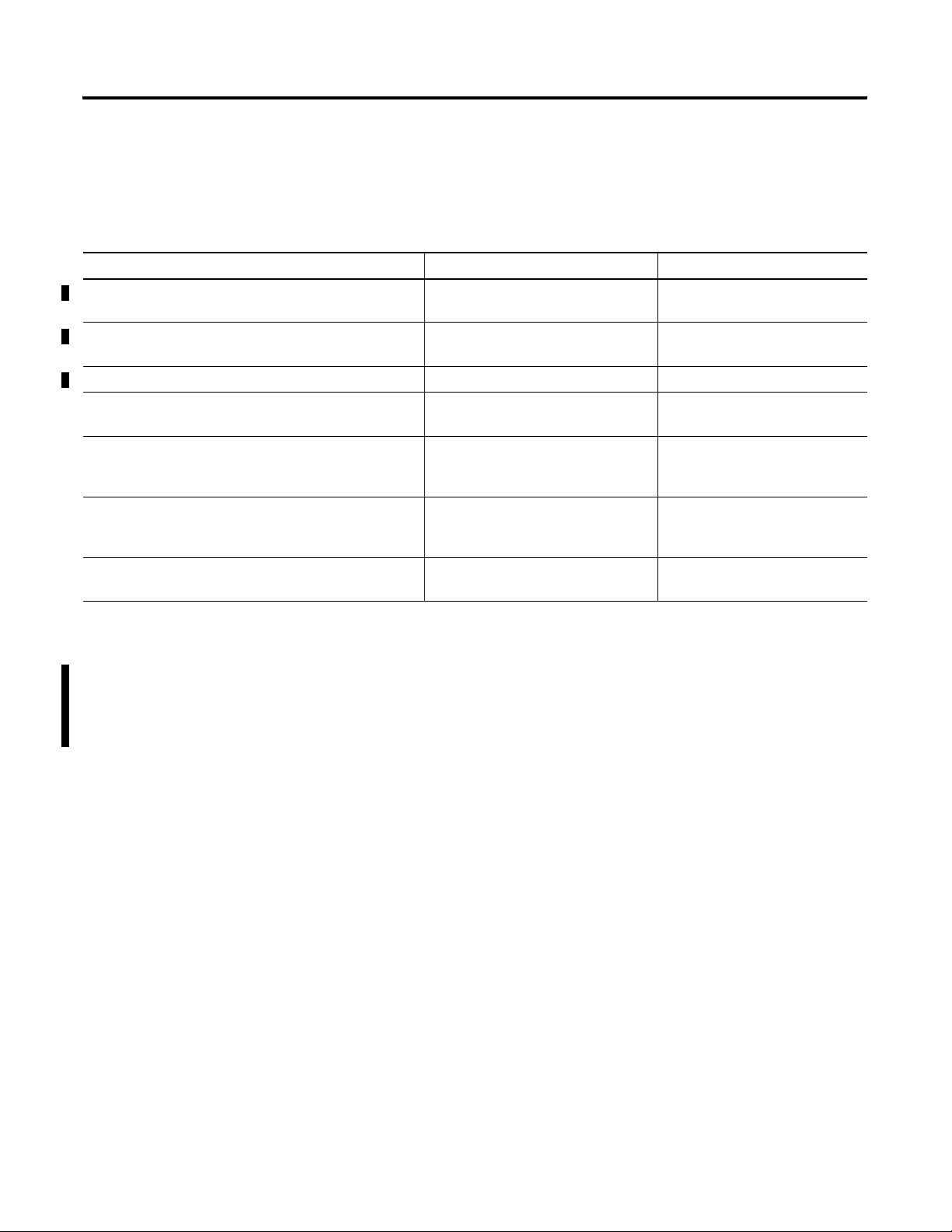

Class 1 vs. Class 4 Comparison

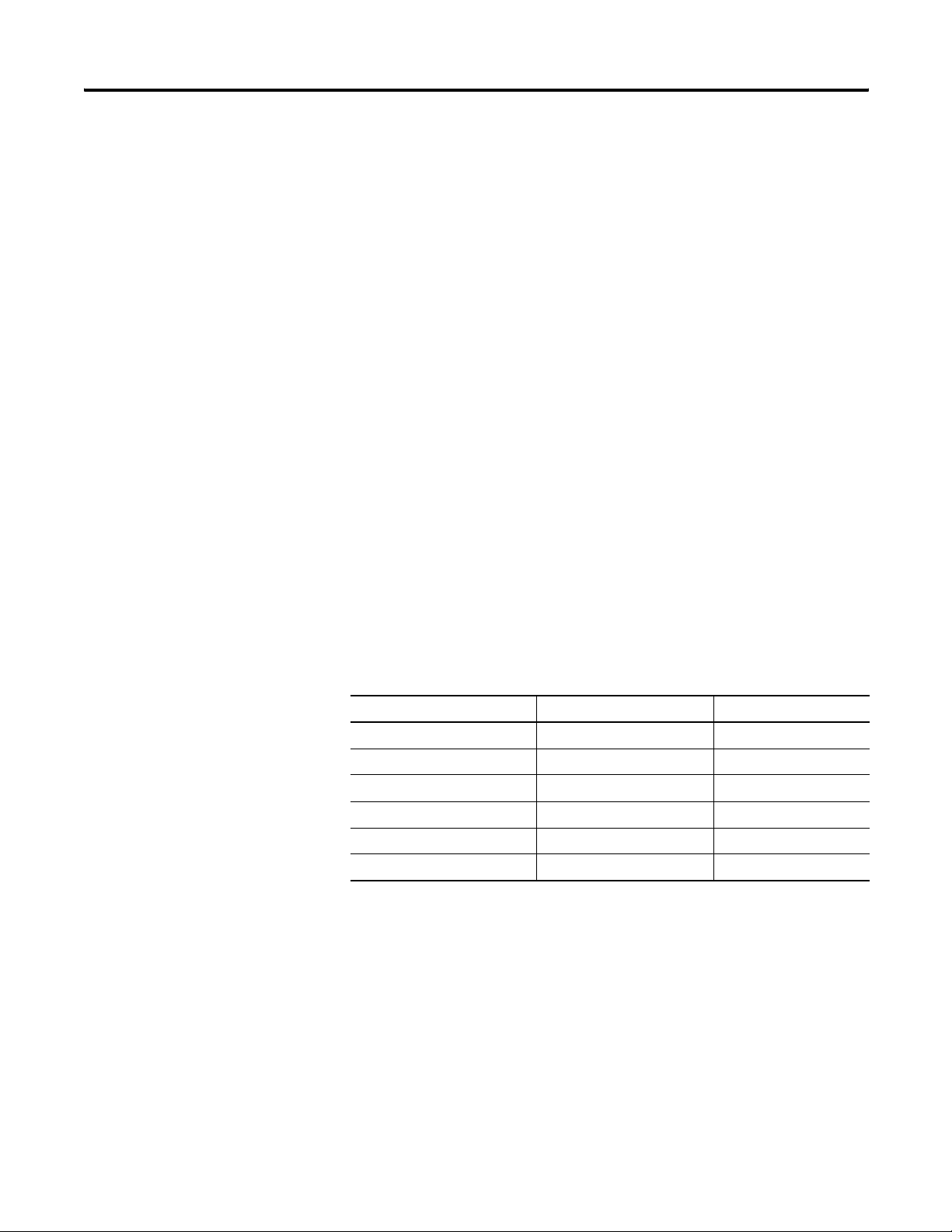

Class Class 1 Class 4

Counters 16-bit (±32,767) 24-bit (±8,388,607)

Input Words 8 with limited information. 23 with all information.

Backplane Interrupts Not permitted. Permitted.

Use in RIO Chassis Permitted. Not permitted.

Use in ControlNet Chassis Not permitted. Permitted.

Module ID Code 3511 15912

Publication 1746-UM002B-EN-P - August 2004

Page 19

Module Overview 1-5

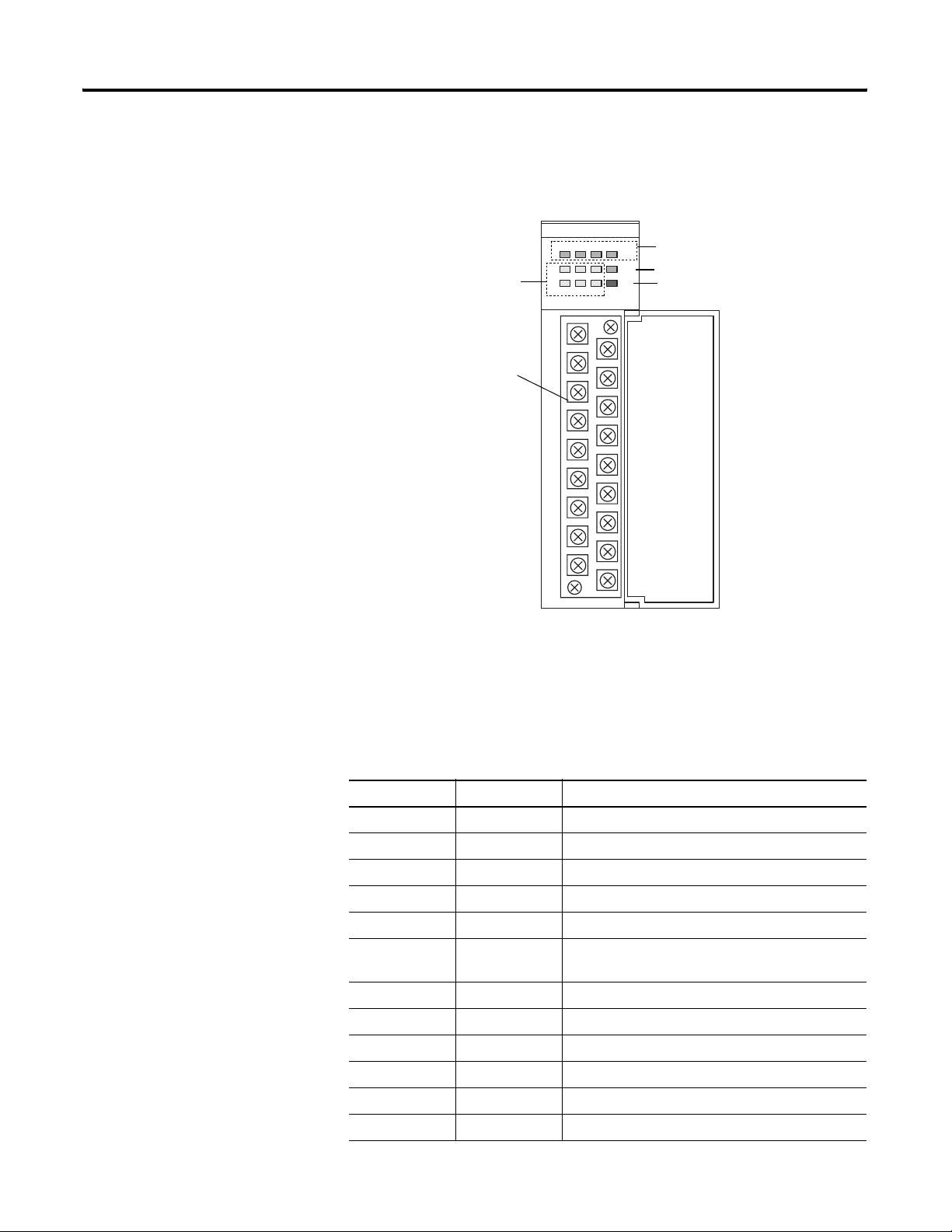

Hardware Features

The module’s hardware features are illustrated below. Refer to

Chapter 3 for detailed information on installation and wiring.

Figure 1.1 Hardware Features

Input Status LEDs

Input and Output

Te rm in al s

COUNTER

OUTPUT STATUS

1023

A1 B1 Z1

A2 B2 Z2

INPUT STATUS

HSCE2

Output Status LEDs

RUN

Running Status LED

FLT

Fault Status LED

LEDs

The front panel has a total of twelve indicator LEDs, as shown in

Figure 1.1 on page 1-5.

LED Color Indicates

0 OUT Green ON/OFF status of real output

1 OUT Green ON/OFF status of real output

2 OUT Green ON/OFF status of real output

3 OUT Green ON/OFF status of real output

RUN Green Running status of the module

FLT Red Steady on: Module fault

Flashing: Output overcurrent

A1 Yellow ON/OFF status of input A1

A2 Yellow ON/OFF status of input A2

B1 Yellow ON/OFF status of input B1

B2 Yellow ON/OFF status of input B2

Z1 Yellow ON/OFF status of input Z1

Z2 Yellow ON/OFF status of input Z2

Publication 1746-UM002B-EN-P - August 2004

Page 20

1-6 Module Overview

Jumpers

Six jumpers select the input voltages for the six inputs A1, B1, Z1, A2,

B2, and Z2. The module accepts input voltages of 5V dc, 12V dc, or

24V dc. See Chapter 3 for jumper locations and settings.

Publication 1746-UM002B-EN-P - August 2004

Page 21

Module Operation

The chapter contains information about:

• operating modes

• input configurations

• gate/preset modes

• counter types

• rate value

• outputs

• range types

Chapter

2

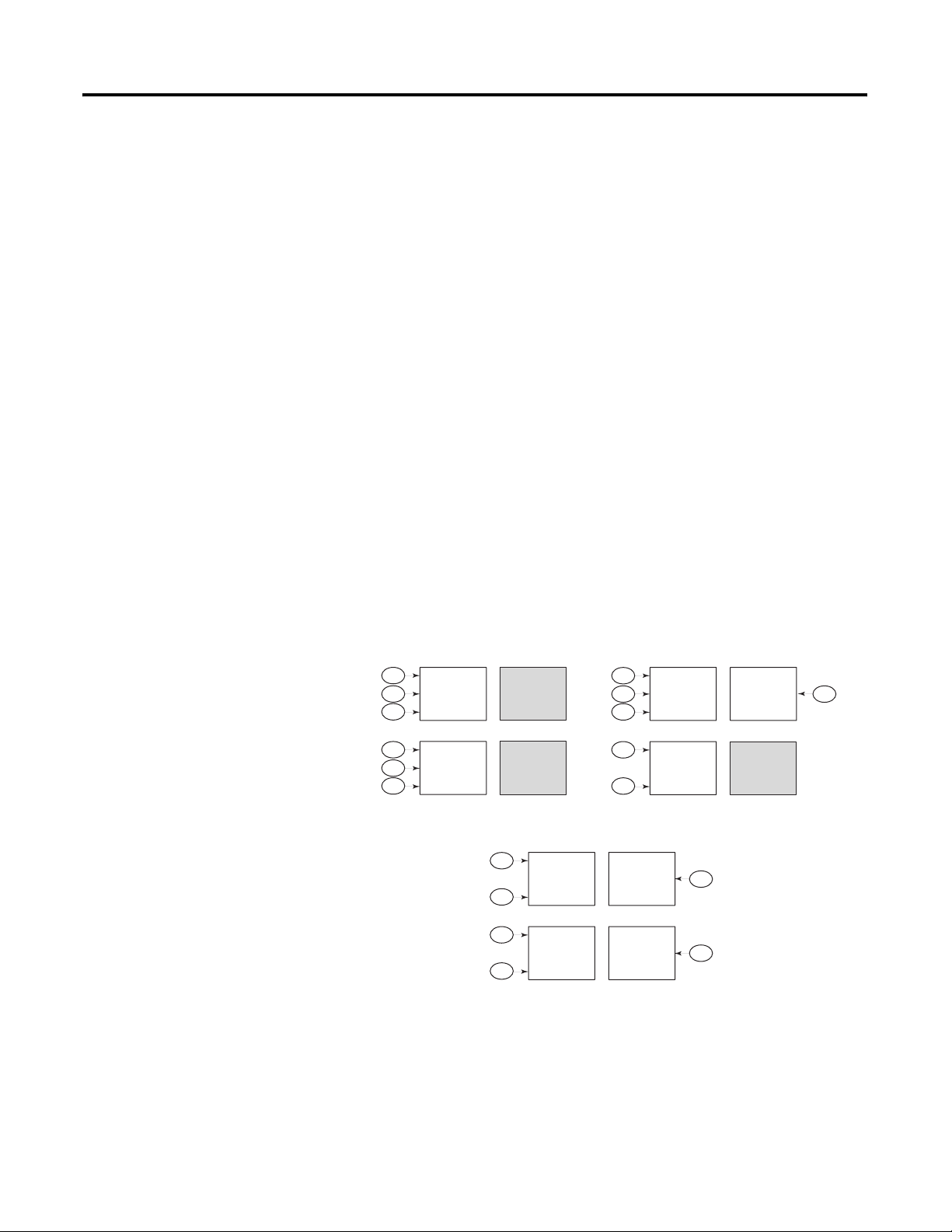

Operating Modes

The module’s operating mode determines the number of available

counters and which inputs are attached to them. The three operating

modes and their input assignments are summarized in Figure 2.1.

Figure 2.1 Operating Mode Input Assignments

A1

Counter 1

B1

Z1

A2

Counter 2

B2

Z2

Operating Mode 1

Counter 3

Counter 4

A1

Counter 1

Z1

A2

Counter 2

Z2

Operating Mode 3

A1

B1

Z1

A2

Z2

Counter 3

Counter 4

Counter 1

Counter 2

Operating Mode 2

B2

B1

Counter 3

Counter 4

B2

1 Publication 1746-UM002B-EN-P - August 2004

Page 22

2-2 Module Operation

Input Configurations

Input configurations determine how the A and B inputs cause the

counter to increment or decrement. The six available configurations

are:

• Pulse/External Direction

• Pulse/Internal Direction

• Up and Down Pulses

• X1 Quadrature Encoder

• X2 Quadrature Encoder

• X4 Quadrature Encoder

See the Summary of Available Counter Configurations on page 2-8 for

the input configurations available for the counters, based on operating

mode.

Pulse/External Direction

With this configuration, the B input controls the direction of the

counter, as shown below. If the B input is low (0), the counter

increments on the rising edges of input A. If the input B is high (1),

the counter decrements on the rising edges of input A.

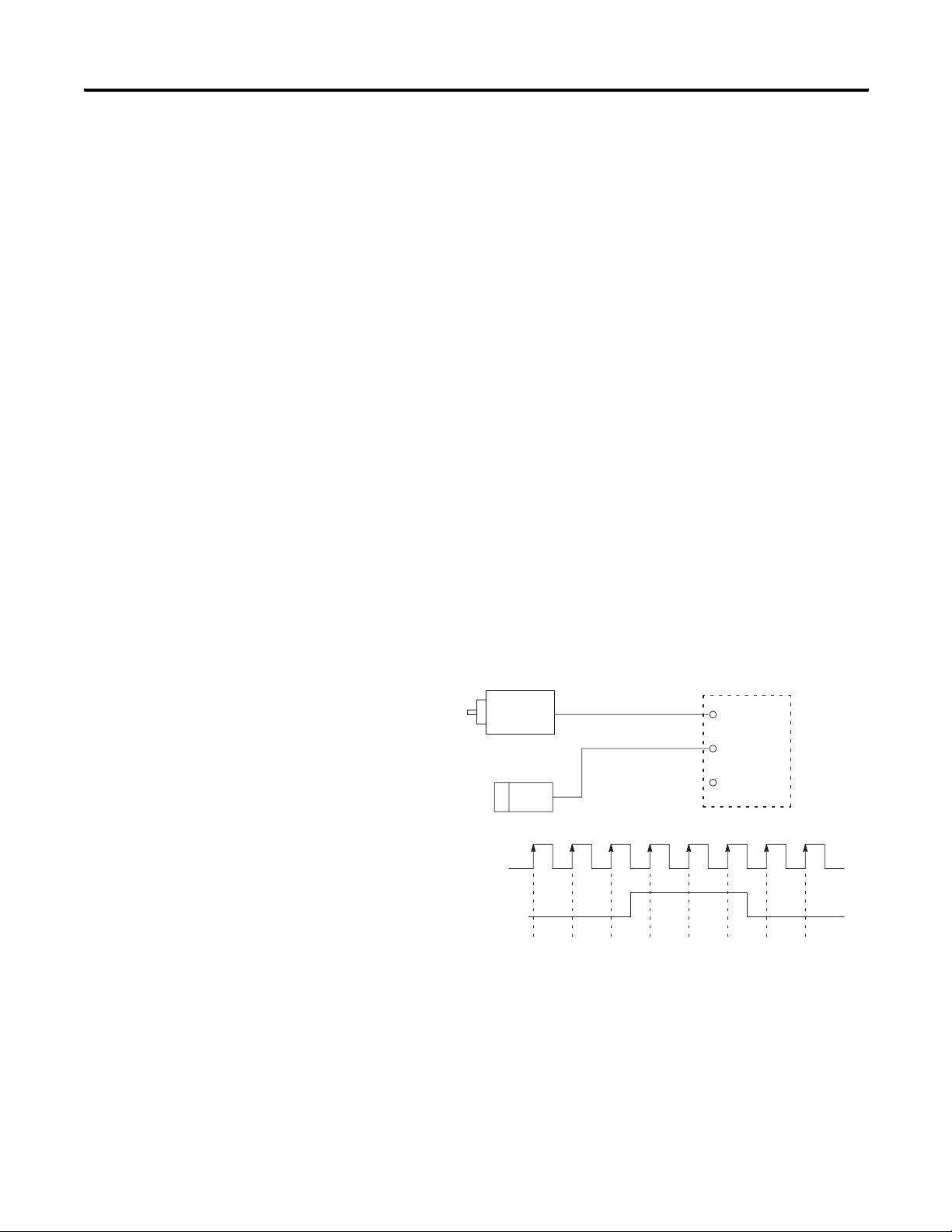

Figure 2.2 Pulse/External Direction Configuration

Count Pulse

Encoder or Sensor

Sensor or Switch

Count Pulse

Direction Control

High = Decrement

Low = Increment

Count

12321012

Direction Control

Input A

Input B

Input Z

Publication 1746-UM002B-EN-P - August 2004

Page 23

Module Operation 2-3

Pulse/Internal Direction

When the Pulse/Internal Direction configuration is selected, a bit

written from the backplane determines the direction of the counter.

The counter increments on the rising edge of the input if the bit is low

(0) and decrements on the rising edge of the input if the bit is high

(1).

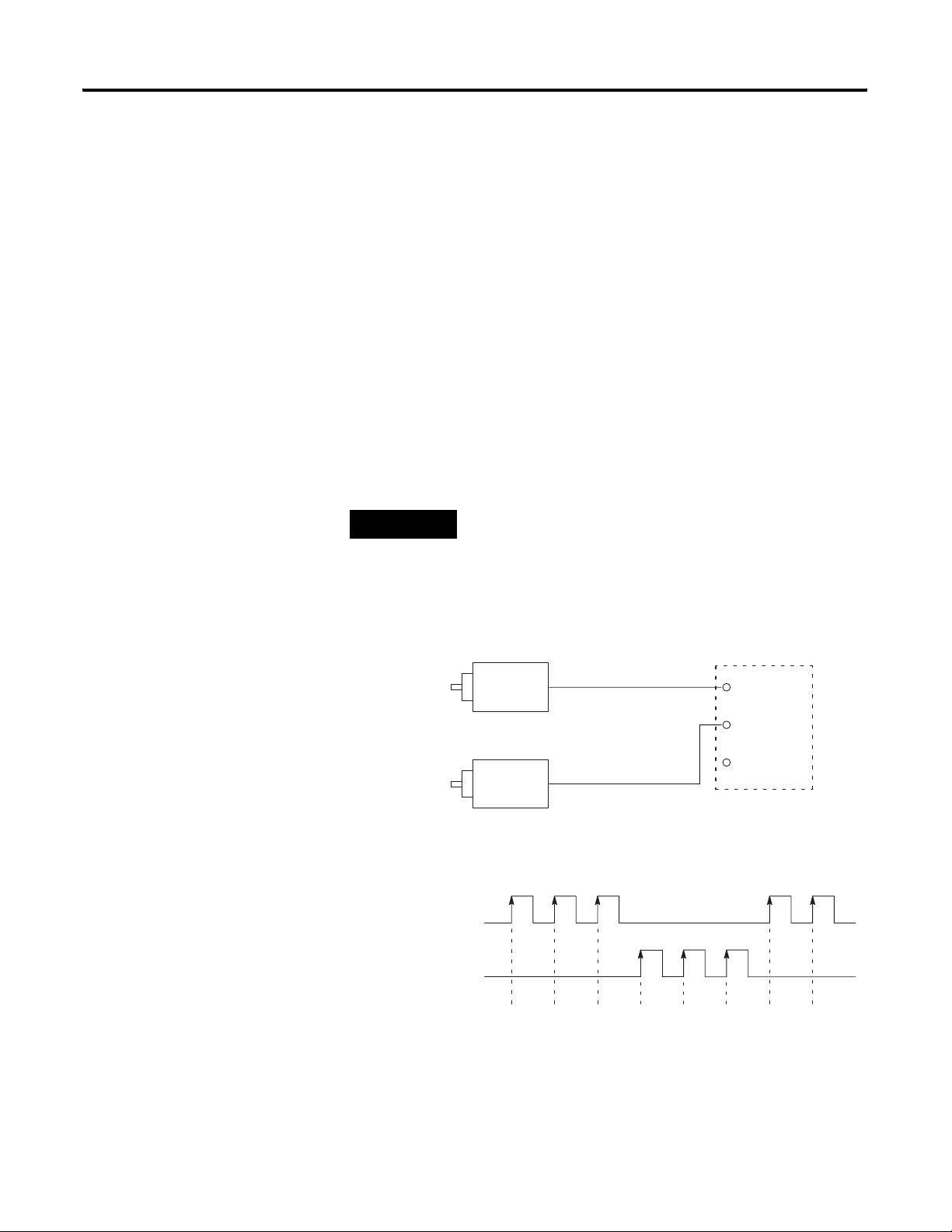

Up and Down Pulses

In this configuration, the counter increments on the rising edge of

pulses applied to input A and decrements on the rising edge of pulses

applied to input B.

TIP

When both inputs transition simultaneously or near

simultaneously, the net result is no change to the

count value. Therefore, simultaneous (or near

simultaneous) pulses are ignored and no change in

the count value is reported.

Figure 2.3 Up and Down Pulse Configuration

Increment Pulse

Incrementing Encoder

or Sensor

Decrement Pulse

Decrementing Encoder or

Sensor

Increment Pulse

(Input A)

(count down)

(count up)

Input A

Input B

Input Z

Module

Decrement Pulse

(Input B)

Count

12321012

Publication 1746-UM002B-EN-P - August 2004

Page 24

2-4 Module Operation

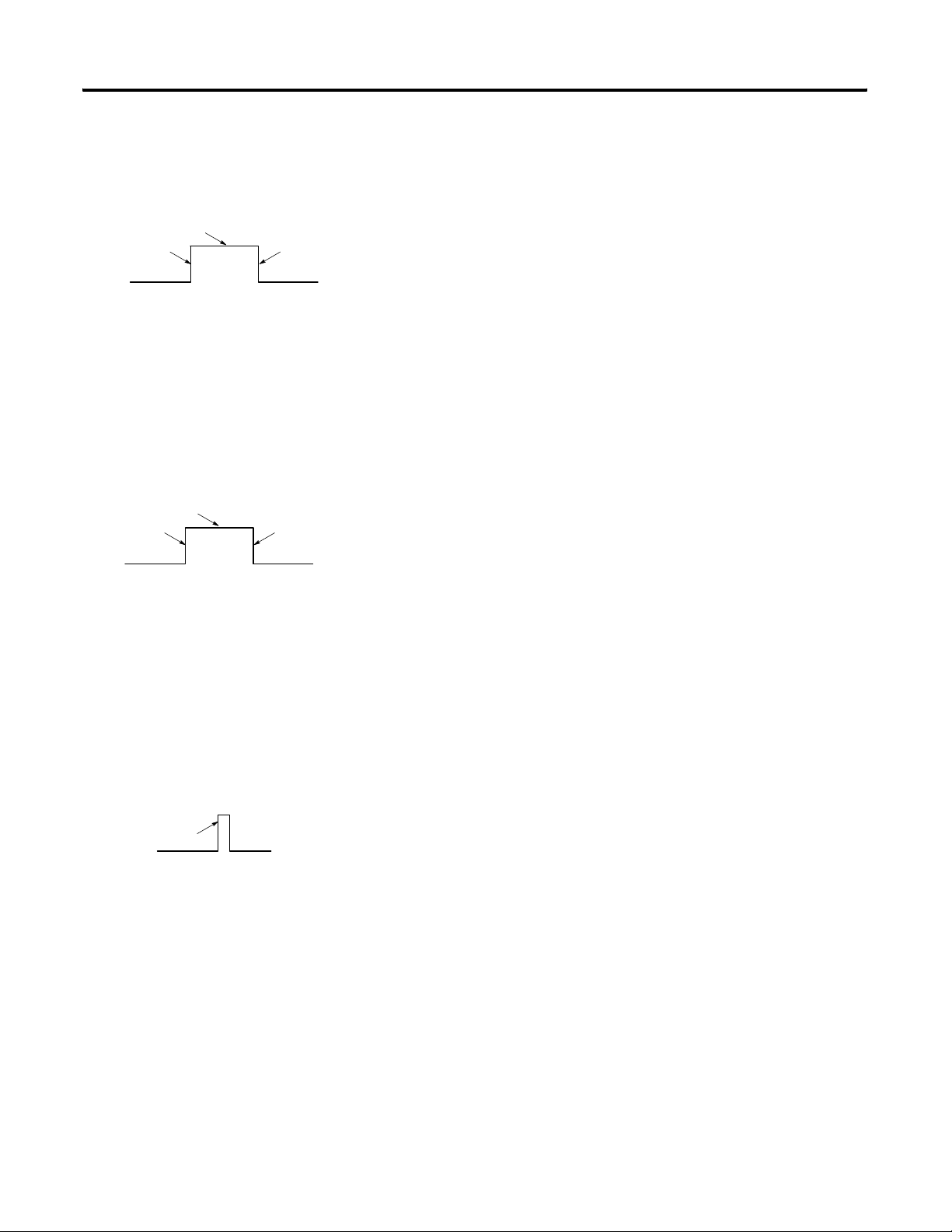

X1 Quadrature Encoder

When a quadrature encoder is attached to inputs A and B, the count

direction is determined by the phase angle between inputs A and B. If

A leads B, the counter increments. If B leads A, the counter

decrements. The counter changes value only on one edge of input A

as shown in Figure 2.4 on page 2-5.

TIP

If B is low, the count increments on the rising edge

of input A and decrements on the falling edge of

input A. If B is high, all transitions on input A are

ignored.

X2 Quadrature Encoder

Like the X1 Quadrature Encoder, the count direction is determined by

the phase angle between inputs A and B. If A leads B, the counter

increments. If B leads A, the counter decrements. However, the

counter changes value on the rising and falling edges of input A, as

shown in Figure 2.4 on page 2-5.

X4 Quadrature Encoder

Operation is similar to the X2 Quadrature Encoder configuration,

except the counter changes value on the rising and falling edges of

inputs A and B as shown in Figure 2.4.

Publication 1746-UM002B-EN-P - August 2004

Page 25

Figure 2.4 Quadrature Encoder Configurations

A

B

Quadrature

Encoder

Z

Module Operation 2-5

Input A

Input B

Input Z

A

B

1 2 3 102

X1 Count

X2 Count

X4 Count

IMPORTANT

Forward Rotation

654321 102345

121110987654321 2345678910 1 0

11

Reverse Rotation

The input configuration is limited by the operating

mode. In mode 1, Counters 1 and 2 can be assigned

any input configuration. In mode 2, Counter 1 can

be assigned any configuration, but Counters 2 and 3

are configured as pulse/internal direction. In mode

3, all counters have the pulse/internal direction

configuration. See the Summary of Available Counter

Configurations on page 2-8.

Input Frequency

Input frequency is determined by the input configuration as shown in

the table below.

Input Configuration Input Frequency

X4 Quadrature Encoder 250 kHz

X2 Quadrature Encoder 500 kHz

All Other Configurations 1 MHz

IMPORTANT

The minimum high and low times for the pulse train

are 475 ns. Therefore, the input pulse train must fall

between a 47.5 to 52.5 percent duty cycle at 1 MHz.

Publication 1746-UM002B-EN-P - August 2004

Page 26

2-6 Module Operation

Gate/Preset Modes

A counter’s gate/preset mode determines what, if any, gating is

applied to the counter and what, if any, conditions will preset the

counter to the preset value. The Z inputs are the only inputs used for

gating or presetting. The six gate/preset modes are described below.

No Preset

The counter is not preset under any conditions. The Z inputs are not

used.

Soft Preset Only

The counter is preset when the matching preset bit in the SLC 500

output image table experiences a positive transition, but not in

response to the Z input.

TIP

The soft preset bit operates in all the gate/preset

modes except No Preset.

store, continue

counting

Store/Continue

The count value is captured when the module detects an

inactive-to-active transition on the Z input of the counter. This stored

value is made available to the backplane. A stored status bit in the

input image table is set to signal the processor that a new value is

available. This bit is active until the capture value is read by the

processor. Therefore, it is on for a maximum of 10 ms in Class 1, and

a maximum of one scan or 10 ms, whichever is shorter, in Class 4. If a

second capture event occurs before the first is read, the first value is

lost. The count and rate values are not affected by a store event.

Publication 1746-UM002B-EN-P - August 2004

Page 27

counter has stopped counting

stop count

store count

resume

counting

Module Operation 2-7

Store/Hold/Resume

The count value, captured when the module detects a positive

transition on the Z input, is made available to the backplane. A stored

status bit is set in the input image table to signal the processor that a

new value is available. This bit is active until the capture value is read

by the processor. Therefore, it is on for a maximum of 10 ms in Class

1, and a maximum of one scan or 10 ms, whichever is shorter, in Class

4. The count value is held as long as the Z input is active. Because the

count value is not changing, the rate value is equal to zero while the

counter is held.

Store/Preset/Hold/Resume

stop count,

store count,

store count,

preset, start

counting

counter has

stopped counting

start

counting

from preset

The counter is set to its programmed preset value when the module

detects a positive transition on the Z input of the counter. The capture

value is made available to the backplane. A stored status bit is set in

the input image table to signal the processor that a new value is

available. This bit is active until the capture value is read by the

processor. Therefore, it is on for a maximum of 10 ms in Class 1, and

a maximum of one scan or 10 ms, whichever is shorter, in Class 4. The

preset counter value is held as long as the Z input remains active.

Because the count value is not changing, the rate value equals zero

while the preset value is held.

Store/Preset/Start

The counter is set to its programmed preset value when the module

detects a positive transition on the Z input of the counter. The capture

value is made available to the backplane. A stored status bit is set in

the input image table to signal the processor that a new value is

available.This bit is active until the capture value is read by the

processor. Therefore, it is on for a maximum of 10 ms in Class 1, and

a maximum of one scan or 10 ms, whichever is shorter, in Class 4.

Publication 1746-UM002B-EN-P - August 2004

Page 28

2-8 Module Operation

Gate and Preset Limitations

Because only the Z inputs are used for external gating and presetting,

the only gate/preset modes available for Counters 3 and 4 are No

Preset and Soft Preset Only. All six modes are always available for

Counters 1 and 2.

IMPORTANT

In Class 1, Operating Mode 2, Counter 2 does not

have a capture value available. In Class 1, Operating

Mode 3, no capture values are available.

Gate and Preset Considerations

Z-pulse Preset Operation

In applications where the Z pulse of the encoder is being used to

preset the position, and where the Z pulse of the encoder is aligned

with either the A or B pulses, the capture or count value may be

affected by ± 1 count. If the Z pulse is edge aligned with the A pulse,

preset operations may not be performed accurately in any of the

quadrature modes. If the Z pulse is edge aligned with the B pulse,

preset operation may not be performed accurately in the X4

quadrature mode only. A small capacitor (for example, 0.01 µF) across

the Z inputs will dis-align these inputs and should correct this

condition.

Summary of Available Counter Configurations

Publication 1746-UM002B-EN-P - August 2004

The table below summarizes the input configurations and gate/preset

modes available for all counters, based on operating mode.

Operating

Mode

11All All

21All All

3 1 Pulse/Internal Direction All

Counter Input Configuration Gate/Preset Mode

2All All

2 Pulse/Internal Direction All

3 Pulse/Internal Direction No Preset or Soft Preset Only

2 Pulse/Internal Direction All

3 Pulse/Internal Direction No Preset or Soft Preset Only

4 Pulse/Internal Direction No Preset or Soft Preset Only

Page 29

Module Operation 2-9

Counter Types

Each counter can be programmed to operate as a linear or ring

counter. Both types are described below.

Linear Counter

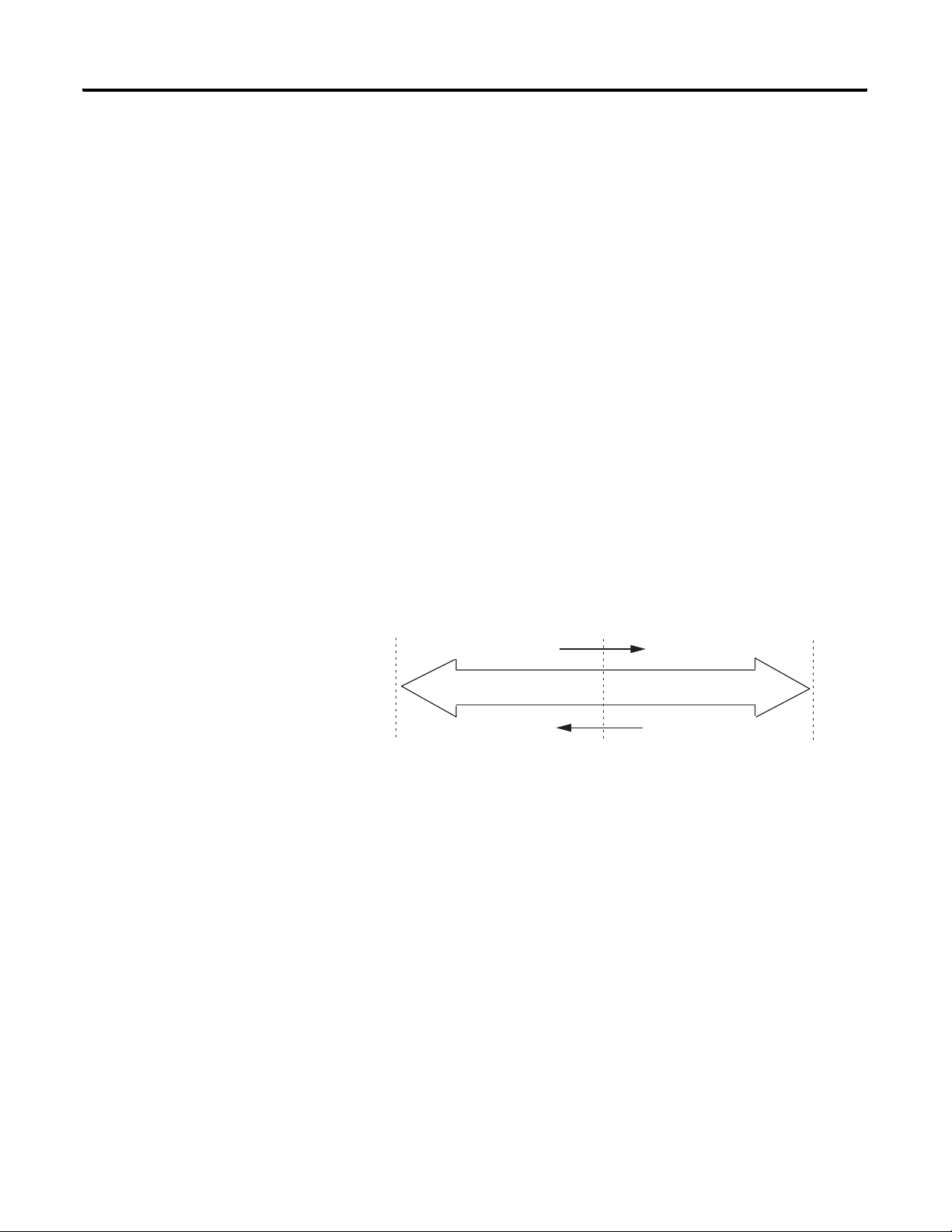

The figure below demonstrates linear counter operation. In linear

operation, the count value must remain within the programmed

minimum/maximum values. If the count value goes above or below

these values, the counter stops counting, and an overflow/underflow

bit is set. In the overflow or underflow condition, the rate value

continues to be updated and valid.

The number of pulses accumulated in an overflow/underflow state

are ignored. The counter begins counting again when pulses are

applied in the proper direction. For example, if you exceed the

maximum by 1,000 counts, you do not need to apply 1,000 counts in

the opposite direction before the counter begins counting down. The

first pulse in the opposite direction decrements the counter.

Figure 2.5 Linear Counter Diagram

Minimum Value

Underflow

Count Up

0

Counter Value

Maximum Value

Count Down

Overflow

Publication 1746-UM002B-EN-P - August 2004

Page 30

2-10 Module Operation

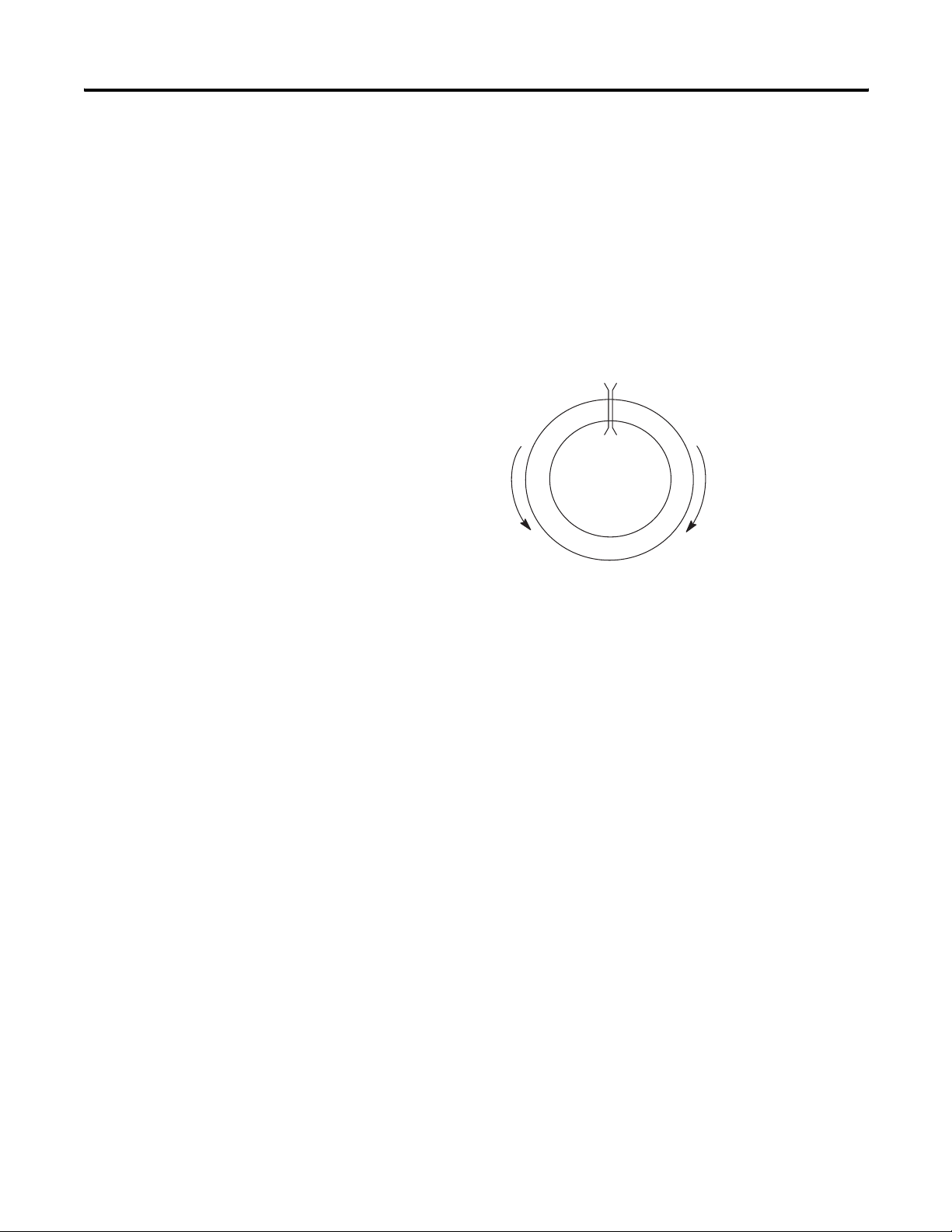

Ring Counter

Figure 2.6 demonstrates ring counter operation. In ring counter

operation, the count value changes between programmable minimum

and maximum values. If, when counting up, the counter reaches the

maximum value, it rolls over to the minimum value. If, when counting

down, the counter reaches the minimum value, it rolls over to the

maximum value.

Figure 2.6 Ring Counter Diagram

Rate Value

Maximum Value

Rollover

Count Down

Minimum Value

Count Up

The rate value reported to the processor is calculated in counts per

second (Hz), and is available with all input configurations. The input

configuration determines how the rate value is calculated. When the

count value is increasing, the rate value is positive. When the count

value is decreasing, the rate value is negative.

The rate value is generally calculated as follows:

When the first input pulse is received, the value of an independent,

free-running timer (Ta) is recorded. The module waits approximately

16 ms, while counting more input pulses. After 16 ms, the module

waits for the next input pulse, and the value of the independent timer

(Tb) is again recorded. The module then calculates the rate value

using the formula:

number of counts

rate value

------------------------------------------

=

Tb Ta–

Publication 1746-UM002B-EN-P - August 2004

Page 31

Module Operation 2-11

Additional checks ensure that rates below 1 Hz, which are not

supported by the module, and frequencies due to motor vibration, are

not counted in the rate value calculation.

Table 2.1 Typical Rate Update Times

Rates (Hz) Time Between Pulses (ms) Time Between Updates (ms)

1 to 59 17 to 1000 17 to 1000

60 to 1000 0 to 16 0 to 33

Above 1000 0 to 1 16

IMPORTANT

Because of the way the 1746-HSCE2 performs rate

value calculations, invalid rate measurements may

occur if the input frequency is below 60 Hz.

Therefore, we recommend that the 1746-HSCE2

module not be used for rate monitoring or rate range

control for frequencies below 60 Hz.

The invalid measurements apply only to rate values

and do not affect the count value reported to the

controller, which are always correct.

Accuracy

The accuracy of the rate value can be ±0.005% (typical). For this

resolution, the rate measurement value must be transferred in

single-precision floating-point format. This format is only available

when the module operates as Class 4. Fractional rates, those between

1 and 0 or -1 and 0, are not reported.

The rate measurement value can also be transferred as an integer

value. The integer format is available in both Class 1 and Class 4.

Output Control

All eight outputs can be controlled by any or all of the counters, or

they can be controlled by the user program. When controlled by a

counter, an output can be programmed to turn on or off based on the

count value and/or rate value of the counter.

The eight outputs are divided into four real outputs and four virtual

outputs. The outputs can be activated from the user program or from

the module in response to specified input events. The status of the

real outputs is available to the user program. The virtual outputs are

available only to the user program. They have no real output

associated with them. The real outputs are protected from overloads

by a self-resetting fuse.

Publication 1746-UM002B-EN-P - August 2004

Page 32

2-12 Module Operation

Range Control

-32,767 +32,767

The module can be programmed to use either counter or rate ranges

to determine whether an output is active. Up to 16 dynamically

configurable ranges are available. The ranges, programmed using

range start and range stop values, can overlap. When the count is

within more than one range, the output patterns of those ranges are

combined (logically ORed) to determine the actual status of the

output. A mixture of count ranges and rate ranges may be used.

Count Range

In a count range, the outputs are active if the count value is within the

user-defined range. The valid count range is dependent upon the

operating class. In Class 1, the valid range is -32,767 to +32,767. In

Class 4, the valid range is -8,388,607 to +8,388,607. The examples in

Figure 2.7 and Figure 2.8 use Class 1 operation.

Figure 2.7 Count Range with Linear Counter

0

Range 4 Stop

on

off

Value

Output 0

Output 1

Output 2

Output 3

Range 1

Range 3

Range Start

Value

1 -7000 -5000 0 0 0 0 0 0 0 1 0

2 -1000 +4500 0 0 0 0 0 0 1 0 1

3 -4000 +3000 0 0 0 0 0 1 0 0 2

4 +9000 -9000 0 0 0 0 1 0 0 1 0 and 3

(1) Bits 0 through 3 are real outputs. Bits 4 through 7 are virtual outputs.

Range 2

Stop

Value

Outputs

76543210

(1)

Range 4 Start

Value

Outputs

Affected

Publication 1746-UM002B-EN-P - August 2004

Page 33

Figure 2.8 Count Range with Ring Counter

Range 3

32,000

32,767

Module Operation 2-13

200

1

500

Range 2

Range

23,000

Range 4

Start

Value

20,000

Stop

Value

10,000

Outputs

Range 1

(1)

12,500

76543210

8,000

1 10,000 12,500 0 0 0 0 0 0 0 1 0

2 200 8,000 00000010 1

3 32,000 500 0 0 0 0 0 1 0 0 2

4 20,000 23,000 0 0 0 0 1 0 0 1 0 and 3

(1) Bits 0 through 3 are real outputs. Bits 4 through 7 are virtual outputs.

Outputs

Affected

Publication 1746-UM002B-EN-P - August 2004

Page 34

2-14 Module Operation

-32,767 0 +32,767

(min. rate value)

Rate Range

In a rate range, the outputs are active if the rate measurement is

within the user-defined range. The valid input rate is dependent upon

the operating class. In Class 1, the input rate can be up to 32,767 Hz in

either direction. In Class 4, the input rate can be up to 1 MHz in either

direction. The linear counter example in Figure 2.9 uses Class 1

operation.

Figure 2.9 Rate Range

(max. rate value)

Rate Value

on

off

Range 4

Output 0

Output 1

Output 2

Output 3

Range 1

Range 3

Range

1 -7000 -5000 00000001 0

2 -1000 +4500 00000010 1

3 -4000 +3000 00000100 2

4 +20000 -20000 00001001 0 and 3

(1) Bits 0 through 3 are real outputs. Bits 4 through 7 are virtual outputs.

Start

Value

Range 2

Stop

Value

Range 4

Outputs

76543210

(1)

Outputs

Affected

Counter Input Data

Publication 1746-UM002B-EN-P - August 2004

The format of the counter input data table depends on the module’s

mode and class of operation. The status data formats for Class 1 and

Class 4 are shown below, followed by explanations of the

programming bits and status bytes. Mode 1 is the default for both

Class 1 and Class 4 operation.

Page 35

Module Operation 2-15

Class 1 Operation

In this operating class, the input data consists of eight words. The

counters are sixteen bits. The data stored in an input word change

based on the module’s operating mode.

Figure 2.10 Mode 1 Input Data Format

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Word 0

0OP

MODE

ACK

MFLT

PERR

DEBUG

FB1

Word 1 Counter 2 Status Counter 1 Status

Word 2 Counter 1: Count Value

Word 3 Counter 1: Rate Value

Word 4

Counter 1: Capture Value

Word 5 Counter 2: Count Value

Word 6 Counter 2: Rate Value

Word 7

(1) See page 2-6 for a description of capture values.

Counter 2: Capture Value

Output State

Virtual Real

(1)

(1)

Figure 2.11 Mode 2 Input Data Format

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Word 0

ACK

MFLT

PERR

DEBUG

0OP

FB1

MODE

Output State

Virtual Real

Word 1 Counter 2: Status Counter 1: Status

Word 2 Counter 1: Count Value

Word 3 Counter 1: Rate Value

Word 4

Counter 1: Capture Value

(1)

Word 5 Counter 2: Count or Rate Value

Word 6

0 0 0 0 0 0 0 0 Counter 3: Status

Word 7 Counter 3: Count or Rate Value

(1) See page 2-6 for a description of capture values.

Figure 2.12 Mode 3 Input Data Format

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Word 0

ACK

MFLT

PERR

DEBUG

0OP

FB1

MODE

Output State

Virtual Real

Word 1 Counter 2 Status Counter 1 Status

Word 2 Counter 1: Count or Rate Value

Word 3 Counter 2: Count or Rate Value

Word 4 Counter 4: Status Counter 3: Status

Word 5 Counter 3: Count or Rate Value

Word 6 Counter 4: Count or Rate Value

Word 7

Not Used. Set equal to 0000H

Publication 1746-UM002B-EN-P - August 2004

Page 36

2-16 Module Operation

Class 4 Operation

In Class 4 operation, the counter data consist of a maximum of 23

words.

Figure 2.13 Class 4 Data Format

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Word 0

ACK

MFLT

PERR

DEBUG

FB1

Word 1 Counter 2 Status Counter 1 Status

Word 2 Upper 4 digits: Counter 1 Count Value

Word 3 Lower 3 digits: Counter 1 Count Value

Word 4

Word 5

Word 6 Upper 4 digits: Counter 1 Capture Value

Word 7 Lower 3 digits: Counter 1 Capture Value

Word 8 Upper 4 digits: Counter 2 Count Value

Word 9 Lower 3 digits: Counter 2 Count Value

Word 10

Word 11

Word 12 Upper 4 digits: Counter 2 Capture Value

Word 13 Lower 3 digits: Counter 2 Capture Value

Word 14 Counter 4 Status Counter 3 Status

Word 15 Upper 4 digits: Counter 3 Count Value

Word 16 Lower 3 digits: Counter 3 Count Value

Word 17

Word 18

OP

0

MODE

Virtual Real

Counter 1 Rate Value

Counter 2 Rate Value

Counter 3 Rate Value

Output State

(1)

(1)

(1)

(2)

Transferred in all Modes

(2)

Publication 1746-UM002B-EN-P - August 2004

Transferred in Modes 2 and 3

Word 19 Upper 4 digits: Counter 4 Count Value

(2)

Word 20 Lower 3 digits: Counter 4 Count Value

Word 21

Counter 4 Rate Value

(1)

Word 22

Transferred in Mode 3

(1) The format of the Rate Values is programmed with the Rate Value Format bit in the Module Setup programming

block. This bit specifies the rate value to be in integer or floating-point format. The default is integer format.

Count values are always transferred in integer format. See Data Format on page 4-3.

(2) Data values transferred. Regardless of operating mode, the module will transfer up to 23 words. Words that do

not contain relevant data are set to 0000H.

Page 37

Module Operation 2-17

Input Word Bit Values

ACK: Acknowledge Bit

This bit makes a 0 to 1 transition to signal the receipt of programming

data.

MFLT: Module Fault Bit

This bit is set only if the module does not power up correctly. After a

proper power up, the MFLT bit remains reset.

PERR: Programming Error Bit

The state of this bit is valid only when the acknowledge bit is set. This

bit is reset when the last programming block is accepted without

error. It is set when any one of the reserved bits are set or another

programming error has occurred. For a list of other programming

error conditions, see Module Programming Errors on page 5-3.

DEBUG: Debug Mode Bit

This bit is set when the debug mode is active.

IMPORTANT

For details, see Debug Mode Operation on page 5-7.

When the debug mode is active, the input data file

shows the programming setup, not rate and count

values.

FB1: Fuse Status Bit

The FB1 fuse status bit is set (1) when the fuse is open. In addition,

the module fault LED blinks to indicate an open fuse.

When FB1 is set (1), the real outputs do not function. Virtual outputs

are not affected. The input word reflects this condition.

The module tries resetting the outputs at intervals of 500 ms. During

each retry, the fuse status bit is reset (0). After the overload condition

is corrected, the fuse bit resets (0) automatically.

Publication 1746-UM002B-EN-P - August 2004

Page 38

2-18 Module Operation

OP MODE: Operating Mode Bits

The module uses these two bits to tell the processor what mode it is

in. In class 1, the data value that an input word contains changes

based on the operating mode.

Table 2.2 Mode Bit Settings

Bit 09 Bit 08 Mode

00Reserved

0 1 Mode 1

1 0 Mode 2

1 1 Mode 3

Output State Byte

These bits correspond to the real or virtual state of the outputs. Bits 00

through 03 represent real outputs. Bits 04 through 07 represent virtual

outputs.

Counter Status Bytes

Each counter has an associated status byte. The format of the byte

depends on the module’s class of operation as shown below.

Figure 2.14 Class 1 Counter Status Byte Format

15 14 13 12 11 10 09 08

07 06 05 04 03 02 01 00

C/R

Figure 2.15 Class 4 Counter Status Byte Format

15 14 13 12 11 10 09 08

07 06 05 04 03 02 01 00

0 0 ROvFRUdFCOvFCUdF CState

0 ROvF RUdF COvF CUdF CState

Publication 1746-UM002B-EN-P - August 2004

Page 39

Module Operation 2-19

C/R: Count/Rate Bit

The count/rate bit is used only in Class 1 operating mode. Because

only one data word is available for Counters 2 and 3 in operating

mode 2, and one data word for each of the four counters in operating

mode 3, the module transfers either the counter’s count or rate value.

When this bit is reset (0), the data in the corresponding word is the

count value. When this bit is set (1), the data in the corresponding

word is the rate value.

ROvF: Rate Overflow Bit

This bit is set when the rate is greater than the maximum rate value.

RUdF: Rate Underflow Bit

This bit is set when the rate is less than the minimum rate value.

COvF: Counter Overflow Bit

When the counter is configured as a linear counter, this bit is set when

the count would become one over the maximum count value.

TIP

Counter overflow or underflow bits are reset when a

pulse in the opposite direction is received.

CUdF: Counter Underflow Bit

When the counter is configured as a linear counter, this bit is set when

the count would become one under the minimum count value.

CState: Counter State Bits

These two bits show the operational state of the counter.

Table 2.3 Counter State Bit Settings

Bits 09 or 01 Bits 08 or 00 Operating State

0 0 Stopped

0 1 Running

10Hold

11Reserved

Publication 1746-UM002B-EN-P - August 2004

Page 40

2-20 Module Operation

Publication 1746-UM002B-EN-P - August 2004

Page 41

Installation and Wiring

This chapter provides the following information:

• compliance to European Union Directives

• module installation

• wiring considerations

• input/output connections

• encoder wiring

• switch wiring

Chapter

3

Compliance to European Union Directives

If this product has the CE mark, it is approved for installation within

the European Union and EEA regions. It has been designed and tested

to meet the following directives.

EMC Directive

This product is tested to meet Council Directive 89/336/EED

Electromagnetic Compatibility (EMC) and the following standards, in

whole or in part, documented in a technical construction file:

EN50081-2

EMC — Generic Emission Standard, Part 2 – Industrial Environment

EN50082-2

EMC — Generic Emission Standard, Part 2 – Industrial Environment

This product is intended for use in an industrial environment.

Low Voltage Directive

This product is tested to meet Council Directive 73/23/EEC Low

Voltage, by applying the safety requirements of EN 61131-2

Programmable Controllers, Part 2 – Equipment Requirements and

Tests.

1 Publication 1746-UM002B-EN-P - August 2004

Page 42

3-2 Installation and Wiring

Prevent Electrostatic Discharge

For specific information required by EN61131-2, see the appropriate

sections in this publication, as well as the following Allen-Bradley

publications:

• Industrial Automation, Wiring and Grounding Guidelines for

Noise Immunity, publication 1770-4.1

• Automation Systems Catalog, publication B111

ATTENTION

Static discharges may cause permanent damage to

the module. Follow these guidelines when you

handle the module:

Setting the Jumpers

!

Six jumpers are located in a column on the side of the module. Use

the jumpers to select the input voltage for each of the inputs A1, B1,

Z1, A2, B2, and Z2. The settings are shown in the figure on the

following page.

• Touch a grounded object to discharge static

potential.

• Wear an approved wrist-strap grounding device.

• Handle module by plastic case only. Avoid

contact between module circuits and any surface

which can hold an electrostatic charge.

• If available, use a static-safe work station.

Publication 1746-UM002B-EN-P - August 2004

Page 43

Figure 3.1 Jumper Settings

Installation and Wiring 3-3

JP1 (A1 )

JP2 (B1)

JP3 (Z1)

JP4 (A2)

JP5 (B2)

JP6 (Z2)

Jumper Settings

24V dc

10-30V dc

(default)

IMPORTANT

ATTENTION

5V dc

4.2-12V dc

For a 12V dc encoder signal, use the 24V dc jumper

setting.

If jumpers are not set to match the encoder type, the

module may be damaged.

!

The 5V dc settings respond to inputs with an active voltage between

4.2 and 12 volts. The 24V dc settings respond to inputs with active or

high settings between 10 and 30 volts.

Installing the Module

ATTENTION

!

Disconnect power before attempting to install,

remove, or wire the module.

Publication 1746-UM002B-EN-P - August 2004

Page 44

3-4 Installation and Wiring

1. Make sure your SLC power supply has adequate reserve current

capacity. The module requires 250 mA at +5V dc.

2. Align the full-sized circuit board with the chassis card guide as

shown in Figure 3.2. The first slot of the first chassis is reserved

for the processor.

3. Slide the module into the chassis until the top and bottom

latches catch. To remove the module, press the release clips at

the top and bottom of the module and slide it out.

4. Cover all unused card slots with the Card Slot Filler, catalog

number 1746-N2.

Figure 3.2 Installing the Module

Important Wiring Considerations

Publication 1746-UM002B-EN-P - August 2004

Use the following guidelines when planning the system wiring for the

module:

• Install the SLC500 system in a NEMA-rated enclosure.

• Disconnect power to the SLC processor and the module before

wiring.

• Make sure the system is properly grounded.

• Group this module and low voltage DC modules away from AC

I/O or high voltage DC modules.

• Shielded cable is required for high-speed input signals A, B, and

Z. Use individually shielded, twisted-pair cable lengths up to

300 m (1000 ft.).

Page 45

Installation and Wiring 3-5

• Shields should be grounded only at one end. Ground the shield

wire outside the module at the chassis mounting screw. Connect

the shield at the encoder end only if the housing is electronically

isolated from the motor and ground

Figure 3.3 Grounding the Shield Wire at the Chassis Mounting Screw

Spade Connector

.

Mounting Screw

Star Washer

Chassis Mounting Tab

• If you have a junction in the cable, treat the shields as

conductors at all junctions. Do not ground them to the junction

box.

• If your application requires only low frequency inputs, you can

use a filter to minimize high frequency noise.

• If the Z pulse is edge aligned with A or B pulses, capture/preset

operation may be affected by ± 1 count. A small capacitor

(0.01µF) across the Z inputs will dis-align these inputs and

should correct this condition. See Z-pulse Preset Operation on

page 2-8.

Considerations for Reducing Noise

In high noise environments, the 1746-HSCE2 inputs may accept “false”

pulses, particularly when using low frequency input signals with

slowly sloping pulse edges. To minimize the effects of high frequency

noise on low frequency signals, the user can do the following:

• Identify and remove noise sources.

• Route 1746-HSCE2 input cabling away from noise sources.

• Install low pass filters on input signals. Filter values are

dependent on the application and can be determined

empirically.

• Use devices which output differential signals, like differential

encoders, to minimize the possibility that a noise source will

cause a false input.

Publication 1746-UM002B-EN-P - August 2004

Page 46

3-6 Installation and Wiring

Electronic Protection

The electronic protection of the 1746-HSCE2 has been designed to

provide protection for the module from overload current conditions.

The protection is based on a thermal cut-out principle. In the event of

a short circuit or overload current condition on an output channel, all

channels will turn off within milliseconds after the thermal cut-out

temperature has been reached.

IMPORTANT

The module does not provide protection against

reverse polarity wiring or wiring to AC power

sources. Electronic protection is not intended to

replace fuses, circuit breakers, or other

code-required wiring protection devices.

Auto Reset Operation

IMPORTANT

1746-HSCE2 outputs perform auto-reset under

overload conditions. When an output channel

overload occurs as described above, all channels

turn off within milliseconds after the thermal cut-out

temperature has been reached. While the

overcurrent condition is present, the module tries

resetting the outputs at intervals of 500 ms. If the

fuse cools below the thermal cut-out temperature, all

outputs auto-reset and resume control of their

external loads as directed by the module until the

thermal cut-out temperature is again reached.

Publication 1746-UM002B-EN-P - August 2004

Removing power from an overloaded output

channel would also allow the fuse to cool below the

thermal cut-out temperature, allowing auto-reset to

occur when power is restored. The output channels

then operate as directed by the module until the

thermal cut-out temperature is again reached.

To avoid auto-reset of output channels under

overload conditions, monitor the fuse blown status

bit (FB1) in the module’s status file and latch the

outputs off when an overcurrent condition occurs.

An external mechanical fuse can also be used to

open output circuits when they are overloaded.

Page 47

Installation and Wiring 3-7

Input and Output Connections

Input and output wiring terminals are shown in the figure below.

Each terminal accepts #14 AWG wire. Tighten screws only tight

enough to immobilize the wire. The torque applied to the screw

should not exceed 0.9 Nm (8 in-lb.).

Figure 3.4 Terminal Wiring

Release Screw

OUTPUT COMMON

Release Screw

A1+

B1+

Z1+

A2+

B2+

Z2+

OUTPUT 1

OUTPUT 3

A1-

B1-

Z1-

A2-

B2-

Z2-

OUTPUT 0

OUTPUT 2

OUTPUT +Vdc

Removing the Terminal Block

Remove the terminal block by turning the slotted terminal block

release screws counterclockwise. The screws are attached to the

terminal block, so it will follow as the screws are turned out.

ATTENTION

To avoid cracking the removable terminal block,

alternate turning the slotted terminal block release

screws.

!

Publication 1746-UM002B-EN-P - August 2004

Page 48

3-8 Installation and Wiring

Encoder Wiring

Differential encoders provide the best immunity to electrical noise. We

recommend, whenever possible, to use differential encoders.

The wiring diagrams on the following pages are provided to support

the Allen-Bradley encoders you may already own.

Differential Encoder Wiring

Figure 3.5 Differential Encoder Wiring

(1)

Allen-Bradley

845H Series

differential

encoder

VS

Cable

GND

A

A

B

B

Z

Z

Shield

+VDC

COM

A1(+)

A1(–)

B1(+)

B1(–)

Z1(+)

Z1(–)

Power

Supply

shield/housing

Connect only if housing is electronically

isolated from the motor and ground.

(1) Refer to your encoder manual for proper cable type. The type of cable used should be twisted pair, individually

shielded cable with a maximum length of 300m (1000 ft.).

Earth

Module Inputs

Differential Encoder Output Waveforms

The Figure 3.6 shows the different encoder output waveforms. If your

encoder matches these waveforms, the encoder signals can be directly

connected to the associated screw terminals on the module. For

example, the A lead from the encoder is connected to the module’s

A+ screw. If your encoder does not match these waveforms, some

wiring modifications may be necessary. See Appendix B for a

description of these modifications.

Figure 3.6 Differential Encoder Output Waveforms

A

A

B

B

Z

Z

Publication 1746-UM002B-EN-P - August 2004

Page 49

Installation and Wiring 3-9

Single-Ended Encoder Wiring (Open Collector)

Figure 3.7 Single-Ended Encoder Wiring

(1)

VS

GND

(2)

R

A

B

Cable

Allen-Bradley

845H Series

Z

single-ended

encoder

Shield

shield/housing

Connect only if housing is electronically

isolated from the motor and ground.

(1) Refer to your encoder manual for proper cable type. The type of cable used should be twisted-pair, individually

shielded cable with a maximum length of 300m (1000 ft.).

(2) Calculate the value of the pull-up resistor (R), as shown below:

Earth

+VDC

COM

A1(+)

A1(–)

B1(+)

B1(–)

Z1(+)

Z1(–)

Power

Supply

Module Inputs

Vcc Vmin–()

R

For 5V dc jumper position:

For 24V dc jumper position:

--------------------------------------=

Imin

Vcc Vmin–()

R

--------------------------------------1KΩ–

=

Imin

where:R = pull-up resistor value

Vcc = power supply voltage

Vmin = 4.2 V dc

Imin = 6.3 mA

Power Supply Voltage (Vcc) Pull-up Resistor Value (R)

5V dc 127 Ω

12V dc 238 Ω

24V dc 2140 Ω

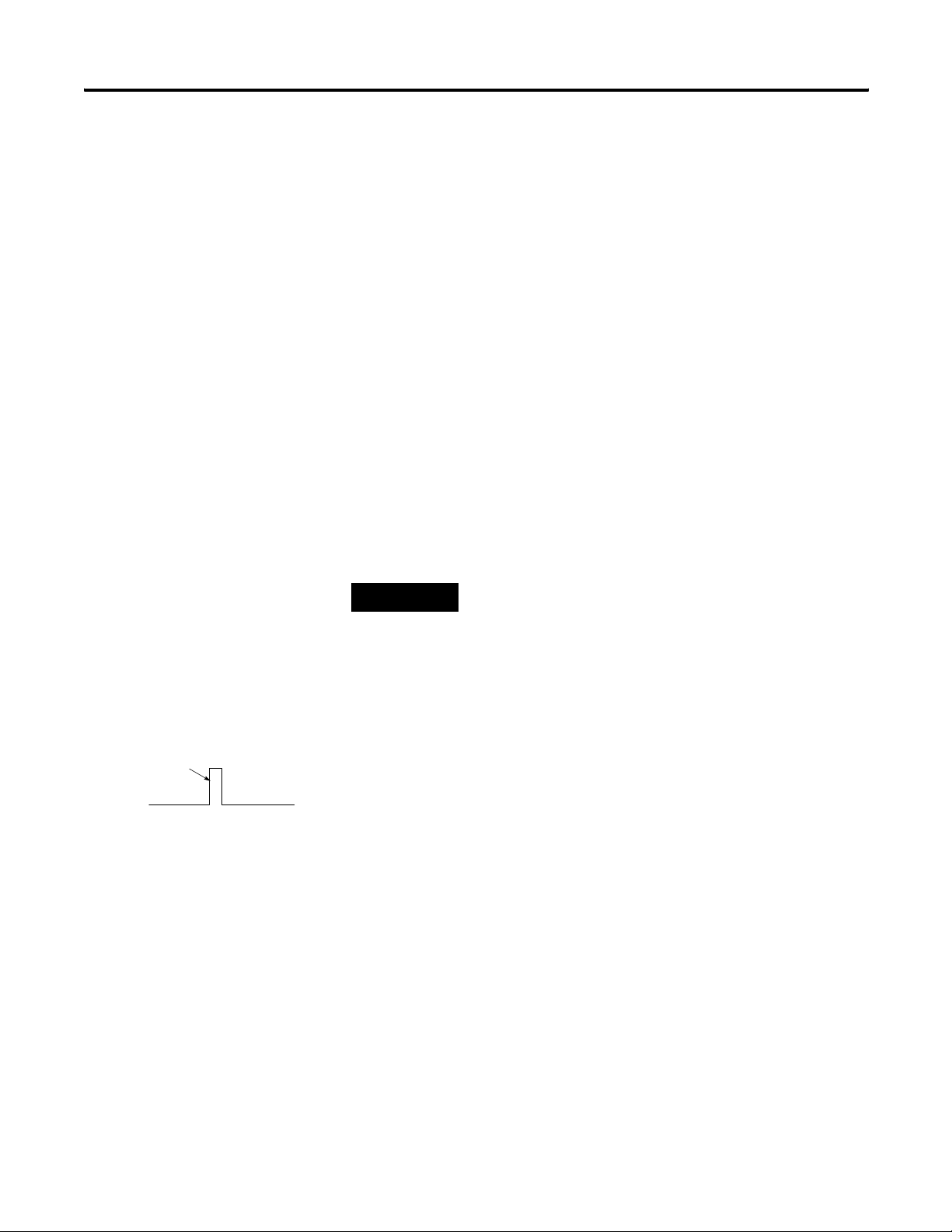

Single-Ended Encoder Output Waveforms

The figure below shows the single-ended encoder output waveforms.

When the waveform is low, the encoder output transistor is on. When

the waveform is high, the encoder output transistor is off.

Figure 3.8 Single-Ended Encoder Output Waveforms

A

B

Z

Publication 1746-UM002B-EN-P - August 2004

Page 50

3-10 Installation and Wiring

Single-Ended Wiring (Discrete Devices)

Figure 3.9 Discrete Device Wiring

Proximity Sensor

VS

OUT

COM

VS

OUT

COM

Photo-electric Sensor

with Open Collector

Sinking Output

VS

OUT

COM

Solid-State

Switch

(1)

R

+VDC

COM

A1(+)

A1(–)

B1(+)

B1(–)

Z1(+)

Z1(–)

Power

Supply

Module Inputs

(1) Calculate the value of the pull-up resistor (R), as shown below:

Vcc Vmin–()

R

For 5V dc jumper position:

For 24V dc jumper position:

--------------------------------------=

Imin

Vcc Vmin–()

R

--------------------------------------1KΩ–

=

Imin

where:R = pull-up resistor value

Vcc = power supply voltage

Vmin = 4.2 V dc

Imin = 6.3 mA

Power Supply Voltage (Vcc) Pull-up Resistor Value (R)

5V dc 127 Ω

12V dc 238 Ω

24V dc 2140 Ω

Publication 1746-UM002B-EN-P - August 2004

Page 51

Configuration and Programming

This chapter provides information about:

• selecting operating class

• module programming

• programming blocks

• programming block default values

Chapter

4

Selecting Operating Class

Power-up Reset

Module Programming

The 1746-HSCE2 module has two operating classes which are

determined by the ID code used by the module.

Class 1 operation uses 8 input and 8 output words and is compatible

with SLC 5/01 and above processors and the 1747-ASB module. Enter

ID Code 3511 to select Class 1 operation.

Class 4 operation uses 23 input and 8 output words and is compatible

with SLC 5/03 and above processors and with 1747-ACN15 and

-ACNR15 modules. Enter ID Code 15912 to select Class 4 operation.

See Operating Class on page 1-4 for more information on Class 1 and

Class 4 operation.

Whenever power is cycled or the processor mode is switched to RUN,

all counters are reset to their defaults. The counters, ranges, presets,

etc., need to be reprogrammed. See the default settings on page 4-28.

Module programming consists of the following six blocks:

• Module Setup

• Counter Configuration

• Minimum/Maximum Count Value

• Minimum/Maximum Rate Value

• Program Ranges

• Counter Control

1 Publication 1746-UM002B-EN-P - August 2004

Page 52

4-2 Configuration and Programming

Each block is made up of eight words. The first word is the control

word. The remaining seven words are data words. The control word

determines which parameters are in the data words. This

programming method applies to both classes of operation. The

programming blocks are described on pages 4-6 through 4-23.

Programming Cycle

Except for the Counter Control Block, all programming blocks are

written to the module with a programming cycle. Programming cycles

are controlled by the transmit and acknowledge bits.

A programming cycle consists of six steps.

1. Write the new data into the correct output image table words.

The lower byte of each configuration block indicates which

block is being transferred. See the programming block

descriptions on pages 4-6 to 4-28.

2. Each block that can be altered has a Transmit bit (O:e.0/15). Set

the Transmit bit in the output image table. The 1746-HSCE2 will

not act on the new programming block until the Transmit bit is

set.

3. Once the Transmit bit is set, an Acknowledge bit (I:e.0/15) is

received.

4. When the ladder logic detects that the Acknowledge bit is set, it

should check for errors. Error bits are only valid when the

Acknowledge bit is set. The error bits are the PERR bit (I:e.0/13)

and the MFLT bit (I:e.0/14).

5. If either bit is set, the programming block is rejected. The block

pointer is not incremented and initialization fails.

If neither error bit is set, the block pointer is incremented and

the Transmit bit is reset, allowing the module to transfer the next

block.

6. Once the desired configurable blocks have been transferred to

the module and the Maximum Block Address is recognized, the

Counter Control Block is transferred to the output image table to

enable the counters.

Publication 1746-UM002B-EN-P - August 2004

Page 53

Configuration and Programming 4-3

Data Format

In Class 4, the counter accepts rate data in either integer or

floating-point data formats, depending upon the setting of the rate

value bit. Both formats are explained below.

TIP

Count values are always in integer format. The

format of rate values is selected in the Module Setup

Block as either integer or floating-point formats. All

other data is in integer format.

Integer Format

In integer format, two words may be needed to hold each data value

because the values can exceed ±32768 (decimal) when the module is

in Class 4 operation. The combined decimal value of both words is

calculated as follows:

actual value = (value of first word x 1000) + value of second word

Both word values must have the same sign or a programming error

results. If the value is positive, both words must be positive. If the

value is negative, both words must be negative.

TIP

A value of zero in either word may be paired with

either sign in the other word.

The following example illustrates how numbers are represented in

integer format.

Table 4.1 Integer Format Example

First Word Second Word Data

12 345 12,345

-12 -345 -12,345

12 0 12,000

-12 0 -12,000

Floating-Point Format

Floating-point notation (IEEE 754 single-precision used) is difficult to

read and use, but may be simplified by using programming software

to view and use the data in a floating-point file.

Publication 1746-UM002B-EN-P - August 2004

Page 54

4-4 Configuration and Programming

Reading the Data

In the following example, the 1746-HSCE2 module is located in slot 3.

The rate value, in floating point rate value format, is located in input

data file words 4 and 5 (I:3.4 and I:3.5). To view the rate value for

counter 1, use the copy instruction as shown below.

COP

Copy File

Source #I:3.4

Dest #F8:1

Length 1

The source is the input data file, and the destination is the floating

point file. The length is 1, the number of elements of the destination

file in the COP instruction.

Writing the Data

In the following example the floating point value is copied into

integer words 1 and 2 of the Minimum/Maximum Rate Value

programming block (N10:0-7). The 1746-HSCE2 module is located in

slot 3.

COP

Copy File

Source #F8:1

Dest N10:1

Length 2