NEC NP84N04EHE, NP84N04KHE, NP84N04CHE, NP84N04DHE, NP84N04MHE Technical data

...

NP84N04CHE

DATA SHEET

MOS FIELD EFFECT TRANSISTOR

NP84N04EHE, NP84N04KHE

NP84N04CHE, NP84N04DHE, NP84N04MHE, NP84N04NHE

SWITCHING

N-CHANNEL POWER MOS FET

DESCRIPTION

These products are N-channel MOS Field Effect Transistors designed for high current switching applications.

<R> ORDERING INFORMATION

PART NUMBER |

LEAD PLATING |

PACKING |

|

PACKAGE |

|

NP84N04EHE-E1-AY Note1, 2 |

|

|

TO-263 (MP-25ZJ) typ. 1.4 g |

||

NP84N04EHE-E2-AY Note1, 2 |

Pure Sn (Tin) |

Tape 800 p/reel |

|||

|

|

||||

NP84N04KHE-E1-AY Note1 |

TO-263 (MP-25ZK) typ. 1.5 g |

||||

|

|

||||

NP84N04KHE-E2-AY Note1 |

|

|

|||

|

|

|

|

||

NP84N04CHE-S12-AZ Note1, 2 |

Sn-Ag-Cu |

|

TO-220 |

(MP-25) typ. 1.9 g |

|

NP84N04DHE-S12-AY Note1, 2 |

|

Tube 50 p/tube |

TO-262 |

(MP-25 Fin Cut) typ. 1.8 g |

|

NP84N04MHE-S18-AY Note1 |

Pure Sn (Tin) |

TO-220 |

(MP-25K) typ. 1.9 g |

||

|

|||||

NP84N04NHE-S18-AY Note1 |

|

|

TO-262 |

(MP-25SK) typ. 1.8 g |

|

Notes 1. Pb-free (This product does not contain Pb in the external electrode.)

(TO-220)

2. Not for new design

FEATURES

• Channel temperature 175 degree rated |

|

• Super low on-state resistance |

|

RDS(on) = 5.2 mΩ MAX. (VGS = 10 V, ID = 42 A) |

|

• Low input capacitance |

(TO-262) |

Ciss = 4410 pF TYP. |

|

• Built-in gate protection diode |

|

(TO-263)

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

Document No. D14240EJ7V0DS00 (7th edition) |

|

1999, 2000, 2007 |

|

||

Date Published October 2007 NS |

|

|

Printed in Japan

The mark <R> shows major revised points.

The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field.

NP84N04EHE,NP84N04KHE,NP84N04CHE, NP84N04DHE, NP84N04MHE,NP84N04NHE

ABSOLUTE MAXIMUM RATINGS (TA = 25°C)

Drain to Source Voltage (VGS = 0 V) |

VDSS |

40 |

V |

Gate to Source Voltage (VDS = 0 V) |

VGSS |

±20 |

V |

Drain Current (DC) (TC = 25°C) Note1 |

ID(DC) |

±84 |

A |

Drain Current (Pulse) Note2 |

ID(pulse) |

±336 |

A |

Total Power Dissipation (TC = 25°C) |

PT |

200 |

W |

Total Power Dissipation (TA = 25°C) |

PT |

1.8 |

W |

Channel Temperature |

Tch |

175 |

°C |

Storage Temperature |

Tstg |

−55 to +175 |

°C |

Single Avalanche Current Note3 |

IAS |

84/61/22 |

A |

Single Avalanche Energy Note3 |

EAS |

70/372/484 |

mJ |

Notes 1. Calculated constant current according to MAX. allowable channel temperature.

2.PW ≤ 10 μs, Duty cycle ≤ 1%

3.Starting Tch = 25°C, VDD = 20 V, RG = 25 Ω, VGS = 20 → 0 V (see Figure 4.)

THERMAL RESISTANCE

Channel to Case Thermal Resistance |

Rth(ch-C) |

0.75 |

°C/W |

Channel to Ambient Thermal Resistance |

Rth(ch-A) |

83.3 |

°C/W |

2 |

Data Sheet D14240EJ7V0DS |

NP84N04EHE,NP84N04KHE,NP84N04CHE, NP84N04DHE, NP84N04MHE,NP84N04NHE

ELECTRICAL CHARACTERISTICS (TA = 25°C) |

|

|

|

|

|

|

|

|||

CHARACTERISTICS |

SYMBOL |

TEST CONDITIONS |

|

MIN. |

TYP. |

MAX. |

UNIT |

|||

Zero Gate Voltage Drain Current |

IDSS |

VDS = 40 V, VGS = 0 V |

|

|

|

10 |

μA |

|||

Gate Leakage Current |

|

IGSS |

VGS = ±20 V, VDS = 0 V |

|

|

|

±10 |

μA |

||

Gate to Source Threshold Voltage |

VGS(th) |

VDS = VGS, ID = 250 μA |

|

2.0 |

3.0 |

4.0 |

V |

|||

Forward Transfer Admittance |

| yfs | |

VDS = 10 V, ID = 42 A |

|

20 |

47 |

|

|

S |

||

Drain to Source On-state Resistance |

RDS(on) |

VGS = 10 V, ID = 42 A |

|

|

4.6 |

5.2 |

mΩ |

|||

Input Capacitance |

|

Ciss |

VDS = 25 V, |

|

|

|

4410 |

6620 |

pF |

|

Output Capacitance |

|

Coss |

VGS = 0 V, |

|

|

|

950 |

1430 |

pF |

|

|

|

|

|

|

||||||

Reverse Transfer Capacitance |

Crss |

f = 1 MHz |

|

|

|

490 |

890 |

pF |

||

|

|

|

|

|||||||

Turn-on Delay Time |

|

td(on) |

VDD = 20 V, ID = 42 A, |

|

|

36 |

79 |

ns |

||

Rise Time |

|

tr |

VGS = 10 V, |

|

|

|

25 |

62 |

ns |

|

|

|

|

|

|

||||||

Turn-off Delay Time |

|

td(off) |

RG = 1 Ω |

|

|

|

77 |

150 |

ns |

|

|

|

|

|

|

||||||

Fall Time |

|

tf |

|

|

|

|

28 |

69 |

ns |

|

Total Gate Charge |

|

QG |

VDD = 32 V, |

|

|

|

87 |

130 |

nC |

|

Gate to Source Charge |

|

QGS |

VGS = 10 V, |

|

|

|

20 |

|

|

nC |

|

|

|

|

|

|

|

||||

Gate to Drain Charge |

|

QGD |

ID = 84 A |

|

|

|

32 |

|

|

nC |

|

|

|

|

|

|

|

||||

Body Diode Forward Voltage |

VF(S-D) |

IF = 84 A, VGS = 0 V |

|

|

1.0 |

|

|

V |

||

Reverse Recovery Time |

trr |

IF = 84 A, VGS = 0 V, |

|

|

49 |

|

|

ns |

||

Reverse Recovery Charge |

Qrr |

di/dt = 100 A/μs |

|

|

|

60 |

|

|

nC |

|

|

|

|

|

|

|

|||||

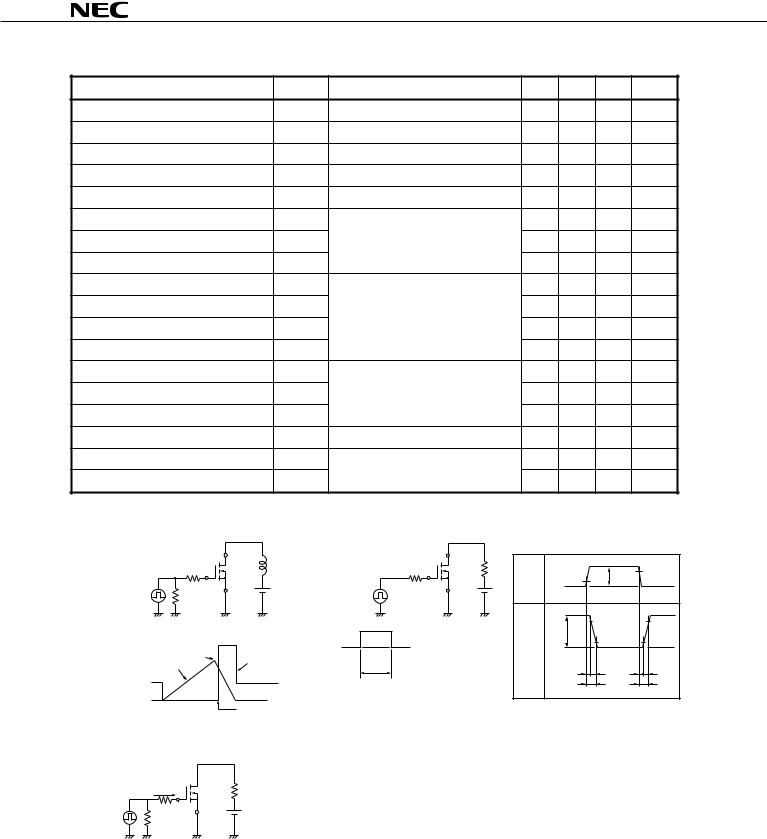

TEST CIRCUIT 1 AVALANCHE CAPABILITY |

TEST CIRCUIT 2 SWITCHING TIME |

|

|

|

|

|||||

|

D.U.T. |

L |

|

D.U.T. |

|

VGS |

|

|

|

|

RG = 25 Ω |

|

|

RL |

|

|

|

||||

|

|

VGS |

|

|

|

90 % |

||||

|

|

|

10 % |

VGS |

||||||

|

|

|

|

|

|

|

||||

|

|

|

|

RG |

|

Wave Form |

|

|

|

|

PG. |

50 Ω |

VDD |

PG. |

|

|

0 |

|

|

|

|

|

VDD |

|

|

|

|

|

||||

VGS = 20 → 0 V |

|

|

VDS |

|

|

|

||||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

90 % |

|

|

90 % |

|

BVDSS |

|

VGS |

|

|

|

VDS |

10 % |

10 % |

|

|

|

0 |

|

|

VDS |

0 |

|

|||

|

IAS |

|

|

|

|

|

|

|||

ID |

VDS |

τ |

|

|

Wave Form |

|

|

|

|

|

|

|

|

|

td(on) |

tr |

td(off) |

tf |

|||

VDD |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

τ = 1 μ s |

|

|

|

ton |

|

|

toff |

|

Starting Tch |

Duty Cycle ≤ 1 % |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

TEST CIRCUIT 3 GATE CHARGE

D.U.T.

|

IG = 2 mA |

RL |

|

|

|

|

|

PG. |

50 |

Ω |

VDD |

|

|||

Data Sheet D14240EJ7V0DS |

3 |

Loading...

Loading...