Denon DN-V750, DN-V755 Service Manual

For U.S.A., Canada

& Europe model

SERVICE MANUAL

MODEL DN-V750/V755

NETWORK AUDIO VIDEO PLAYER

Ver. 2

●

For purposes of improvement, specifications and

design are subject to change without notice.

●

Please use this service manual with referring to the

operating instructions without fail.

●

Some illustrations using in this service manual are

slightly different from the actual set.

注 意

サービスをおこなう前に、このサービスマニュアルを

必ずお読みください。本機は、火災、感電、けがなど

に対する安全性を確保するために、さまざまな配慮を

おこなっており、また法的には「電気用品安全法」に

もとづき、所定の許可を得て製造されております。

従ってサービスをおこなう際は、これらの安全性が維

持されるよう、このサービスマニュアルに記載されて

いる注意事項を必ずお守りください。

●

本機の仕様は性能改良のため、予告なく変更すること

があります。

●

補修用性能部品の保有期間は、製造打切後8年です。

●

修理の際は、必ず取扱説明書を参照の上、作業を行っ

てください。

●

本文中に使用しているイラストは、説明の都合上現物

と多少異なる場合があります。

Professional business company

JAPAN

X0221V.02 DE/CDM 0412

DN-V750/V755

SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

LEAKAGE CURRENT CHECK

Before returning the unit to the customer, make sure you make either (1) a leakage current check or (2) a line to chassis

resistance check. If the leakage current exceeds 0.5 milliamps, or if the resistance from chassis to either side of the

power cord is less than 460 kohms, the unit is defective.

LASER RADIATION

Do not stare into beam or view directly with optical instruments, class 3A laser product.

500V

(1)

(2)

1M

(1)

(2)

2

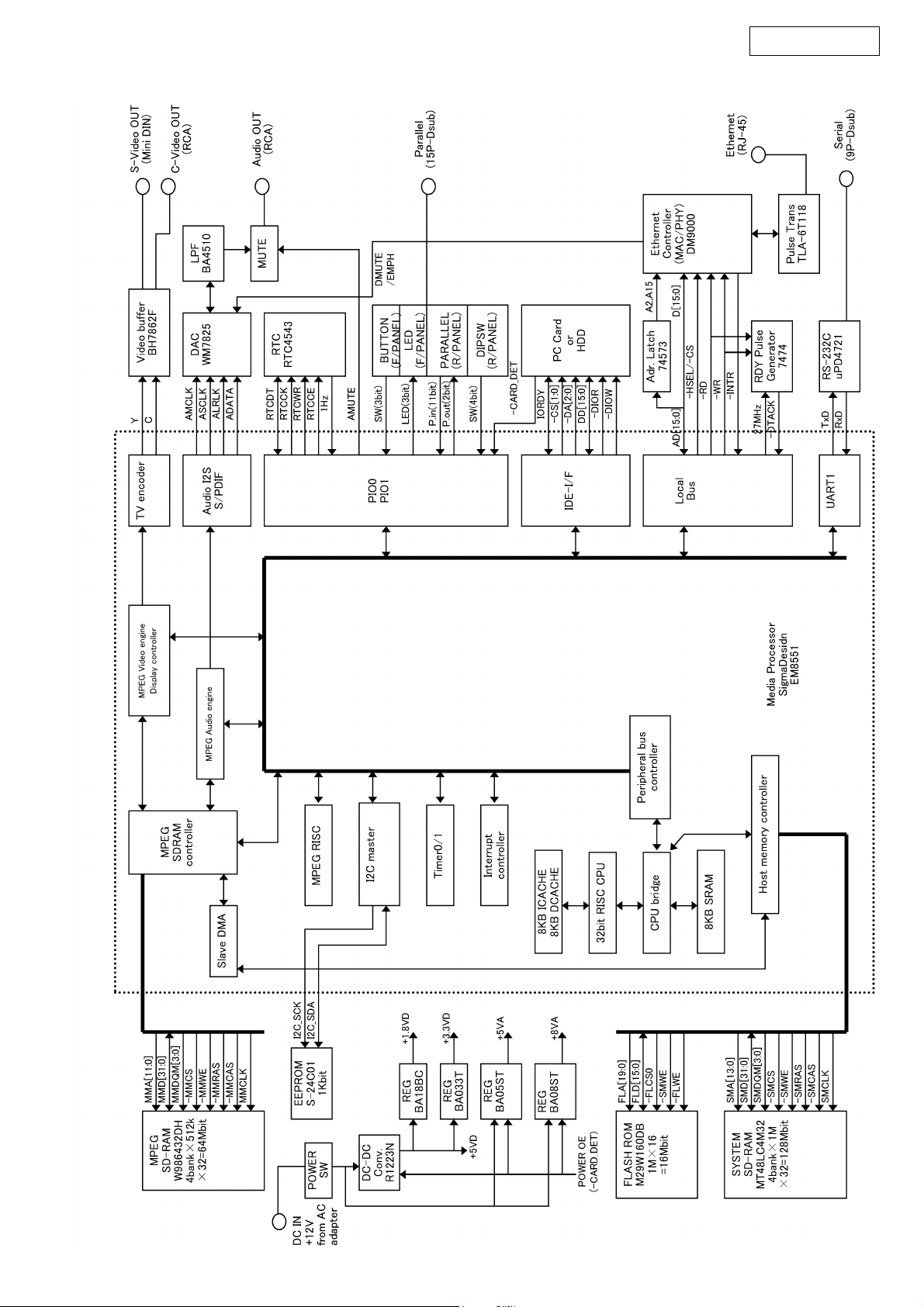

BLOCK DIAGRAM

DN-V750/V755

3

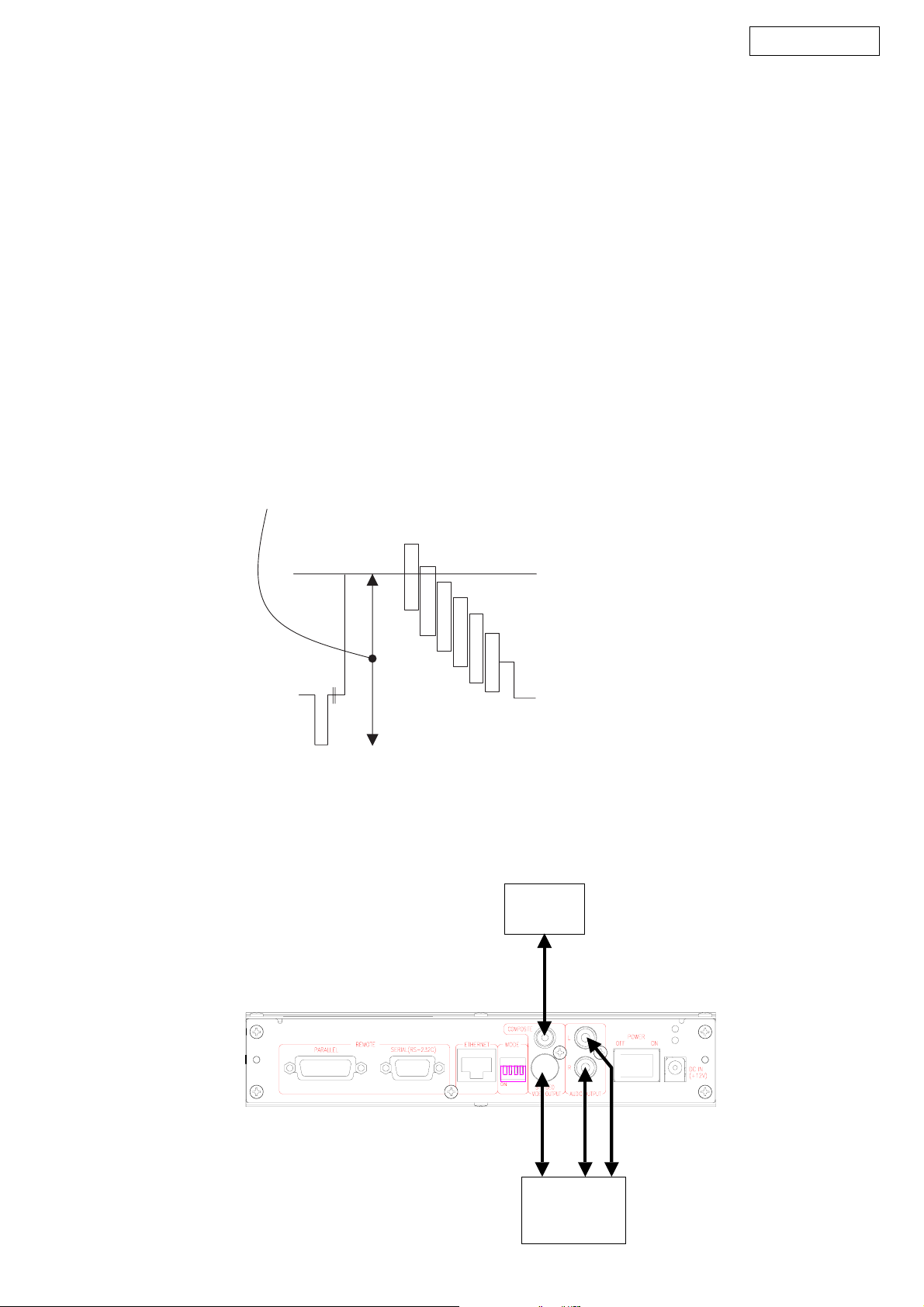

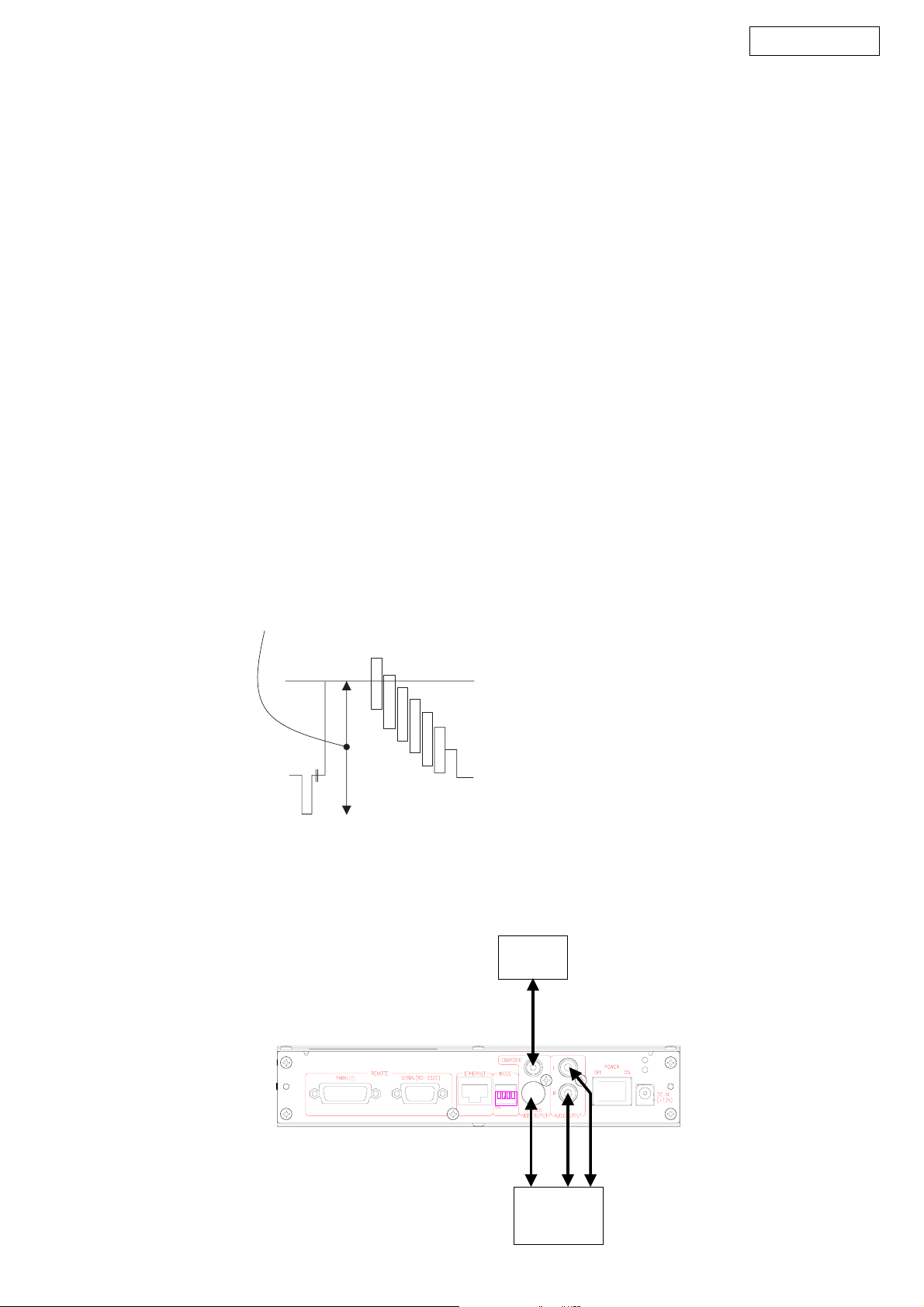

ADJUSTMENT (for DN-V750 model)

1. Connect the terminal as shown fig. 1.

2. Set the CF card (CF-96-27=adjustment 2) to CARD SLOT.

3. Turn OFF the 1 and 2 Dip switch on the back panel.

4. Turn the power switch ON.

5. VIDEO mode

(1) Press the "SELECT" button about for 2 second.

(2) Until the display appear at the upper right of a monitor.

(3) Set "VIDEO", "AUDIO", "PICTURE", "SCRIPT" to "VIDEO".

6. Display "Color bar".

(1) Press the "STOP" button, pressing the "SELECT" button.

(2) Until the display appear at the upper right of a monitor.

(3) Press the "STOP" button to 1, pressing the "SELECT" button.

(4) Press the "PLAY" button and quickly press the "PAUSE" button.

Display "Color bar" with a still picture.

7. Adjusting the output of Composite.

Adjust "980mVP-P ± 40mVP-P" by VR101.

DN-V750/V755

8. Turn the power switch OFF.

Oscilloscope

Monitor

fig.1

4

ADJUSTMENT (for DN-V755 model)

1. Connect the terminal as shown fig. 1.

2. Set to the IDE→CF conversion P.W.B.

(1) Extract the IDE cable of HDD from the main P.W.B.

(2) Extract the power cable of HDD from the HDD.

→

(3) Insert the IDE cable of IDE

(4) The power cable of IDE→CF conversion P.W.B. connect to the power cable of HDD.

(5) Set the CF card (CF-96-27=adjustment 2) to IDE→CF conversion P.W.B.

3. Turn OFF the 1 and 2 Dip switch on the back panel.

4. Turn the power switch ON.

5. VIDEO mode

(1) Press the "SELECT" button about for 2 second.

(2) Until the display appear at the upper right of a monitor.

(3) Set "VIDEO", "AUDIO", "PICTURE", "SCRIPT" to "VIDEO".

6. Display "Color bar".

(1) Press the "STOP" button, pressing the "SELECT" button.

(2) Until the display appear at the upper right of a monitor.

(3) Press the "STOP" button to 1, pressing the "SELECT" button.

(4) Press the "PLAY" button and quickly press the "PAUSE" button.

Display "Color bar" with a still picture.

7. Adjusting the output of Composite.

Adjust "980mVP-P ± 40mVP-P" by VR101.

CF conversion P.W.B. to the main P.W.B.

DN-V750/V755

8. Turn the power switch OFF.

5

Oscilloscope

Monitor

fig.1

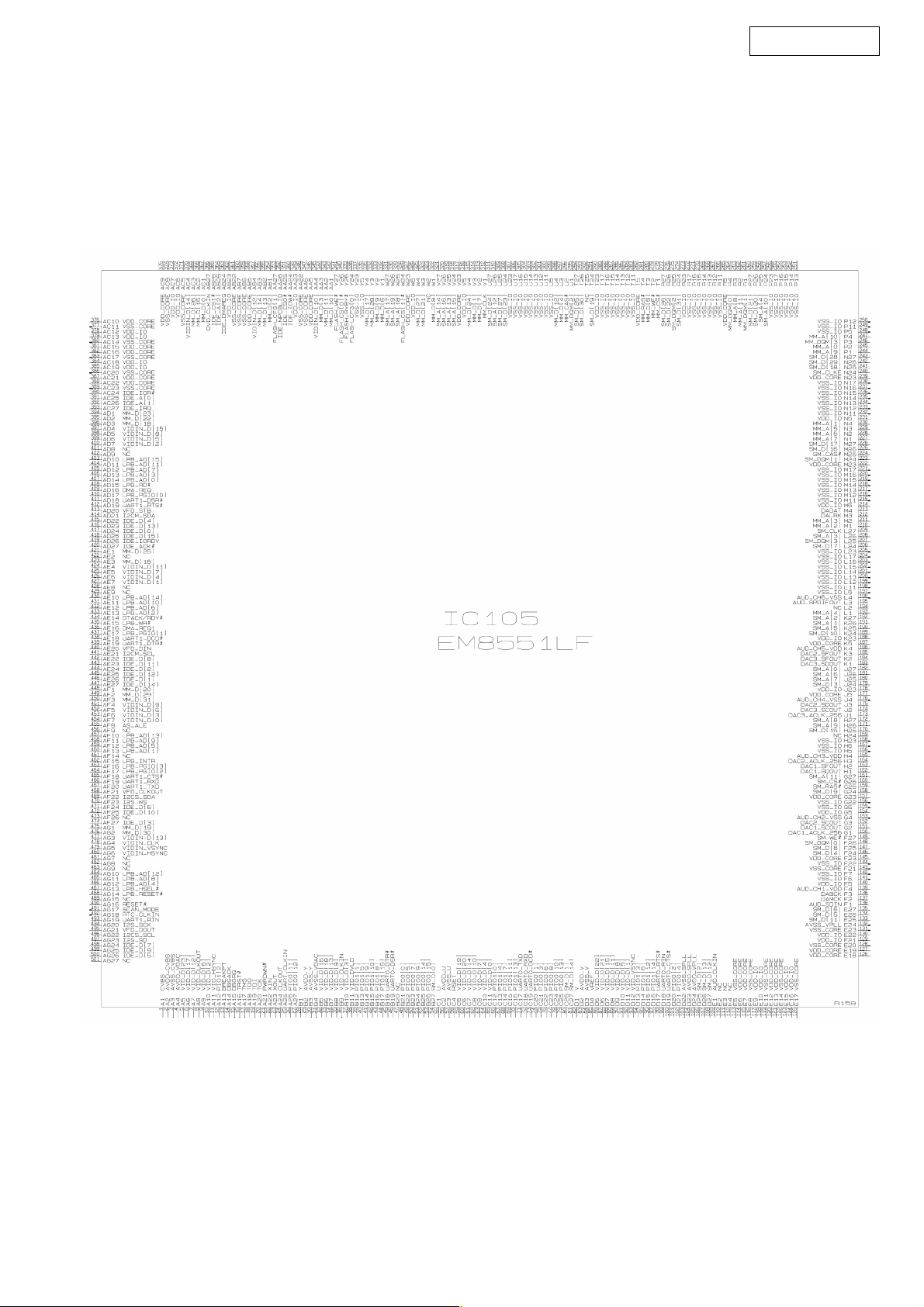

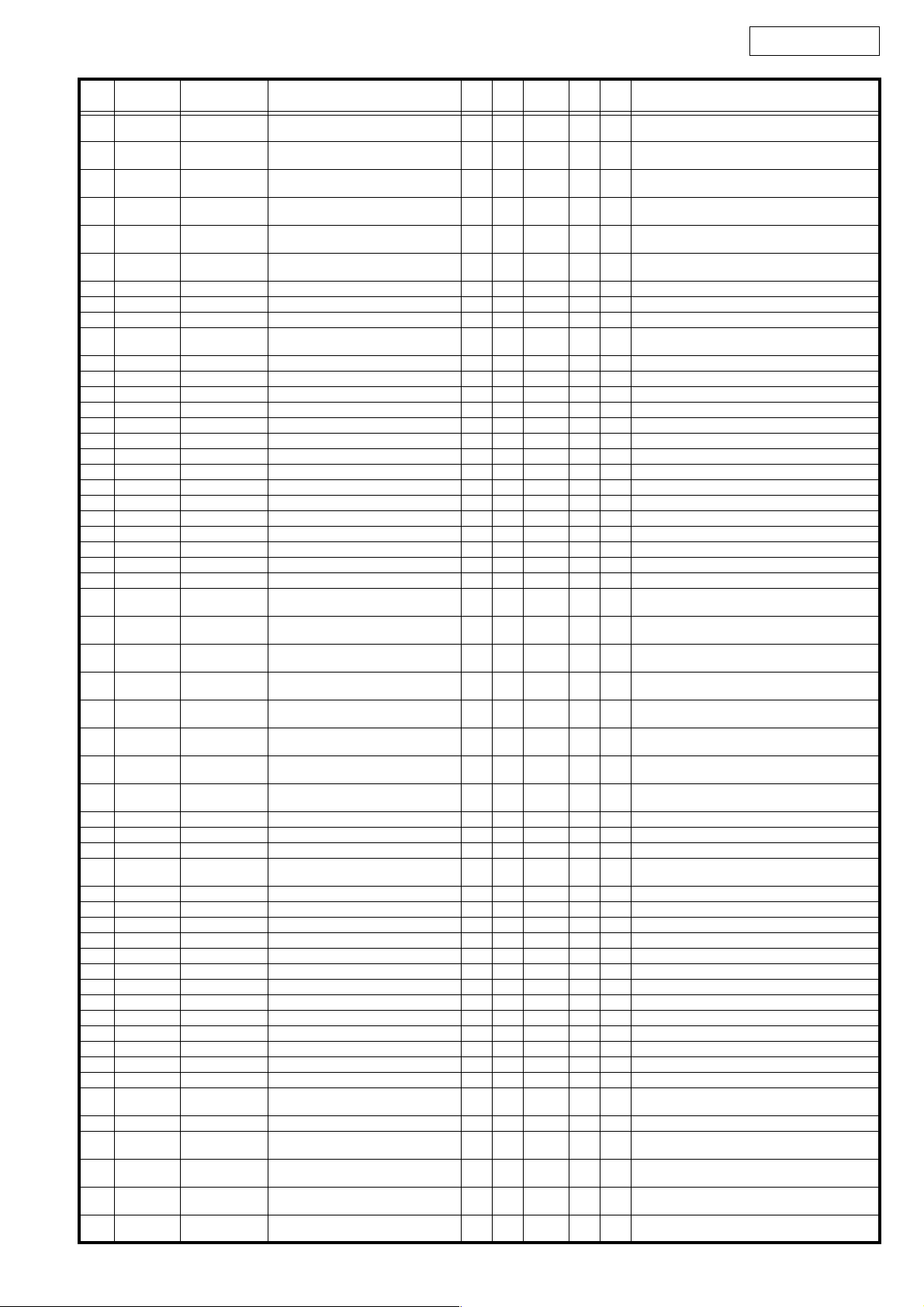

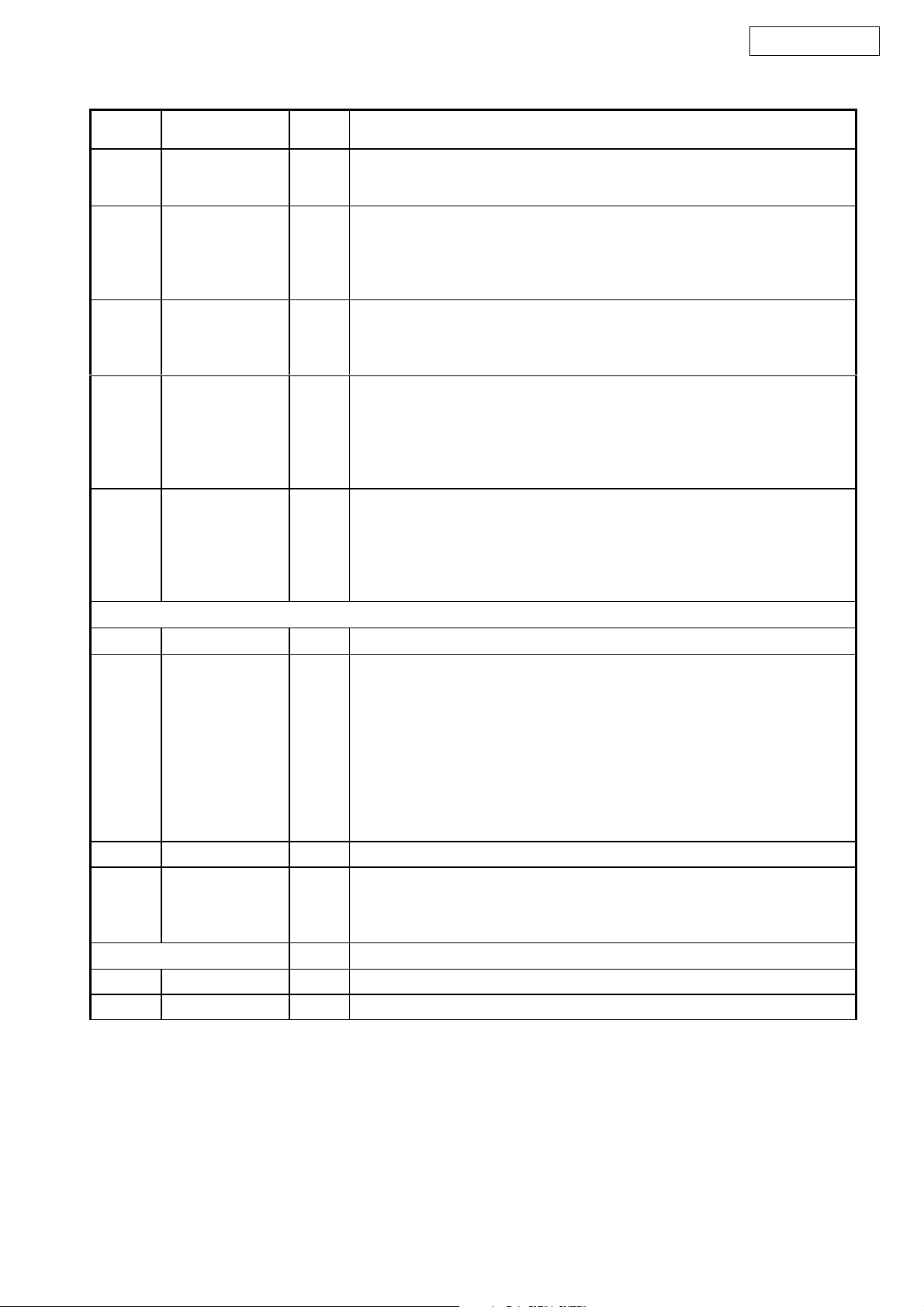

SEMICONDUCTORS

Only major semiconductors are shown, general semiconductors etc. are omitted to list.

主な半導体を記載しています。汎用の半導体は記載を省略しています。

1. IC’s

EM8551B (IC105)

DN-V750/V755

6

DN-V750/V755

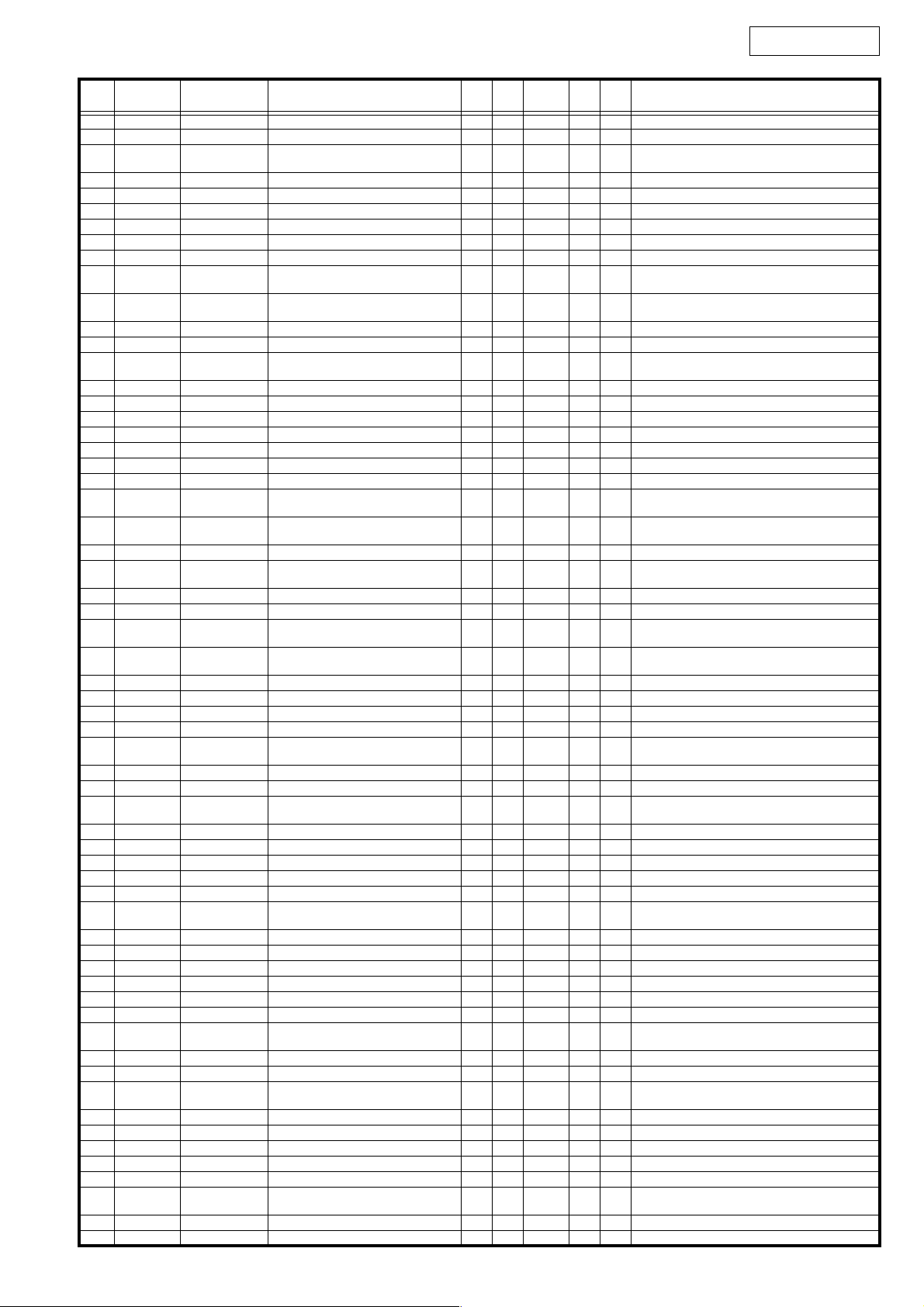

EM8551B Terminal Function

Pin

Port Name Symbol Description I/O Det Ext Res Ini Function

No.

1 A1 CVBS Analog Video Output CVBS O - - - - Ext video buffer(BH7862) ganerates composite

2 A2 AVDD_CVBS VDD3_3CVBS - - - - - Connect to 3.3V_A(for Video DAC)

3 A3 AVSS_CVBS VSS_CVBS - - - - - Connect to GND_A(for Video DAC)

4 A4 AVDD_VDAC VDD3_3DAC - - - - - Connect to 3.3V_A(for Video DAC)

5 A5 VID_D[23] - (O) - - - - Not used

6 A6 VID_D[17] - (O) - - - - Not used

7 A7 VID_D[12] Video Output:C[4] (O) - - - - Not used

8 A8 VID_CLKOUT Video Output:Video(Pixel) clock out (O) - - - - Not used

9 A9 VID_D[6] Video Output:Y[6] (O) - - - - Not used

10 A10 VID_D[2] Video Output:Y[2] (O) - - - - Not used

11 A11 VID_HSYNC Video Output Horizontal sync (O) - - - - Not used

12 A12 PIO1[2] Programmable I/O Port 1 Bit 2 I Lev Pu H H L:Active

13 A13 BREAKPT DEBUG IF:Breakpoint I - GND L L Connect to GND_D

14 A14 DBGACK DEBUG IF:Debug Acknowledge O - - - - Not used

15 A15 DBGRQ DEBUG IF:Debug Request I - GND L L Not used

16 A16 TRST# JTAG:Test Reset I - GND L L Not used

17 A17 TMS JTAG:Test Mode Select I - GND L L Not used

18 A18 TDO JTAG:Test Data Output O - - - - Not used

19 A19 TDI JTAG:Test Data Input I - GND L L Not used

20 A20 TCK JTAG:Test Clock Input I - A24 - - Connect to 27M(A24[24])

21 A21 PWRDWN# PowerDown/PLL Enable - - 3.3V_D H H Connect to 3.3V_D(PLL Enable)

22 A22 XIN 27MHz crystal oscillator input I - - - - Connect to X'tal for system clock

23 A23 XOUT 27MHz crystal oscillator output O - - - - Connect to X'tal for system clock

24 A24 CLKOUT 27MHz internal Oscillator

25 A25 UART_CLKIN Receive Clock for UART 0 and 1 (I) - intPd - - Not used

26 A26 PIO0[11] Programmable I/O Port 0 Bit 11 I Lev Pu H/L H/L L:Active

27 A27 PIO0[12] Programmable I/O Port 0 Bit 12 I Lev Pu H/L H/L L:Active

28 B1 Y Analog video output Y O - - - - Connect to video buffer(BH7862:YIN and PYIN)

29 B2 AVDD_Y VDD3_3Y - - - - - Connect to 3.3V_A(for Video DAC)

30 B3 AVSS_Y VSS_Y - - - - - Connect to GND_A(for Video DAC)

31 B4 AVSS_VDAC VSS_DAC - - - - - Connect to GND_A(for Video DAC)

32 B5 VID_D[16] - (O) - - - - Not used

33 B6 VID_D[18] - (O) - - - - Not used

34 B7 VID_D[13] Video Output:C[5] (O) - - - - Not used

35 B8 VID_D[9] Video Output:C[1] (O) - - - - Not used

36 B9 VID_CLKIN Video Output:Video Clock In - - - - 37 B10 VID_D[3] Video Output:Y[3] (O) - - - - Not used

38 B11 VID_DVLD Video Output:Video active/Video valid (O) - - - - Not used

39 B12 PIO1[1] Programmable I/O Port 1 Bit 1 I Lev Pu H/L H/L L:Active

40 B13 PIO1[5] Programmable I/O Port 1 Bit 5 O - Pd L L H:Active

41 B14 PIO1[9] Programmable I/O Port 1 Bit 9 O - - H H for Ethernet(DM9000) H:Active

42 B15 PIO1[10] Programmable I/O Port 1 Bit 10 O - Pu H H for IDE/PC card L:Active

43 B16 PIO1[8] Programmable I/O Port 1 Bit 8 O - Pd L L L:Active(mute on)/H:Mute off

44 B17 PIO1[15] Programmable I/O Port 1 Bit 15 O - - - - Control signal for rtc(RTC4543)

45 B18 UART0_DTR# UART0:Data Terminal Ready (O) - - - - Not used

46 B19 UART0_DSR# UART0:Data Set Ready (I) - intPd - - Not used

47 B20 NC - - - - - Not used

48 B21 PIO0[0] Programmable I/O Port 0 Bit 0 I Lev Pu H/L H/L L:Time set mode/H:Normal mode

49 B22 PIO0[5] Programmable I/O Port 0 Bit 5 I Lev Pu H/L H/L L:Active

50 B23 PIO0[7] Programmable I/O Port 0 Bit 7 I Ed Pu H/L H/L H to L:Pc card inserted/L to H:Pc card ejected

51 B24 PIO0[9] Programmable I/O Port 0 Bit 9 I Lev Pu H/L H/L L:Active

52 B25 PIO0[14] Programmable I/O Port 0 Bit 14 I Lev Pu H/L H/L L:Active

53 B26 PIO0[15] Programmable I/O Port 0 Bit 15 I Lev Pu H/L H/L L:Active

54 B27 SM_D[0] System Memory Data Bit0 I/O - - - - Connect to system sdram(D0) and flash chip(D0)

55 C1 U Analog Video output U O - - - - Connect to video buffer(BH7862:PBIN)

56 C2 AVDD_U VDD3_3_U - - - - - Connect to 3.3V_A(for Video DAC)

57 C3 AVSS_U VSS U - - - - - Connect to GND_A(for Video DAC)

58 C4 RSET - - - - - - 200ohm terminated(single termination)

59 C5 VID_D[19] - (O) - - - - Not used

60 C6 VID_D[20] - (O) - - - - Not used

61 C7 VID_D[14] Video Output:C[6] (O) - - - - Not used

62 C8 VID_D[10] Video Output:C[2] (O) - - - - Not used

63 C9 VID_D[7] Video Output:Y[7] (O) - - - - Not used

64 C10 VID_D[4] Video Output:Y[4] (O) - - - - Not used

65 C11 VID_D[0] Video Output:Y[0] (O) - - - - Not used

66 C12 PIO1[0] Programmable I/O Port 1 Bit 0 I Lev Pu H/L H/L L:Active

67 C13 PIO1[4] Programmable I/O Port 1 Bit 4 O - Pd L L H:Active

68 C14 PIO1[7] Programmable I/O Port 1 Bit 7 O - Pd L L H:Active

69 C15 PIO1[11] Programmable I/O Port 1 Bit 11 I - - H/L H/L Connect to RTC 1Hz output

output(bufferd)

O - - - - 27M clock is used for -DTACK/RDY signal

video.

generating.

7

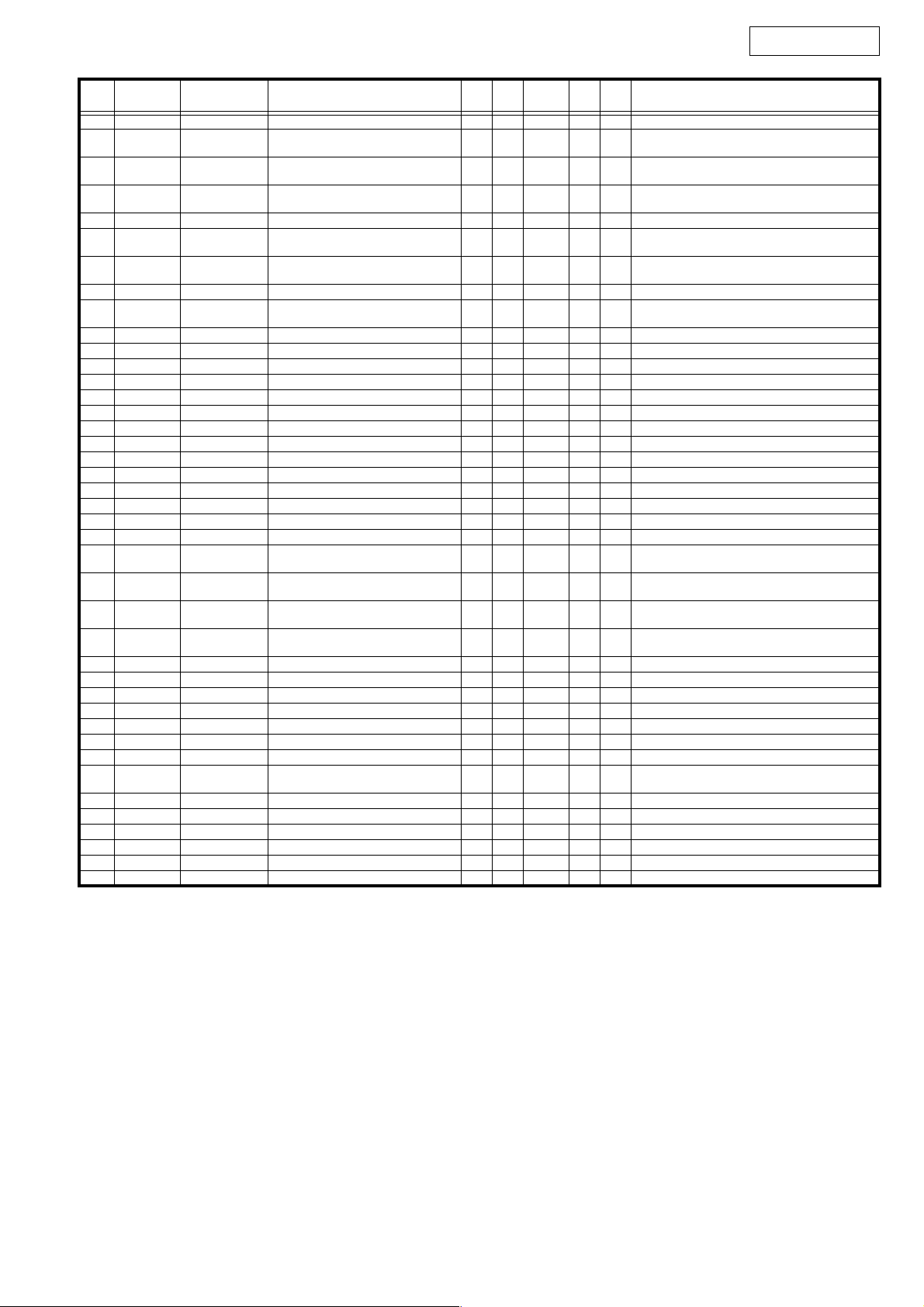

DN-V750/V755

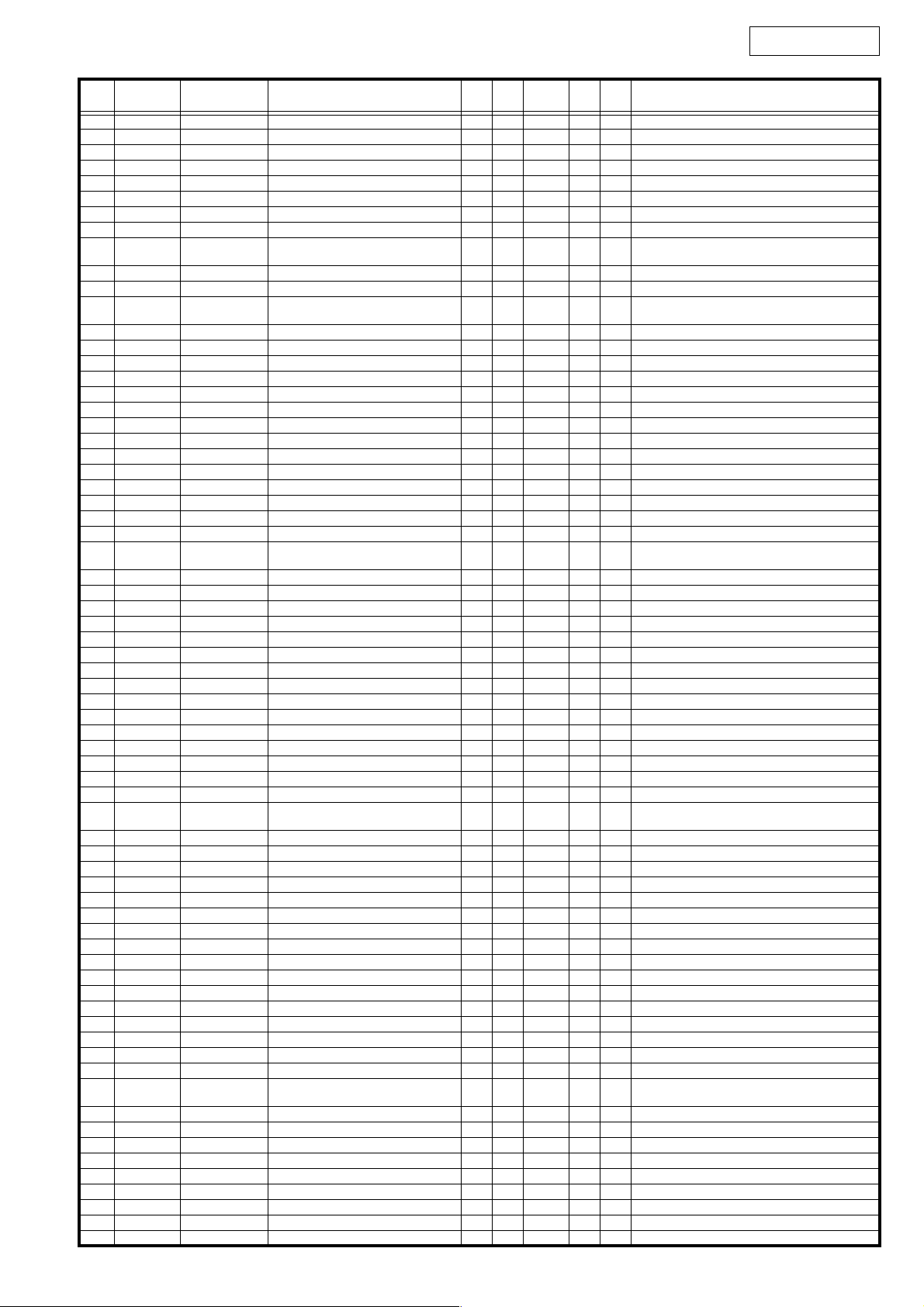

Pin

Port Name Symbol Description I/O Det Ext Res Ini Function

No.

70 C16 PIO1[13] Programmable I/O Port 1 Bit 13 O - Pd - - Control signal for rtc(RTC4543) L:disable/

71 C17 UART0_TXD UART0:Transmit Data O - - - - Not used

72 C18 UART0_RXD UART0:Receive Data I - intPd - - Not used

73 C19 UART0_DCD# UART0:Data Carriar Detect (I) - intPd - - Not used

74 C20 PIO0[1] Programmable I/O Port 0 Bit 1 I Lev Pu H/L H/L L:Pioneer LD compatible mode/H:Normal mode

75 C21 PIO0[3] Programmable I/O Port 0 Bit 3 I Lev Pu H/L H/L Reserved

76 C22 PIO0[6] Programmable I/O Port 0 Bit 6 I Lev Pu H/L H/L L:Active

77 C23 PIO0[8] Programmable I/O Port 0 Bit 8 I Lev Pu H/L H/L L:Active

78 C24 PIO0[10] Programmable I/O Port 0 Bit 10 I Lev Pu H/L H/L L:Active

79 C25 PIO0[13] Programmable I/O Port 0 Bit 13 I Lev Pu H/L H/L L:Active

80 C26 SM_D[1] System Memory Data Bit1 I/O - - - - Connect to system sdram(D1) and flash chip(D1)

81 C27 SM_D[14] System Memory Data Bit14 I/O - - - - Connect to system sdram(D14) and flash

82 D1 V Analog Video output V O - - - - Connect to video buffer(BH7862:CIN and PRIN)

83 D2 AVDD_V VDD3_3V - - - - - Connect to 3.3V_A(for Video DAC)

84 D3 AVSS_V VSS V - - - - - Connect to GND_A(for Video DAC)

85 D4 VREF - O - - - - Connect to GND_D through capacitor(0.1uF)

86 D5 VID_D[22] - (O) - - - - Not used

87 D6 VID_D[21] - (O) - - - - Not used

88 D7 VID_D[15] Video Output:C[7] (O) - - - - Not used

89 D8 VID_D[11] Video Output:C[3] (O) - - - - Not used

90 D9 VID_D[8] Video Output:C[0] (O) - - - - Not used

91 D10 VID_D[5] Video Output:Y[5] (O) - - - - Not used

92 D11 VID_D[1] Video Output:Y[1] (O) - - - - Not used

93 D12 VID_VSYNC Video Output:Vertical sync (O) - - - - Not used

94 D13 PIO1[3] Programmable I/O Port 1 Bit 3 O - Pd L L H:Active

95 D14 PIO1[6] Programmable I/O Port 1 Bit 6 O - Pd L L H:Active

96 D15 PIO1[12] Programmable I/O Port 1 Bit 12 O - - - - Control signal for rtc(RTC4543) L:read/H:write

97 D16 PIO1[14] Programmable I/O Port 1 Bit 14 I/O - - - - Control signal for rtc(RTC4543)

98 D17 UART0_RTS# UART0:Request to Send (O) - - - - Not used

99 D18 UART0_RIN UART0:Ring Indicator (I) - intPd - - Not used

100 D19 UART0_CTS# UART0:Clear to Send (I) - intPd - - Not used

101 D20 PIO0[2] Programmable I/O Port 0 Bit 2 I Lev Pu H/L H/L L:OSD Off/H:OSD On

102 D21 PIO0[4] Programmable I/O Port 0 Bit 4 I Lev Pu H/L H/L L:Active

103 D22 AVSS_SPLL System PLL Ground - - - - - Connect to GND_D

104 D23 AVDD_SPLL System PLL Power - - - - - Connect to 1.8V_A(for System PLL)

105 D24 AVDD_VPLL Video PLL Power - - - - - Connect to 1.8V_A(for System PLL)

106 D25 SM_D[2] System Memory Data Bit2 I/O - Pd - - Connect to system sdram(D2) and flash chip(D2)

107 D26 SM_D[13] System Memory Data Bit13 I/O - - - - Connect to system sdram(D13) and flash

108 D27 SM_D[12] System Memory Data Bit12 I/O - Pd - - Connect to system sdram(D12) and flash

109 E1 AUD_CLKIN Serial clock input (I) - intPd - - Not used

110 E2 NC - - - - - Not used

111 E3 NC - - - - - Not used

112 E4 NC - - - - - Not used

113 E5 VSS_CORE - - - - - - Connect to GND_D

114 E6 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

115 E7 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

116 E8 VSS_CORE - - - - - - Connect to GND_D

117 E9 VDD_IO - - - - - - Connect to 3.3V_D

118 E10 VDD_IO - - - - - - Connect to 3.3V_D

119 E11 VSS_CORE - - - - - - Connect to GND_D

120 E12 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

121 E13 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

122 E14 VSS_CORE - - - - - - Connect to GND_D

123 E15 VDD_IO - - - - - - Connect to 3.3V_D

124 E16 VDD_IO - - - - - - Connect to 3.3V_D

125 E17 VSS_CORE - - - - - - Connect to GND_D

126 E18 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

127 E19 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

128 E20 VSS_CORE - - - - - - Connect to GND_D

129 E21 VDD_IO - - - - - - Connect to 3.3V_D

130 E22 VDD_IO - - - - - - Connect to 3.3V_D

131 E23 VSS_CORE - - - - - - Connect to GND_D

132 E24 AVSS_VPLL Video PLL Ground - - - - - Connect to GND_D

133 E25 SM_D[11] System Memory Data Bit11 I/O - Pd - - Connect to system sdram(D11) and flash

134 E26 SM_D[5] System Memory Data Bit5 I/O - Pd - - Connect to system sdram(D5) and flash chip(D5)

135 E27 SM_D[6] System Memory Data Bit6 I/O - - - - Connect to system sdram(D6) and flash chip(D6)

136 F1 AUD_SDIN Serial data input (I) - intPd - - Not used

H:enable

chip(D14)

and mode select pulldown is mounted.

chip(D13)

chip(D12) and mode select pulldown is mounted.

chip(D11) and mode select pulldown is mounted.

and mode select pulldown is mounted.

8

DN-V750/V755

Pin

Port Name Symbol Description I/O Det Ext Res Ini Function

No.

137 F2 DAMCK Serial Audio Clk Out (O) - - - - Not used

138 F3 DABCK Bitclk (O) - - - - Not used

139 F4 AUD_CH1_VDDDAC1 VCC 3V3 - - - - - Connect to 3.3V_D

140 F5 VDD_IO - - - - - - Connect to 3.3V_D

141 F6 VSS_IO - - - - - - Connect to GND_D

142 F7 VSS_IO - - - - - - Connect to GND_D

143 F21 VSS_CORE - - - - - - Connect to GND_D

144 F22 VSS_IO - - - - - - Connect to GND_D

145 F23 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

146 F24 SM_D[4] System Memory Data Bit4 I/O - Pd - - Connect to system sdram(D4) and flash chip(D4)

147 F25 SM_D[8] System Memory Data Bit8 I/O - Pd - - Connect to system sdram(D8) and flash chip(D8)

148 F26 SM_DQM[0] System Memory SDRAM I/O mask 0 O - - - - Connect to system sdram(DQM0)

149 F27 SM_WE# System Memory SDRAM Write enable O - - - - Connect to system sdram(-WE) and FLASH(-OE).

150 G1 DAC1_ACLK_256DAC1 L Channel Positive Terminal O - - - - connect to audio dac(WM8725) I2S format

151 G2 DAC1_SCOUT DAC1 L Channel Negative Terminal O - - - - connect to audio dac(WM8725) I2S format

152 G3 DAC2_SCOUT DAC2 L Channel Negative Terminal (O) - - - - Not used

153 G4 AUD_CH2_VSS DAC1 VSS - - - - - Connect to GND_D

154 G5 VDD_IO - - - - - - Connect to 3.3V_D

155 G6 VSS_IO - - - - - - Connect to GND_D

156 G22 VSS_IO - - - - - - Connect to GND_D

157 G23 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

158 G24 SM_D[9] System Memory Data Bit9 I/O - Pd - - Connect to system sdram(D9) and flash chip(D9)

159 G25 SM_RAS# System Memory SDRAM Row addr.

160 G26 SM_CS# System Memory SDRAM Chip select O - - - - Connect to system sdram(-CS)

161 G27 SM_A[11] System Memory Address Bit11 O - - - - Connect to system sdram(A11) and flash

162 H1 DAC1_SDOUT DAC1 R Channel Positive Terminal O - - - - connect to audio dac(WM8725) I2S format

163 H2 DAC1_SFOUT DAC1 R Channel Negative Terminal O - - - - connect to audio dac(WM8725) I2S format

164 H3 DAC2_ACLK_256DAC2 L Channel Positive Terminal (O) - - - - Not used

Strobe

O - - - - Connect to system sdram(-RAS).

and mode select pulldown is mounted.

and mode select pulldown is mounted.

and mode select pulldown is mounted.

chip(A11)

165 H4 AUD_CH3_VDDDAC2 VCC 3V3 - - - - - Connect to 3.3V_D

166 H5 VSS_IO - - - - - - Connect to GND_D

167 H6 VSS_IO - - - - - - Connect to GND_D

168 H23 VSS_IO - - - - - - Connect to GND_D

169 H24 NC - - - - - Not used

170 H25 SM_D[15] System Memory Data Bit15 I/O - - - - Connect to system sdram(D15) and flash

171 H26 SM_A[9] System Memory Address Bit9 O - - - - Connect to system sdram(A9) and flash chip(A9)

172 H27 SM_A[8] System Memory Address Bit8 O - - - - Connect to system sdram(A8) and flash chip(A8)

173 J1 DAC3_ACLK_256DAC3 L Channel Positive Terminal (O) - - - - Not used

174 J2 DAC3_SCOUT DAC3 L Channel Negative Terminal (O) - - - - Not used

175 J3 DAC2_SDOUT DAC2 R Channel Positive Terminal (O) - - - - Not used

176 J4 AUD_CH4_VSS DAC2 VSS - - - - - Connect to GND_D

177 J5 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

178 J23 VDD_IO - - - - - - Connect to 3.3V_D

179 J24 SM_D[3] System Memory Data Bit3 I/O - Pd - - Connect to system sdram(D3) and flash chip(D3)

180 J25 SM_A[7] System Memory Address Bit7 O - - - - Connect to system sdram(A7) and flash chip(A7)

181 J26 SM_A[6] System Memory Address Bit6 O - - - - Connect to system sdram(A6) and flash chip(A6)

182 J27 SM_A[0] System Memory Address Bit0 O - - - - Connect to system sdram(A0) and flash chip(A0)

183 K1 DAC3_SDOUT DAC3 R Channel Positive Terminal (O) - - - - Not used

184 K2 DAC3_SFOUT DAC3 R Channel Negative Terminal (O) - - - - Not used

185 K3 DAC2_SFOUT DAC2 R Channel Negative Terminal (O) - - - - Not used

186 K4 AUD_CH5_VDDDAC3 VCC 3V3 - - - - - Connect to 3.3V_D

187 K5 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

188 K23 VDD_IO - - - - - - Connect to 3.3V_D

189 K24 SM_D[10] System Memory Data Bit10 I/O - Pd - - Connect to system sdram(D10) and flash

190 K25 SM_A[5] System Memory Address Bit5 O - - - - Connect to system sdram(A5) and flash chip(A5)

191 K26 SM_A[1] System Memory Address Bit1 O - - - - Connect to system sdram(A1) and flash chip(A1)

192 K27 SM_A[2] System Memory Address Bit2 O - - - - Connect to system sdram(A2) and flash chip(A2)

193 L1 MM_A[4] Mpeg Memory Address Bit 4 O - - - - Connect to MPEG SDRAM(A4)

194 L2 NC - - - - - Not used

195 L3 AUD_SPDIFOUTSPDIF Digital Out (O) - - - - Not used

chip(D15)

and mode select pulldown is mounted.

chip(D10) and mode select pulldown is mounted.

196 L4 AUD_CH6_VSS DAC3 VSS - - - - - Connect to GND_D

197 L5 VSS_IO - - - - - - Connect to GND_D

9

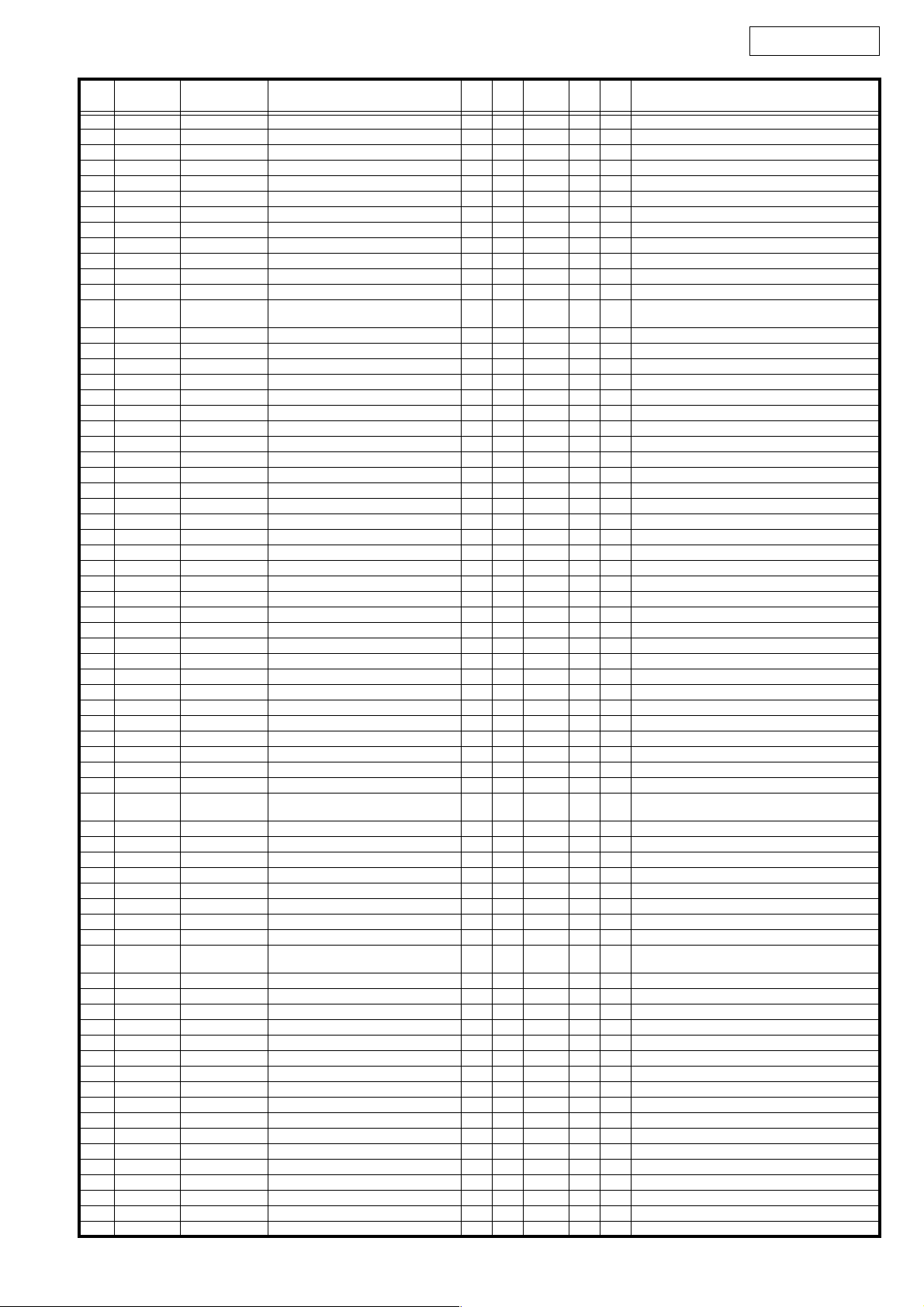

DN-V750/V755

Pin

Port Name Symbol Description I/O Det Ext Res Ini Function

No.

198 L11 VSS_IO - - - - - - Connect to GND_D

199 L12 VSS_IO - - - - - - Connect to GND_D

200 L13 VSS_IO - - - - - - Connect to GND_D

201 L14 VSS_IO - - - - - - Connect to GND_D

202 L15 VSS_IO - - - - - - Connect to GND_D

203 L16 VSS_IO - - - - - - Connect to GND_D

204 L17 VSS_IO - - - - - - Connect to GND_D

205 L23 VSS_IO - - - - - - Connect to GND_D

206 L24 SM_D[7] System Memory Data Bit7 I/O - Pd - - Connect to system sdram(D7) and flash chip(D7)

207 L25 SM_DQM[3] System Memory SDRAM I/O mask 3 O - - - - Connect to system sdram(DQM3)

208 L26 SM_A[3] System Memory Address Bit3 O - - - - Connect to system sdram(A3) and flash chip(A3)

209 L27 SM_CLK System Memory SDRAM Clock 100

210 M1 MM_A[2] Mpeg Memory Address Bit 2 O - - - - Connect to MPEG SDRAM(A2)

211 M2 MM_A[3] Mpeg Memory Address Bit 3 O - - - - Connect to MPEG SDRAM(A3)

212 M3 DALRK Serial data L/R clk (O) - - - - Not used

213 M4 DADAT Serial data output (O) - - - - Not used

214 M5 VDD_IO - - - - - - Connect to 3.3V_D

215 M11 VSS_IO - - - - - - Connect to GND_D

216 M12 VSS_IO - - - - - - Connect to GND_D

217 M13 VSS_IO - - - - - - Connect to GND_D

218 M14 VSS_IO - - - - - - Connect to GND_D

219 M15 VSS_IO - - - - - - Connect to GND_D

220 M16 VSS_IO - - - - - - Connect to GND_D

221 M17 VSS_IO - - - - - - Connect to GND_D

222 M23 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

223 M24 SM_DQM[1] System Memory SDRAM I/O mask 1 O - - - - Connect to system sdram(DQM1)

224 M25 SM_CAS# System Memory SDRAM Column

225 M26 SM_D[16] System Memory Data Bit16 I/O - - - - Connect to system sdram(D16)

226 M27 SM_D[17] System Memory Data Bit17 I/O - - - - Connect to system sdram(D17)

227 N1 MM_A[7] Mpeg Memory Address Bit 7 O - - - - Connect to MPEG SDRAM(A7)

228 N2 MM_A[6] Mpeg Memory Address Bit 6 O - - - - Connect to MPEG SDRAM(A6)

229 N3 MM_A[5] Mpeg Memory Address Bit 5 O - - - - Connect to MPEG SDRAM(A5)

230 N4 MM_A[1] Mpeg Memory Address Bit 1 O - - - - Connect to MPEG SDRAM(A1)

231 N5 VDD_IO - - - - - - Connect to 3.3V_D

232 N11 VSS_IO - - - - - - Connect to GND_D

233 N12 VSS_IO - - - - - - Connect to GND_D

234 N13 VSS_IO - - - - - - Connect to GND_D

235 N14 VSS_IO - - - - - - Connect to GND_D

236 N15 VSS_IO - - - - - - Connect to GND_D

237 N16 VSS_IO - - - - - - Connect to GND_D

238 N17 VSS_IO - - - - - - Connect to GND_D

239 N23 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

240 N24 SM_CLKE System Memory SDRAM Clock

241 N25 SM_D[18] System Memory Data Bit18 I/O - - - - Connect to system sdram(D18)

242 N26 SM_D[29] System Memory Data Bit29 I/O - - - - Connect to system sdram(D29)

243 N27 SM_D[28] System Memory Data Bit28 I/O - - - - Connect to system sdram(D28)

244 P1 MM_A[9] Mpeg Memory Address Bit 9 O - - - - Connect to MPEG SDRAM(A9)

245 P2 MM_A[0] Mpeg Memory Address Bit 0 O - - - - Connect to MPEG SDRAM(A0)

246 P3 MM_DQM[3] Mpeg Memory Input/Output mask Bit 3 O - - - - Connect to MPEG SDRAM(DQM3)

247 P4 MM_A[10] Mpeg Memory Address Bit 10 O - - - - Connect to MPEG SDRAM(A10)

248 P5 VSS_IO - - - - - - Connect to GND_D

249 P11 VSS_IO - - - - - - Connect to GND_D

250 P12 VSS_IO - - - - - - Connect to GND_D

251 P13 VSS_IO - - - - - - Connect to GND_D

252 P14 VSS_IO - - - - - - Connect to GND_D

253 P15 VSS_IO - - - - - - Connect to GND_D

254 P16 VSS_IO - - - - - - Connect to GND_D

255 P17 VSS_IO - - - - - - Connect to GND_D

256 P23 VSS_IO - - - - - - Connect to GND_D

257 P24 SM_A[10] System Memory Address Bit10 O - - - - Connect to system sdram(A10) and flash

258 P25 SM_A[4] System Memory Address Bit4 O - - - - Connect to system sdram(A4) and flash chip(A4)

259 P26 SM_D[20] System Memory Data Bit20 I/O - - - - Connect to system sdram(D20)

260 P27 SM_D[21] System Memory Data Bit21 I/O - - - - Connect to system sdram(D21)

261 R1 MM_DQM[1] Mpeg Memory Input/Output mask Bit 1 O - - - - Connect to MPEG SDRAM(DQM1)

262 R2 MM_A[11] Mpeg Memory Address Bit 11 O - - - - Connect to MPEG SDRAM(BA0)

263 R3 MM_A[8] Mpeg Memory Address Bit 8 O - - - - Connect to MPEG SDRAM(A8)

264 R4 MM_DQM[0] Mpeg Memory Input/Output mask Bit 0 O - - - - Connect to MPEG SDRAM(DQM0)

265 R5 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

266 R11 VSS_IO - - - - - - Connect to GND_D

MHz

addr. Strobe

Enable

O - - - - Connect to system sdram(CLOCK)

O - - - - Connect to system sdram(-CAS)

O - - - - Connect to system sdram(CLKE)

and mode select pulldown is mounted.

chip(A10)

10

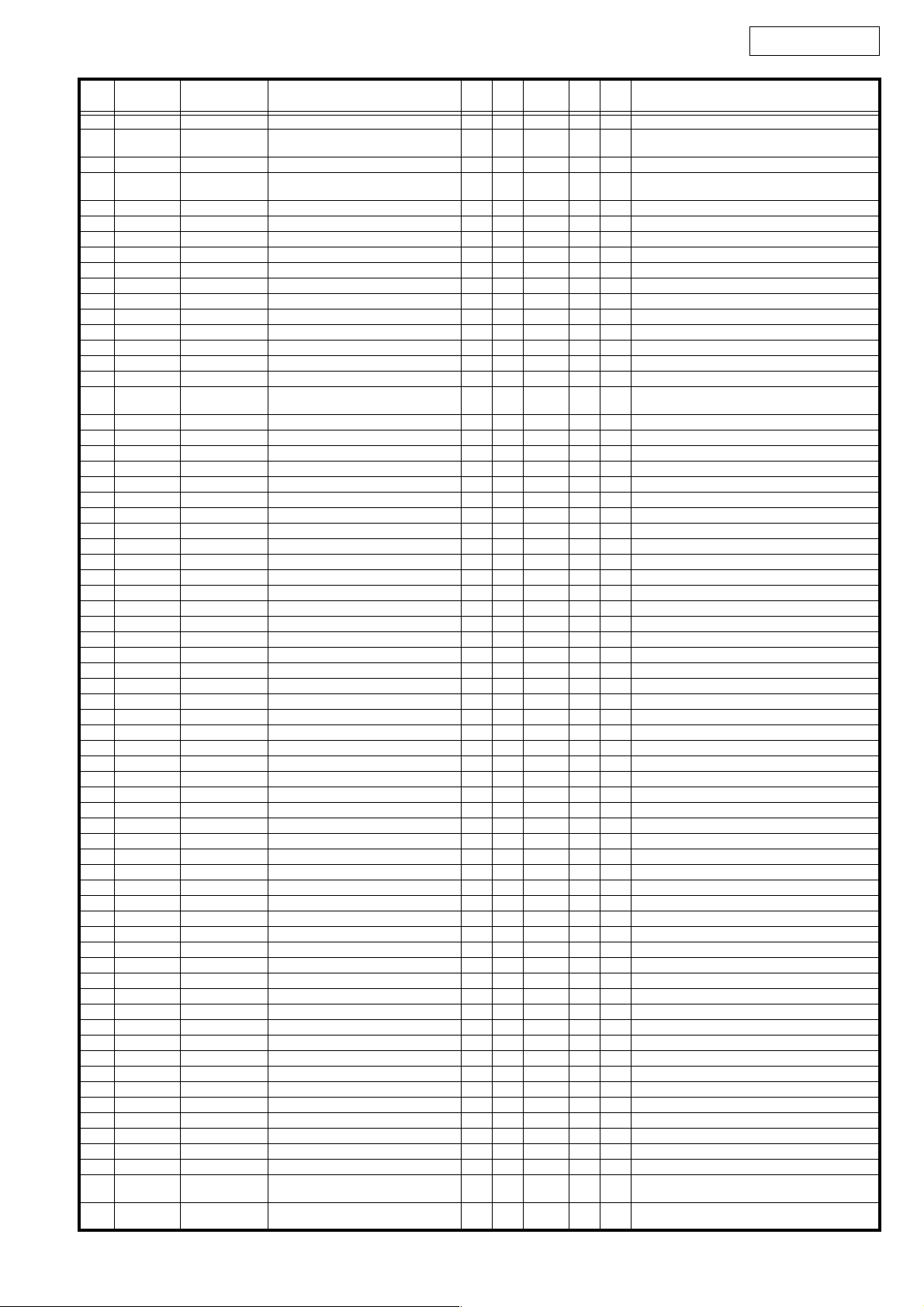

DN-V750/V755

Pin

Port Name Symbol Description I/O Det Ext Res Ini Function

No.

267 R12 VSS_IO - - - - - - Connect to GND_D

268 R13 VSS_IO - - - - - - Connect to GND_D

269 R14 VSS_IO - - - - - - Connect to GND_D

270 R15 VSS_IO - - - - - - Connect to GND_D

271 R16 VSS_IO - - - - - - Connect to GND_D

272 R17 VSS_IO - - - - - - Connect to GND_D

273 R23 VDD_IO - - - - - - Connect to 3.3V_D

274 R24 SM_D[31] System Memory Data Bit31 I/O - - - - Connect to system sdram(D31)

275 R25 SM_DQM[2] System Memory SDRAM I/O mask 2 O - - - - Connect to system sdram(DQM2)

276 R26 SM_D[22] System Memory Data Bit22 I/O - - - - Connect to system sdram(D22)

277 R27 SM_D[26] System Memory Data Bit26 I/O - - - - Connect to system sdram(D26)

278 T1 MM_CS# Mpeg Memory Chip Select O - - - - Connect to MPEG SDRAM(-CS)

279 T2 MM_WE# Mpeg Memory Write Enable for

SDRAM

280 T3 MM_D[5] Mpeg Memory Data Bit 5 I/O - - - - Connect to MPEG SDRAM(D5)

281 T4 MM_RAS# Mpeg Memory Row address strobe O - - - - Connect to MPEG SDRAM(-RAS)

282 T5 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

283 T11 VSS_IO - - - - - - Connect to GND_D

284 T12 VSS_IO - - - - - - Connect to GND_D

285 T13 VSS_IO - - - - - - Connect to GND_D

286 T14 VSS_IO - - - - - - Connect to GND_D

287 T15 VSS_IO - - - - - - Connect to GND_D

288 T16 VSS_IO - - - - - - Connect to GND_D

289 T17 VSS_IO - - - - - - Connect to GND_D

290 T23 VDD_IO - - - - - - Connect to 3.3V_D

291 T24 SM_D[19] System Memory Data Bit19 I/O - - - - Connect to system sdram(D19)

292 T25 NC - - - - - Not used

293 T26 SM_D[30] System Memory Data Bit30 I/O - - - - Connect to system sdram(D30)

294 T27 SM_D[25] System Memory Data Bit25 I/O - - - - Connect to system sdram(D25)

295 U1 MM_DQM[2] Mpeg Memory Input/Output mask Bit 2 O - - - - Connect to MPEG SDRAM(DQM2)

296 U2 MM_CAS# Mpeg Memory Column address strobe O - - - - Connect to MPEG SDRAM(-CAS)

297 U3 MM_D[4] Mpeg Memory Data Bit 4 I/O - - - - Connect to MPEG SDRAM(D4)

298 U4 MM_D[12] Mpeg Memory Data Bit 12 I/O - - - - Connect to MPEG SDRAM(D12)

299 U5 VSS_IO - - - - - - Connect to GND_D

300 U11 VSS_IO - - - - - - Connect to GND_D

301 U12 VSS_IO - - - - - - Connect to GND_D

302 U13 VSS_IO - - - - - - Connect to GND_D

303 U14 VSS_IO - - - - - - Connect to GND_D

304 U15 VSS_IO - - - - - - Connect to GND_D

305 U16 VSS_IO - - - - - - Connect to GND_D

306 U17 VSS_IO - - - - - - Connect to GND_D

307 U23 VSS_IO - - - - - - Connect to GND_D

308 U24 SM_D[23] System Memory Data Bit23 I/O - - - - Connect to system sdram(D23)

309 U25 SM_D[27] System Memory Data Bit27 I/O - - - - Connect to system sdram(D27)

310 U26 SM_A[12] System Memory Address Bit12 O - - - - Connect to system sdram(BA0) and flash

311 U27 SM_D[24] System Memory Data Bit24 I/O - - - - Connect to system sdram(D24)

312 V1 MM_CLK Mpeg Memory Clock 100 MHz O - - - - Connect to MPEG SDRAM(CLK)

313 V2 MM_D[7] Mpeg Memory Data Bit 7 I/O - - - - Connect to MPEG SDRAM(D7)

314 V3 MM_D[1] Mpeg Memory Data Bit 1 I/O - - - - Connect to MPEG SDRAM(D1)

315 V4 MM_D[24] Mpeg Memory Data Bit 24 I/O - - - - Connect to MPEG SDRAM(D24)

316 V5 VDD_IO - - - - - - Connect to 3.3V_D

317 V23 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

318 V24 SM_A[15] System Memory Address Bit15 O - - - - Connect to flash chip(A15)

319 V25 SM_A[13] System Memory Address Bit13 O - - - - Connect to system sdram(BA1) and flash

320 V26 SM_A[16] System Memory Address Bit16 O - - - - Connect to flash chip(A16)

321 V27 SM_A[14] System Memory Address Bit14 O - - - - Connect to flash chip(A14)

322 W1 MM_D[8] Mpeg Memory Data Bit 8 I/O - - - - Connect to MPEG SDRAM(D8)

323 W2 NC - - - - - Not used

324 W3 MM_D[21] Mpeg Memory Data Bit 21 I/O - - - - Connect to MPEG SDRAM(D21)

325 W4 MM_D[27] Mpeg Memory Data Bit 27 I/O - - - - Connect to MPEG SDRAM(D27)

326 W5 VDD_IO - - - - - - Connect to 3.3V_D

327 W23 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

328 W24 FLASH_CS[1]# Flash Chip Select 1 O - - - H Connect to flash chip(-CS1) or adress decoder(A)

329 W25 SM_A[18] System Memory Address Bit18 O - - - - Connect to flash chip(A18)

330 W26 SM_A[19] System Memory Address Bit19 O - - - - Connect to flash chip(A19)

331 W27 SM_A[17] System Memory Address Bit17 O - - - - Connect to flash chip(A17)

332 Y1 MM_D[6] Mpeg Memory Data Bit 6 I/O - - - - Connect to MPEG SDRAM(D6)

333 Y2 MM_D[9] Mpeg Memory Data Bit 9 I/O - - - - Connect to MPEG SDRAM(D9)

334 Y3 MM_D[28] Mpeg Memory Data Bit 28 I/O - - - - Connect to MPEG SDRAM(D28)

335 Y4 MM_D[17] Mpeg Memory Data Bit 17 I/O - - - - Connect to MPEG SDRAM(D17)

336 Y5 VSS_IO - - - - - - Connect to GND_D

O - - - - Connect to MPEG SDRAM(-WE)

chip(A12)

chip(A13)

11

DN-V750/V755

Pin

Port Name Symbol Description I/O Det Ext Res Ini Function

No.

337 Y23 VSS_IO - - - - - - Connect to GND_D

338 Y24 FLASH_CFG[0] Flash configulation(16#/32bits flash

339 Y25 FLASH_RYBY# Flash ready/busy (I) - Pu H H Reserved function.

340 Y26 FLASH_CS[0]# Flash Chip Select 0 O - - - L Connect to flash chip(-CS0) or adress decoder(-

341 Y27 FLASH_WE# Flash Write Enable O - - - - Connect to flash chip(-WE)

342 AA1 MM_D[10] Mpeg Memory Data Bit 10 I/O - - - - Connect to MPEG SDRAM(D10)

343 AA2 MM_D[11] Mpeg Memory Data Bit 11 I/O - - - - Connect to MPEG SDRAM(D11)

344 AA3 MM_D[3] Mpeg Memory Data Bit 3 I/O - - - - Connect to MPEG SDRAM(D3)

345 AA4 VIDIN_D[10] Video Input Data Bit 10 (I) - intPd - - Not used

346 AA5 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

347 AA6 VSS_CORE - - - - - - Connect to GND_D

348 AA22 VSS_CORE - - - - - - Connect to GND_D

349 AA23 VDD_IO - - - - - - Connect to 3.3V_D

350 AA24 IDE_IOW# IDE I/O write O - - - - IDE/PC Card I/O Write

351 AA25 IDE_CS0# IDE Chip Select 0 O - - - - IDE/PC Card chip select0

352 AA26 IDE_NPCBLID IDE Cable ID I - - - - IDE/PC Card cable ID

353 AA27 FLASH_CFG[1] Flash configulation(1#/2chips select

354 AB1 MM_D[2] Mpeg Memory Data Bit 2 I/O - - - - Connect to MPEG SDRAM(D2)

355 AB2 MM_D[13] Mpeg Memory Data Bit 13 I/O - - - - Connect to MPEG SDRAM(D13)

356 AB3 MM_D[14] Mpeg Memory Data Bit 14 I/O - - - - Connect to MPEG SDRAM(D14)

357 AB4 VIDIN_D[12] Video Input Data Bit 12 (I) - intPd - - Not used

358 AB5 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

359 AB6 VSS_CORE - - - - - - Connect to GND_D

360 AB7 VSS_CORE - - - - - - Connect to GND_D

361 AB22 VSS_CORE - - - - - - Connect to GND_D

362 AB23 VDD_IO - - - - - - Connect to 3.3V_D

363 AB24 IDE_DMAREQ IDE DMA request I - Pd - - IDE/PC Card DMA request.

364 AB25 IDE_A[2] IDE Adress bit2 O - - - - IDE/PC Card address bit2

365 AB26 IDE_CS1# IDE Chip Select 1 O - - - - IDE/PC Card chip select1

366 AB27 DVD_CLKIN - I - GND L L Not used

367 AC1 MM_D[0] Mpeg Memory Data Bit 0 I/O - - - - Connect to MPEG SDRAM(D0)

368 AC2 MM_D[15] Mpeg Memory Data Bit 15 I/O - - - - Connect to MPEG SDRAM(D15)

369 AC3 MM_D[26] Mpeg Memory Data Bit 26 I/O - - - - Connect to MPEG SDRAM(D26)

370 AC4 VIDIN_D[14] Video Input Data Bit 14 (I) - intPd - - Not used

371 AC5 VSS_CORE - - - - - - Connect to GND_D

372 AC6 VDD_IO - - - - - - Connect to 3.3V_D

373 AC7 VDD_IO - - - - - - Connect to 3.3V_D

374 AC8 VSS_CORE - - - - - - Connect to GND_D

375 AC9 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

376 AC10 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

377 AC11 VSS_CORE - - - - - - Connect to GND_D

378 AC12 VDD_IO - - - - - - Connect to 3.3V_D

379 AC13 VDD_IO - - - - - - Connect to 3.3V_D

380 AC14 VSS_CORE - - - - - - Connect to GND_D

381 AC15 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

382 AC16 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

383 AC17 VSS_CORE - - - - - - Connect to GND_D

384 AC18 VDD_IO - - - - - - Connect to 3.3V_D

385 AC19 VDD_IO - - - - - - Connect to 3.3V_D

386 AC20 VSS_CORE - - - - - - Connect to GND_D

387 AC21 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

388 AC22 VDD_CORE - - - - - - Connect to 1.8V_D(for core)

389 AC23 VSS_CORE - - - - - - Connect to GND_D

390 AC24 IDE_IOR# IDE I/O read O - - - - IDE/PC Card I/O read

391 AC25 IDE_A[0] IDE Adress bit0 O - - - - IDE/PC Card address bit0

392 AC26 IDE_A[1] IDE Adress bit1 O - - - - IDE/PC Card address bit1

393 AC27 IDE_IRQ IDE Interrupt Request I - Pd - - IDE/PC Card IRQ

394 AD1 MM_D[23] Mpeg Memory Data Bit 23 I/O - - - - Connect to MPEG SDRAM(D23)

395 AD2 MM_D[22] Mpeg Memory Data Bit 22 I/O - - - - Connect to MPEG SDRAM(D22)

396 AD3 MM_D[18] Mpeg Memory Data Bit 18 I/O - - - - Connect to MPEG SDRAM(D18)

397 AD4 VIDIN_D[15] Video Input Data Bit 15 (I) - intPd - - Not used

398 AD5 VIDIN_D[8] Video Input Data Bit 8 (I) - intPd - - Not used

399 AD6 VIDIN_D[5] Video Input Data Bit 5 (I) - intPd - - Not used

400 AD7 VIDIN_D[2] Video Input Data Bit 2 (I) - intPd - - Not used

401 AD8 NC No Connection - - - - - Not used

402 AD9 NC No Connection - - - - - Not used

403 AD10 LPB_AD[15] Local Peripheral Bus Address/Data bit 15I/O - - - - Connect to Ethernet(DM9000) and CX303(for

404 AD11 LPB_AD[11] Local Peripheral Bus Address/Data bit 11I/O - - - - Connect to Ethernet(DM9000) and CX303(for

Width)

signal)

I - GND L L Select bus width.(L fixed:16bit bus width)

G).

I - Pu/Pd - - Select quantity of flash chip(L:single

chip,H:double chip)

DN-V1500X)

DN-V1500X)

12

DN-V750/V755

Pin

Port Name Symbol Description I/O Det Ext Res Ini Function

No.

405 AD12 LPB_AD[7] Local Peripheral Bus Address/Data bit 7I/O - - - - Connect to Ethernet(DM9000) and CX303(for

406 AD13 LPB_AD[3] Local Peripheral Bus Address/Data bit 3I/O - - - - Connect to Ethernet(DM9000) and CX303(for

407 AD14 LPB_AD[0] Local Peripheral Bus Address/Data bit 0I/O - - - - Connect to Ethernet(DM9000) and CX303(for

408 AD15 LPB_RD# Local Peripheral Bus Read Command O - - - - Connect to Ethernet(DM9000) and CX241(for

409 AD16 DMA_REQ Local Peripheral Bus DMA Request I (Ed) intPd - - Connect to CX241(Expansion connector for DN-

410 AD17 LPB_PGIO[0] Local Peripheral Bus Programmable I/

411 AD18 UART1_DSR# UART1:Data Set Ready (I) - intPd - - Not used

412 AD19 UART1_RTS# UART1:Request to Send (O) - - - - Not used

413 AD20 VFD_STB VFD:Strobe Output (O) - - - - Not used

414 AD21 I2CM_SDA I2C Master:2wire bus interface data I/O - Pu - - Connect to serial EEPROM for preset

415 AD22 IDE_D[4] IDE Data bit4 I/O - - - - IDE/PC Card data bit4

416 AD23 IDE_D[13] IDE Data bit13 I/O - - - - IDE/PC Card data bit13

417 AD24 IDE_D[0] IDE Data bit0 I/O - - - - IDE/PC Card data bit0

418 AD25 IDE_D[15] IDE Data bit15 I/O - - - - IDE/PC Card data bit15

419 AD26 IDE_IORDY IDE I/O channel ready I - Pu - - IDE/PC Card ready

420 AD27 IDE_ACK# IDE DMA acknowledge O - - - - IDE/PC Card DMA acknowredge.

421 AE1 MM_D[25] Mpeg Memory Data Bit 25 I/O - - - - Connect to MPEG SDRAM(D25)

422 AE2 NC - - - - - Not used

423 AE3 MM_D[16] Mpeg Memory Data Bit 16 I/O - - - - Connect to MPEG SDRAM(D16)

424 AE4 VIDIN_D[11] Video Input Data Bit 11 (I) - intPd - - Not used

425 AE5 VIDIN_D[7] Video Input Data Bit 7 (I) - intPd - - Not used

426 AE6 VIDIN_D[4] Video Input Data Bit 4 (I) - intPd - - Not used

427 AE7 VIDIN_D[1] Video Input Data Bit 1 (I) - intPd - - Not used

428 AE8 NC No Connection - - - - - Not used

429 AE9 NC No Connection - - - - - Not used

430 AE10 LPB_AD[14] Local Peripheral Bus Address/Data bit 14I/O - - - - Connect to Ethernet(DM9000) and CX303(for

431 AE11 LPB_AD[10] Local Peripheral Bus Address/Data bit 10I/O - - - - Connect to Ethernet(DM9000) and CX303(for

432 AE12 LPB_AD[6] Local Peripheral Bus Address/Data bit 6I/O - - - - Connect to Ethernet(DM9000) and CX303(for

433 AE13 LPB_AD[2] Local Peripheral Bus Address/Data bit 2I/O - - - - Connect to Ethernet(DM9000) and CX303(for

434 AE14 DTACK/RDY# Local Peripheral Bus Transfer

435 AE15 LPB_WR# Local Peripheral Bus Write Command O - - - - Connect to Ethernet(DM9000) and CX241(for

436 AE16 DMA_REQ1 No Connection (I) - intPd - - Connect to CX241(for DN-V1500X). Not

437 AE17 LPB_PGIO[1] Local Peripheral Bus Programmable I/

438 AE18 UART1_DCD# UART1:Data Carriar Detect (I) - intPd - - Not used

439 AE19 UART1_DTR# UART1:Data Terminal Ready (O) - - - - Not used

440 AE20 VFD_DIN VFD:Data from VFD CTRL (I) - Pu - - Connect to VFD_DOUT(AG21)

441 AE21 I2CM_SCL I2C Master:2wire bus interface clock O - (Pu) - - Connect to serial EEPROM for preset

442 AE22 IDE_D[8] IDE Data bit8 I/O - - - - IDE/PC Card data bit8

443 AE23 IDE_D[11] IDE Data bit11 I/O - - - - IDE/PC Card data bit11

444 AE24 IDE_D[2] IDE Data bit2 I/O - - - - IDE/PC Card data bit2

445 AE25 IDE_D[12] IDE Data bit12 I/O - - - - IDE/PC Card data bit12

446 AE26 IDE_D[1] IDE Data bit1 I/O - - - - IDE/PC Card data bit1

447 AE27 IDE_D[14] IDE Data bit14 I/O - - - - IDE/PC Card data bit14

448 AF1 MM_D[20] Mpeg Memory Data Bit 20 I/O - - - - Connect to MPEG SDRAM(D20)

449 AF2 MM_D[29] Mpeg Memory Data Bit 29 I/O - - - - Connect to MPEG SDRAM(D29)

450 AF3 MM_D[31] Mpeg Memory Data Bit 31 I/O - - - - Connect to MPEG SDRAM(D31)

451 AF4 VIDIN_D[9] Video Input Data Bit 9 (I) - intPd - - Not used

452 AF5 VIDIN_D[6] Video Input Data Bit 6 (I) - intPd - - Not used

453 AF6 VIDIN_D[3] Video Input Data Bit 3 (I) - intPd - - Not used

454 AF7 VIDIN_D[0] Video Input Data Bit 0 (I) - intPd - - Not used

455 AF8 AS_ALE Local Peripheral Bus Address Strobe O - - - - Connect to address latch(SN74LVC573) and

456 AF9 NC No Connection - - - - - Not used

457 AF10 LPB_AD[13] Local Peripheral Bus Address/Data bit 13I/O - - - - Connect to Ethernet(DM9000) and CX303(for

458 AF11 LPB_AD[9] Local Peripheral Bus Address/Data bit 9I/O - - - - Connect to Ethernet(DM9000) and CX303(for

459 AF12 LPB_AD[5] Local Peripheral Bus Address/Data bit 5I/O - - - - Connect to Ethernet(DM9000) and CX303(for

460 AF13 LPB_AD[1] Local Peripheral Bus Address/Data bit 1I/O - - - - Connect to Ethernet(DM9000) and CX303(for

O Bit 0

Acknowredge

O Bit 1

I/O (Lev)intPd - - Connect to CX241(for DN-V1500X)

I (Ed) Pu H H ACK/RDY(-WAIT) signal input for local peripheral

I/O (Lev)intPd - - Connect to CX241(for DN-V1500X)

DN-V1500X)

DN-V1500X)

DN-V1500X)

DN-V1500X)

V1500X)

memory(DATA)

DN-V1500X)

DN-V1500X)

DN-V1500X)

DN-V1500X)

bus.

DN-V1500X)

supported function.

memory(CLK)

CX241(for DN-V1500X)

DN-V1500X)

DN-V1500X)

DN-V1500X)

DN-V1500X)

13

DN-V750/V755

Pin

Port Name Symbol Description I/O Det Ext Res Ini Function

No.

461 AF14 NC - - - - - Not used

462 AF15 LPB_INTR Local Peripheral Bus Interrupt

463 AF16 LPB_PGIO[3] Local Peripheral Bus Programmable I/

464 AF17 LPB_PGIO[2] Local Peripheral Bus Programmable I/

465 AF18 UART1_CTS# UART1:Clear to Send (I) - intPd - - Not used

466 AF19 UART1_RXD UART1:Receive Data (I) - intPd - - Connect to RS232C receiver(uPD4721) and

467 AF20 UART1_TXD UART1:Transmit Data (O) - - - - Connect to RS232C driver(uPD4721) and

468 AF21 VFD_CLKOUT VFD:Clock out to CTRL (O) - - - - Not used

469 AF22 I2CS_SDA I2C Slave:2wire bus interface data (I/O)- - - - Not used

470 AF23 I2S_WS I2S Frame (O) - - - - Not used

471 AF24 IDE_D[6] IDE Data bit6 I/O - - - - IDE/PC Card data bit6

472 AF25 IDE_D[10] IDE Data bit10 I/O - - - - IDE/PC Card data bit10

473 AF26 NC - - - - - Not used

474 AF27 IDE_D[3] IDE Data bit3 I/O - - - - IDE/PC Card data bit3

475 AG1 MM_D[19] Mpeg Memory Data Bit 19 I/O - - - - Connect to MPEG SDRAM(D19)

476 AG2 MM_D[30] Mpeg Memory Data Bit 30 I/O - - - - Connect to MPEG SDRAM(D30)

477 AG3 VIDIN_D[13] Video Input Data Bit 13 (I) - intPd - - Not used

478 AG4 VIDIN_CLK Video Input Pixel Clock In (I) - intPd - - Not used

479 AG5 VIDIN_VSYNC Video Input Vsync In I - intPd - - Connect to CX303(for DN-V1500X)

480 AG6 VIDIN_HSYNC Video Input Hsync In I - intPd - - Connect to CX303(for DN-V1500X)

481 AG7 NC No Connection - - - - - Not used

482 AG8 NC No Connection - - - - - Not used

483 AG9 NC No Connection - - - - - Not used

484 AG10 LPB_AD[12] Local Peripheral Bus Address/Data bit 12I/O - - - - Connect to Ethernet(DM9000) and CX303(for

485 AG11 LPB_AD[8] Local Peripheral Bus Address/Data bit 8I/O - - - - Connect to Ethernet(DM9000) and CX303(for

486 AG12 LPB_AD[4] Local Peripheral Bus Address/Data bit 4I/O - - - - Connect to Ethernet(DM9000) and CX303(for

487 AG13 LPB_HSEL# Local Peripheral Bus Device Chip

488 AG14 LPB_RESET# Local Peripheral Bus Reset O - - - - Connect to CX241(for DN-V1500X)

489 AG15 NC No Connection - - - - - Not used

490 AG16 RESET# Chip reset I - Pu - - EM8550 reset

491 AG17 SCAN_MODE Scan Mode (I) - GND L L Connect to GND_D

492 AG18 RTC_CLKIN 32kHz Clock input for Real Time Clock I - GND L L RTC is not work

493 AG19 UART1_RIN UART1:Ring Indicator (I) - intPd - - Not used

494 AG20 I2S_SCK I2S Clock (O) - - - - Not used

495 AG21 VFD_DOUT VFD:Data to VFD CTRL (I/O)- - - - Connect to VFD_DIN(AE20)

Request

O Bit 3

O Bit 2

Select

I (Ed) Pu - - Connect to Ethernet(DM9000) and CX241(for

I/O (Lev)intPd - - Connect to CX241(for DN-V1500X)

I/O (Lev)intPd - - Connect to CX241(for DN-V1500X)

O - - - - Connect to Ethernet(DM9000) and CX241(for

DN-V1500X)

CX241(for DN-V1500X)

CX241(for DN-V1500X)

DN-V1500X)

DN-V1500X)

DN-V1500X)

DN-V1500X)

496 AG22 I2CS_SCL I2C Slave:2wire bus interface clock (O) - - - - Not used

497 AG23 I2S_SD I2S Data (O) - - - - Not used

498 AG24 IDE_D[7] IDE Data bit7 I/O - Pd - - IDE/PC Card data bit7

499 AG25 IDE_D[9] IDE Data bit9 I/O - - - - IDE/PC Card data bit9

500 AG26 IDE_D[5] IDE Data bit5 I/O - - - - IDE/PC Card data bit5

501 AG27 NC - - - - - Not used

14

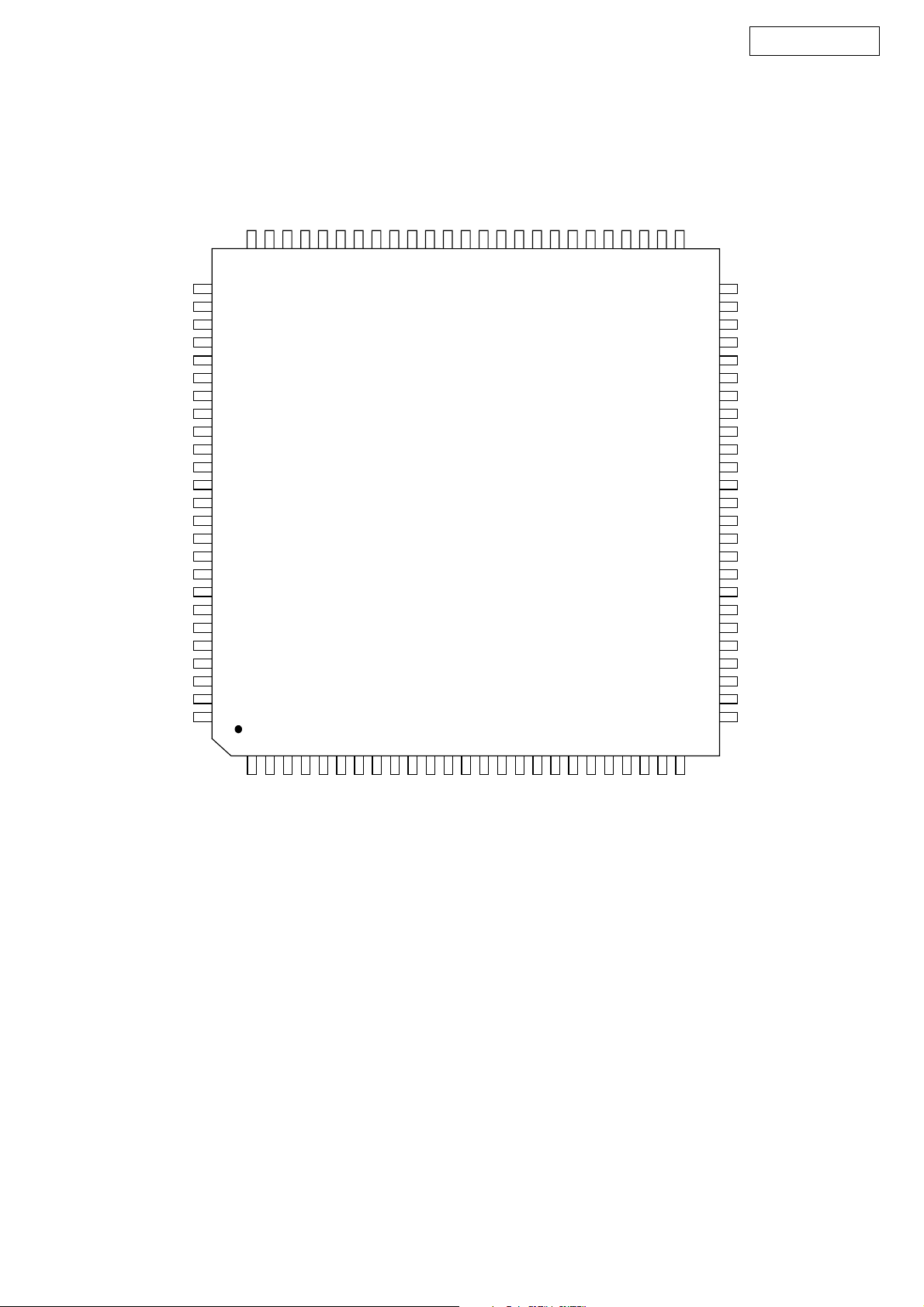

DM9000EP (IC308)

NC

NC

DVDD

DVDD

GPIO3

GPIO2

GPIO1

GPIO0

DN-V750/V755

TXD1

TXD2

TXD3

TX_EN

DVDD

MDIO

MDC

DGND

CLK20MO

SPEED#

DUP#

LINKACT#

DGND

EEDI

EEDO

EECK

EECS

DGND

NC

LINK_O

WAKEUP

PW_RST#

DGND

SD15

SD14

SD13

SD12

SD11

SD10

SD9

SD8

DVDD

IO16

CMD

SA4

SA5

SA6

SA7

SA8

SA9

DGND

INT

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

75

1

74

73

72

71706968676665

64

63

62

616059

58

57

DM9000

4

3

56789

10

1213141516

11

17

18

19

2

545352

55

56

202122

23

24

51

25

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

TXD0

TX_CLK

TEST5

RX_CLK

RX_ER

RX_DV

COL

CRS

DGND

RXD3

RXD2

RXD1

RXD0

LINK_I

DVDD

AVDD

TXOTXO+

AGND

AGND

RXRX+

AVDD

AVDD

BGRES

IOR#

IOW#

X1_25M

SD

AGND

DGND

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

AEN

DVDD

IOWAIT

RST

DGND

TEST1

TEST2

TEST3

TEST4

DVDD

X2_25M

15

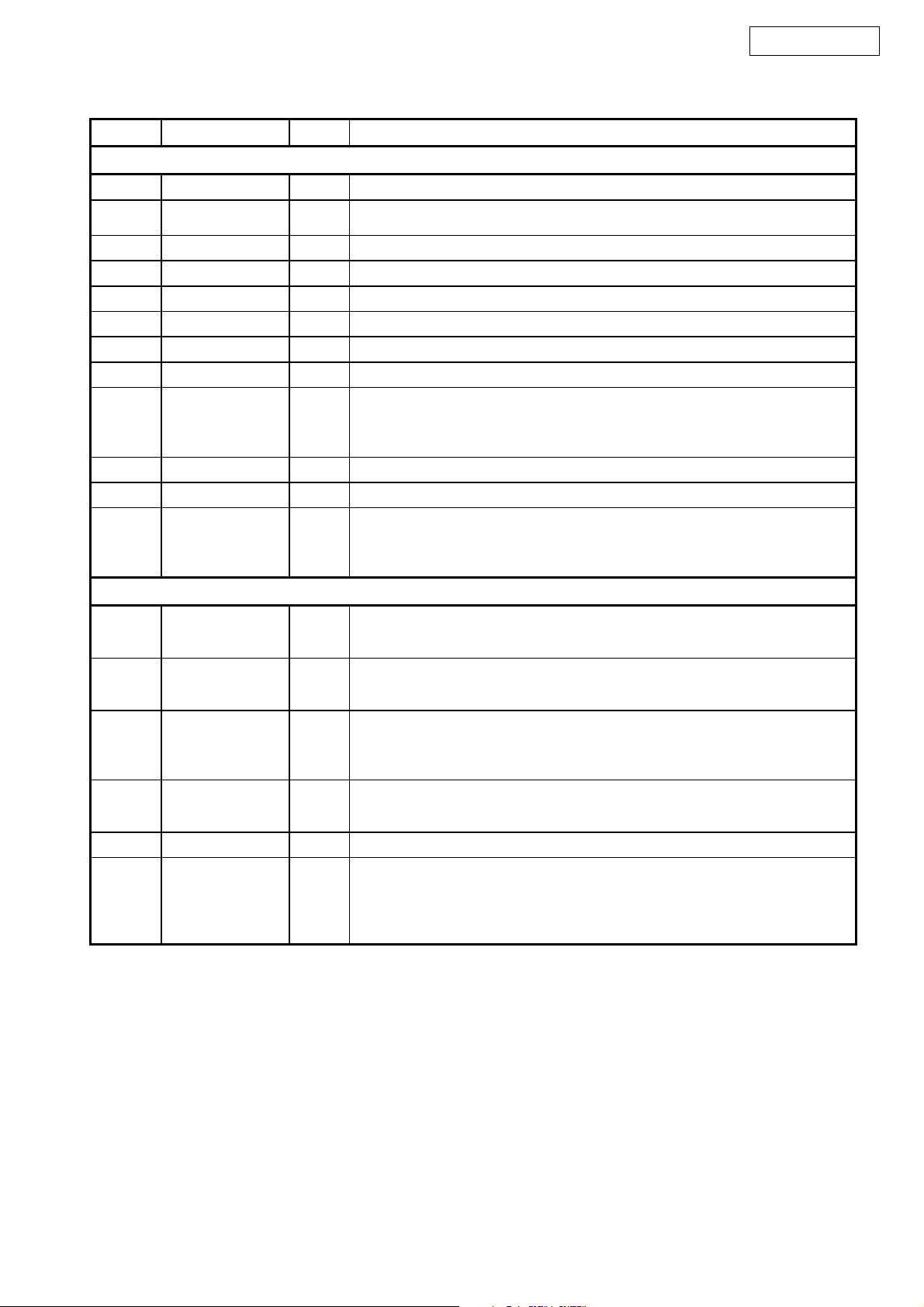

DM9000EP Terminal Function

Pin No. Pin Name Type Description

MII Interface

37 LINK_I I External MII device link status.

41,40,39,38RXD[3:0] I External MII Receive Data

43 CRS I External MII Carrier Sense

44 COL I External MII Collision Detect

45 RX_DV I External MII Receive Data Valid

46 RX_ER I External MII Receive Error

47 RX_CLK I External MII Receive Clock

49 TX_CLK I External MII Transmit Clock

53,52,51,50TXD[3:0] I/O External MII Transmit Data

TXD[2:0] also used as the strap pins of IO base address when the DM9000 is

operated in ISA mode.

The IO base = (strap pin value of TXD[2:0]) * 10H + 300H

54 TX_EN O External MII Transmit Enable

56 MDIO I/O MII Serial Management Data

57 MDC I/O MII Serial Management Data Clock

This pin is also used as the strap pin of the polarity of the INT pin.

When the MDC pin is pull-high, the INT pin low active; otherwise the INT pin is

high active.

Processor interface

DN-V750/V755

1 IOR# I Processor Read command.

This pin is low active at default, its polarity can be modified by EEPROM setting.

See the EEPROM content description for detail.

2 IOW# I Processor Write command.

This pin is low active at default, its polarity can be modified by EEPROM setting.

See the EEPROM content description for detail.

3 AEN I Address enable used for ISA mode or

chip select for general processor mode.

In general processor mode, the polarity of this pin can be modified by EEPROM

setting. See the EEPROM content description for detail.

4 IOWAIT O Processor command ready

When a command is issued before last command completed, the IOWAIT will be

pulled to low to indicate the current command is waited.

14 RST I Hardware reset command, high active to reset the DM9000.

6,7,8,9,10,

11,12,13,

89,88,87,

86,85,84,

83,82

SD0~15 I/O Processor data bus bit 0~15

16

DN-V750/V755

93,94,95,

96,97,98

100 INT O interrupt request

56,53,52,

51,50,49,

47,46,45,

44,43,41,

40,39,38

EEPROM Interface

SA4~9 I address bus 4~9 for ISA mode

92 CMD I Command type:

When high, the access of this command cycle is DATA port.

When low, the access of this command cycle is ADDRESS port.

91 IO16 O word command indication

When the access of internal memory is word or dword width, this pin will

be asserted.

This pin is low active at default, its polarity can be modified by EEPROM

setting. See the EEPROM content description for detail.

This pin is high active at default, its polarity can be modified by EEPROM

setting or strap pin MDC. See the EEPROM content description for detail.

SD16~31 (in

double word

mode)

37

57 IO32 (in double

word mode)

I/O Processor data bus bit 16~31

These pins are used as data bus bits 16~31 when the DM9000 is set to

double word mode (the straps pin EEDO is pull-high and WAKEUP is not

pull-high).

O Double word command indication

This pins is used as the Double word command indication when the

DM9000 is set to double data word mode and when the access of internal

memory is double word width, this pin will be asserted.

This pin is low active at default, its polarity can be modified by EEPROM

setting. See the EEPROM content description for detail.

64 EEDI I Data from EEPROM

65 EEDO I/O Data to EEPROM

This pin is also as a strap pin. Combine with strap pin WOL, it can set the

data width of the internal memory access.

The decoder table is the following, where the logic 1 means the strap pin

is pull-high.

WAKEUP EEDO data width

0 0 word

0 1 double word

1 0 byte

1 1 reserved

66 EECK O Clock to EEPROM

67 EECS I/O Chip Select to EEPROM

This pin is also used as a strap pin to define the LED modes.

When it is pull-high, the LED mode is the mode 1;

Otherwise it is mode 0.

Clock Interface

21 X2_25M O Crystal 25MHz Out

22 X1_25M I Crystal 25MHz In

17

Loading...

Loading...