Denon DN-V1700 Service Manual

SERVICE MANUAL

For U.S.A. & Canada model

MODEL

NETWORK AUDIO VIDEO PLAYER

DN-V1700

Some illustrations using in this service manual are slightly different from the actual set.

16-11, YUSHIMA 3-CHOME, BUNKYOU-KU, TOKYO 113-0034 JAPAN

Telephone: 03 (3837) 5321

X0153 DE 0209

SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

LEAKAGE CURRENT CHECK

Before returning the unit to the customer, make sure you make either (1) a leakage current check or (2) a line to chassis

resistance check. If the leakage current exceeds 10mA, or if the resistance from chassis to either side of the power cord

is less than 1MΩ, the unit is defective.

SPECIFICATIONS

Playable formats: <Video + audio or Video only>

ISO/IEC 13818-1 MPEG2 MP@ML PS (Program Stream) files (video + audio)

ES files (video only) Resolution: 720 × 480

<Still images>

ISO/IEC 13818-2 MPEG2 MP@ML ES files

Resolution: 720 × 480 per frame intraframe

<Audio format>

MPEG1 – Audio Layer 2 (ISO/IEC 11172-3)

Sampling frequency: 48 kHz, 44.1 kHz

<Max. baud rate>

Max. 10 Mbps total for video + audio (as per card performance)

DN-V1700

Playback medium: DENON recommended flash memory card

Internal hard disk drive

Input/output terminals: Component video (Y/Cb/Cr) output BNC terminal

Composite output BNC terminal, composite output RCA terminal

Y/C separated signal output S terminal, VITC input BNC terminal, VITC output BNC terminal

Analog audio output RCA terminal (stereo) × 2

Analog audio output balanced active, XLR connector x 1

Digital audio output RCA terminal (EIAJ format)

DC input terminal, serial mode (D-sub female 9 pin) terminal (for both RS232C and RS422A)

Parallel remote (D-sub female 15 pin) terminal

Ethernet (LAN) (RJ-45) terminal (10 Base-T/100 Base-TX, automatic selection)

Video performance: Video outputs Composite: 1.0 Vp-p (negative resistance 75 Ω/ohms)

S-Video:Y (brightness) signal: 1.0 Vp-p (negative resistance 75 Ω/ohms)

C (color) signal: 286 mVp-p (negative resistance 75 Ω/ohms)

Component: Y (brightness) signal: 1.0 Vp-p (negative resistance 75 Ω/ohms)

Cb (color) signal: 0.65 Vp-p (negative resistance 75 Ω/ohms)

Cr (color) signal: 0.65 Vp-p (negative resistance 75 Ω/ohms)

Sampling frequency: 13.5 MHz

S/N ratio: 50 dB or greater

Audio performance: RCA output level: 1.3 Vrms (negative resistance 10kΩ/kohms: 1 kHz, 0 dB playback)

Balance output level: +18 dBm, 600 Ω/ohms: 1kHz, 0 dB playback

Distortion: 0.3% or less (when playing 1 kHz, 0 dB sine wave, using LPF)

S/N ratio: 65 dB or greater (when playing 1 kHz, 0 dB sine wave, using LPF and A-Filter)

Channel separation: 65 dB or greater (stereo, when playing 1 kHz, 0 dB sine wave,

using LPF A-Filter)

Frequency response (1 kHz base): Within 0 ±3 dB at 20 to 20 kHz: fs = 44.1 kHz

Internal clock error: Within 60 seconds per month

2

External dimensions: 484 (W) × 44 (H) × 375 (D) mm

Mass: 4.6 kg (not including IC memory card)

Power supply: AC adaptor (EPA-301DAN-06) Input: AC 120V, 60 Hz

Power consumption: DC 6 V 1.8 A

Surrounding conditions: Operating temperature range: 5 to 35°C

Operating humidity range: 40 to 80%

Storage temperature range: −20 to 60°C (not including playback media)

Storage humidity range: 42 to 90% (not including playback media)

Period of warranty: 1 year from date of purchase (not including playback media)

* For improvement purposes, specifications and design are subject to change without notice.

DN-V1700

3

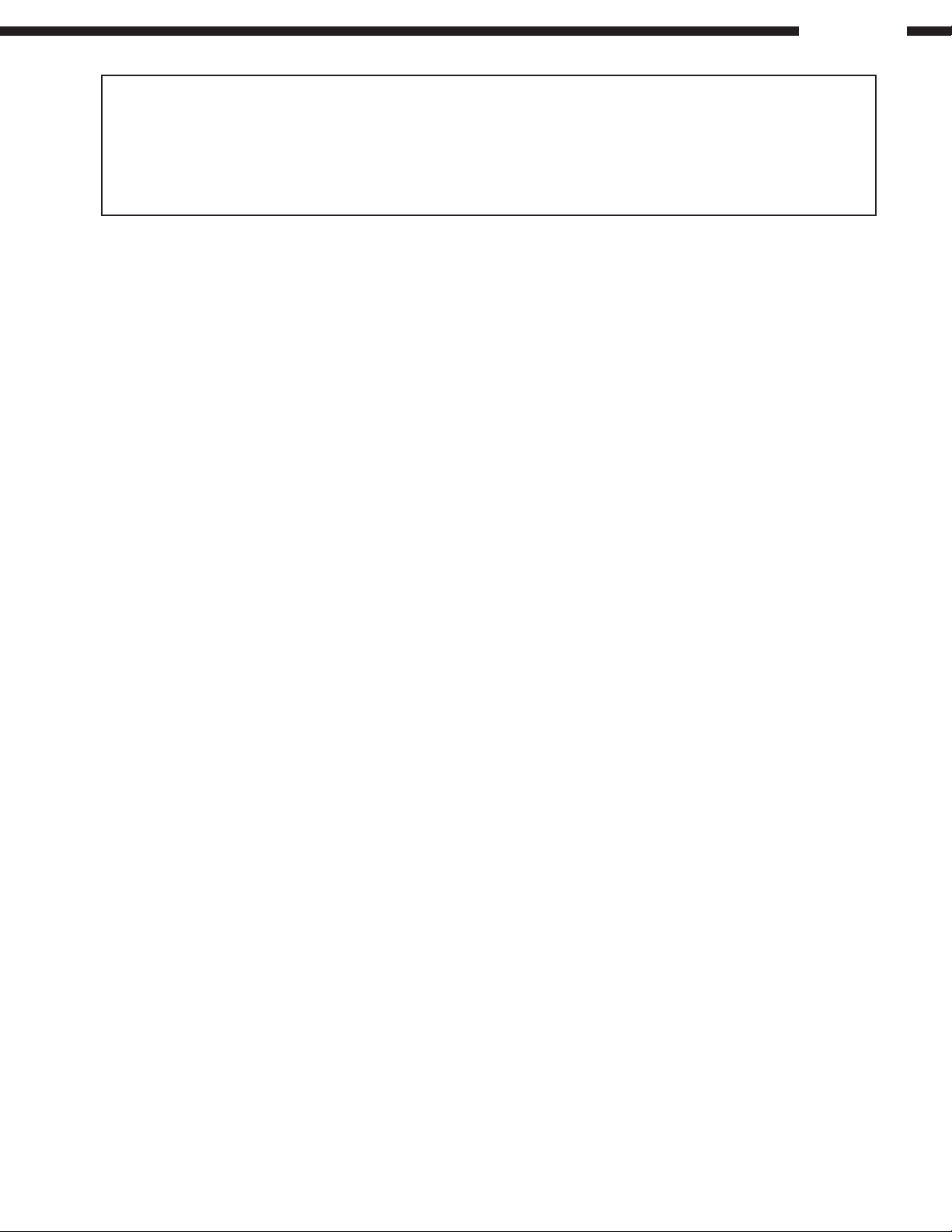

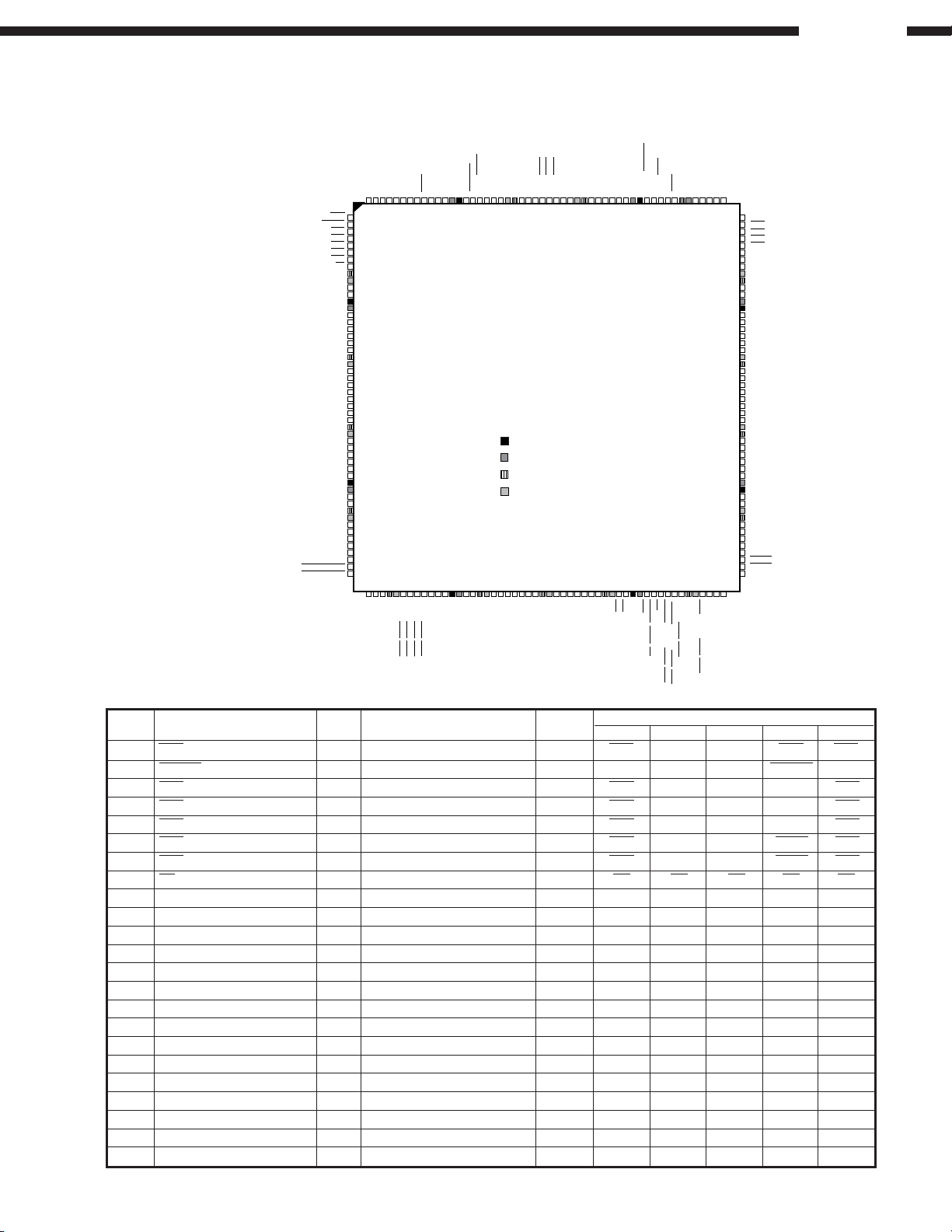

BLOCK DIAGRAM

1 5678

DN-V1700

32

4

VITC out

Serial

9p-Dsub

Connector

Connector

RJ-45

VITC in

Switch

Video SYNC

Separator

LM1881

RS-232C Driver

75ALS181

RS-422 Driver

uPD4721

Ethernet MAC/PHY

LAN91C111

10BASE-T /

100BASE-TX

VITC code VITC code

SYNC

SMPTE (VITC)

Reader/Writer

ICS2008B

H-SYNC

27MHz

VCXO

Time code

PLL

SYNC

Video signal

Generator

Bt864A

Mix

Composite

Video

Audio MCK

Generator

BU2280

Front panel

Key & LED

Logic control

Audio I/F

XCS-30XL

Video Clock

Parallel-I/F

Stereo DAC

PCM1716

DAIF

CS8402

15p

Parallel-I/F

Audio out

(Unbalanced)

Analogue out

(Balanced)

Digital out

A

B

C

68p

PC card

Connector

44p IDE

Connector

PCMCIA-I/F

for flash

memory or

HDD card

ATA-IDE I/F

for 2.5 inch

HDD

PIO-mode3

MPEG-Audio decoder

System Controller

SD-RAM (64Mb)

(Work Area)

SH4(162MHz)

512KBytes

Flash memory

(Firm ware)

Audio Data etc.

Video Data

MPEG2 Video CODEC

(MPEG1/2V~mp@ml)

HG75C013

SD-RAM (64Mb)

(Work Area)

Video

Encoder

ADV7170

Video out

Composite

S Connector

(Y/C)

Component

(Y/Cr/Cb)

D

E

4

ADJUSTMENT OF VIDEO SIGNAL LEVEL

Adjustment items

1. Y-signal of component video output

2. Cb-signal of component video output

3. C-signal of S-video output

Equipment

1. Oscilloscope with TV trigger.

2. PC-card in which 100% color-bar signal is recorded.

3. Coaxial video cable. (One side must be terminated at 75 Ohms.)

4. S-video cable. (One side must be terminated at 75 Ohms.)

Process

1. Connect the Oscilloscope to the Cb-signal of component video output and terminate at 75 Ohms.

2. Play “100% color-bar signal” file.

3. Adjust the Cb-signal of component video output level to 650mVp-p±40mVp-p (MAIN UNIT VR401)

4. Connect the Oscilloscope to the Y-signal of component video output and terminate at 75 Ohms.

5. Adjust the Y-signal of component video output level to 960mV

6. Connect the Oscilloscope to the C-signal of S-video output and terminate at 75 Ohms.

7. Adjust the color burst level of S-video output to 286mV

p-p±40mVp-p

p-p±30mVp-p

(MAIN UNIT VR403)

(MAIN UNIT VR402)

DN-V1700

5

DN-V1700

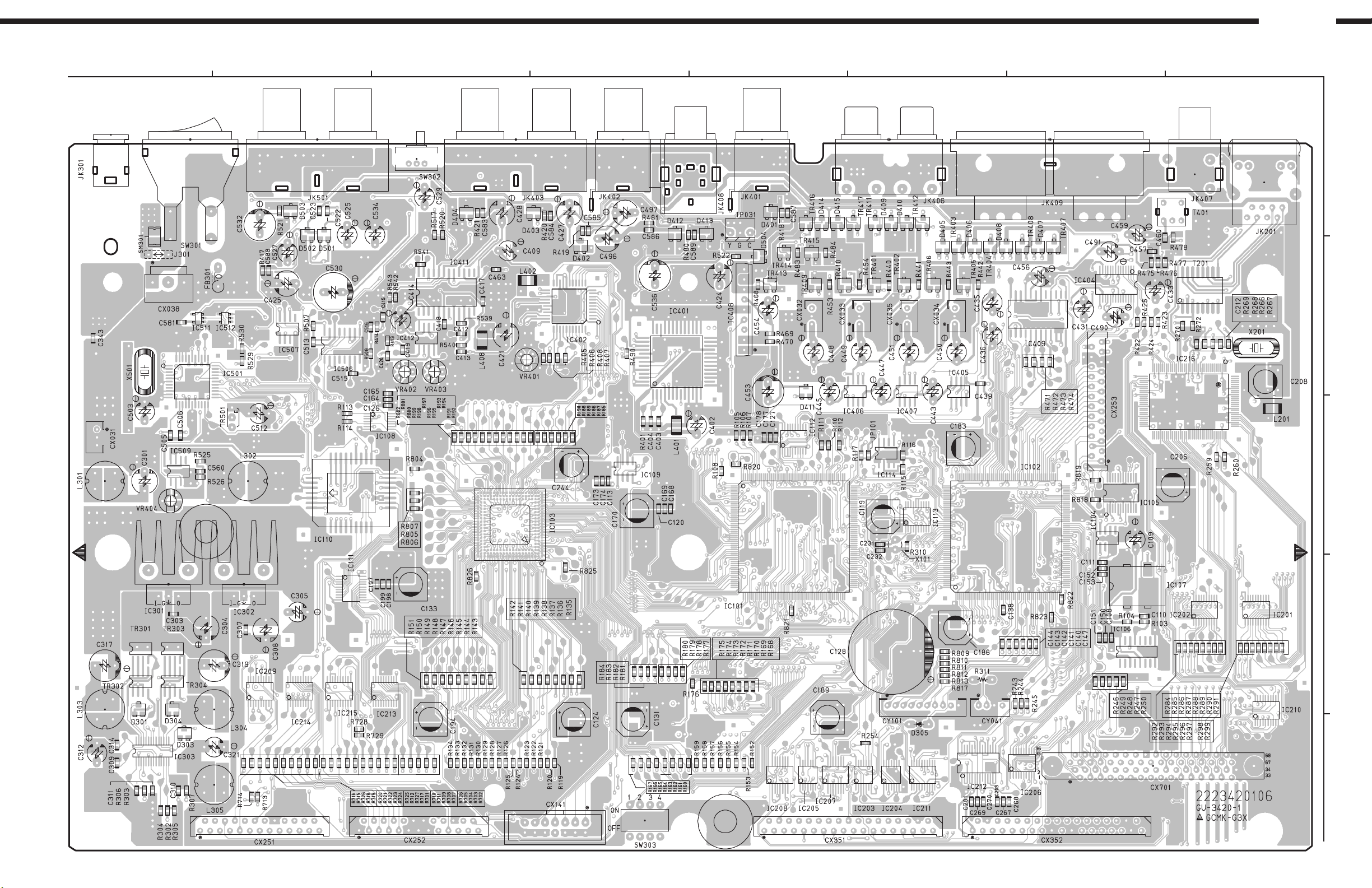

MAC ADDRESS

Each DN-V1700 is assigned own MAC address for network connection. The MAC address is described at the sticker on the

printing circuit board. (MAIN UNIT GU-3420A)

If the MAIN UNIT (GU-3420A) or FLASH ROM (IC110) is replaced to another one, reset the same MAC address and confirm it.

If the MAIN UNIT (GU-3420A) is replaced to another one and MAC address is reset, put the sticker described MAC address on

the same place of the MAIN UNIT.

Setting and confirmation of MAC address are enable by sending serial command from PC. The operation requires RS-232C

connection between the PC and DN-V1700.

Serial command “MA” is applied for the MAC address setting.

MAC address setting

<Format> “MACaddress” MA<CR><LF>

(MACaddress = hexadecimal numbers [0, . . ,9, a, . . . ,f ] of 12 digits)

<Reply> R<CR><LF>

<Details> Sets the DN-V1700’s MAC address. The new setting is reflected after the system is rebooted. This command is

only accepted in the stop mode. It is not accepted when a clip is playing. The contents of a setting of this

command become effective after a reboot.

Serial command “3?E” is applied for the MAC address setting.

Confirmation of MAC address

<Format> 3?E<CR><LF>

<Reply> MAC: 0005cd******<CR><LF>

R<CR><LF>

<Details> Reply the own MAC adddress.

6

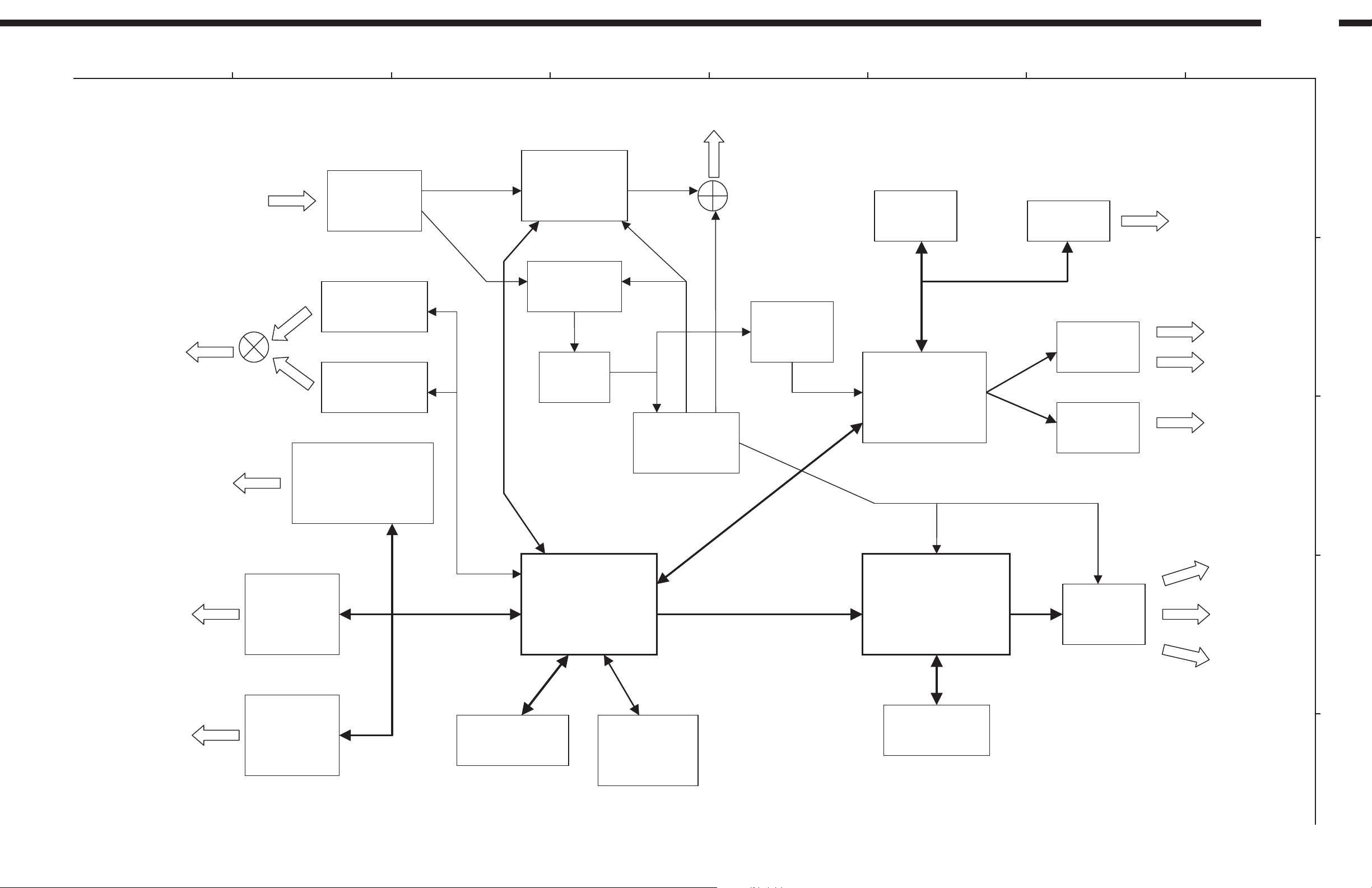

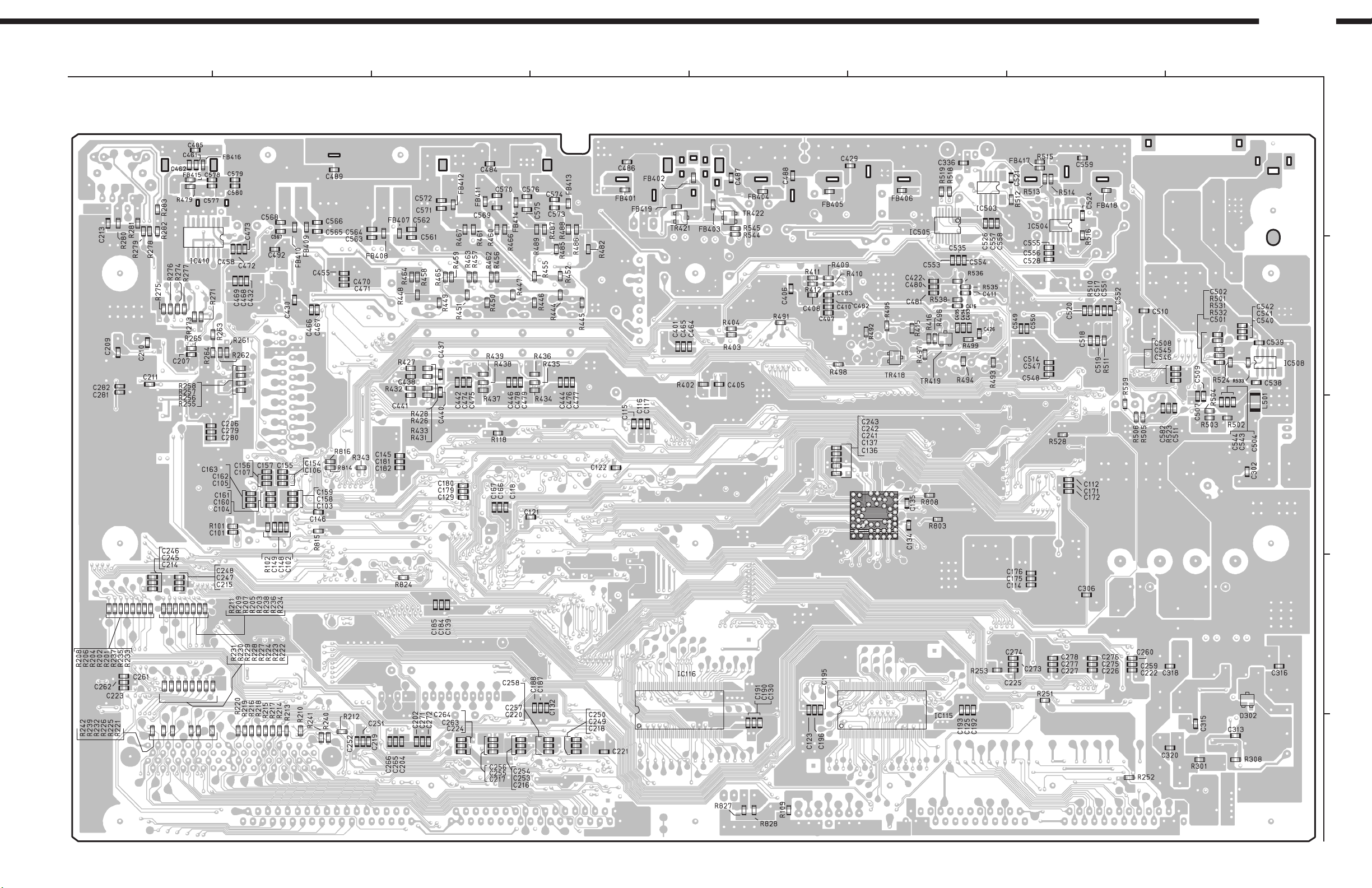

PRINTED WIRING BOARD

DN-V1700

1

GU-3420A MAIN UNIT Ass'y

2

3

4

5

76

8

A

B

C

D

E

COMPONENT SIDE

7

DN-V1700

1

2

3

4

5

76

8

A

B

C

D

E

FOIL SIDE

8

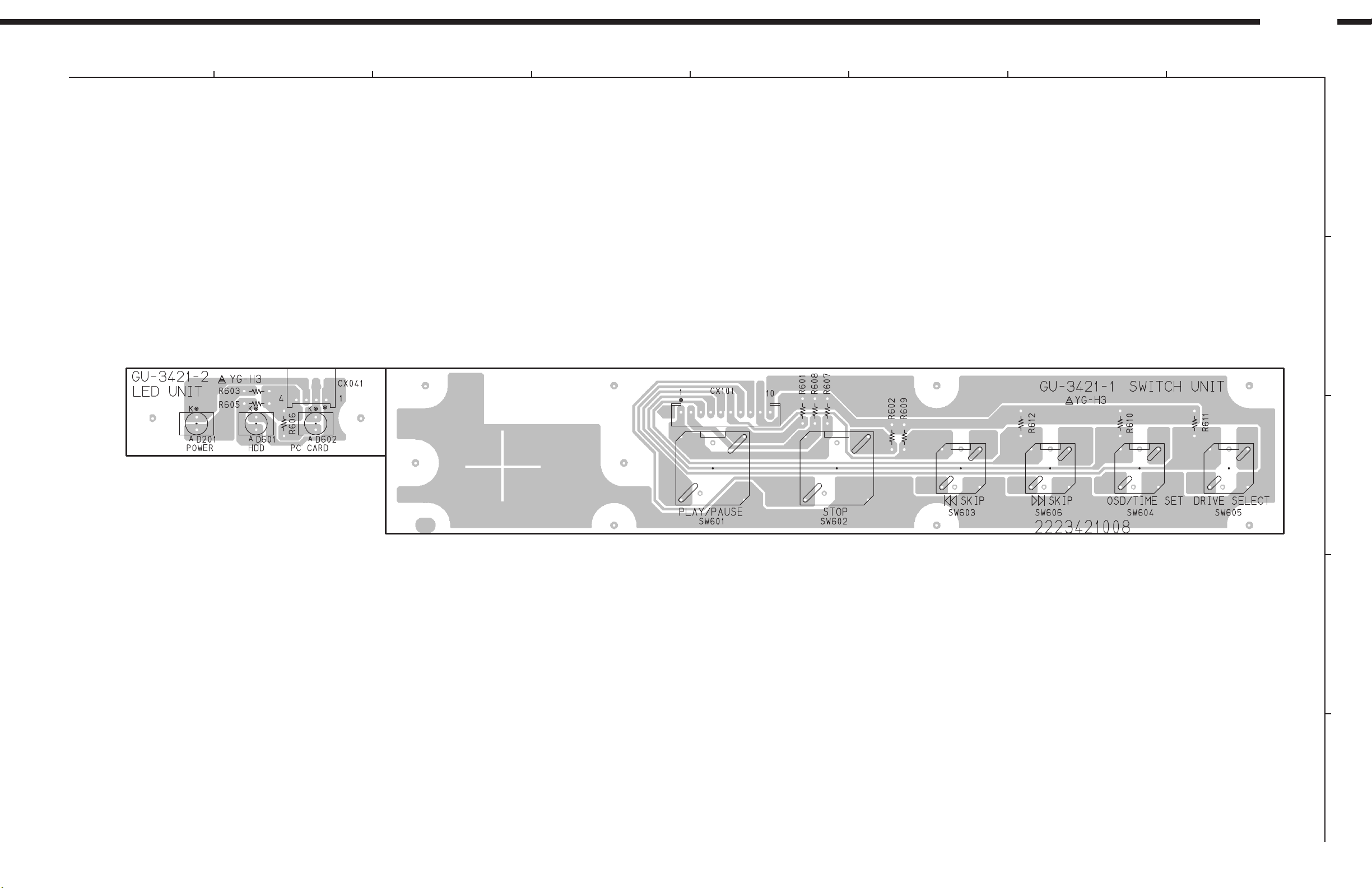

DN-V1700

1

GU-3421 PANEL UNIT Ass'y

2

3

4

5

76

8

A

B

COMPONENT SIDE

C

D

E

9

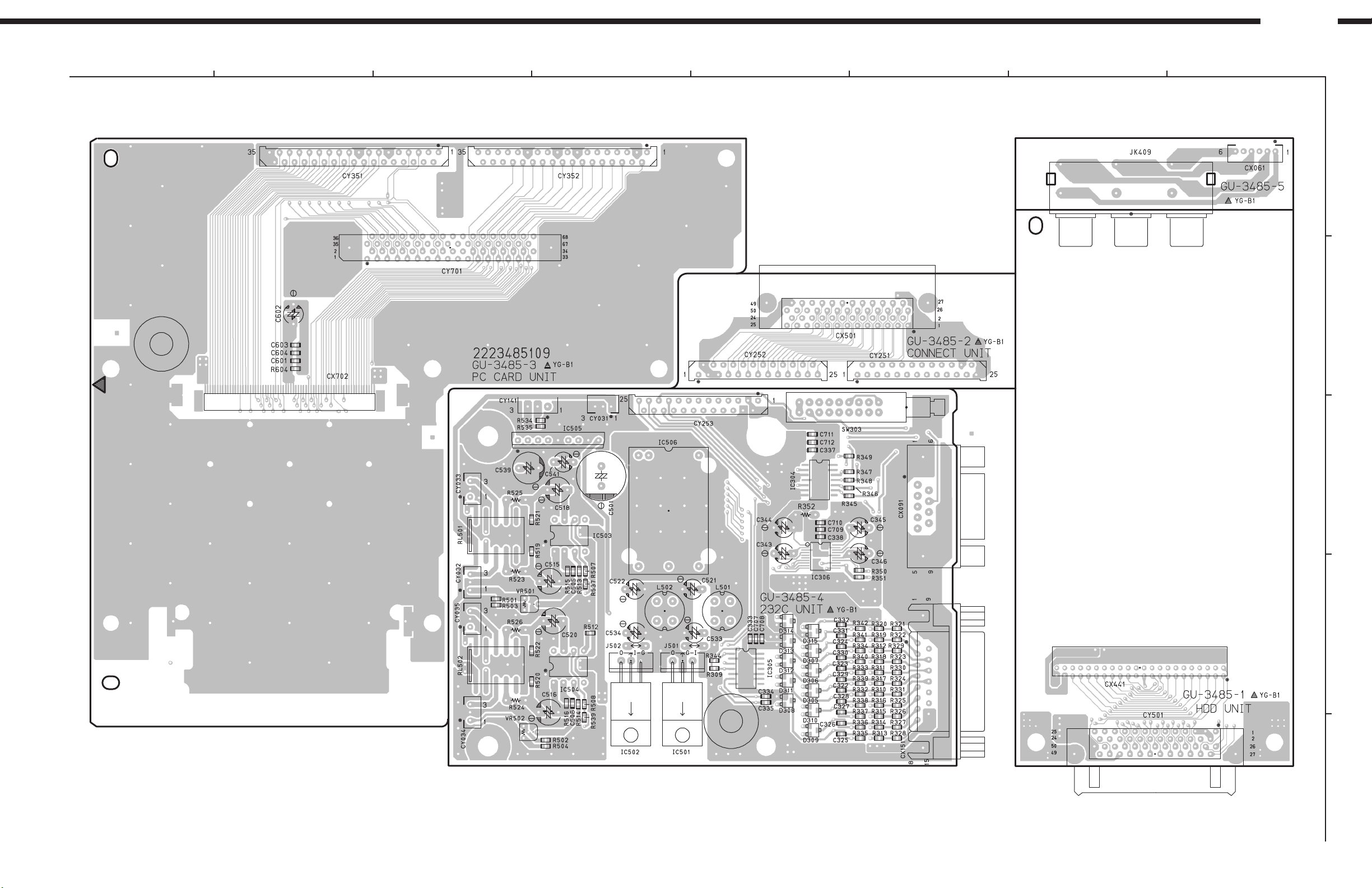

DN-V1700

1

GU-3485 PC HDD UNIT Ass'y

2

3

4

5

76

8

A

B

C

D

E

COMPONENT SIDE

10

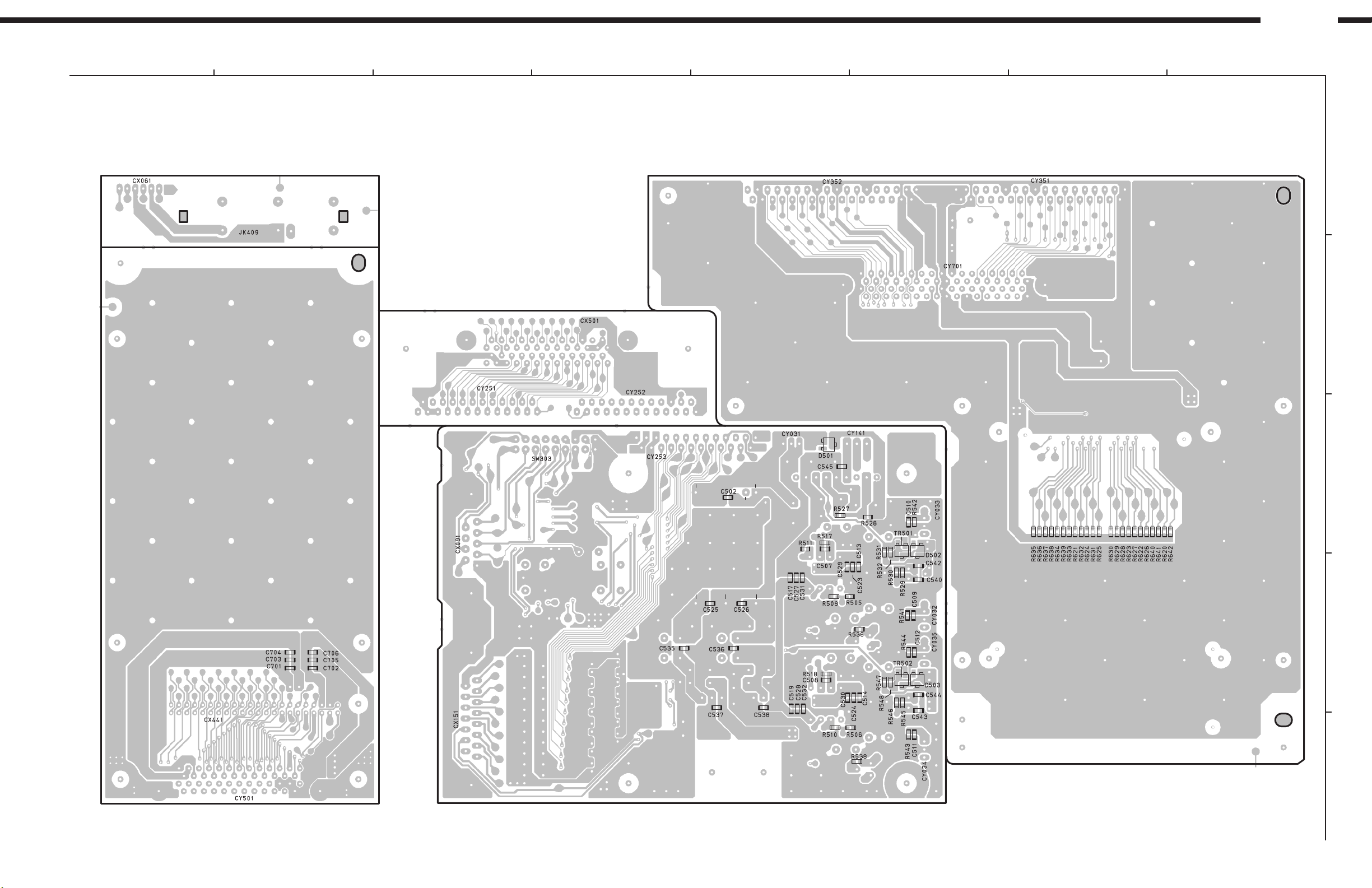

DN-V1700

1

2

3

4

5

76

8

A

B

C

D

E

FOIL SIDE

11

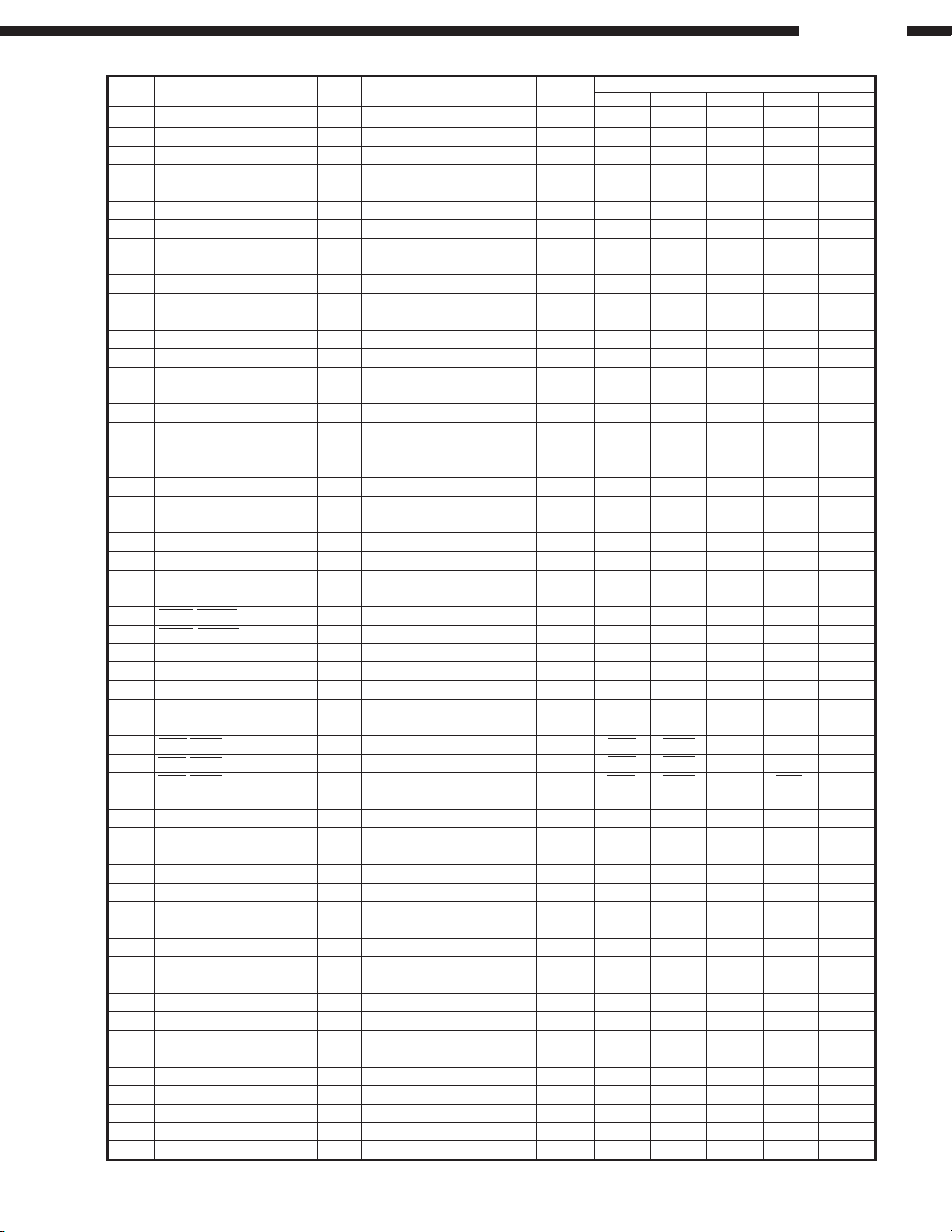

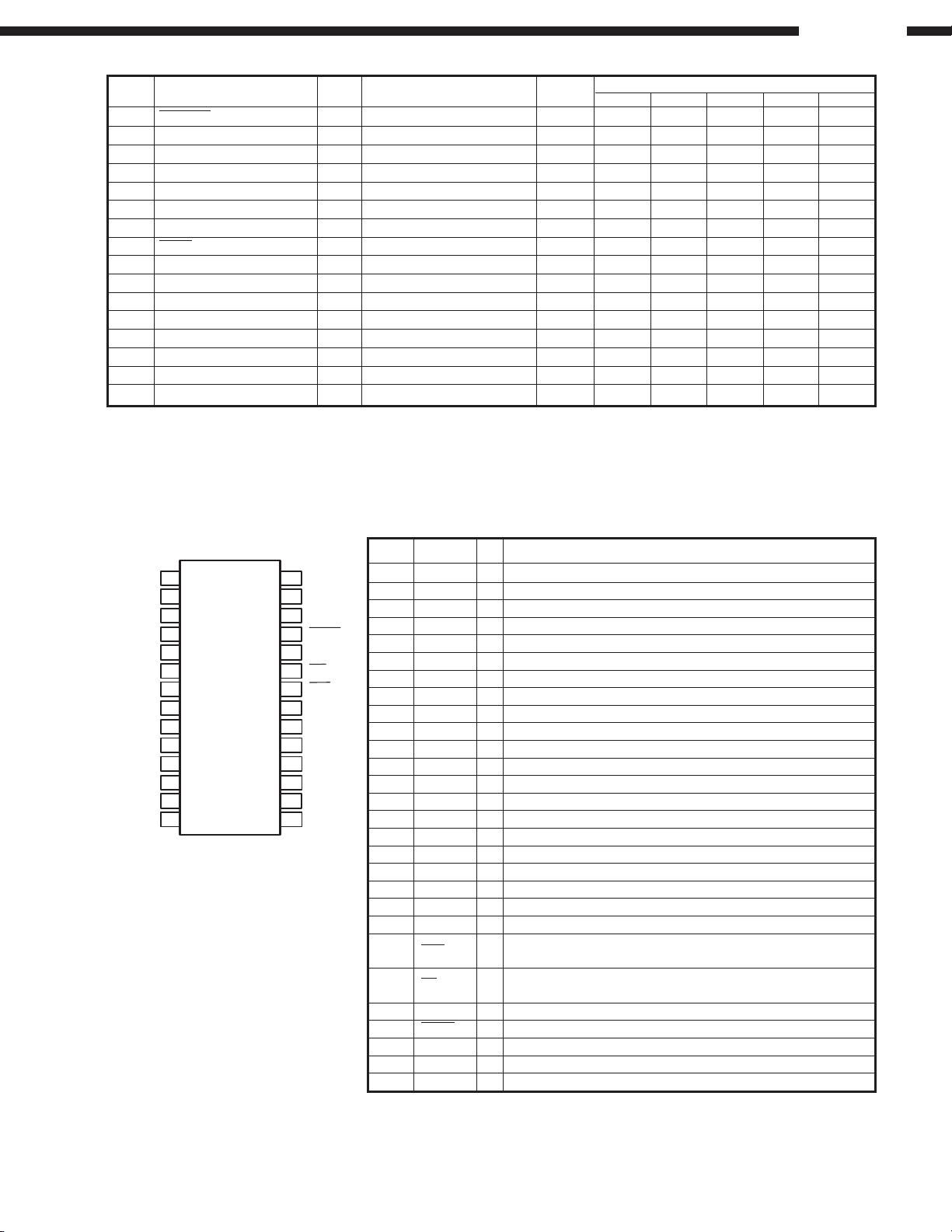

SEMICONDUCTORS

IC's

HH

HD6417750SF167 (IC101)

HH

Note: When this IC is defective,

replace P.W.B. Unit Ass'y.

BACK/BSREQ

BREQ/BSACK

RDY

RESET

CS0

CS1

CS4

CS5

CS6

D47

D32

D46

D33

D45

D34

D44

D35

D43

D36

D42

D37

D41

D38

D40

D39

D15

D14

D13

D12

D11

D10

EXTAL

XTAL

VSS-CPG

VDD-CPG(3.3V)

VSS-PLL1

VDD-PLL1(3.3V)

VSS-PLL2

VDD-PLL2(3.3V)

TDI

TRST

208

207

206

205

204

203

202

201

200

1

2

3

4

5

6

7

BS

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

D0

35

36

D1

37

38

D2

39

40

41

42

D3

43

44

45

46

D4

47

48

D5

49

D9

50

D6

51

52

5354555657585960616263646566676869707172737475767778798081828384858687888990919293949596979899

D8

D7

CKE

199

A17

TCK

198

A16

TMS

197

A15

TDO

ASEBRK/BRKACK

196

195

194

193

A14

A13

MD6/IOIS16

STATUS1

STATUS0A1A0

DACK1

DACK0

MD5/RAS2

MD4/CE2B

MD3/CE2A

192

191

190

189

188

187

186

185

184

183

182

181

TOP VIEW

VDD (INTERNAL 1.8V)

VSS (INTERNAL 0V)

VDDQ (IO 3.3V)

VSSQ (IO 0V)

A9A8A7

CKIO

A6A5A4A3A2

A12

A11

A10

A25

A24

A23

A22

A21

180

179

178

177

176

175

174

DRAK1

DRAK0

A20

173

A19

A18

172

171

CS3

CS2

SCK2/MRESET

MD7/TXD

170

169

168

167

RAS

MD8/RTS2

TCLKCACTS2

166

165

164

163

RD/WR

VDD-RTC(3.3V)

VSS-RTC

162

161

160

159

100

101

102

D23

EXTAL2

XTAL2

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

103

104

D24

D22

NMI

IRL3

IRL2

IRL1

IRL0

MD2/RXD2

MD1/TXD2

MD0/SCK

D63

D48

D62

D49

D61

D50

D60

D51

D59

D52

D58

D53

D57

D54

D56

D55

D31

D16

D30

D17

D29

D18

D28

D19

D27

D20

D26

D21

D25

DREQ1

DREQ0

RXD

DN-V1700

WE5/CAS5/DQM5

WE4/CAS4/DQM4

WE1/CAS1/DQM1

WE0/CAS0/DQM0

RD/CASS/FRAME

WE6/CAS6/DQM6

WE7/CAS7/DQM7/REG

WE2/CAS2/DQM2/IOICRD

WE3/CAS3/DQM3/IOICWR

HD6417750SF167 Terminal Function

Pin No.

Pin Name FunctionI/O

Reset

SRAM DRAM SDRAM PCMCIA

1 PDY I Bus preparation RDY RDY RDY

2 RESET I RESET RESET

3 CS0 O Chip select 0 CS0 CS0

4 CS1 O Chip select 1 CS1 CS1

5 CS4 O Chip select 4 CS4 CS4

6 CS5 O Chip select 5 CS5 CE1A CS5

7 CS6 O Chip select 6 CS6 CE1B CS6

8 BS O Bus start BS BS BS BS BS

9 VDDQ Power IO VDD (3.3V)

10 VSSQ Power IO GND (0V)

11 D47 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

12 D32 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

13 VDD Power Internal VDD (1.8V)

14 VSS Power Internal GND (0V)

15 D46 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

16 D33 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

17 D45 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

18 D34 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

19 D44 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

20 D35 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

21 VDDQ Power IO VDD (3.3V)

22 VSSQ Power IO GND (0V)

23 D43 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

Memory Interface

MPX

12

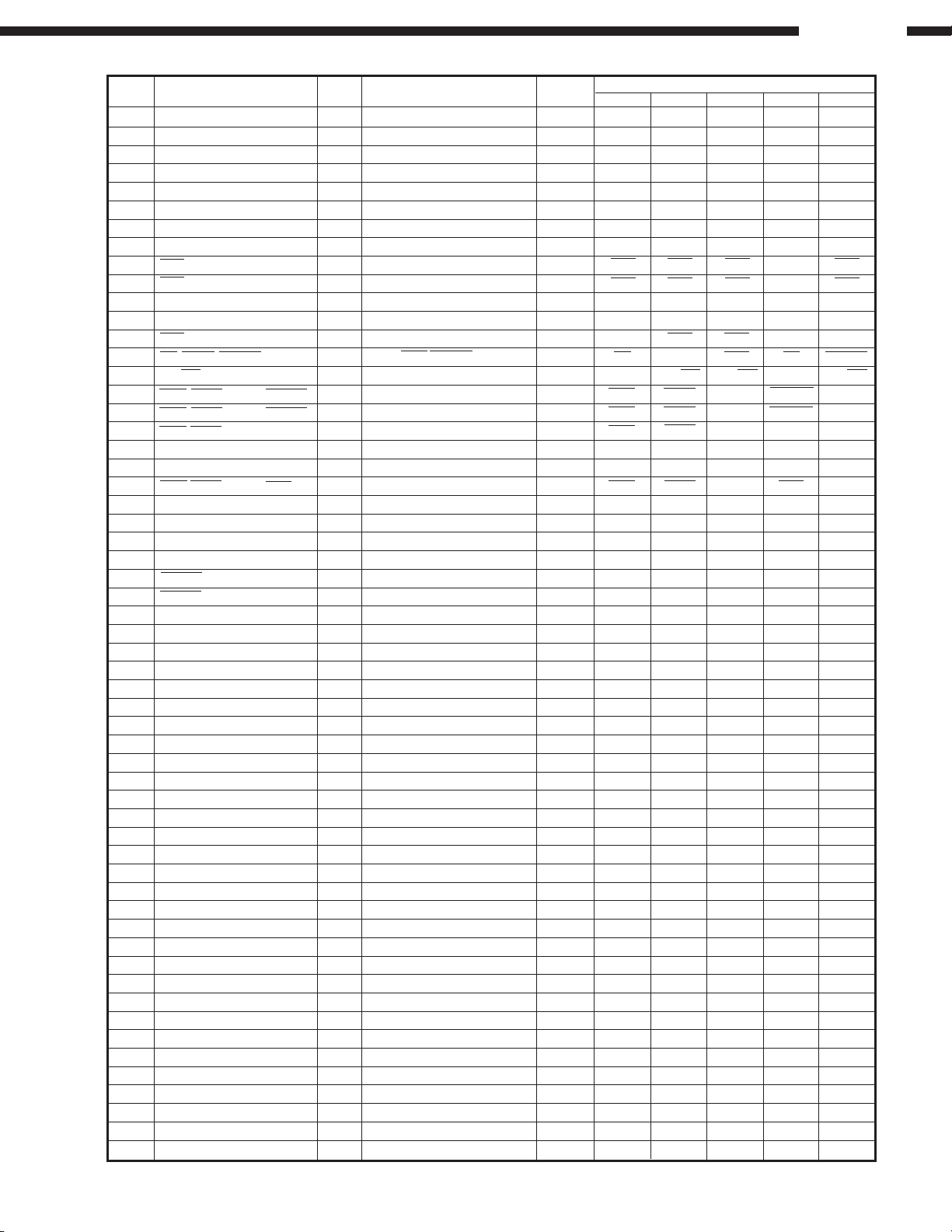

DN-V1700

Pin No.

24 D36 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

25 D42 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

26 D37 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

27 D41 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

28 D38 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

29 D40 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

30 D39 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

31 VDDQ Power IO VDD (3.3V)

32 VSSQ Power IO GND (0V)

33 D15 I/O Data A15

34 D0 I/O Data A0

35 D14 I/O Data A14

36 D1 I/O Data A1

37 D13 I/O Data A13

38 D2 I/O Data A2

39 VDD Power Internal VDD (1.8V)

40 VSS Power Internal GND (0V)

41 D12 I/O A12

42 D3 I/O A3

43 VDDQ Power IO VDD (3.3V)

44 VSSQ Power IO GND (0V)

45 D11 I/O Data A11

46 D4 I/O Data A4

47 D10 I/O Data A10

48 D5 I/O Data A5

49 D9 I/O Data A9

50 D6 I/O Data A6

51 BACK/BSREQ O Bus recognition/Bus request

52 BREQ/BSACK I Bus request/Bus recognition

53 D8 I/O Data A8

54 D7 I/O Data A7

55 CKE O Clock out enable CKE

56 VDDQ Power IO VDD (3.3V)

57 VSSQ Power IO GND (0V)

58 WE5/CAS5/DQM5 O D47-D40 select signal WE5 CAS5 DQM5

59 WE4/CAS4/DQM4 O D39-D32 select signal WE4 CAS4 DQM4

60 WE1/CAS1/DQM1 O D15-D8 select signal WE1 CAS1 DQM1 WE1

61 WE0/CAS0/DQM0 O D7-D0 select signal WE0 CAS0 DQM0

62 A17 O Address

63 A16 O Address

64 A15 O Address

65 VDD Power Internal VDD (1.8V)

66 VSS Power Internal GND (0V)

67 A14 O Address

68 A13 O Address

69 VDDQ Power IO VDD (3.3V)

70 VSSQ Power IO GND (0V)

71 A12 O Address

72 A11 O Address

73 A10 O Address

74 A9 O Address

75 A8 O Address

76 A7 O Address

77 CKIO O Clock output CKIO

78 VDDQ Power IO VDD (3.3V)

79 VSSQ Power IO GND (0V)

80 A6 O Address

Pin Name FunctionI/O

Reset

SRAM DRAM SDRAM PCMCIA

Memory Interface

MPX

13

DN-V1700

Pin No.

81 A5 O Address

82 A4 O Address

83 A3 O Address

84 A2 O Address

85 DRAK1 O DMAC1 request recognition

86 DRAK0 O DMAC0 request recognition

87 VDDQ Power IO VDD (3.3V)

88 VSSQ Power IO GND (0V)

89 CS3 O Chip select 3 CS3 (CS3) CS3 CS3

90 CS2 O Chip select 2 CS2 (CS2) CS2 CS2

91 VDD Power Internal VDD (1.8V)

92 VSS Power Internal GND (0V)

93 RAS O RAS RAS RAS

94 RD/CASS/FRAME O Read/CAS/FRAME OE CAS OE FRAME

95 RD/WR O Read/Write RD/WR RD/WR RD/WR

96 WE2/CAS2/DQM2/IOICRD O D23-D16 select signal WE2 CAS2 DQM2 ICIORD

97 WE3/CAS3/DQM3/IOICWR O D31-D24 select signal WE3 CAS3 DQM3 ICIOWR

98 WE6/CAS6/DQM6 D55-D48 select signal WE6 CAS6 DQM6

99 VDDQ Power IO VDD (3.3V)

100 VSSQ Power IO GND (0V)

101 WE7/CAS7/DQM7/REG O D63-D56 select signal WE7 CAS7 DQM7 REG

102 D23 I/O Data A23

103 D24 I/O Data A24

104 D22 I/O Data A22

105 RXD I SCI data input

106 DREQ0 I Request from DMAC0

107 DREQ1 I Request from DMAC1

108 D25 I/O Data A25

109 D21 I/O Data A21

110 D26 I/O Data

111 D20 Data A20

112 D27 Data

113 VDDQ Power IO VDD (3.3V)

114 VSSQ Power IO GND (0V)

115 D19 Data A19

116 D28 I/O Data

117 VDD Power Internal VDD (1.8V)

118 VSS Power Internal GND (0V)

119 D18 I/O Data A18

120 D29 I/O Data

121 D17 I/O Data A17

122 D30 I/O Data

123 D16 I/O Data A16

124 D31 I/O Data

125 VDDQ Power IO VDD (3.3V)

126 VSSQ Power IO GND (0V)

127 D55 I/O Data

128 D56 I/O Data

129 D54 I/O Data

130 D57 I/O Data

131 D53 I/O Data

132 D58 I/O Data

133 D52 I/O Data

134 D59 I/O Data

135 VDDQ Power IO VDD (3.3V)

136 VSSQ Power IO GND (0V)

137 D51 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

Pin Name FunctionI/O

Reset

SRAM DRAM SDRAM PCMCIA

Memory Interface

MPX

14

DN-V1700

Pin No.

138 D60 I/O Data

139 D50 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

140 D61 I/O Data

141 D49 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

142 D62 I/O Data

143 VDD Power Internal VDD (1.8V)

144 VSS Power Internal GND (0V)

145 D48 I/O Data/Port (Port) (Port) (Port) (Port) (Port)

146 D63 I/O Data

147 VDDQ Power IO VDD (3.3V)

148 VSSQ Power IO GND (0V)

149 MD0/SCK I/O Mode/SCI clock MD0 SCK SCK SCK SCK SCK

150 MD1/TXD2 I/O Mode/SCIF data output MD1 TXD2 TXD2 TXD2 TXD2 TXD2

151 MD2/RXD2 I Mode/SCIF data input MD2 RXD2 RXD2 RXD2 RXD2 RXD2

152 IRL0 I Interrupt 0

153 IRL1 I Interrupt 1

154 IRL2 I Interrupt 2

155 IRL3 I Interrupt 3

156 NMI I Non-maskable interrupt

157 XTAL2 O RTC crystal oscillator pin

158 EXTAL2 I RTC crystal oscillator pin

159 VSS-RTC Power RTC GND (0V)

160 VDD-RTC Power RTC VDD (3.3V)

161 CA I (SH7750S only), pull-up to

162 VSS Power Internal GND (0V)

163 VDDQ Power IO VDD (3.3V)

164 CTS2 I/O SCIF data control (CTS)

165 TCLK I/O RTC/TMU Clock

166 MD8/RTS2 I/O Mode/SCIF data control (RTS) MD8 RTS2 RTS2 RTS2 RTS2 RTS2

167 MD7/TXD I/O Mode/SCI data output MD7 TXD TXD TXD TXD TXD

168 SCK2/MRESET I/O SCIF clock/Manual reset MRESET SCK2 SCK2 SCK2 SCK2 SCK2

169 VDD Power Internal VDD (1.8V)

170 VSS Power Internal GND (0V)

171 A18 O Address

172 A19 O Address

173 A20 O Address

174 A21 O Address

175 A22 O Address

176 A23 O Address

177 VDDQ Power IO VDD (3.3V)

178 VSSQ Power IO GND (0V)

179 A24 O Address

180 A25 O Address

181 MD3/CE2A I/O Mode/PCMCIA-CE MD3 CE2A

182 MD4/CE2B I/O Mode/PCMCIA-CE MD4 CE2B

183 MD5/RAS2 I/O Mode/RAS (DRAM) MD5 RAS2

184 DACK0 O DMAC0 Bus recognition

185 DACK1 O DMAC1 Bus recognition

186 A0 O Address

187 VDDQ Power IO VDD (3.3V)

188 VSSQ Power IO GND (0V)

189 A1 O Address

190 STATUS0 O Status

191 STATUS1 O Status

192 MD6/IOIS16 I Mode/IOIS16 (PCMCIA) MD6 IOIS16

Pin Name

Hardware standby request

3.3V for SH7550

FunctionI/O

Reset

SRAM DRAM SDRAM PCMCIA

Memory Interface

ACCSIZE0

ACCSIZE1

ACCSIZE2

MPX

15

DN-V1700

Pin No.

Pin Name

FunctionI/O

193 ASEBRK/BRKACK I/O Pin break/Acknowledge

194 TD0 O Data out

195 VDD Power Internal VDD (1.8V)

196 VSS Power Internal GND (0V)

197 TMS I Mode

198 TCK I Clock

199 TDI I Data in

200 TRST I Reset

201 VDD-PLL2 Power PLL2 VDD (3.3V)

202 VSS-PLL2 Power PLL2 GND (0V)

203 VDD-PLL1 Power PLL1 VDD (3.3V)

204 VSS-PLL1 Power PLL1 GND (0V)

205 VDD-CPG Power CPG VDD (3.3V)

206 VSS-CPG Power CPG GND (0V)

207 XTAL O Crystal oscillator

208 EXTAL I

External clock/Crystal oscillator

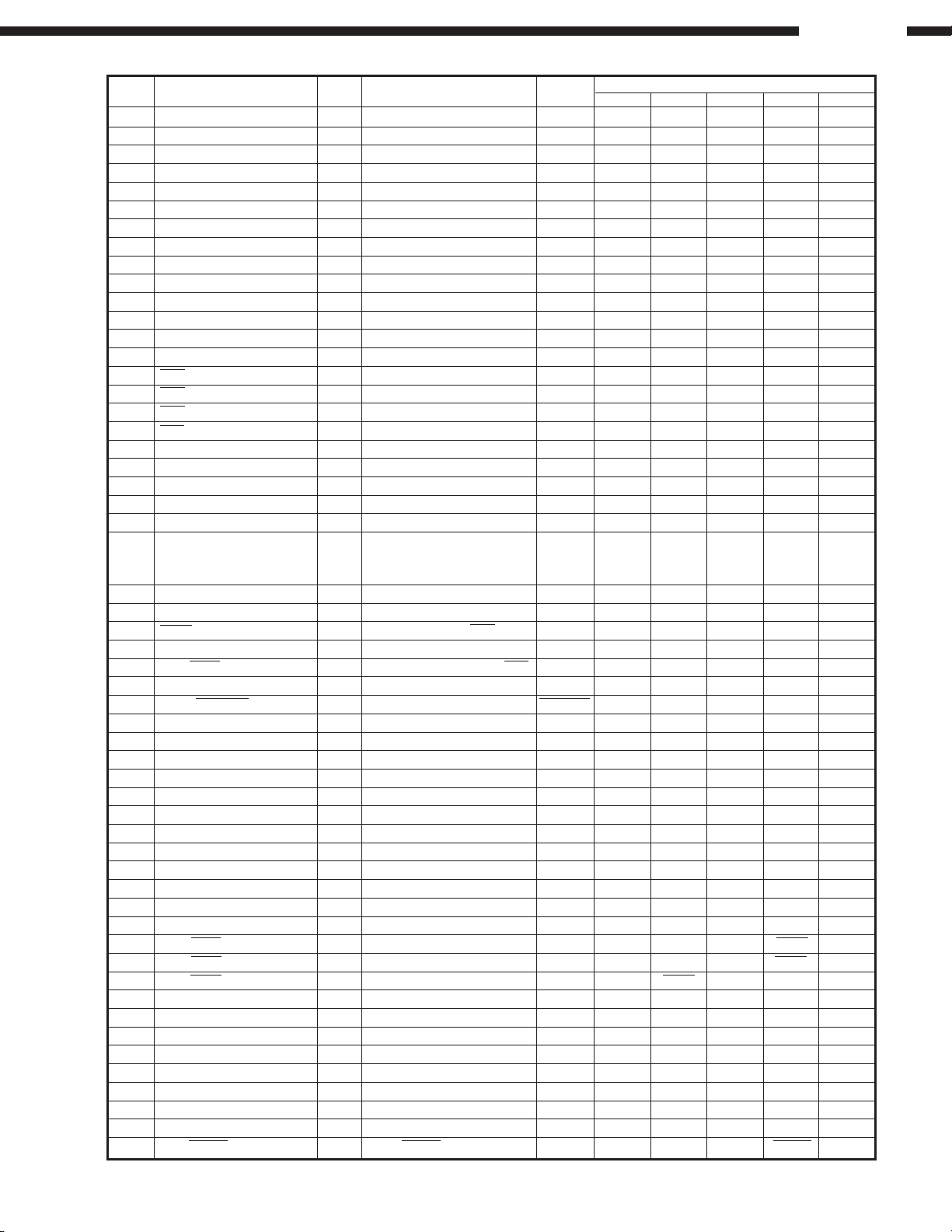

PCM1716E (IC404)

Pin Description

Pin Name FunctionPin No. I/O

1

LRCIN ML/IIS

DIN MC/DM1

2

BCKIN MD/DM0

3

4

CLKO

5

XTI MODE

XTO CS/IWO

6

DGND RST

7

V

DD

8

9

CC

2R VCC2L

V

AGND2R AGND2L

10

11

EXTR

12

NC NC

13

OUT

RV

V

14

AGND1 V

28

27

26

25

24

23

22

21

20

19

18

17

16

15

MUTE

ZERO

EXTL

OUT

CC

L

1

1 LRCIN I

2 DIN I Serial audio data input. *1

3 BCKIN I Bit clock input for serial audio data. *1

4 CLKO O Buffered output of oscillator. Equivalent to system clock.

5 XTI I Oscillator input (External clock input).

6 XTO O Oscillator output.

7 DGND Digital ground.

8VDD Digital power. +5V

9VCC2R Digital power. +5V

10 AGND2R Analog power. +5V

11 EXTR O R-ch, common pin of analog output amp.

12 NC No connection.

13 VOUTR O R-ch, analog voltage output of audio signal.

14 AGND1 Analog ground.

15 VCC1 Analog power. +5V

16 VOUTL O L-ch, analog voltage output of audio signal.

17 NC No connection.

18 EXTL O R-ch, common pin of analog output amp.

19 AGND2L Analog ground.

20 VCC2L Analog power. +5V

21 ZERO O Zero data flag.

22 RST I

23 CS/IWO I

24 MODE I Mode control Select. (H: Software, L: Hardware) *2

25 MUTE I Mute control. *2

26 MD/DM0 I Mode control, DATA/De-emphasis selection1. *2

27 MC/DM1 I Mode control, BCK/De-emphasis selection2. *2

28 ML/IIS I Mode control, WDCK/input format selection. *2

Note1: Pins 1,2,3; Schmitt Trigger input.

Note2: Pins 22,24,25,26,27,28; Schmitt Trigger input with pull-up resister.

Note3: Pins 23; Schmitt Trigger input with pull-down resister.

Reset

SRAM DRAM SDRAM PCMCIA

Memory Interface

MPX

Left & Right clock input. This clock is equal to the sampling rate-fs.*1

Reset. When this pin is low, the DF and modulators are held

in reset. *2

Chip select/input format selection.

When this pin is low, the Mode Control is effective. *3

16

Loading...

Loading...