Denon DN-C680 Service Manual

SERVICE MANUAL

For U.S.A., Canada &

Europe model

SUPPLEMENT

MODEL

DN-C680

CD PLAYER

We have two version of DN-C680. The new version of

DN-C680 is replaced discontinued parts of the old version. (CD mechanism, microprocessor and D/A converter etc.)

Serial number of new version are renumbered from

*****50001.

This service manual is supplement for new version of

DN-C680 and only mentioned difference between old

and new version. So, please refer to previously issued

service manual of DN-C680 when servicing.

Ver . 1

DN‑C680には新旧の2つのバージョンがあります。

旧

バージョン(

なった部品(CDメカ、マイコン等)を置き換えたものが

新バージョン

本書は、

ていますので、

ービスマニュアル

注 意

サービスをおこなう前に、このサービスマニュアルを

必ずお読みください。本機は、火災、感電、けがなど

に対する安全性を確保するために、さまざまな配慮を

おこなっており、また法的には「電気用品安全法」に

もとづき、所定の許可を得て製造されております。

従ってサービスをおこなう際は、これらの安全性が維

持されるよう、このサービスマニュアルに記載されて

いる注意事項を必ずお守りください。

製造番号*****50000以前)で生産中止に

(製造番号*****50001以降)です。

新バージョンで

サービスの際は本書と共に

DN‑C680を

変更された内容のみを記載し

ご用意願います。

既発行のサ

●

For purposes of improvement, specifications and

design are subject to change without notice.

●

Please use this service manual with referring to the

operating instructions without fail.

●

Some illustrations using in this service manual are

slightly different from the actual set.

16-11, YUSHIMA 3-CHOME, BUNKYOU-KU, TOKYO 113-0034 JAPAN

●

本機の仕様は性能改良のため、予告なく変更すること

があります。

●

新バージョン用の補修用性能部品の保有期間は、製造

打切後8年です。

●

修理の際は、必ず取扱説明書を参照の上、作業を行っ

てください。

●

本文中に使用しているイラストは、説明の都合上現物

と多少異なる場合があります。

X0179V.01 DE/CDM 0308

SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

LEAKAGE CURRENT CHECK

Before returning the unit to the customer, make sure you make either (1) a leakage current check or (2) a line to chassis

resistance check. If the leakage current exceeds 0.5 milliamps, or if the resistance from chassis to either side of the

power cord is less than 460 kohms, the unit is defective.

LASER RADIATION

Do not stare into beam or view directly with optical instruments, class 3A laser product.

500V

2DN-C680

(1)

(2)

1M

(1)

(2)

2

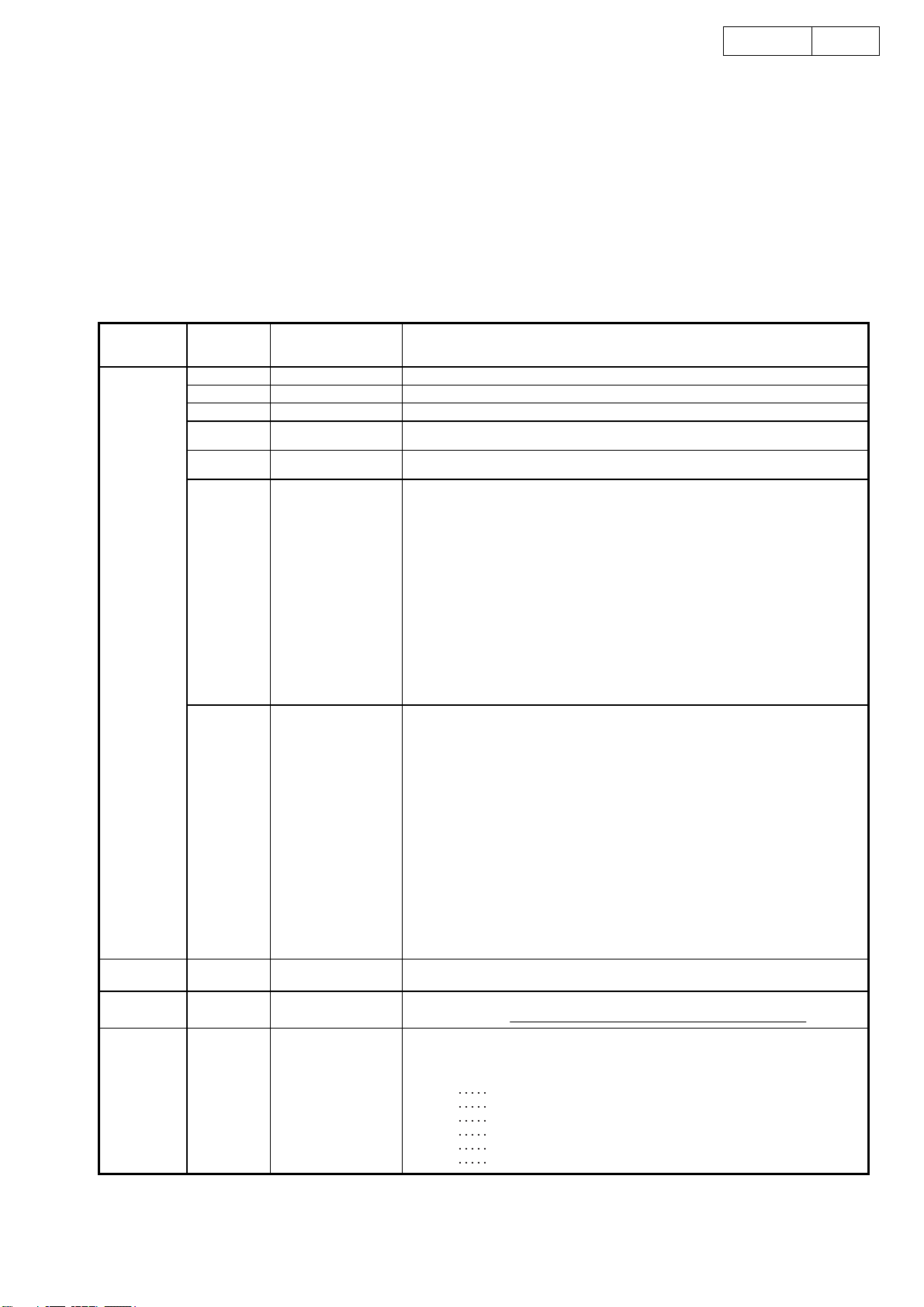

BLOCK DIAGRAM

3DN-C680

ACD25

GU-3578-2

4M DRAM

AN22002A

ACD27

M66005AFP

+7V_D1

+3.3V_D1

MN102H60KDA

GU-3578-1

+6V

+3.3V

XCS05XL

YM3437

GU-3578-3

PCM1738

RS-232C

HD26C32A

HD26LS31FP

RS-232C

RS-422ARS-422A

+5V_A1

+5V_A2

FOR DSP, MECHA

-

12V_A

+12V_A +16V_A

Not use

NJM5532

NJM5532

3

CONFIRMING THE SERVO

j

j

p

j

p

CAUTION:

The Optical Pick-up used for CD player may invite defection by an external noise, such as electrostatic, etc.,

please pay the following attention.

1. Use a conductive mat on a working table to avoid electrostatic damage.

2. A working personnel should use a wrist strap to ground human body.

3. Tools, etc., specially for a soldering iron must use with its tip grounded and without leakage of electricity.

Utmost care must be taken to your clothes for electrostatic damaging in a low humidity environment.

Required Measuring Implement

1. Dual trace oscilloscope

2. Reference disc (TCD784 or CO-74176)

1. Actuating the Service Program and Servo Confirming Method

1. Turn the power switch off.

2. While simultaneously pushing the STANDBY/CUE button and PLAY/PAUSE button, turn the power on.

3. Displayed indication is version number of microcomputer program.

3. Turn SELECT knob. Display shows "

4 figures on the left are program version of remote control, and 4 figures on the right are program version of main body

4. As the tray opens, set the adjustment disc (TCD784 or CO-74176)

mechanism.

5. Turn SELECT knob ("

4. Turn SELECT knob. Display shows "

Tracking error signal can be observed with the connection below. (Fig1)

5. As the tray opens, set the adjustment disc (TCD784 or CO-74176)

6. Turn SELECT knob ("

6. Turn SELECT knob ("

HF signal can be observed with the connection below. (Fig2)

Tracking error signal can be observed with the connection below. (Fig1)

7. Turn SELECT knob ("

7. Turn SELECT knob ("

By pressing button servo automatic adjustment value can be called. (Ref. Table below)

" is displayed), also, press PLAY/PAUSE button.

" is displayed), also, press PLAY/PAUSE button.

" is displayed), also, press PLAY/PAUSE button.

" is displayed), also, press PLAY/PAUSE button.

" is displayed), also, press PLAY/PAUSE button.

HF signal can be observed with the connection below. (Fig2)

8. Turn SELECT knob ("

By pressing button servo automatic adjustment value can be called. (Ref. Table below)

TP101

VREF

TP101

VREF

NC

HF

NC

TE

NC

HF

FE

TE

NC

FE

1

2

3

1

4

2

5

3

6

4

5

6

" is displayed), also, press PLAY/PAUSE button.

Oscilloscope

Oscilloscope

Fig1 Fig2

" and each pressing of PLAY button opens or closes the tray.

" and each pressing of PLAY button opens or closes the tray.

TP101

NC

VREF

TP101

HF

NC

TE

VREF

NC

HF

FE

TE

NC

FE

1

2

3

1

4

2

5

3

6

4

5

6

Oscilloscope

Oscilloscope

4DN-C680

TRACK Portion

Fig1 Fig2

Indication

TRACK Portion

Indication

04

04

Adjustment

Item

Error Code 00

Focus Gain (FG) 125 ~728 01

Focus Balance (FBAL) 120 ~ 120 02

Error Code 00

Focus Offset (FOFS) 57 ~ 57 03

Focus Gain (FG) 125 ~728 01

Tracking Gain (TG) 101 ~ 808 04

Focus Balance (FBAL) 120 ~ 120 02

Tracking Balance (TBAL) 105 ~ 105 05

Focus Offset (FOFS) 57 ~ 57 03

Tracking Offset (TOFS) 31 ~ 31 06

Tracking Gain (TG) 101 ~ 808 04

* When adjustment range exceeds, replace pick-up.

Tracking Balance (TBAL) 105 ~ 105 05

Adjustment

Item

ustment Value

Ad

indication

at S and F

ustment Value

Ad

ortions.

indication

at S and F portions.

ustment Item

Ad

No. indication

at M

ortion.

Adjustment Item

No. indication

at M portion.

Tracking Offset (TOFS) 31 ~ 31 06

* When adjustment range exceeds, replace pick-up.

4

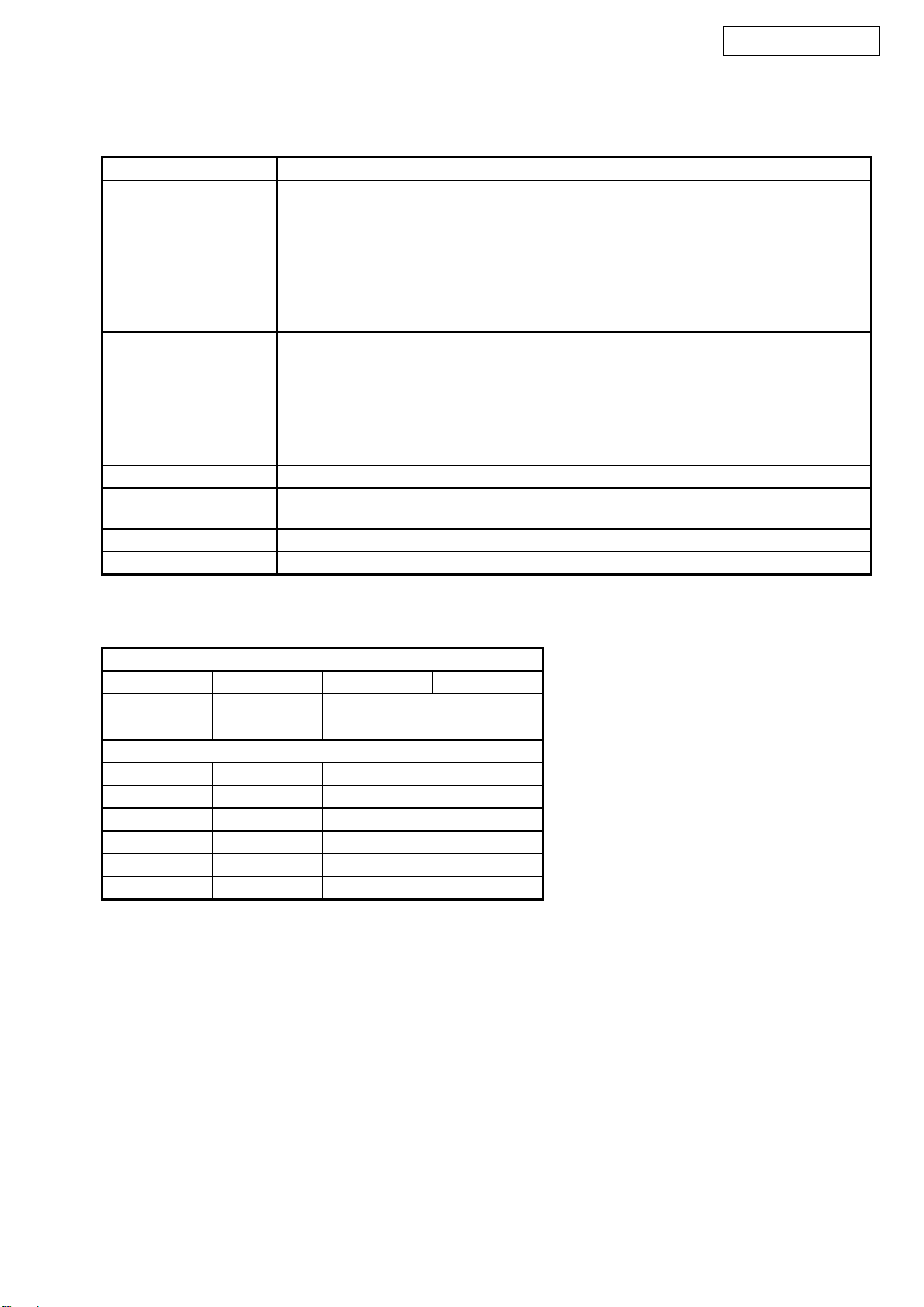

2. What is Service Program

Service program is a special program intended for confirming servo.

3. Contents of Service Program

While simultaneously pushing the STANDBY/CUE and PLAY/PAUSE buttons, turn the power on. (TRACK Indication “00”)

After actuating the service program, select an aiming process number with the SELECT KNOB, PITCH button, and TIME

button, and push the PLAY/PAUSE button to execute processing, The process number is then displayed on the TRACK

indication portion.

Work No.

(TRACK

Indication)

01 OPEN/CLOSE Performs OPEN/CLOSE each tome when the PLAY/PAUSE button is pushed.

02 Tracking Error Check tracking error signal, then performs the Automatic Adjustment.

03 HF Signal Check HF signal.

04

05

06

SELECT knob

07

PITCH 08 CHUCKING Test

TIME 09

REPEAT 11 Error code check

Function Contents

Automatic

Adjustment call

Cleaning of

Pick-up Lens

Focus Gain Changing Select Gain with search dial. Press PLAY/PAUSE button, the display lights that will

Tracking Gain

Changing

Heat Run

(No Skip Check)

Turn the Search dial to display the Automatic adjustment data.

Tray opens and pick-up moves out of mechanism, and clean the lens.

be newly memory in EEPROM.

when select data becomes big or small, the Gain is up or down.

In normally, do not change the data that is setted by 750.0.

The set No. and frequency in the EEPROM are storred as below:

No. Frequency No. Frequency

(SEC indicator) (FRAME indicator) (SEC indicator) (FRAME indicator)

-

7 477 Hz 1 847 Hz

-

6 509 Hz 2 956 Hz

-

5 543 Hz 3 1079 Hz

-

4 579 Hz 4 1218 Hz

-

3 618 Hz 5 1375 Hz

-

2 659 Hz 6 1552 Hz

-

1 703 Hz 7 1753 Hz

0 750 Hz 8 1978 Hz

Select Gain with Search dial. Press PLAY/PAUSE button, the display lights that will

be newly memory in EEPROM.

When select data becomes big or small, the Gain is up or down.

In normally, do not change the data that is setted by 1000.0.

When sound out is occured by oscillation, please raise gain.

But there is sound out easily by defective disc.

The set No. and frequency in the EEPROM are storred as below:

No. Frequency No. Frequency

(SEC indicator) (FRAME indicator) (SEC indicator) (FRAME indicator)

-

7 637 Hz 1 1129 Hz

-

6 679 Hz 2 1274 Hz

-

5 724 Hz 3 1439 Hz

-

4 772 Hz 4 1624 Hz

-

3 824 Hz 5 1834 Hz

-

2 879 Hz 6 2070 Hz

-

1 938 Hz 7 2337 Hz

0 1000 Hz 8 2638 Hz

Repeats OPEN/CLOSE of tray, servo ON, and TOC read and displays the number

of the tray OPEN/CLOSE times with the Time indicator.

Repeats OPEN/CLOSE of tray, repeats playing the first and the last programs of

music on the disc. When an error occurs, displays error code and stops.

Turn the search dial to display the logging error codes in the occurred order.

Kinds of displayed Error Code

(1) Error Code Table (Appears only at Heat Run and Chucking Test function)

(2) E204 Servo down during Cue

(3) E205 Servo down during pause

(4) E206 Servo down during manual search and scan

(5) E214 Unable to read the subcode during CUE

(6) E215

(7) E216 Unable to read the subcode during the manual serach and scan

Unable to read the subcode during PAUSE

5DN-C680

5

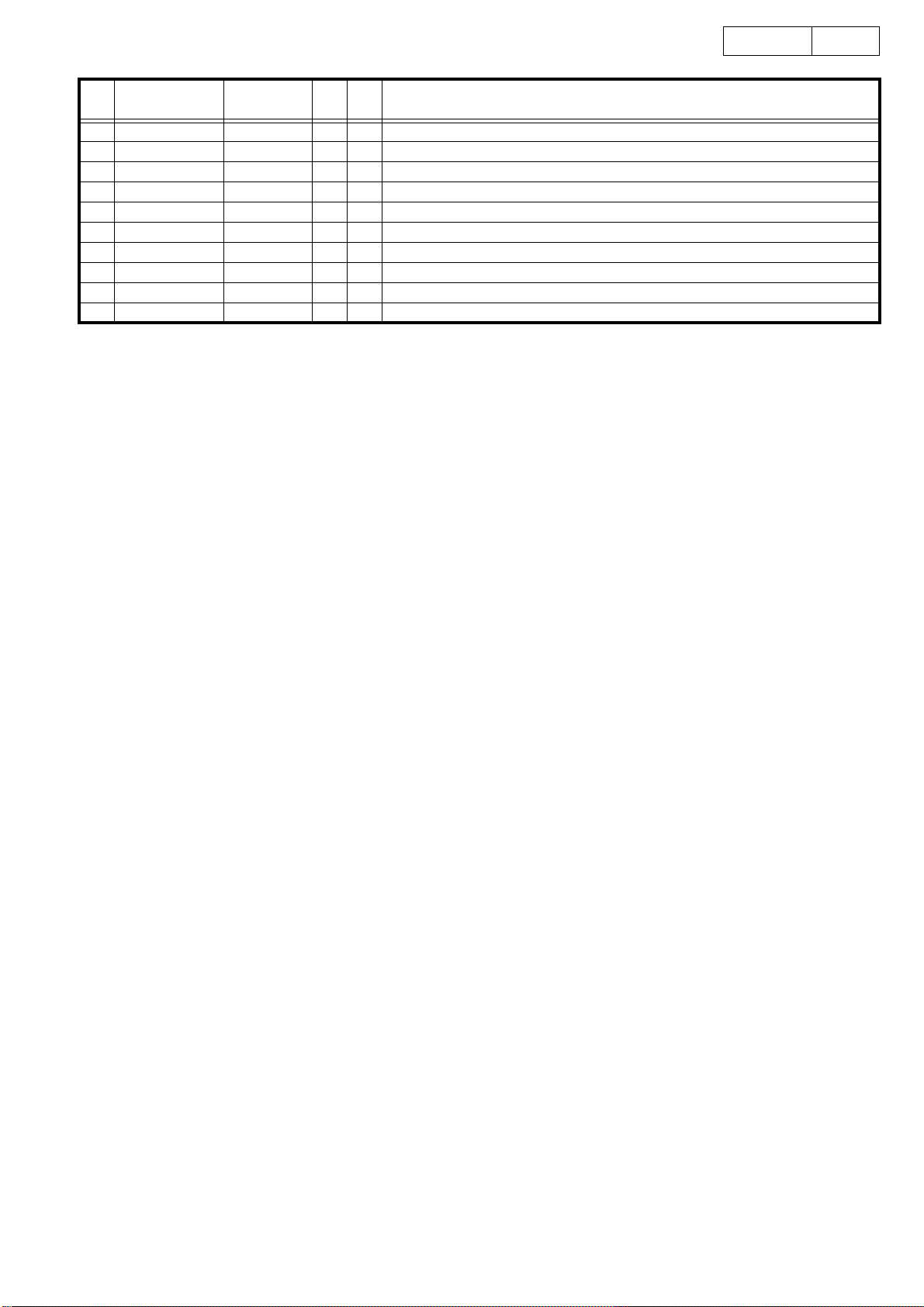

Error Code Table (Appears only at Heat Run and Chucking Test function

Error Code at TRACK portion Contents No. at m portion Contents

Automatic Adjustment Error

00

01

E1

E2

E3 Unable to read TOC

E4

E5 Slide error

E6 Sound skip error (only at the sound skip check)

02

03

04

05

06

00

01

02

03

10

11

12

00

01

Unable to detect disc

Unable to adjust tracking offset

Unable to adjust focus offset

Unable to adjust focus fine gain

Unable to actuate focus

Unable to actuate tracking

Unable to adjust tracking fine gain

Servo down during playback

Servo down during search

Servo down during automatic adjustment

Servo down during TOC read

Unable to read the subcode between 500 msec. during the playback

Unable to read the subcode between 1 sec. during the search

Unable to read the subcode between 500 msec. during the TOC read

Unable to close the disc holder in the regular time

Unable to open the disc holder in the regular time

6DN-C680

Detailed error can be display by select knob when error occurs.

Error indication

TR MIN SEC FRAM

Error Code Contents No.

Indication state when error occurs

01 FG data

02 FBAL data

03 FOFS data

04 TG data

05 TBAL data

06 TOFS data

Accumulated number of open/close

function of the tray prior to Error

occures.

6

CONFIRMING THE AUDIO

r

1. Necessary Equipment for Adjustment

Distortion--Factor Meter

VTVM

Low-Pass Filter (20kHz)

Reference Disc; DENON Audio Technical CD (38C39-7174)

2. Prior to Starting the Adjustment

1) Audio circuit shall be adjusted after adjustment of servo circuit.

3. Output Level Adjustment

1) Connect VTVM to the output connector of DN-C680.

Use 1:1 600 ohm Audio Transformer between the unit and VTVMs in order for matching the unbalanced input of VTVM

and the active bakanced output of DN-C680 as shown in figure.

7DN-C680

DN-C680

Line Out

2) Play track number "49".

3) While reading VTVM indication, adjust VR407 (L-ch) and VR408 (R-ch) so that the output level attains +18dBm

(or desired level).

Audio Transformer

1:1

600ohm

Connection for Output Level Adjustment

RL

VR408

Location of Level Adjustment VRs

VR407

(20kHz)

LPF

Distortion Mete

7

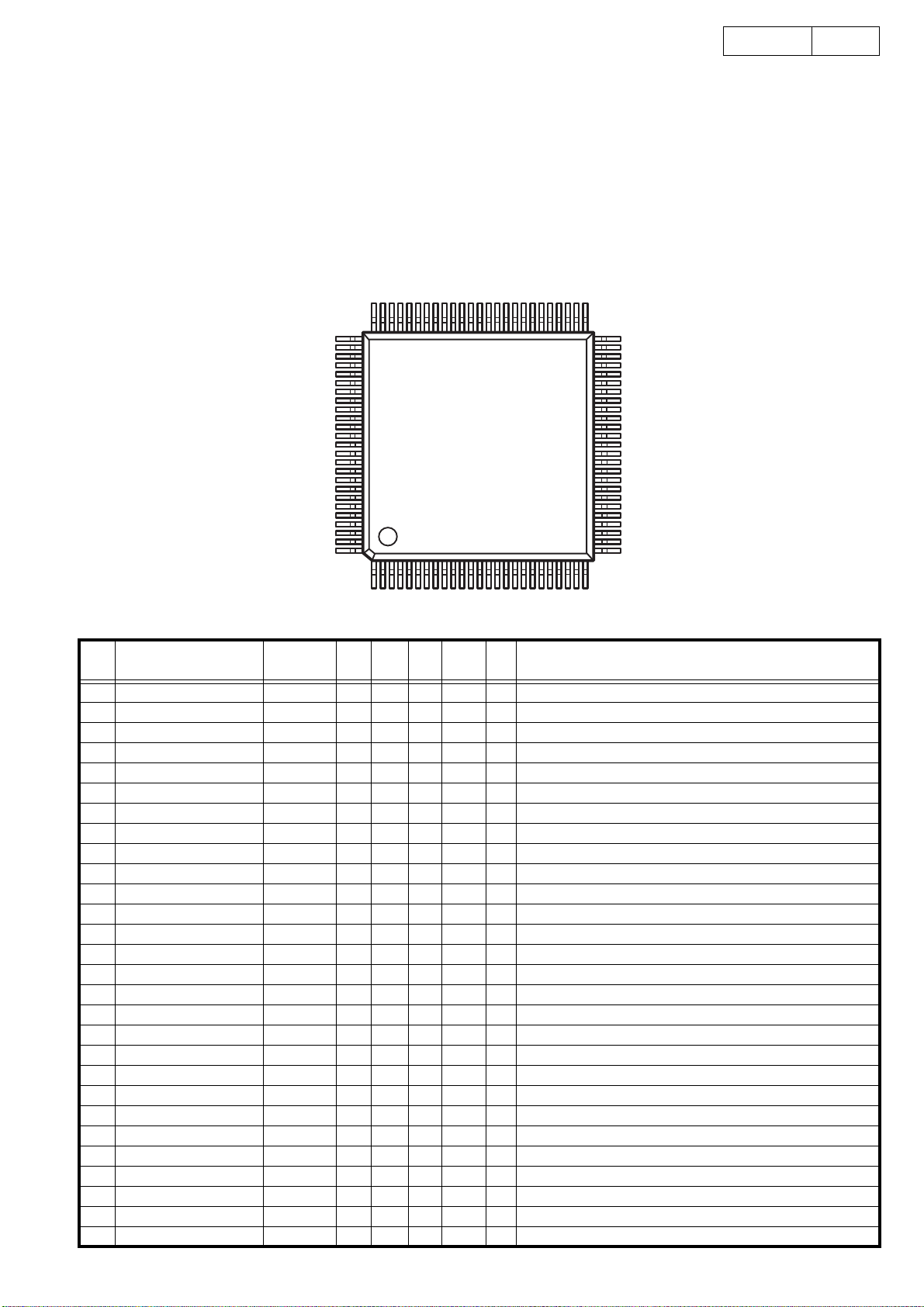

SEMICONDUCTORS

Only major semiconductors are shown, general semiconductors etc. are omitted to list.

主な半導体を記載しています。汎用の半導体は記載を省略しています。

1. IC’s

Note : Abbreviation ahead of IC No. indicates the name of P.W.B., etc.

注 ): ICNo. の前の記号は、基板の名称を表します。

MA : Main P.W.B.

DK : Display/Key P.W.B.

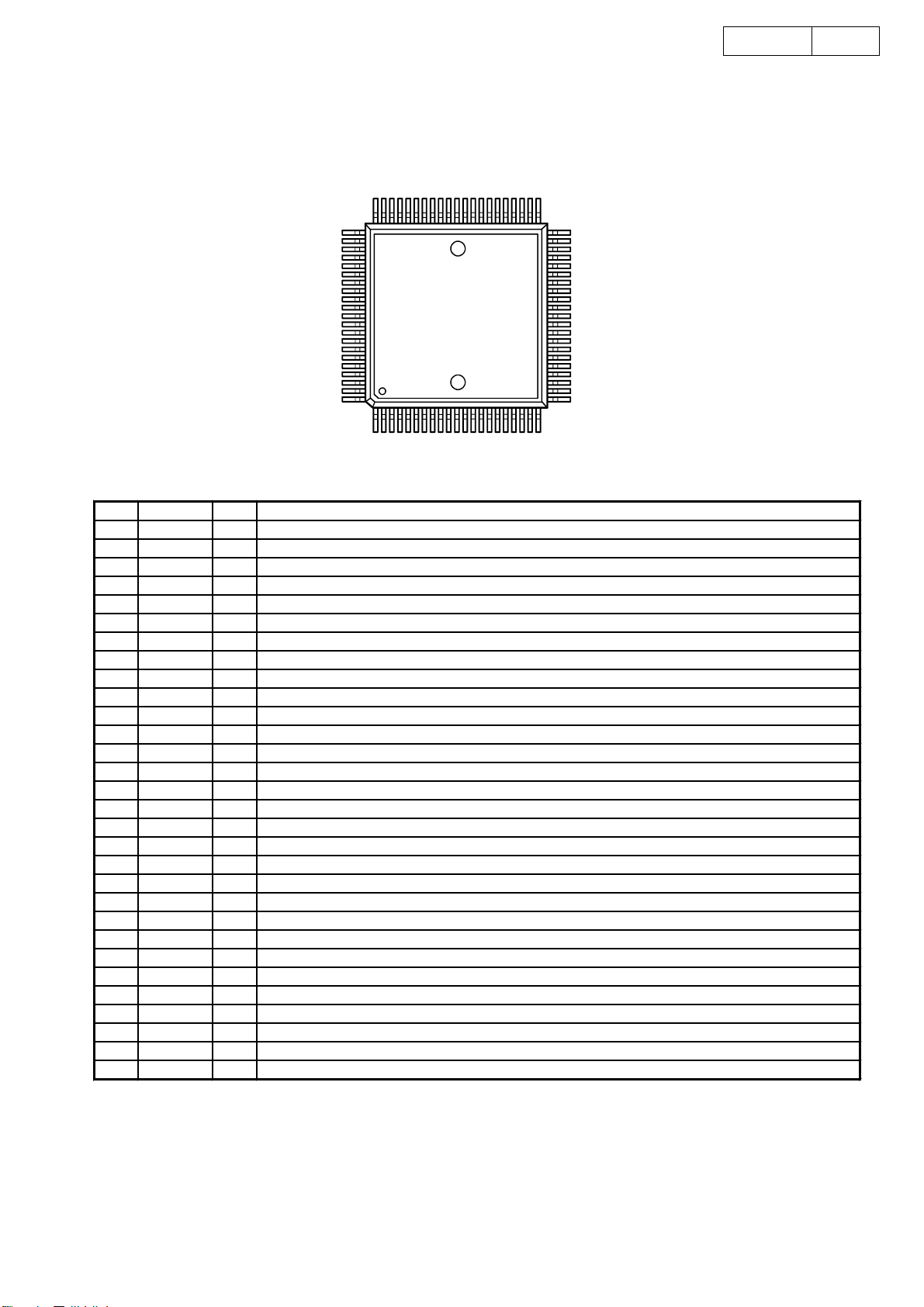

MN102H60KDA (MA: IC137)

8DN-C680

75

76

100

1

51

50

26

25

MN102H60KDA Terminal Function

Pin

No.

1 P60,WAIT,SBT2 CDMUTE O Lv Pu H H DSP(MN662724) control signal:Mute 'H':Mute

2 -RE -RE O - Pu H - Read signal

3 -WEL,P62 -WE O - Pu H - Write signal

4 -WE,P63 -SMRDY I Lv Pu H - ACD27(SMPTE option unit) control signal:Ready

5 -CS0 -CS0 O - Pu H L Chip select signal(CS0:Flash ROM)

6 -CS1,P51,TMI30B -CS1 O - Pu H - Chip select signal(CS1:IO Expander port0-3)

7 -CS2,P52,TMI40A -CS2 O - Pu H - Chip select signal(CS2:IO Expander port4-7)

8 -CS3,P53,TMI40B -CS3 O - Pu H - Chip select signal(CS3:ACD27(SMPTE option unit))

9 P54,-BREQ ROMCLK O - Pu H - EEPROM(S24C04) control signal:Clock

10 P55,-BRACK ROMDAT I/O - Pu H - EEPROM(S24C04) control signal:Data

11 P56,-BSTRE,TMI51A P56 - - - - - Not used. Open

12 -WORD -WORD IN - H H H Data bit bus width select 'H':8bit

13 A0 A0 O - - Unfix - Address bus

14 A1 A1 O - - Unfix - Address bus

15 A2 A2 O - - Unfix - Address bus

16 A3 A3 O - - Unfix - Address bus

17 Vdd VDD - - - - - Power supply(+3.3V)

18 fosc,PB0,BIBT1,BIBT2 TRCK O - - fosc - DIT(YM3437C) control signal:Clock

19 Vss Vss - - - - - GND(0V)

20 XI,PB1 TRDAT O - Pu H - DIT(YM3437C) control signal:Data

21 XO XO - - - - - Not used. Open

22 Vdd Vdd - - - - - Power supply(+3.3V)

23 OSCI OSCI I - - - - X'tal input(12.288MHz)

24 OSCO OSCO O - - - - X'tal output(12.288MHz)

25 MODE MODE I - L L L Mode select 'L':Processor mode

26 A4 A4 O - - Unfix - Address bus

27 A5 A5 O - - Unfix - Address bus

28 A6 A6 O - - Unfix - Address bus

Port Name Symbol I/O DET Ext Res Ini Note

8

9DN-C680

Pin

No.

29 A7 A7 O - - Unfix - Address bus

30 A8 A8 O - - Unfix - Address bus

31 A9 A9 O - - Unfix - Address bus

32 A10 A10 O - - Unfix - Address bus

33 A11 A11 O - - Unfix - Address bus

34 AVdd AVdd - - - - - Analog power supply(+3.3V)

35 A12 A12 O - - Unfix - Address bus

36 A13 A13 O - - Unfix - Address bus

37 A14 A14 O - - Unfix - Address bus

38 A15 A15 O - - Unfix - Address bus

39 A16,P40 A16 O - - Unfix - Address bus

40 A17,P41 A17 O - - Unfix - Address bus

41 A18,P42 A18 O - - Unfix - Address bus(Not used.)

42 A19,P43 A19 O - - Unfix - Address bus(Not used.)

43 VREF- VREF- - - - - - Analog reference voltage supply

44 A20,P44,AN4 A20 O - - Unfix - Address bus

45 A21,P45,AN5 A21 O - - Unfix - Address bus

46 A22,P46,AN6,STOP CCLK O - - - H FL DRIVER(M66005),LED DRIVER(NJU3713),PARALLEL

47 A23,P47,AN7,WDOUT CDAT O - - - H FL DRIVER(M66005),LED DRIVER(NJU3713),PARALLEL

48 P80,TMI40A -LDC I - - - - FPGA(XCS05XL) control signal:Ldc(not used)

49 P81,TMI40B DONE I - Pu L - FPGA(XCS05XL) control signal:Done

50 P82,TMOIO,SBT3,

51 P83,TM4IO,SBI3 SYSRSTO O - Pu H - System reset output 'L':Reset

52 P84,TM7IO,SBO3,SDA3 TRCL0 O - - - H DIT(YM3437C) control signal:Strobe

53 P85,TM9IOA,SBT4,

54 VREF+ VREF+ - - - - - Analog reference voltage supply

55 P86,TM9IOB,SBI4 RXD I - Pu H - Serial port(Receive)

56 P87,TM9IC,SB04,SDA4 TXD O - - - - Serial port(Transmission)

57 P90,TM8IOA,BIBT1,

58 P91,TMIOIOA,BIBT2,

59 P92,TMIOIOB,

60 P93,TMIOIC,

61 AVss AVss - - - - - Analog GND(0V)

62 P94,AN0 STAT I - Pu H - DSP(MN662724) status input

63 P95,AN1 SQCK O - - - H DSP(MN662724) control signal:SQCK(subcode read clock)

64 P96,AN2 -INIT I - Pu H - FPGA(XCS05XL) control signal:Init

65 P97,AN3 -PGM O - Pu H - FPGA(XCS05XL) control signal:Program

66 Vdd VDD - - - - - Power supply(+3.3V)

67 P70,SBT0,-RAS MDAT O - - - - DSP(MN662724),DAC(PCM1738) control signal:Data

68 P71,SBIO,-LCAS,-CAS -CSEN O - Pu H H KEY MATRIX(74HC138) control signal:enable

69 P72,SBD0 -PRST O Lv Pd L - Round IC reset signal

70 P73,SBT1,DMUX CCLK O - - - - FPGA(XCS05XL) control signal:Clock

71 P74,SBI1 MCLK O - - - - DSP(MN662724),DAC(PCM1738) control signal:Clock

72 P75,SBO1 SPDATA O - - - - FPGA(XCS05XL) control signal:Data

73 PULLUP PULLUP I - Pu H - Pull up 33-50K

74 PULLUP PULLUP I - Pu H - Pull up 33-50K

75 -NMI -NMI I - Pu H - Not used. Open

76 PA0,-IRQ0 BLKCK I Ed Pu - - DSP(MN662724) subcode input(interrupt)

77 PA1,-IRQ1 RFDET I Ed Pu H - DSP(MN662724) HF detect signal(not used)

Port Name Symbol I/O DET Ext Res Ini Note

DRIVER(NJU3715) control signal:Clock

DRIVER(NJU3715) control signal:Data

SCL3,SBI2

SCL4,SBO2

-DMAREQ1

-DMAACK1

-DMAREQ0

-DMAACK0

-PSTB0 O - Pu H H NJU3713 control signal:Strobe

TRCL1 O - - - - FPGA(XCS05XL) initialize status

('L':While initializing,'H':Operation(*1))

SUBQ I - Pu H - DSP(MN662724) subcode data input

SENSE I - Pu H - DSP(MN662724) servo status input

-FLOCK I - Pu H - DSP(MN662724) status input 'L':focus on

-TLOCK I - Pu H - DSP(MN662724) status input 'L':tracking servo on input

9

10DN-C680

Pin

No.

78 PA2,-IRQ2 -SMIRQ I Ed Pu H - ACD27(SMPTE option unit) control signal:Interrupt request

79 PA3,-IRQ3 -TRSLA I Ed Pu - - Track select signal input(interrupt)

80 PA4,-IRQ4,TMI51B -TRSLB I Ed Pu - - Track select inverted signal(interrupt)

81 ADSEP ADSEP I - H H H Mode select 'H':Address data separation mode

82 -RST -RST I Lv - L - Reset signal 'L':Reset

83 Vdd Vdd - - - - - Power supply(+3.3V)

84 D0 D0 I/O - Pu H - Data bus

85 D1 D1 I/O - Pu H - Data bus

86 D2 D2 I/O - Pu H - Data bus

87 D3 D3 I/O - Pu H - Data bus

88 D4 D4 I/O - Pu H - Data bus

89 D5 D5 I/O - Pu H - Data bus

90 D6 D6 I/O - Pu H - Data bus

91 D7 D7 I/O - Pu H - Data bus

92 Vss Vss - - - - - GND(0V)

93 P10,TM810B -MLE O - - - - DAC(PCM1738) control signal:Latch

94 P11,TM81C -MLD O - - - - DSP(MN662724) control signal:Latch

95 P12,TM11IOA -MRST O Lv Pd L L DSP(MN662724) control signal:Reset

96 P13,TM11IOB P13 I Lv Pu H - ASP(MN19412A) status0 input

97 P14,TM11IOC P14 I Lv Pu H - ASP(MN19412A) status1 input

98 P15,TM12IOA P15 O Lv - - H ASP(MN19412A) ext.dram/disc data compare start signal

99 P16,TM12IOB MSCL O - - - H ASP(MN19412A) control signal:Clock

100 P17,TM12IC MSDA O - - - H ASP(MN19412A) control signal:Data

Port Name Symbol I/O DET Ext Res Ini Note

'L':start

LED (LD101) lights up during initialization of FPGA (IC112) (it is less than 1 second at the time of normal), and LED puts out the

*1:

light after initialization.

When LED is carrying out continuation lighting even of after initialization, please check whether the control signal line for FPGA

initialization (pin 49, 64, 65, and 70) is carrying out the electrical connection, or it does not short-circuit with other signal lines,

and correct fault.

When LED is still carrying out continuation lighting, please correct in order of exchange of FLASH ROM (IC106), exchange of

FPGA (IC112), and exchange of a microcomputer (IC137).

*1: FPGA(IC112) の初期化の間、LED(LD101) が点灯 ( 正常時は 1 秒以内 ) し、初期化後に LED が消灯します。

もし、LED が初期完了後も連続点灯している場合は FPGA 初期化のための制御信号線 (pin49,64,65,70) が導通しているか、他

の信号線とショートしていないか確認し、修正して下さい。

それでも LED が連続点灯している場合は、FLASHROM(IC106) の交換、FPGA(IC112) の交換、マイコン (IC137) の交換の順で

修正を行って下さい。

10

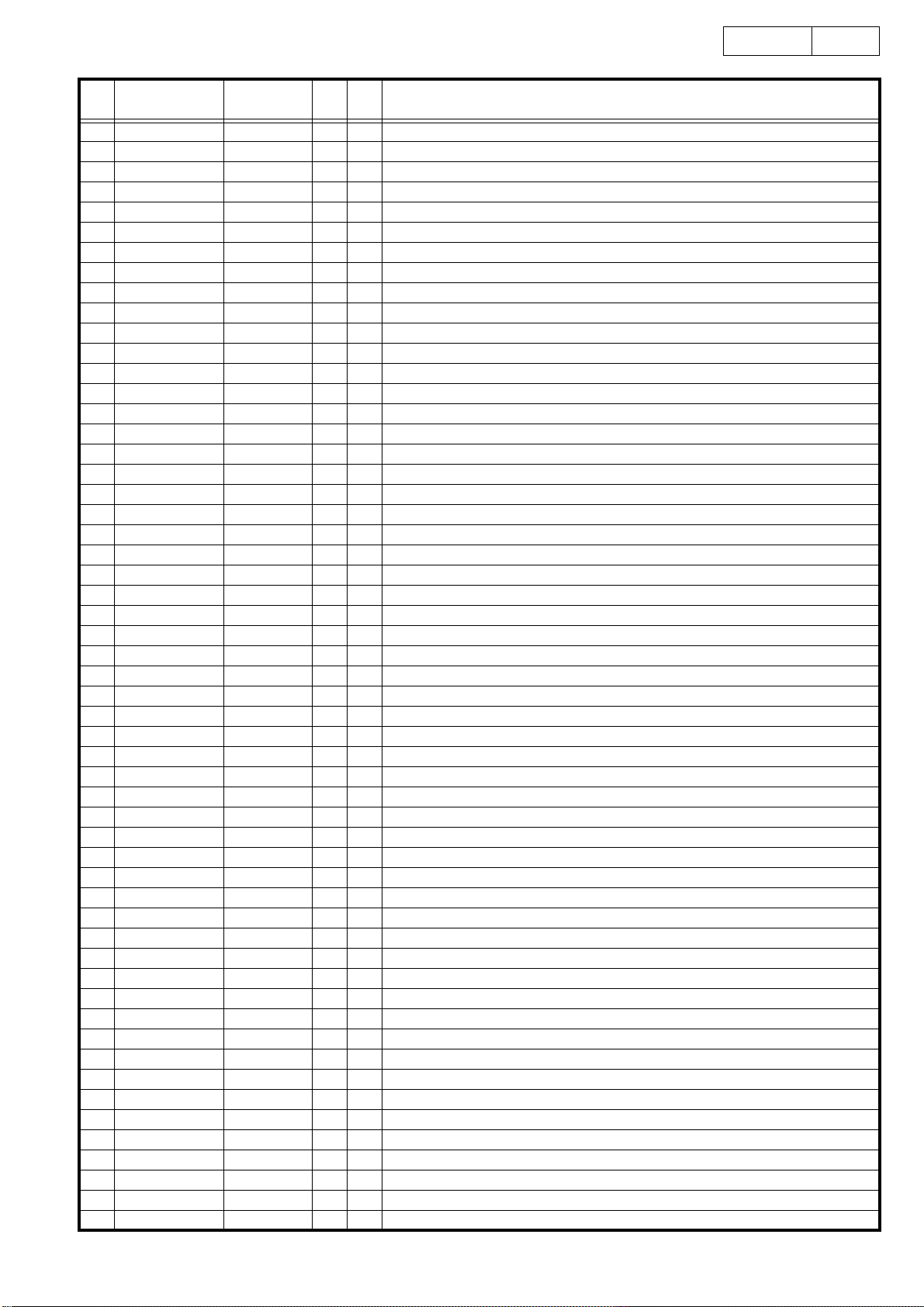

XCS05XL-5VQ100C (MA: IC112)

11DN-C680

75

76

100

1

51

50

26

25

XCS05XL-5VQ100C Terminal Function

Pin

No.

10 I/O -CS2 I Pu Chip select signal

11 GND GND - - GND(0V)

12 VCC VCC - - Power supply(+3.3V)

13 I/O D0 I/O Pu Data bus

14 I/O D1 I/O Pu Data bus

15 I/O D2 I/O Pu Data bus

16 I/O D3 I/O Pu Data bus

17 I/O D4 I/O Pu Data bus

18 I/O D5 I/O Pu Data bus

19 I/O D6 I/O Pu Data bus

20 I/O D7 I/O Pu Data bus

21 I/O,GCK2 CHGOFT O - Off track detect sensitivity select signal

22 M1 M1 I - FPGA(XCS05XL) Mode select 'H':Slave serial mode

23 GND GND - - GND(0V)

24 M0 M0 I - FPGA(XCS05XL) Mode select 'H':Slave serial mode

25 VCC VCC - - Power supply(+3.3V)

26 -PWRDWN -PWRDWN I - FPGA(XCS05XL) control signal:Power down(Not used. Internal pullup)

27 I/O,GCK3 A20 I - Address bus

28 I/O(HDC) CHGICO O - RF equalizer specification select signal

29 I/O A21 I - Address bus

30 I/O(-LDC) I/O O Pu FPGA(XCS05XL) control signal:-LDC(Not used)

31 I/O PDI0 I Pu Parallel port 'L':Play command input

32 I/O PDI1 I Pu Parallel port 'L':Pause command input

33 I/O PDI2 I Pu Parallel port 'L':Standby/cue command input

34 I/O PDI3 I Pu Parallel port 'L':Track+ command input

35 I/O PDI4 I Pu Parallel port 'L':Track- command input

Port Name Symbol I/O Ext Note

1 GND GND - - GND(0V)

2 I/O,GCK1 I/O - - Not used. Open

3 I/O -PRST I Pd Reset signal 'L':Reset(internal register cleared)

4 I/O,TDI I/O - - Not used. Open

5 I/O,TCK I/O - - Not used. Open

6 I/O,TMS I/O - - Not used. Open

7 I/O -R I Pu Read signal

8 I/O -W I Pu Write signal

9 I/O -CS1 I Pu Chip select signal

11

12DN-C680

Pin

No.

36 I/O(-INIT) -INIT O Pu FPGA(XCS05XL) control signal:-INIT

37 VCC VCC - - Power supply(+3.3V)

38 GND GND - - GND(0V)

39 I/O PDI5 I Pu Parallel port 'L':Forward search command input

40 I/O PDI6 I Pu Parallel port 'L':Reverse search command input

41 I/O PDI7 I Pu Parallel port 'L':Fader start command input

42 I/O PDI8 I Pu Parallel port(Reserved)

43 I/O PDI9 I Pu Parallel port(Reserved)

44 I/O PDI10 I Pu Parallel port(Reserved)

45 I/O -CLOSE O Pu Loading motor driver(BA6287) control signal 'L':Close

46 I/O -OPEN O Pu Loading motor driver(BA6287) control signal 'L':Open

47 I/O -LIMITSW+ I Pu Laser pickup position status signal 'L':pickup is most inside position

48 I/O,GCK4 -LDIN I Pu Loading status singal 'L':Close operation finished

49 GND GND - - GND(0V)

50 DONE DONE O Pu FPGA(XCS05XL) control signal:DONE

51 VCC VCC - - Power supply(+3.3V)

52 -PROGRAM -PGM I Pu FPGA(XCS05XL) control signal:-PROGRAM

53 I/O(D7) -LDOUT I Pu Loading status singal 'L':Open operation finished

54 I/O,GCK5 -JOG0 I Pu Jog dial status detect signal

55 I/O(D6) -JOG1 I Pu Jog dial status detect signal

56 I/O -SHTL0 I Pu Shuttle status detect signal

57 I/O(D5) -SHTL1 I Pu Shuttle status detect signal

58 I/O -SHTL2 I Pu Shuttle status detect signal

59 I/O -SHTL3 I Pu Shuttle status detect signal

60 I/O -TRSLC I Pu Select knob status signal

61 I/O(D4) -PUSH I Pu Select button(PUSH) status signal

62 I/O AMUTE O Pu Analog Audio control signal:Mute 'H':Mute

63 VCC VCC - - Power supply(+3.3V)

64 GND GND - - GND(0V)

65 I/O(D3) DMUTE O Pu Digital Audio control signal:Mute 'H:Mute

66 I/O FSI0 O Pu X'tal(8.192MHz for FS converter unit) control signal:Enable 'L':Enable

67 I/O FSI1 O Pu X'tal(12.288MHz for FS converter unit) control signal:Enable 'L':Enable

68 I/O(D2) SEL0 O - Key matrix scan signal

69 I/O SEL1 O - Key matrix scan signal

70 I/O(D1) SEL2 O - Key matrix scan signal

71 I/O DYCON O Pu Serial Driver(HD26LS31) control signal:Enable 'H':Enable

72 I/O(D0,DIN) DIN I - FPGA(XCS05XL) control signal:DIN

73 I/O,GCK6(DOUT) I/O - - Not used. Open

74 CCLK CCLK I - FPGA(XCS05XL) control signal:CCLK

75 VCC VCC - - Power supply(+3.3V)

76 O,TDO O O - Not used. Open

77 GND GND - - GND(0V)

78 I/O -TRRST0 O Pd DIT(YM3437) and FS unit control signal:Reset 'L':Reset

79 I/O,GCK7 V/-W O Pd PLL circuit of Ext.sync.unit control signal

80 I/O(CS1) FSNOO O Pd Digital audio control signal:Data select 'L':DSP data 'H':FS unit data

81 I/O FSSEL O Pd FS unit control signal:FSSEL 'L':FS=32kHz 'H':FS=48kHz

82 I/O -FSIN I Pu FS unit status signal 'L':FS unit detected

83 I/O -SUBON O - Digital audio control signal:Subcode ON/OFF

84 I/O -SMIN I Pu Ext.sync.unit status signal 'L':Ext.sync.unit detected

85 I/O -CLKIN I Pu Ext.sync.unit status signal 'L':Video/word clock detected

86 I/O PITCH O Pd Not used. Open

87 I/O GSEL O - RF amprifier gain control signal

88 GND GND - - GND(0V)

89 VCC VCC - - Power supply(+3.3V)

90 I/O CKSEL O - Master clock(384FS) control signal 'L':Ext.sync.unit

Port Name Symbol I/O Ext Note

12

13DN-C680

Pin

No.

91 I/O KI0 I Pu Key matrix data bus

92 I/O KI1 I Pu Key matrix data bus

93 I/O KI2 I Pu Key matrix data bus

94 I/O KI3 I Pu Key matrix data bus

95 I/O KI4 I Pu Key matrix data bus

96 I/O KI5 I Pu Key matrix data bus

97 I/O KI6 I Pu Key matrix data bus

98 I/O KI7 I Pu Key matrix data bus(Not used)

99 I/O,GCK8 I/O - - Not used. Open

100 VCC VCC - - Power supply(+3.3V)

Note:

Port Name Symbol I/O Ext Note

FS unit:FS converter unit(ACD25,option)

Ext.sync.unit:External video synchronizing unit(ACD27CS,Option)

13

MN19412A (MA: IC126)

MN19412A (Mecha Unit)

(IC104)

63

14DN-C680

43

64

84

1

42

22

21

MN19412A Terminal Function

Pin No. Symbol I/O/T Function

1N.C.

2 SOEN2 I Output enable for serial output 2.

3 SCKO2 I Serial clock for serial output 2.

4 SDO3 O/T Data for serial output 3.

5 WSO3 I Word select for serial output 3.

6 SCKO3 I Serial clock for serial output 3.

7 SOEN3 I Output enable for serial output 3.

8Vss

9Vss

10 XCAS O Column address strobe for external DRAM. Open when not used.

11 XOE O Output enable for external RAM.

12 A14 O Address 14 for external RAM.

13 A13 O Address 13 for external RAM.

14 A12 O Address 12 for external RAM.

15 A11 O Address 11 for external RAM.

16 A10 O Address 10 for external RAM.

17 A9 O Address 9 for external RAM.

18 A8 O Address 8 for external RAM.

19 A7 O Address 7 for external RAM.

20 A6 O Address 6 for external RAM.

21 N.C.

22 A5 O Address 5 for external RAM.

23 A4 O Address 4 for external RAM.

24 A3 O Address 3 for external RAM.

25 A2 O Address 2 for external RAM.

26 A1 O Address 1 for external RAM.

27 A0 O Address 0 for external RAM.

28 XCE2 O Chip enable 2 for external SRAM.

29 XCE1 O Chip enable 1 for external SRAM.

30 XRAS O Row address strobe for external DRAM. Open when not used.

Non connection.

—

GND terminal (0V).

—

GND terminal (0V).

—

Non connection.

—

14

Pin No. Symbol I/O/T Function

31 XWE O Write enable for external RAM.

32 VSS

33 VSS

GND terminal (0V).

—

GND terminal (0V).

—

34 D7 I/O Data 7 for external RAM (Connect to D4~7 when one DRAM is used).

35 D6 I/O Data 6 for external RAM.

36 D5 I/O Data 5 for external RAM.

37 D4 I/O Data 4 for external RAM.

38 D3 I/O Data 3 for external RAM.

39 D2 I/O Data 2 for external RAM.

40 D1 I/O Data 1 for external RAM.

41 D0 I/O Data 0 for external RAM.

42 P7 I/O/T General purpose port 7.

43 P6 I/O/T General purpose port 6.

44 P5 I/O/T General purpose port 5.

45 P4 I/O/T General purpose port 4.

46 P3 I/O/T General purpose port 3.

47 P2 I/O/T General purpose port 2.

48 P1/PT1 I/O/T General purpose port 1/Flag 1 for condition dividing.

49 P0/PT0 I/O/T General purpose port 0/Flag 0 for condition dividing.

50 N.C.

Non connection.

—

51 SYNC I Input for progr am sync (condition input).

52 V

DD

Power supply terminal.

—

53 INT0 I Interrupt input 0.

54 INT1 I Interrupt input 1.

55 XRESET I System reset input.

56 Vss

GND terminal (0V).

—

57 CLKI I System clock input.

58 CLKO O System clock output.

59 V

60 V

DD

DD

Power supply terminal.

—

Power supply terminal.

—

61 ADDR0 I Address select 0 for IIC bus.

62 ADDR1 I Address select 1 for IIC bus.

63 XCE I Chip enable for IIC bus.

64 IICSEL I IIC/IC switching for IIC bus.

65 XTRANS I Data transfer control for IIC bus.

66 SDA I/O Serial data for IIC bus.

67 SCL I/O Serial clock for IIC bus.

68 MATCH O Address match at coefficient input for IIC bus.

69 SDI1 I Data for serial input 1.

70 WSI1 I Word select for serial input 1.

71 N.C.

Non connection.

—

72 SCKI1 I Serial clock for serial input 1.

73 SDI2 I Data for serial input 2.

74 WSI2 I Word select for serial input 2.

75 SCKI2 I Serial clock for serial input 2.

76 V

77 V

DD

DD

Power supply terminal.

—

Power supply terminal.

—

78 SDO1 O/T Data for serial output 1.

79 WSO1 I Word select for serial output 1.

80 N.C.

Non connection.

—

81 SCKO1 I Serial clock for serial output 1.

82 SOEN1 I Output enable for serial output 1.

83 SDO2 O/T Data for serial output 2.

84 WSO2 I Word select for serial output 2.

15DN-C680

15

Loading...

Loading...