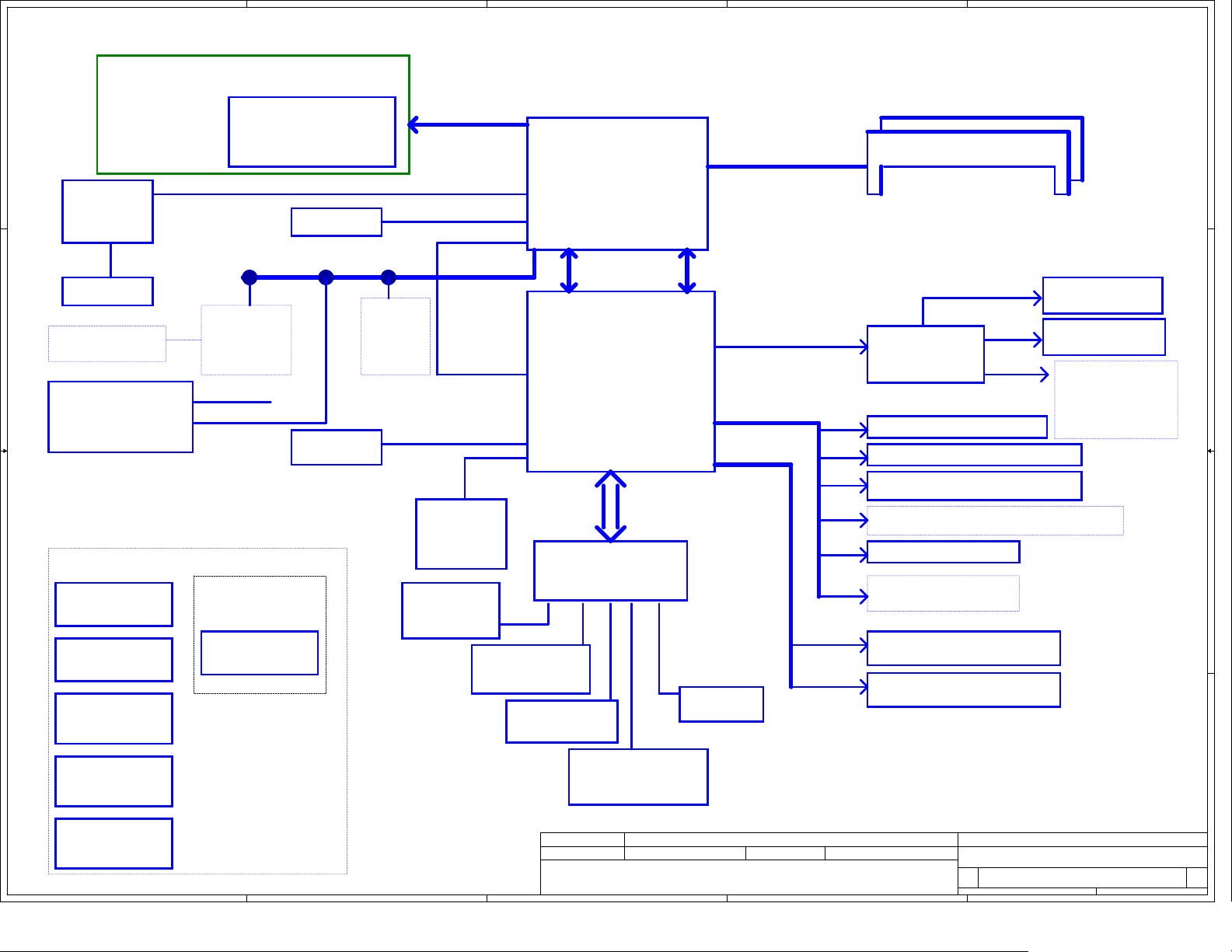

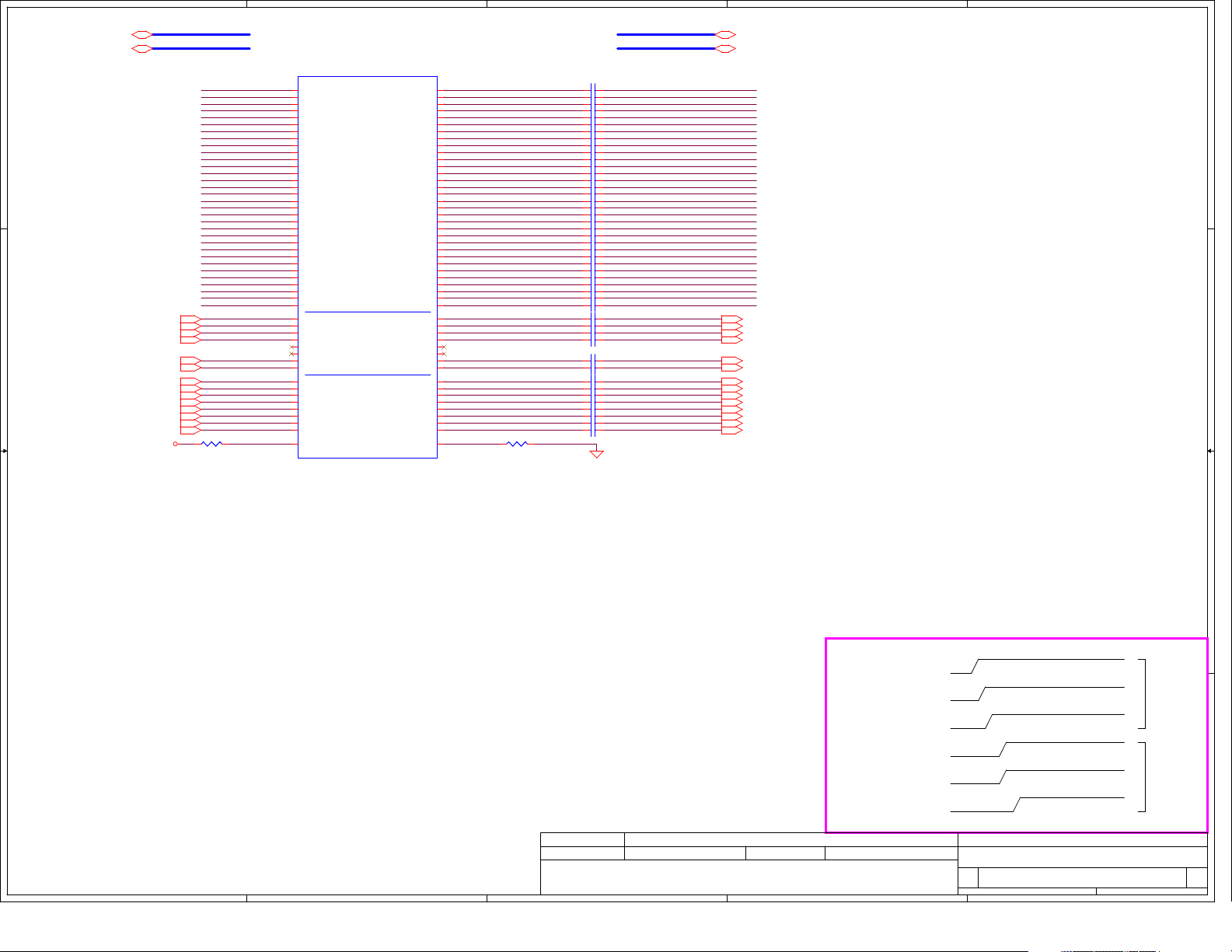

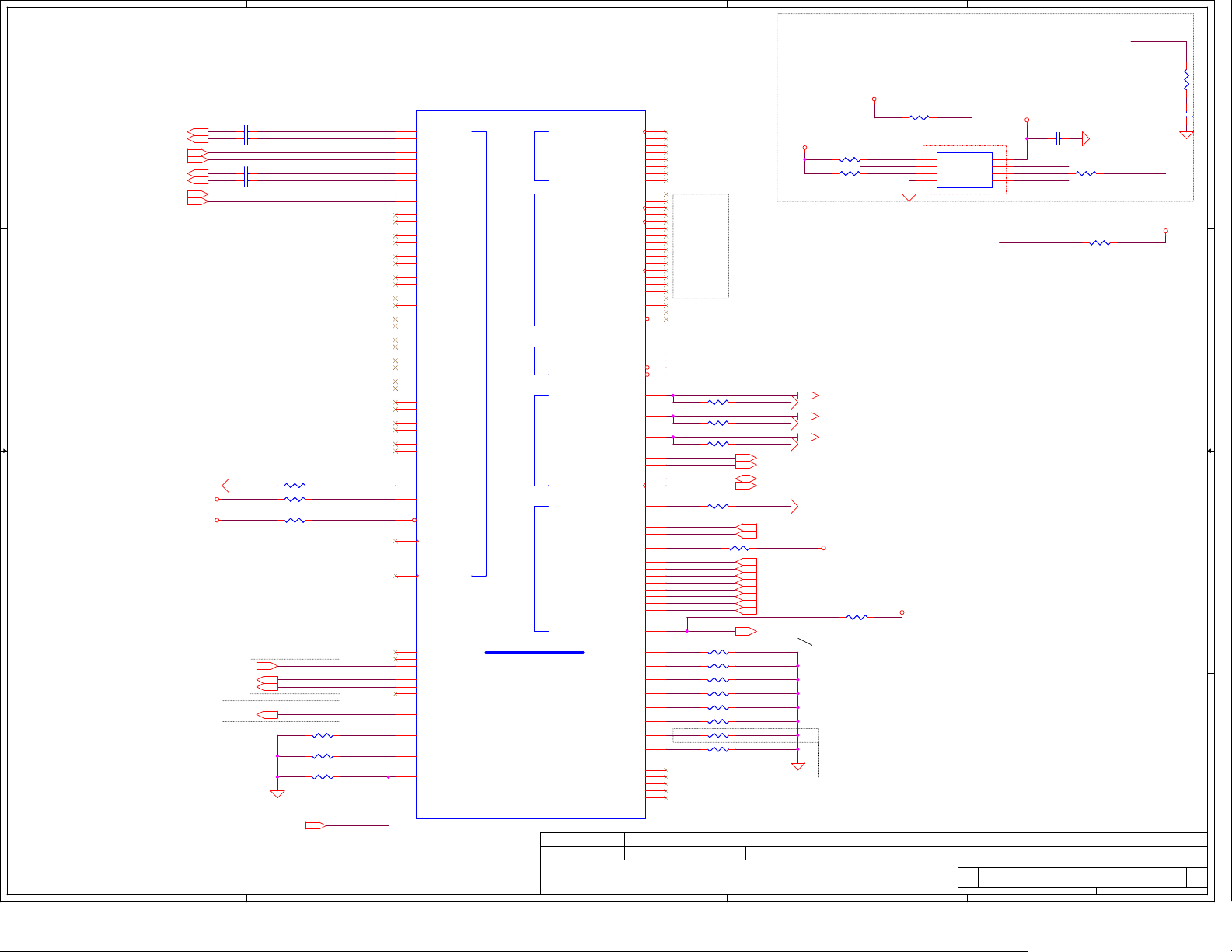

Compal LA-8124P QALEA, ThinkPad Edge E535, LA-8124P QALEB Schematic

A

1 1

B

C

D

E

Compal Confidential

2 2

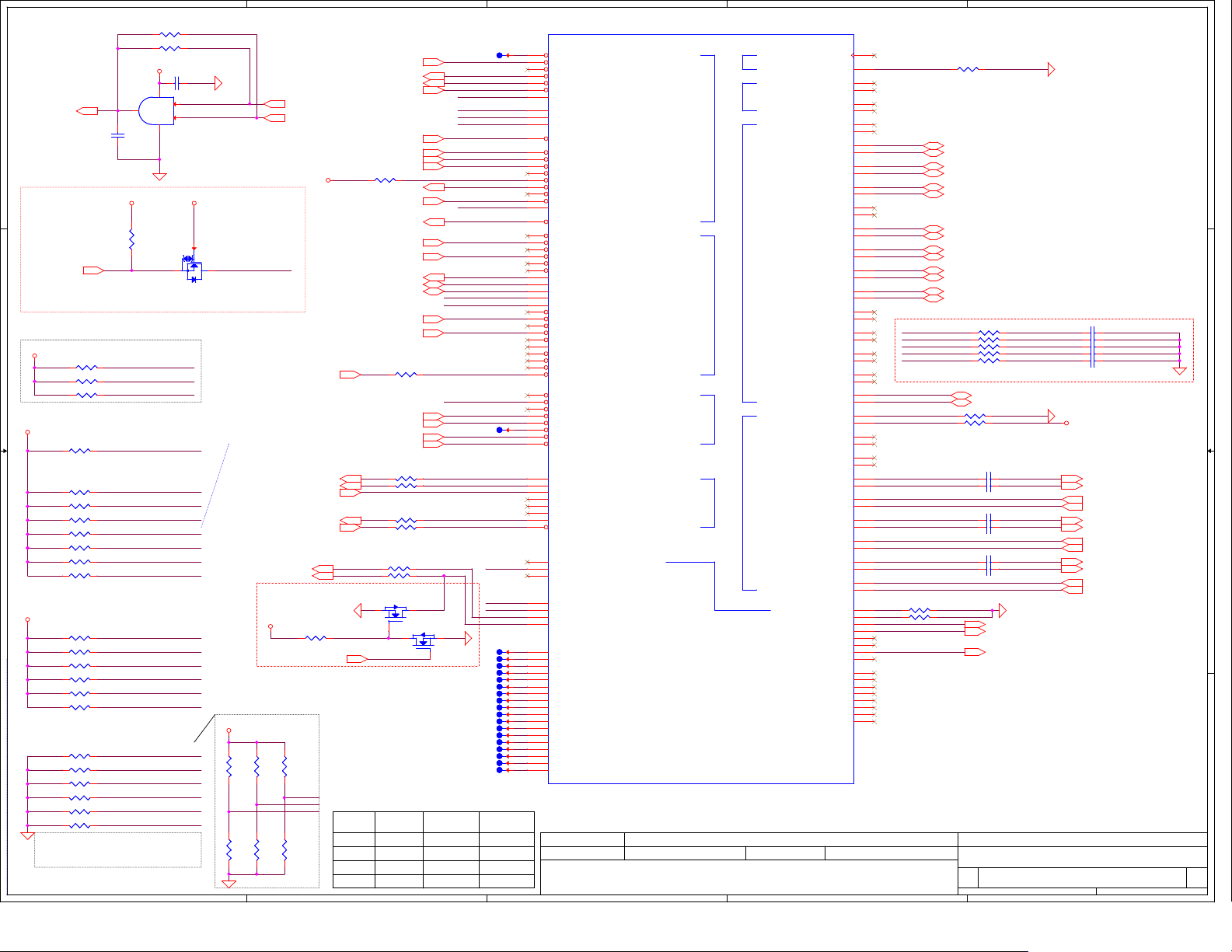

QALEA/QALEB Schematics Document

AMD APU Trinity FS1r2 + FCH Hudson-M3 + GPU Seymour XTX/Thames XT

2012-01-16

3 3

4 4

A

B

REV:0.4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/04/18 2015/07/08

2011/04/18 2015/07/08

2011/04/18 2015/07/08

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-8124P

LA-8124P

LA-8124P

1 50Monday, January 16, 2 012

1 50Monday, January 16, 2 012

1 50Monday, January 16, 2 012

E

0.4

0.4

0.4

A

Compal confidential

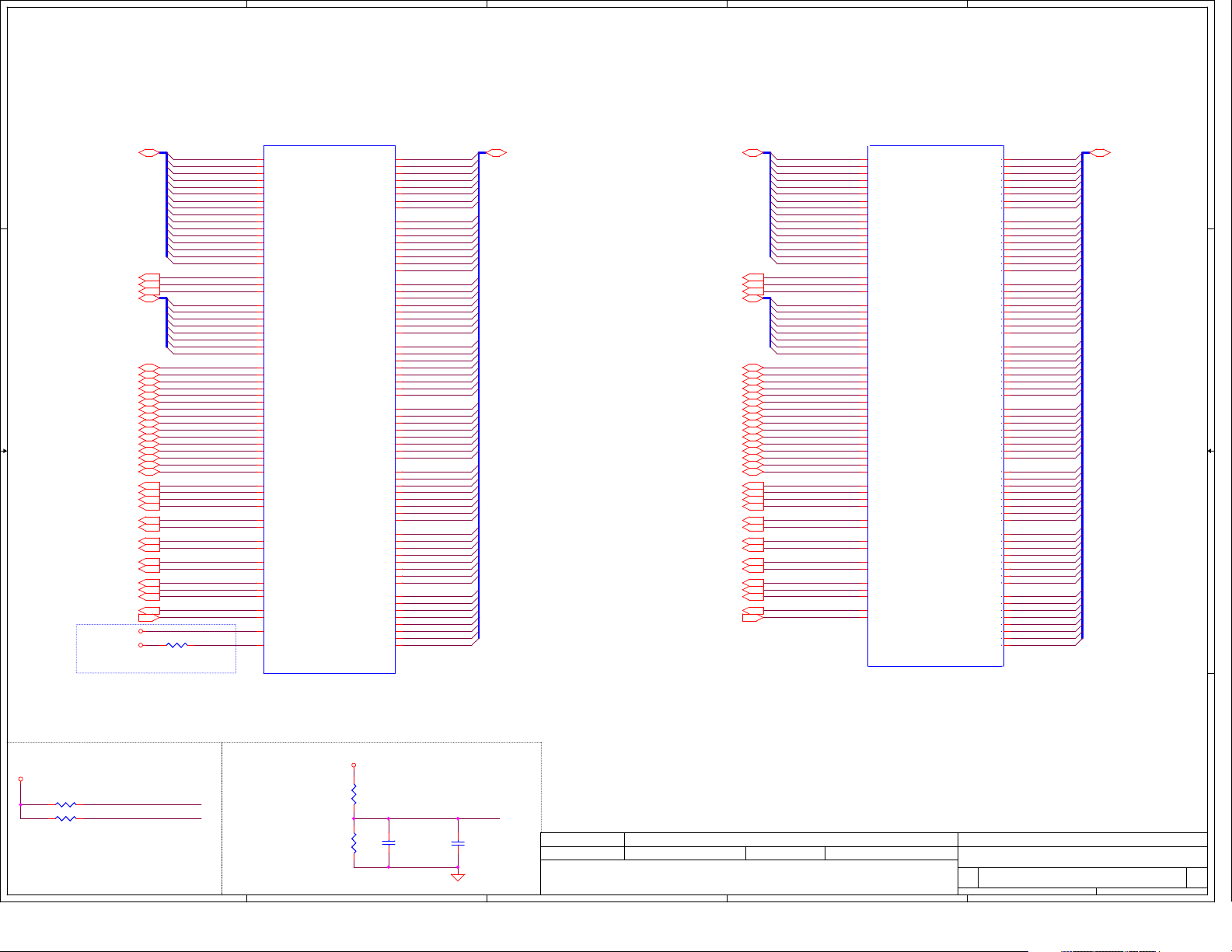

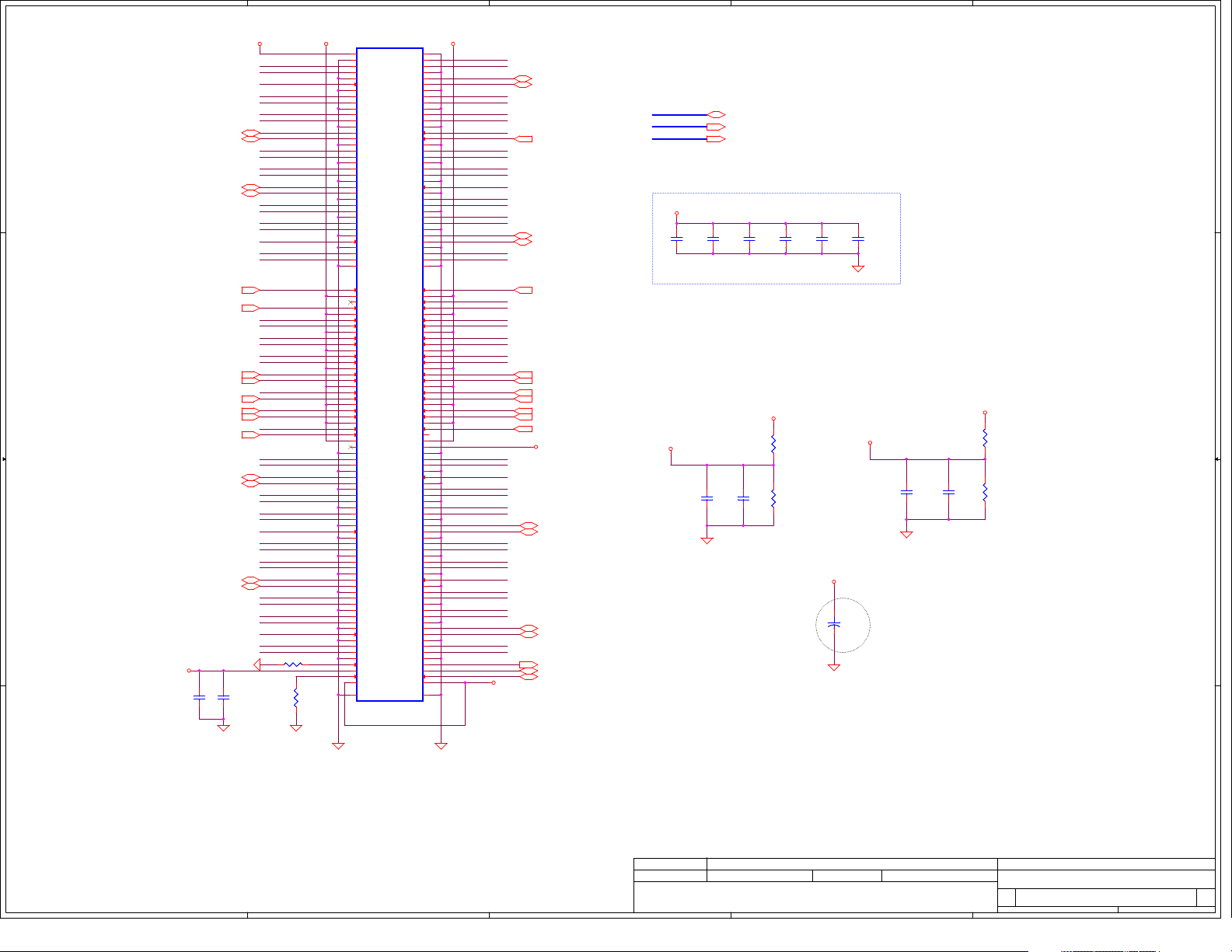

File Name : QALEA/QALEB

Themes XT M2/Seymour XTX M2

B

C

D

E

1 1

VRAM

64M16/128M16/256M16

DDR3 x 8

Page 17

~~~~

24

LVDS

translator

RTD2132S

Page 25

HDMI Conn.

Page 27

4 * x1 PCI-E 2.0

LVDS Conn.

Page 26

GPP1GPP3

CardReader

2 2

4 in 1 Conn.

PCI Express

Mini card Slot 1

WLAN

Page 33

IC

RTS5229

USB(BT)

PCI-E(WLAN)

CRT CONN

Page 28

GPP0

LAN

RTL 8111F

FCH CRT (VGA DAC)

SPI ROM

4MB

3 3

Sub board

Power Board

LAN

Page 35

15" only

ODD board

G Sensor

ST LIS34ALTR

Audio Jack+

USB2.0

Gen2PCIE x 16

DP Port0

DP Port2

DP Port1

Page 13

Page 30

Track Point

AMD FS1r2 APU

Trinity

uPGA 722 pin

35mm x 35mm

x4 UMI Gen. 1

2.5GT/s per lane

Hudson M3

uFCBGA-656

24.5mm x 24.5mm

EC

ENE KB9012

Page 33

Click Pad

Page 33

Page 5

~~~~

Page 12

LPC BUS

Page 31

Memory BUS(DDRIII)

Dual Channel

1.5V DDRIII 1600 (1866)

9

AZALIA

14*USB2.0/

4*USB3.0,10*USB2.0

6*SATA serial

~~~~

16

Int.KBD

Page 33

SATA0

SATA1

204pin DDRIII-SO-DIMM X2

Page 10

~~~~

BANK 0, 1, 2

11

2Channel Speaker

Audio Codec

CX20671-21Z

Page 29

CMOS Camera

BlueTooth CONN

USB PORT 3.0 x3

Internal MIC

Audio Jacks

Combo jack

Page 26

Page 32

Page 34

USB PORT 2.0 x1 +Charger

WLAN

Page 33

Finger Printer

UPEK TCS5DA6C0

SATA3.0 HDD CONN

SATA ODD CONN

Page 30

Page 30

4 4

FingerPrint

Card reader

A

B

Thermal Sensor

Fintek 5303

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Page 32

Compal Secret Data

Compal Secret Data

2011/04/18 2015/07/08

2011/04/18 2015/07/08

2011/04/18 2015/07/08

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

LA-8124P

LA-8124P

LA-8124P

2 50Monday, January 16, 2 012

2 50Monday, January 16, 2 012

2 50Monday, January 16, 2 012

E

0.4

0.4

0.4

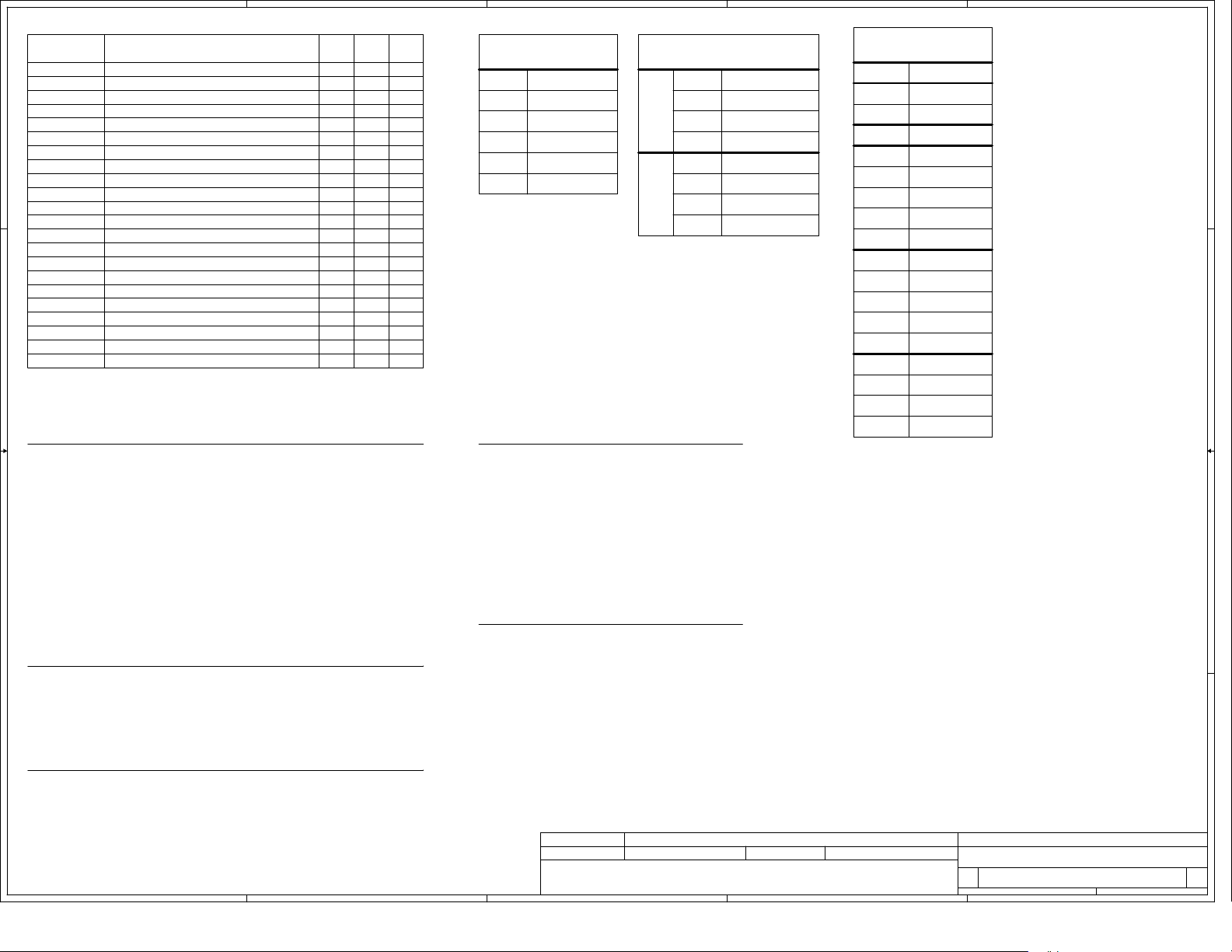

A

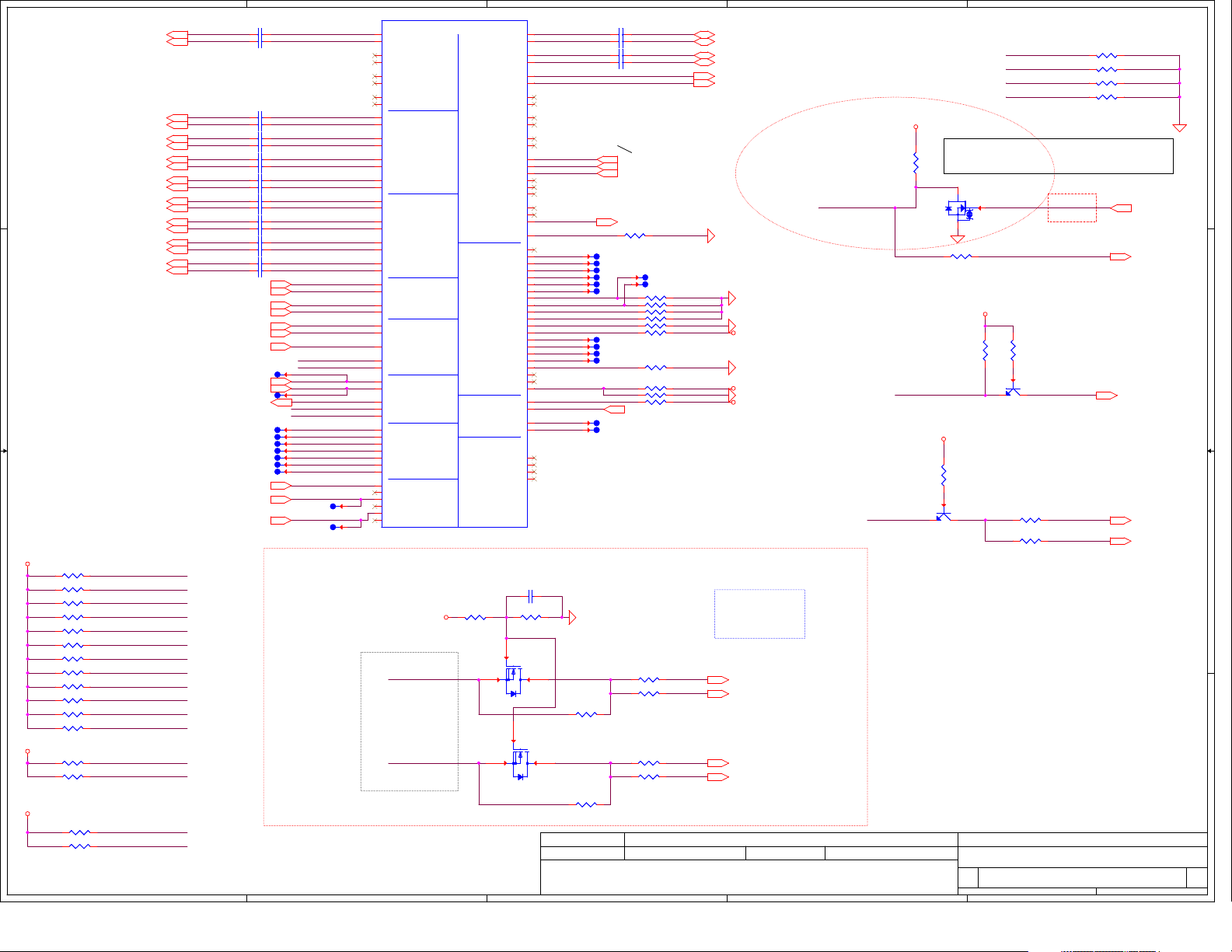

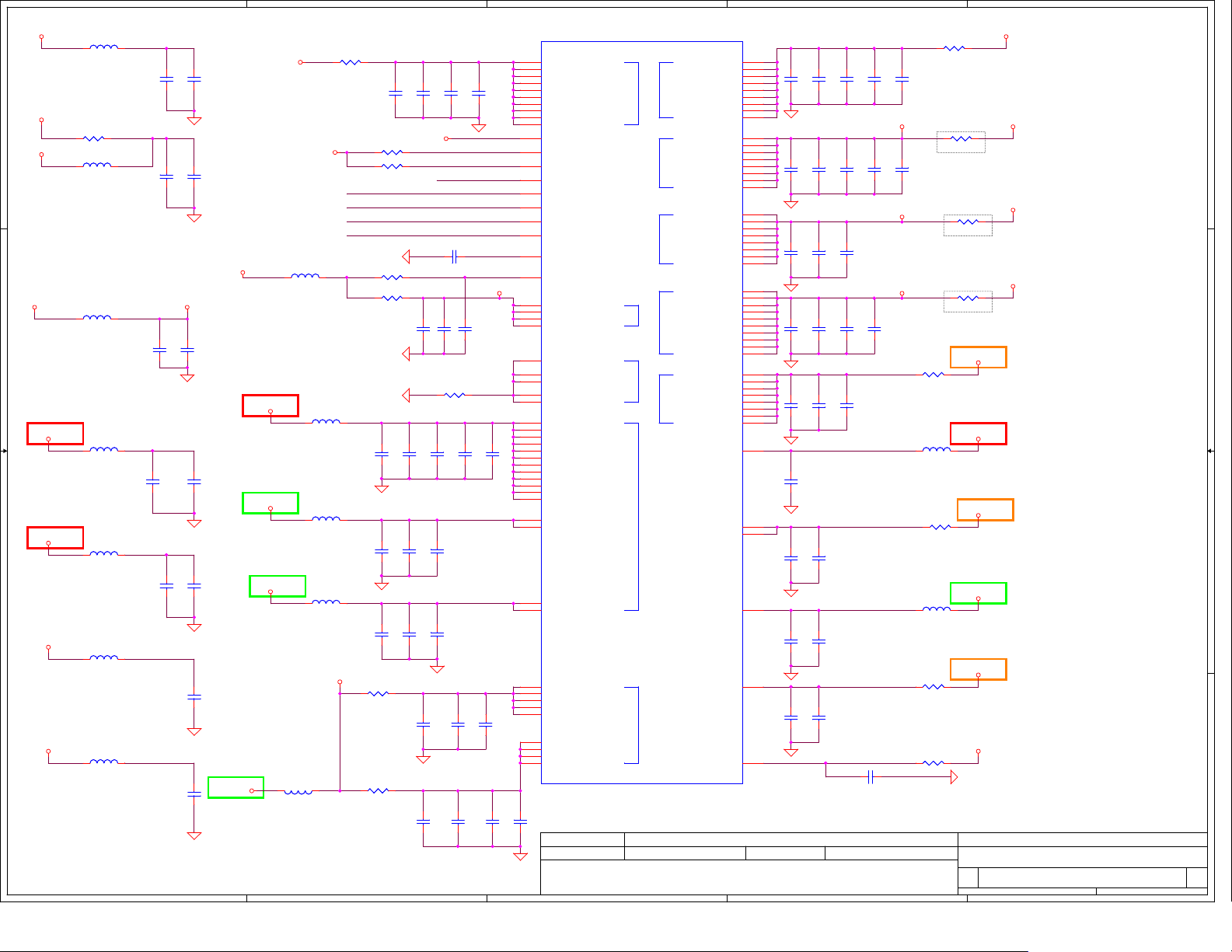

Voltage Rails

Power Plane Description

VIN

B+

+APU_CORE

+APU_CORE_NB ON OFF OFFVoltage for On-die VGA of APU

1 1

+1.5V ON

+0.75VS OFFON OFF0.75V switched power rail for DDR termi nator

+1.2VS ON OFF OFF

+2.5VS

+1.1VALW 1.1V switched power rail for FCH ON ON*ON

+1.1VS

+1.5VS OFF1.5V switched power rail ON OFF

+VGA_CORE OFFOFFON0.95-1.2V switched power rai l

+1.5VGS

+1.8VGS OFFON OFF1.8V switched power rail

+1.0VGS ON OFF OFF1.0V switched power rail for VGA

+3VALW

+3VS_WLAN ON OFF

+3VS

+5VALW

+5VS

2 2

+VSB ON ON*

+RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

EC SM Bus1 address

Device Address Address

Smart Battery

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for APU

1.5V power rail for APU VDDIO and DDR

1.2V (VDDR, VDDP) switched power rail for APU

2.5V for APU VDDA

1.5V switched power rail

3.3V always on power rail

3.3V power rail for WLAN

3.3V switched power rail

5V always on power rail

5V switched power rail

VSB always on power rail

RTC power

EC SM Bus2 address

0001-011xb

HEX

15H

Device

F75303 (DDR,VRAM,CPUCORE)1001-101xb

SB-TSI

Seymour XTX

LVDS translator

B

S0 S3 S5

N/A N/A N/A

ON OFF

ON

ON OFF OFF1.1V switched power rail for FCH

ON OFF

ON

ON

ON

ON

ON

1001-100xb

1000-0010b

N/AN/AN/A

OFF

OFF

ON

OFF

OFF

OFF

ON ON*

OFF

OFF

OFF

ON

ON*

OFF

OFFON

ONON

HEX

9AH

98H

82H

FCH Hudson-M2/3

SATA Port List

SATA0

SATA1

SATA2

SATA3

SATA4

SATA5

HDD

ODD

NC

NC

NC

NC

BOM Structure

UMA@ : UMA only

DIS@ : DIS muxluss

PX40@ : PX4.0 Support

PX50@ : PX5.0 Support

CMOS@ : USB camera

C

Comal

PCIE Port List

LAN

WLAN

NC

Card Reader

NC

NC

NC

NC

APUFCH

PCIE0

PCIE1

PCIE2

PCIE3

PCIE0

PCIE1

PCIE2

PCIE3

D

FCH Hudson-M2/3

USB Port List

USB1.1

Port0

Port1

USB2.0

Port0

Port1

Port2

Port3

Port4

Port5

Port6

Port7

Port8

Port9

Port10

Port11

Port12

Port13

NC

NC

USB2.0 Port

NC

NC

NC

NC

WLAN

CMOS

FP

BT

NC

USB 3.0

USB 3.0

USB 3.0

NC

E

CONN@ : ME components

X76@, H2G@, S2G@ : VRAM

3 3

Tha@: Thames VGA

Sey@: Seymour VGA

BOM option and stencil

SDV:

FCH SMB0

Device Address

DDR DIMM1 (FCH_SMB0)

DDR DIMM2 (FCH_SMB0)

WLAN (FCH_SMB 0)

Security ROM

1001-000xb

1001-001xb

(FCH_SMB0)

HEX

90

92

CMOS@/DIS@/PX40@/SEY@ + X76@

PJ201,PJ401,PJ502,PJ503,PJ504,PJ601,PJ603,PJ604,

PJ701,PJ702,PJ703,PJ704,J1,J2301,J2401,J2402,J2403

PJ402,PJ403,PJ501,PJ602,PJ801,PJ802,PJ803,PJ804,PJ805

Stencil Memo

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/04/18 2015/07/08

2011/04/18 2015/07/08

2011/04/18 2015/07/08

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-8124P

LA-8124P

LA-8124P

3 50Monday, January 16, 2 012

3 50Monday, January 16, 2 012

3 50Monday, January 16, 2 012

E

0.4

0.4

0.4

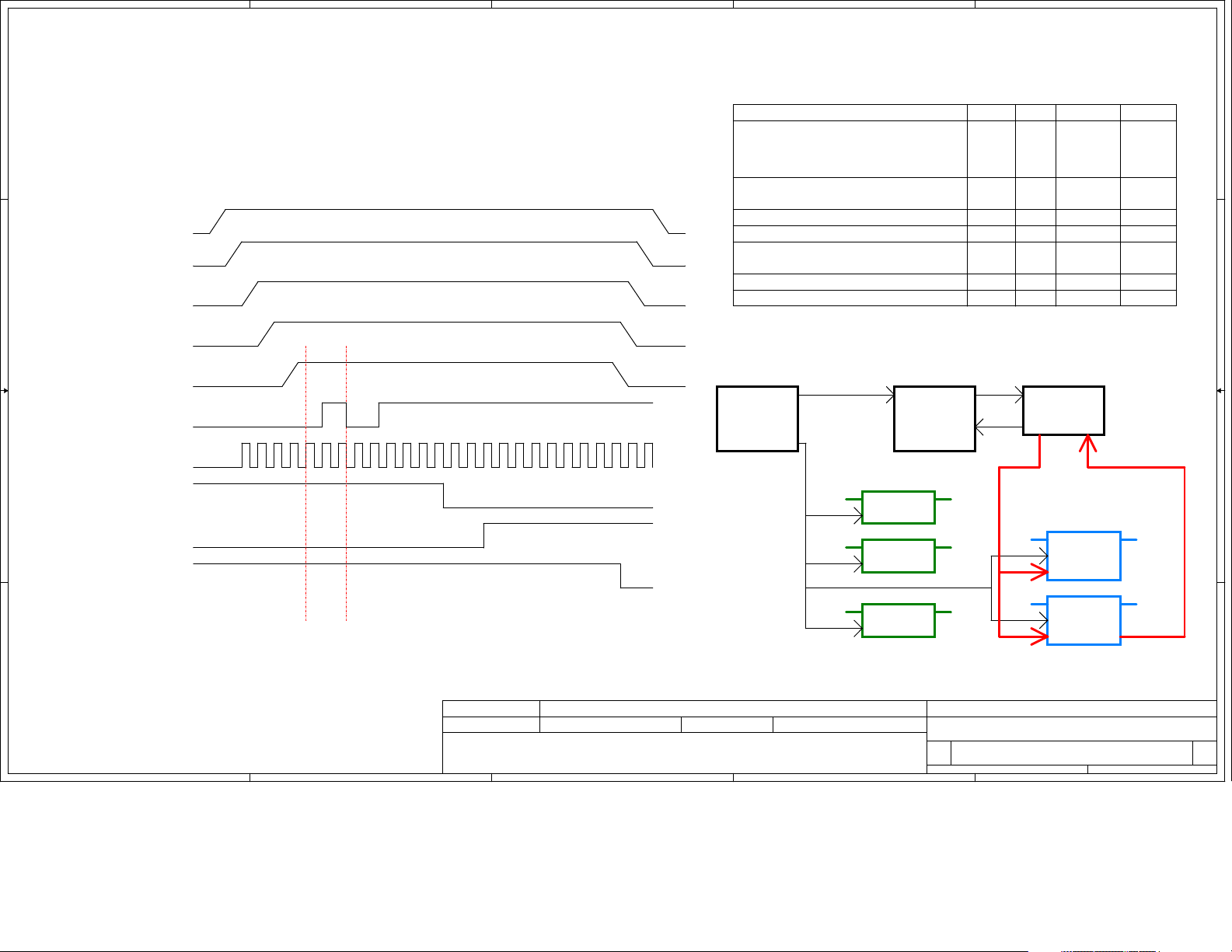

5

4

3

2

1

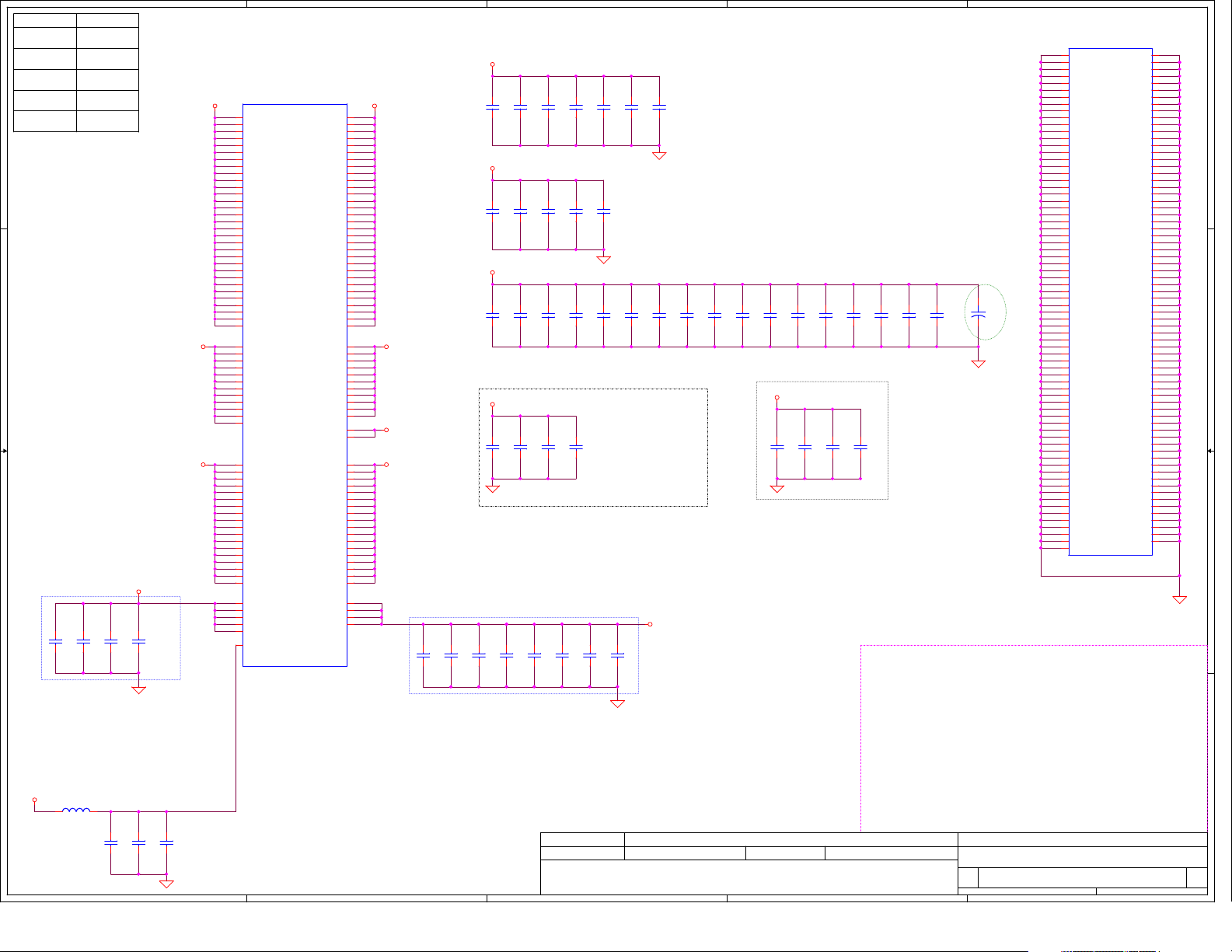

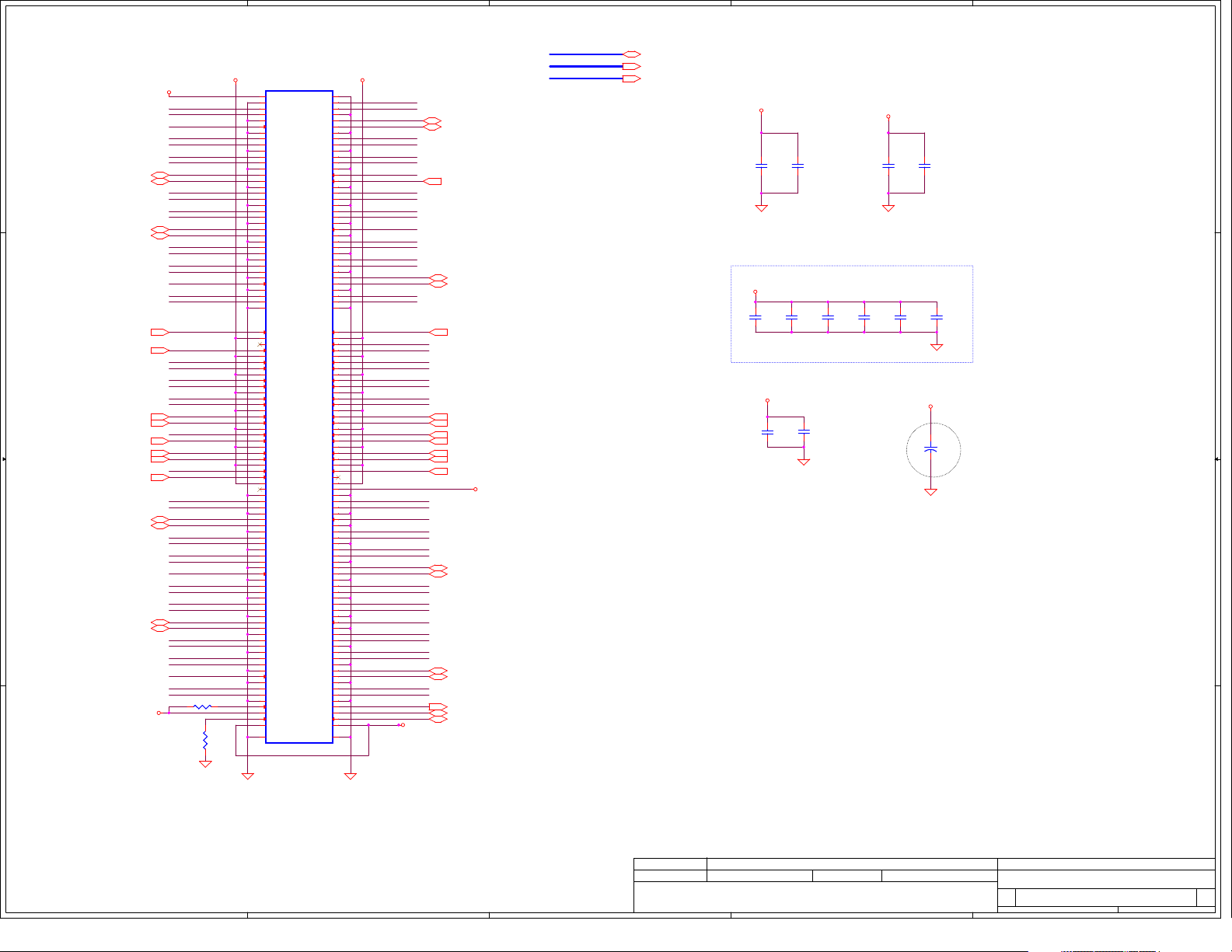

Without BACO option :

Power-Up/Down Sequence

All the ASIC supplies, except for VDDR3, must fully reach their respective

‧

nominal voltages within 20 ms of the start of the ramp-up sequence, though a

shorter ramp-up duration is preferred. There is no timing requirement on the

ramp up of VDDR3 relative to other power rails.

D D

The external pull-up resistors on the DDC/AUX signals (if applicable) should

‧

ramp up before or after both VDDC and VDD_CT have ramped up.

VDDC and VDD_CT should not ramp up simultaneously. For example, VDDC

‧

should reach 90% before VDD_CT starts to ramp up (or vice versa).

For power down, reversing the ramp-up sequence is recommended.

‧

VDDR3(3.3VGS)

PCIE_VDDC(1.0V)

C C

VDDR1(1.5VGS)

PE_GPIO0 : Low -> Reset dGPU ; High ->Normal operation

PE_GPIO1 : Low -> dGPU Power OFF ; High -> dGPU Power ON

BACO option :

PE_GPIO0 : High ->Normal operation (dGPU is not reset on BACO mode)

PE_GPIO1 : Low -> dGPU Power OFF ; High -> dGPU Power ON (always High)

dGPU Power Pins Max current

PCIE_PVDD, PCIE_VDDR, TSVDD, VDDR4, VDD_CT,

DPE_PVDD, DP[F:E]_VDD18, DP[D:A]_PVDD,

DP[D:A]_VDD18, AVDD, VDD1DI, A2VDDQ, VDD2DI,

DPLL_PVDD, MPV18, and SPV18

DP[F:E]_VDD10, DP[D:A]_VDD10, DPLL_VDDC, and

SPV10

PCIE_VDDC

VDDR3

BIF_VDDC (current consumption = 55mA@1.0V, in

BACO mode)

VDDR1

VDDC/VDDCI

Voltage

1.8V

1.0V

1.0V

3.3V

Same as

VDDC

1.5V

TBD

PX 3.0

OFF

OFF

OFF

OFF

OFF

OFF

OFF

BACO Mode

ON

ON

ON

ON

ON

Same as

PCIE_VDDC

OFF

OFF

1679mA

775mA

1.1A

60mA

70mA

1.2A

28

VDDC/VDDCI(1.12V)

VDD_CT(1.8V)

iGPU

PERSTb

REFCLK

B B

Straps Reset

Straps Valid

Global ASIC Reset

T4+16clock

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERI NG DRAWING IS THE PROPRIETARY PROPERTY OF COMP AL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERI NG DRAWING IS THE PROPRIETARY PROPERTY OF COMP AL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERI NG DRAWING IS THE PROPRIETARY PROPERTY OF COMP AL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMAT ION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

AND TRADE SECRET INFORMAT ION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

AND TRADE SECRET INFORMAT ION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION IT CONTAIN S

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION IT CONTAIN S

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION IT CONTAIN S

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONS ENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONS ENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONS ENT OF COMPAL ELECTRONICS, INC.

2011/04/18 2015/07/08

2011/04/18 2015/07/08

2011/04/18 2015/07/08

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

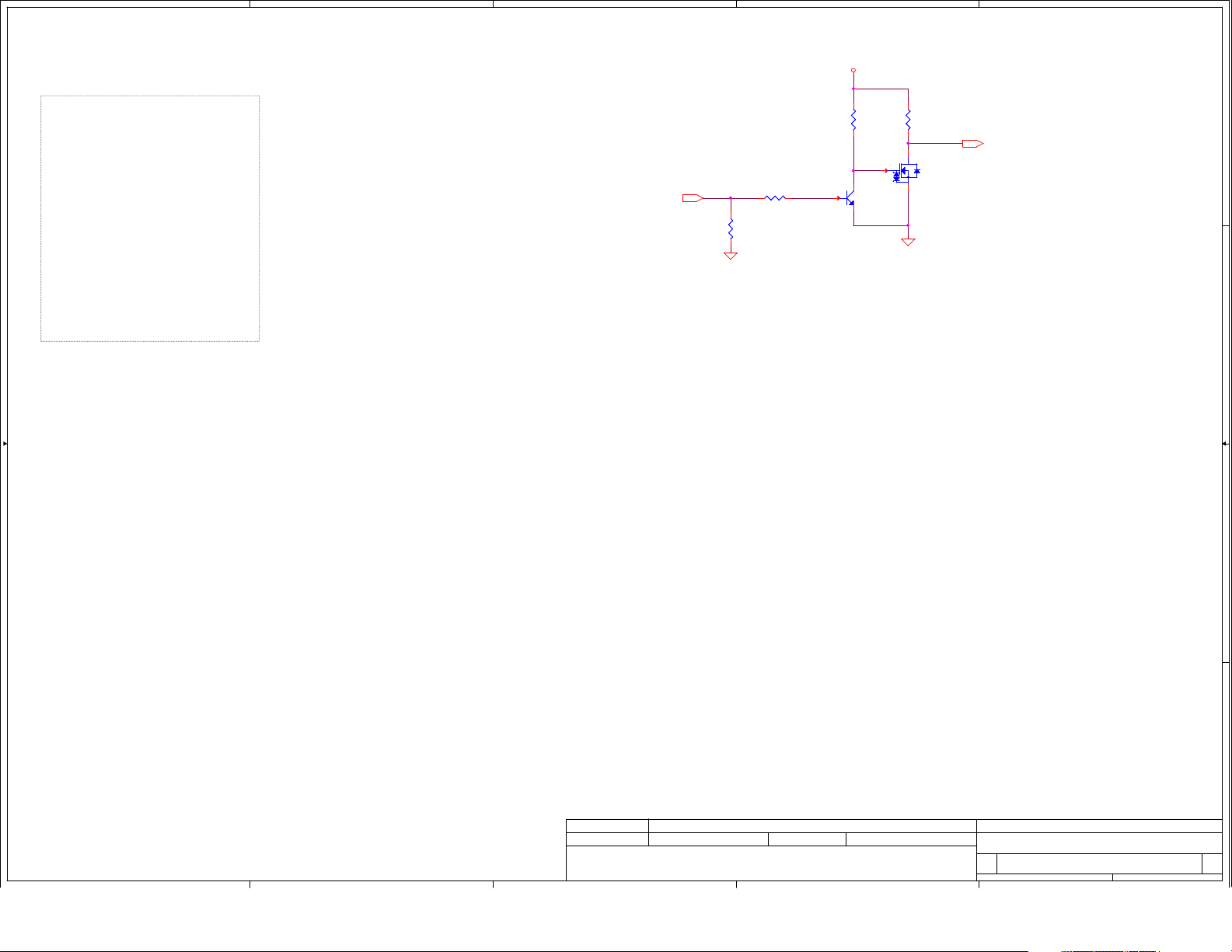

PE_GPIO0(PXS_RST#) PE_EN

dGPU

BIF_VDDC

PE_GPIO1(PXS_PWREN )

+3.3VALW

+1.5V

+5VLAW

MOS

LDO

Regulator

2

+3.3VGS

1

+1.0VGS

2

+1.8VGS

5

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

BACO Switch

PX_mode

+1.5V

SI4800

+B

Regulator

dGPU Block Diagram

dGPU Block Diagram

dGPU Block Diagram

LA-8124P

LA-8124P

LA-8124P

3

4

1

+1.5VGS

+VGA_CORE

PWRGOOD

4 50Monday, January 16, 2012

4 50Monday, January 16, 2012

4 50Monday, January 16, 2012

0.4

0.4

0.4

A

B

C

D

E

PCIE_CRX_GTX_P[0..15]17

JCPU1A

JCPU1A

PCI EXPRESS

PCI EXPRESS

P_GFX_RXP0

P_GFX_RXN0

P_GFX_RXP1

P_GFX_RXN1

P_GFX_RXP2

P_GFX_RXN2

P_GFX_RXP3

P_GFX_RXN3

P_GFX_RXP4

P_GFX_RXN4

P_GFX_RXP5

P_GFX_RXN5

P_GFX_RXP6

P_GFX_RXN6

P_GFX_RXP7

P_GFX_RXN7

P_GFX_RXP8

P_GFX_RXN8

P_GFX_RXP9

P_GFX_RXN9

P_GFX_RXP10

P_GFX_RXN10

P_GFX_RXP11

P_GFX_RXN11

P_GFX_RXP12

P_GFX_RXN12

P_GFX_RXP13

P_GFX_RXN13

P_GFX_RXP14

P_GFX_RXN14

P_GFX_RXP15

P_GFX_RXN15

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_UMI_RXP0

P_UMI_RXN0

P_UMI_RXP1

P_UMI_RXN1

P_UMI_RXP2

P_UMI_RXN2

P_UMI_RXP3

P_UMI_RXN3

P_ZVDDP

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

CONN@

GPP GRAPHICS

GPP GRAPHICS

UMI

UMI

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

AB2

PCIE_CTX_C_GRX_P0

AB1

PCIE_CTX_C_GRX_N0

AA3

PCIE_CTX_C_GRX_P1

AA2

PCIE_CTX_C_GRX_N1

Y5

PCIE_CTX_C_GRX_P2

Y4

PCIE_CTX_C_GRX_N2

Y2

PCIE_CTX_C_GRX_P3

Y1

PCIE_CTX_C_GRX_N3

W3

PCIE_CTX_C_GRX_P4

W2

PCIE_CTX_C_GRX_N4

V5

PCIE_CTX_C_GRX_P5

V4

PCIE_CTX_C_GRX_N5

V2

PCIE_CTX_C_GRX_P6

V1

PCIE_CTX_C_GRX_N6

U3

PCIE_CTX_C_GRX_P7

U2

PCIE_CTX_C_GRX_N7

T5

PCIE_CTX_C_GRX_P8

T4

PCIE_CTX_C_GRX_N8

T2

PCIE_CTX_C_GRX_P9

T1

PCIE_CTX_C_GRX_N9

R3

PCIE_CTX_C_GRX_P10

R2

PCIE_CTX_C_GRX_N10

P5

PCIE_CTX_C_GRX_P11

P4

PCIE_CTX_C_GRX_N11

P2

PCIE_CTX_C_GRX_P12

P1

PCIE_CTX_C_GRX_N12

N3

PCIE_CTX_C_GRX_P13

N2

PCIE_CTX_C_GRX_N13

M5

PCIE_CTX_C_GRX_P14

M4

PCIE_CTX_C_GRX_N14

M2

PCIE_CTX_C_GRX_P15

M1

PCIE_CTX_C_GRX_N15

AD5

PCIE_CTX_C_DRX_P0

AD4

PCIE_CTX_C_DRX_N0

AD2

PCIE_CTX_C_DRX_P1

AD1

PCIE_CTX_C_DRX_N1

AC3

AC2

AB5

PCIE_CTX_C_DRX_P3

AB4

PCIE_CTX_C_DRX_N3

AG2

UMI_TXP0_C

AG3

UMI_TXN0_C

AF4

UMI_TXP1_C

AF5

UMI_TXN1_C

AF1

UMI_TXP2_C

AF2

UMI_TXN2_C

AE2

UMI_TXP3_C

AE3

UMI_TXN3_C

AH11

P_ZVSS

1 2

R2 196_0402_1%R2 196_0402_1%

P_ZVDDP

AG11

AB8

AB7

AA9

AA8

AA5

AA6

Y8

Y7

W9

W8

W5

W6

V8

V7

U9

U8

U5

U6

T8

T7

R9

R8

R5

R6

P8

P7

N9

N8

N5

N6

M8

M7

AE5

AE6

AD8

AD7

AC9

AC8

AC5

AC6

AG8

AG9

AG6

AG5

AF7

AF8

AE8

AE9

PCIE_CRX_GTX_P0

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_N1

1 1

PCIE_CRX_DTX_P035

PCIE_CRX_DTX_N035

LAN

PCIE_CRX_DTX_P133

PCIE_CRX_DTX_N133

2 2

WLAN

Card Reader

PCIE_CRX_DTX_P335

PCIE_CRX_DTX_N335

UMI_RXP012

UMI_RXN012

UMI_RXP112

UMI_RXN112

UMI_RXP212

UMI_RXN212

UMI_RXP312

UMI_RXN312

+1.2VS

PCIE_CRX_GTX_P2

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P3

PCIE_CRX_GTX_N3

PCIE_CRX_GTX_P4

PCIE_CRX_GTX_N4

PCIE_CRX_GTX_P5

PCIE_CRX_GTX_N5

PCIE_CRX_GTX_P6

PCIE_CRX_GTX_N6

PCIE_CRX_GTX_P7

PCIE_CRX_GTX_N7

PCIE_CRX_GTX_P8

PCIE_CRX_GTX_N8

PCIE_CRX_GTX_P9

PCIE_CRX_GTX_N9

PCIE_CRX_GTX_P10

PCIE_CRX_GTX_N10

PCIE_CRX_GTX_P11

PCIE_CRX_GTX_N11

PCIE_CRX_GTX_P12

PCIE_CRX_GTX_N12

PCIE_CRX_GTX_P13

PCIE_CRX_GTX_N13

PCIE_CRX_GTX_P14

PCIE_CRX_GTX_N14

PCIE_CRX_GTX_P15

PCIE_CRX_GTX_N15

1 2

R1 196_0402_1%R1 196_0402_1%

1 2

C1 .1U_0402_16V7KDIS@C1 .1U_0402_16V7KDIS@

1 2

C2 .1U_0402_16V7KDIS@C2 .1U_0402_16V7KDIS@

1 2

C3 .1U_0402_16V7KDIS@C3 .1U_0402_16V7KDIS@

1 2

C4 .1U_0402_16V7KDIS@C4 .1U_0402_16V7KDIS@

1 2

C5 .1U_0402_16V7KDIS@C5 .1U_0402_16V7KDIS@

1 2

C6 .1U_0402_16V7KDIS@C6 .1U_0402_16V7KDIS@

1 2

C7 .1U_0402_16V7KDIS@C7 .1U_0402_16V7KDIS@

1 2

C8 .1U_0402_16V7KDIS@C8 .1U_0402_16V7KDIS@

1 2

C9 .1U_0402_16V7KDIS@C9 .1U_0402_16V7KDIS@

1 2

C10 .1U_0402_16V7KDIS@C10 .1U_0402_16V7KDIS@

1 2

C11 .1U_0402_16V7KDIS@C11 .1U_0402_16V7KDIS@

1 2

C12 .1U_0402_16V7KDIS@C12 .1U_0402_16V7KDIS@

1 2

C13 .1U_0402_16V7KDIS@C13 .1U_0402_16V7KDIS@

1 2

C14 .1U_0402_16V7KDIS@C14 .1U_0402_16V7KDIS@

1 2

C15 .1U_0402_16V7KDIS@C15 .1U_0402_16V7KDIS@

1 2

C16 .1U_0402_16V7KDIS@C16 .1U_0402_16V7KDIS@

1 2

C17 .1U_0402_16V7KDIS@C17 .1U_0402_16V7KDIS@

1 2

C18 .1U_0402_16V7KDIS@C18 .1U_0402_16V7KDIS@

1 2

C19 .1U_0402_16V7KDIS@C19 .1U_0402_16V7KDIS@

1 2

C20 .1U_0402_16V7KDIS@C20 .1U_0402_16V7KDIS@

1 2

C21 .1U_0402_16V7KDIS@C21 .1U_0402_16V7KDIS@

1 2

C22 .1U_0402_16V7KDIS@C22 .1U_0402_16V7KDIS@

1 2

C23 .1U_0402_16V7KDIS@C23 .1U_0402_16V7KDIS@

1 2

C24 .1U_0402_16V7KDIS@C24 .1U_0402_16V7KDIS@

1 2

C25 .1U_0402_16V7KDIS@C25 .1U_0402_16V7KDIS@

1 2

C26 .1U_0402_16V7KDIS@C26 .1U_0402_16V7KDIS@

1 2

C27 .1U_0402_16V7KDIS@C27 .1U_0402_16V7KDIS@

1 2

C28 .1U_0402_16V7KDIS@C28 .1U_0402_16V7KDIS@

1 2

C29 .1U_0402_16V7KDIS@C29 .1U_0402_16V7KDIS@

1 2

C30 .1U_0402_16V7KDIS@C30 .1U_0402_16V7KDIS@

1 2

C31 .1U_0402_16V7KDIS@C31 .1U_0402_16V7KDIS@

1 2

C32 .1U_0402_16V7KDIS@C32 .1U_0402_16V7KDIS@

1 2

C33 . 1U_0402_16V7KC33 .1U_0402_16 V7K

1 2

C34 . 1U_0402_16V7KC34 .1U_0402_16 V7K

1 2

C123 .1U_0402_16V7KC123 .1U_0402_16V7K

1 2

C124 .1U_0402_16V7KC124 .1U_0402_16V7K

1 2

C35 . 1U_0402_16V7KC35 .1U_0402_16 V7K

1 2

C36 . 1U_0402_16V7KC36 .1U_0402_16 V7K

1 2

C37 . 1U_0402_16V7KC37 .1U_0402_16 V7K

1 2

C38 . 1U_0402_16V7KC38 .1U_0402_16 V7K

1 2

C39 . 1U_0402_16V7KC39 .1U_0402_16 V7K

1 2

C40 . 1U_0402_16V7KC40 .1U_0402_16 V7K

1 2

C41 . 1U_0402_16V7KC41 .1U_0402_16 V7K

1 2

C42 .1U_0402_16V7KC42 .1U_0402_16V7K

1 2

C43 . 1U_0402_16V7KC43 .1U_0402_16 V7K

1 2

C44 . 1U_0402_16V7KC44 .1U_0402_16 V7K

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_P8

PCIE_CTX_GRX_N8

PCIE_CTX_GRX_P9

PCIE_CTX_GRX_N9

PCIE_CTX_GRX_P10

PCIE_CTX_GRX_N10

PCIE_CTX_GRX_P11

PCIE_CTX_GRX_N11

PCIE_CTX_GRX_P12

PCIE_CTX_GRX_N12

PCIE_CTX_GRX_P13

PCIE_CTX_GRX_N13

PCIE_CTX_GRX_P14

PCIE_CTX_GRX_N14

PCIE_CTX_GRX_P15

PCIE_CTX_GRX_N15

PCIE_CTX_GRX_P[0..15] 17

PCIE_CTX_GRX_N[0..15] 17PCIE_CRX_GTX_N[0..15]17

PCIE_CTX_DRX_P0 35

PCIE_CTX_DRX_N0 35

PCIE_CTX_DRX_P1 33

PCIE_CTX_DRX_N1 33

PCIE_CTX_DRX_P3 35

PCIE_CTX_DRX_N3 35

UMI_TXP0 12

UMI_TXN0 12

UMI_TXP1 12

UMI_TXN1 12

UMI_TXP2 12

UMI_TXN2 12

UMI_TXP3 12

UMI_TXN3 12

3 3

Power Sequence of APU

+1.5V

+2.5VS

+1.5VS

+APU_CORE

4 4

+APU_CORE_NB

+1.2VS

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/04/18 2015/07/08

2011/04/18 2015/07/08

2011/04/18 2015/07/08

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

FS1r2 PCIE/UMI

FS1r2 PCIE/UMI

FS1r2 PCIE/UMI

LA-8121P

LA-8121P

LA-8121P

E

5 50Monday, January 16, 2 012

5 50Monday, January 16, 2 012

5 50Monday, January 16, 2 012

Group A

Group B

0.4

0.4

0.4

A

1 1

JCPU1B

JCPU1B

MEMORY CHANNEL A

DDRA_SMA[15..0]10

DDRA_SBS0#10

DDRA_SBS1#10

DDRA_SBS2#10

DDRA_SDM[7..0]10

2 2

DDRA_SDQS010

DDRA_SDQS0#10

DDRA_SDQS110

DDRA_SDQS1#10

DDRA_SDQS210

DDRA_SDQS2#10

DDRA_SDQS310

DDRA_SDQS3#10

DDRA_SDQS410

DDRA_SDQS4#10

DDRA_SDQS510

DDRA_SDQS5#10

DDRA_SDQS610

DDRA_SDQS6#10

DDRA_SDQS710

DDRA_SDQS7#10

DDRA_CLK010

DDRA_CLK0#10

DDRA_CLK110

DDRA_CLK1#10

DDRA_CKE010

DDRA_CKE110

DDRA_ODT010

DDRA_ODT110

3 3

DDRA_SCS0#10

DDRA_SCS1#10

DDRA_SRAS#10

DDRA_SCAS#10

DDRA_SWE#10

MEM_MA_RST#10

MEM_MA_EVENT#10

+MEM_VREF

+1.5V

15mil

Place them close to APU within 1"

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

DDRA_SMA13

DDRA_SMA14

DDRA_SMA15

DDRA_SBS0#

DDRA_SBS1#

DDRA_SBS2#

DDRA_SDM0

DDRA_SDM1

DDRA_SDM2

DDRA_SDM3

DDRA_SDM4

DDRA_SDM5

DDRA_SDM6

DDRA_SDM7

DDRA_SDQS0

DDRA_SDQS0#

DDRA_SDQS1

DDRA_SDQS1#

DDRA_SDQS2

DDRA_SDQS2#

DDRA_SDQS3

DDRA_SDQS3#

DDRA_SDQS4

DDRA_SDQS4#

DDRA_SDQS5

DDRA_SDQS5#

DDRA_SDQS6

DDRA_SDQS6#

DDRA_SDQS7

DDRA_SDQS7#

DDRA_CLK0

DDRA_CLK0#

DDRA_CLK1

DDRA_CLK1#

DDRA_CKE0

DDRA_CKE1

DDRA_ODT0

DDRA_ODT1

DDRA_SCS0#

DDRA_SCS1#

DDRA_SRAS#

DDRA_SCAS#

DDRA_SWE#

MEM_MA_RST#

MEM_MA_EVENT#

1 2

R3 39.2_0402_1%R3 39.2_0402_1%

M_ZVDDIO

AA25

AD27

AC23

AD19

AC15

AE26

AD26

AB22

AA22

AB18

AA18

AA14

AA15

AA27

AA26

W24

W23

W20

W21

U20

R20

R21

P22

P21

N24

N23

N20

N21

M21

U23

M22

L24

L21

L20

U24

U21

L23

E14

J17

E21

F25

G14

H14

G18

H18

J21

H21

E27

E26

T21

T22

R23

R24

H28

H27

Y25

V22

V21

H25

T24

MEMORY CHANNEL A

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_CKE0

MA_CKE1

MA_ODT0

MA_ODT1

MA_CS_L0

MA_CS_L1

MA_RAS_L

MA_CAS_L

MA_WE_L

MA_RESET_L

MA_EVENT_L

M_VREF

M_ZVDDIO

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

CONN@

B

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

E13

J13

H15

J15

H13

F13

F15

E15

H17

F17

E19

J19

G16

H16

H19

F19

H20

F21

J23

H23

G20

E20

G22

H22

G24

E25

G27

G26

F23

H24

E28

F27

AB28

AC27

AD25

AA24

AE28

AD28

AB26

AC25

Y23

AA23

Y21

AA20

AB24

AD24

AA21

AC21

AA19

AC19

AC17

AA17

AB20

Y19

AD18

AD17

AA16

Y15

AA13

AC13

Y17

AB16

AB14

Y13

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

DDRA_SDQ[63..0] 10

C

DDRB_SMA[15..0]11

DDRB_SBS0#11

DDRB_SBS1#11

DDRB_SBS2#11

DDRB_SDM[7..0]11

DDRB_SDQS011

DDRB_SDQS0#1 1

DDRB_SDQS111

DDRB_SDQS1#1 1

DDRB_SDQS211

DDRB_SDQS2#1 1

DDRB_SDQS311

DDRB_SDQS3#1 1

DDRB_SDQS411

DDRB_SDQS4#1 1

DDRB_SDQS511

DDRB_SDQS5#1 1

DDRB_SDQS611

DDRB_SDQS6#1 1

DDRB_SDQS711

DDRB_SDQS7#1 1

DDRB_CLK011

DDRB_CLK0#11

DDRB_CLK111

DDRB_CLK1#11

DDRB_CKE011

DDRB_CKE111

DDRB_ODT011

DDRB_ODT111

DDRB_SCS0#11

DDRB_SCS1#11

DDRB_SRAS#11

DDRB_SCAS#11

DDRB_SWE#11

MEM_MB_RST#11

MEM_MB_EVENT#11

DDRB_SMA0

DDRB_SMA1

DDRB_SMA2

DDRB_SMA3

DDRB_SMA4

DDRB_SMA5

DDRB_SMA6

DDRB_SMA7

DDRB_SMA8

DDRB_SMA9

DDRB_SMA10

DDRB_SMA11

DDRB_SMA12

DDRB_SMA13

DDRB_SMA14

DDRB_SMA15

DDRB_SBS0#

DDRB_SBS1#

DDRB_SBS2#

DDRB_SDM0

DDRB_SDM1

DDRB_SDM2

DDRB_SDM3

DDRB_SDM4

DDRB_SDM5

DDRB_SDM6

DDRB_SDM7

DDRB_SDQS0

DDRB_SDQS0#

DDRB_SDQS1

DDRB_SDQS1#

DDRB_SDQS2

DDRB_SDQS2#

DDRB_SDQS3

DDRB_SDQS3#

DDRB_SDQS4

DDRB_SDQS4#

DDRB_SDQS5

DDRB_SDQS5#

DDRB_SDQS6

DDRB_SDQS6#

DDRB_SDQS7

DDRB_SDQS7#

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#

DDRB_CKE0

DDRB_CKE1

DDRB_ODT0

DDRB_ODT1

DDRB_SCS0#

DDRB_SCS1#

DDRB_SRAS#

DDRB_SCAS#

DDRB_SWE#

MEM_MB_RST#

MEM_MB_EVENT#

D

JCPU1C

JCPU1C

MEMORY CHANNEL B

MEMORY CHANNEL B

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CKE0

MB_CKE1

MB_ODT0

MB_ODT1

MB_CS_L0

MB_CS_L1

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

MB_EVENT_L

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

CONN@

W26

AF25

AG22

AH18

AD14

AG24

AG25

AG21

AF21

AG17

AG18

AH14

AG14

W27

T27

P24

P25

N27

N26

M28

M27

M24

M25

L26

U26

L27

K27

K25

K24

U27

T28

K28

D14

A18

A22

C25

C15

B15

E18

D18

E22

D22

B26

A26

R26

R27

P27

P28

J26

J27

Y28

V25

Y27

V24

V27

V28

J25

T25

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

A14

B14

D16

E16

B13

C13

B16

A16

C17

B18

B20

A20

E17

B17

B19

C19

C21

B22

C23

A24

D20

B21

E23

B23

E24

B25

B27

D28

B24

D24

D26

C27

AG26

AH26

AF23

AG23

AG27

AF27

AH24

AE24

AE22

AH22

AE20

AH20

AD23

AD22

AD21

AD20

AF19

AE18

AE16

AH16

AG20

AG19

AF17

AD16

AG15

AD15

AG13

AD13

AG16

AF15

AE14

AF13

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ4

DDRB_SDQ5

DDRB_SDQ6

DDRB_SDQ7

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ12

DDRB_SDQ13

DDRB_SDQ14

DDRB_SDQ15

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDQ22

DDRB_SDQ23

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDQ26

DDRB_SDQ27

DDRB_SDQ28

DDRB_SDQ29

DDRB_SDQ30

DDRB_SDQ31

DDRB_SDQ32

DDRB_SDQ33

DDRB_SDQ34

DDRB_SDQ35

DDRB_SDQ36

DDRB_SDQ37

DDRB_SDQ38

DDRB_SDQ39

DDRB_SDQ40

DDRB_SDQ41

DDRB_SDQ42

DDRB_SDQ43

DDRB_SDQ44

DDRB_SDQ45

DDRB_SDQ46

DDRB_SDQ47

DDRB_SDQ48

DDRB_SDQ49

DDRB_SDQ50

DDRB_SDQ51

DDRB_SDQ52

DDRB_SDQ53

DDRB_SDQ54

DDRB_SDQ55

DDRB_SDQ56

DDRB_SDQ57

DDRB_SDQ58

DDRB_SDQ59

DDRB_SDQ60

DDRB_SDQ61

DDRB_SDQ62

DDRB_SDQ63

E

DDRB_SDQ[63..0] 1 1

EVENT# pull high 0.75V reference voltage

+1.5V

4 4

1 2

R5 1K_0402_5%R5 1K_0402_5%

1 2

R6 1K_0402_5%R6 1K_0402_5%

MEM_MA_EVENT#

MEM_MB_EVENT# +MEM_VREF

A

R4

R4

1K_0402_1%

1K_0402_1%

R7

R7

1K_0402_1%

1K_0402_1%

+1.5V

1 2

1

C45

C45

1000P_0402_50V7K

1000P_0402_50V7K

2

1 2

B

15mil

2

C46

C46

.1U_0402_16V7K

.1U_0402_16V7K

1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/04/18 2015/07/08

2011/04/18 2015/07/08

2011/04/18 2015/07/08

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

FS1r2 DDRIII Memory I/F

FS1r2 DDRIII Memory I/F

FS1r2 DDRIII Memory I/F

LA-8121P

LA-8121P

LA-8121P

6 50Monday, January 16, 2 012

6 50Monday, January 16, 2 012

6 50Monday, January 16, 2 012

E

0.4

0.4

0.4

A

Place near APU

1 2

DP0_TXP0_C25

DP0_TXN0_C25

1 1

2 2

+1.5V

3 3

4 4

1 2

R49 1K_0402_5%R49 1K_0402_5%

1 2

R52 1K_0402_5%R52 1K_0402_5%

1 2

R32 1K_0402_5%R32 1K_0402_5%

1 2

R37 1K_0402_5%R37 1K_0402_5%

1 2

R39 1K_0402_5%R39 1K_0402_5%

R36 1K_0402_5%R36 1K_0402_5%

1 2

R33 1K_0402_5%@R33 1K_0402_5%@

1 2

R38 1K_0402_5%@R38 1K_0402_5%@

1 2

R40 1K_0402_5%@R40 1K_0402_5%@

1 2

R41 1K_0402_5%R41 1K_0402_5%

1 2

R43 1K_0402_5%R43 1K_0402_5%

1 2

R46 1K_0402_5%R46 1K_0402_5%

+1.5VS

1 2

R54 300_0402_5%R54 300_0402_5%

1 2

R57 300_0402_5%R57 300_0402_5%

+3VS

1 2

R60 10K_0402_5%R60 10K_0402_5%

1 2

R61 10K_0402_5%R61 10K_0402_5%

Aux signal are re-configured as I2C signals for DDC. APU AUX pin are 3.3V tolerant

Default follow PAWGX setting for pull-high resistor value

ML_VGA_TXP013

ML_VGA_TXN01 3

ML_VGA_TXP113

ML_VGA_TXN11 3

ML_VGA_TXP213

ML_VGA_TXN21 3

ML_VGA_TXP313

ML_VGA_TXN31 3

HDMI_TX2P27

HDMI_TX2N27

HDMI_TX1P27

HDMI_TX1N27

HDMI_TX0P27

HDMI_TX0N27

HDMI_CLKP27

HDMI_CLKN27

Route as differential

with VSS_SENSE

ALLOW_STOP

APU_DBREQ#

12

APU_TRST#

APU_RST#

APU_PWRGD

A

APU_TCK

APU_TMS

APU_TDI

APU_SVT

APU_SVC

APU_SVD

APU_SIC

APU_SID

ALERT_L

HDMI_CLK

HDMI_DATA

C52 .1U_0402_16V7KC52 .1U_0402_16V7K

1 2

C47 .1U_0402_16V7KC47 .1U_0402_16V7K

1 2

C61 .1U_0402_16V7KC61 .1U_0402_16V7K

1 2

C62 .1U_0402_16V7KC62 .1U_0402_16V7K

1 2

C63 .1U_0402_16V7KC63 .1U_0402_16V7K

1 2

C64 .1U_0402_16V7KC64 .1U_0402_16V7K

1 2

C65 .1U_0402_16V7KC65 .1U_0402_16V7K

1 2

C66 .1U_0402_16V7KC66 .1U_0402_16V7K

1 2

C67 .1U_0402_16V7KC67 .1U_0402_16V7K

1 2

C68 .1U_0402_16V7KC68 .1U_0402_16V7K

1 2

C50 .1U_0402_16V7KC50 .1U_0402_16V7K

1 2

C51 .1U_0402_16V7KC51 .1U_0402_16V7K

1 2

C55 .1U_0402_16V7KC55 .1U_0402_16V7K

1 2

C56 .1U_0402_16V7KC56 .1U_0402_16V7K

1 2

C57 .1U_0402_16V7KC57 .1U_0402_16V7K

1 2

C58 .1U_0402_16V7KC58 .1U_0402_16V7K

1 2

C59 .1U_0402_16V7KC59 .1U_0402_16V7K

1 2

C60 .1U_0402_16V7KC60 .1U_0402_16V7K

APU_CLK12

APU_CLK#12

APU_DISP_CLK12

APU_DISP_CLK#12

APU_SVC45

APU_SVD45

APU_SVT45

T32T32

APU_RST#1 2

APU_PWRGD12,45

APU_PROCHOT#1 2

APU_VDD_SEN_L4 5

APU_VDDNB_SEN45

APU_VDD_SEN_H45

T33T33

T23T23

T24T24

T25T25

T26T26

T27T27

T28T28

T29T29

APU_RST#

APU_PWRGD

APU_PROCHOT#

APU_THERMTRIP#

ALERT_L

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

APU_VDD_SEN_L

APU_VDDNB_SEN

APU_VDD_SEN_H

FVT, NO.37

APU_CLK

APU_CLK#

APU_DISP_CLK

APU_DISP_CLK#

APU_SIC

APU_SID

T20T20

T21T21

DP0_TXP0

DP0_TXN0

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP2_TXP0

DP2_TXN0

DP2_TXP1

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

B

ANALOG/DISPLAY/MISC

ANALOG/DISPLAY/MISC

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

To FCH

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP2_TXP0

DP2_TXN0

DP2_TXP1

HDMI

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

CLKIN_H

CLKIN_L

DISP_CLKIN_H

DISP_CLKIN_L

SVC

SVD

SVT

SIC

SID

RESET_L

PWROK

PROCHOT_L

THERMTRIP_L

ALERT_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

VSS_SENSE

VDDP_SENSE

VDDNB_SENSE

VDDIO_SENSE

VDD_SENSE

VDDR_SENSE

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

CONN@

+3VS

AE11

AD11

AB11

AA11

AG12

AH12

AF10

AB12

AC10

AE12

AF12

L3

L2

K5

K4

K2

K1

J3

J2

H5

H4

H2

H1

G3

G2

F2

F1

L9

L8

L5

L6

K8

K7

J6

J5

B3

A3

C3

H10

J10

F10

G10

F9

G9

H9

B4

C5

A4

A5

C4

B5

SIT, NO.3

APU_SIC

B

LVDS

JCPU1D

JCPU1D

DISPLAY PORT 0

DISPLAY PORT 0

DISPLAY PORT MISC.

DISPLAY PORT MISC.

DISPLAY PORT 2 DISPLAY PORT 1

DISPLAY PORT 2 DISPLAY PORT 1

TEST

TEST

CTRL SER. CLK

CTRL SER. CLK

JTAG

JTAG

SENSE

SENSE

1 2

R34

R34

31.6K_0402_1%

31.6K_0402_1%

D1

DP0_AUXP

D2

DP0_AUXN

E1

DP1_AUXP

E2

DP1_AUXN

D5

DP2_AUXP

D6

DP2_AUXN

E5

DP3_AUXP

E6

DP3_AUXN

F5

DP4_AUXP

F6

DP4_AUXN

G5

DP5_AUXP

G6

DP5_AUXN

D3

DP0_HPD

E3

DP1_HPD

D7

DP2_HPD

E7

DP3_HPD

F7

DP4_HPD

G7

DP5_HPD

C6

DP_BLON

B6

DP_DIGON

DP_VARY_BL

DP_AUX_ZVSS

DMAACTIVE_L

RSVD

RSVD

A6

C1

AD12

TEST6

M18

TEST9

N18

TEST10

F11

TEST14

G11

TEST15

H11

TEST16

J11

TEST17

F12

TEST18

G12

TEST19

J12

TEST20

H12

TEST24

AE10

TEST25_H

AD10

TEST25_L

L10

TEST28_H

M10

TEST28_L

P19

TEST30_H

R19

TEST30_L

K22

TEST31

T19

TEST32_H

N19

TEST32_L

AA12

TEST35

W10

FS1R2

AC12

P18

TEST4

R18

TEST5

Y10

RSVD1

AA10

RSVD2

Y12

RSVD3

K21

RSVD4

@

@

1 2

C69 0.1U_0402_16V4Z

C69 0.1U_0402_16V4Z

1 2

R35

R35

30K_0402_1%

30K_0402_1%

2

3 1

SGD

SGD

BSH111_SOT23-3

BSH111_SOT23-3

2

3 1

SGD

SGD

BSH111_SOT23-3

BSH111_SOT23-3

DP0_AUXP

DP0_AUXN

ML_VGA_AUXP

ML_VGA_AUXN

HDMI_CLK

HDMI_DATA

LVDS_HPD

ML_VGA_HPD

HDMI_DET

DP_INT_PWM

DP_AUX_ZVSS

APU_TEST18

APU_TEST19

APU_TEST20

APU_TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

APU_TEST31

APU_TEST35

FS1R2

ALLOW_STOP

C

1 2

C53 . 1U_0402_16V7KC53 .1U_0402_16 V7K

1 2

C48 . 1U_0402_16V7KC48 .1U_0402_16 V7K

1 2

C54 . 1U_0402_16V7KC54 .1U_0402_16 V7K

1 2

C49 . 1U_0402_16V7KC49 .1U_0402_16 V7K

SIT, NO.4

LVDS_HPD 25

ML_VGA_HPD 13

HDMI_DET 27

DP_INT_PWM 9

1 2

R13 150_0402_1%R13 150_0402_1%

T1T1

T2T2

T3T3

T4T4

T5T5

T6T6

T14T14

T15T15

T7T7

T8T8

T9T9

T10T10

T30T30

T31T31

1 2

R14 1K_0402_5%R14 1K_0402_5%

1 2

R15 1K_0402_5%R15 1K_0402_5%

1 2

R16 1K_0402_5%R16 1K_0402_5%

1 2

R17 1K_0402_5%R17 1K_0402_5%

1 2

R20 510_0402_1%R20 510_0402_1%

1 2

R23 510_0402_1%R23 510_0402_1%

1 2

R25 39.2_0402_1%R25 39.2_0402_1%

1 2

R26 300_0402_5%R26 300_0402_5%

1 2

R27 300_0402_5%@R27 300_0402_5%@

1 2

R28 10K_0402_5%R28 10K_0402_5%

ALLOW_STOP 12

DP0_AUXP_C 25

DP0_AUXN_C 25

ML_VGA_AUXP_C 13

ML_VGA_AUXN_C 13

HDMI_CLK 27

HDMI_DATA 27

+1.2VS

+1.5V

+3VALW

To LVDS

Translater

To FCH

MainLink

To HDMI

Asserted as an input to force the

processor into the HTC-active state

D

SDV2, NO.45

R12

R12

1K_0402_5%

1K_0402_5%

APU_PROCHOT#

THERMTRIP shutdown

Temperature: 125 degree

ALERT_L

To FCH

+1.5V

1 2

R78 0_0402_5%@R78 0_0402_5%@

APU_THERMTRIP#

3 1

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

CPU TSI interface level shift

BSH111, the Vgs is:

min = 0.4V

Max = 1.3V

Q4

Q4

EC_SMB_DAAPU_SID

1 2

R50

@ R50

@

0_0402_5%

0_0402_5%

Q5

Q5

EC_SMB_CK

1 2

R59

@ R59

@

0_0402_5%

0_0402_5%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

@ R47

@

@ R58

@

R44

R44

R47

R55

R55

R58

1 2

0_0402_5%

0_0402_5%

1 2

0_0402_5%

0_0402_5%

1 2

0_0402_5%

0_0402_5%

1 2

0_0402_5%

0_0402_5%

2011/04/18 2015/07/08

2011/04/18 2015/07/08

2011/04/18 2015/07/08

EC_SMB_DA2 18,25,31,32,33

FCH_SID 14

EC_SMB_CK2 18,25,31,32,33

FCH_SIC 14

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

To EC

To FCH

To EC

To FCH

D

E

If not used, pins are left unconnected (DG ref.)

20101111

ML_VGA_AUXP

R9 1.8K_0402_5%R9 1.8K_0402_5%

ML_VGA_AUXN

R8 1.8K_0402_5%R8 1.8K_0402_5%

DP0_AUXP

R79 1.8K_0402_5%R79 1.8K_0402_5%

DP0_AUXN

R81 1.8K_0402_5%R81 1.8K_0402_5%

H_PROCHOT#_EC: default low/a ctive high

APU_PROCHOT# : default high/ active low

H_PROCHOT#: default high/ ac tive low

Q7

Q7

13

2N7002K_SOT23-3

2N7002K_SOT23-3

D

D

2

G

G

S

S

1 2

+1.5V

R21

R21

1K_0402_5%

1K_0402_5%

1 2

E

E

3 1

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

+1.5V

12

R29

R29

10K_0402_5%@

10K_0402_5%@

B

B

2

Q3

@

Q3

@

E

E

C

C

R30 0_0402_5%@R30 0_0402_5%@

R31 0_0402_5%@R31 0_0402_5%@

Title

Title

Title

FS1r2 Display/MISC/HDT

FS1r2 Display/MISC/HDT

FS1r2 Display/MISC/HDT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

SIT, NO.16

Indicates to the FCH that a thermal trip

has occurred. Its assertion will cause the

FCH to transition the system to S5 immediately

12

R18

R18

10K_0402_5%

10K_0402_5%

B

B

2

Q2

Q2

C

C

1 2

1 2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

LA-8121P

LA-8121P

LA-8121P

12

12

12

12

H_THERMTRIP# 14

E

H_PROCHOT#_EC 31,38

H_PROCHOT# 38,45

APU_ALERT#_FCH 13

APU_ALERT#_EC 3 1

0.4

0.4

7 50Monday, January 16, 2 012

7 50Monday, January 16, 2 012

7 50Monday, January 16, 2 012

0.4

A

Power Name

VDD

+APU_CORE

VDDNB

+APU_CORE_NB

VDDIO

+1.5V

VDDP / VDDR

+1.2VS

VDDA

1 1

+2.5VS 0.5A

2 2

3 3

Consumption

5A / 3.5A

VDDR decoupling

180P_0402_50V8J

180P_0402_50V8J

C104

C104

C103

C103

1

1

2

2

60A

44A

3.2A

180P_0402_50V8J

180P_0402_50V8J

+APU_CORE

F8

VDD_1

H6

VDD_2

J1

VDD_3

J14

VDD_4

P6

VDD_5

P10

VDD_6

J16

VDD_7

J18

VDD_8

J9

VDD_9

K19

VDD_10

K3

VDD_11

K17

VDD_12

M3

VDD_13

K6

VDD_14

V10

VDD_15

V18

VDD_16

V3

VDD_17

F3

VDD_18

L18

VDD_19

V6

VDD_20

W1

VDD_21

T18

VDD_22

Y14

VDD_23

AA1

VDD_24

AB6

VDD_25

AC1

VDD_26

R1

VDD_27

P3

VDD_28

K10

VDD_29

H3

VDD_30

M19

VDD_31

+APU_CORE_NB

+1.5V

+1.2VS

C106

0.22U_0402_6.3V6K

C106

0.22U_0402_6.3V6K

C105

0.22U_0402_6.3V6K

C105

0.22U_0402_6.3V6K

1

1

2

2

C8

VDDNB_1

D10

VDDNB_2

B8

VDDNB_3

B12

VDDNB_4

C9

VDDNB_5

A9

VDDNB_6

A10

VDDNB_7

A8

VDDNB_8

A11

VDDNB_9

E10

VDDNB_10

E11

VDDNB_11

C10

VDDNB_12

H26

VDDIO_1

K20

VDDIO_2

J28

VDDIO_3

K23

VDDIO_4

K26

VDDIO_5

L22

VDDIO_6

L25

VDDIO_7

L28

VDDIO_8

M20

VDDIO_9

M23

VDDIO_10

M26

VDDIO_11

N22

VDDIO_12

N25

VDDIO_13

N28

VDDIO_14

P20

VDDIO_15

P23

VDDIO_16

P26

VDDIO_17

AA28

VDDIO_18

AH6

VDDP_1

AH5

VDDP_2

AH4

VDDP_3

AH3

VDDP_4

AH7

VDDP_5

AB10

VDDA

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

CONN@

JCPU1E

JCPU1E

VDDNB_13

VDDNB_14

VDDNB_15

VDDNB_16

VDDNB_17

VDDNB_18

VDDNB_19

VDDNB_20

VDDNB_21

VDDNB_22

VDDNB_23

VDDNB_CAP_1

VDDNB_CAP_2

VDDIO_19

VDDIO_20

VDDIO_21

VDDIO_22

VDDIO_23

VDDIO_24

VDDIO_25

VDDIO_26

VDDIO_27

VDDIO_28

VDDIO_29

VDDIO_30

VDDIO_31

VDDIO_32

VDDIO_33

VDDIO_34

VDDIO_35

VDDIO_36

VDDR_1

VDDR_2

VDDR_3

VDDR_4

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDD_50

VDD_51

VDD_52

VDD_53

VDD_54

VDD_55

VDD_56

VDD_57

VDD_58

VDD_59

VDD_60

VDD_61

VDD_62

B

+APU_CORE

R11

T10

H8

G1

U11

W11

W13

W15

W17

W19

AB3

AD3

AD6

AE1

L1

Y6

M6

N11

N1

T3

T6

U19

U1

Y16

Y18

Y3

D4

F4

AF6

AF3

L11

C11

C12

D9

D8

D12

D11

B11

A12

B10

E12

B9

K13

K12

T23

T26

U22

U25

U28

Y26

T20

R28

R25

R22

V20

V23

V26

W22

W25

W28

Y24

G28

AG10

AH8

AH9

AH10

+APU_CORE_NB

+APU_CORE_NB_CAP

+1.5V

C107

180P_0402_50V8J

C107

180P_0402_50V8J

1

2

C108

180P_0402_50V8J

C108

180P_0402_50V8J

1

2

+APU_CORE

C73

0.22U_0402_6.3V6K

C73

0.22U_0402_6.3V6K

1

2

+APU_CORE_NB

C77

0.22U_0402_6.3V6K

C77

0.22U_0402_6.3V6K

1

2

+1.5V

C82

22U_0603_6.3V6M@C82

22U_0603_6.3V6M

1

@

2

+1.5V

C99

0.22U_0402_6.3V6K

C99

0.22U_0402_6.3V6K

1

2

C110

C109

1000P_0402_50V7K

C109

1000P_0402_50V7K

1

2

@

C70

0.01U_0402_16V7K

C70

0.01U_0402_16V7K

C74

0.22U_0402_6.3V6K

C74

0.22U_0402_6.3V6K

1

1

2

2

C78

0.22U_0402_6.3V6K

C78

0.22U_0402_6.3V6K

C79

180P_0402_50V8J

C79

180P_0402_50V8J

1

1

2

2

C84

22U_0603_6.3V6M

C84

22U_0603_6.3V6M

C83

22U_0603_6.3V6M

C83

22U_0603_6.3V6M

1

1

2

2

Across VDDIO and VSS

split

C100

0.22U_0402_6.3V6K

C100

0.22U_0402_6.3V6K

C101

180P_0402_50V8J

C101

180P_0402_50V8J

1

1

2

2

1000P_0402_50V7K@C110

1000P_0402_50V7K

C112

C111

1000P_0402_50V7K@C111

1000P_0402_50V7K

1

1

2

2

@

@

C

C71

0.01U_0402_16V7K

C71

0.01U_0402_16V7K

C75

C75

1

1

2

2

C80

180P_0402_50V8J

C80

180P_0402_50V8J

C81

C81

1

1

2

2

C85

22U_0603_6.3V6M

C85

22U_0603_6.3V6M

C86

C86

1

1

2

2

C102

180P_0402_50V8J

C102

180P_0402_50V8J

1

2

VDDR decoupling

C113

0.22U_0402_6.3V6K

C113

0.22U_0402_6.3V6K

1000P_0402_50V7K@C112

1000P_0402_50V7K

1

1

2

2

D

C72

180P_0402_50V8J

C72

180P_0402_50V8J

0.01U_0402_16V7K

0.01U_0402_16V7K

C76

180P_0402_50V8J

C76

180P_0402_50V8J

1

1

2

2

180P_0402_50V8J

180P_0402_50V8J

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

22U_0603_6.3V6M

22U_0603_6.3V6M

C114

C114

1

2

4.7U_0603_6.3V6K

C87

C87

C88

C88

1

1

2

2

+1.2VS

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

C91

C91

C90

C90

C89

C89

1

1

2

1

2

2

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

C92

0.22U_0402_6.3V6K

C92

0.22U_0402_6.3V6K

1

2

+APU_CORE_NB_CAP

C216

1

@

2

C93

0.22U_0402_6.3V6K

C93

0.22U_0402_6.3V6K

C94

C94

1

1

2

2

22U_0603_6.3V6M@C216

22U_0603_6.3V6M

C215

C215

C214

22U_0603_6.3V6M

C214

22U_0603_6.3V6M

1

2

C96

0.22U_0402_6.3V6K

C96

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

22U_0603_6.3V6M

22U_0603_6.3V6M

1

2

0.22U_0402_6.3V6K

C97

180P_0402_50V8J

C97

C95

0.22U_0402_6.3V6K

C95

0.22U_0402_6.3V6K

1

2

C217

180P_0402_50V8J

C217

180P_0402_50V8J

1

2

180P_0402_50V8J

C136

180P_0402_50V8J

C136

180P_0402_50V8J

C98

330U_D2_2.5VY_R9M+C98

330U_D2_2.5VY_R9M

1

1

2

2

1

1

+

2

2

Demo Board Capacitor

APU_CORE

22uF x 10

0.22uF x 2

0.01uF x 3

180pF x 2

CORE_NB

22uF x 2

10uF x 1

0.22uF x 2

180pF x 3

CORE_NB_CAP

22uF x 2

180pF x 1

E

JCPU1F

JCPU1F

J20

VSS_1

L4

VSS_2

R7

VSS_3

W18

VSS_4

A15

VSS_5

AB17

VSS_6

AC22

VSS_7

AE21

VSS_8

AF24

VSS_9

AH23

VSS_10

AH25

VSS_11

B7

VSS_12

C14

VSS_13

C16

VSS_14

C2

VSS_15

C20

VSS_16

C22

VSS_17

C24

VSS_18

C26

VSS_19

C28

VSS_20

D13

VSS_21

D15

VSS_22

D17

VSS_23

D19

VSS_24

D23

VSS_25

D25

VSS_26

D27

VSS_27

E4

VSS_28

E9

VSS_29

F14

VSS_30

F16

VSS_31

F18

VSS_32

F20

VSS_33

F22

VSS_34

F26

VSS_35

F28

VSS_36

G13

VSS_37

G15

VSS_38

G17

VSS_39

G19

VSS_40

G21

VSS_41

G23

VSS_42

G25

VSS_43

G4

VSS_44

J22

VSS_45

J24

VSS_46

J4

VSS_47

J7

VSS_48

K11

VSS_49

K14

VSS_50

K9

VSS_51

AC11

VSS_52

L19

VSS_53

L7

VSS_54

M11

VSS_55

AF11

VSS_56

V19

VSS_57

V9

VSS_58

W16

VSS_59

W4

VSS_60

W7

VSS_61

Y11

VSS_62

Y20

VSS_63

Y22

VSS_64

Y9

VSS_65

A17

VSS_66

A13

VSS_67

K16

VSS_68

F24

VSS_69

G8

VSS_70

H7

VSS_71

J8

VSS_72

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

CONN@

VDDIO_SUS

(CPU side)

22uF x 4

4.7uF x 4

0.22uF x 6 +2(split)

180pF x 1 + 2(split)

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

A19

A21

A23

A25

A7

AA4

AA7

AB13

AB15

AB19

AB21

AB23

AB25

AB27

AB9

AC14

AC16

AC18

AC20

AC24

AC26

AC28

AC4

AC7

AD9

AE13

AE15

AE17

M9

N10

N4

N7

R10

R4

T11

T9

U10

U18

U4

U7

V11

AE19

AE23

AE25

AE27

AE4

AE7

AF14

AF16

AF18

AF20

AF22

AF26

AF28

AF9

AG4

AG7

AH13

AH15

AH17

AH19

AH21

P9

C18

D21

W14

P11

C7

E8

K18

W12

4 4

+2.5VS

L1

L1

FBMA-L11-201209-221LMA30T_0 805

FBMA-L11-201209-221LMA30T_0 805

12

C116

C116

C115

3300P_0402_50V7-K

C115

3300P_0402_50V7-K

1

1

2

2

A

40mil

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

+VDDA

C117

4.7U_0402_6.3V6M

C117

4.7U_0402_6.3V6M

1

2

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/04/18 2015/07/08

2011/04/18 2015/07/08

2011/04/18 2015/07/08

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

VDDP

0.22uF x 2

180pF x 2

D

VDDR

0.22uF x 2

1nF x 4

180pF x 2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

VDDA

4.7uF x 1

0.22uF x 1

3.3nF x 1

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

FS1r2 PWR/GND

FS1r2 PWR/GND

FS1r2 PWR/GND

VDDIO_SUS

(DIMM x2)

100uF x 2

0.1uF x 12

LA-8121P

LA-8121P

LA-8121P

E

8 50Monday, January 16, 2 012

8 50Monday, January 16, 2 012

8 50Monday, January 16, 2 012

0.4

0.4

0.4

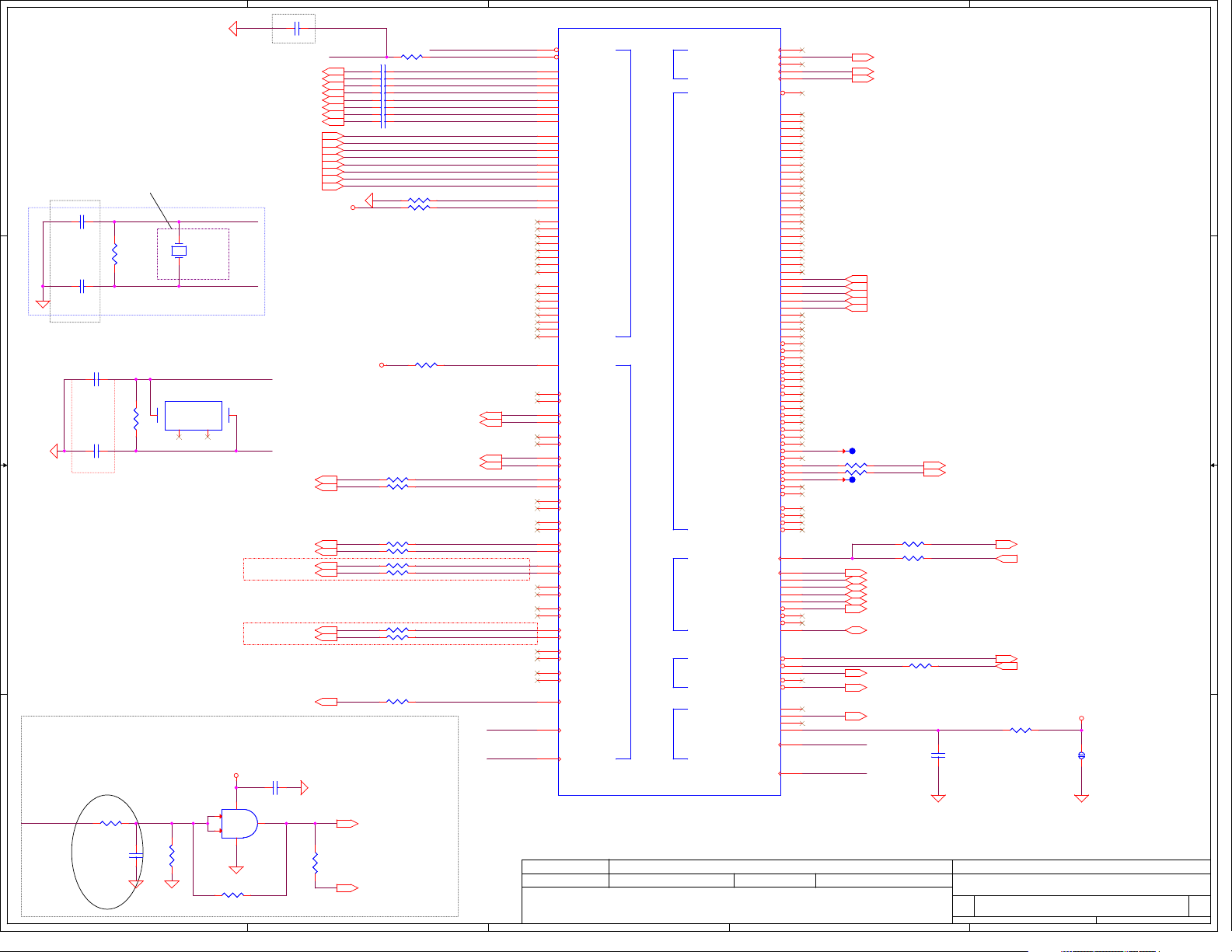

5

4

3

2

1

Panel PWM

D D

C C

SIT, NO.4

HPD

DP_INT_PWM7

1 2

R66 2.2K_0402_5%R66 2.2K_0402_5%

12

R67

R67

4.7K_0402_5%

4.7K_0402_5%

+3VS

R62

R62

47K_0402_5%

47K_0402_5%

2

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

G

G

12

R63

R63

4.7K_0402_5%

4.7K_0402_5%

13

D

D

Q6

Q6

2N7002K_SOT23-3

2N7002K_SOT23-3

S

S

APU_INVT_PWM 25

12

C

C

Q8

Q8

2

B

B

E

E

3 1

B B

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/04/18 2015/07/08

2011/04/18 2015/07/08

2011/04/18 2015/07/08

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

FS1r2 Signal Level Shifter

FS1r2 Signal Level Shifter

FS1r2 Signal Level Shifter

LA-8121P

LA-8121P

LA-8121P

9 50Monday, January 16, 2012

9 50Monday, January 16, 2012

9 50Monday, January 16, 2012

1

0.4

0.4

0.4

A

B

C

D

E

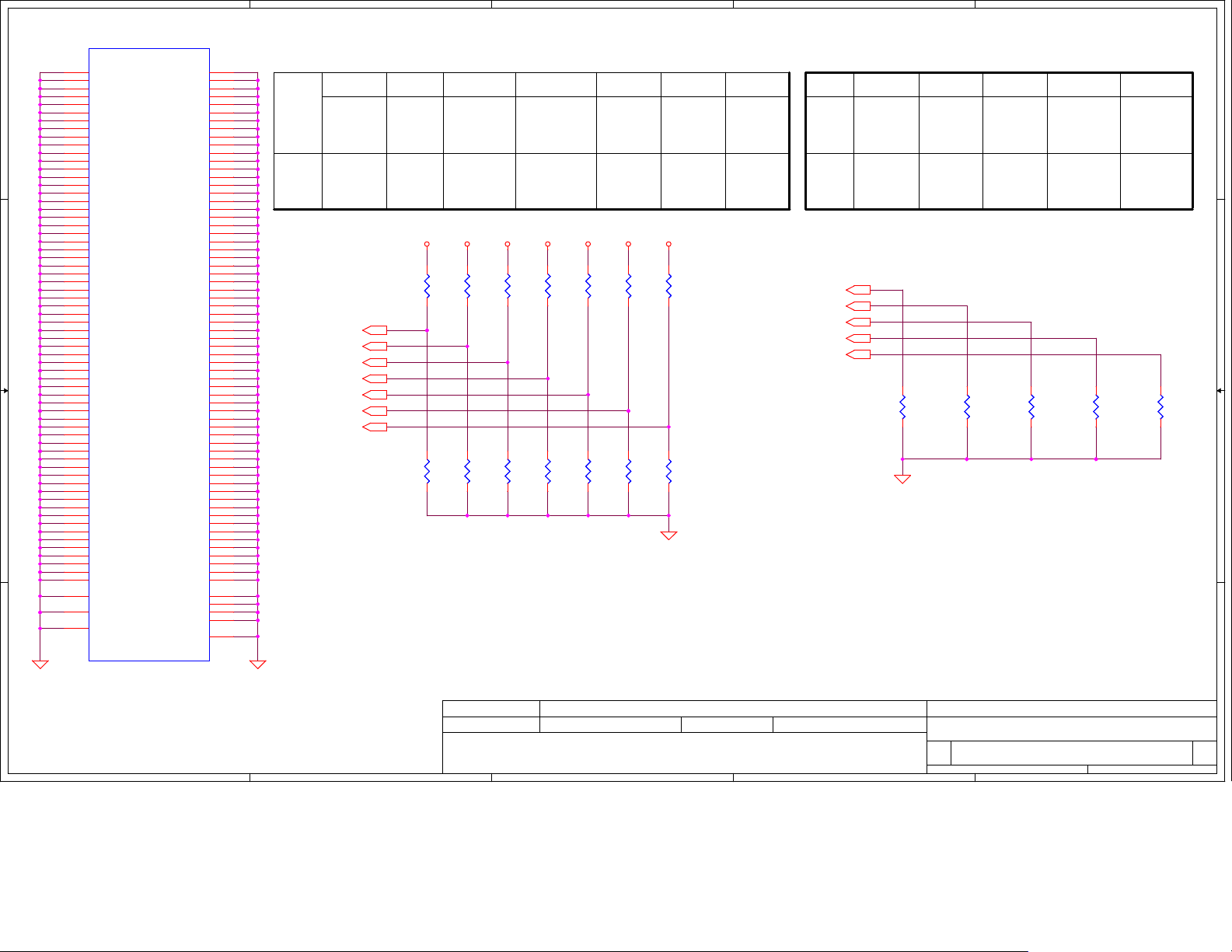

+VREF_DQ

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDM0

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ8

C2011

C2011

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDRA_SDQ9

DDRA_SDQS1#

DDRA_SDQS1

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQS2#

DDRA_SDQS2

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDM3

DDRA_SDQ26

DDRA_SDQ27

DDRA_CKE0

DDRA_SBS2#

DDRA_SMA12

DDRA_SMA9

DDRA_SMA8

DDRA_SMA5

DDRA_SMA3

DDRA_SMA1

DDRA_CLK0

DDRA_CLK0#

DDRA_SMA10

DDRA_SBS0#

DDRA_SWE#

DDRA_SCAS#

DDRA_SMA13

DDRA_SCS1#

DDRA_SDQ32

DDRA_SDQ33