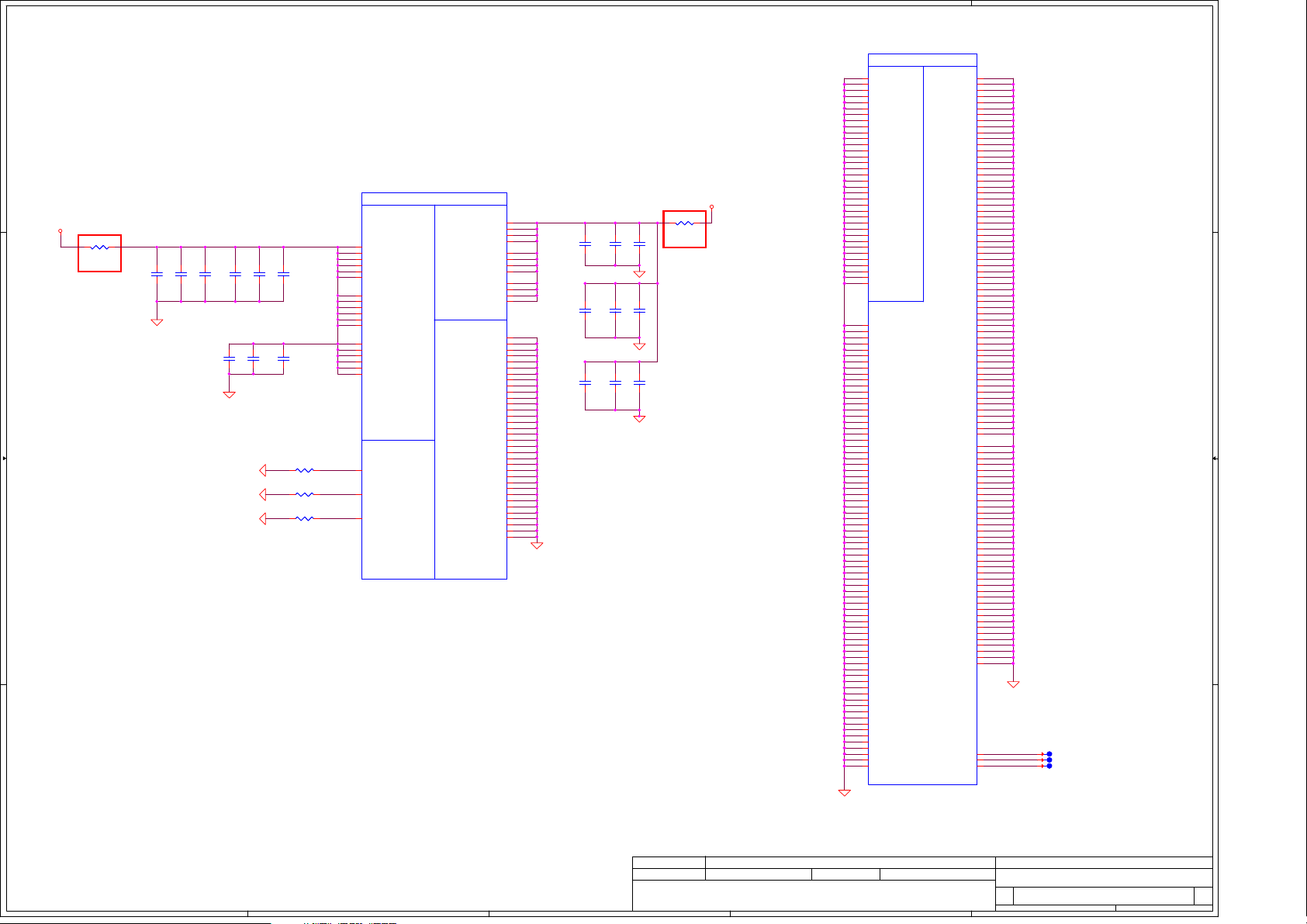

Compal LA-8712P QCL51 AMD, ENVY M6 Schematic

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

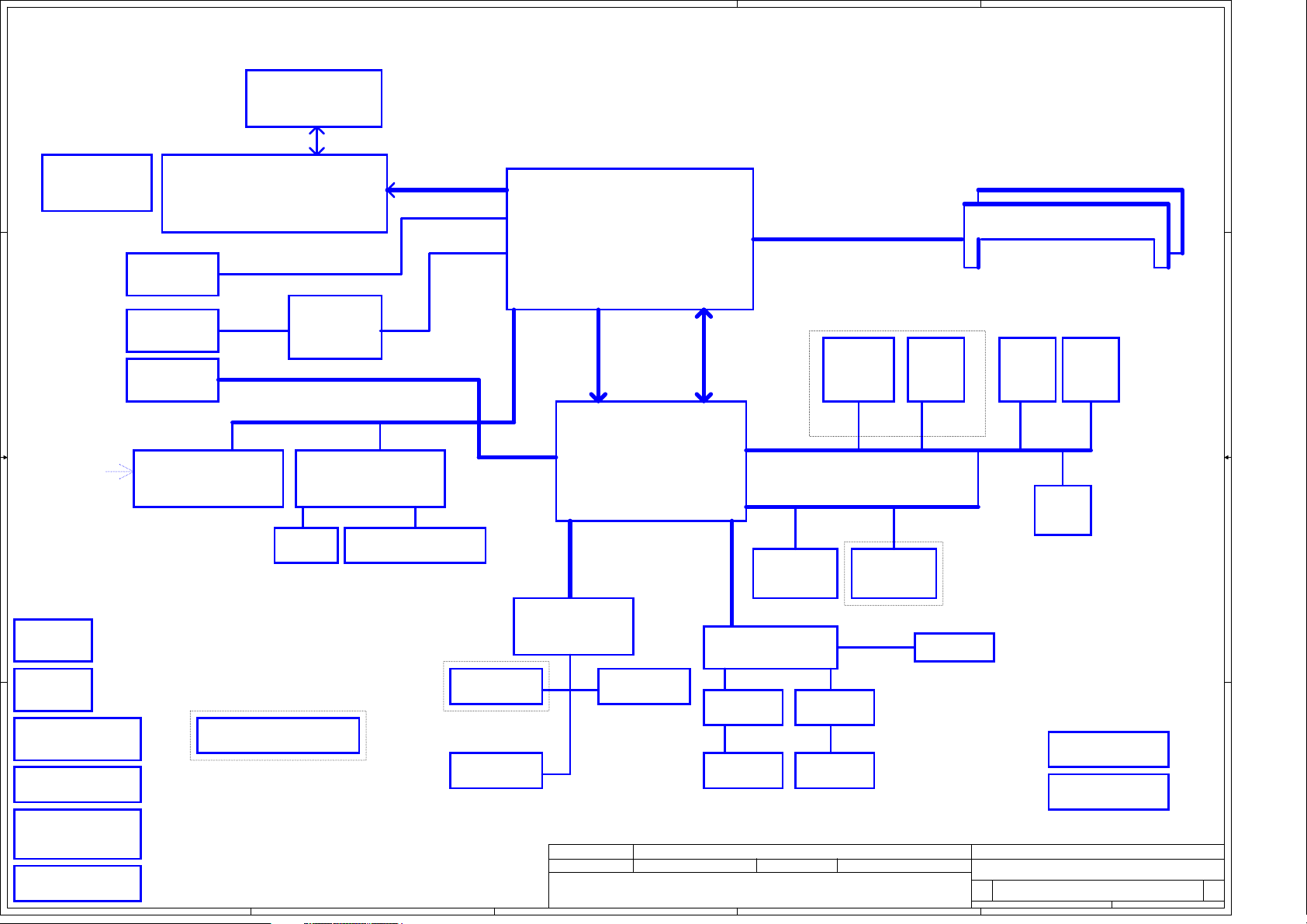

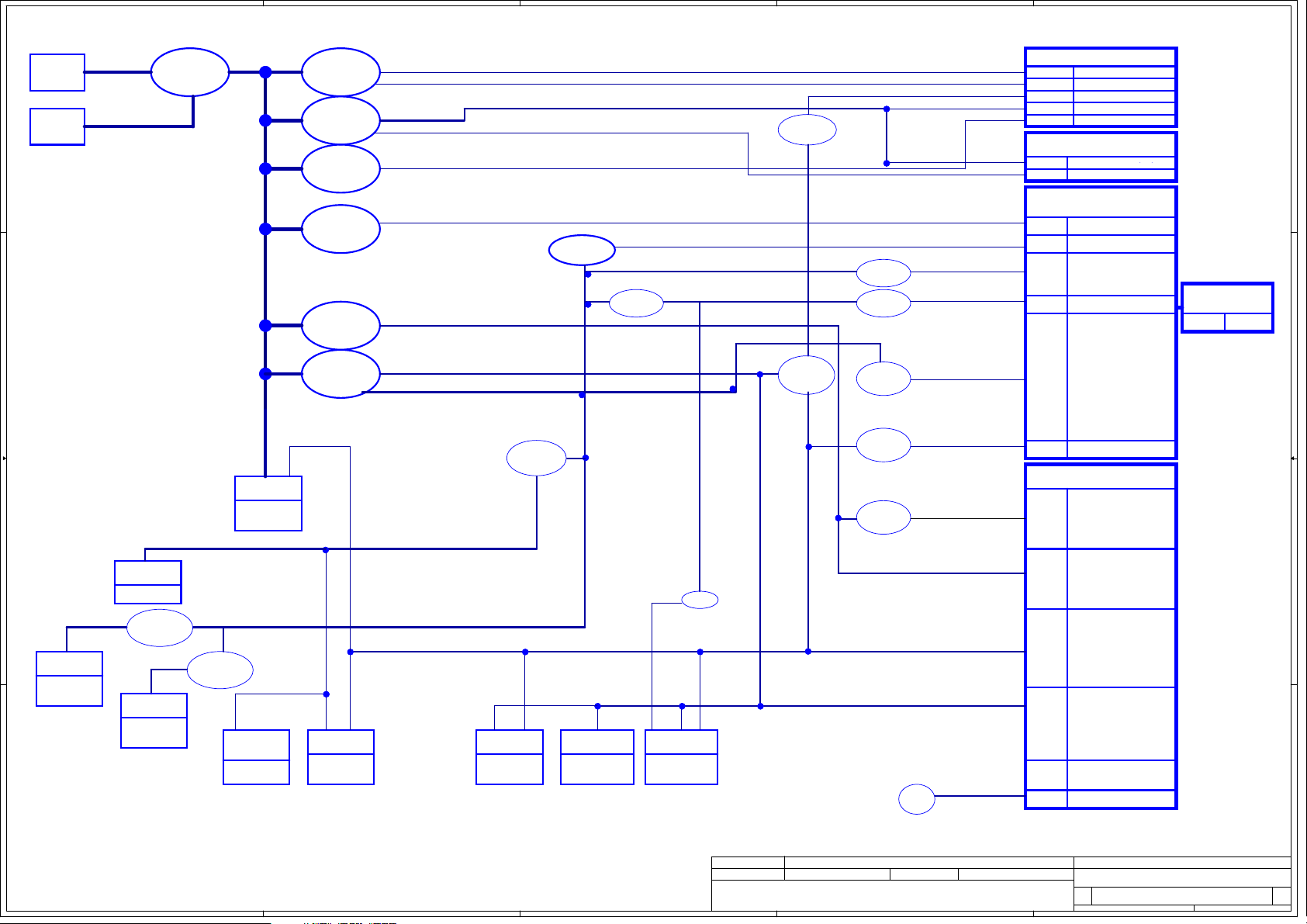

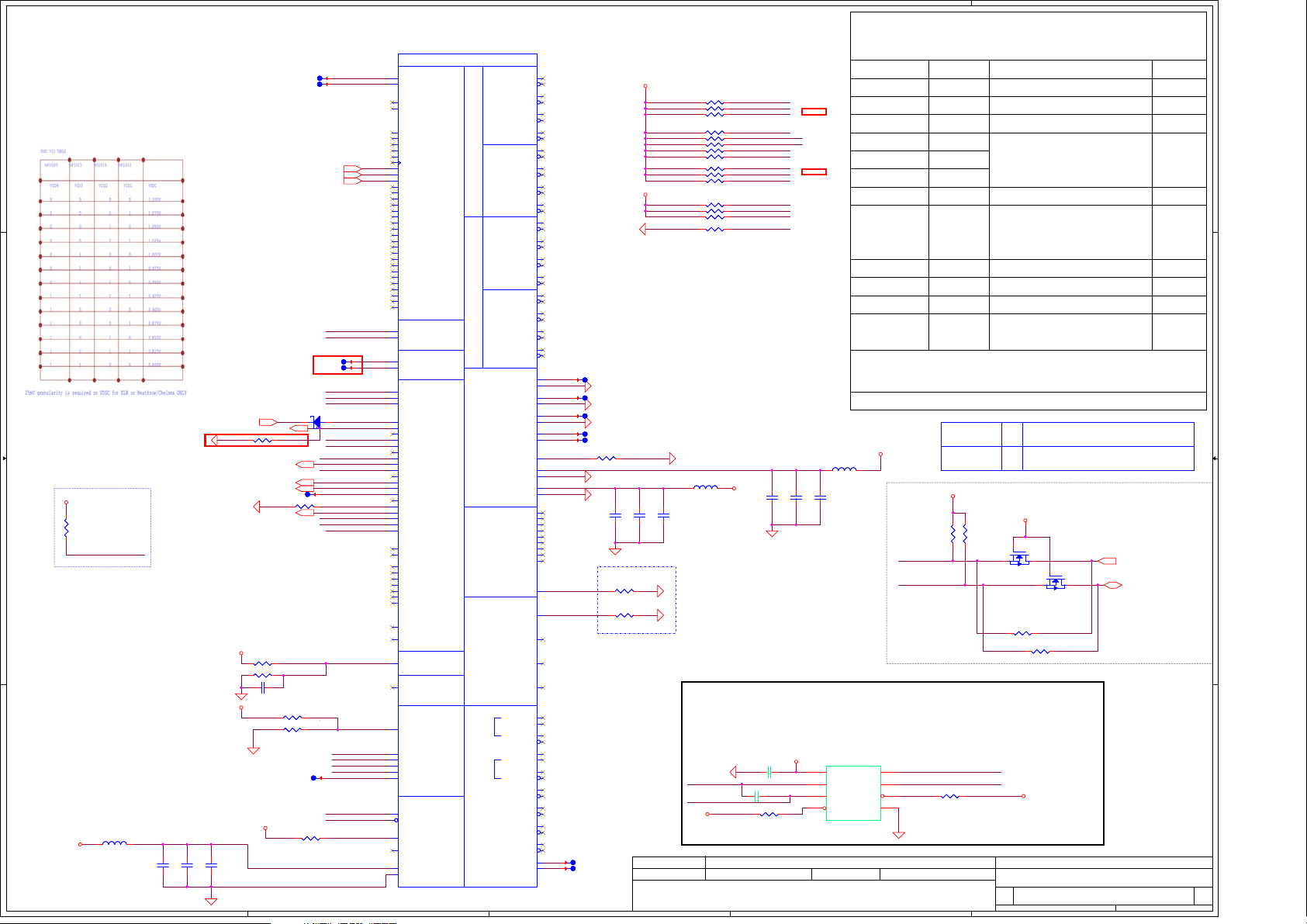

AMD Trinity APU / Hudson FCH / ATI Chelsea Pro M2

QCL51 Schematics Document

LA-8712P REV: 0.1

Compal Confidential

AMD Comal Platform

Muxless/UMA / PX 4.0 / PX 5.0

2011-10-26

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

Cover Page

B

1 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

Cover Page

B

1 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

Cover Page

B

1 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

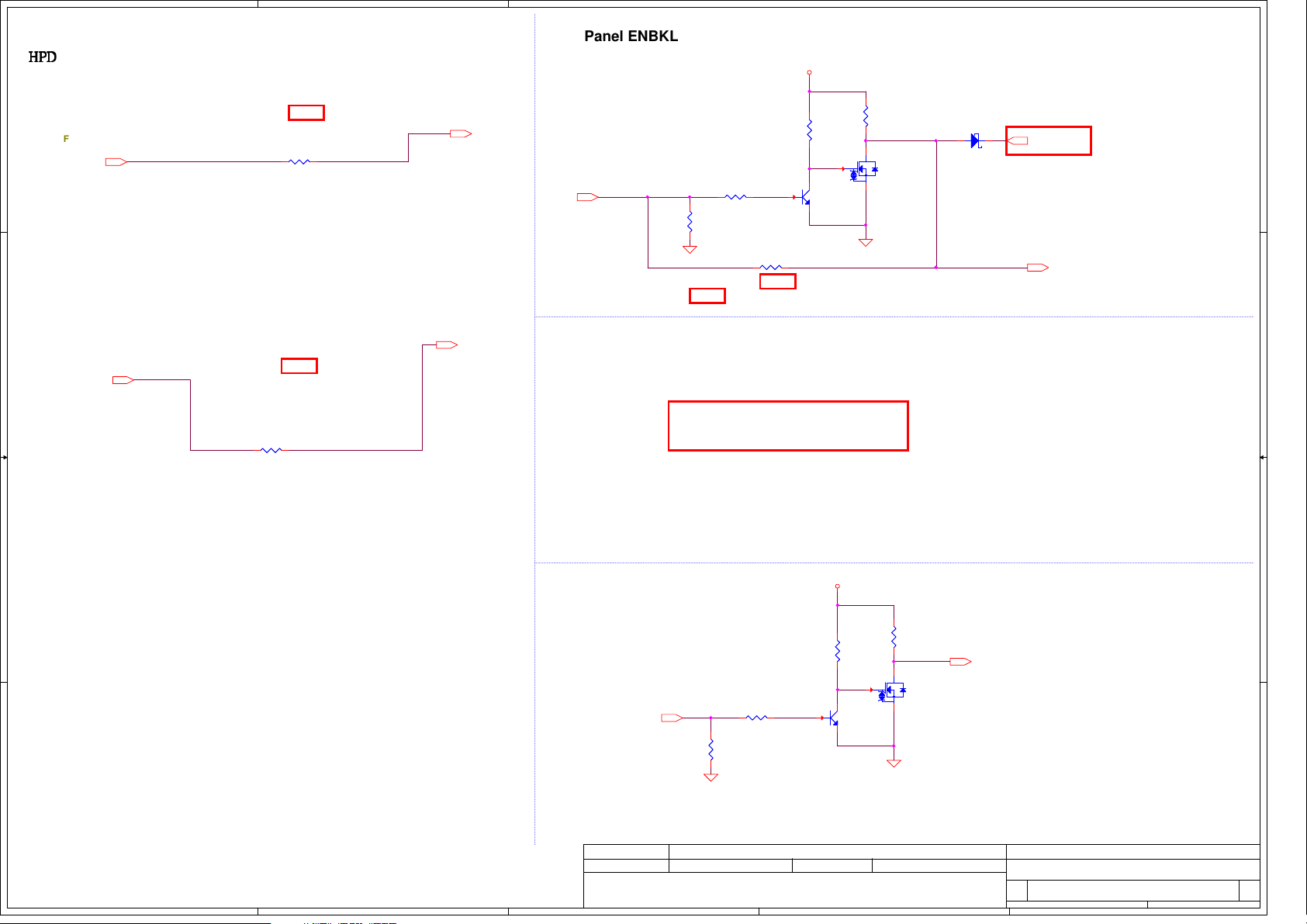

LPC BUS

Compal Confidential

USB20

Sub/B*1

USB Charger

HD Audio

FCH

Page 25~29

Model Name : QCL51 AMD

SATA

page 30

port 0

CMOS

Camera

Port 0

USB

SATA ODD

page 30

port 1

page 40 page 22

uFCBGA-656

AMD Comal

AMD FS1R2 APU

uPGA-722 Package

Page 6~10

Trinity

Hudson-M3

Dual Channel

BANK 0, 1, 2, 3

204pin DDRIII-SO-DIMM X2

1.5V DDRIII 1333/1600MHz

Memory BUS(DDR3/DDR3L)

Page 11,12

page 23

Gen2GFX x 16

64M x16

128M x 16

VRAM DDR3

DDR3

page 19, 20

uFCBGA-962

ATI Chelsea Pro M2

page 14

Thermal Sensor

ADM1032

DP2

APU HDMI

(UMA / Muxless)

HDMI Conn.

LVDS Conn.

DP0

DP1

LVDS

Translator

ANX3112

page 21

DP x 4

(DP1 TXP/N 0~4)

UMI

MINI Card 1

(Wireless LAN with BT)

page 32

GPP0GPP1

Transformer / RJ45

page 31

SATA HDD

P_GPP x 3

GEN1

Page 13~18

Touch Pad Int.KBD

page 37

page 38page 39

ENE

KBC932

Port 5

USB 2.0 Port 8

page 41

USB30

M/B*2

page 33

HDA Codec

IDT 92HD91

USB 2.0 Port 10,11

page 39

LED

RTC CKT.

page 25

Fan Control

page 30

DC/DC

Interface CKT.

page 42

Power On/Off CKT.

page 38

Power Circuit

page 38

Power/B with LED

page 22

ML for FCH VGA

Card Reader/Gbe Lan

Realtek RTL8411

page 31

Gen2 3Gb/sGen3 6Gb/s

SD slot

page 31

FAN/LED

page 39

Sub Woofer

Amp

Sub Woofer

SPK

HP Amp

Combo

jack

CRT Conn.

page 24

page 34page 35

page 34

page 36

page 36

USB 3.0 Port 0,1

page 40

USB30

Sub*1

Repeater

USB 3.0 Port 2

USB 2.0 Port 12

page 38

EC BIOS (256K)

page 26

SYS BIOS (4M)

BIOS ROM

Daughter board

1 CH

1 CH

page 39

FP

Port 1

Daughter board

Daughter board

Daughter board

page 44~56

Board Name : LA-8712P

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

Block Diagrams

B

2 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

Block Diagrams

B

2 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

Block Diagrams

B

2 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

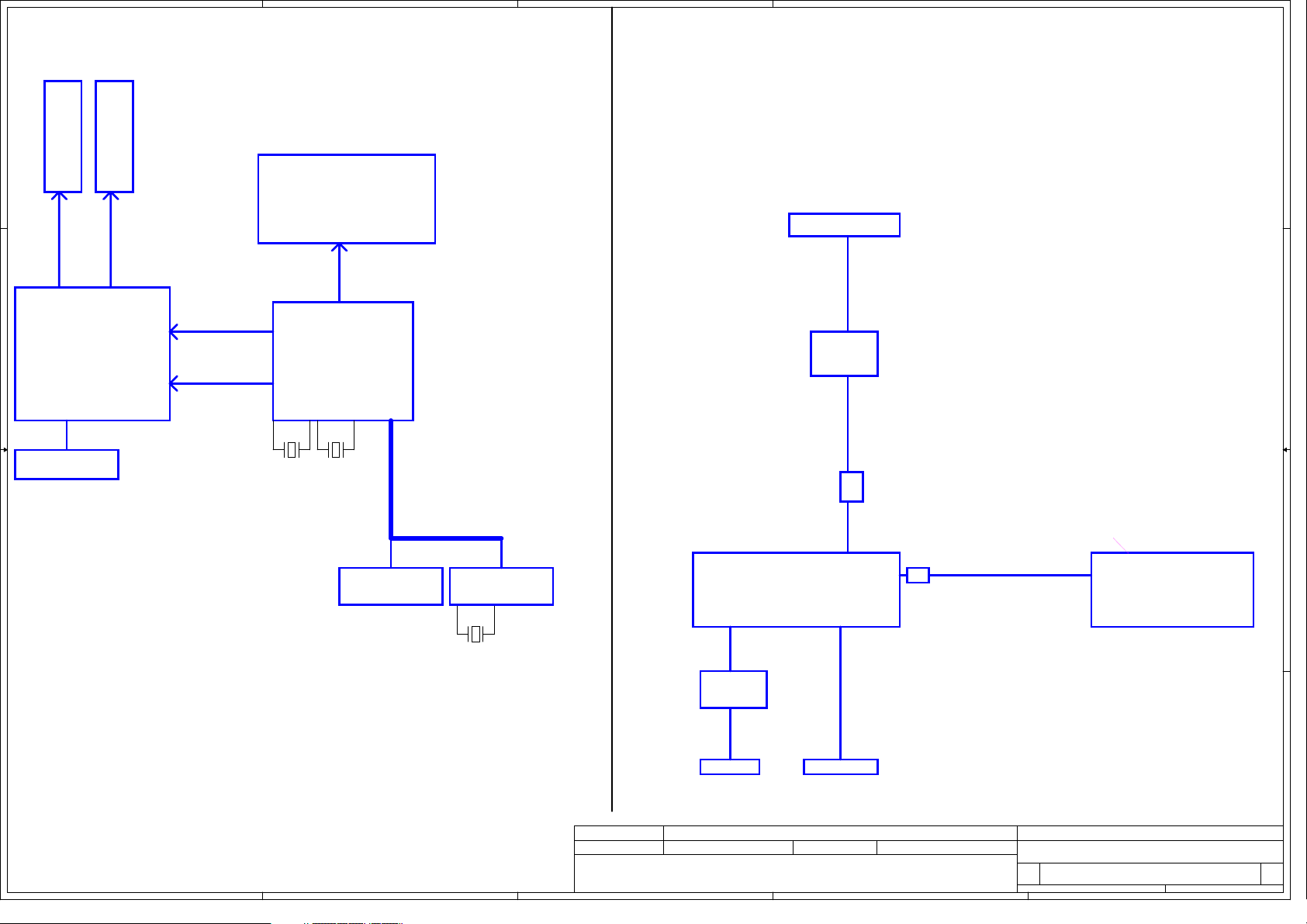

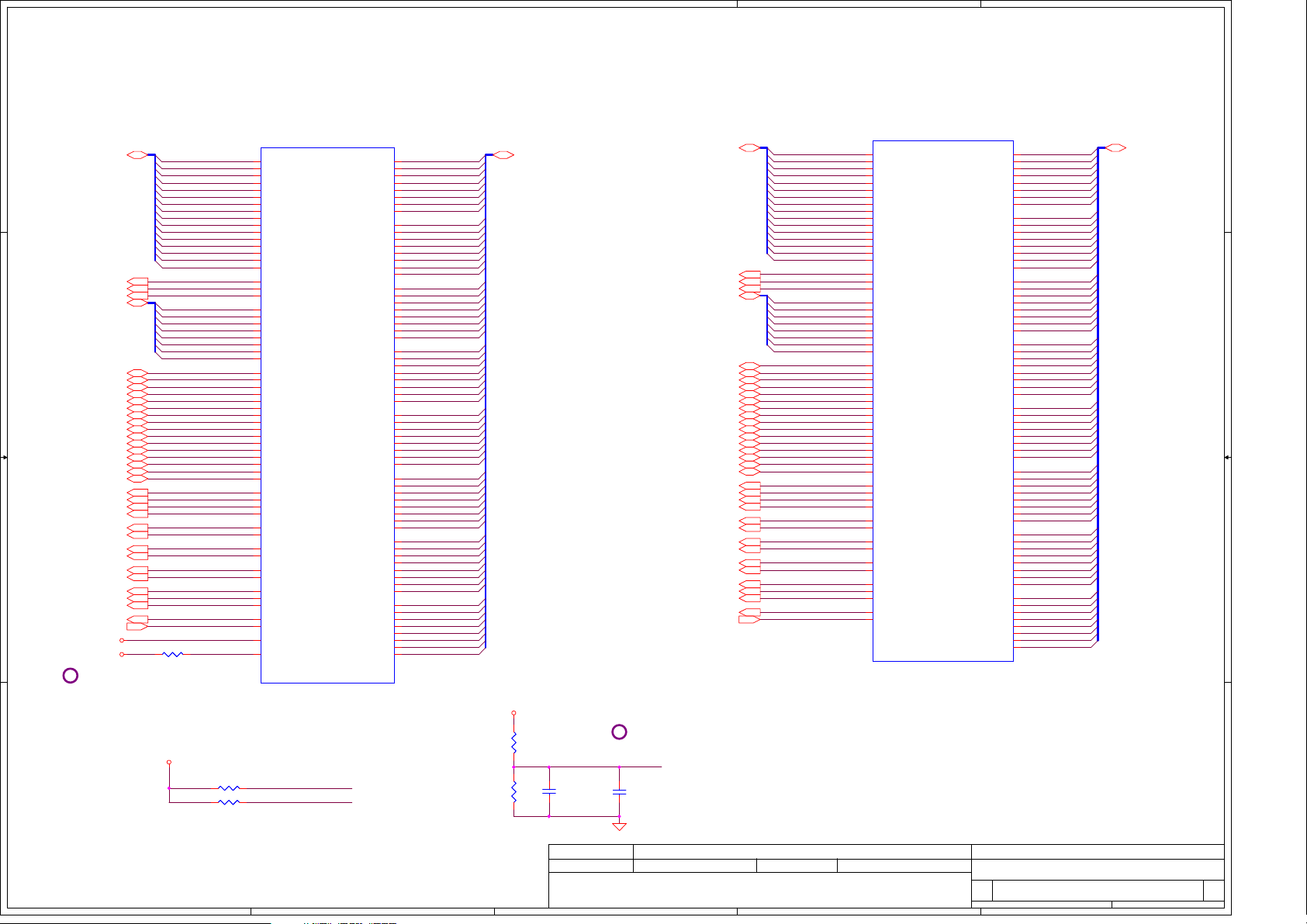

DP0

APU

DP0_TXP/N0

DP0_AUXP/N

C

RTD2132

LVDS_OUT

DP_IN

APU_TXOUT[0:2]+/-

APU_TXOUT_CLK+/-

APU_LVDS_CLK/DATA

C

VGA

DPFDPE

AMD

Chelsea Pro

ATI VGA

HDMI CONN

PCIE_GFX[0:15]

CRT CONN

PCIE_GFX[0:15]

DP1 DPA

FCH

DAC1

DISPLAY OUTPUT

CLOCK DISTRIBUTION

A_SODIMM

CPU FS1 SOCKET

FCH

Hudson-M2/M3

Internal CLK GEN

100MHz

APU_DISP_CLKP/N

100MHz

APU_CLKP/N

GbE LAN/

Card reader

25MHz

GPP_CLK

WLAN

Mini PCI Socket

GPP2 GPP3

DP0_AUX

LVDS Transtator

B_SODIMM

1066~1866MHz

DDRA_CLK1P/N

1066~1866MHz

AMD

AMD

100MHz

CLK_PEG_VGAP/N

100MHz

32.768KHz 25MHz

LVDS CONN

DP2

X1X5

DDRA_CLK0P/N

DDRB_CLK0P/N

DDRB_CLK1P/N

YL1

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONS ENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

CLOCK / DISPLAY DISTRIBUTION

Custom

3 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONS ENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

CLOCK / DISPLAY DISTRIBUTION

Custom

3 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONS ENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

CLOCK / DISPLAY DISTRIBUTION

Custom

3 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

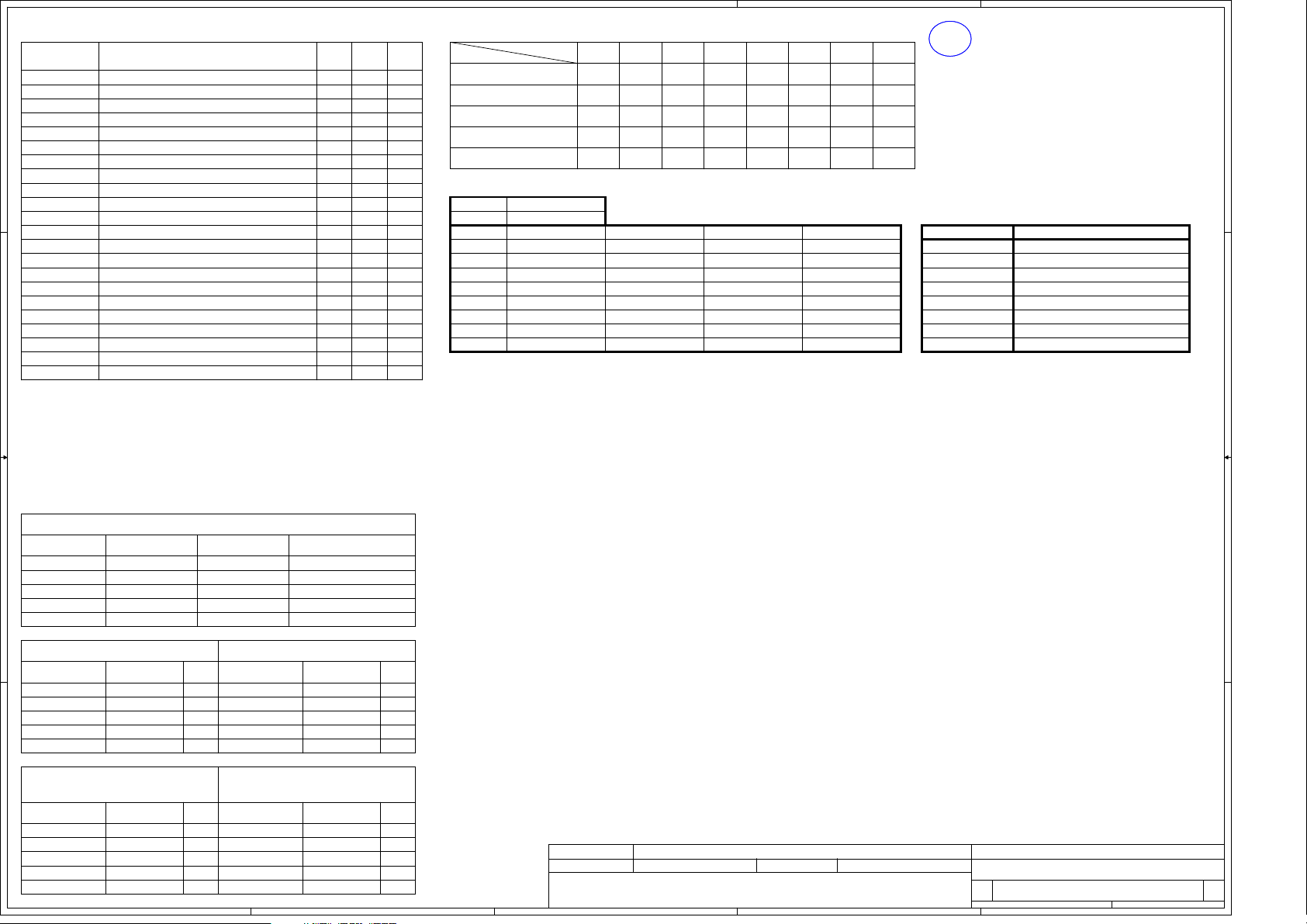

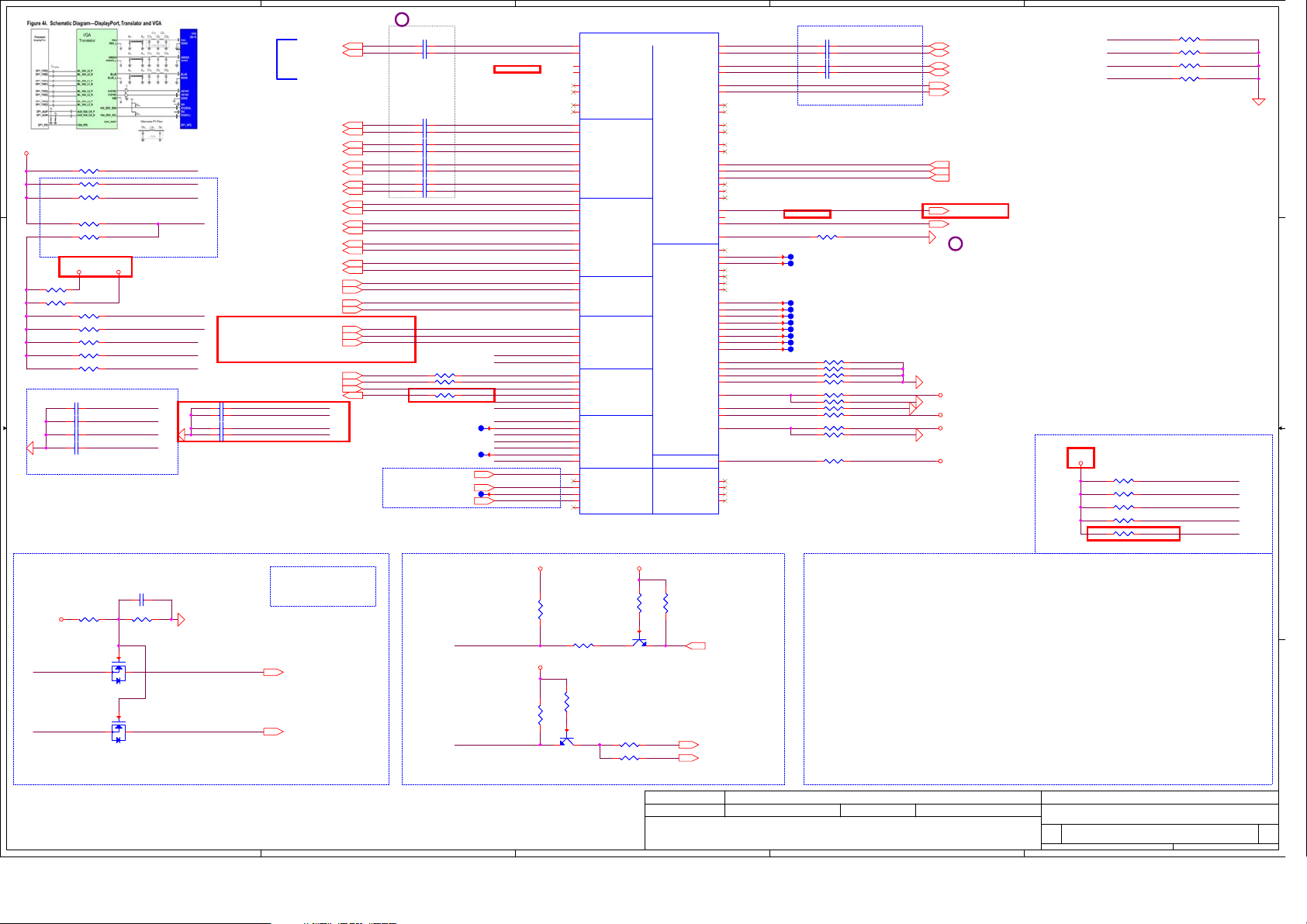

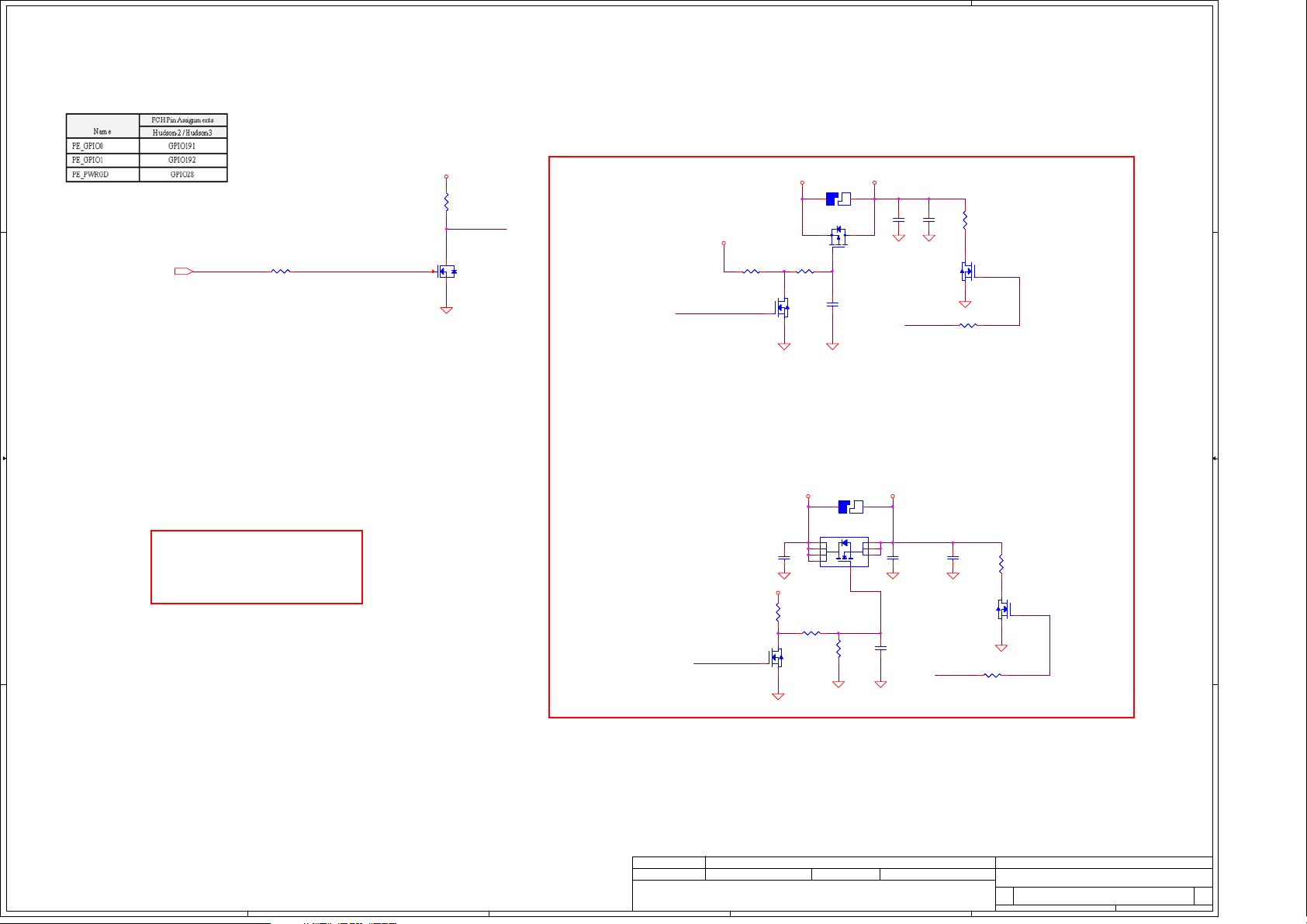

FCH (S0~S5)

SM Bus 1 address

DDR DIMM1

1010 000X b

DDR DIMM2

1010 001X b

FCH (S0)

SM Bus 0 address

Device Address Device Address

HEX

A0

A2

HEX

Device Address HEX

EC SM Bus1 address EC SM Bus2 address

Smart Battery

0001 011X b

16H

Device IDSEL# REQ#/GNT# Interrupts

External PCI Devices

+APU_CORE_NB ON OFF OFFVoltage for On-die VGA of APU

+APU_CORE

Voltage Rails

VIN

B+

S1 S3 S5

ON OFF

N/A N/A N/A

N/AN/AN/A

Power Plane Description

OFF

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

+VGA_CORE OFFOFFON0.95-1.2V switched power rail

+0.75VS ONON OFF0.75V switched power rail for DDR terminator

+0.935VGS ON OFF OFF0.935V switched power rail for VGA

STATE

LOW

LOW

LOW

SIGNAL

Full ON

S1(Power On Suspend)

LOW

LOW LOW

LOW

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF) LOW

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

Vcc 3.3V +/- 5%

100K +/- 5%Ra/Rb

Board ID

Ra / Rb V min

0

1

2

3

0

8.2K +/- 5%

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

0.503 V

0.819 V

0.538 V

0.875 V

AD_BID

V typ

AD_BID

V

AD_BID

max

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

3.300 V

0 V 0 V

4

5

6

7 NC

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

2.341 V

1.185 V 1.264 V

Board ID / SKU ID Table for AD channel

ON

ON

ON

ON

ON

ON

ON ON

ON

ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

LOW

LOW

LOW

HIGH HIGH HIGH HIGH

HIGHHIGHHIGH

HIGH

HIGH

HIGH

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

+RTCVCC

+2.5VS

+5VS

+3VS

+5VALW

+3VALW

+VSB ON ON*

ONON

ON

ON

ON ON*

+LAN_VDD_3V3 ON ON ON

ON

OFF

OFF

OFF

ON

OFFON

ON

ON

OFF

ON*

OFF

ON

RTC power

2.5V for CPU_VDDA

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

VSB always on power rail

3.3V power rail for LAN

+1.8VGS OFFON OFF1.8V switched power rail

+1.5V_PCIE

+1.5V ON

OFF

OFF

ON OFF

ON

1.5V switched power rail

1.5V power rail for CPU VDDIO and DDR

+1.1VS

+1.2VS ON OFF OFF

ON OFF OFF1.1V switched power rail for FCH

1.2V switched power rail for APU

+1.1ALW 1.1V switched power rail for FCH ON ON*ON

2

3

4

5

6

7

PCB Revision

BOARD ID Table

Board ID

0

1

Device Address HEX

ADI ADM1032 (GPU)

1001 101X b

9AH

PX@ PX function

BOM Option Table

x = 1 is read cmd, x= 0 is writee cmd.

DB

SB-TSI (APU)

1001 100X b

98H

BOM

Structure

Description

BOM Config

UMA PX

+VDDCI OFF0.95-1.2V switched power rail ON OFF

VGA Internal Thermal

1000 001X b

82H

V

Amplifier

Touch pad

LVDS TR

1010 100X b

A8H

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

Notes List

B

4 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

Notes List

B

4 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

Notes List

B

4 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

ZZZ1

PCB

Part Number = DA80000SH00

PCB 0OH LA-8712P REV0 M/B

ZZZ1

PCB

Part Number = DA80000SH00

PCB 0OH LA-8712P REV0 M/B

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

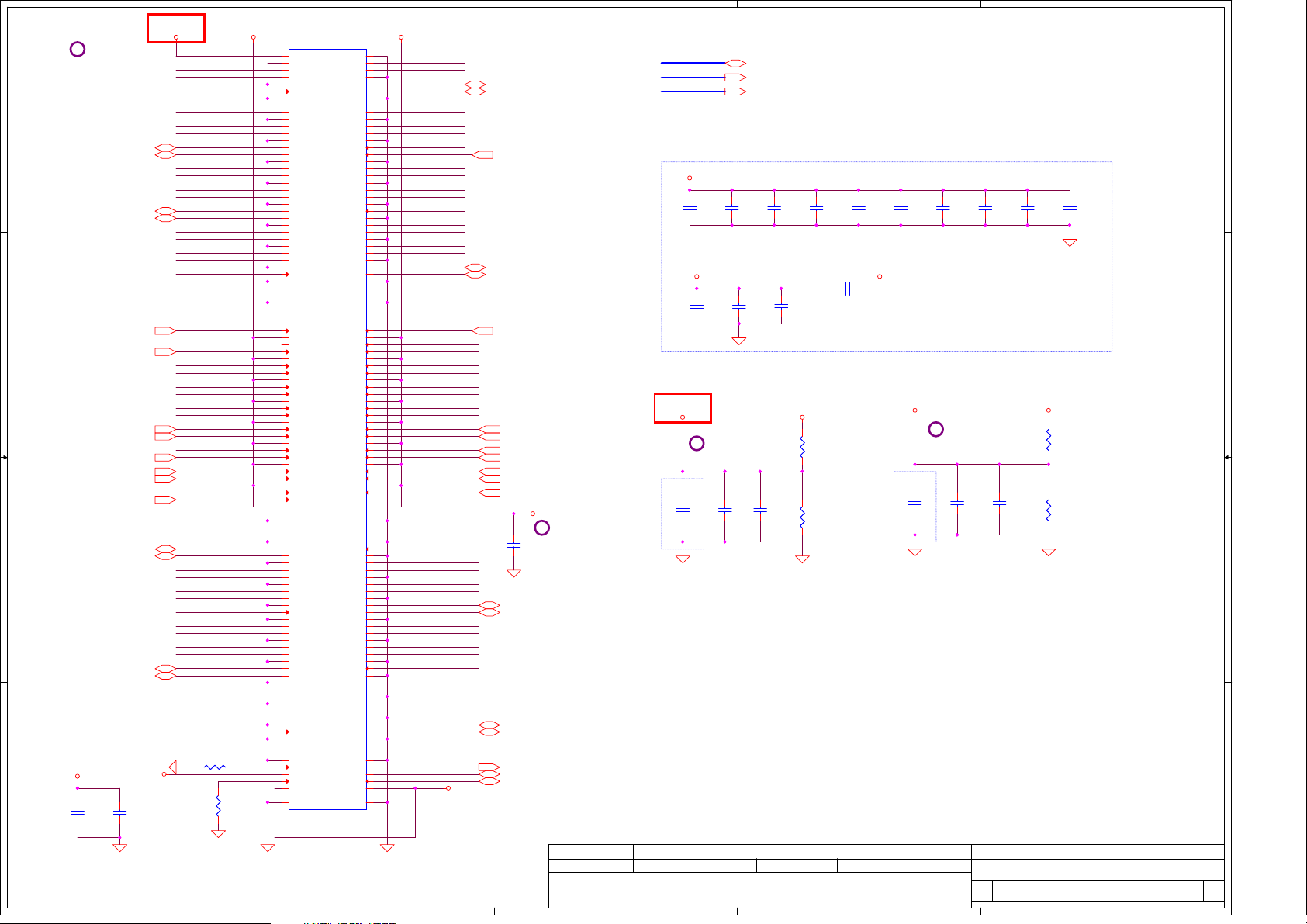

EC

ENE KB932

+1.5V

+0.75VS

+1.5VS 500mA

+3.3VS 1A

+3.3VALW 330mA

+3.3VS 3mA

+3.3VALW 30mA

SATA

HDD*1

ODD*1

+5V 45mA

+3.3VS 25mA

+3.3VALW 201mA

+5V 3A

BATTERY

12.6V

PU101

CHARGER

BQ24738ARGRR

AC ADAPTOR

19V 90W

LAN /Card reader

RTL8411

RAM DDRIII SODIMMX2

VDD_MEM 4A

Audio Codec

IDT 92HD91

RTC

Bettary

VTT_MEM 0.5A

Mini Card

WLAN

BATT+

V

IN

VDD CORE 60A

VDDNB 44A

VDDIO 3.2A

VDDR 8.5A

VDDA 0.5A

AMD APU FS1R2

0.7~1.475V

+2.5VS

+1.5V

+1.2VS

FCH AMD Hudson M3

VDDIO_33_PCIGP: 102 mA

VDDPL_33_SYS: 47 mA

VDDPL_33_DAC: 20 mA

VDDPL_33_ML: 12 mA

VDDAN_33_DAC: 30 mA

VDDPL_33_PCIE: 11 mA

VDDPL_33_SATA: 12 mA

VDDPL_33_USB_S: 14 mA

VDDPL_33_SSUSB_S: 11 mA

VDDIO_AZ_S: 26 mA

VDDAN_33_USB_S: 470 mA

VDDIO_33_S: 59 mA

VDDXL_33_S: 5 mA

VDDAN_33_HWM_S: 12 mA

VDDIO_GEB_S: 145mA

VDDIO_33_GBE_S: 2mA

VDDIO_33_GBE_S

VDDCR_11_GBE_S

VDDIO_GBE_S

VDDPL_11_DAC: 7 mA

VDDAN_11_ML: 226 mA

VDDCR_11: 1007 mA

VDDAN_11_CLK: 340 mA

VDDAN_11_PCIE: 1088 mA

VDDAN_11_SATA: 1337 mA

VDDAN_11_USB_S: 140 mA

VDDCR_11_USB_S: 42 mA

VDDAN_11_SSUSB_S: 282 mA

VDDCR_11_SSUSB_S: 424 mA

VDDCR_11_S: 187 mA

VDDPL_11_SYS: 70 mA

VDDCR_11_GBE_S:63mA

+1.1VALW

+1.1VS

+3VALW

+3VS

GND

VDDBT_RTC_GRTC BAT

VGA ATI

Chelsea Pro

PLL_PVDD: 75 mA

TSVDD: 5 mA

AVDD: 70 mA

VDD1DI: 45 mA

VDD_CT: 17mA

PCIE_VDDR: 440 mA

DP[A:F]_VDD18: 990 mA

SPV18: 50mA

MPV18: 150mA

VDDCI 4.6A

DPLL_VDDC: 125 mA

SPV10: 100 mA

PCIE_VDDC: 1100 mA

DP[A:E]_VDD10: 880 mA

VDDC 28A

VDDR3: 60 mA

+0.935VGS

+3VGS

0.85~1.1V

+1.5VGS

+1.8VGS

B+

+APU_CORE

+APU_CORE_NB

+5VALW

+3VALW

+USB3_VCCA

U61

TPS2540RTER

+APU_CORE

+APU_CORE_NB

0.9~1.0V

VDDR1: 1200 mA

VRAM 512/1GB/2GB

64M / 128Mx16 * 4 / 8

+1.5VGS 2.4 A

0.7~1.475V

+1.8VGS

+0.935VGS

PU2000

ISL6277HRTZ-T

+1.5V

PU501

RT8207MZQW

PU701

RT8237EZQW

+1.2VS

+1.2VS

+1.5V

PU900

ADP3211MNR2G

+VGA_CORE

+VGA_CORE

+VDDCI

+VDDCI

PU935

SY8809DFC

PU401

SY8033BDBC

+1.8VGS

PU702

APL5508

+2.5VS

PU301

RT8205LZQW

+1.1VALW

PU801

SY8809DFC

UV19

AO4430L

+1.5VGS

+0.75VS

U39

AO4430L

+1.1VS

+1.1VS

+1.1VALW

U40

SI4800

+3VALW

+3VS

JUMP @

+3VSG

+3VSG

+3.3 350mA

B+ 300mA

LCD panel

15.6"

+INVPWR_B+

+5V

Dual+1

2.5A

USB3.0 X2

RM13

+1.5VS_WLAN

+3VALW

+3VS

+5VS

+5VALW

+3VS

+5VS

U38

SI4800

FAN Control

APL5607

+5VS 500mA

+3VS

+0.75VS

PU1000

SY8033BDBC

+1.5V

+2.5VS

PU1501

SY8036DBC

+1.5V_PCIE

QV16

AP2301GN

U54

AP2301MPG

USB3.0 X1

USB2.0 X1

+5V

Dual+1

2.5A

+USB_BS

+0.935VGS

+1.5VGS

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

POWER DELIVERY CHART

Custom

5 56Monday, November 28, 2011

2011/07/08 2015/07/08

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

POWER DELIVERY CHART

Custom

5 56Monday, November 28, 2011

2011/07/08 2015/07/08

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

POWER DELIVERY CHART

Custom

5 56Monday, November 28, 2011

2011/07/08 2015/07/08

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

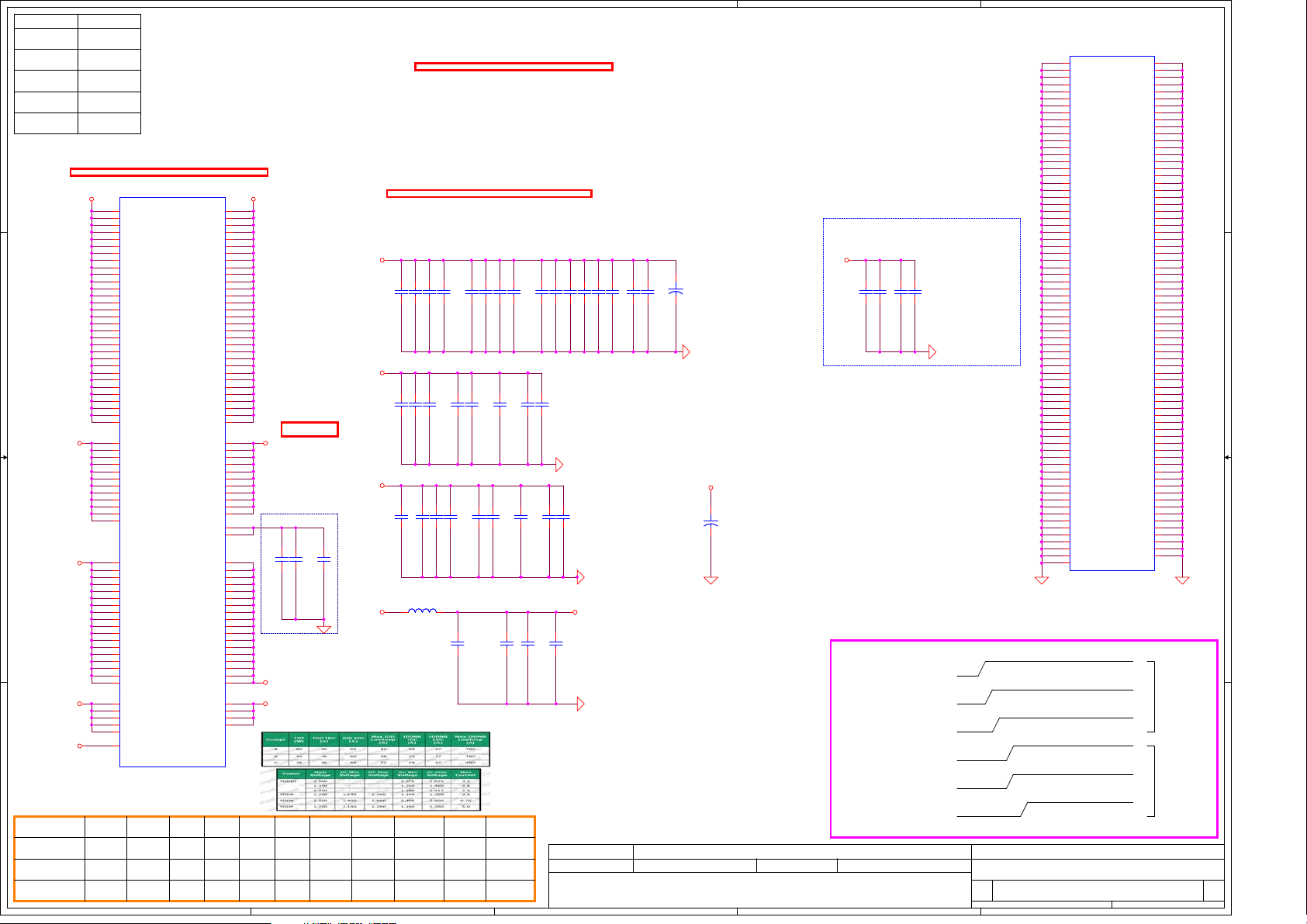

GLAN/Card reader

WLAN

GPU

UMI

GPU

GLAN/Card reader

WLAN

UMI

P_ZVSS W/S=8/12 mil, <3000mil

L

P_ZVDDP W/S=8/12 mil, <3000mil

L

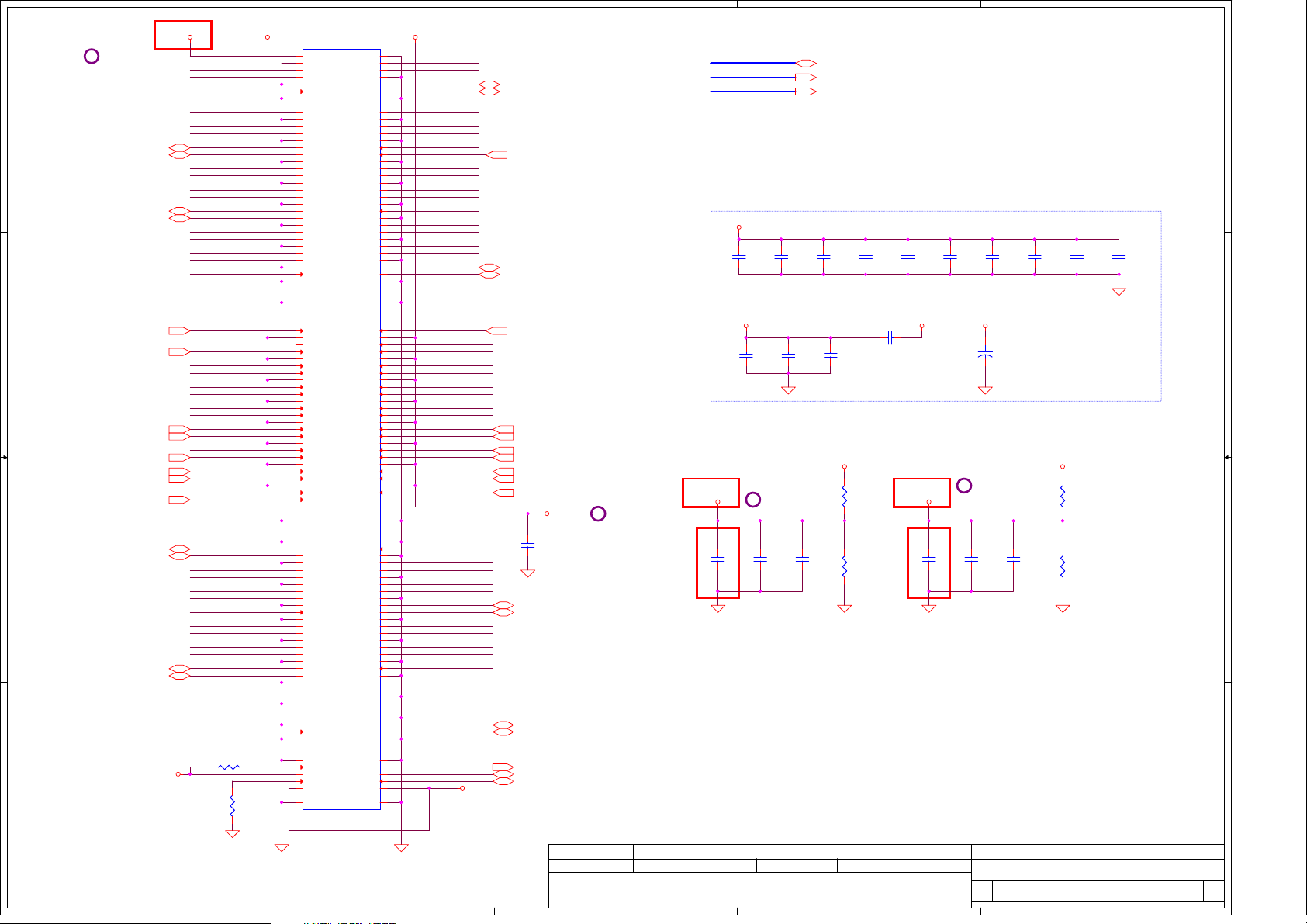

PCIE_GTX_C_FRX_P0

PCIE_GTX_C_FRX_N0

PCIE_GTX_C_FRX_P1

PCIE_GTX_C_FRX_N1

PCIE_GTX_C_FRX_P2

PCIE_GTX_C_FRX_P5

PCIE_FTX_GRX_P2

PCIE_FTX_GRX_P3

PCIE_FTX_C_GRX_P2

PCIE_FTX_C_GRX_P3

PCIE_GTX_C_FRX_N2

PCIE_GTX_C_FRX_P3

PCIE_GTX_C_FRX_N3

PCIE_GTX_C_FRX_P4

PCIE_GTX_C_FRX_N4

PCIE_GTX_C_FRX_N5

PCIE_GTX_C_FRX_P6

PCIE_GTX_C_FRX_N6

PCIE_GTX_C_FRX_P7

PCIE_GTX_C_FRX_N7

PCIE_GTX_C_FRX_P8

PCIE_GTX_C_FRX_N8

PCIE_GTX_C_FRX_P9

PCIE_GTX_C_FRX_N9

PCIE_GTX_C_FRX_P10

PCIE_GTX_C_FRX_N10

PCIE_GTX_C_FRX_P11

PCIE_GTX_C_FRX_N11

PCIE_GTX_C_FRX_P12

PCIE_GTX_C_FRX_N12

PCIE_GTX_C_FRX_P13

PCIE_GTX_C_FRX_N13

PCIE_GTX_C_FRX_P14

PCIE_GTX_C_FRX_N14

PCIE_GTX_C_FRX_P15

PCIE_GTX_C_FRX_N15

P_ZVDDP

PCIE_FTX_GRX_P0 PCIE_FTX_C_GRX_P0

PCIE_FTX_GRX_N0 PCIE_FTX_C_GRX_N0

PCIE_FTX_GRX_P1 PCIE_FTX_C_GRX_P1

PCIE_FTX_GRX_N1 PCIE_FTX_C_GRX_N1

PCIE_FTX_GRX_N2 PCIE_FTX_C_GRX_N2

PCIE_FTX_GRX_N3 PCIE_FTX_C_GRX_N3

PCIE_FTX_GRX_P4 PCIE_FTX_C_GRX_P4

PCIE_FTX_GRX_N4 PCIE_FTX_C_GRX_N4

PCIE_FTX_GRX_P5 PCIE_FTX_C_GRX_P5

PCIE_FTX_GRX_N5 PCIE_FTX_C_GRX_N5

PCIE_FTX_GRX_P6 PCIE_FTX_C_GRX_P6

PCIE_FTX_GRX_N6 PCIE_FTX_C_GRX_N6

PCIE_FTX_GRX_P7 PCIE_FTX_C_GRX_P7

PCIE_FTX_GRX_N7 PCIE_FTX_C_GRX_N7

PCIE_FTX_GRX_P8 PCIE_FTX_C_GRX_P8

PCIE_FTX_GRX_N8 PCIE_FTX_C_GRX_N8

PCIE_FTX_GRX_P9 PCIE_FTX_C_GRX_P9

PCIE_FTX_GRX_N9 PCIE_FTX_C_GRX_N9

PCIE_FTX_GRX_P10 PCIE_FTX_C_GRX_P10

PCIE_FTX_GRX_N10 PCIE_FTX_C_GRX_N10

PCIE_FTX_GRX_P11 PCIE_FTX_C_GRX_P11

PCIE_FTX_GRX_N11 PCIE_FTX_C_GRX_N11

PCIE_FTX_GRX_P12 PCIE_FTX_C_GRX_P12

PCIE_FTX_GRX_N12 PCIE_FTX_C_GRX_N12

PCIE_FTX_GRX_P13 PCIE_FTX_C_GRX_P13

PCIE_FTX_GRX_N13 PCIE_FTX_C_GRX_N13

PCIE_FTX_GRX_P14 PCIE_FTX_C_GRX_P14

PCIE_FTX_GRX_N14 PCIE_FTX_C_GRX_N14

PCIE_FTX_GRX_P15 PCIE_FTX_C_GRX_P15

PCIE_FTX_GRX_N15 PCIE_FTX_C_GRX_N15

PCIE_FTX_DRX_P0

PCIE_FTX_DRX_N0

PCIE_FTX_DRX_P1

PCIE_FTX_DRX_N1

UMI_FTX_MRX_P0

UMI_FTX_MRX_N0

UMI_FTX_MRX_P1

UMI_FTX_MRX_N1

UMI_FTX_MRX_P2

UMI_FTX_MRX_N2

UMI_FTX_MRX_P3

UMI_FTX_MRX_N3

P_ZVSS

PCIE_GTX_C_FRX_N[0..15]13

PCIE_GTX_C_FRX_P[0..15]13 PCIE_FTX_C_GRX_P[0..15] 13

PCIE_FTX_C_GRX_N[0..15] 1 3

PCIE_DTX_C_FRX_P031

PCIE_DTX_C_FRX_N031

PCIE_DTX_C_FRX_P132

PCIE_DTX_C_FRX_N132

UMI_MTX_C_FRX_P025

UMI_MTX_C_FRX_N025

UMI_MTX_C_FRX_P125

UMI_MTX_C_FRX_N125

UMI_MTX_C_FRX_P225

UMI_MTX_C_FRX_N225

UMI_MTX_C_FRX_P325

UMI_MTX_C_FRX_N325

PCIE_FTX_C_DRX_P0 31

PCIE_FTX_C_DRX_N0 31

PCIE_FTX_C_DRX_P1 32

PCIE_FTX_C_DRX_N1 32

UMI_FTX_C_MRX_P0 25

UMI_FTX_C_MRX_N0 25

UMI_FTX_C_MRX_P1 25

UMI_FTX_C_MRX_N1 25

UMI_FTX_C_MRX_P2 25

UMI_FTX_C_MRX_N2 25

UMI_FTX_C_MRX_P3 25

UMI_FTX_C_MRX_N3 25

+1.2VS

Title

Size Docum ent Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1R2 PCIE / GFX / UMI

B

6 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Docum ent Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1R2 PCIE / GFX / UMI

B

6 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Docum ent Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1R2 PCIE / GFX / UMI

B

6 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

C928 .1U_0402_16V7KPX@C928 .1U_0402_16V7KPX@

1 2

C936 .1U_0402_16V7KPX@C936 .1U_0402_16V7KPX@

1 2

C929 .1U_0402_16V7KPX@C929 .1U_0402_16V7KPX@

1 2

C938 .1U_0402_16V7KPX@C938 .1U_0402_16V7KPX@

1 2

PCI EXPRESS

GRAPHICS

GPPUMI

JCPU1A

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

PCI EXPRESS

GRAPHICS

GPPUMI

JCPU1A

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

P_GFX_RXP0

AB8

P_GFX_RXN0

AB7

P_GFX_RXP1

AA9

P_GFX_RXN1

AA8

P_GFX_RXP2

AA5

P_GFX_RXN2

AA6

P_GFX_RXP3

Y8

P_GFX_RXN3

Y7

P_GFX_RXP4

W9

P_GFX_RXN4

W8

P_GFX_RXP5

W5

P_GFX_RXN5

W6

P_GFX_RXP6

V8

P_GFX_RXN6

V7

P_GFX_RXP7

U9

P_GFX_RXN7

U8

P_GFX_RXP8

U5

P_GFX_RXN8

U6

P_GFX_RXP9

T8

P_GFX_RXN9

T7

P_GFX_RXP10

R9

P_GFX_RXN10

R8

P_GFX_RXP11

R5

P_GFX_RXN11

R6

P_GFX_RXP12

P8

P_GFX_RXN12

P7

P_GFX_RXP13

N9

P_GFX_RXN13

N8

P_GFX_RXP14

N5

P_GFX_RXN14

N6

P_GFX_RXP15

M8

P_GFX_RXN15

M7

P_GPP_RXP0

AE5

P_GPP_RXN0

AE6

P_GPP_RXP1

AD8

P_GPP_RXN1

AD7

P_GPP_RXP2

AC9

P_GPP_RXN2

AC8

P_GPP_RXP3

AC5

P_GPP_RXN3

AC6

P_UMI_RXP0

AG8

P_UMI_RXN0

AG9

P_UMI_RXP1

AG6

P_UMI_RXN1

AG5

P_UMI_RXP2

AF7

P_UMI_RXN2

AF8

P_UMI_RXP3

AE8

P_UMI_RXN3

AE9

P_ZVDDP

AG11

P_UMI_TXP0

AG2

P_UMI_TXN0

AG3

P_UMI_TXP1

AF4

P_UMI_TXN1

AF5

P_UMI_TXP2

AF1

P_UMI_TXN2

AF2

P_UMI_TXP3

AE2

P_UMI_TXN3

AE3

P_ZVSS

AH11

P_GPP_TXP0

AD5

P_GPP_TXN0

AD4

P_GPP_TXP1

AD2

P_GPP_TXN1

AD1

P_GPP_TXP2

AC3

P_GPP_TXN2

AC2

P_GPP_TXP3

AB5

P_GPP_TXN3

AB4

P_GFX_TXP0

AB2

P_GFX_TXN0

AB1

P_GFX_TXP1

AA3

P_GFX_TXN1

AA2

P_GFX_TXP2

Y5

P_GFX_TXN2

Y4

P_GFX_TXP3

Y2

P_GFX_TXN3

Y1

P_GFX_TXP4

W3

P_GFX_TXN4

W2

P_GFX_TXP5

V5

P_GFX_TXN5

V4

P_GFX_TXP6

V2

P_GFX_TXN6

V1

P_GFX_TXP7

U3

P_GFX_TXN7

U2

P_GFX_TXP8

T5

P_GFX_TXN8

T4

P_GFX_TXP9

T2

P_GFX_TXN9

T1

P_GFX_TXP10

R3

P_GFX_TXN10

R2

P_GFX_TXP11

P5

P_GFX_TXN11

P4

P_GFX_TXP12

P2

P_GFX_TXN12

P1

P_GFX_TXP13

N3

P_GFX_TXN13

N2

P_GFX_TXP14

M5

P_GFX_TXN14

M4

P_GFX_TXP15

M2

P_GFX_TXN15

M1

C943 .1U_0402_16V7KPX@C943 .1U_0402_16V7KPX@

1 2

R539 196_0402_1%R539 196_0402_1%

1 2

C931 .1U_0402_16V7KPX@C931 .1U_0402_16V7KPX@

1 2

C941 .1U_0402_16V7KPX@C941 .1U_0402_16V7KPX@

1 2

C945 .1U_0402_16V7KPX@C945 .1U_0402_16V7KPX@

1 2

C933 .1U_0402_16V7KPX@C933 .1U_0402_16V7KPX@

1 2

C922 .1U_0402_16V7KPX@C922 .1U_0402_16V7KPX@

1 2

C950 .1U_0402_16V7KC950 .1U _0402_16V7K

1 2

C925 .1U_0402_16V7KPX@C925 .1U_0402_16V7KPX@

1 2

C919 .1U_0402_16V7KPX@C919 .1U_0402_16V7KPX@

1 2

C940 .1U_0402_16V7KPX@C940 .1U_0402_16V7KPX@

1 2

C948 .1U_0402_16V7KPX@C948 .1U_0402_16V7KPX@

1 2

C942 .1U_0402_16V7KPX@C942 .1U_0402_16V7KPX@

1 2

C937 .1U_0402_16V7KPX@C937 .1U_0402_16V7KPX@

1 2

C956 .1U_0402_16V7KC956 .1U _0402_16V7K

1 2

C962 .1U_0402_16V7KC962 .1U _0402_16V7K

1 2

C959 .1U_0402_16V7KC959 .1U _0402_16V7K

1 2

C921 .1U_0402_16V7KPX@C921 .1U_0402_16V7KPX@

1 2

C960 .1U_0402_16V7KC960 .1U _0402_16V7K

1 2

C932 .1U_0402_16V7KPX@C932 .1U_0402_16V7KPX@

1 2

C961 .1U_0402_16V7KC961 .1U _0402_16V7K

1 2

C934 .1U_0402_16V7KPX@C934 .1U_0402_16V7KPX@

1 2

C930 .1U_0402_16V7KPX@C930 .1U_0402_16V7KPX@

1 2

C958 .1U_0402_16V7KC958 .1U _0402_16V7K

1 2

C939 .1U_0402_16V7KPX@C939 .1U_0402_16V7KPX@

1 2

C927 .1U_0402_16V7KPX@C927 .1U_0402_16V7KPX@

1 2

C923 .1U_0402_16V7KPX@C923 .1U_0402_16V7KPX@

1 2

C918 .1U_0402_16V7KPX@C918 .1U_0402_16V7KPX@

1 2

C924 .1U_0402_16V7KPX@C924 .1U_0402_16V7KPX@

1 2

R540 196_0402_1%R540 196_0402_1%

1 2

C947 .1U_0402_16V7KPX@C947 .1U_0402_16V7KPX@

1 2

C952 .1U_0402_16V7KC952 .1U _0402_16V7K

1 2

C917 .1U_0402_16V7KPX@C917 .1U_0402_16V7KPX@

1 2

C944 .1U_0402_16V7KPX@C944 .1U_0402_16V7KPX@

1 2

C949 .1U_0402_16V7KPX@C949 .1U_0402_16V7KPX@

1 2

C946 .1U_0402_16V7KPX@C946 .1U_0402_16V7KPX@

1 2

C957 .1U_0402_16V7KC957 .1U _0402_16V7K

1 2

C951 .1U_0402_16V7KC951 .1U _0402_16V7K

1 2

C926 .1U_0402_16V7KPX@C926 .1U_0402_16V7KPX@

1 2

C920 .1U_0402_16V7KPX@C920 .1U_0402_16V7KPX@

1 2

C963 .1U_0402_16V7KC963 .1U _0402_16V7K

1 2

C953 .1U_0402_16V7KC953 .1U _0402_16V7K

1 2

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

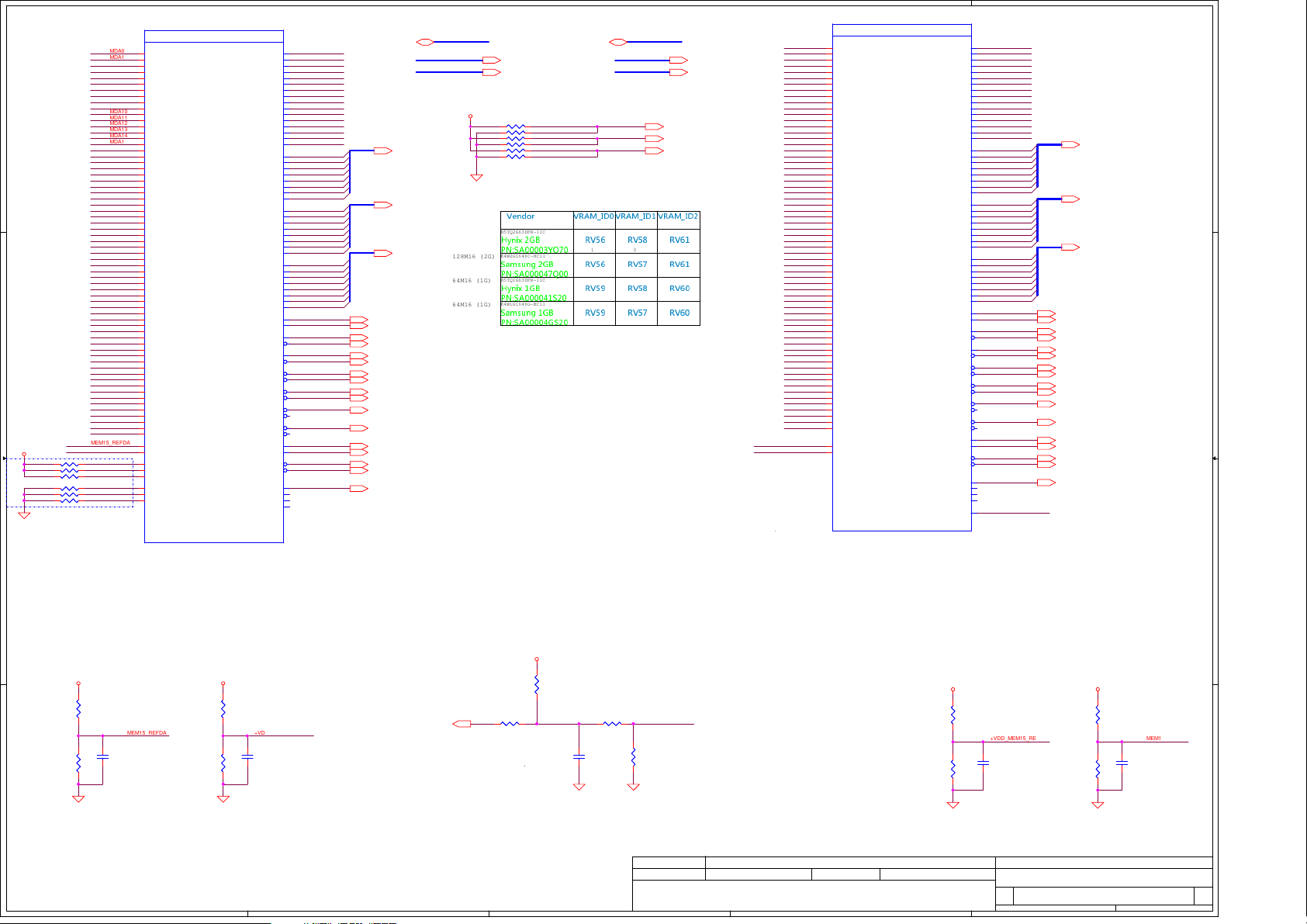

EVENT# pull high

0.75V reference voltage

M_ZVDDIO W/S=8/12 mil, <1000mil

L

+MEM_VREF 15mil

Close to JCPU1

L

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ3

DDRA_SDQ13

DDRA_SDQ40

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ61

DDRA_SDQ15

DDRA_SDQ34

DDRA_SDQ36

DDRA_SDQ4

DDRA_SDQ0

DDRA_SDQ53

DDRA_SDQ47

DDRA_SDQ43

DDRA_SDQ39

DDRA_SDQ46

DDRA_SDQ33

DDRA_SDQ24

DDRA_SDQ54

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ8

DDRA_SDQ51

DDRA_SDQ9

DDRA_SDQ50

DDRA_SDQ12

DDRA_SDQ31

DDRA_SDQ7

DDRA_SDQ63

DDRA_SDQ62

DDRA_SDQ42

DDRA_SDQ26

DDRA_SDQ58

DDRA_SDQ25

DDRA_SDQ32

DDRA_SDQ1

DDRA_SDQ44

DDRA_SDQ48

DDRA_SDQ11

DDRA_SDQ55

DDRA_SDQ2

DDRA_SDQ38

DDRA_SDQ27

DDRA_SDQ41

DDRA_SDQ10

DDRA_SDQ14

DDRA_SDQ49

DDRA_SDQ30

DDRA_SDQ35

DDRA_SDQ37

DDRA_SDQ52

DDRA_SDQ45

DDRA_SDQ57

DDRA_SDQ56

DDRB_SDQ48

DDRB_SDQ39

DDRB_SDQ1

DDRB_SDQ42

DDRB_SDQ36

DDRB_SDQ2

DDRB_SDQ58

DDRB_SDQ33

DDRB_SDQ31

DDRB_SDQ21

DDRB_SDQ54

DDRB_SDQ62

DDRB_SDQ24

DDRB_SDQ15

DDRB_SDQ12

DDRB_SDQ49

DDRB_SDQ60

DDRB_SDQ43

DDRB_SDQ18

DDRB_SDQ34

DDRB_SDQ4

DDRB_SDQ61

DDRB_SDQ6

DDRB_SDQ25

DDRB_SDQ23

DDRB_SDQ57

DDRB_SDQ13

DDRB_SDQ0

DDRB_SDQ28

DDRB_SDQ16

DDRB_SDQ22

DDRB_SDQ19

DDRB_SDQ9

DDRB_SDQ50

DDRB_SDQ35

DDRB_SDQ46

DDRB_SDQ5

DDRB_SDQ37

DDRB_SDQ26

DDRB_SDQ3

DDRB_SDQ8

DDRB_SDQ29

DDRB_SDQ14

DDRB_SDQ7

DDRB_SDQ51

DDRB_SDQ10

DDRB_SDQ59

DDRB_SDQ17

DDRB_SDQ44

DDRB_SDQ41

DDRB_SDQ38

DDRB_SDQ47

DDRB_SDQ32

DDRB_SDQ20

DDRB_SDQ52

DDRB_SDQ30

DDRB_SDQ63

DDRB_SDQ53

DDRB_SDQ40

DDRB_SDQ27

DDRB_SDQ45

DDRB_SDQ55

DDRB_SDQ56

DDRB_SDQ11

DDRA_SWE#

DDRA_SCAS#

DDRA_SRAS#

DDRA_SBS2#

DDRA_SBS1#

DDRA_SBS0#

DDRA_SMA15

DDRA_SMA12

DDRA_SMA14

DDRA_SMA13

DDRA_SMA11

DDRA_SMA10

DDRA_SMA6

DDRA_SMA1

DDRA_SMA7

DDRA_SMA2

DDRA_SMA3

DDRA_SMA8

DDRA_SMA5

DDRA_SMA4

DDRA_SMA9

DDRA_SMA0

DDRA_SDM6

DDRA_SDM3

DDRA_SDM5

DDRA_SDM4

DDRA_SDM2

DDRA_SDM1

DDRA_SDM7

DDRA_SDM0

DDRA_SDQS0

DDRA_SDQS0#

DDRA_SDQS3

DDRA_SDQS3#

DDRA_SDQS2

DDRA_SDQS2#

DDRA_SDQS1

DDRA_SDQS1#

DDRA_SDQS4

DDRA_SDQS4#

DDRA_SDQS5

DDRA_SDQS5#

DDRA_SDQS6

DDRA_SDQS6#

DDRA_SDQS7#

DDRA_SDQS7

DDRA_CLK0#

DDRA_CLK0

DDRA_SCS1#

DDRA_SCS0#

DDRA_ODT0

DDRA_ODT1

DDRA_CKE0

DDRA_CKE1

MEM_MA_EVENT#

M_ZVDDIO

MEM_MA_RST#

DDRA_CLK1#

DDRA_CLK1

DDRA_SDQ20

DDRA_SDQ22

DDRA_SDQ21

DDRA_SDQ23

DDRA_SDQ17

DDRA_SDQ16

DDRA_SDQ18

DDRB_SMA14

DDRB_SMA10

DDRB_SMA7

DDRB_SMA1

DDRB_SMA12

DDRB_SMA6

DDRB_SMA11

DDRB_SMA0

DDRB_SMA9

DDRB_SMA15

DDRB_SMA3

DDRB_SMA5

DDRB_SMA8

DDRB_SMA13

DDRB_SMA2

DDRB_SMA4

DDRB_SRAS#

DDRB_SCAS#

DDRB_SWE#

DDRB_ODT0

DDRB_ODT1

DDRB_CKE1

DDRB_CKE0

DDRB_CLK0#

DDRB_CLK0

DDRB_SCS1#

DDRB_SCS0#

DDRB_CLK1#

MEM_MB_RST#

MEM_MB_EVENT#

DDRB_CLK1

DDRB_SDQS6

DDRB_SDQS6#

DDRB_SDQS2

DDRB_SDQS2#

DDRB_SDQS5

DDRB_SDQS5#

DDRB_SDQS1

DDRB_SDQS1#

DDRB_SDQS4

DDRB_SDQS4#

DDRB_SDQS0

DDRB_SDQS0#

DDRB_SDQS7

DDRB_SDQS7#

DDRB_SDQS3

DDRB_SDQS3#

DDRB_SDM6

DDRB_SDM4

DDRB_SDM2

DDRB_SDM0

DDRB_SDM5

DDRB_SDM3

DDRB_SDM1

DDRB_SDM7

DDRB_SBS0#

DDRB_SBS1#

DDRB_SBS2#

DDRA_SDQ19

MEM_MA_EVENT#

MEM_MB_EVENT#

+MEM_VREF

DDRB_SDQ[63..0] 12

DDRA_SBS0#11

DDRA_SBS1#11

DDRA_SBS2#11

DDRA_SDQS011

DDRA_SDQS0#11

DDRA_SDQS111

DDRA_SDQS1#11

DDRA_SDQS211

DDRA_SDQS2#11

DDRA_SDQS311

DDRA_SDQS3#11

DDRA_SDQS411

DDRA_SDQS4#11

DDRA_SDQS511

DDRA_SDQS5#11

DDRA_SDQS611

DDRA_SDQS6#11

DDRA_SDQS711

DDRA_SDQS7#11

DDRA_CLK011

DDRA_CLK0#11

DDRA_CKE011

DDRA_CKE111

DDRA_ODT011

DDRA_ODT111

DDRA_SCS0#11

DDRA_SCS1#11

DDRA_SRAS#11

DDRA_SCAS#11

DDRA_SWE#11

MEM_MA_RST#11

MEM_MA_EVENT#11

DDRA_CLK111

DDRA_CLK1#11

DDRA_SMA[15..0]11

DDRA_SDM[7..0]11

DDRA_SDQ[63..0] 11

DDRB_SBS0#12

DDRB_SBS1#12

DDRB_SBS2#12

DDRB_SMA[15..0]12

DDRB_SRAS#12

DDRB_SCAS#12

DDRB_SWE#12

DDRB_CLK012

DDRB_CLK0#12

DDRB_CKE012

DDRB_CKE112

DDRB_ODT012

DDRB_ODT112

DDRB_SCS0#12

DDRB_SCS1#12

MEM_MB_RST#12

MEM_MB_EVENT#12

DDRB_CLK112

DDRB_CLK1#12

DDRB_SDQS712

DDRB_SDQS7#12

DDRB_SDQS612

DDRB_SDQS512

DDRB_SDQS412

DDRB_SDQS312

DDRB_SDQS212

DDRB_SDQS112

DDRB_SDQS012

DDRB_SDQS6#12

DDRB_SDQS5#12

DDRB_SDQS4#12

DDRB_SDQS3#12

DDRB_SDQS2#12

DDRB_SDQS1#12

DDRB_SDQS0#12

DDRB_SDM[7..0]12

+1.5V

+MEM_VREF

+1.5V

+1.5V

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1 DDRIII I/F

Custom

7 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1 DDRIII I/F

Custom

7 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1 DDRIII I/F

Custom

7 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

R545 1K_0402_5%R545 1K_0402_5%

1 2

C964

1000P_0402_50V7K

C964

1000P_0402_50V7K

1

2

C965

.1U_0402_16V7K

C965

.1U_0402_16V7K

1

2

R542

1K_0402_1%

R542

1K_0402_1%

1 2

R541 39.2_0402_1%R541 39.2_0402_1%

1 2

MEMORY CHANNEL B

JCPU1C

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

MEMORY CHANNEL B

JCPU1C

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

MB_ADD0

T27

MB_ADD1

P24

MB_ADD2

P25

MB_ADD3

N27

MB_ADD4

N26

MB_ADD5

M28

MB_ADD6

M27

MB_ADD7

M24

MB_ADD8

M25

MB_ADD9

L26

MB_ADD10

U26

MB_ADD11

L27

MB_ADD12

K27

MB_ADD13

W26

MB_ADD14

K25

MB_ADD15

K24

MB_BANK0

U27

MB_BANK1

T28

MB_BANK2

K28

MB_DM0

D14

MB_DM1

A18

MB_DM2

A22

MB_DM3

C25

MB_DM4

AF25

MB_DM5

AG22

MB_DM6

AH18

MB_DM7

AD14

MB_DQS_H0

C15

MB_DQS_L0

B15

MB_DQS_H1

E18

MB_DQS_L1

D18

MB_DQS_H2

E22

MB_DQS_L2

D22

MB_DQS_H3

B26

MB_DQS_L3

A26

MB_DQS_H4

AG24

MB_DQS_L4

AG25

MB_DQS_H5

AG21

MB_DQS_L5

AF21

MB_DQS_H6

AG17

MB_DQS_L6

AG18

MB_DQS_H7

AH14

MB_DQS_L7

AG14

MB_CLK_H0

R26

MB_CLK_L0

R27

MB_CLK_H1

P27

MB_CLK_L1

P28

MB_CKE0

J26

MB_CKE1

J27

MB_ODT0

W27

MB_ODT1

Y28

MB_CS_L0

V25

MB_CS_L1

Y27

MB_RAS_L

V24

MB_CAS_L

V27

MB_WE_L

V28

MB_RESET_L

J25

MB_EVENT_L

T25

MB_DATA0

A14

MB_DATA1

B14

MB_DATA2

D16

MB_DATA3

E16

MB_DATA4

B13

MB_DATA5

C13

MB_DATA6

B16

MB_DATA7

A16

MB_DATA8

C17

MB_DATA9

B18

MB_DATA10

B20

MB_DATA11

A20

MB_DATA12

E17

MB_DATA13

B17

MB_DATA14

B19

MB_DATA15

C19

MB_DATA16

C21

MB_DATA17

B22

MB_DATA18

C23

MB_DATA19

A24

MB_DATA20

D20

MB_DATA21

B21

MB_DATA22

E23

MB_DATA23

B23

MB_DATA24

E24

MB_DATA25

B25

MB_DATA26

B27

MB_DATA27

D28

MB_DATA28

B24

MB_DATA29

D24

MB_DATA30

D26

MB_DATA31

C27

MB_DATA32

AG26

MB_DATA33

AH26

MB_DATA34

AF23

MB_DATA35

AG23

MB_DATA36

AG27

MB_DATA37

AF27

MB_DATA38

AH24

MB_DATA39

AE24

MB_DATA40

AE22

MB_DATA41

AH22

MB_DATA42

AE20

MB_DATA43

AH20

MB_DATA44

AD23

MB_DATA45

AD22

MB_DATA46

AD21

MB_DATA47

AD20

MB_DATA48

AF19

MB_DATA49

AE18

MB_DATA50

AE16

MB_DATA51

AH16

MB_DATA52

AG20

MB_DATA53

AG19

MB_DATA54

AF17

MB_DATA55

AD16

MB_DATA56

AG15

MB_DATA57

AD15

MB_DATA58

AG13

MB_DATA59

AD13

MB_DATA60

AG16

MB_DATA61

AF15

MB_DATA62

AE14

MB_DATA63

AF13

R544 1K_0402_5%R544 1K_0402_5%

1 2

R543

1K_0402_1%

R543

1K_0402_1%

1 2

MEMORY CHANNEL A

JCPU1B

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

MEMORY CHANNEL A

JCPU1B

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

MA_ADD0

U20

MA_ADD1

R20

MA_ADD2

R21

MA_ADD3

P22

MA_ADD4

P21

MA_ADD5

N24

MA_ADD6

N23

MA_ADD7

N20

MA_ADD8

N21

MA_ADD9

M21

MA_ADD10

U23

MA_ADD11

M22

MA_ADD12

L24

MA_ADD13

AA25

MA_ADD14

L21

MA_ADD15

L20

MA_BANK0

U24

MA_BANK1

U21

MA_BANK2

L23

MA_DM0

E14

MA_DM1

J17

MA_DM2

E21

MA_DM3

F25

MA_DM4

AD27

MA_DM5

AC23

MA_DM6

AD19

MA_DM7

AC15

MA_DQS_H0

G14

MA_DQS_L0

H14

MA_DQS_H1

G18

MA_DQS_L1

H18

MA_DQS_H2

J21

MA_DQS_L2

H21

MA_DQS_H3

E27

MA_DQS_L3

E26

MA_DQS_H4

AE26

MA_DQS_L4

AD26

MA_DQS_H5

AB22

MA_DQS_L5

AA22

MA_DQS_H6

AB18

MA_DQS_L6

AA18

MA_DQS_H7

AA14

MA_DQS_L7

AA15

MA_CLK_H0

T21

MA_CLK_L0

T22

MA_CLK_H1

R23

MA_CLK_L1

R24

MA_CKE0

H28

MA_CKE1

H27

MA_ODT0

Y25

MA_ODT1

AA27

MA_CS_L0

V22

MA_CS_L1

AA26

MA_RAS_L

V21

MA_CAS_L

W24

MA_WE_L

W23

MA_RESET_L

H25

MA_EVENT_L

T24

M_VREF

W20

M_ZVDDIO

W21

MA_DATA0

E13

MA_DATA1

J13

MA_DATA2

H15

MA_DATA3

J15

MA_DATA4

H13

MA_DATA5

F13

MA_DATA6

F15

MA_DATA7

E15

MA_DATA8

H17

MA_DATA9

F17

MA_DATA10

E19

MA_DATA11

J19

MA_DATA12

G16

MA_DATA13

H16

MA_DATA14

H19

MA_DATA15

F19

MA_DATA16

H20

MA_DATA17

F21

MA_DATA18

J23

MA_DATA19

H23

MA_DATA20

G20

MA_DATA21

E20

MA_DATA22

G22

MA_DATA23

H22

MA_DATA24

G24

MA_DATA25

E25

MA_DATA26

G27

MA_DATA27

G26

MA_DATA28

F23

MA_DATA29

H24

MA_DATA30

E28

MA_DATA31

F27

MA_DATA32

AB28

MA_DATA33

AC27

MA_DATA34

AD25

MA_DATA35

AA24

MA_DATA36

AE28

MA_DATA37

AD28

MA_DATA38

AB26

MA_DATA39

AC25

MA_DATA40

Y23

MA_DATA41

AA23

MA_DATA42

Y21

MA_DATA43

AA20

MA_DATA44

AB24

MA_DATA45

AD24

MA_DATA46

AA21

MA_DATA47

AC21

MA_DATA48

AA19

MA_DATA49

AC19

MA_DATA50

AC17

MA_DATA51

AA17

MA_DATA52

AB20

MA_DATA53

Y19

MA_DATA54

AD18

MA_DATA55

AD17

MA_DATA56

AA16

MA_DATA57

Y15

MA_DATA58

AA13

MA_DATA59

AC13

MA_DATA60

Y17

MA_DATA61

AB16

MA_DATA62

AB14

MA_DATA63

Y13

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

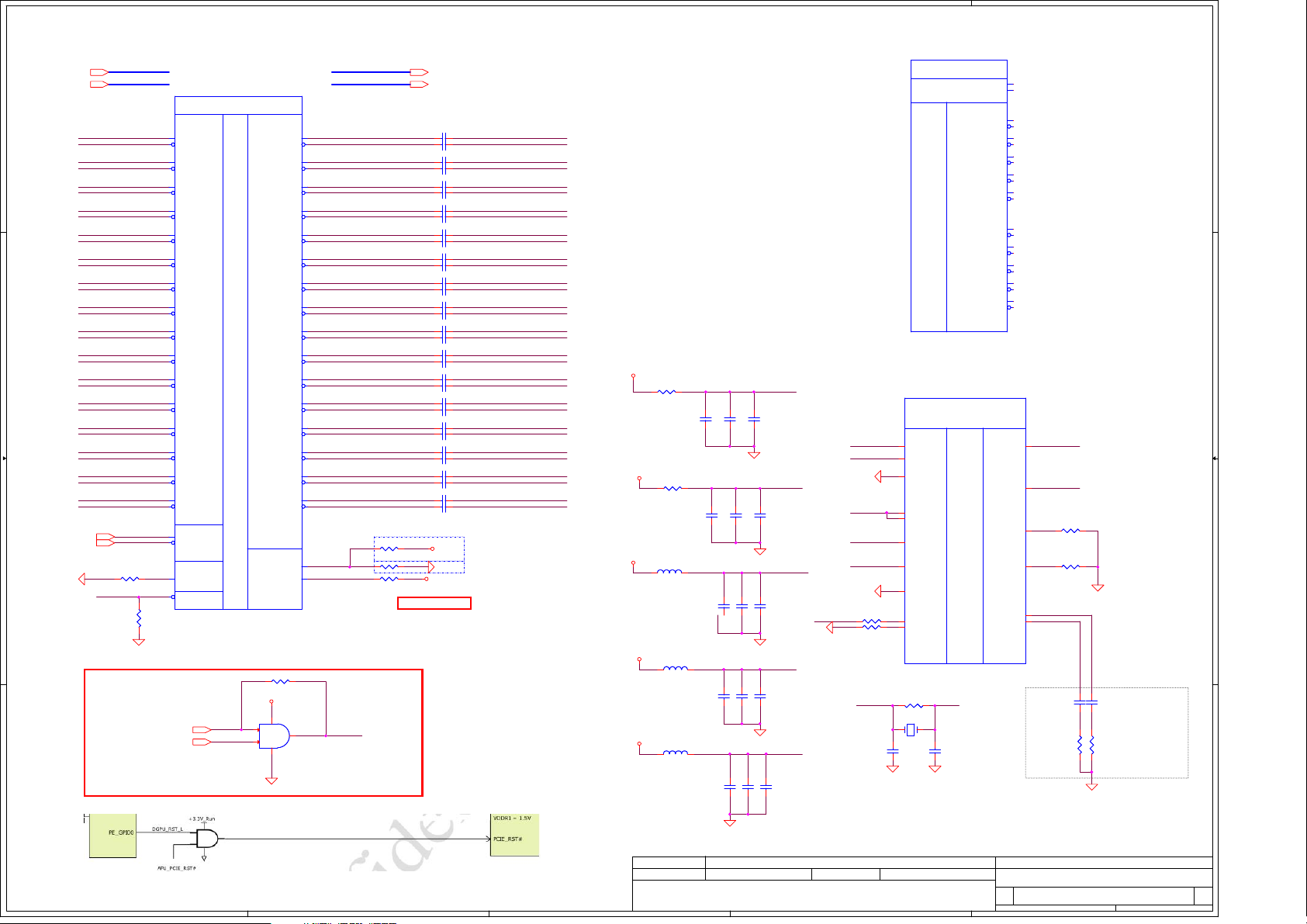

100MHz

100MHz

NSS

To LVDS Translator

CRT

To LVDS

Translator

To FCH

VDDIO level

Need Level shift

THERMTRIP shutdown

temperature: 115 degree

Asserted as an input to

force processor into

HTC-active state

Indicates to the FCH that a th ermal trip

has occurred. Its assertion wi ll cause the FCH

to transition the system to S5 immediately

TEST35 change to PU for

HDMI can not output

20110126

Allow_STOP leakage issue

SVI 2.0

(0 ohm

at Power Side)

Route as differential with APU _VDD_RUN_FB_L

LVDS/eDP

To HDMI

CPU TSI interface level shift

BSH111, the Vgs is:

min = 0.4V

Max = 1.3V

HDT Debug conn

Close to Header

HDMI

For ESD request close APU side

To HDMI

Place near APU

Internal PU when no use HDT

Vg = 1.607 V

When APU High -> MOS OFF (Vgs < 0.4V )

APU Low -> MOS ON (Vgs > 1.3V)

10/27 300 ohm??

To FCH

VGA ML

Close to APU (JCPU1)

L

Del DP0_TXP1/N1

DP_AUX_ZVSS W/S=8/12 mil, <3000mil

L

SB-TSI (S5 Domain)

Del DP_ENVDD

LA-8124 no use this DP_ENBKL.

11/10 del debug connector

11/14 Change net name

11/14 Reserve

11/15 RF

APU_DISP_CLKP

APU_DISP_CLKN

APU_THERMTRIP#

APU_PROCHOT#

APU_CLKP

APU_CLKN

DP_AUX_ZVSS

DP0_TXN0

APU_SID

APU_SIC

DP1_HPD

ALERT_L

APU_PROCHOT#

APU_THERMTRIP#

TEST35

ALLOW_STOP

APU_THERMTRIP#

APU_PROCHOT#

APU_PWRGD

APU_RST#

APU_DBRDY

APU_DBREQ#

DP0_TXP0

APU_SVC

APU_SVD

APU_RST#_APUAPU_RST#

APU_PWRGD APU_PWRGD_APU

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_VDDNB_SEN

APU_VDD_SEN

DP0_HPD

DP_ENBKL

DP_INT_PWM

APU_TEST18

APU_TEST19

APU_TEST20

APU_TEST24

FS1R2

ALLOW_STOP

DP0_AUXP

DP0_AUXN

ML_VGA_AUXP

ML_VGA_AUXN

APU_SID

APU_SIC

APU_SIC

APU_SID

ALERT_L

APU_RST#

APU_PWRGD

APU_TDI

APU_TCK

APU_TMS

APU_TRST#

APU_DBREQ#

EC_SMB_CK2

EC_SMB_DA2

APU_SVT

APU_SVT

APU_SVC

APU_SVD

APU_HDMI_CLK

APU_HDMI_DATA

DP2_HPD

DP0_AUXN

ML_VGA_AUXP

ML_VGA_AUXN

DP0_AUXP

M_TEST

TEST25_H

TEST25_L

DP1_TXN1

DP1_TXP3

DP1_TXN0

DP1_TXN3

DP1_TXP2

DP1_TXN2

DP1_TXP1

DP1_TXP0

APU_DISP_CLKP

APU_DISP_CLKN

APU_CLKP

APU_CLKN

APU_CLKP25

APU_CLKN25

APU_DISP_CLKP25

APU_DISP_CLKN25

DP0_TXN0_C21

DP0_AUXP_C 21

DP0_AUXN_C 21

APU_VDD_RUN_FB_L54

DP1_HPD 10

EC_THERM# 25,37,45,54

H_THERMTRIP# 27

MAINPWON 45,46

DP0_TXP0_C21

APU_SVC54

APU_SVD54

APU_RST#25

APU_PWRGD25,54

APU_VDDNB_SEN54

APU_VDD_SEN54

ML_VGA_AUXP_C 26

ML_VGA_AUXN_C 26

DP0_HPD 10

DP_ENBKL 10

DP_INT_PWM 10

ALLOW_STOP25

EC_SMB_DA2 14,21,37

EC_SMB_CK2 14,21,37

APU_SVT54

APU_HDMI_TXD2+23

APU_HDMI_TXD2-23

APU_HDMI_TXD1-23

APU_HDMI_TXD1+23

APU_HDMI_TXD0-23

APU_HDMI_TXD0+23

APU_HDMI_TXC-23

APU_HDMI_TXC+23

APU_HDMI_CLK 23

APU_HDMI_DATA 23

DP2_HPD 23

ML_VGA_TXP026

ML_VGA_TXN026

ML_VGA_TXP126

ML_VGA_TXN126

ML_VGA_TXP226

ML_VGA_TXN226

ML_VGA_TXP326

ML_VGA_TXN326

H_PROCHOT#45

+3VS+1.5V

+1.5V

+1.5V

+3VALW

+3VS

+1.5V

+1.5V

+1.2VS

+1.5V

+1.5V_PCIE +1.5V

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1 Display / MISC / HDT

Custom

8 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1 Display / MISC / HDT

Custom

8 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1 Display / MISC / HDT

Custom

8 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

R596 1K_0402_5%R596 1K_0402_5%

1 2

R582 1K_0402_5%R582 1K_0402_5%

1 2

R586

1K_0402_5%

R586

1K_0402_5%

1 2

C972 .1U_0402_16V7KC972 .1U_0402_16V7K

1 2

C968 .1U_0402_16V7KC968 .1U_0402_16V7K

1 2

R623 0_0402_5%@R623 0_0402_5%@

1 2

R611 0_0402_5%R611 0_0402_5%

1 2

E

B

C

Q11

MMBT3904_SOT23-3

E

B

C

Q11

MMBT3904_SOT23-3

2

31

R548 510_0402_1%R548 510_0402_1%

1 2

C981 .1U_0402_16V7KC981 .1U_0402_16V7K

1 2

C4703 22P_0402_50V8JC4703 22P_0402_50V8J

12

R604 1K_0402_5%R604 1K_0402_5%

12

R564 39.2_0402_1%@R564 39.2_0402_1%@

1 2

C38 33P_0402_50V8JC38 33P_0402_50V8J

R593 1K_0402_5%R593 1K_0402_5%

1 2

R556 1.8K_0402_5%R556 1.8K_0402_5%

12

R583 1K_0402_5%R583 1K_0402_5%

1 2

R594 1K_0402_5%R594 1K_0402_5%

1 2

T16T16

C969 .1U_0402_16V7KC969 .1U_0402_16V7K

1 2

R554 1.8K_0402_5%R554 1.8K_0402_5%

12

C4704 22P_0402_50V8JC4704 22P_0402_50V8J

12

R555 1.8K_0402_5%R555 1.8K_0402_5%

12

R578 300_0402_5%R578 300_0402_5%

12

R575 1K_0402_5%@R575 1K_0402_5%@

1 2

T6T6

C978 .1U_0402_16V7KC978 .1U_0402_16V7K

1 2

C976 .1U_0402_16V7KC976 .1U_0402_16V7K

1 2

R615 0_0402_5%R615 0_0402_5%

1 2

R595 1K_0402_5%R595 1K_0402_5%

1 2

C4705 22P_0402_50V8JC4705 22P_0402_50V8J

12

C979 .1U_0402_16V7KC979 .1U_0402_16V7K

1 2

R576 1K_0402_5%@R576 1K_0402_5%@

1 2

T11T11

R571 10K_0402_5%R571 10K_0402_5%

1 2

T15T15

E

B

C

Q12

MMBT3904_SOT23-3

E

B

C

Q12

MMBT3904_SOT23-3

2

3 1

C935 0.1U_0402_16V4ZC935 0.1U_0402_16V4Z

1 2

C970 .1U_0402_16V7KC970 .1U_0402_16V7K

1 2

R574 1K_0402_5%R574 1K_0402_5%

1 2

R580 300_0402_5%R580 300_0402_5%

12

R598 0_0402_5%R598 0_0402_5%

1 2

T10T10

T13T13

T8T8

R547 1.8K_0402_5%R547 1.8K_0402_5%

12

C36 22P_0402_50V8JC36 22P_0402_50V8J

12

C977 .1U_0402_16V7KC977 .1U_0402_16V7K

1 2

R584 1K_0402_5%R584 1K_0402_5%

1 2

T17T17

R591

0_0402_5%

R591

0_0402_5%

1 2

R791 1K_0402_5%R791 1K_0402_5%

1 2

R569 150_0402_1%R569 150_0402_1%

1 2

C40 33P_0402_50V8JC40 33P_0402_50V8J

R581 1K_0402_5%R581 1K_0402_5%

1 2

C971 .1U_0402_16V7KC971 .1U_0402_16V7K

1 2

R577 1K_0402_5%

@

R577 1K_0402_5%

@

12

R567 39.2_0402_1%R567 39.2_0402_1%

1 2

R579 1K_0402_5%R579 1K_0402_5%

1 2

T12T12

G

D

S

Q10

BSH111_SOT23-3

G

D

S

Q10

BSH111_SOT23-3

2

13

R535

31.6K_0402_1%

R535

31.6K_0402_1%

1 2

G

D

S

Q9

BSH111_SOT23-3

G

D

S

Q9

BSH111_SOT23-3

2

13

ANALOG/DISPLAY/MIS C

DISPLAY PORT

0

DISPLAY PORT 1DISPLAY PORT 2CLKSER.CTRLJTAGSENSE

DISPLAY PORT

MISC.

TESTRSVD

JCPU1D

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

ANALOG/DISPLAY/MIS C

DISPLAY PORT

0

DISPLAY PORT 1DISPLAY PORT 2CLKSER.CTRLJTAGSENSE

DISPLAY PORT

MISC.

TESTRSVD

JCPU1D

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

DP0_TXP0

L3

DP0_TXN0

L2

DP0_TXP1

K5

DP0_TXN1

K4

DP0_TXP2

K2

DP0_TXN2

K1

DP0_TXP3

J3

DP0_TXN3

J2

DP1_TXP0

H5

DP1_TXN0

H4

DP1_TXP1

H2

DP1_TXN1

H1

DP1_TXP2

G3

DP1_TXN2

G2

DP1_TXP3

F2

DP1_TXN3

F1

DP2_TXP0

L9

DP2_TXN0

L8

DP2_TXP1

L5

DP2_TXN1

L6

DP2_TXP2

K8

DP2_TXN2

K7

DP2_TXP3

J6

DP2_TXN3

J5

CLKIN_H

AE11

CLKIN_L

AD11

DISP_CLKIN_H

AB11

DISP_CLKIN_L

AA11

SVC

B3

SVD

A3

SVT

C3

SIC

AG12

SID

AH12

RESET_L

AF10

PWROK

AB12

DMAACTIVE_L

AC12

PROCHOT_L

AC10

THERMTRIP_L

AE12

ALERT_L

AF12

TDI

H10

TDO

J10

TCK

F10

TMS

G10

TRST_L

F9

DBRDY

G9

DBREQ_L

H9

VSS_SENSE

B4

VDDP_SENSE

C5

VDDNB_SENSE

A4

VDDIO_SENSE

A5

VDD_SENSE

C4

VDDR_SENSE

B5

DP0_AUXP

D1

DP0_AUXN

D2

DP1_AUXP

E1

DP1_AUXN

E2

DP2_AUXP

D5

DP2_AUXN

D6

DP3_AUXP

E5

DP3_AUXN

E6

DP4_AUXP

F5

DP4_AUXN

F6

DP5_AUXP

G5

DP5_AUXN

G6

DP0_HPD

D3

DP1_HPD

E3

DP2_HPD

D7

DP3_HPD

E7

DP4_HPD

F7

DP5_HPD

G7

DP_BLON

C6

DP_DIGON

B6

DP_VARY_BL

A6

DP_AUX_ZVSS

C1

TEST6

AD12

TEST28_H

L10

TEST28_L

M10

TEST30_H

P19

TEST30_L

R19

TEST32_H

T19

TEST32_L

N19

TEST4

P18

TEST5

R18

TEST9

M18

TEST10

N18

TEST14

F11

TEST15

G11

TEST16

H11

TEST17

J11

TEST18

F12

TEST19

G12

TEST20

J12

TEST24

H12

TEST35

AA12

TEST25_H

AE10

TEST25_L

AD10

TEST31

K22

RSVD1

Y10

RSVD2

AA10

RSVD3

Y12

RSVD4

K21

FS1R2

W10

R588

10K_0402_5%

R588

10K_0402_5%

12

T18T18

C974 .1U_0402_16V7KC974 .1U_0402_16V7K

1 2

R613 0_0402_5%

@

R613 0_0402_5%

@

1 2

R592 1K_0402_5%R592 1K_0402_5%

1 2

C973 .1U_0402_16V7KC973 .1U_0402_16V7K

1 2

T9T9

R587

10K_0402_5%

R587

10K_0402_5%

12

R536

30K_0402_1%

R536

30K_0402_1%

1 2

R558 300_0402_5%R558 300_0402_5%

1 2

T21T21

C980 .1U_0402_16V7KC980 .1U_0402_16V7K

1 2

T7T7

R557 510_0402_1%R557 510_0402_1%

1 2

C35 22P_0402_50V8JC35 22P_0402_50V8J

12

R92 1K_0402_5%@R92 1K_0402_5%@

1 2

C975 .1U_0402_16V7KC975 .1U_0402_16V7K

1 2

R616 0_0402_5%R616 0_0402_5%

1 2

R612 0_0402_5%@R612 0_0402_5%@

1 2

R609

10K_0402_5%

R609

10K_0402_5%

12

R559 300_0402_5%@R559 300_0402_5%@

1 2

R610

1K_0402_5%

R610

1K_0402_5%

1 2

C4702 22P_0402_50V8JC4702 22P_0402_50V8J

12

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

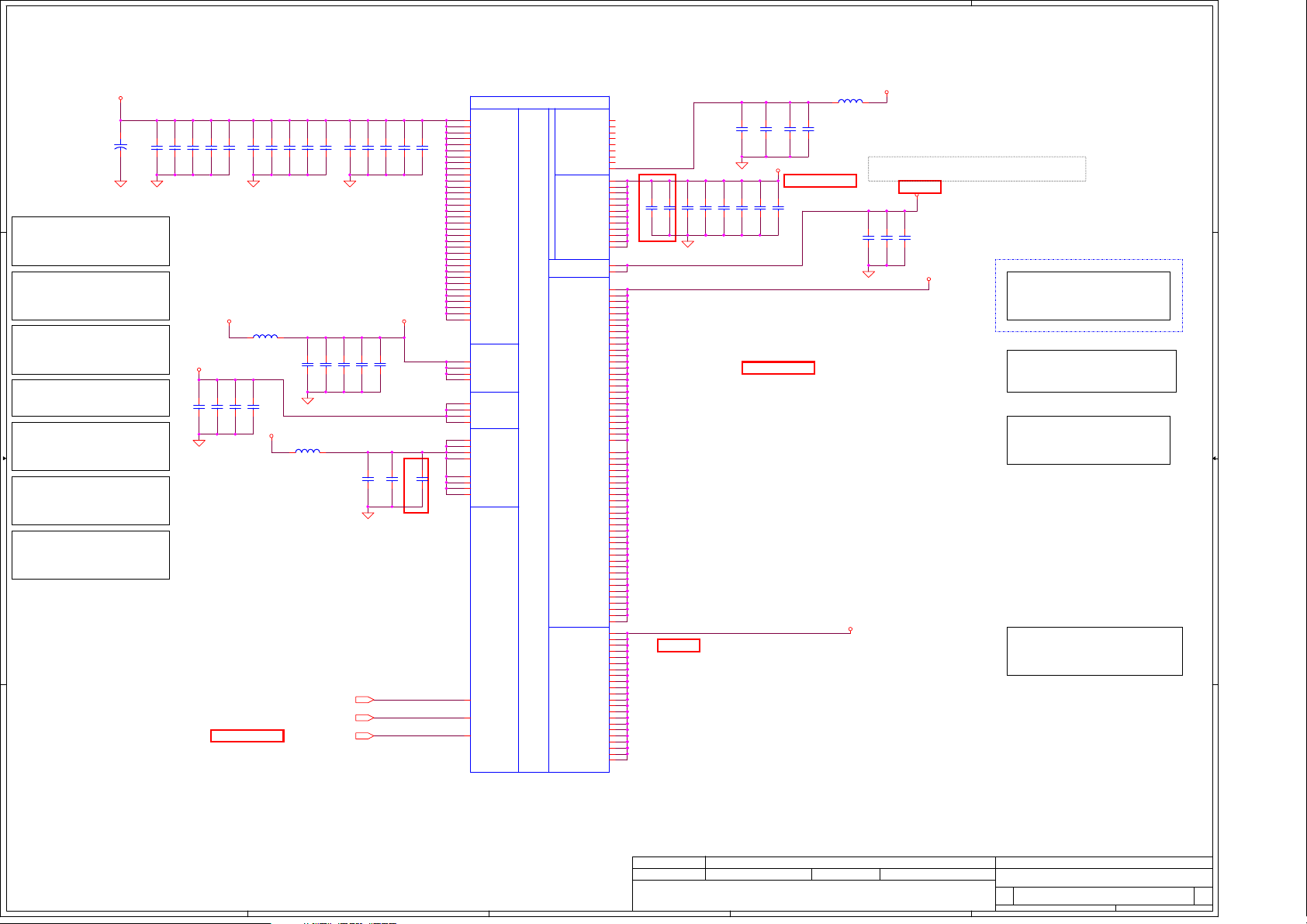

Decoupling betwe en CPU and DIMMs

across VDDIO and VSS split

3.2A

VDD

+CPU_CORE

VDDA

+2.5VS

0.75A

VDDNB

+CPU_CORE_NB

VDDIO

+1.5V

Consumption

60A

VDDP / VDDR

+1.2VS

Power Name

5A / 3.5A

37A

+CPU_CORE Decoupling

330uF x 4 @ x1

22uF x 10

0.22uF x2

0.01uF x3

180pF x2 @ x1

VDDR Decoupling

Close JCPU1.AG10,AH8,AH9,AH10

10uF x3

0.22uF x2

1000pF x1

180pF x2

+CPU_CORE_NB Decoupling

330uF x2

22uF x2 @ x2

10uF x1

0.22uF x2

180pF x3

+1.5V / VDDIO Decoupling

330uF x1

22uF x4

4.7uF x4

0.22uF x6

180pF x1 @x1

+1.5VS

Group A

Group B

+CPU_CORE

+CPU_CORE_NB

+1.2VS

Power Sequence of APU

+1.5V

+2.5VS

VDDP Decoupling

Close JCPU1.AH3~7

22uF x1

10uF x3

0.22uF x2

1000pF @x1

180pF x2

VDDA Decoupling

47uF x1

0.22uF x1

3300pF x1

180pF x1

Comal

Pumori 2.0

P5WS5

330uF 220uF 47uF 22uF 10uF 4.7uF 0.22uF 0.01uF 3300pF 180pF1nF

7 / 2

Pop / @

7 / 2

1

1

1

1

0

19/11 7 4 17 3

Decoupling Caps.

1 1 / 1 14/2

19/11 7 35 17 1 1 / 1 13/3

13 3 8 19 3 1 4 16

Northbridge Powe r Pins

for Remote Decou pling

220uF x1

VDDIO: 3200mA

VDDR: 3500mA

VDDA: 750mA

VDDP: 5000mA

+CPU_CORE-->+APU_CORE

+CPU_CORE_NB-->+APU_CORE_NB

On power team page

On power team page

VDDNB_CAP

+APU_CORE

+APU_CORE_NB

+1.5V

+1.2VS

+APU_CORE

+APU_CORE_NB

+1.5V

+1.2VS

+APU_VDDA

+APU_VDDA

+1.2VS

+1.5V

+1.2VS

+1.5V

+1.2VS

+2.5VS

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1R2 PWR / GND

Custom

9 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1R2 PWR / GND

Custom

9 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QCL51 LA-8712P

0.1

AMD FS1R2 PWR / GND

Custom

9 56Monday, November 28, 2011

2011/07/08 2015/07/08

Compal Electronics, Inc.

C1012 22U_0805_6.3V6MC1012 22U_0805_6.3V6M

1

2

C18 47U_0805_4V6C18 47U_0805_4V6

1

2

C51 22U_0805_6.3V6MC51 22U_0805_6.3V6M

1

2

C6 10U_0603_6.3V6MC6 10U_0603_6.3V6M

1

2

C1027 0.22U_0402_10V4 ZC1027 0.22U_0402_10V4Z

1

2

C50 1000P_0402_50V7K

@

C50 1000P_0402_50V7K

@

1

2

C53 10U_0603_6.3V6MC53 10U_0603_6.3V6M

1

2

L1

FBMA-L11-201209-221LMA30T_0805

L1

FBMA-L11-201209-221LMA30T_0805

12

+

C1038220U_6.3V_M

+

C1038220U_6.3V_M

1

2

C7 10U_0603_6.3V6MC7 10U_0603_6.3V6M

1

2

C1041 0.22U_0402_10V4 ZC1041 0.22U_0402_10V4Z

1

2

C1044 180P _0402_50V8JC1044 180P _0402_50V8J

1

2

C1052 0.22U_04 02_10V4ZC1052 0.22U_0402_10V 4Z

1

2

GND

JCPU1F

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

GND

JCPU1F

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

VSS_1

J20

VSS_2

L4

VSS_3

R7

VSS_4

W18

VSS_5

A15

VSS_6

AB17

VSS_7

AC22

VSS_8

AE21

VSS_9

AF24

VSS_10

AH23

VSS_11

AH25

VSS_12

B7

VSS_13

C14

VSS_14

C16

VSS_15

C2

VSS_16

C20

VSS_17

C22

VSS_18

C24

VSS_19

C26

VSS_20

C28

VSS_21

D13

VSS_22

D15

VSS_23

D17

VSS_24

D19

VSS_25

D23

VSS_26

D25

VSS_27

D27

VSS_28

E4

VSS_29

E9

VSS_30

F14

VSS_31

F16

VSS_32

F18

VSS_33

F20

VSS_34

F22

VSS_35

F26

VSS_36

F28

VSS_37

G13

VSS_38

G15

VSS_39

G17

VSS_40

G19

VSS_41

G21

VSS_42

G23

VSS_43

G25

VSS_44

G4

VSS_45

J22

VSS_46

J24

VSS_47

J4

VSS_48

J7

VSS_49

K11

VSS_50

K14

VSS_51

K9

VSS_52

AC11

VSS_53

L19

VSS_54

L7

VSS_55

M11

VSS_56

AF11

VSS_57

V19

VSS_58

V9

VSS_59

W16

VSS_60

W4

VSS_61

W7

VSS_62

Y11

VSS_63

Y20

VSS_64

Y22

VSS_65

Y9

VSS_66

A17

VSS_67

A13

VSS_68

K16

VSS_69

F24

VSS_70

G8

VSS_71

H7

VSS_72

J8

VSS_73

A19

VSS_74

A21

VSS_75

A23

VSS_76

A25

VSS_77

A7

VSS_78

AA4

VSS_79

AA7

VSS_80

AB13

VSS_81

AB15

VSS_82

AB19

VSS_83

AB21

VSS_84

AB23

VSS_85

AB25

VSS_86

AB27

VSS_87

AB9

VSS_88

AC14

VSS_89

AC16

VSS_90

AC18

VSS_91

AC20

VSS_92

AC24

VSS_93

AC26

VSS_94

AC28

VSS_95

AC4

VSS_96

AC7

VSS_97

AD9

VSS_98

AE13

VSS_99

AE15

VSS_100

AE17

VSS_101

M9

VSS_102

N10

VSS_103

N4

VSS_104

N7

VSS_105

R10

VSS_106

R4

VSS_107

T11

VSS_108

T9

VSS_109

U10

VSS_110

U18

VSS_111

U4

VSS_112

U7

VSS_113

V11

VSS_114

AE19

VSS_115

AE23

VSS_116

AE25

VSS_117

AE27

VSS_118

AE4

VSS_119

AE7

VSS_120

AF14

VSS_121

AF16

VSS_122

AF18

VSS_123

AF20

VSS_124

AF22

VSS_125

AF26

VSS_126

AF28

VSS_127

AF9

VSS_128

AG4

VSS_129

AG7

VSS_130

AH13

VSS_131

AH15

VSS_132

AH17

VSS_133

AH19

VSS_134

AH21

VSS_135

P9

VSS_136

C18

VSS_137

D21

VSS_138

W14

VSS_139

P11

VSS_140

C7

VSS_141

E8

VSS_142

K18

VSS_143

W12

C1020 0.22U_0402_10V4 ZC1020 0.22U_0402_10V4Z

1

2

POWER

JCPU1E

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

POWER

JCPU1E

LOTES_ACA-ZIF-109-P12-A_FS1R2

CONN@

VDD_1

F8

VDD_2

H6

VDD_3

J1

VDD_4

J14

VDD_5

P6

VDD_6

P10

VDD_7

J16

VDD_8

J18

VDD_9

J9

VDD_10

K19

VDD_11

K3

VDD_12

K17

VDD_13

M3

VDD_14

K6

VDD_15

V10

VDD_16

V18

VDD_17

V3

VDD_18

F3

VDD_19

L18

VDD_20

V6

VDD_21

W1

VDD_22

T18

VDD_23

Y14

VDD_24

AA1

VDD_25

AB6

VDD_26

AC1

VDD_27

R1

VDD_28

P3

VDD_29

K10

VDD_30

H3

VDD_31

M19

VDDNB_1

C8

VDDNB_2

D10

VDDNB_3

B8

VDDNB_4

B12

VDDNB_5

C9

VDDNB_6

A9

VDDNB_7

A10

VDDNB_8

A8

VDDNB_9

A11

VDDNB_10

E10

VDDNB_11

E11

VDDNB_12

C10

VDDIO_1

H26

VDDIO_2

K20

VDDIO_3

J28

VDDIO_4

K23

VDDIO_5

K26

VDDIO_6

L22

VDDIO_7

L25

VDDIO_8

L28

VDDIO_9

M20

VDDIO_10

M23

VDDIO_11

M26

VDDIO_12

N22

VDDIO_13

N25

VDDIO_14

N28

VDDIO_15

P20

VDDIO_16

P23

VDDIO_17

P26

VDDIO_18

AA28

VDDP_1

AH6

VDDP_2

AH5

VDDP_3

AH4

VDDP_4

AH3

VDDP_5

AH7

VDDA

AB10

VDDR_1

AG10

VDDR_2

AH8

VDDR_3

AH9

VDDR_4

AH10

VDDIO_19

T23

VDDIO_20

T26

VDDIO_21

U22

VDDIO_22

U25

VDDIO_23

U28

VDDIO_24

Y26

VDDIO_25

T20

VDDIO_26

R28

VDDIO_27

R25

VDDIO_28

R22

VDDIO_29

V20

VDDIO_30

V23

VDDIO_31

V26

VDDIO_32

W22

VDDIO_33

W25

VDDIO_34

W28

VDDIO_35

Y24

VDDIO_36

G28

VDDNB_13

C11

VDDNB_14

C12

VDDNB_15

D9

VDDNB_16

D8

VDDNB_17

D12

VDDNB_18

D11

VDDNB_19

B11

VDDNB_20

A12

VDDNB_21

B10

VDDNB_22

E12

VDDNB_23

B9

VDDNB_CAP_1

K13

VDDNB_CAP_2

K12

VDD_32

R11

VDD_33

T10

VDD_34

H8

VDD_35

G1

VDD_36

U11

VDD_37

W11

VDD_38

W13

VDD_39

W15

VDD_40

W17

VDD_41

W19

VDD_42

AB3

VDD_43

AD3

VDD_44

AD6

VDD_45

AE1

VDD_46

L1

VDD_47

Y6

VDD_48

M6

VDD_49

N11

VDD_50

N1

VDD_51

T3

VDD_52

T6

VDD_53

U19

VDD_54

U1

VDD_55

Y16

VDD_56

Y18

VDD_57

Y3

VDD_58

D4

VDD_59

F4

VDD_60

AF6

VDD_61

AF3

VDD_62

L11

C16 4.7U_0603_6.3V6KC16 4.7U_0603_6.3V6K

1

2

C52 10U_0603_6.3V6MC52 10U_0603_6.3V6M

1

2

C1028 0.22U_0402_10V4 ZC1028 0.22U_0402_10V4Z

1

2

C15 4.7U_0603_6.3V6KC15 4.7U_0603_6.3V6K

1

2

+

C5 330U_D2_2V_Y

+

C5 330U_D2_2V_Y

1

2

C17 4.7U_0603_6.3V6KC17 4.7U_0603_6.3V6K

1

2

C8 10U_0603_6.3V6MC8 10U_0603_6.3V6M

1

2

C1024 180P_0402_50V 8JC1024 180P_0402_50V 8J

1

2

C1025 180P_0402_50V 8JC1025 180P_0402_50V 8J

1

2

C1043 180P_0402_50V 8JC1043 180P_0402_50V 8J

1

2

C1045 180P _0402_50V8JC1045 180P _0402_50V8J

1

2

C14 4.7U_0603_6.3V6KC14 4.7U_0603_6.3V6K

1

2

C1036 0.22U_0402_10V4 ZC1036 0.22U_0402_10V4Z

1

2

C1053 0.22U_04 02_10V4ZC1053 0.22U_0402_10V 4Z

1

2

C1013 22U_0805_6.3V6MC1013 22U_0805_6.3V6M

1

2

C1037 0.22U_0402_10V4 ZC1037 0.22U_0402_10V4Z

1

2

C54 10U_0603_6.3V6MC54 10U_0603_6.3V6M

1