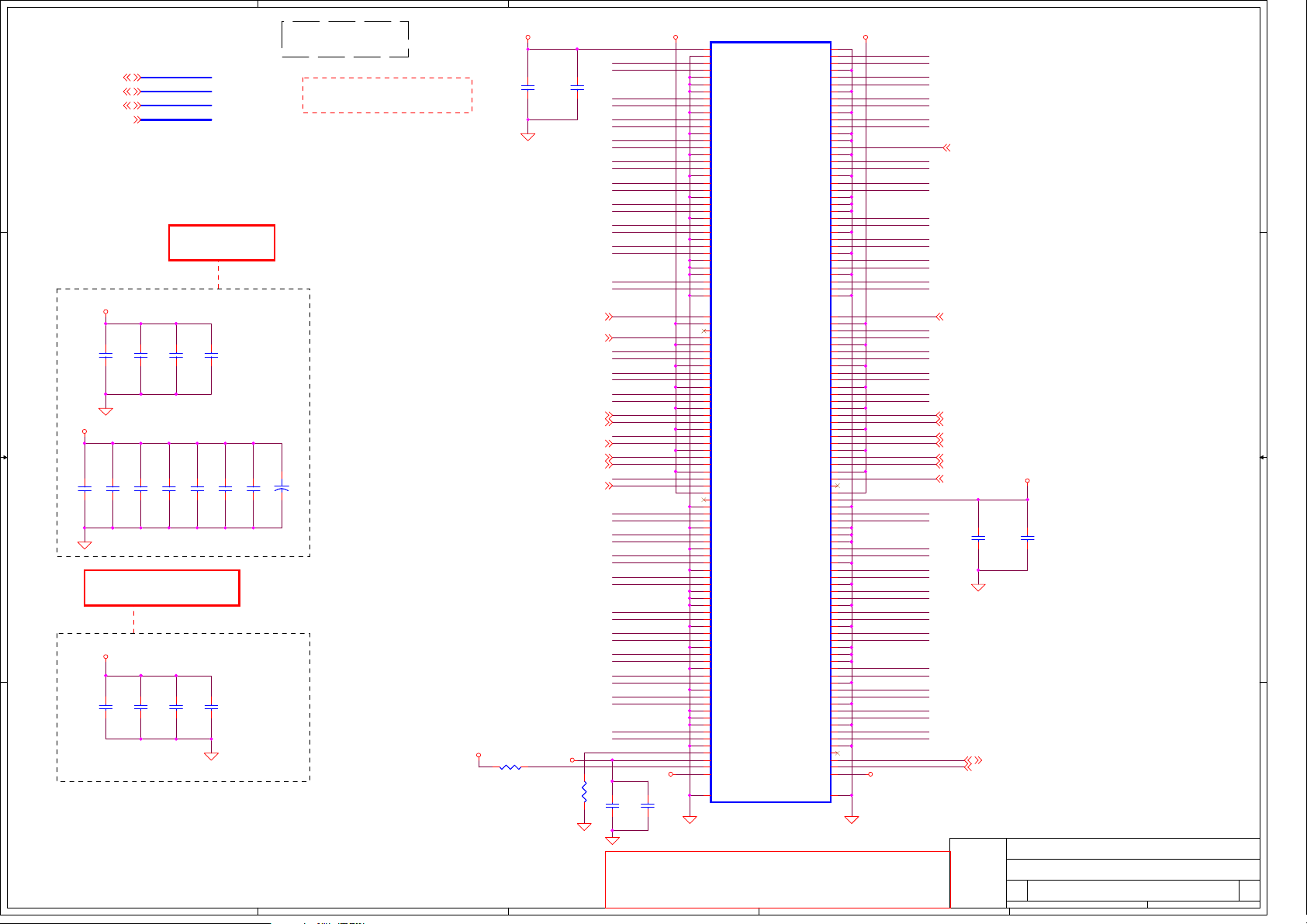

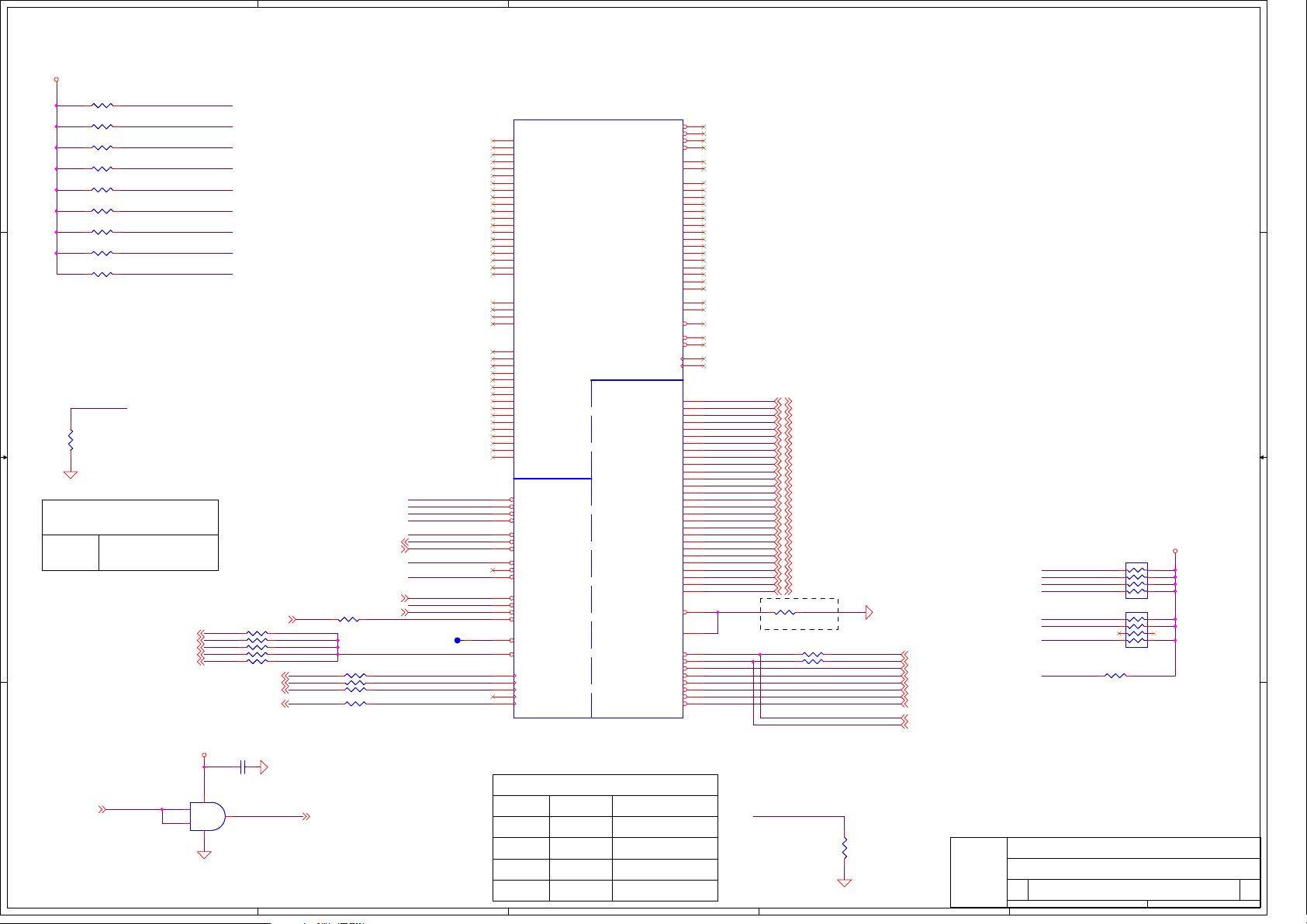

COMPAL LA-6591P Schematics

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Cover Sheet

1 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Cover Sheet

1 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Cover Sheet

1 66Monday, January 10, 2011

Compal Electronics, Inc.

BOM P/N :

PCB NO :

COMPAL CONFIDENTIAL

MODEL NAME :

E3 MACALLAN 14" UMA/ATG

rPGA Sandy Bridge +

FCBGA PCH Cougar Point-M

REV : 1.0(A00)

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

@ : Nopop Component

PAL50/52

LA-6591P (DA80000JV10)

LA-6593P HF (DA80000MB10)

43192831L01

2011-1-6

1@

2@

MB Type

TPM EN/ TCM DIS

TPM DIS/ TCM EN

BOM P/N

TPM DIS/ TCM DIS

GPIO MAP:{Macallan} GPIO Map 10102010.xlsx

3@

4@

2@

3@

1@

2@

ATG TPM EN/ TCM DIS

ATG TPM DIS/ TCM EN

ATG TPM DIS/ TCM DIS 2@

3@

3@

4@

43192831L01

43192831L02

43192831L11

43192831L12

TPM EN/ TCM DIS HF 1@ 3@4319BP31L01

CONN@ : ME controll and stuff by default

7@

7@

7@

7@

7@

7@

8@

43192831L04

43192831L13

Part Number Description

DA80000JV10

PCB 0FD LA-6591P REV0 M/B UMA

MB PCB17@

Part Number Description

DA80000JV10

PCB 0FD LA-6591P REV0 M/B UMA

MB PCB17@

Part Number Description

DA80000MB10

PCB 0FD LA-6593P REV0 M/B UMA HF

MB PCB28@

Part Number Description

DA80000MB10

PCB 0FD LA-6593P REV0 M/B UMA HF

MB PCB28@

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

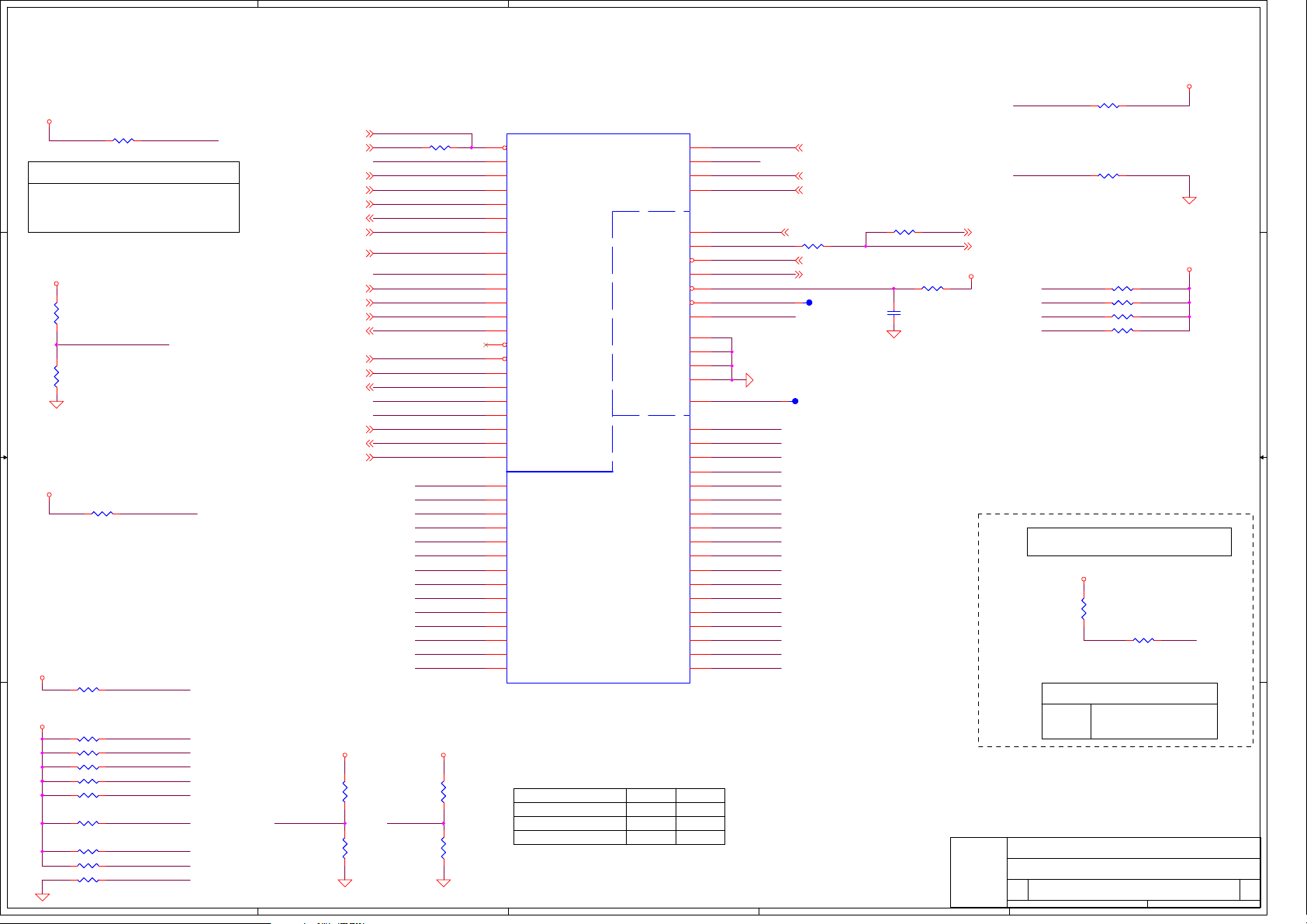

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

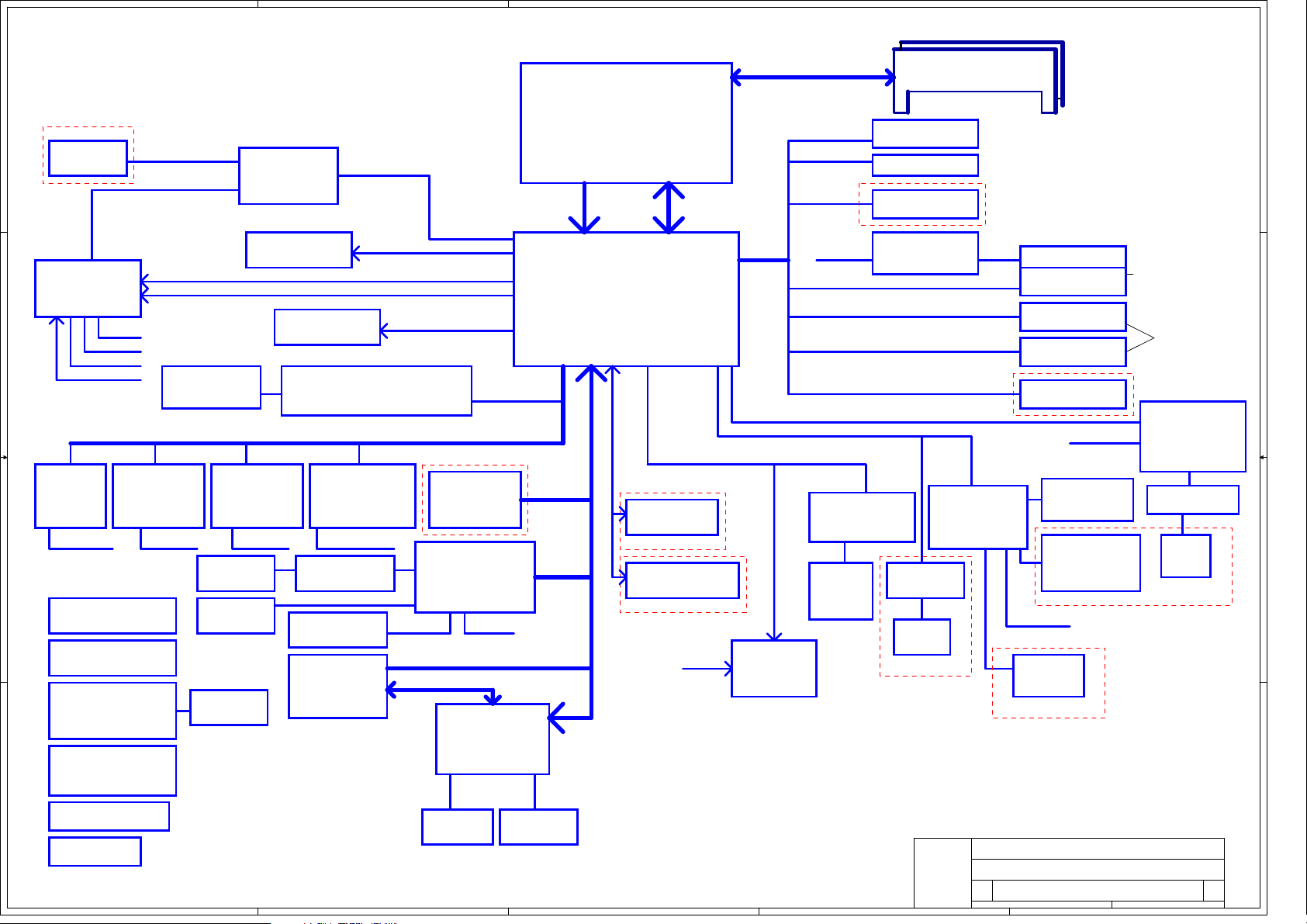

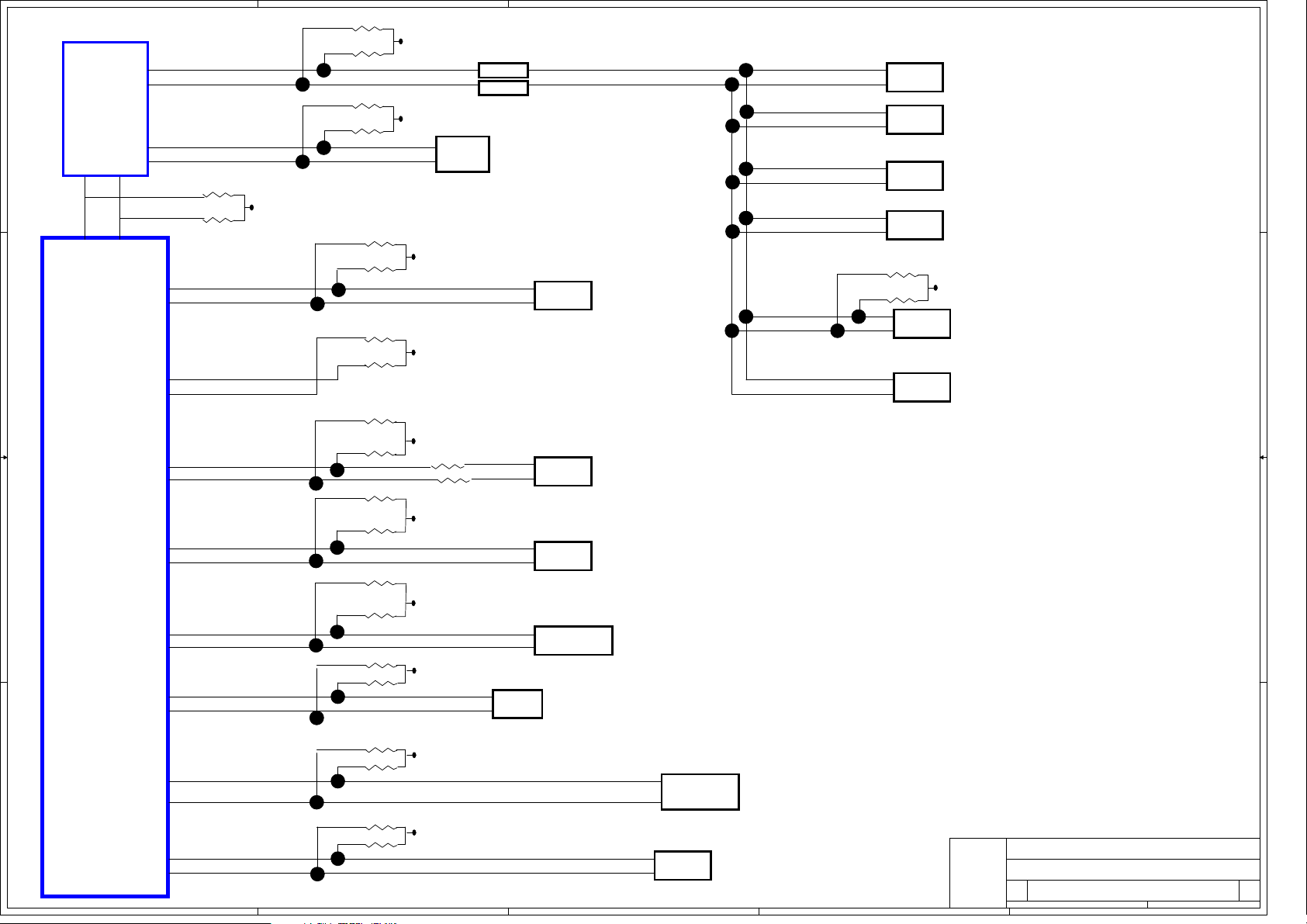

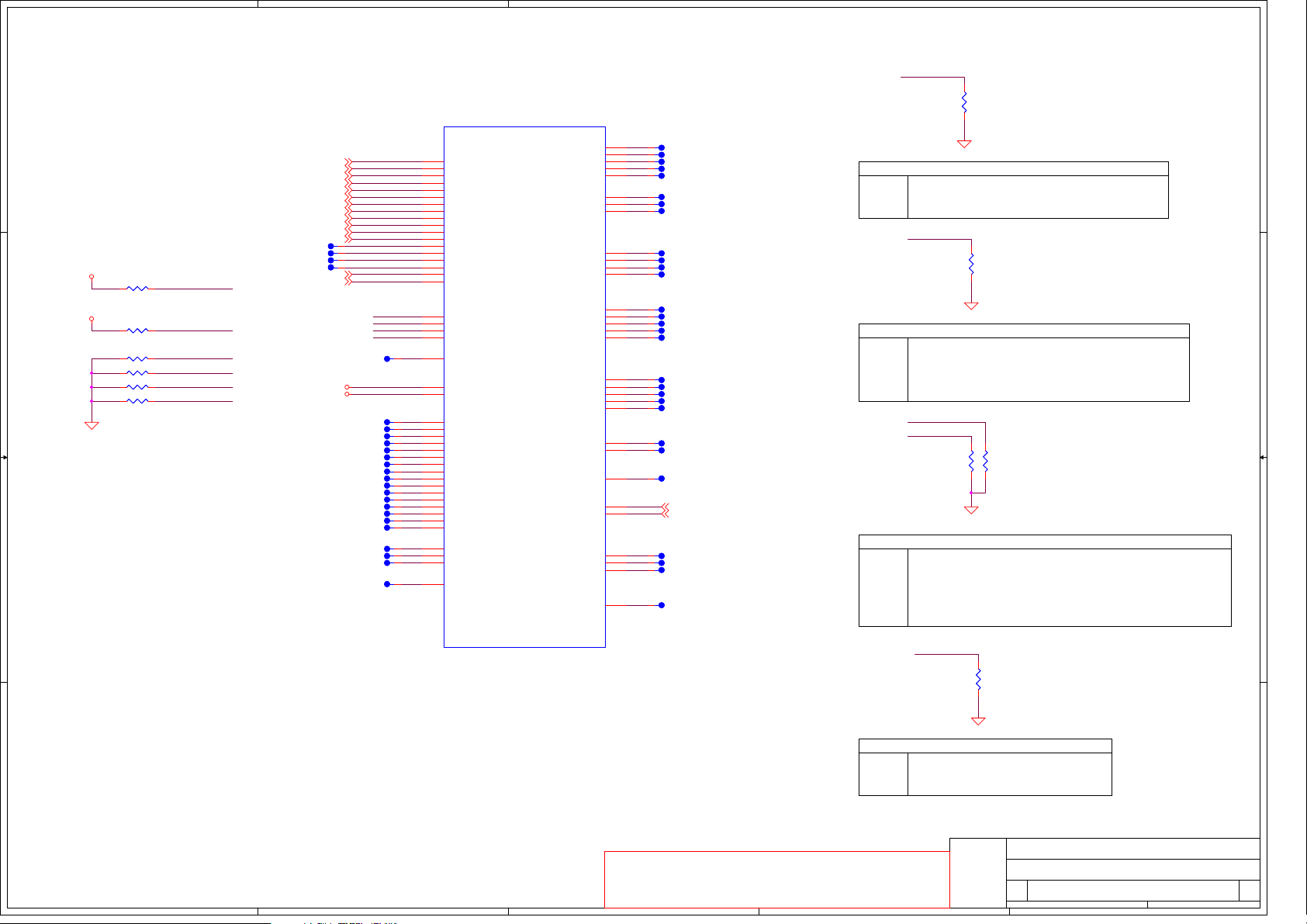

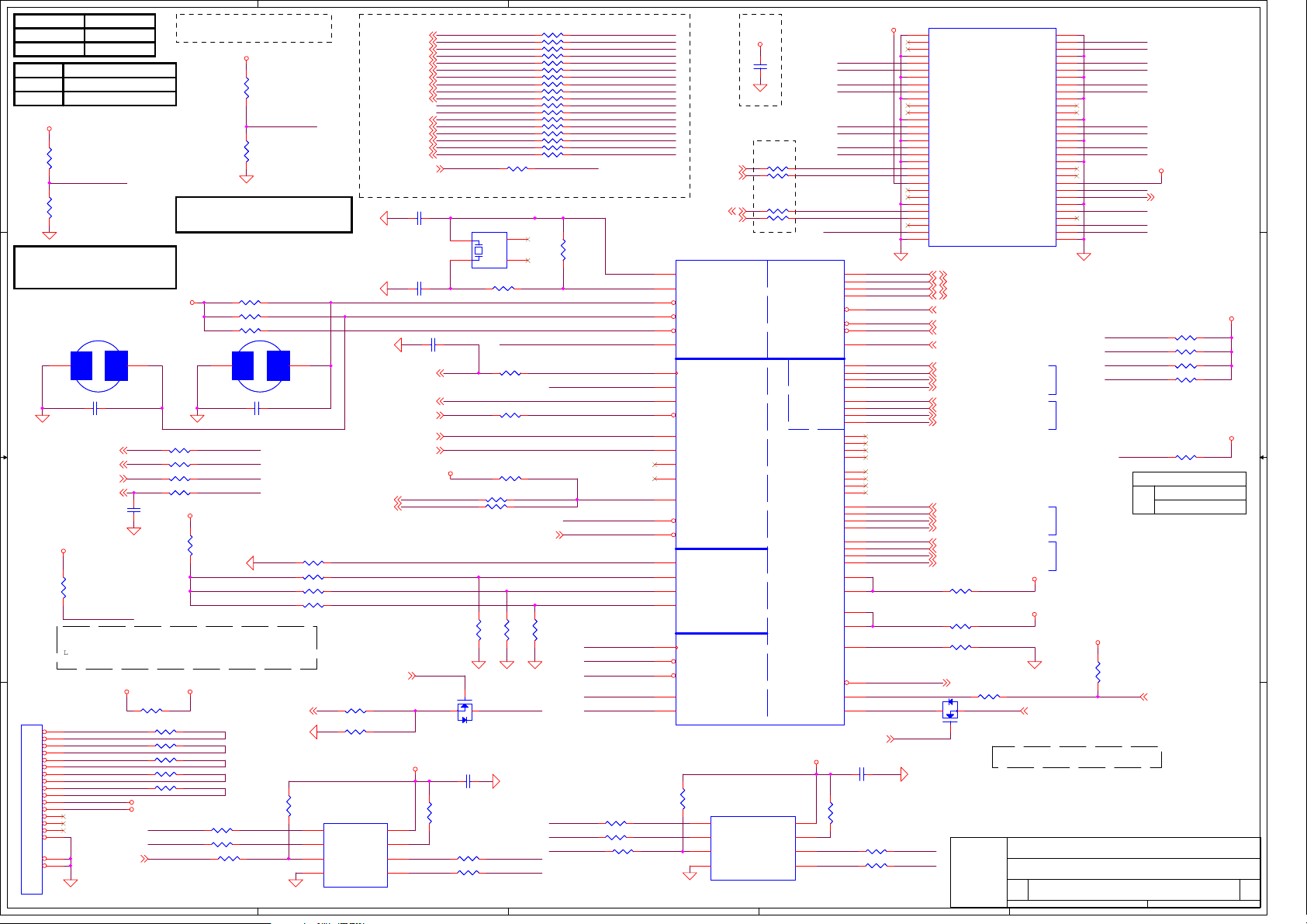

UMA Block Diagram

2 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

UMA Block Diagram

2 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

UMA Block Diagram

2 66Monday, January 10, 2011

Compal Electronics, Inc.

Compal confidential Model: PAL50/52

DELL CONFIDENTIAL/PROPRIETARY

Block Diagram

USB[8,9]

SATA5

DOCK LAN

DAI

DOCKING PORT

VGA

VGA

LVDS

PI3V712-AZLE

Video Switch

CRT CONN

1066/1333MHz

PAGE 40

PAGE 35

PAGE 14

PAGE 14

PAGE 33,34

PAGE 33

PAGE 41

PAGE 42

PAGE 43 PAGE 43

PAGE 29

PAGE 7

PAGE 14

PAGE 22

PAGE 44

PAGE 45

PAGE 28

PAGE 28

PAGE 30

PAGE 30

PAGE 32

PAGE 32

PAGE 38

PAGE 38

PAGE 39

PAGE 39

PAGE 43

PAGE 24

PAGE 12,13

USB5USB4

100MHz

33MHz

W25Q16BVSSIG

64M 4K sector

100MHz

PCI Express BUS

on IO board

USB Port

USB Port

USB Port

on IO board

PAGE 6-11

PAGE 14-21

On IO board

PCIE4

PAGE 24

PAGE 26

PAGE 35

PAGE 34PAGE 36PAGE 36PAGE 36PAGE 37

PAGE 33

PAGE 33

PAGE 23

PAGE 22

LVDS CONN

PCI Express BUS

PCIE x1

MDC

HD Audio I/F

WWAN/UWB

HeadPhone &

MIC Jack

RJ45

S-ATA 0/1 6GB/s, S-ATA 2/3/4/5 3GB/s

1/2 Mini Card

WiFi ON/OFF &

Power ON/OFF SW

GUARDIAN III

EMC4022

Thermal

PCH XDP Port

CPU XDP Port

DC/DC Interface

Memory BUS (DDR3)

LED

BANK 0, 1, 2, 3, 4 ,5 ,6 ,7

DDRIII-DIMM X2

Touch Screen

KB CONNTP CONN

LPC BUS

1/2 Mini Card

BCM5882

USH

Smart Card

Lane x 8

FDI

RFID

W25X64ZE

16M 4K sector

HDD

SATA Repeater

MAX4951BE

USB7

E-Module

Dig.

MIC

Trough eDP Cable

INT.Speaker

ECE5028

PCIE1PCIE3

TPM1.2

China TPM1.2

Lane x 4

USB6

PCIE5

PWM FAN

92HD90B2

HDA Codec

USB10

Trough eDP Cable

USB Port

Camera

USB

RJ11

LAN SWITCH

PI3L720

82579LM

Intel Lewisville

SATA Repeater

MAX4951BE

PCIE2

TDA8034HN

SSX44B

SATA

Flash

E-SATA

SATA

EXPRESS

Card

BT

Option

SDXC/MMC/MS

OZ600FJ0LN

Card reader

SPI

2560

2560

2062

To Docking side

on IO board

SMSC SIO

rPGA CPU

INTEL

DMI2

Sandy Bridge

BGA

COUGAR POINT-M

988 pins

4MB (Socket 988B)

BC BUS

Fingerprint

CONN

DAI

DOCK LAN

FP_USB

SMSC KBC

MEC5055

Full Mini Card

WLAN

HDMI CONN

DPC

DPD

DPB

For MB/DOCK

VGA

PAGE 31

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

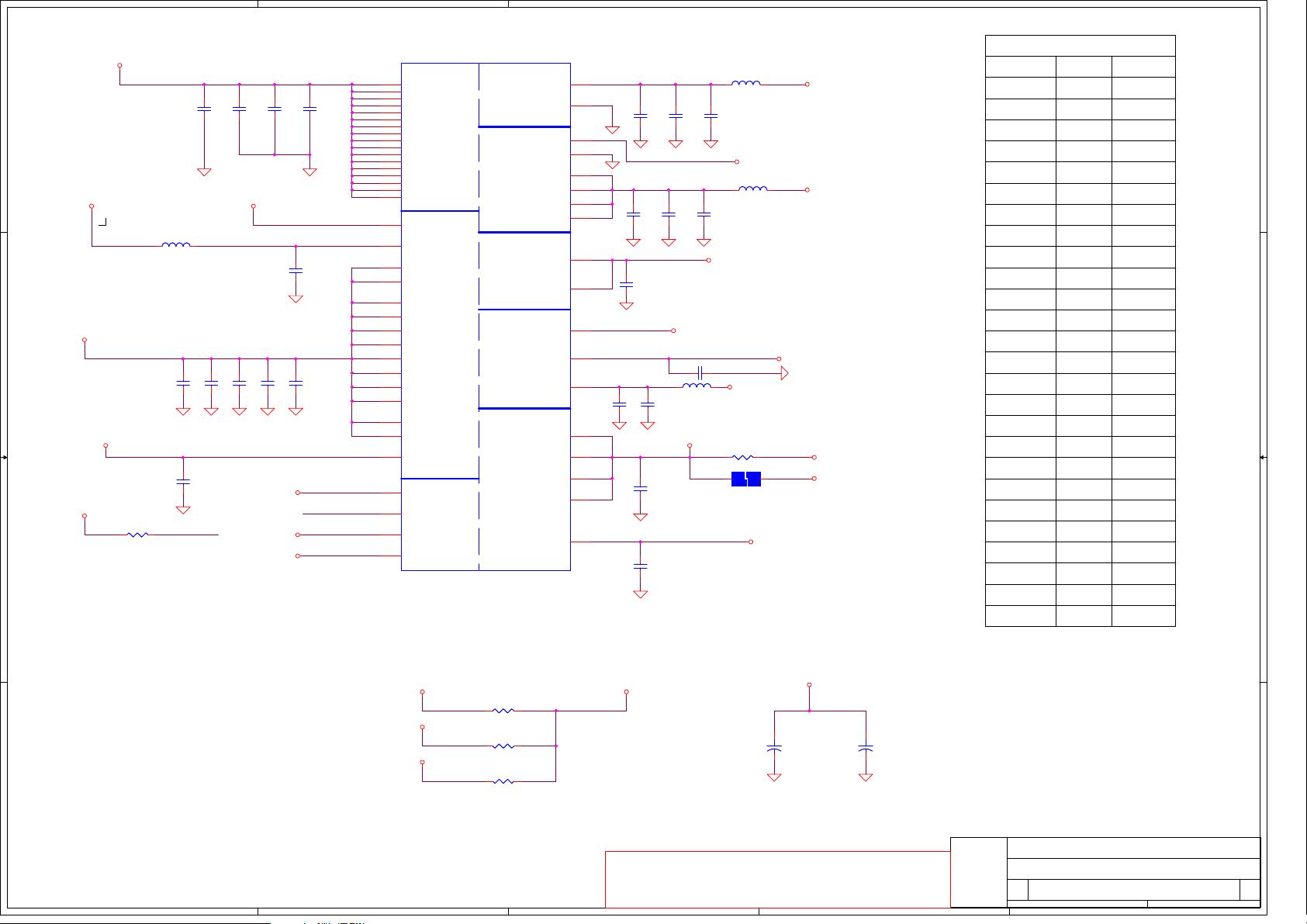

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

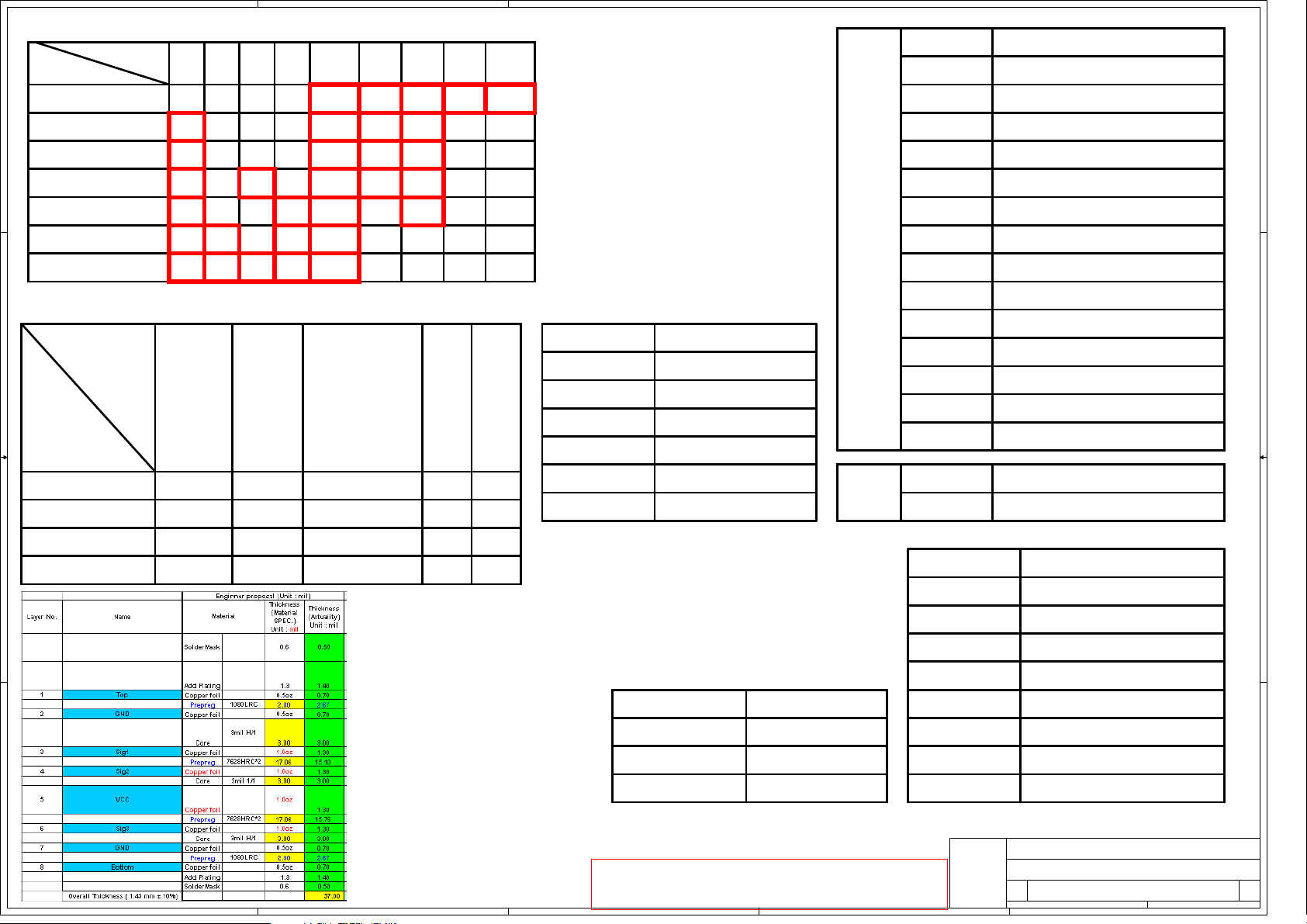

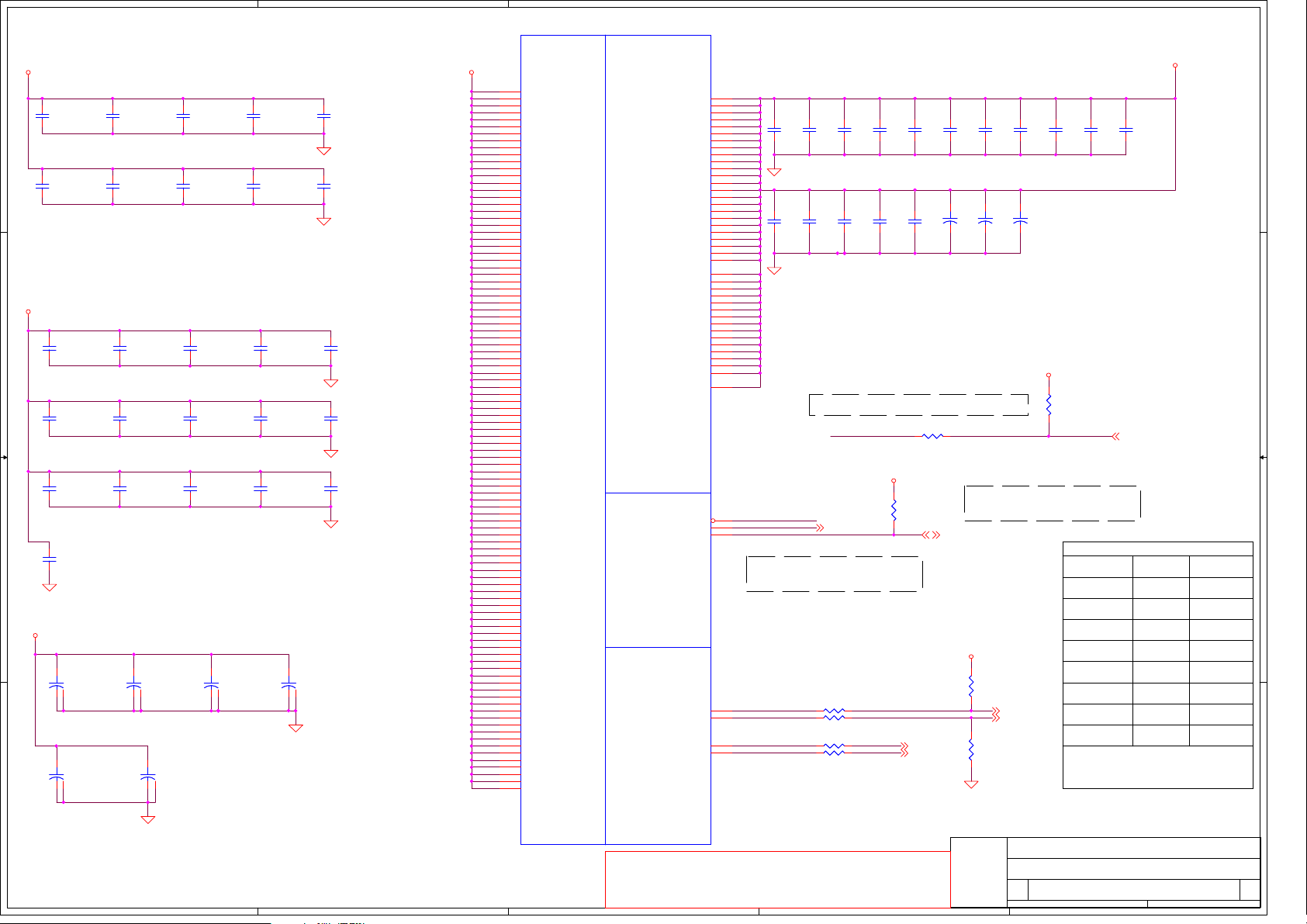

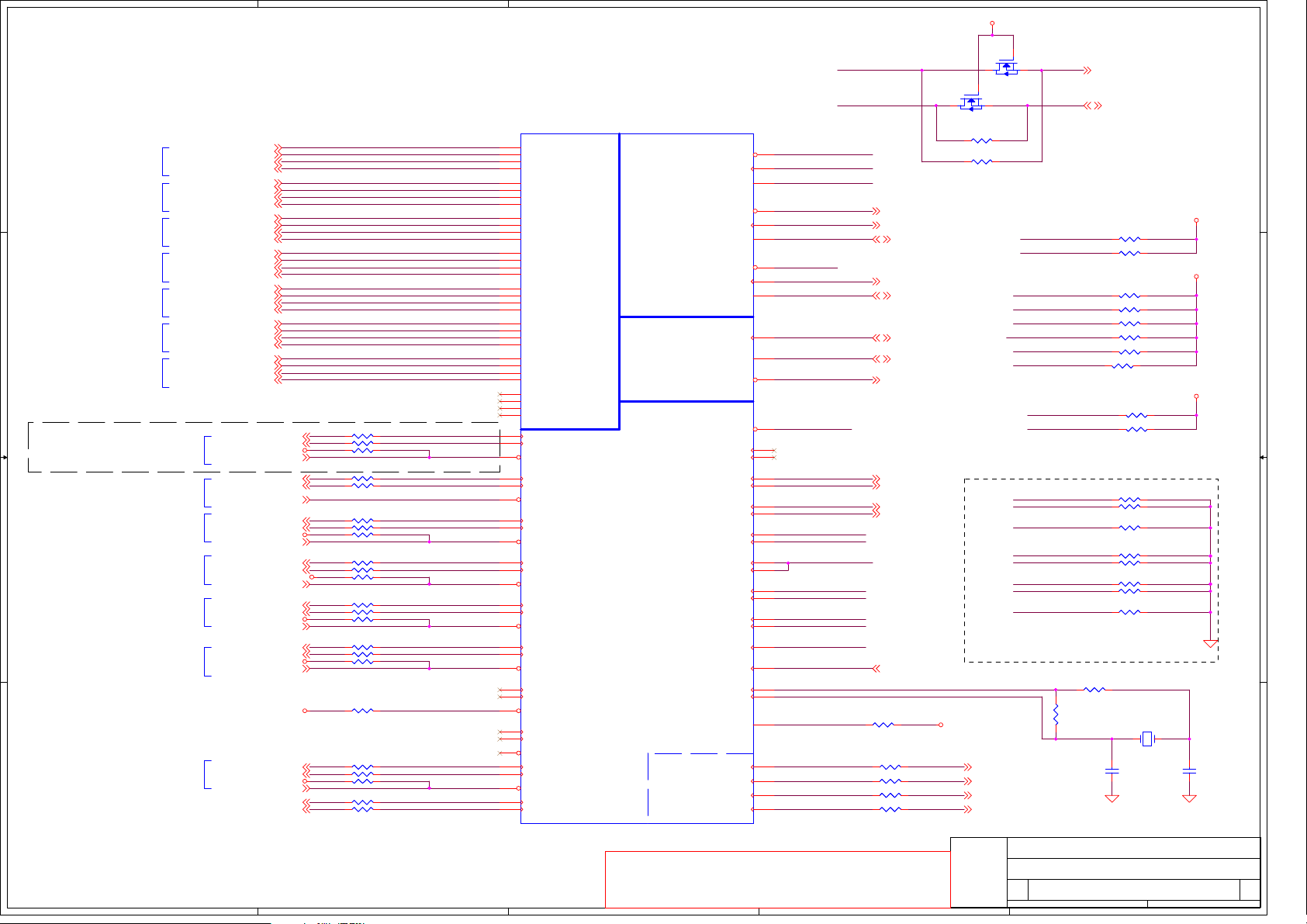

Index and Config.

3 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Index and Config.

3 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Index and Config.

3 66Monday, January 10, 2011

Compal Electronics, Inc.

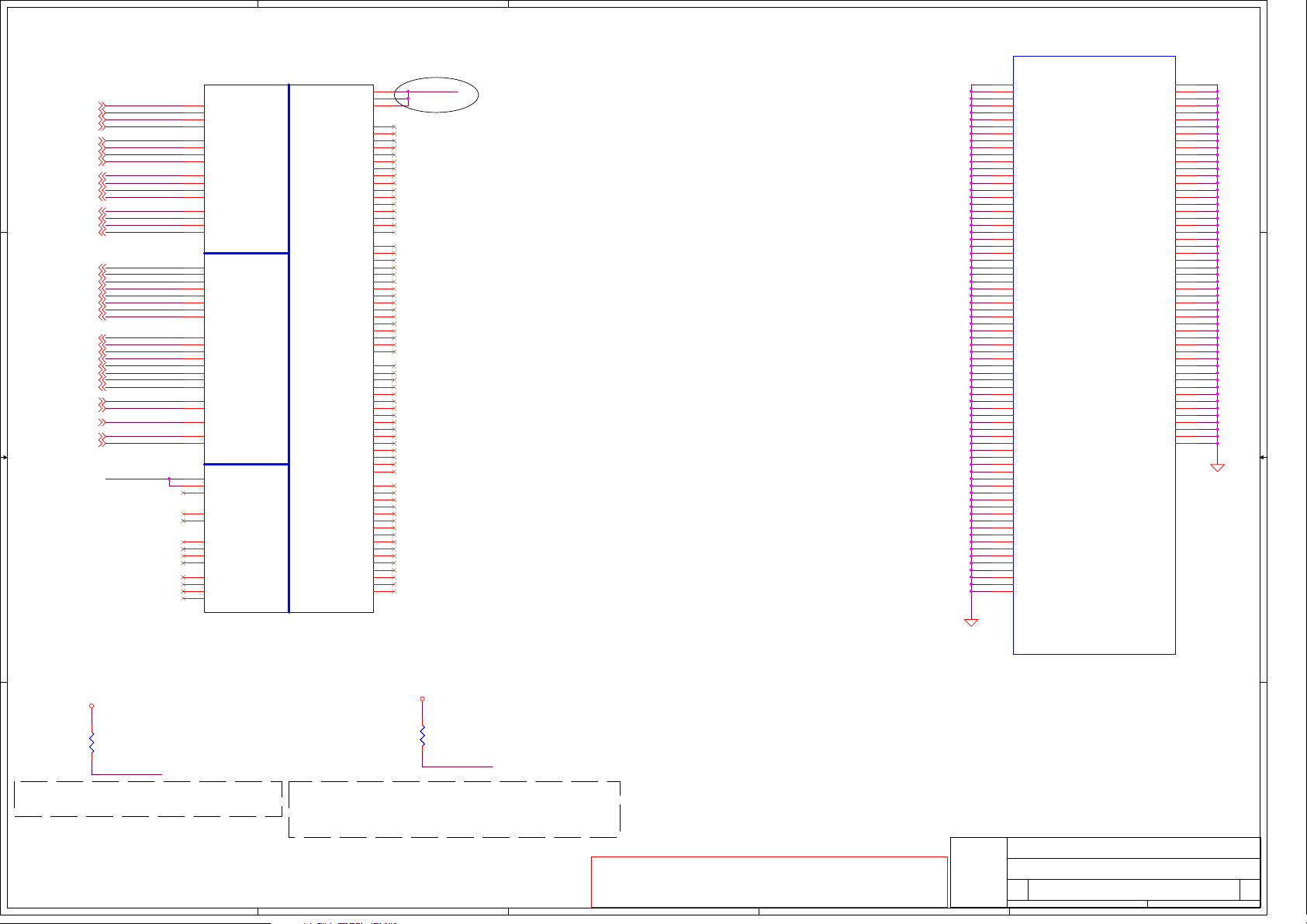

PM TABLE

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

MINI CARD-2 WLAN

PCI EXPRESS

Lane 1

DESTINATION

Lane 2

Lane 3

Lane 4

MINI CARD-1 WWAN

POWER STATES

Lane 5

Lane 6

Express card

MMI

+3.3V_M +3.3V_M

(M-OFF)

ON

ON

ON

ON

OFF

OFF

OFFOFF

+3.3V_SUS

+5V_ALW

+5V_RUN

+3.3V_ALW_PCH

+1.5V_MEM

S0

S3

S5 S4/AC don't exist

ON

power

plane

S5 S4/AC

State

OFFON

ON

ON

ON ON

OFF

OFF

OFF

OFFOFF

+15V_ALW

+3.3V_RTC_LDO

+1.05V_M

E3 Module Bay (USB3)

WLAN

WWAN

DOCKING8

9

USH->BIO

10 Express card

11

2

3

1

4

USB PORT#

0

DESTINATION

6

5

7

DOCKING

PCH

Lane 7

Lane 8 None

10/100/1G LOM

12

13

+1.05V_M

+1.8V_RUN

+1.05V_RUN_VTT

+3.3V_RUN

+0.75V_DDR_VTT

+1.5V_RUN

+VCC_CORE

+1.05V_RUN

1/2vMINI CARD-3 PCIE

HDD

NA

ODD/ E3 Module Bay

SATA

SATA 0

DESTINATION

NA

SATA 1

SATA 2

SATA 3

SATA 4

SATA 5

ESATA

Dock

0

1

BIO

NA

USH

need to update Power Status and PM Table

JESA1 (Right Side ESATA)

JUSB1 (Ext Left Side )

JMINI3(Flash)

JUSB2 (Right side 1)

JUSB3 (Right side 2)

Camera

LCD Touch

Bluetooth

Dock DP port 2

UMA DP/HDMI Port

Port C

Connetion

Port D

Port B

Dock DP port 1

MB HDMI Conn

OFF

OFF

OFF

LOW

LOW

OFF

OFF

S0 (Full ON) / M0

SLP

S3#

SLP

S5#

HIGH

Signal

State

SLP

S4#

HIGH HIGH

ALWAYS

PLANE

ON

M

PLANE

ON

SUS

PLANE

RUN

PLANE

CLOCKS

ON ON ON

S3 (Suspend to RAM) / M3 LOW HIGH HIGH ON ON ON OFF

S4 (Suspend to DISK) / M3 ON ON OFF

SLP

A#

HIGH

HIGH

LOW HIGH HIGH

S5 (SOFT OFF) / M3 ON ON OFFL

OW HIGHLOW

S3 (Suspend to RAM) / M-OFF

S5 (SOFT OFF) / M-OFF

LOW HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

S4 (Suspend to DISK) / M-OFF HIGH

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

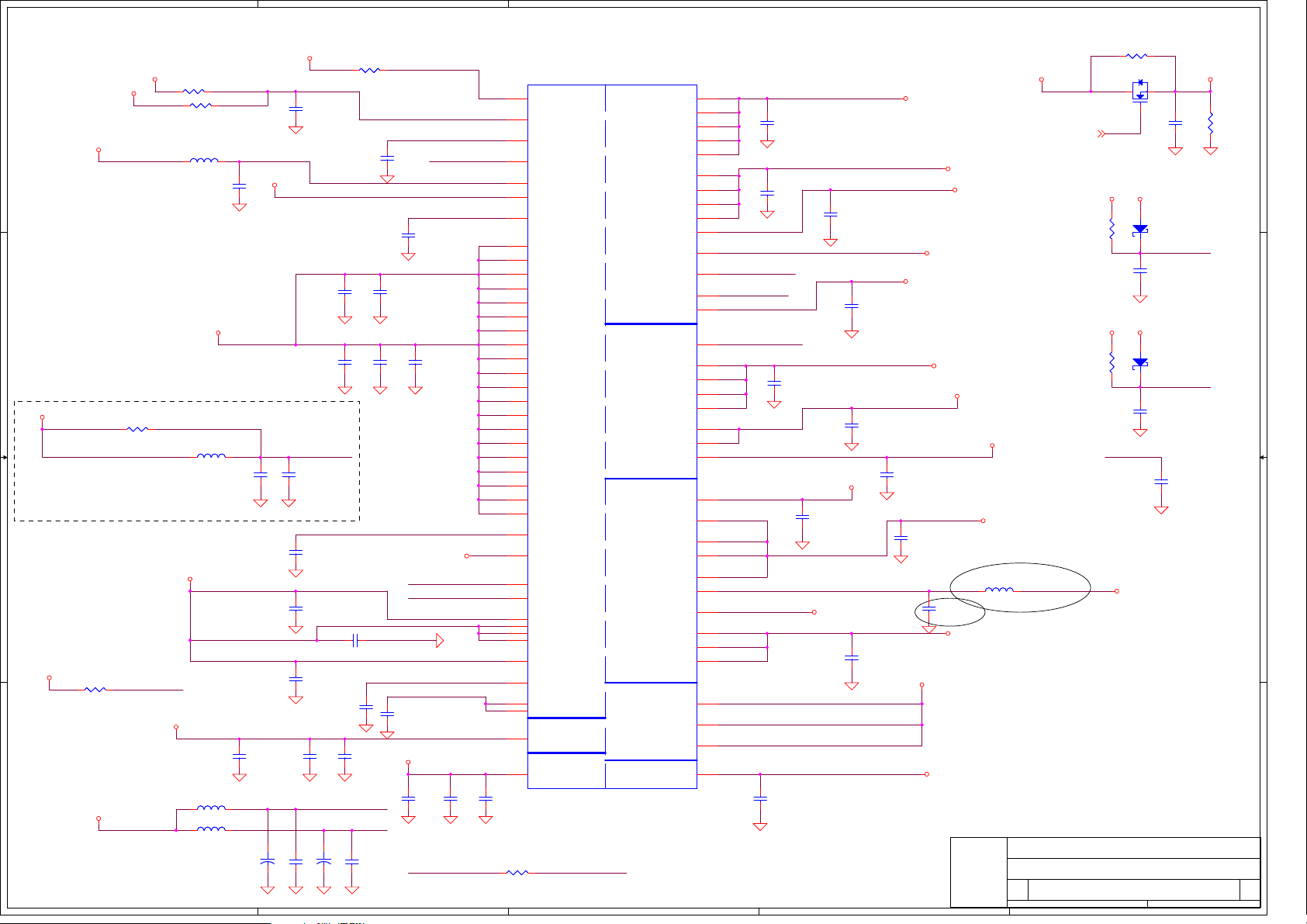

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

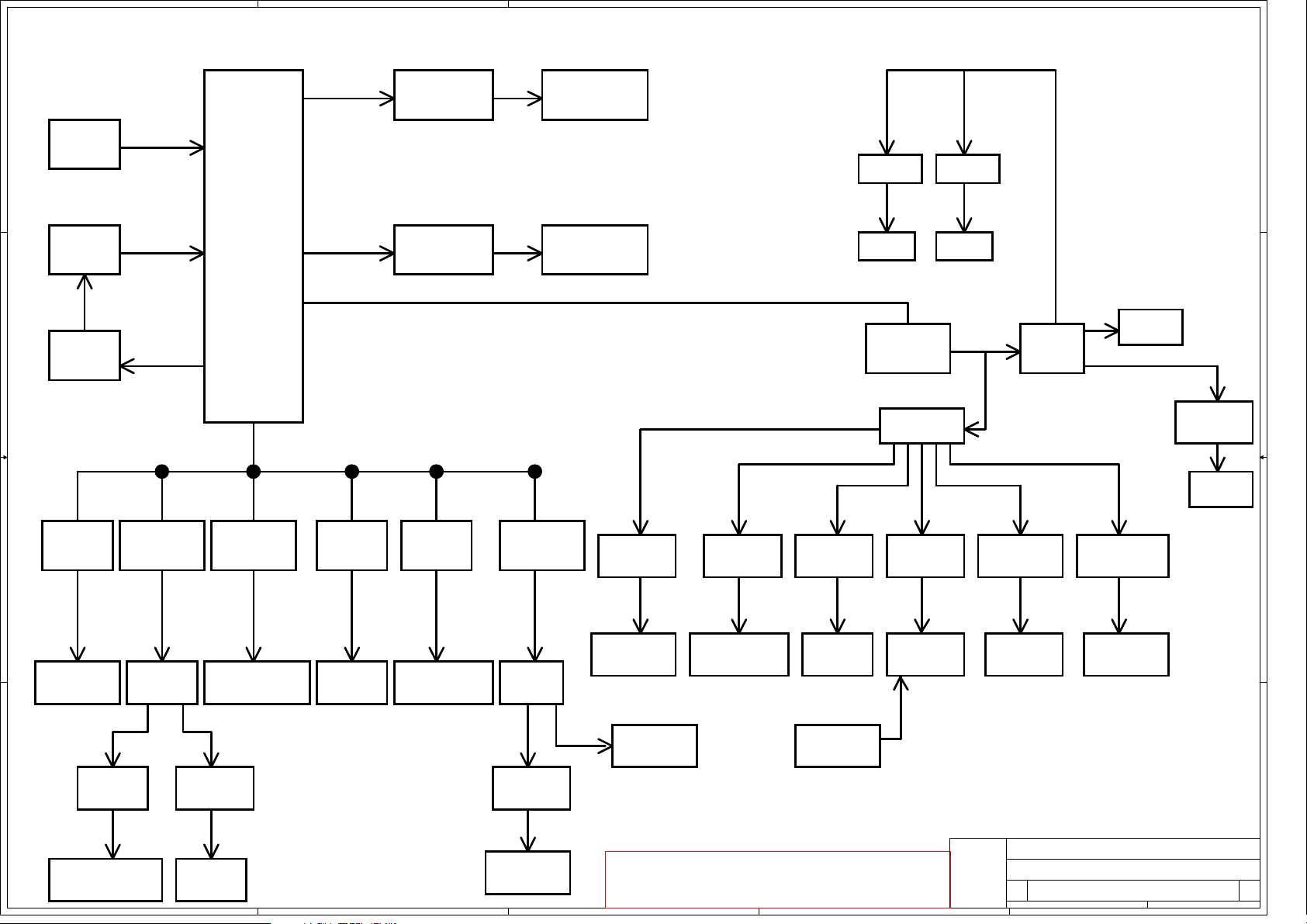

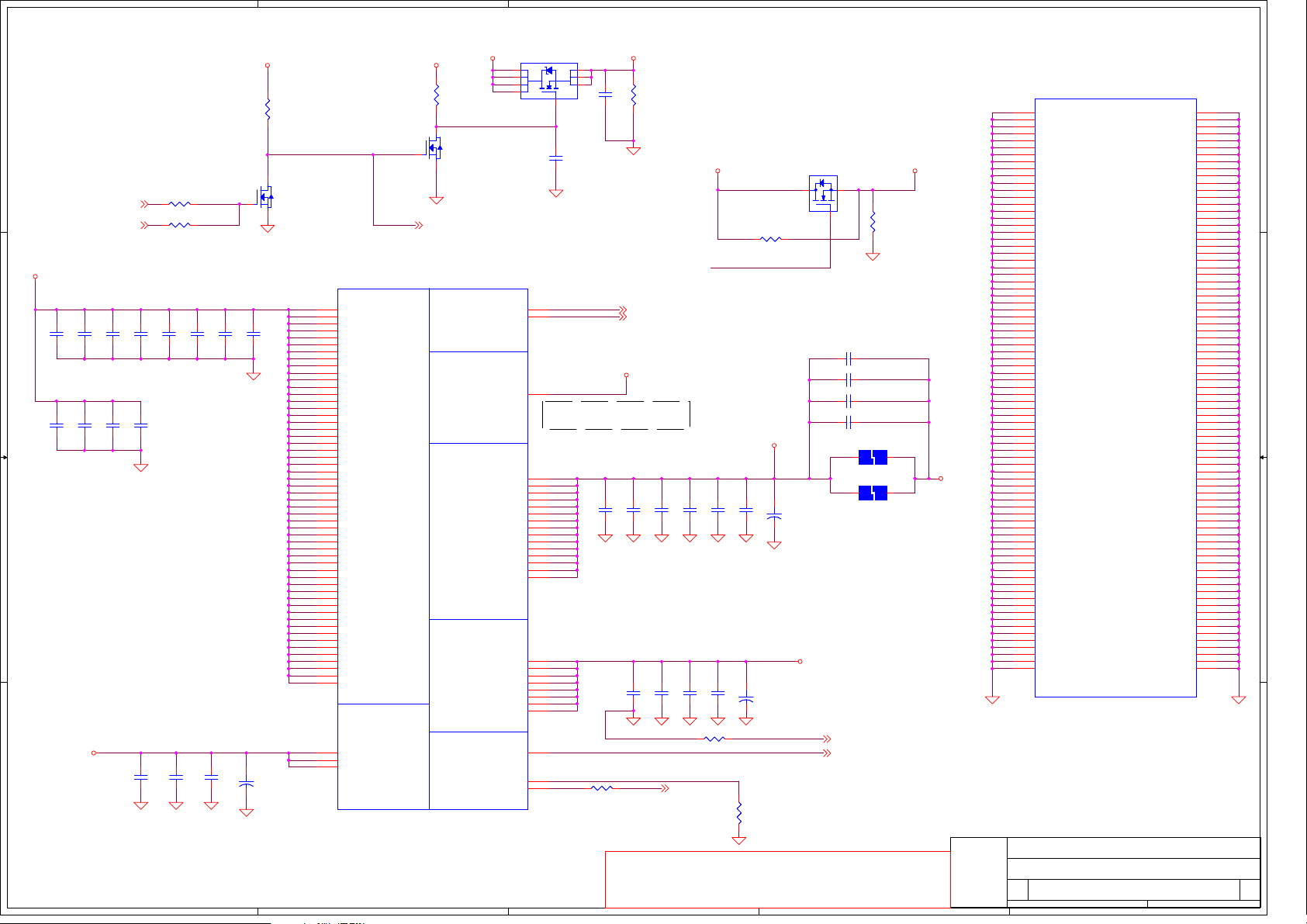

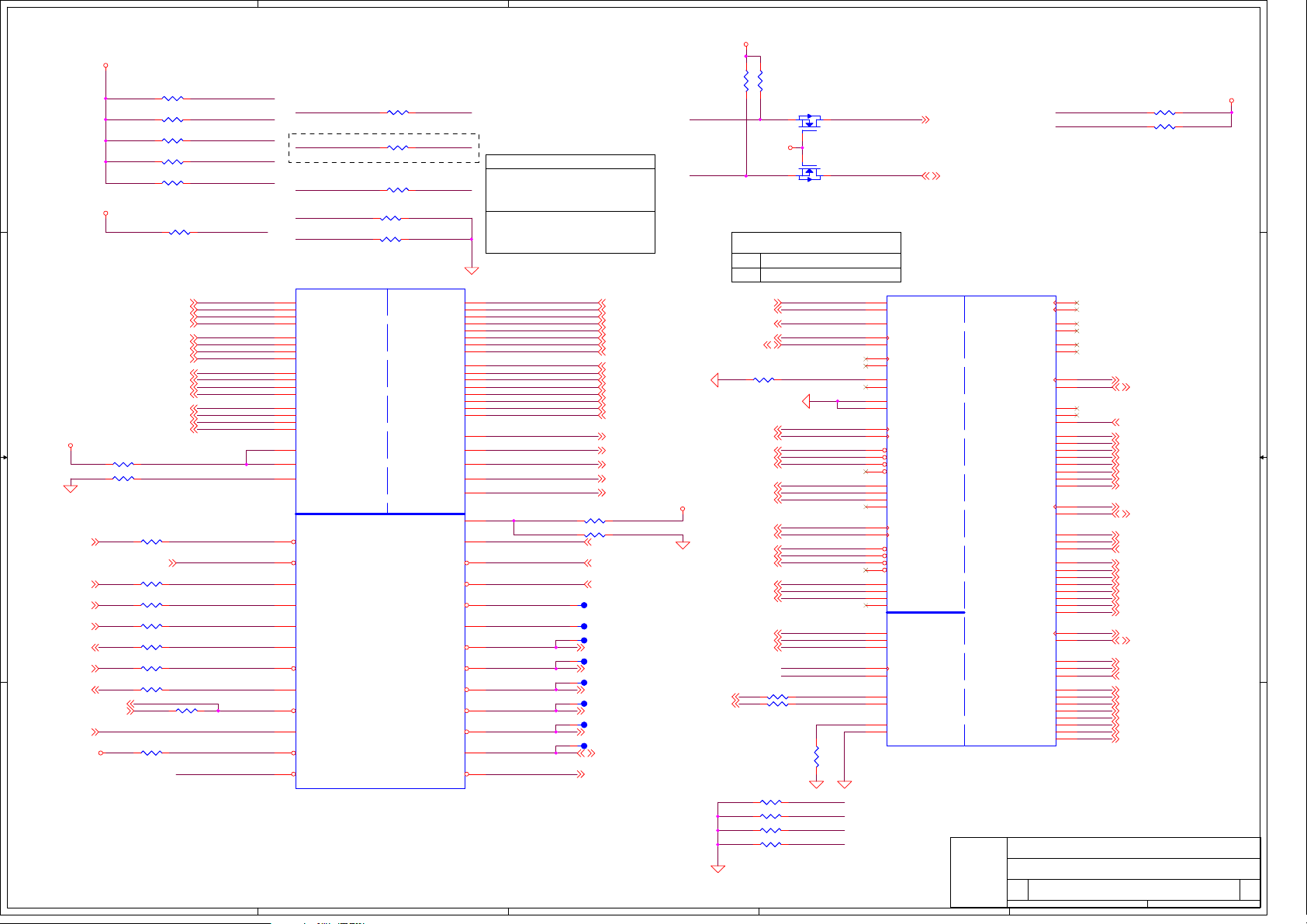

Power Rail

4 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Power Rail

4 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Power Rail

4 66Monday, January 10, 2011

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Pop option

+1.0V_LAN

BATTERY

+PWR_SRC

ADAPTER

FDC654P

+BL_PWR_SRC

EN_INVPWR

SI3456BDVSI3456BDV

HDDC_EN

+5V_MOD

MODC_EN

CHARGER

+3.3V_ALW

SN0608098

+15V_ALW

+5V_ALW

ALWON

SI3456

+3.3V_LAN+3.3V_SUS

RUN_ON

NTMS4920

RUN_ON

+3.3V_RUN

+5V_HDD

Q21

(Q30)(Q27)

(PU2)

(Q34) (Q55)

+5V_RUN

SI4164DY

(Q50)

+VCC_CORE

MAX17411

(PU9)

+1.5V_MEM +0.75V_DDR_VTT

DDR_ON

0.75V_VR_EN

RT8209BGQW

(PU3)

+1.05V_RUN_VTT +1.05V_M

M_ON

SUS_ON

S13456

(Q54)

1.05V_0.8V_PWROK

RT9026GFP

(PU5) SI3456

+3.3V_M

(Q58)

M_ON

+3.3V_ALW_PCH

PCH_ALW_ON

SI3456

(Q49)

+1.5V_RUN

RUN_ON

NTGS4141N

(Q59)

AUX_ON

+1.8V_RUN

RUN_ON

(PU4)

+3.3V_WLAN

SI3456

(Q38)

AUX_EN_WOWL

SI4164

(Q63)

+1.05V_RUN

(PU7)

RUN_ON

+3.3V_M

Pop option

CPU_VTT_ON

AO4728

(QC3)

+1.5V_CPU_VDDQ

CPU1.5V_S3_GATE

TPS51311

SN1003055

(PU16)

SN1003055RUWR

ISL95870AH

1.05V_VTTPWRGD

(PU13)

+VCC_SA

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

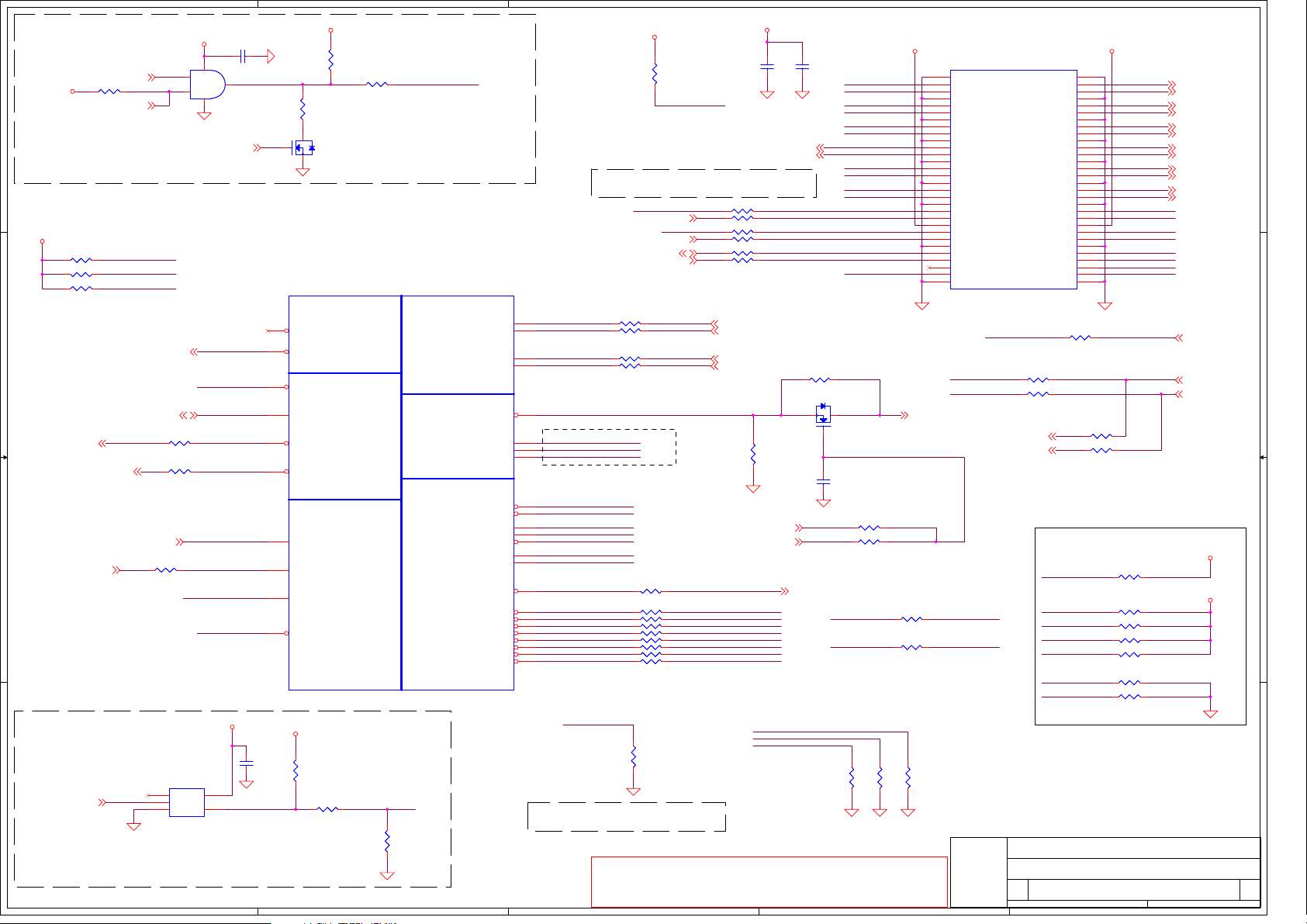

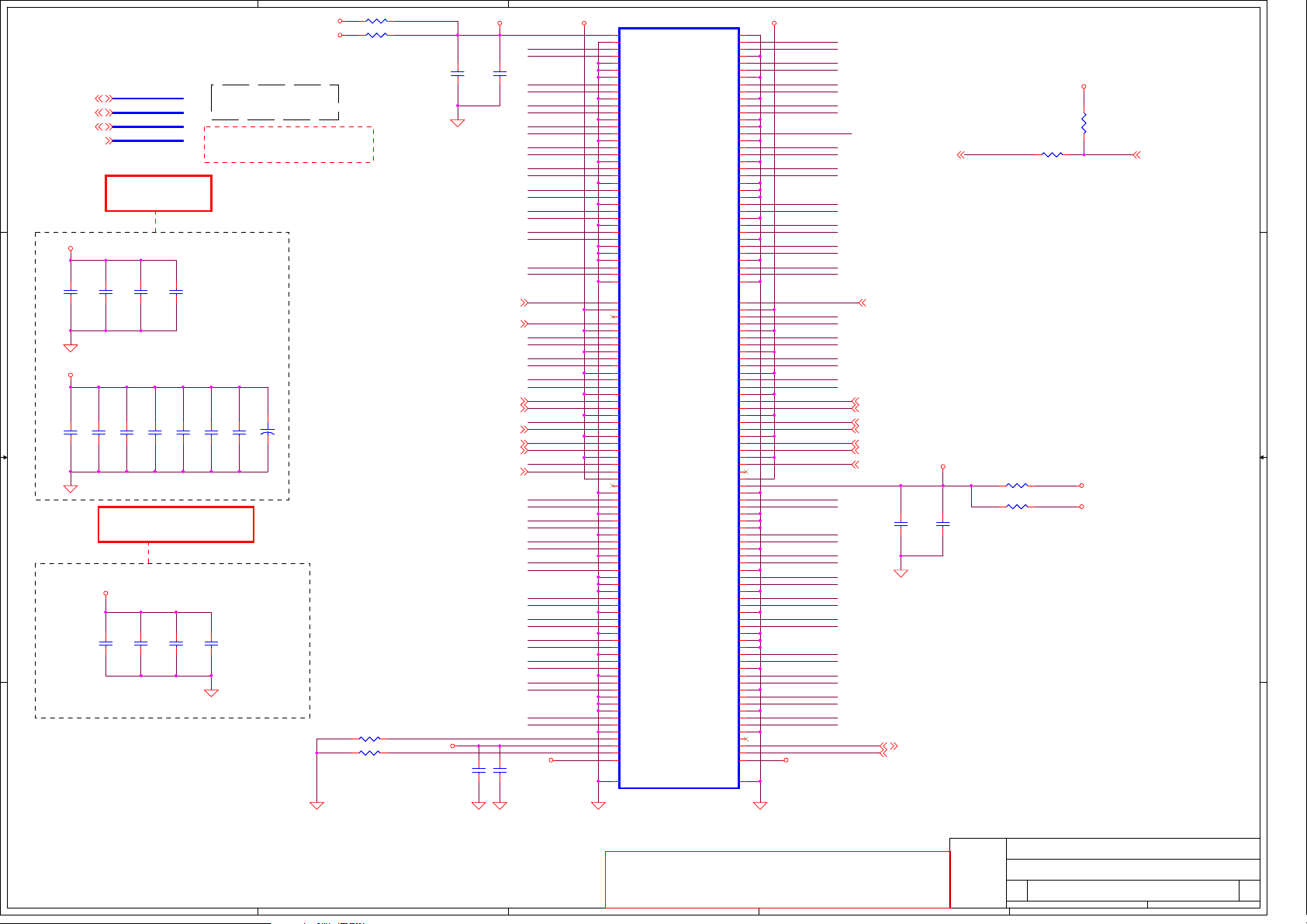

SMBUS TOPOLOGY

5 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

SMBUS TOPOLOGY

5 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

SMBUS TOPOLOGY

5 66Monday, January 10, 2011

Compal Electronics, Inc.

MEC 5055

MEM_SMBDATA

MEM_SMBCLK

KBC

C9

H14

+3.3V_ALW_PCH

2.2K

2.2K

200

DIMMA

SMBUS Address [A4]

202

DIMMB

SMBUS Address [A0]

200

202

C8

G12

+3.3V_LAN

2.2K

2.2K

LAN_SMBCLK

LAN_SMBDATA

+3.3V_ALW

129

127

SMBUS Address

2.2K

DOCK_SMB_CLK

DOCK_SMB_DAT

DOCKING

2.2K

B4

A3

1A

1A

A4

B5

2.2K

2.2K

LCD_SMBCLK

LCD_SMDATA

1B

1B

1C

1C

B59

A56

+3.3V_ALW

2.2K

2.2K

100 ohm

100 ohm

BATTERY

CONN

7

6

SMBUS Address [0x16]

PBAT_SMBCLK

PBAT_SMBDAT

3A

1E

1E

2B

2B

B50

1G

1G

A47

2A

2A

B7

A7

+3.3V_ALW

2.2K

2.2K

2D

2D

30

29

BAY_SMBDAT

BAY_SMBCLK

E3 Module Bay

SMBUS Address [0xd2]

A49

B52

CARD_SMBCLK

CARD_SMBDAT

+3.3V_SUS

2.2K

2.2K

SMBUS Address [C8]

LOM

CHARGER_SMBCLK

CHARGER_SMBDAT

Charger

SMBUS Address [0x12]

SML1_SMBDATA

PCH

SML1_SMBCLK

E14M16

A50

B53

B49

B48

3A

B6A5

+3.3V_ALW_PCH

2.2K

2.2K

USH

+3.3V_ALW

USH_SMBCLK

USH_SMBDAT

+3.3V_ALW

2.2K

2.2K

53

51

SMBUS Address [TBD]

XDP1

SMBUS Address [TBD]

XDP2

53

51

8

9

DAI_SMBCLK

DAI_SMBDAT

A/D,D/A

converter

SMBUS Address [0x30]

+3.3V_RUN

2.2K

2.2K

M9

L9

SMBUS Address [0xa4]

10

9

31

28

G Sensor

SMBUS Address [3B]

2N7002

2N7002

+3.3V_RUN

2.2K

2.2K

14

13

2.2K

2.2K

Express card

7

8

SMBUS Address [TBD]

APR_EC: 0x48

SPR_EC: 0x70

MSLICE_EC: 0x72

USB: 0x59

AUDIO: 0x34

SLICE_BATTERY: 0x17

SLICE_CHARGER: 0x13

SMBUS Address [0x9a]

@

@

+3.3V_ALW

WWAN

SMBUS Address [TBD]

32

30

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CTX_PRX_N0

DMI_CRX_PTX_N2

DMI_CTX_PRX_P2

DMI_CTX_PRX_P1

DMI_CRX_PTX_N0

DMI_CRX_PTX_P0

DMI_CRX_PTX_N3

DMI_CTX_PRX_N3

DMI_CRX_PTX_P3

DMI_CTX_PRX_P3

DMI_CTX_PRX_P0

DMI_CTX_PRX_N1

DMI_CRX_PTX_N1

DMI_CTX_PRX_N2

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N6

FDI_CTX_PRX_N5

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P5

FDI_CTX_PRX_P4

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC0

FDI_INT

FDI_LSYNC1

FDI_CTX_PRX_N0

PEG_COMP

PEG_COMP

EDP_COMP

EDP_COMP

+1.05V_RUN_VTT

+1.05V_RUN_VTT

DMI_CRX_PTX_P016

DMI_CRX_PTX_N316

DMI_CRX_PTX_P116

DMI_CRX_PTX_N116

DMI_CRX_PTX_P316

DMI_CRX_PTX_N216

DMI_CRX_PTX_P216

DMI_CRX_PTX_N016

DMI_CTX_PRX_N016

DMI_CTX_PRX_N116

DMI_CTX_PRX_N216

DMI_CTX_PRX_N316

DMI_CTX_PRX_P016

DMI_CTX_PRX_P116

DMI_CTX_PRX_P216

DMI_CTX_PRX_P316

FDI_CTX_PRX_N116

FDI_CTX_PRX_N016

FDI_CTX_PRX_N416

FDI_CTX_PRX_N316

FDI_CTX_PRX_N216

FDI_CTX_PRX_N716

FDI_CTX_PRX_N616

FDI_CTX_PRX_N516

FDI_CTX_PRX_P216

FDI_CTX_PRX_P116

FDI_CTX_PRX_P016

FDI_CTX_PRX_P516

FDI_CTX_PRX_P416

FDI_CTX_PRX_P316

FDI_FSYNC016

FDI_LSYNC016

FDI_CTX_PRX_P716

FDI_CTX_PRX_P616

FDI_LSYNC116

FDI_FSYNC116

FDI_INT16

Title

S

ize Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (1/6)

6 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (1/6)

6 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (1/6)

6 66Monday, January 10, 2011

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

PEG Compensation

PEG_ICOMPI and R COMPO signals sh ould be shorted a nd routed

with - max lengt h = 500 mils - t ypical impedance = 43 mohms

PEG_ICOMPO signa ls should be rou ted with - max le ngth = 500 mils

- typical impeda nce = 14.5 mohms

(1)PEG_RCOMPO (H22) use 4mil connect to PEG_ICOMPI, then use 4mil connect to RC2.

(2)PEG_ICOMPO use 12mil connect to RC2

(1) EDP_COMPIO use 4mil trace to RC1

(2) EDP_ICOMPO use 12mil to RC1

eDP_COMPIO and I COMPO signals sh ould be shorted n ear

balls and routed with typical im pedance <25 mohms

DP Compensation

RC1

24.9_0402_1%~D

RC1

24.9_0402_1%~D

12

VSS

JCPU1I

Sandy Bridge_rPGA_Rev1p0

VSS

JCPU1I

Sandy Bridge_rPGA_Rev1p0

VSS161

T35

VSS162

T34

VSS163

T33

VSS164

T32

VSS165

T31

VSS166

T30

VSS167

T29

VSS168

T28

VSS169

T27

VSS170

T26

VSS171

P9

VSS172

P8

VSS173

P6

VSS174

P5

VSS175

P3

VSS176

P2

VSS177

N35

VSS178

N34

VSS179

N33

VSS180

N32

VSS181

N31

VSS182

N30

VSS183

N29

VSS184

N28

VSS185

N27

VSS186

N26

VSS187

M34

VSS188

L33

VSS189

L30

VSS190

L27

VSS191

L9

VSS192

L8

VSS193

L6

VSS194

L5

VSS195

L4

VSS196

L3

VSS197

L2

VSS198

L1

VSS199

K35

VSS200

K32

VSS201

K29

VSS202

K26

VSS203

J34

VSS204

J31

VSS205

H33

VSS206

H30

VSS207

H27

VSS208

H24

VSS209

H21

VSS210

H18

VSS211

H15

VSS212

H13

VSS213

H10

VSS214

H9

VSS215

H8

VSS216

H7

VSS217

H6

VSS218

H5

VSS219

H4

VSS220

H3

VSS221

H2

VSS222

H1

VSS223

G35

VSS224

G32

VSS225

G29

VSS226

G26

VSS227

G23

VSS228

G20

VSS229

G17

VSS230

G11

VSS231

F34

VSS232

F31

VSS233

F29

VSS234

F22

VSS235

F19

VSS236

E30

VSS237

E27

VSS238

E24

VSS239

E21

VSS240

E18

VSS241

E15

VSS242

E13

VSS243

E10

VSS244

E9

VSS245

E8

VSS246

E7

VSS247

E6

VSS248

E5

VSS249

E4

VSS250

E3

VSS251

E2

VSS252

E1

VSS253

D35

VSS254

D32

VSS255

D29

VSS256

D26

VSS257

D20

VSS258

D17

VSS259

C34

VSS260

C31

VSS261

C28

VSS262

C27

VSS263

C25

VSS264

C23

VSS265

C10

VSS266

C1

VSS267

B22

VSS268

B19

VSS269

B17

VSS270

B15

VSS271

B13

VSS272

B11

VSS273

B9

VSS274

B8

VSS275

B7

VSS276

B5

VSS277

B3

VSS278

B2

VSS279

A35

VSS280

A32

VSS281

A29

VSS282

A26

VSS283

A23

VSS284

A20

VSS285

A3

RC2

24.9_0402_1%~D

RC2

24.9_0402_1%~D

12

PCI EXPRESS* - GRAPHICS

DMI

Intel(R) FDI

eDP

JCPU1A

Sandy Bridge_rPGA_Rev1p0

PCI EXPRESS* - GRAPHICS

DMI

Intel(R) FDI

eDP

JCPU1A

Sandy Bridge_rPGA_Rev1p0

DMI_RX#[0]

B27

DMI_RX#[1]

B25

DMI_RX#[2]

A25

DMI_RX#[3]

B24

DMI_RX[0]

B28

DMI_RX[1]

B26

DMI_RX[2]

A24

DMI_RX[3]

B23

DMI_TX#[0]

G21

DMI_TX#[1]

E22

DMI_TX#[2]

F21

DMI_TX#[3]

D21

DMI_TX[0]

G22

DMI_TX[1]

D22

DMI_TX[3]

C21

DMI_TX[2]

F20

FDI0_TX#[0]

A21

FDI0_TX#[1]

H19

FDI0_TX#[2]

E19

FDI0_TX#[3]

F18

FDI1_TX#[0]

B21

FDI1_TX#[1]

C20

FDI1_TX#[2]

D18

FDI1_TX#[3]

E17

FDI0_TX[0]

A22

FDI0_TX[1]

G19

FDI0_TX[2]

E20

FDI0_TX[3]

G18

FDI1_TX[0]

B20

FDI1_TX[1]

C19

FDI1_TX[2]

D19

FDI1_TX[3]

F17

FDI0_FSYNC

J18

FDI1_FSYNC

J17

FDI_INT

H20

FDI0_LSYNC

J19

FDI1_LSYNC

H17

PEG_ICOMPI

J22

PEG_ICOMPO

J21

PEG_RCOMPO

H22

PEG_RX#[0]

K33

PEG_RX#[1]

M35

PEG_RX#[2]

L34

PEG_RX#[3]

J35

PEG_RX#[4]

J32

PEG_RX#[5]

H34

PEG_RX#[6]

H31

PEG_RX#[7]

G33

PEG_RX#[8]

G30

PEG_RX#[9]

F35

PEG_RX#[10]

E34

PEG_RX#[11]

E32

PEG_RX#[12]

D33

PEG_RX#[13]

D31

PEG_RX#[14]

B33

PEG_RX#[15]

C32

PEG_RX[0]

J33

PEG_RX[1]

L35

PEG_RX[2]

K34

PEG_RX[3]

H35

PEG_RX[4]

H32

PEG_RX[5]

G34

PEG_RX[6]

G31

PEG_RX[7]

F33

PEG_RX[8]

F30

PEG_RX[9]

E35

PEG_RX[10]

E33

PEG_RX[11]

F32

PEG_RX[12]

D34

PEG_RX[13]

E31

PEG_RX[14]

C33

PEG_RX[15]

B32

PEG_TX#[0]

M29

PEG_TX#[1]

M32

PEG_TX#[2]

M31

PEG_TX#[3]

L32

PEG_TX#[4]

L29

PEG_TX#[5]

K31

PEG_TX#[6]

K28

PEG_TX#[7]

J30

PEG_TX#[8]

J28

PEG_TX#[9]

H29

PEG_TX#[10]

G27

PEG_TX#[11]

E29

PEG_TX#[12]

F27

PEG_TX#[13]

D28

PEG_TX#[14]

F26

PEG_TX#[15]

E25

PEG_TX[0]

M28

PEG_TX[1]

M33

PEG_TX[2]

M30

PEG_TX[3]

L31

PEG_TX[4]

L28

PEG_TX[5]

K30

PEG_TX[6]

K27

PEG_TX[7]

J29

PEG_TX[8]

J27

PEG_TX[9]

H28

PEG_TX[10]

G28

PEG_TX[11]

E28

PEG_TX[12]

F28

PEG_TX[13]

D27

PEG_TX[14]

E26

PEG_TX[15]

D25

eDP_AUX

C15

eDP_AUX#

D15

eDP_TX[0]

C17

eDP_TX[1]

F16

eDP_TX[2]

C16

eDP_TX[3]

G15

eDP_TX#[0]

C18

eDP_TX#[1]

E16

eDP_TX#[2]

D16

eDP_TX#[3]

F15

eDP_COMPIO

A18

eDP_HPD

B16

eDP_ICOMPO

A17

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

XDP_TMS

XDP_TDO_R

SM_RCOMP0

XDP_DBRESET#

XDP_TRST#

XDP_TDI_R

XDP_TCLK

XDP_PRDY#

SM_RCOMP2

XDP_PREQ#

SM_RCOMP1

XDP_DBRESET#_R

CLK_XDP

CLK_XDP#

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

CFD_PWRBTN#_X DP

CFG1

CFG2

CFG0

CFG3

CFG4

CFG5

CFG6

CFG7

XDP_TMS

XDP_PREQ#

XDP_PRDY#

XDP_DBRESET#

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TCLK

H_CPUPWRGD

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

CFG0

H_CPUPWRGD_XD P

XDP_RST#_RXDP_HOOK2

DDR_XDP_WAN_ SMBDAT_R1

DDR_XDP_WAN_ SMBCLK_R1

XDP_OBS2

XDP_OBS3X DP_OBS3_R

XDP_OBS5_R

XDP_OBS2_R

XDP_OBS1_R

XDP_OBS0_R

XDP_OBS4_R XDP_OBS4

XDP_OBS7

XDP_OBS5

XDP_OBS6_R

XDP_OBS7_R

XDP_OBS6

XDP_OBS0

XDP_OBS1

DDR_HVREF_RST

VCCPWRGOOD_0_R

H_PM_SYNC

H_CATERR#

H_PROCHOT#_R

H_THERMTRIP#_R

PM_DRAM_PWR GD_CPU

VCCPWRGOOD_0_R

H_CATERR#

H_PROCHOT#

H_THERMTRIP#

CPU_DMI

CPU_DMI#

DDR3_DRAMRST#_CP U

XDP_DBRESET#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDO

XDP_TDI_R

XDP_PREQ#

SYS_PWROK_XDP

SYS_PWROK_XDP

CLK_XDP

CLK_XDP#

SM_RCOMP0

SM_RCOMP2

SM_RCOMP1

XDP_TDIXDP_TDI_R

XDP_TDO_R XDP_TDO

PCH_PLTRST#_R

PCH_PLTRST#_BUF PCH_PLTRST#_R

CFG11

CFG10

CFG9

CFG8

CFG16

CFG17

XDP_RST#_R

CPU_DPLL

CPU_DPLL#

RUNPWROK_AND PM_DRAM_PWR GD_CPU

+1.05V_RUN_VTT

+1.05V_RUN_VTT +1.05V_RUN_VTT

+1.05V_RUN_VTT

+1.05V_RUN_VTT

+1.05V_RUN_VTT

+3.3V_RUN

+3.3V_ALW_PCH

+3.3V_RUN

+3.3V_ALW_PCH

+1.5V_CPU_VDDQ

+3.3V_ALW_PCH

XDP_DBRESET# 14,16

SIO_PWRBTN#_R14,16

CFG0 9

CFG1 9

CFG2 9

CFG3 9

CFG4 9

CFG5 9

CFG6 9

CFG7 9

DDR3_DRAMRST# 12

H_THERMTRIP#22

H_CPUPWRGD18

H_PM_SYNC16

CPU_DETECT#41

H_PROCHOT#42,52,54

CLK_CPU_DMI 15

SYS_PWROK16,41

H_PECI18

CLK_CPU_ITP 15

CLK_CPU_ITP# 15

CLK_XDP_ITP9

CLK_XDP_ITP#9

PCH_PLTRST#14,17

CFG119

CFG109

CFG9 9

CFG8 9

CFG16 9

CFG17 9

DDR_HVREF_RST_GATE42

DDR_HVREF_RST_PCH15

PLTRST_XDP# 17

CLK_CPU_DMI# 15

CLK_CPU_DPLL 15

CLK_CPU_DPLL# 15

RUN_ON_CPU1.5VS3#11,44

RUNPWROK41,42

PM_DRAM_PWR GD16

DDR_XDP_WAN_ SMBDAT12,13,14,15,28,36

DDR_XDP_WAN_ SMBCLK12,13,14,15,28,36

Title

S

ize Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (2/6)

7 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (2/6)

7 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (2/6)

7 66Monday, January 10, 2011

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Place near JXDP1

Keep R1132, R1133, R1136-R119

for slew rate control.

For ESD concern, please put near CPU

Avoid stub in th e PWRGD path

while placing re sistors RC25 & R C130

place RC129 near CPU

PU/PD for JTAG signals

Buffered reset to CPU

Close to JCBU1

Max 500mils

Open drain buffer

SM_RCOMP2 --> 15mil

SM_RCOMP1/0 --> 20mil

The resistor for HOOK2 should be placed

such that the st ub is very small on CFG0 net

Follow DG Rev0.71 SM_DRAMPWROK topology

RC64

39_0402_5%~D

RC64

39_0402_5%~D

1 2

RC39 0_0402_5%~DRC39 0_0402_5%~D

1 2

RC127 0_0402_5%~DRC127 0_0402_5%~D

1 2

RC10 43_0402_5%~DRC10 43_0402_5%~D

1 2

RC47 0_0402_5%~D@RC47 0_0402_5%~D@

1 2

RC33 0_0402_5%~DRC33 0_0402_5%~D

1 2

G

D

S

QC1

SSM3K7002FU_SC70-3~D

G

D

S

QC1

SSM3K7002FU_SC70-3~D

2

13

RC17 0_0402_5%~DRC17 0_0402_5%~D

1 2

RC28 130_0402_5%~DRC28 130_0402_5%~D

1 2

RC29 51_0402_1%~DRC29 51_0402_1%~D

12

UC1

SN74LVC1G07DCKR_SC70-5~D

UC1

SN74LVC1G07DCKR_SC70-5~D

NC

1

A

2

GND

3

Y

4

VCC

5

RC130

10K_0402_5%~D

RC130

10K_0402_5%~D

12

RC50

4.99K_0402_1%~D

RC50

4.99K_0402_1%~D

12

RC40

51_0402_1%~D

RC40

51_0402_1%~D

12

RC45

200_0402_1%~D

RC45

200_0402_1%~D

12

RC25 0_0402_5%~DRC25 0_0402_5%~D

1 2

RC43

25.5_0402_1%~D

RC43

25.5_0402_1%~D

12

RC26 0_0402_5%~DRC26 0_0402_5%~D

12

RC15 0_0402_5%~DRC15 0_0402_5%~D

1 2

RC23 0_0402_5%~DRC23 0_0402_5%~D

1 2

RC32 51_0402_1%~D@RC32 51_0402_1%~D@

12

RC129 0_0402_5%~DRC129 0_0402_5%~D

1 2

G

D

S

QC2

BSS138W-7-F_SOT323-3~D

G

D

S

QC2

BSS138W-7-F_SOT323-3~D

2

13

RC46 0_0402_5%~DRC46 0_0402_5%~D

1 2

RC31 0_0402_5%~DRC31 0_0402_5%~D

1 2

RC11

0_0402_5%~D

@RC11

0_0402_5%~D

@

12

RC6 0_0402_5%~DRC6 0_0402_5%~D

1 2

RC44 62_0402_5%~DRC44 62_0402_5%~D

1 2

RC36 0_0402_5%~DRC36 0_0402_5%~D

1 2

RC13 0_0402_5%~DRC13 0_0402_5%~D

1 2

RC24 0_0402_5%~DRC24 0_0402_5%~D

1 2

CC65

0.1U_0402_16V4Z~D

CC65

0.1U_0402_16V4Z~D

1

2

RC37 0_0402_5%~DRC37 0_0402_5%~D

1 2

RC126 56_0402_5%~D@RC126 56_0402_5%~D@

1 2

CC140

0.1U_0402_16V4Z~D

CC140

0.1U_0402_16V4Z~D

1

2

RC42

140_0402_1%~D

RC42

140_0402_1%~D

12

RC48 0_0402_5%~D@RC48 0_0402_5%~D@

1 2

RC16 0_0402_5%~DRC16 0_0402_5%~D

1 2

RC38 0_0402_5%~DRC38 0_0402_5%~D

1 2

RC7 1K_0402_5%~DRC7 1K_0402_5%~D

1 2

RC5 1K_0402_5%~DRC5 1K_0402_5%~D

1 2

RC9 0_0402_5%~D@ RC9 0_0402_5%~D@

1 2

RC4

75_0402_1%~D

RC4

75_0402_1%~D

12

RC12

200_0402_5%~D

RC12

200_0402_5%~D

12

RC18 200_0402_5%~DRC18 200_0402_5%~D

1 2

RH109 0_0402_5%~D@RH109 0_0402_5%~D@

1 2

RH108 0_0402_5%~D@RH108 0_0402_5%~D@

1 2

RC124

1K_0402_5%~D

@RC124

1K_0402_5%~D

@

12

RC30 0_0402_5%~DRC30 0_0402_5%~D

1 2

RC27 51_0402_1%~DRC27 51_0402_1%~D

12

RC57 56_0402_5%~DRC57 56_0402_5%~D

1 2

RC41

51_0402_1%~D

RC41

51_0402_1%~D

12

CC66

0.1U_0402_16V4Z~D

CC66

0.1U_0402_16V4Z~D

1

2

RH106 0_0402 _5%~DRH106 0_0402_5%~D

1 2

RH107 0_0402 _5%~DRH107 0_0402_5%~D

1 2

JXDP1

SAMTE_BSH-030-01-L-D-A

@JXDP1

SAMTE_BSH-030-01-L-D-A

@

GND0

1

OBSFN_A0

3

OBSFN_A1

5

GND2

7

OBSDATA_A0

9

OBSDATA_A1

11

GND4

13

OBSDATA_A2

15

OBSDATA_A3

17

GND6

19

OBSFN_B0

21

OBSFN_B1

23

GND8

25

OBSDATA_B0

27

OBSDATA_B1

29

GND10

31

OBSDATA_B2

33

OBSDATA_B3

35

GND12

37

PWRGOOD/HOOK0

39

HOOK1

41

VCC_OBS_AB

43

HOOK2

45

HOOK3

47

GND14

49

SDA

51

SCL

53

TCK1

55

TCK0

57

GND16

59

GND1

2

OBSFN_C0

4

OBSFN_C1

6

GND3

8

OBSDATA_C0

10

OBSDATA_C1

12

GND5

14

OBSDATA_C2

16

OBSDATA_C3

18

GND7

20

OBSFN_D0

22

OBSFN_D1

24

GND9

26

OBSDATA_D0

28

OBSDATA_D1

30

GND11

32

OBSDATA_D2

34

OBSDATA_D3

36

GND13

38

ITPCLK/HOOK4

40

ITPCLK#/HOOK5

42

VCC_OBS_CD

44

RESET#/HOOK6

46

DBR#/HOOK7

48

GND15

50

TD0

52

TRST#

54

TDI

56

TMS

58

GND17

60

RC34 0_0402_5%~DRC34 0_0402_5%~D

1 2

RC125 0_0402_5%~DRC125 0_0402_5%~D

1 2

RC128 49.9_0402_1%~D@RC128 49.9_0402_1%~D@

1 2

RC19 1K_0402_5%~DRC19 1K_0402_5%~D

12

CC177

0.047U_0402_16V4Z~D

CC177

0.047U_0402_16V4Z~D

1

2

CC156

0.1U_0402_16V4Z~D

CC156

0.1U_0402_16V4Z~D

1 2

RC8 1K_0402_5%~DRC8 1K_0402_5%~D

12

RC35 51_0402_1%~DRC35 51_0402_1%~D

12

UC2

74AHC1G09GW_TSSOP5~D

UC2

74AHC1G09GW_TSSOP5~D

B

1

A

2

G

3

O

4

P

5

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

JCPU1B

Sandy Bridge_rPGA_Rev1p0

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

JCPU1B

Sandy Bridge_rPGA_Rev1p0

SM_RCOMP[1]

A5

SM_RCOMP[2]

A4

SM_DRAMRST#

R8

SM_RCOMP[0]

AK1

BCLK#

A27

BCLK

A28

DPLL_REF_CLK#

A15

DPLL_REF_CLK

A16

CATERR#

AL33

PECI

AN33

PROCHOT#

AL32

THERMTRIP#

AN32

SM_DRAMPWR OK

V8

RESET#

AR33

PRDY#

AP29

PREQ#

AP27

TCK

AR26

TMS

AR27

TRST#

AP30

TDI

AR28

TDO

AP26

DBR#

AL35

BPM#[0]

AT28

BPM#[1]

AR29

BPM#[2]

AR30

BPM#[3]

AT30

BPM#[4]

AP32

BPM#[5]

AR31

BPM#[6]

AT31

BPM#[7]

AR32

PM_SYNC

AM34

SKTOCC#

AN34

PROC_SELECT#

C26

UNCOREPWRGOOD

AP33

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_A_D59

DDR_A_D31

DDR_A_D9

DDR_A_BS1

DDR_A_D50

DDR_A_D42

DDR_A_D29

DDR_A_D51

DDR_A_D46

DDR_A_D36

DDR_A_D18

DDR_A_D4

DDR_A_D58

DDR_A_D55

DDR_A_D14

DDR_A_D24

DDR_A_D8

DDR_A_D63

DDR_A_D49

DDR_A_D41

DDR_A_D34

DDR_A_D28

DDR_A_D25

DDR_A_D35

DDR_A_D17

DDR_A_D13

DDR_A_D3

DDR_A_RAS#

DDR_A_D57

DDR_A_D54

DDR_A_D22

DDR_A_D21

DDR_A_D6

DDR_A_D23

DDR_A_D7

DDR_A_BS2

DDR_A_D62

DDR_A_D48

DDR_A_D40

DDR_A_D33

DDR_A_D27

DDR_A_WE#

DDR_A_D44

DDR_A_D16

DDR_A_D12

DDR_A_D2

DDR_A_CAS#

DDR_A_D56

DDR_A_D53

DDR_A_D45

DDR_A_D38

DDR_A_D20

DDR_A_D60

DDR_A_D5

DDR_A_D61

DDR_A_D47

DDR_A_D39

DDR_A_D32

DDR_A_D26

DDR_A_D10

DDR_A_D0

DDR_A_BS0

DDR_A_D43

DDR_A_D15

DDR_A_D11

DDR_A_D1

DDR_A_D52

DDR_A_D37

DDR_A_D30

DDR_A_D19

DDR_B_D29

DDR_B_RAS#

DDR_B_D59

DDR_B_D50

DDR_B_D49

DDR_B_D13

DDR_B_D11

DDR_B_D19

DDR_B_D14

DDR_B_D3

DDR_B_D55

DDR_B_D47

DDR_B_WE#

DDR_B_BS2

DDR_B_D52

DDR_B_D44

DDR_B_D41

DDR_B_D8

DDR_B_D5

DDR_B_CAS#

DDR_B_D56

DDR_B_D48

DDR_B_D38

DDR_B_D35

DDR_B_D26

DDR_B_D25

DDR_B_D4

DDR_B_D63

DDR_B_D34

DDR_B_D32

DDR_B_D10

DDR_B_BS1

DDR_B_D17

DDR_B_D51

DDR_B_D40

DDR_B_D36

DDR_B_D31

DDR_B_D21

DDR_B_D20

DDR_B_D15

DDR_B_D7

DDR_B_D62

DDR_B_D46

DDR_B_D42

DDR_B_D18

DDR_B_D12

DDR_B_D1

DDR_B_D53

DDR_B_D37

DDR_B_D22

DDR_B_D57

DDR_B_D27

DDR_B_D54

DDR_B_D45

DDR_B_D39

DDR_B_D30

DDR_B_D9

DDR_B_D60

DDR_B_D58

DDR_B_D33

DDR_B_D0

DDR_B_D61

DDR_B_D43

DDR_B_D28

DDR_B_D23

DDR_B_D24

DDR_B_D16

DDR_B_D6

DDR_B_D2

DDR_B_BS0

M_CLK_DDR#0

M_CLK_DDR#1

DDR_CKE0_DIMMA

DDR_A_DQS7

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS6

DDR_A_DQS#2

DDR_A_DQS#1

DDR_A_DQS#0

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#6

DDR_A_MA0

DDR_A_MA1

DDR_A_MA3

DDR_A_MA7

DDR_A_MA8

DDR_A_MA13

DDR_A_MA2

DDR_A_MA14

DDR_A_MA5

DDR_A_MA10

DDR_A_MA4

DDR_A_MA11

DDR_A_MA9

DDR_A_MA6

DDR_A_MA12

M_CLK_DDR1

M_CLK_DDR0

DDR_A_MA15

DDR_CS1_DIMMA#

DDR_CS0_DIMMA#

DDR_CKE1_DIMMA

M_ODT1

M_ODT0

M_CLK_DDR3

M_CLK_DDR#2

M_CLK_DDR#3

DDR_B_MA10

DDR_B_MA9

DDR_B_MA14

DDR_B_MA5

DDR_B_MA13

DDR_B_MA11

DDR_B_MA7

DDR_B_MA2

DDR_B_MA0

DDR_B_MA6

DDR_B_MA1

DDR_B_MA12

DDR_B_MA4

DDR_B_MA8

DDR_B_MA3

DDR_B_DQS3

DDR_B_DQS2

DDR_B_DQS7

DDR_B_DQS4

DDR_B_DQS1

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS0

DDR_B_DQS#3

DDR_B_DQS#6

DDR_B_DQS#1

M_CLK_DDR2

DDR_B_DQS#2

DDR_B_DQS#0

DDR_B_DQS#5

DDR_B_DQS#7

DDR_B_DQS#4

M_ODT2

DDR_CKE2_DIMMB

DDR_B_MA15

DDR_CKE3_DIMMB

M_ODT3

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

DDR_A_D[0..63]12

DDR_A_BS012

DDR_A_BS112

DDR_A_BS212

DDR_A_WE#12

DDR_A_CAS#12

DDR_A_RAS#12

DDR_B_D[0..63]13

DDR_B_BS213

DDR_B_BS113

DDR_B_WE#13

DDR_B_CAS#13

DDR_B_RAS#13

DDR_B_BS013

DDR_A_DQS[0..7] 12

DDR_A_DQS#[0..7] 12

DDR_A_MA[0..15] 12

DDR_CKE1_DIMMA 12

DDR_CKE0_DIMMA 12

DDR_CS0_DIMMA# 12

M_ODT0 12

DDR_CS1_DIMMA# 12

M_ODT1 12

M_CLK_DDR1 12

M_CLK_DDR0 12

M_CLK_DDR#1 12

M_CLK_DDR#0 12

DDR_B_MA[0..15] 13

DDR_B_DQS#[0..7] 13

DDR_B_DQS[0..7] 13

DDR_CS3_DIMMB# 13

DDR_CS2_DIMMB# 13

M_ODT3 13

DDR_CKE3_DIMMB 13

DDR_CKE2_DIMMB 13

M_ODT2 13

M_CLK_DDR#2 1 3

M_CLK_DDR2 13

M_CLK_DDR#3 1 3

M_CLK_DDR3 13

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (3/6)

8 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (3/6)

8 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (3/6)

8 66Monday, January 10, 2011

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

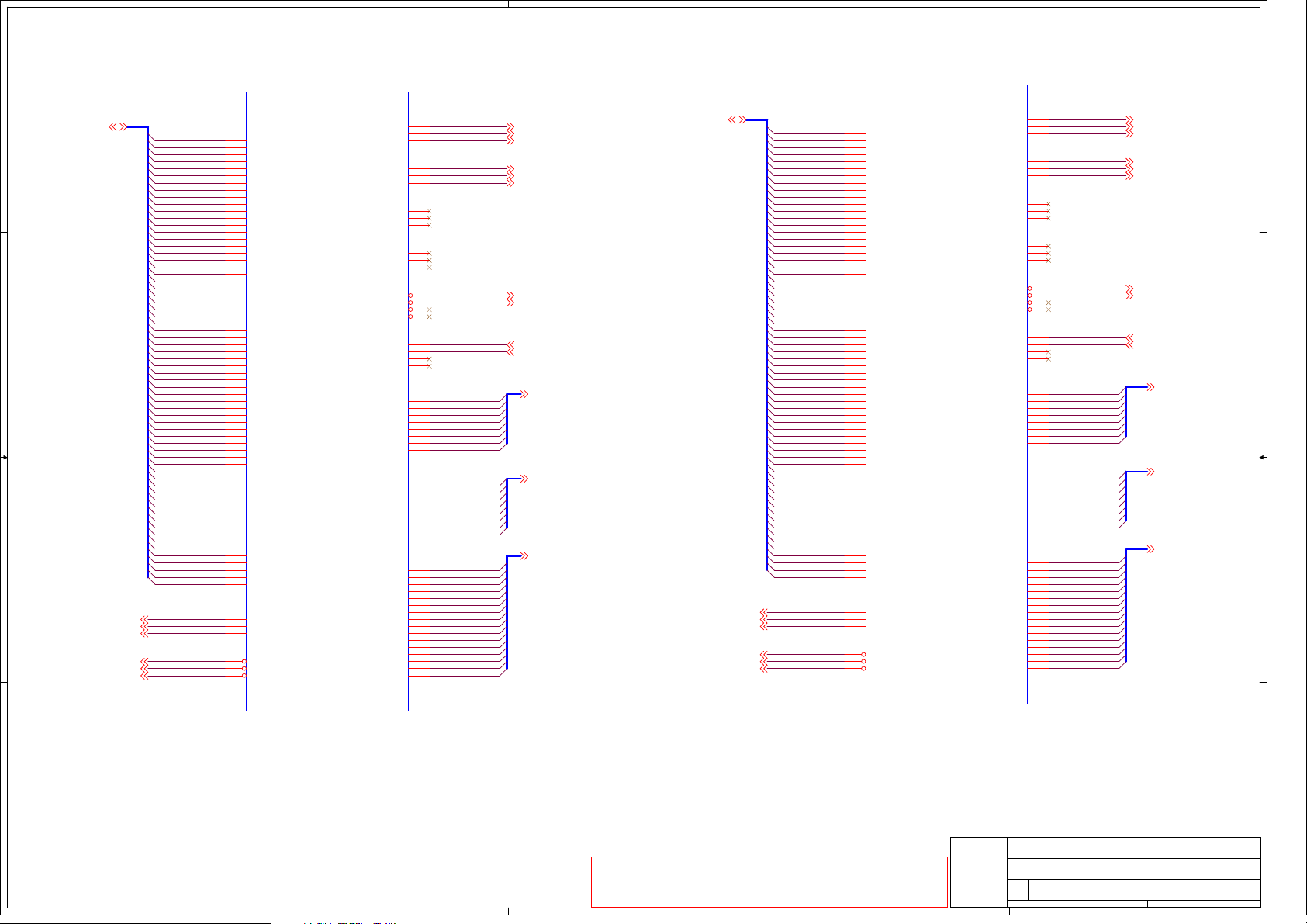

DDR SYSTEM MEMORY B

JCPU1D

Sandy Bridge_rPGA_Rev1p0

DDR SYSTEM MEMORY B

JCPU1D

Sandy Bridge_rPGA_Rev1p0

SB_BS[0]

AA9

SB_BS[1]

AA7

SB_BS[2]

R6

SB_CAS#

AA10

SB_RAS#

AB8

SB_WE#

AB9

SB_CLK[0]

AE2

SB_CLK[1]

AE1

SB_CLK#[0]

AD2

SB_CLK#[1]

AD1

SB_CKE[0]

R9

SB_CKE[1]

R10

SB_ODT[0]

AE4

SB_ODT[1]

AD4

SB_DQS[4]

AN6

SB_DQS#[4]

AN5

SB_DQS[5]

AP8

SB_DQS#[5]

AP9

SB_DQS[6]

AK11

SB_DQS#[6]

AK12

SB_DQS[7]

AP14

SB_DQS#[7]

AP15

SB_DQS[0]

C7

SB_DQS#[0]

D7

SB_DQS[1]

G3

SB_DQS#[1]

F3

SB_DQS[2]

J6

SB_DQS#[2]

K6

SB_DQS[3]

M3

SB_DQS#[3]

N3

SB_MA[0]

AA8

SB_MA[1]

T7

SB_MA[2]

R7

SB_MA[3]

T6

SB_MA[4]

T2

SB_MA[5]

T4

SB_MA[6]

T3

SB_MA[7]

R2

SB_MA[8]

T5

SB_MA[9]

R3

SB_MA[10]

AB7

SB_MA[11]

R1

SB_MA[12]

T1

SB_MA[13]

AB10

SB_MA[14]

R5

SB_MA[15]

R4

SB_DQ[0]

C9

SB_DQ[1]

A7

SB_DQ[2]

D10

SB_DQ[3]

C8

SB_DQ[4]

A9

SB_DQ[5]

A8

SB_DQ[6]

D9

SB_DQ[7]

D8

SB_DQ[8]

G4

SB_DQ[9]

F4

SB_DQ[10]

F1

SB_DQ[11]

G1

SB_DQ[12]

G5

SB_DQ[13]

F5

SB_DQ[14]

F2

SB_DQ[15]

G2

SB_DQ[16]

J7

SB_DQ[17]

J8

SB_DQ[18]

K10

SB_DQ[19]

K9

SB_DQ[20]

J9

SB_DQ[21]

J10

SB_DQ[22]

K8

SB_DQ[23]

K7

SB_DQ[24]

M5

SB_DQ[25]

N4

SB_DQ[26]

N2

SB_DQ[27]

N1

SB_DQ[28]

M4

SB_DQ[29]

N5

SB_DQ[30]

M2

SB_DQ[31]

M1

SB_DQ[32]

AM5

SB_DQ[33]

AM6

SB_DQ[34]

AR3

SB_DQ[35]

AP3

SB_DQ[36]

AN3

SB_DQ[37]

AN2

SB_DQ[38]

AN1

SB_DQ[39]

AP2

SB_DQ[40]

AP5

SB_DQ[41]

AN9

SB_DQ[42]

AT5

SB_DQ[43]

AT6

SB_DQ[44]

AP6

SB_DQ[45]

AN8

SB_DQ[46]

AR6

SB_DQ[47]

AR5

SB_DQ[48]

AR9

SB_DQ[49]

AJ11

SB_DQ[50]

AT8

SB_DQ[51]

AT9

SB_DQ[52]

AH11

SB_DQ[53]

AR8

SB_DQ[54]

AJ12

SB_DQ[55]

AH12

SB_DQ[56]

AT11

SB_DQ[57]

AN14

SB_DQ[58]

AR14

SB_DQ[59]

AT14

SB_DQ[60]

AT12

SB_DQ[61]

AN15

SB_DQ[62]

AR15

SB_DQ[63]

AT15

RSVD_TP[11]

AB2

RSVD_TP[12]

AA2

RSVD_TP[13]

T9

RSVD_TP[14]

AA1

RSVD_TP[15]

AB1

RSVD_TP[16]

T10

SB_CS#[0]

AD3

SB_CS#[1]

AE3

RSVD_TP[17]

AD6

RSVD_TP[18]

AE6

RSVD_TP[19]

AD5

RSVD_TP[20]

AE5

DDR SYSTEM MEMORY A

JCPU1C

Sandy Bridge_rPGA_Rev1p0

DDR SYSTEM MEMORY A

JCPU1C

Sandy Bridge_rPGA_Rev1p0

SA_BS[0]

AE10

SA_BS[1]

AF10

SA_BS[2]

V6

SA_CAS#

AE8

SA_RAS#

AD9

SA_WE#

AF9

SA_CLK[0]

AB6

SA_CLK[1]

AA5

SA_CLK#[0]

AA6

SA_CLK#[1]

AB5

SA_CKE[0]

V9

SA_CKE[1]

V10

SA_CS#[0]

AK3

SA_CS#[1]

AL3

SA_ODT[0]

AH3

SA_ODT[1]

AG3

SA_DQS[0]

D4

SA_DQS#[0]

C4

SA_DQS[1]

F6

SA_DQS#[1]

G6

SA_DQS[2]

K3

SA_DQS#[2]

J3

SA_DQS[3]

N6

SA_DQS#[3]

M6

SA_DQS[4]

AL5

SA_DQS#[4]

AL6

SA_DQS[5]

AM9

SA_DQS#[5]

AM8

SA_DQS[6]

AR11

SA_DQS#[6]

AR12

SA_DQS[7]

AM14

SA_DQS#[7]

AM15

SA_MA[0]

AD10

SA_MA[1]

W1

SA_MA[2]

W2

SA_MA[3]

W7

SA_MA[4]

V3

SA_MA[5]

V2

SA_MA[6]

W3

SA_MA[7]

W6

SA_MA[8]

V1

SA_MA[9]

W5

SA_MA[10]

AD8

SA_MA[11]

V4

SA_MA[12]

W4

SA_MA[13]

AF8

SA_MA[14]

V5

SA_MA[15]

V7

SA_DQ[0]

C5

SA_DQ[1]

D5

SA_DQ[2]

D3

SA_DQ[3]

D2

SA_DQ[4]

D6

SA_DQ[5]

C6

SA_DQ[6]

C2

SA_DQ[7]

C3

SA_DQ[8]

F10

SA_DQ[9]

F8

SA_DQ[10]

G10

SA_DQ[11]

G9

SA_DQ[12]

F9

SA_DQ[13]

F7

SA_DQ[14]

G8

SA_DQ[15]

G7

SA_DQ[16]

K4

SA_DQ[17]

K5

SA_DQ[18]

K1

SA_DQ[19]

J1

SA_DQ[20]

J5

SA_DQ[21]

J4

SA_DQ[22]

J2

SA_DQ[23]

K2

SA_DQ[24]

M8

SA_DQ[25]

N10

SA_DQ[26]

N8

SA_DQ[27]

N7

SA_DQ[28]

M10

SA_DQ[29]

M9

SA_DQ[30]

N9

SA_DQ[31]

M7

SA_DQ[32]

AG6

SA_DQ[33]

AG5

SA_DQ[34]

AK6

SA_DQ[35]

AK5

SA_DQ[36]

AH5

SA_DQ[37]

AH6

SA_DQ[38]

AJ5

SA_DQ[39]

AJ6

SA_DQ[40]

AJ8

SA_DQ[41]

AK8

SA_DQ[42]

AJ9

SA_DQ[43]

AK9

SA_DQ[44]

AH8

SA_DQ[45]

AH9

SA_DQ[46]

AL9

SA_DQ[47]

AL8

SA_DQ[48]

AP11

SA_DQ[49]

AN11

SA_DQ[50]

AL12

SA_DQ[51]

AM12

SA_DQ[52]

AM11

SA_DQ[53]

AL11

SA_DQ[54]

AP12

SA_DQ[55]

AN12

SA_DQ[56]

AJ14

SA_DQ[57]

AH14

SA_DQ[58]

AL15

SA_DQ[59]

AK15

SA_DQ[60]

AL14

SA_DQ[61]

AK14

SA_DQ[62]

AJ15

SA_DQ[63]

AH15

RSVD_TP[1]

AB4

RSVD_TP[2]

AA4

RSVD_TP[4]

AB3

RSVD_TP[5]

AA3

RSVD_TP[3]

W9

RSVD_TP[6]

W10

RSVD_TP[7]

AG1

RSVD_TP[8]

AH1

RSVD_TP[9]

AG2

RSVD_TP[10]

AH2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

CFG10

CFG11

CFG13

CFG14

CFG15

CFG16

CFG17

CFG12

CFG1

CFG2

CFG0

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

RSVD3

RSVD4

RSVD1

RSVD2

CFG4

CFG6

CFG5

CFG2

CFG7

RSVD4

RSVD2

RSVD1

RSVD3

+DIMM0_1_VREF_CPU

+DIMM0_1_CA_CPU

+DIMM0_1_CA_CPU

+DIMM0_1_VREF_CPU

+VCC_CORE

+VCC_GFXCORE

+DIMM0_1_VREF_CPU

+DIMM0_1_CA_CPU

CFG07

CFG17

CFG27

CFG37

CFG47

CFG57

CFG67

CFG77

CFG87

CFG97

CFG107

CFG117

CLK_XDP_ITP 7

CLK_XDP_ITP# 7

CFG177

CFG167

Title

S

ize Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (4/6)

9 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (4/6)

9 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (4/6)

9 66Monday, January 10, 2011

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

DELL CONFIDENTIAL/PROPRIETARY

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

PCIE Port Bifurcation Straps

CFG[6:5]

11: (Default) x16 - Device 1 functions 1 and 2 disabled

CFG7

PEG DEFER TRAINING

0: PEG Wait for BIOS for training

1: (Default) PEG Train immediately

following xxRESETB de assertion

CFG4

Display Port Presence Strap

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

CFG Straps for Processor

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

0:Lane Reversed

1:(Default) Normal Operation; Lane #

definition matches socket pin map definition

follow DG0.9 change to 1Kohm 5%

T44 PAD~D@ T44 PAD~D@

T51 PAD~D@T51 PAD~D@

T8 PAD~D@ T8 PAD~D@

RC96 1K_0402_5%~D@RC96 1K_040 2_5%~D@

1 2

T47 PAD~D@ T47 PAD~D@

RC53

1K_0402_5%~D

@RC53

1K_0402_5%~D

@

12

T50 PAD~D@T50 PAD~D@

T5 PAD~D@ T5 PAD~D@

RC123 49.9_0402_1%~D@RC123 49.9_0402_1%~D@

1 2

T27 PAD~D@T27 PAD~D@

RC54

1K_0402_5%~D

@RC54

1K_0402_5%~D

@

12

T25 PAD~D@T25 PAD~D@

T43 PAD~D@ T43 PAD~D@

T40 PAD~D@ T40 PAD~D@

T3 PAD~D@ T3 PAD~D@

RC97 1K_0402_5%~D@RC97 1K_040 2_5%~D@

1 2

T53 PAD~D@T53 PAD~D@

T31 PAD~D@ T31 PAD~D@

T52 PAD~D@ T52 PAD~D@

T17 PAD~D@T17 PAD~D@

T36 PAD~D@ T36 PAD~D@

T20 PAD~D@T20 PAD~D@

T19 PAD~D@T19 PAD~D@

T13 PAD~D@T13 PAD~D@ RC52

1K_0402_5%~D

@RC52

1K_0402_5%~D

@

12

T29 PAD~D@ T29 PAD~D@

T10 PAD~D@T10 PAD~D@

T30 PAD~D@ T30 PAD~D@

T32 PAD~D@T32 PAD~D@

T14 PAD~D@T14 PAD~D@

T39 PAD~D@T39 PAD~D@

T21 PAD~D@T21 PAD~D@

T15 PAD~D@T15 PAD~D@

T41 PAD~D@ T41 PAD~D@

T35 PAD~D@ T35 PAD~D@

T16 PAD~D@T16 PAD~D@

T155 PAD~D@T155 PAD~D@

T11 PAD~D@T11 PAD~D@

T4 PAD~D@ T4 PAD~D@

T22 PAD~D@T22 PAD~D@

T33 PAD~D@ T33 PAD~D@

T49 PAD~D@T49 PAD~D@

T1 PAD~D@ T1 PAD~D@

T24 PAD~D@T24 PAD~D@

T45 PAD~D@ T45 PAD~D@

RC122 49.9_0402_1%~D@RC122 49.9_0402_1%~D@

1 2

RESERVED

JCPU1E

Sandy Bridge_rPGA_Rev1p0

RESERVED

JCPU1E

Sandy Bridge_rPGA_Rev1p0

CFG[0]

AK28

CFG[1]

AK29

CFG[2]

AL26

CFG[3]

AL27

CFG[4]

AK26

CFG[5]

AL29

CFG[6]

AL30

CFG[7]

AM31

CFG[8]

AM32

CFG[9]

AM30

CFG[10]

AM28

CFG[11]

AM26

CFG[12]

AN28

CFG[13]

AN31

CFG[14]

AN26

CFG[15]

AM27

CFG[16]

AK31

CFG[17]

AN29

RSVD34

AM33

RSVD35

AJ27

RSVD38

J16

RSVD42

AT34

RSVD39

H16

RSVD40

G16

RSVD41

AR35

RSVD43

AT33

RSVD45

AR34

RSVD56

AT2

RSVD57

AT1

RSVD58

AR1

RSVD46

B34

RSVD47

A33

RSVD48

A34

RSVD49

B35

RSVD50

C35

RSVD51

AJ32

RSVD52

AK32

RSVD30

AE7

RSVD31

AK2

RSVD28

L7

RSVD29

AG7

RSVD27

J15

RSVD16

C30

RSVD15

D23

RSVD17

A31

RSVD18

B30

RSVD20

D30

RSVD19

B29

RSVD22

A30

RSVD21

B31

RSVD23

C29

RSVD24

J20

RSVD37

T8

RSVD6

B4

RSVD7

D1

RSVD8

F25

RSVD9

F24

RSVD11

D24

RSVD12

G25

RSVD13

G24

RSVD14

E23

RSVD32

W8

RSVD33

AT26

RSVD25

B18

RSVD44

AP35

RSVD10

F23

RSVD5

AJ26

VAXG_VAL_SENSE

AJ31

VSSAXG_VAL_SENSE

AH31

VCC_VAL_SENSE

AJ33

VSS_VAL_SENSE

AH33

KEY

B1

VCC_DIE_SENSE

AH27

VCCIO_SEL

A19

RSVD54

AN35

RSVD55

AM35

T37 PAD~D@ T37 PAD~D@

T46 PAD~D@ T46 PAD~D@

T28 PAD~D@ T28 PAD~D@

T7 PAD~D@ T7 PAD~D@

T12 PAD~D@T12 PAD~D@

RC56

1K_0402_5%~D

@RC56

1K_0402_5%~D

@

12

T38 PAD~D@ T38 PAD~D@

T9 PAD~D@ T9 PAD~D@

T2 PAD~D@ T2 PAD~D@

T42 PAD~D@ T42 PAD~D@

RC121 49.9_0402_1%~D@RC121 49.9_0402_1%~D@

1 2

T34 PAD~D@T34 PAD~D@

T6 PAD~D@ T6 PAD~D@

T26 PAD~D@T26 PAD~D@

T48 PAD~D@ T48 PAD~D@

RC51

1K_0402_5%~D

@RC51

1K_0402_5%~D

@

12

T18 PAD~D@T18 PAD~D@

T23 PAD~D@T23 PAD~D@

RC120 49.9_0402_1%~D@RC120 49.9_0402_1%~D@

1 2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

VCCSENSE_R

VSSSENSE_R

VTT_SENSE_R

VSSIO_SENSE_R

H_CPU_SVIDALRT#

VIDSOUT

H_CPU_SVIDALRT#

VIDSCLK

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

+1.05V_RUN_VTT

+1.05V_RUN_VTT

+1.05V_RUN_VTT

VSSSENSE 52

VCCSENSE 52

VTT_SENSE 51

VIDALERT_N 52

VIDSCLK 52

VIDSOUT 52

VTT_GND 51

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (5/6)

10 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (5/6)

10 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (5/6)

10 66Monday, January 10, 2011

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

53A 8.5A

CPU Power Rail Table

1.5

0.65-0.9

VCC

VCCIO

VAXG

VCCPLL

VDDQ

VCCSA

Voltage Rail

0.65-1.3

1.05

1.8

53

8.5

26

3

12-16

6

0.0-1.1

Voltage

S0 Iccmax

Current (A)

5A to Mem contro ller(+1.5V_CPU_V DDQ)

5-6A to 2 DIMMs/ channel

2-5A to +1.5V_RU N & +0.75V_DDR_V TT

*

*

Description

5

+1.5V_MEM 1.5

Iccmax current c hanged for PDDG Rev0.7

Note: Place the PU resistors clo se to CPU

R1555 close to C PU 300 - 1500mil s

CAD Note: Place the PU

resistors close to CPU

R1558 close to C PU 300 - 1500mil s

DELL CONFIDENTIAL/PROPRIETARY

Place RC66, RC70near CPU

SVID note: VIDAL ERT# trace

routing need to be routed betwee n

VIDSCLK and VIDS OUT signals

+

CC131

470U_D2_2V-M~D

+

CC131

470U_D2_2V-M~D

1

2 3

CC116

22U_0805_6.3VAM~D

CC116

22U_0805_6.3VAM~D

1

2

CC122

22U_0805_6.3VAM~D

CC122

22U_0805_6.3VAM~D

1

2

CC92

22U_0805_6.3VAM~D

@CC92

22U_0805_6.3VAM~D

@

1

2

+

CC129

470U_D2_2V-M~D

@

+

CC129

470U_D2_2V-M~D

@

1

2 3

CC89

22U_0805_6.3VAM~D

CC89

22U_0805_6.3VAM~D

1

2

RC68 0_0402_5%~DRC68 0_0402_5%~D

1 2

CC75

10U_0805_4VAM~D

CC75

10U_0805_4VAM~D

1

2

CC112

22U_0805_6.3VAM~D

CC112

22U_0805_6.3VAM~D

1

2

RC63

130_0402_1%~D

RC63

130_0402_1%~D

12

RC60

75_0402_1%~D

RC60

75_0402_1%~D

12

CC85

22U_0805_6.3VAM~D

CC85

22U_0805_6.3VAM~D

1

2

CC82

22U_0805_6.3VAM~D

CC82

22U_0805_6.3VAM~D

1

2

CC72

10U_0805_4VAM~D

CC72

10U_0805_4VAM~D

1

2

CC80

22U_0805_6.3VAM~D

CC80

22U_0805_6.3VAM~D

1

2

CC117

22U_0805_6.3VAM~D

CC117

22U_0805_6.3VAM~D

1

2

RC66

100_0402_1%~D

RC66

100_0402_1%~D

12

CC110

22U_0805_6.3VAM~D

CC110

22U_0805_6.3VAM~D

1

2

+

CC130

470U_D2_2V-M~D

@

+

CC130

470U_D2_2V-M~D

@

1

2 3

CC79

22U_0805_6.3VAM~D

CC79

22U_0805_6.3VAM~D

1

2

CC73

10U_0805_4VAM~D

CC73

10U_0805_4VAM~D

1

2

CC113

22U_0805_6.3VAM~D

CC113

22U_0805_6.3VAM~D

1

2

CC86

22U_0805_6.3VAM~D

CC86

22U_0805_6.3VAM~D

1

2

RC61 43_0402_5%~DRC 61 43_0402_5%~D

1 2

CC90

22U_0805_6.3VAM~D

@CC90

22U_0805_6.3VAM~D

@

1

2

CC69

22U_0805_6.3VAM~D

CC69

22U_0805_6.3VAM~D

1

2

CC120

22U_0805_6.3VAM~D

CC120

22U_0805_6.3VAM~D

1

2

+

CC132

470U_D2_2V-M~D

+

CC132

470U_D2_2V-M~D

1

2 3

+

CC134

470U_D2_2V-M~D

+

CC134

470U_D2_2V-M~D

1

2 3

CC87

10U_0805_4VAM~D

CC87

10U_0805_4VAM~D

1

2

CC68

10U_0805_4VAM~D

CC68

10U_0805_4VAM~D

1

2

RC132 0_0402_5%~DRC132 0_0402_5%~D

1 2

RC67 0_0402_5%~DRC67 0_0402_5%~D

1 2

RC70

100_0402_1%~D

RC70

100_0402_1%~D

12

RC133 0_0402_5%~DRC133 0_0402_5%~D

1 2

CC93

22U_0805_6.3VAM~D

@CC93

22U_0805_6.3VAM~D

@

1

2

+

CC107

330U_D2_2VM_R6M~D

+

CC107

330U_D2_2VM_R6M~D

1

2

CC84

22U_0805_6.3VAM~D

CC84

22U_0805_6.3VAM~D

1

2

CC124

22U_0805_6.3VAM~D

CC124

22U_0805_6.3VAM~D

1

2

CC83

22U_0805_6.3VAM~D

CC83

22U_0805_6.3VAM~D

1

2

+

CC108

330U_D2_2VM_R6M~D

+

CC108

330U_D2_2VM_R6M~D

1

2

CC77

10U_0805_4VAM~D

CC77

10U_0805_4VAM~D

1

2

CC78

22U_0805_6.3VAM~D

CC78

22U_0805_6.3VAM~D

1

2

+

CC133

470U_D2_2V-M~D

+

CC133

470U_D2_2V-M~D

1

2 3

+

CC109

330U_D2_2VM_R6M~D

@

+

CC109

330U_D2_2VM_R6M~D

@

1

2

CC67

10U_0805_4VAM~D

CC67

10U_0805_4VAM~D

1

2

CC88

10U_0805_4VAM~D

CC88

10U_0805_4VAM~D

1

2

CC91

22U_0805_6.3VAM~D

@CC91

22U_0805_6.3VAM~D

@

1

2

CC123

22U_0805_6.3VAM~D

CC123

22U_0805_6.3VAM~D

1

2

CC111

22U_0805_6.3VAM~D

CC111

22U_0805_6.3VAM~D

1

2

CC115

22U_0805_6.3VAM~D

CC115

22U_0805_6.3VAM~D

1

2

CC71

10U_0805_4VAM~D

CC71

10U_0805_4VAM~D

1

2

CC121

22U_0805_6.3VAM~D

CC121

22U_0805_6.3VAM~D

1

2

CC76

10U_0805_4VAM~D

CC76

10U_0805_4VAM~D

1

2

CC114

22U_0805_6.3VAM~D

CC114

22U_0805_6.3VAM~D

1

2

CC70

22U_0805_6.3VAM~D

CC70

22U_0805_6.3VAM~D

1

2

CC125

22U_0805_6.3VAM~D

CC125

22U_0805_6.3VAM~D

1

2

POWER

CORE SUPPLY

PEG AND DDR

SENSE LINES SVID

JCPU1F

Sandy Bridge_rPGA_Rev1p0

POWER

CORE SUPPLY

PEG AND DDR

SENSE LINES SVID

JCPU1F

Sandy Bridge_rPGA_Rev1p0

VCC_SENSE

AJ35

VSS_SENSE

AJ34

VIDALERT#

AJ29

VIDSCLK

AJ30

VIDSOUT

AJ28

VSSIO_SENSE

A10

VCC1

AG35

VCC2

AG34

VCC3

AG33

VCC4

AG32

VCC5

AG31

VCC6

AG30

VCC7

AG29

VCC8

AG28

VCC9

AG27

VCC10

AG26

VCC11

AF35

VCC12

AF34

VCC13

AF33

VCC14

AF32

VCC15

AF31

VCC16

AF30

VCC17

AF29

VCC18

AF28

VCC19

AF27

VCC20

AF26

VCC21

AD35

VCC22

AD34

VCC23

AD33

VCC24

AD32

VCC25

AD31

VCC26

AD30

VCC27

AD29

VCC28

AD28

VCC29

AD27

VCC30

AD26

VCC31

AC35

VCC32

AC34

VCC33

AC33

VCC34

AC32

VCC35

AC31

VCC36

AC30

VCC37

AC29

VCC38

AC28

VCC39

AC27

VCC40

AC26

VCC41

AA35

VCC42

AA34

VCC43

AA33

VCC44

AA32

VCC45

AA31

VCC46

AA30

VCC47

AA29

VCC48

AA28

VCC49

AA27

VCC50

AA26

VCC51

Y35

VCC52

Y34

VCC53

Y33

VCC54

Y32

VCC55

Y31

VCC56

Y30

VCC57

Y29

VCC58

Y28

VCC59

Y27

VCC60

Y26

VCC61

V35

VCC62

V34

VCC63

V33

VCC64

V32

VCC65

V31

VCC66

V30

VCC67

V29

VCC68

V28

VCC69

V27

VCC70

V26

VCC71

U35

VCC72

U34

VCC73

U33

VCC74

U32

VCC75

U31

VCC76

U30

VCC77

U29

VCC78

U28

VCC79

U27

VCC80

U26

VCC81

R35

VCC82

R34

VCC83

R33

VCC84

R32

VCC85

R31

VCC86

R30

VCC87

R29

VCC88

R28

VCC89

R27

VCC90

R26

VCC91

P35

VCC92

P34

VCC93

P33

VCC94

P32

VCC95

P31

VCC96

P30

VCC97

P29

VCC98

P28

VCC99

P27

VCC100

P26

VCCIO1

AH13

VCCIO12

J11

VCCIO18

G12

VCCIO19

F14

VCCIO20

F13

VCCIO21

F12

VCCIO22

F11

VCCIO23

E14

VCCIO24

E12

VCCIO2

AH10

VCCIO3

AG10

VCCIO4

AC10

VCCIO5

Y10

VCCIO6

U10

VCCIO7

P10

VCCIO8

L10

VCCIO9

J14

VCCIO10

J13

VCCIO11

J12

VCCIO13

H14

VCCIO14

H12

VCCIO15

H11

VCCIO16

G14

VCCIO17

G13

VCCIO25

E11

VCCIO32

C12

VCCIO33

C11

VCCIO34

B14

VCCIO35

B12

VCCIO36

A14

VCCIO37

A13

VCCIO38

A12

VCCIO39

A11

VCCIO26

D14

VCCIO27

D13

VCCIO28

D12

VCCIO29

D11

VCCIO30

C14

VCCIO31

C13

VCCIO_SENSE

B10

VCCIO40

J23

CC119

22U_0805_6.3VAM~D

CC119

22U_0805_6.3VAM~D

1

2

CC81

22U_0805_6.3VAM~D

CC81

22U_0805_6.3VAM~D

1

2

CC118

22U_0805_6.3VAM~D

CC118

22U_0805_6.3VAM~D

1

2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

RUN_ON_CPU1.5VS3#

RUN_ON_CPU1.5VS3

RUN_ON_CPU1.5VS3

H_FC_C22

+1.5V_MEM +1.5V_CPU_VDDQ

+15V_ALW+3.3V_ALW2

+1.5V_MEM

+V_DDR_REF

+VCC_GFXCORE

+1.8V_RUN

+VCC_SA

+1.5V_CPU_VDDQ

+V_SM_VREF_CNT

+V_SM_VREF_CNT

RUN_ON37,41,44,49

CPU1.5V_S3_GATE42 RUN_ON_CPU1.5VS3# 7,44

VCC_AXG_SENSE 52

VSS_AXG_SENSE 52

VCCSA_VID_1 55

+GND_VCC_SA 55

+VCCSA_SENSE 55

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (6/6)

11 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (6/6)

11 66Monday, January 10, 2011

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

LA-6591P

1.0

Sandy Bridge (6/6)

11 66Monday, January 10, 2011

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

+1.5V_CPU_VDDQ Source

+V_SM_VREF should

have 10 mil trace width

26A

5A

3A

6A

QC4A

DMN66D0LDW-7_SOT363-6~D

QC4A

DMN66D0LDW-7_SOT363-6~D

61

2

CC139

22U_0805_6.3VAM~D

CC139

22U_0805_6.3VAM~D

1

2

CC162

10U_0805_4VAM~D

CC162

10U_0805_4VAM~D

1

2

CC136

4700P_0402_25V7K~D

CC136

4700P_0402_25V7K~D

1

2

RC74

100K_0402_5%~D

RC74

100K_0402_5%~D

12

CC144

22U_0805_6.3VAM~D

CC144

22U_0805_6.3VAM~D

1

2

CC171

10U_0603_6.3V6M~D

@CC171

10U_0603_6.3V6M~D

@

1

2

CC179 0.1U_0402_10V7K~DCC179 0.1U_0402_10V7K~D

12

CC166

10U_0805_4VAM~D

CC166

10U_0805_4VAM~D

1

2

RC83

10K_0402_5%~D

RC83

10K_0402_5%~D

12

CC168

10U_0805_4VAM~D

CC168

10U_0805_4VAM~D

1

2

+

CC167

330U_D2_2VM_R6M~D

+

CC167

330U_D2_2VM_R6M~D

1

2

CC175

1U_0402_6.3V6K~D

CC175

1U_0402_6.3V6K~D

1

2

RC72

100K_0402_5%~D

RC72

100K_0402_5%~D

12

QC3

AO4728L_SO8~D

QC3

AO4728L_SO8~D

4

7

8

6

5

1

2

3

RC138 0_0402_5%~DRC138 0_0402_5%~D

1 2

CC149 0.1U_0402_10V7K~DCC149 0.1U_0402_10V7K~D

12

CC174

1U_0402_6.3V6K~D

CC174

1U_0402_6.3V6K~D

1

2

CC169

10U_0805_4VAM~D

CC169

10U_0805_4VAM~D

1

2

CC164

10U_0805_4VAM~D

CC164

10U_0805_4VAM~D

1

2

POWER

GRAPHICS

DDR3 -1.5V RAILS

SENSE

LINES

1.8V RAIL

SA RAIL

VREFMISC

JCPU1G

Sandy Bridge_rPGA_Rev1p0

POWER

GRAPHICS

DDR3 -1.5V RAILS

SENSE

LINES

1.8V RAIL

SA RAIL

VREFMISC

JCPU1G

Sandy Bridge_rPGA_Rev1p0

SM_VREF

AL1

VSSAXG_SENSE

AK34

VAXG_SENSE

AK35

VAXG1

AT24

VAXG2

AT23

VAXG3

AT21

VAXG4

AT20

VAXG5

AT18

VAXG6

AT17

VAXG7

AR24

VAXG8

AR23

VAXG9

AR21

VAXG10

AR20

VAXG11

AR18

VAXG12

AR17

VAXG13

AP24

VAXG14

AP23

VAXG15

AP21

VAXG16

AP20

VAXG17

AP18

VAXG18

AP17

VAXG19

AN24

VAXG20

AN23

VAXG21

AN21

VAXG22

AN20

VAXG23

AN18

VAXG24

AN17

VAXG25

AM24

VAXG26

AM23

VAXG27

AM21

VAXG28

AM20

VAXG29

AM18

VAXG30

AM17

VAXG31

AL24

VAXG32

AL23

VAXG33

AL21

VAXG34

AL20

VAXG35

AL18

VAXG36

AL17

VAXG37

AK24

VAXG38

AK23

VAXG39

AK21

VAXG40

AK20

VAXG41

AK18

VAXG42

AK17

VAXG43

AJ24

VAXG44

AJ23

VAXG45

AJ21

VAXG46

AJ20

VAXG47

AJ18

VAXG48

AJ17

VAXG49

AH24

VAXG50

AH23

VAXG51

AH21

VAXG52

AH20

VAXG53

AH18

VAXG54

AH17

VDDQ11

U4

VDDQ12

U1

VDDQ13

P7

VDDQ14

P4

VDDQ15

P1

VDDQ1

AF7

VDDQ2

AF4

VDDQ3

AF1

VDDQ4

AC7

VDDQ5

AC4

VDDQ6

AC1

VDDQ7

Y7

VDDQ8

Y4

VDDQ9

Y1

VDDQ10

U7

VCCPLL1

B6

VCCPLL2

A6

VCCSA1

M27

VCCSA2

M26

VCCSA3

L26

VCCSA4

J26

VCCSA5

J25

VCCSA6

J24

VCCSA7

H26

VCCSA8

H25

VCCSA_SENSE

H23

VCCSA_VID1

C24

VCCPLL3

A2

FC_C22

C22

CC137

22U_0805_6.3VAM~D

CC137

22U_0805_6.3VAM~D

1

2

QC4B

DMN66D0LDW-7_SOT363-6~D

QC4B

DMN66D0LDW-7_SOT363-6~D

3

5

4

CC146

22U_0805_6.3VAM~D

CC146

22U_0805_6.3VAM~D

1

2

CC173

10U_0805_4VAM~D

CC173

10U_0805_4VAM~D

1

2

CC163

10U_0805_4VAM~D

CC163

10U_0805_4VAM~D

1

2

PJP2

PAD-OPEN 4x4m

@PJP2

PAD-OPEN 4x4m

@

1 2

CC150 0.1U_0402_10V7K~DCC150 0.1U_0402_10V7K~D

12

CC161

10U_0805_4VAM~D

CC161

10U_0805_4VAM~D

1

2

RC134 0_0402_5%~D@RC134 0_0402_5%~D@

1 2

RC73

20K_0402_5%~D

@RC73

20K_0402_5%~D

@

12

RC137 0_0402_5%~DRC137 0_0402_5%~D

1 2

CC145

22U_0805_6.3VAM~D

CC145

22U_0805_6.3VAM~D

1

2

CC141

22U_0805_6.3VAM~D

CC141

22U_0805_6.3VAM~D

1

2

RC78

100K_0402_5%~D

RC78

100K_0402_5%~D

12

+

CC176

330U_D2_2.5VM_R6M~D

+

CC176

330U_D2_2.5VM_R6M~D

1

2

VSS

JCPU1H

Sandy Bridge_rPGA_Rev1p0

VSS

JCPU1H

Sandy Bridge_rPGA_Rev1p0

VSS1

AT35

VSS2

AT32

VSS3

AT29

VSS4

AT27

VSS5

AT25

VSS6

AT22

VSS7

AT19

VSS8

AT16

VSS9

AT13

VSS10

AT10

VSS11

AT7

VSS12

AT4

VSS13

AT3

VSS14

AR25

VSS15

AR22

VSS16

AR19

VSS17

AR16

VSS18

AR13

VSS19

AR10

VSS20

AR7

VSS21

AR4

VSS22

AR2

VSS23

AP34

VSS24

AP31

VSS25

AP28

VSS26

AP25

VSS27

AP22

VSS28

AP19

VSS29

AP16

VSS30

AP13

VSS31

AP10

VSS32

AP7

VSS33

AP4

VSS34

AP1

VSS35

AN30

VSS36

AN27

VSS37

AN25

VSS38

AN22

VSS39

AN19

VSS40

AN16

VSS41

AN13

VSS42

AN10

VSS43

AN7

VSS44

AN4

VSS45

AM29

VSS46

AM25

VSS47

AM22

VSS48

AM19

VSS49

AM16

VSS50

AM13

VSS51

AM10

VSS52

AM7

VSS53

AM4

VSS54

AM3

VSS55

AM2

VSS56

AM1

VSS57

AL34

VSS58

AL31

VSS59

AL28

VSS60

AL25

VSS61

AL22

VSS62

AL19

VSS63

AL16

VSS64

AL13

VSS65

AL10

VSS66

AL7

VSS67

AL4

VSS68

AL2

VSS69

AK33

VSS70

AK30

VSS71

AK27

VSS72

AK25

VSS73

AK22

VSS74

AK19

VSS75

AK16

VSS76

AK13

VSS77

AK10

VSS78

AK7

VSS79

AK4

VSS80

AJ25

VSS81

AJ22

VSS82

AJ19

VSS83

AJ16

VSS84

AJ13

VSS85

AJ10

VSS86

AJ7

VSS87

AJ4

VSS88

AJ3

VSS89

AJ2

VSS90

AJ1

VSS91

AH35

VSS92

AH34

VSS93

AH32

VSS94

AH30

VSS95

AH29

VSS96

AH28

VSS97

AH26

VSS98

AH25

VSS99

AH22

VSS100

AH19

VSS101

AH16

VSS102

AH7

VSS103

AH4

VSS104

AG9

VSS105

AG8

VSS106

AG4

VSS107

AF6

VSS108

AF5

VSS109

AF3

VSS110

AF2

VSS111

AE35

VSS112

AE34

VSS113

AE33

VSS114

AE32

VSS115

AE31

VSS116

AE30

VSS117

AE29

VSS118

AE28

VSS119

AE27

VSS120

AE26

VSS121

AE9

VSS122

AD7

VSS123

AC9

VSS124

AC8