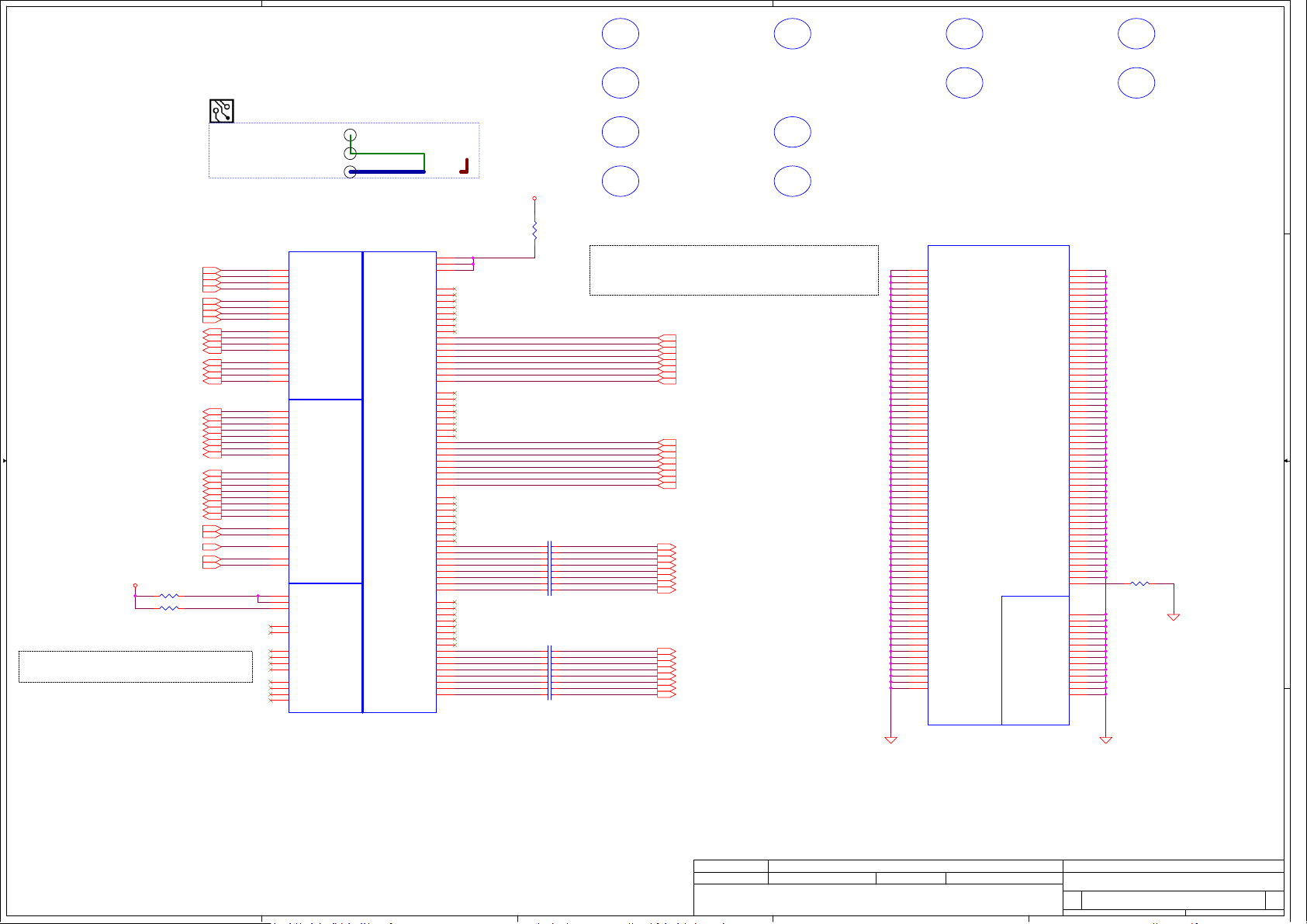

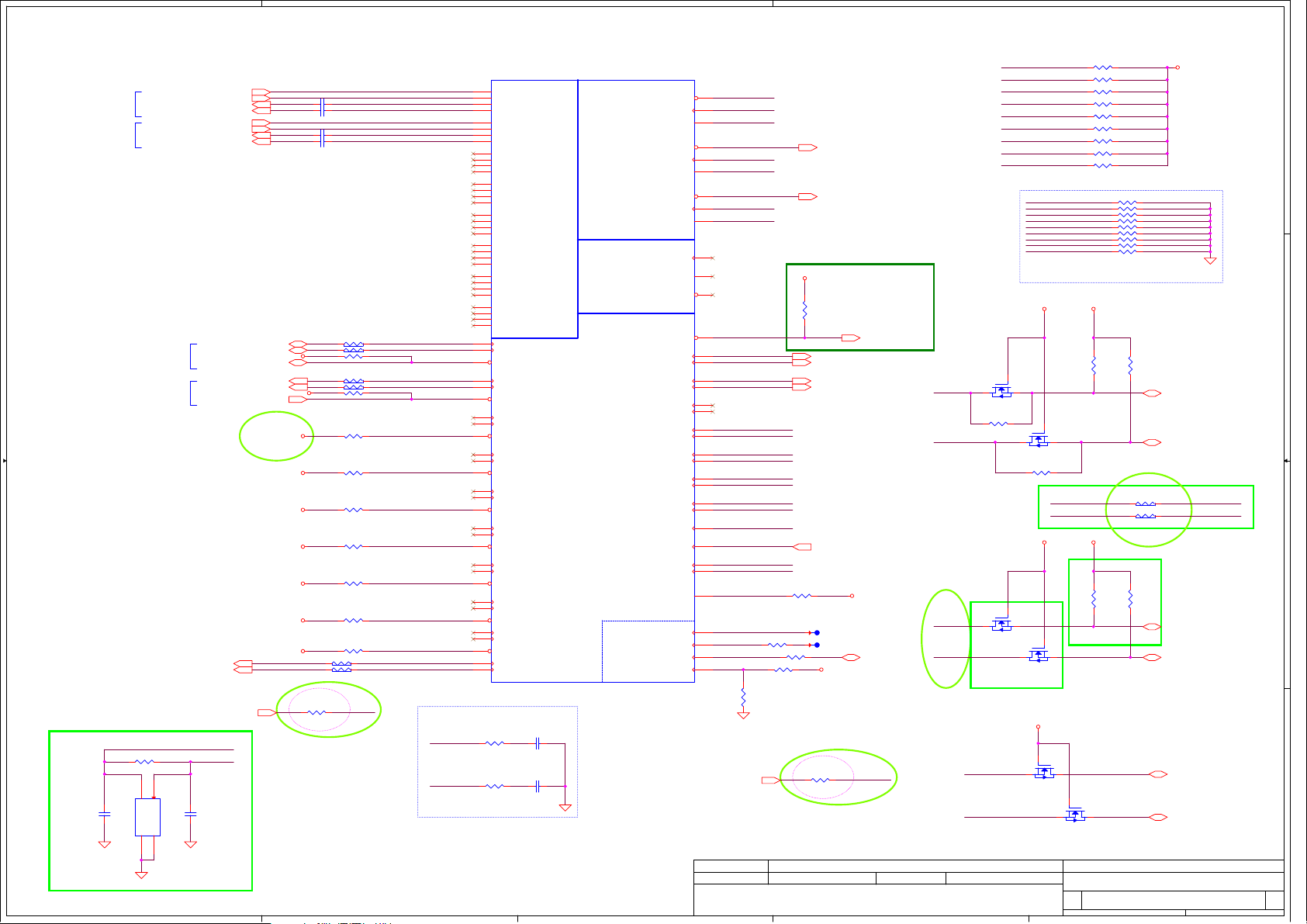

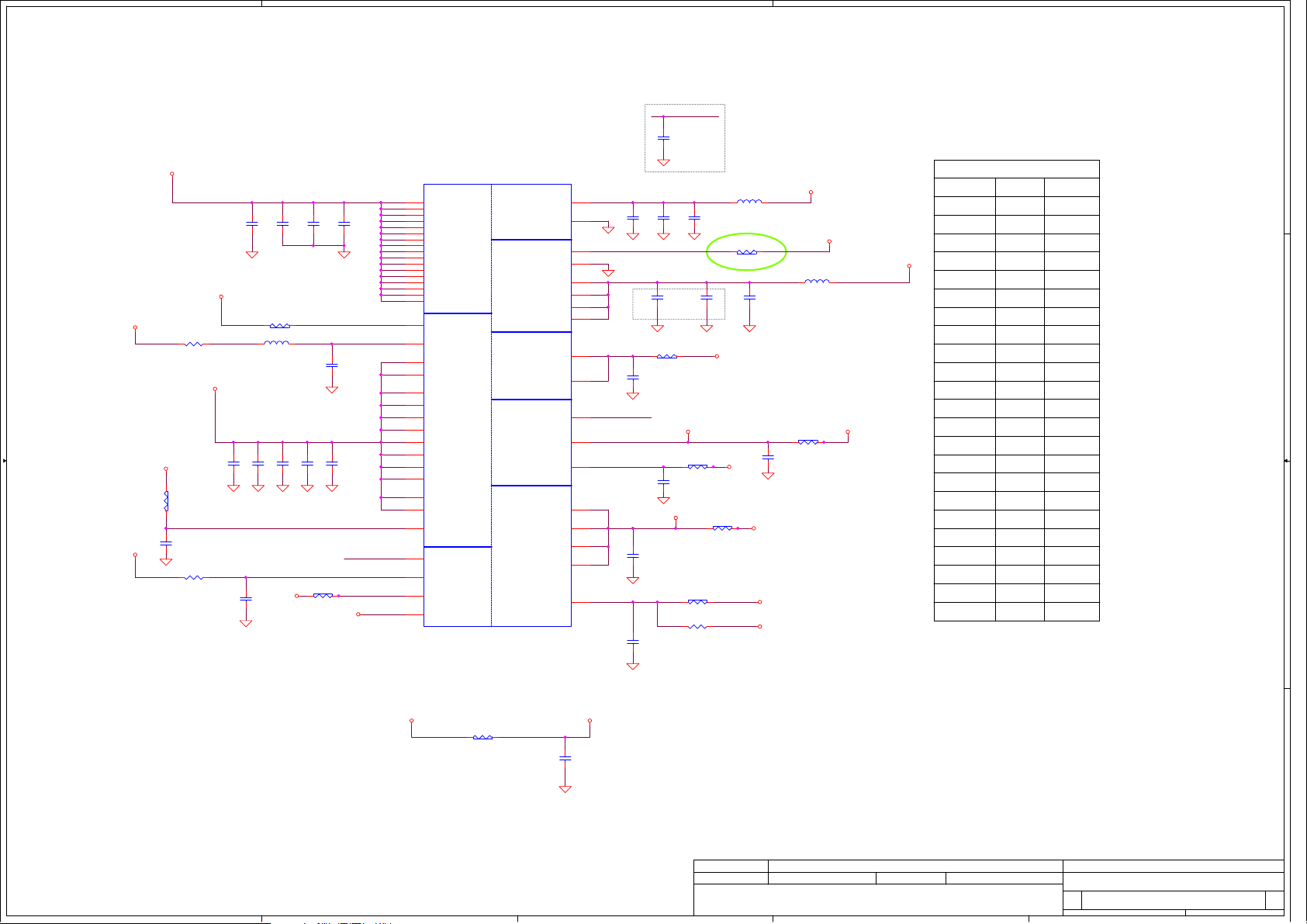

Compal LA-9104P VAW00, Inspiron 15 3521 Schematic

A

B

C

D

E

MODEL NAME : VAW00

ZZZ

R1@

ZZZ

GCER3@

ZZZ

TRIR3@

PROJECT CODE : ANRVAW0000

1 1

DA60000VV00 LA-9104P M/B

DA40001FO00 LS-9101P POWER BUTTON/B

PCB NO : LA-9104P (Thames XT )

PCB VAW00 LA-9104P LS-9101P/9102P/9103P

DAZ0SZ00200

PCB VAW00 LA-9104P LS-9101P/9102P/9103P GOLD A31 !

DAZ0SZ00201

ZZZ

HANNR3@

PCB VAW00 LA-9104P LS-9101P/9102P/9103P TRIPOD A31 !

DAZ0SZ00202

ZZZ

ZDTR3@

DA40001FP00 LS-9102P USB/B

DA40001FQ00 LS-9103P TP BUTTON/B

PCB VAW00 LA-9104P LS-9101P/9102P/9103P HANNSTARB A31 !

DAZ0SZ00203

PCB VAW00 LA-9104P LS-9101P/9102P/9103P ZDT A31 !

DAZ0SZ00204

Dell / Compal Confidential

2 2

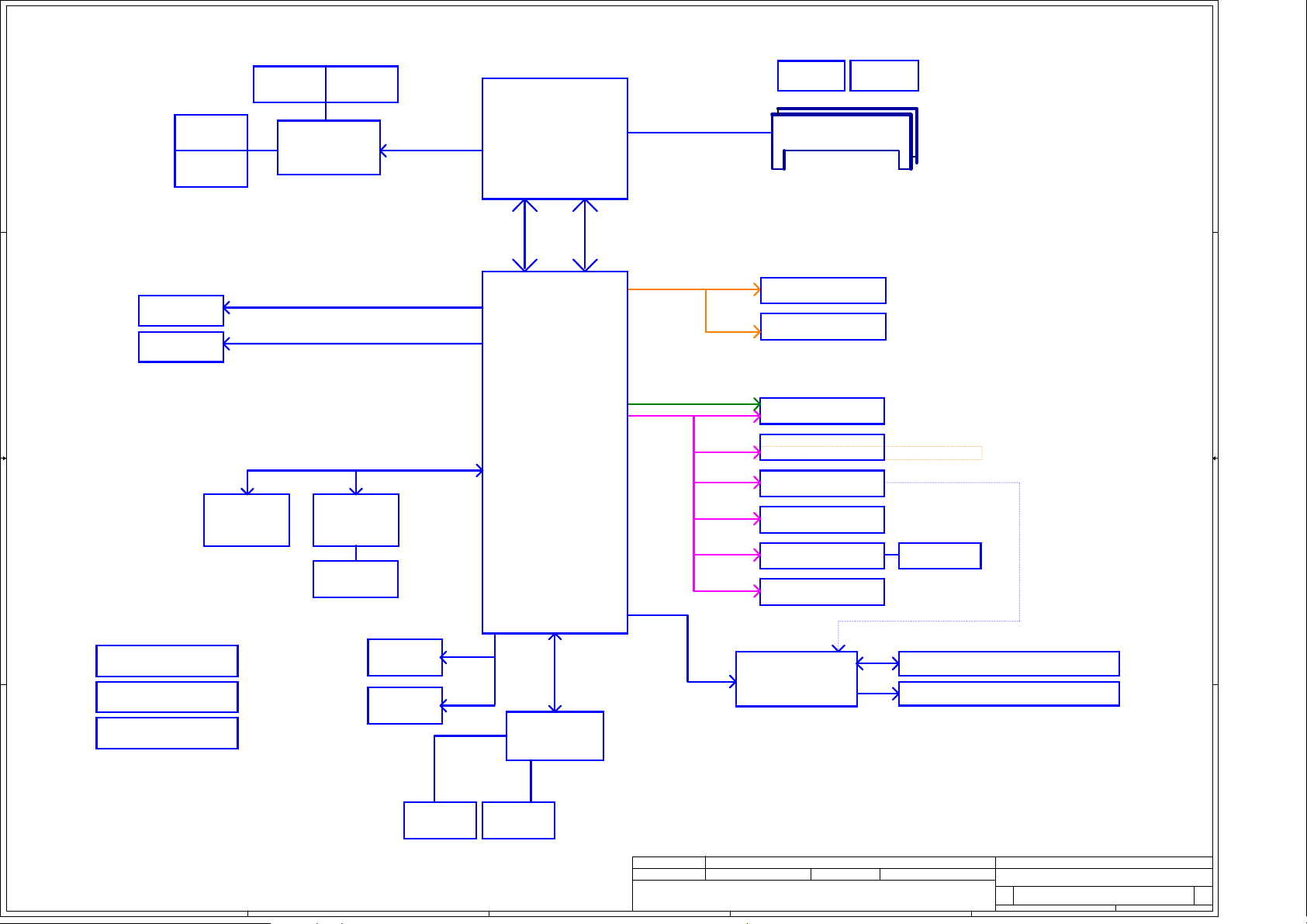

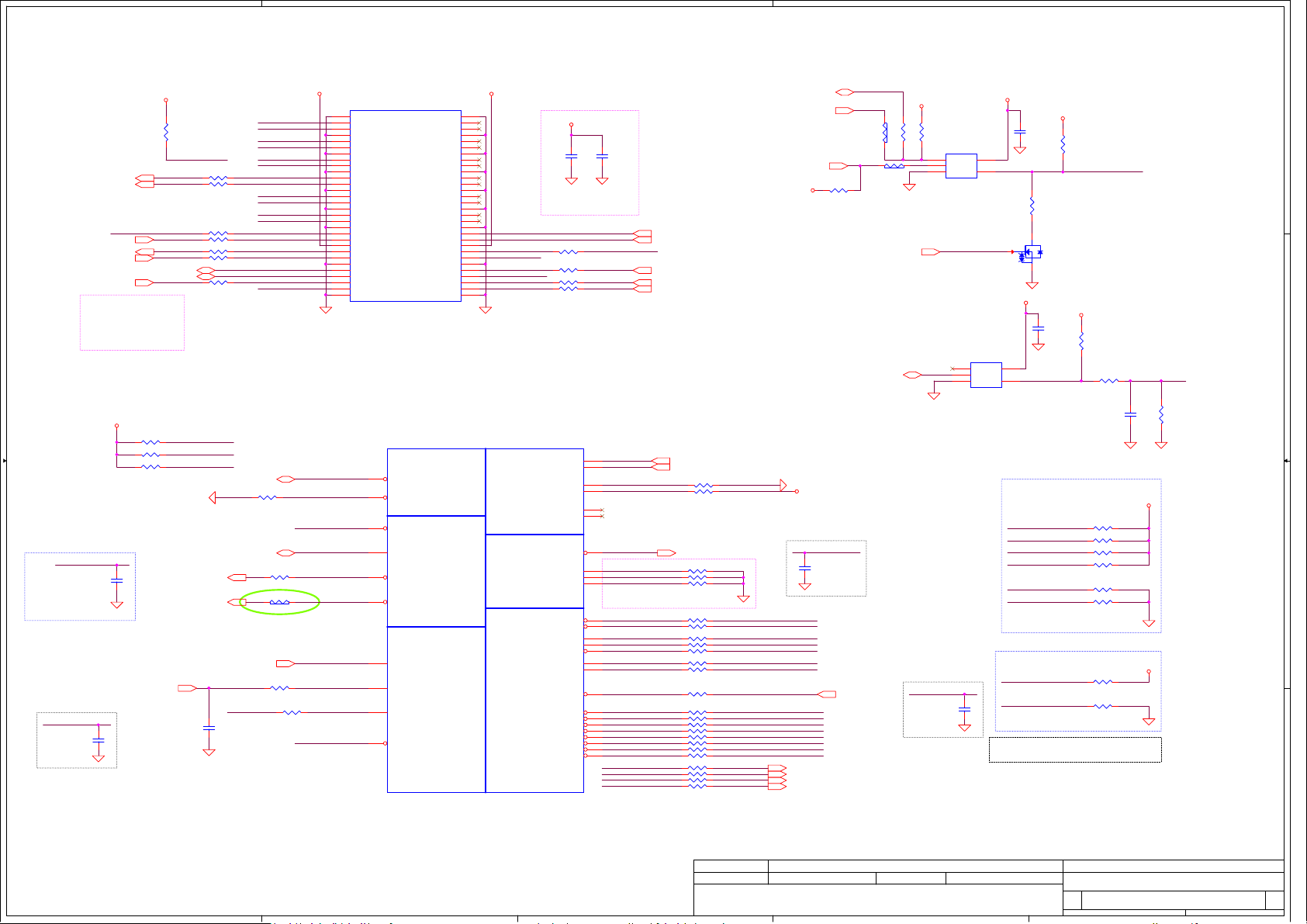

Ivy Bridge(BGA) + Panther Point

OAK 15" UMA/DIS AMD Thames XT

Schematic Document

Intel Chief River

2012-08-22

3 3

46@ : for 46 level

@ : Nopop Component

CONN@ : Connector Component

R1@ : R1 P/N

R3@ : R3 P/N

KB9012@ : ENE KB9012 Implemented

UMA@ : Only for UMA

EMC@ : EMI/ESD parts

Rev: 1.0

i3R1@ : CPU i3-3217 1.8G

i3VOSR1@ : CPU i3-2365 1.4G

i5R1@ : CPU i5-3317 1.7G

i7R1@ : CPU i7-3517 1.9G

CELR1@ : CPU Celeron 887 1.5G

PENR1@ : CPU Pentium 997 1.6G

DIS@ : Only for Discrete

TH@/THR1@ : Thames-XT

MS@/MSR1@ : Mars Pro

X76@ :

SPI-ROM & VRAM Group

GCLK@ : Green CLK implemented

GCLKUMA@ : Green CLK for UMA

GCLKDIS@ : Green CLK for DIS

XTAL@ : X'tal implemented

XTALDIS@ : X'tal with DIS implemented

A

B

C

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2012/08/22 2013/08/31

2012/08/22 2013/08/31

2012/08/22 2013/08/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-9104P

LA-9104P

LA-9104P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

1 57Wednesday, August 29, 2012

1 57Wednesday, August 29, 2012

1 57Wednesday, August 29, 2012

1.0

1.0

1.0

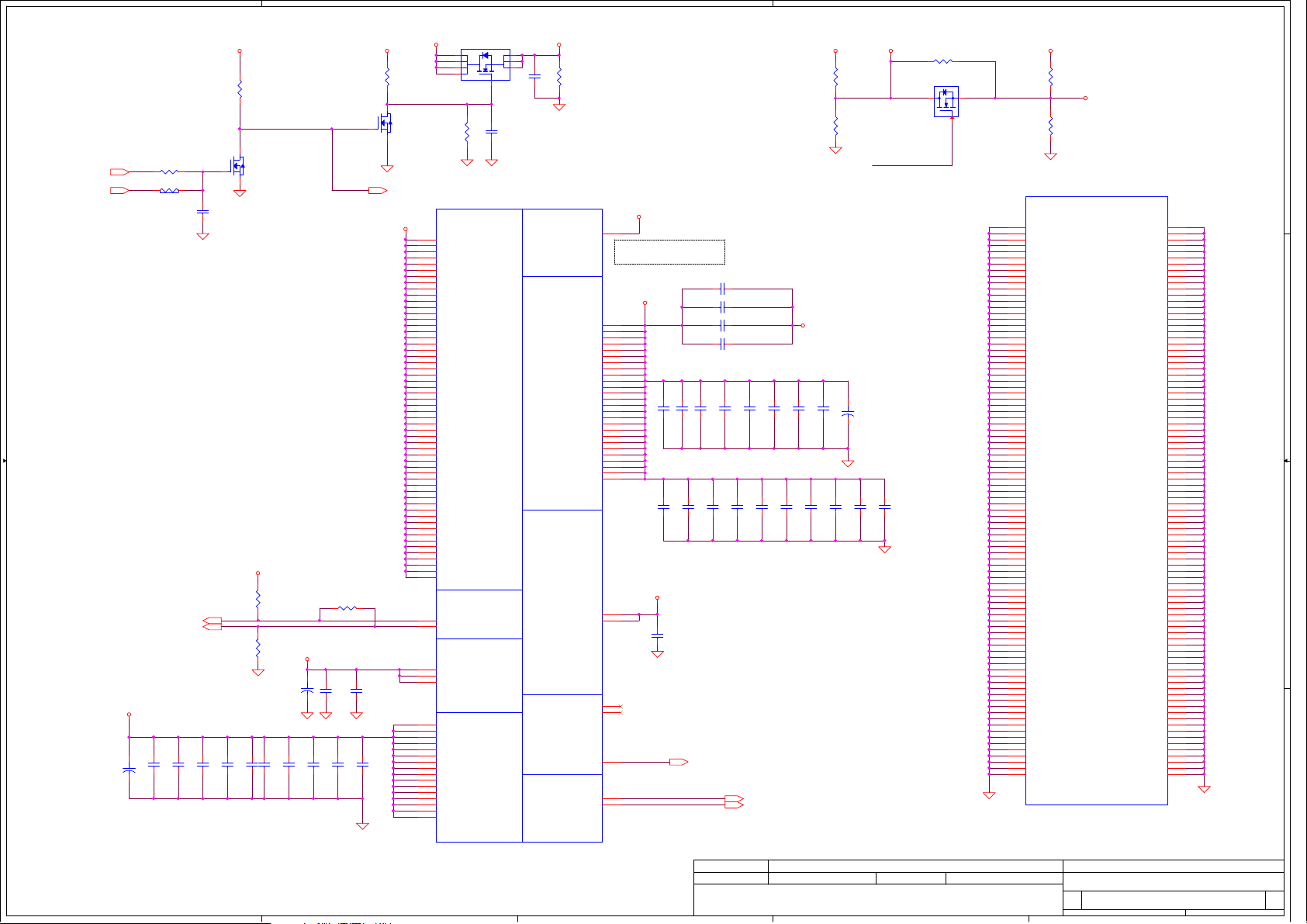

4

A

64M*16

V

RAM * 4

DDR3

1 1

64M*16

RAM * 4

V

DDR3

128M*16

RAM * 4

V

DDR3

P.31

P.31

4bit

6

P.30

AMD

Thames-XT

24-26 W

A

MD Thames XT, 128b,

B

128M*16

VRAM * 4

DDR3

64bit

P.24~29

P.30

PEG 2.0 x8

Intel

vy Bridge

I

Processor

17W DC

BGA 1023

C

emory Bus (DDR3)

M

1.5V DDR3 1333 MHz

P.5~10

Dual Channel

D

Fan Control

DDRIII-DIMM X2

BANK 0, 1, 2, 3, 4 ,5 ,6 ,7

P.40

C

Conn.

8GB Max

E

PU XDP

P.6

P.11~12

Radeon HD7670M,

P5500

1GB DDR3 (8-64Mx16),

2

GB DDR3 (8-128Mx16)

100MHz 100M

2.7GT/s

DMI x4FDI x8

5GB/s

Hz

SATA3.0

LVDS Conn.

LVDS

P.21

HDMI

2 2

HDMI Conn.

P.22

I

ntel

Port 0

Port 2

SATA HDD Conn.

SATA ODD Conn.

P.35

P.35

Panther Point

PCH HM76

USB 3.0

USB2.0

PCI-E x1

Port 2

M

ini Card

WLAN/BT4.0

Half

3 3

P.38

E

R

thernet

TL8105E

RJ45

Port 1

P.32

P.32

BGA 989 Balls

HD Audio

13~20

P

RTC CKT.

Power On/Off CKT.

DC/DC Interface CKT.

P.44

P.40

P.41

SPI ROM

4MB

SPI ROM

MB

2

P.13

P.13

SPI

S

LPC Bus

PI

33MHz

ENE KBC

KB9012

P.39

Port 1,2

Port 0,1

Port 2,3

Port 11

Port 8

Port 10

Port 9

USB 3.0 Conn. 1

USB 3.0 Conn. 2

USB 3.0 Conn. 3

USB 2.0 Conn. 4

Digital Camera

(With Digital MIC)

Mini Card

W

LAN (Half)

Card Reader

R

TS5179

Touch Screen

Digital Mic.

A

udio Codec

ALC3221

P.33

P.36

P

.37

Daughter board

P.21

P.38

3 in 1 Socket

P.34

P.21

P.34

Headphone Jack / Mic. Jack combo

Int. Speaker R / L

P

P.33

.33

4 4

PS/2

Int.KBD

A

B

P.40

Touch Pad

P.40

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

C

2012/08/22 2013/08/31

2012/08/22 2013/08/31

2012/08/22 2013/08/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block diagram

Block diagram

Block diagram

LA-9104P

LA-9104P

LA-9104P

E

2 57Wednesday, August 29, 2012

2 57Wednesday, August 29, 2012

2 57Wednesday, August 29, 2012

1.0

1.0

1.0

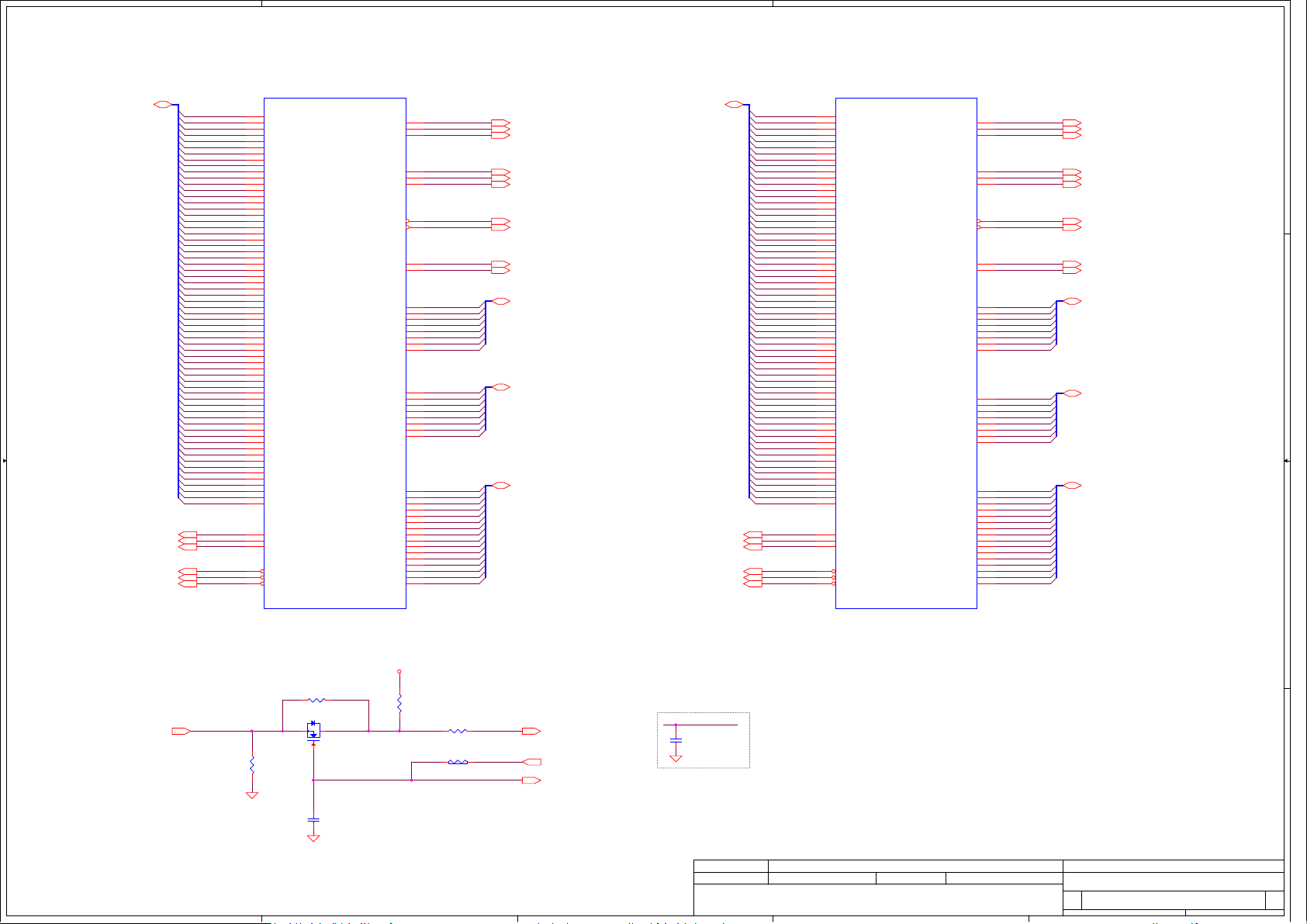

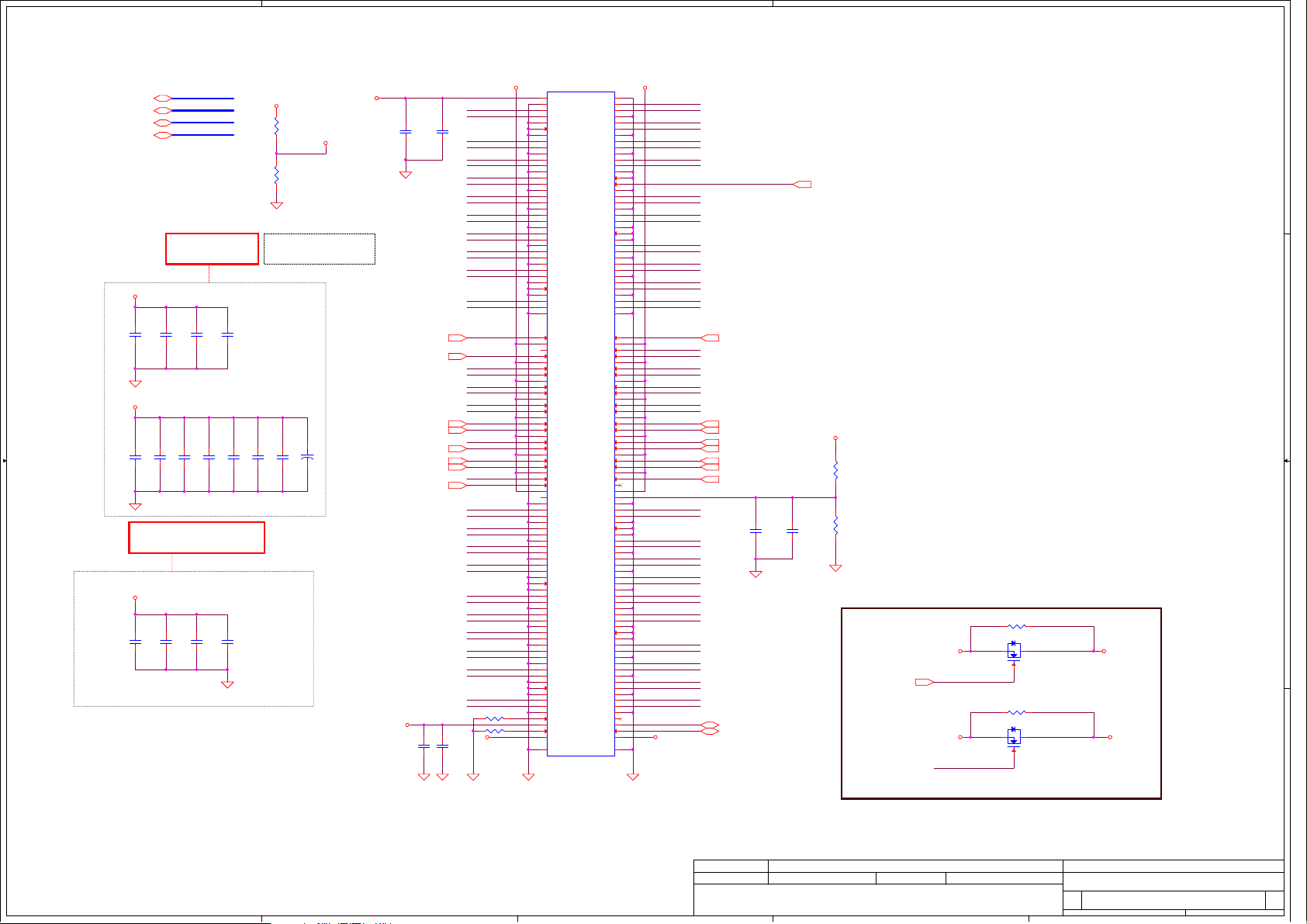

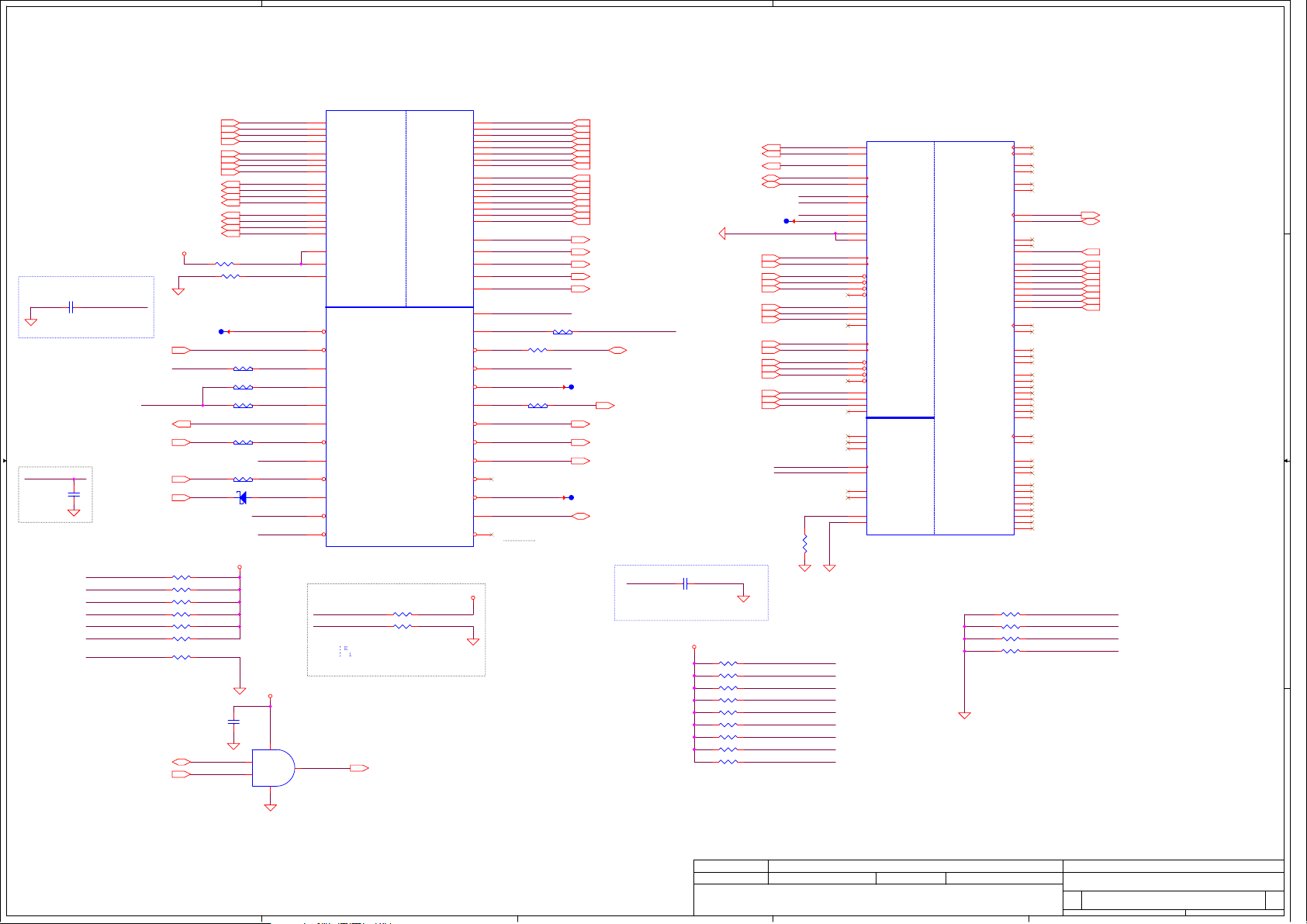

A

B

C

D

E

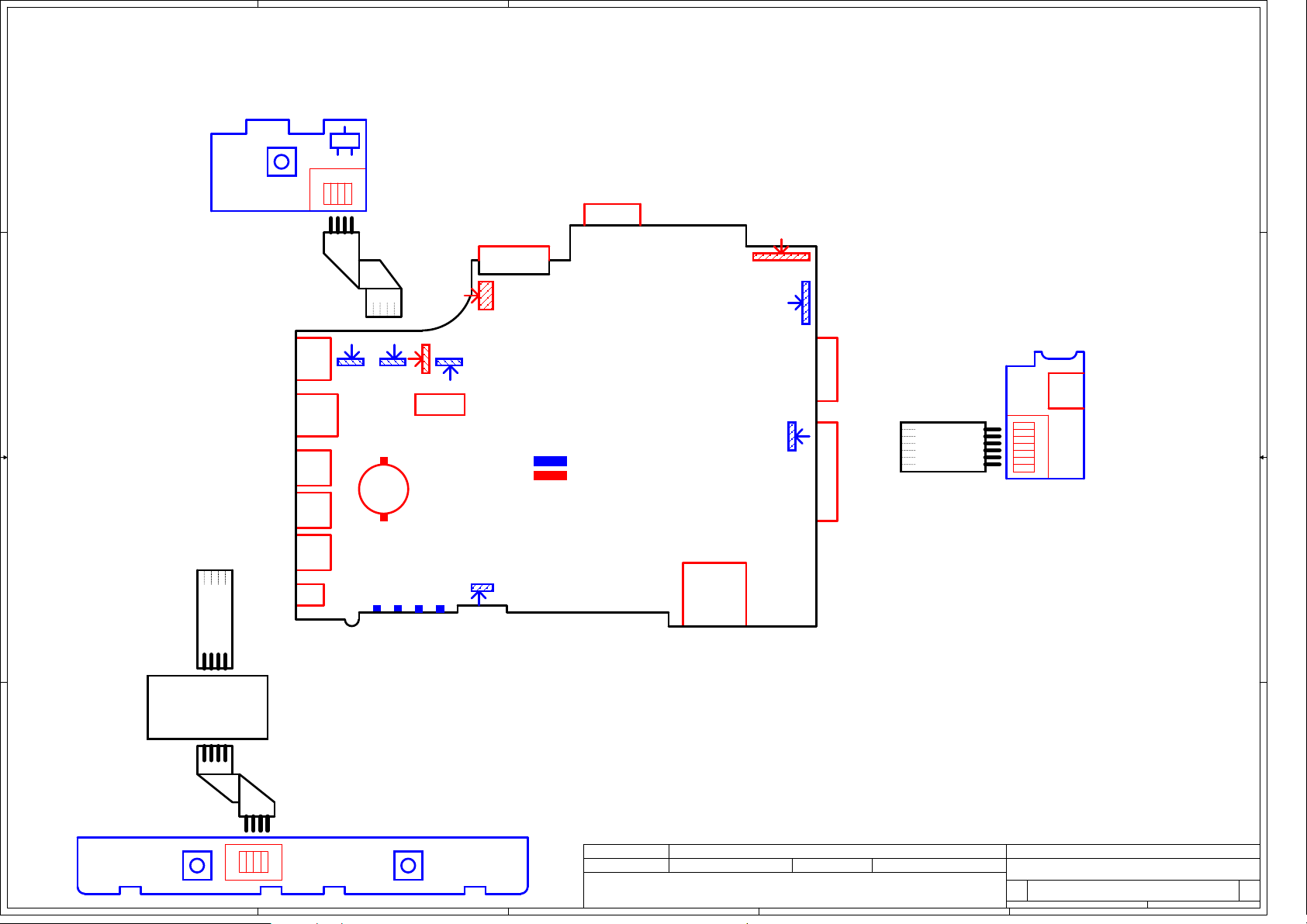

Compal Confidential

Project Code : VAW00

File Name : LA-9104P

1 1

LS-9101P (PWR/B)

Lid

UE5

(SA00003VQ00)

SW1

(SN100004Y00)

4 pin-Hot Bar

PBATT

Battery

PWR-BTN FFC

2 2

3 3

TP-MB FFC

6 pin

JHDMI

JLAN

JUSB1

JUSB2

JUSB3

JHP

4 pin

HDMI

RJ-45

USB

USB

USB

HP

JTOUCH

6 pin

JPWR

4 pin

JFAN

3 pin

RTC JRTC

2 pin

Led1

Led3

Led2

XDP

JXDP

Led4

JTP

6 pin

JMINI

MINI Card

PJPDC

5 pin

LA-9104P M/B

(OAK 15")

JSPK

4 pin

Top Side

Bottom Side

JLVDS

40 pin

JREAD

Card

Reader

JKB

30 pin

JDB

8 pin

JODD

JHDD

USB-DB FFC

8 pin

LS-9102P (USB/B)

USB

8 pin

Hot Bar

JUSB4

TP-Module

4 4

TP-BTN FFC

4 pin

A

4 pin

Hot Bar

SW2 S

B

LS-9103P (TP-BTN/B)

W3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2012/08/22 2013/08/31

2012/08/22 2013/08/31

2012/08/22 2013/08/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Compal Electronics, Inc.

DB block diagram

DB block diagram

DB block diagram

LA-9104P

LA-9104P

LA-9104P

E

3 57Wednesday, August 29, 2012

3 57Wednesday, August 29, 2012

3 57Wednesday, August 29, 2012

1.0

1.0

1.0

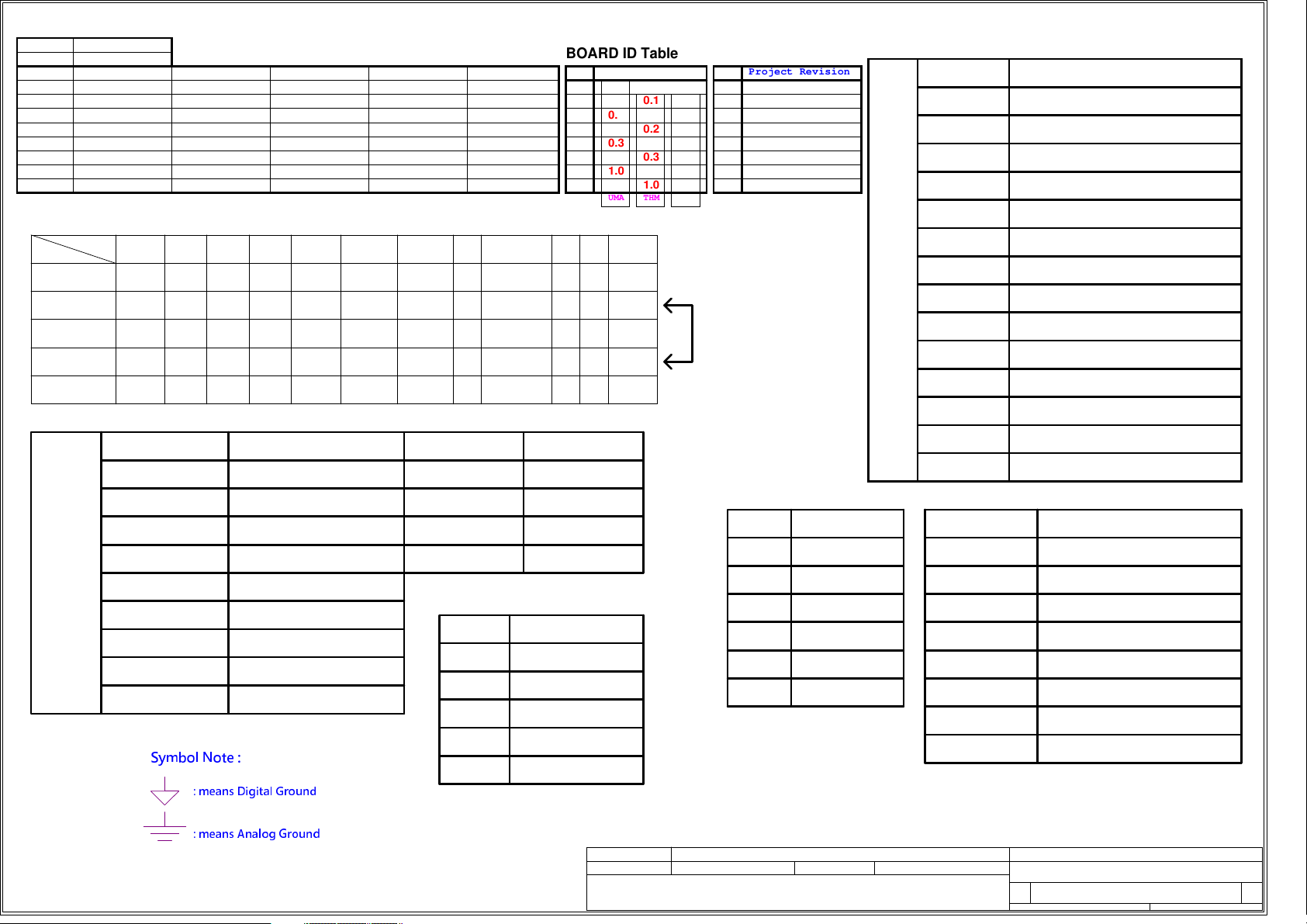

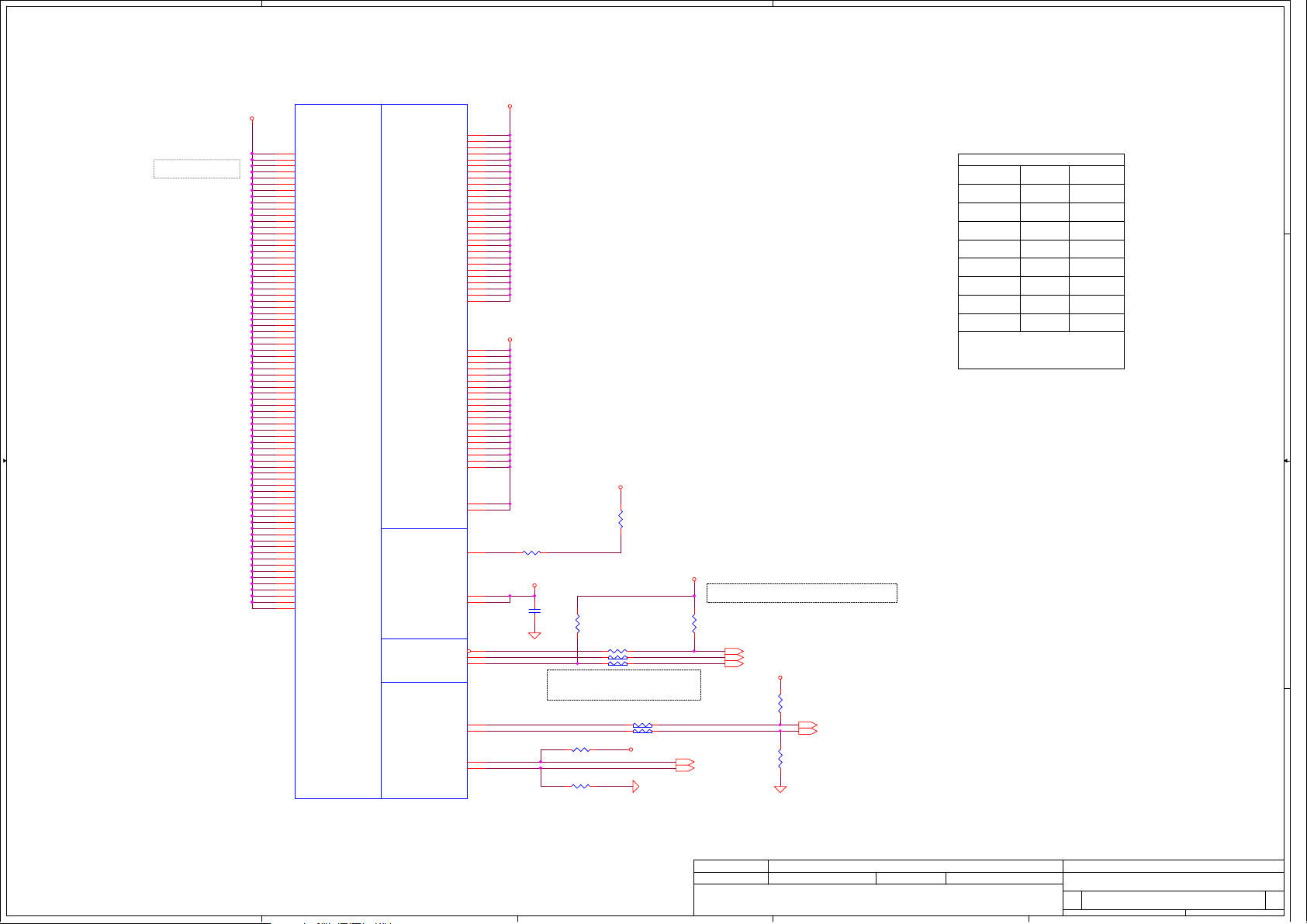

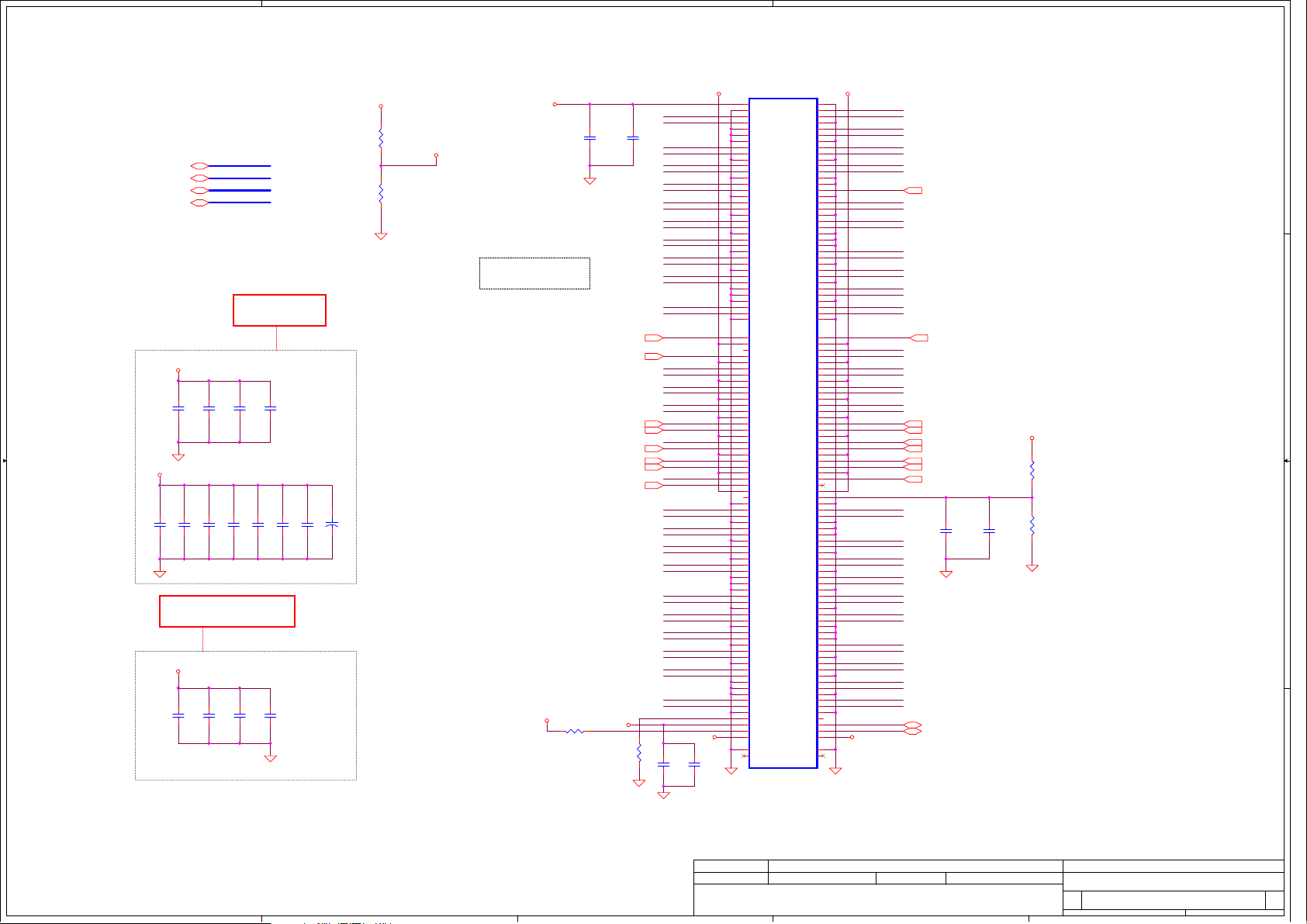

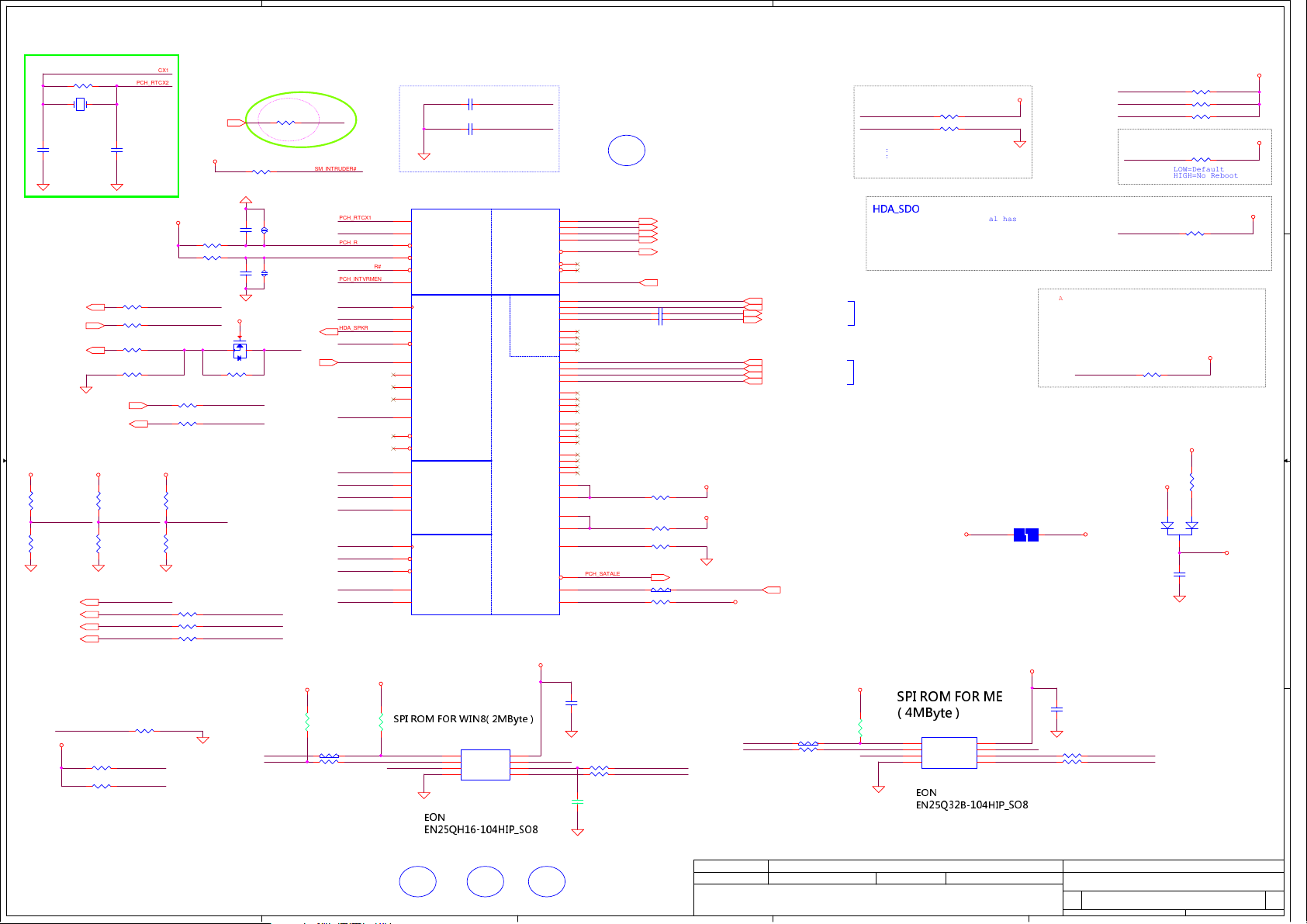

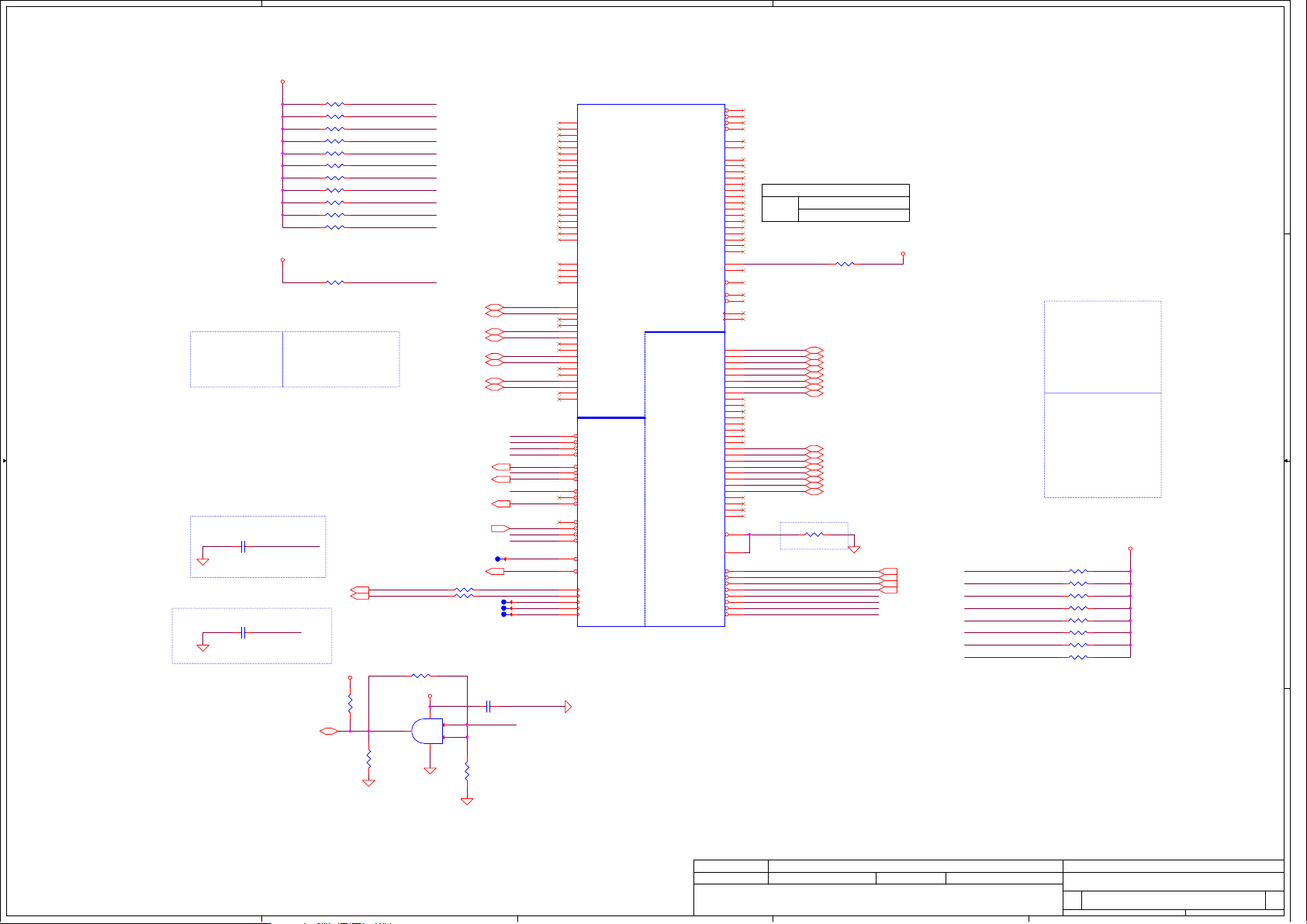

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7

SMBUS Control Table

100K +/- 5%Ra

Rb V min

0 0 V

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

NC

SOURCE

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SML0CLK PCH

PCH_SML0DATA

PCH_SML1CL K

PCH_SML1DA TA

MEM_SMBCLK

MEM_SMBDAT A

KB9012

KB9012

PCH

PCH

AD_BID

0.168 V

0.375 V 0.503 V

.634 V

0

0.958 V

1.372 V

1.851 V 2.200 V

2.433 V

MINI1 BATT SODIMM

MINI2

V typ

AD_BID

V

0 V 0.155 V

0.250 V

0.819 V

1.185 V

1.650 V

3.300 V

Express

Card

V

VV V

V

AD_BID

0.362 V

0.621 V

0.945 V

1.359 V

1.838 V

2.420 V

3.300 V

max

Thermal

Sensor

EC AD3

0x00-0x0C

0x0D-0x1C

0x1D-0x30

0x31-0x49

0x4A-0x69

0x6A-0x8E

0x8F-0xBB

0xBC-0xFF

VGA Thermal

FFS VGA

Sensor

V

V

V

A

BOARD ID Table

ID

PCB Revision

0

0.1

1

2

3

4

5

6

7

XDP

0.1

0.2

0.2

0.3

0.3

1.0

1.0

UMA THM

Charger

V

V

Project ID Table

ID

0

0.1

0.2

0.3

1.0

MARS

1

2

3

4

5

6

7

Link

Project Revision

UMA

DIS THAMES

DIS MARS PRO

PCH

USB PORT#

0

1

2

3

4

5

6

7

8

9

10

11

DESTINATION

USB conn.2

USB conn.1

USB conn.3

USB conn.4 (DB)

NC

NC

NC

NC

MINI CARD (WLAN)

Touch Screen

Card Reader

Camera

1 1

CLKOUT_PCIE0

CLKOUT_PCIE1

CLKOUT_PCIE2

CLK

CLKOUT_PCIE3

CLKOUT_PCIE4

CLKOUT_PCIE5

CLKOUT_PCIE6

DESTINATIONDIFFERENTIAL

10/100 LAN

MINI CARD WLAN

None

None

None

None

None

CLKOUT_PCIE7 None

CLKOUT_PEG_B

None

FLEX CLOCKS DESTINATION

CLKOUTFLEX0

CLKOUTFLEX1

CLKOUTFLEX2

CLKOUTFLEX3

CLKOUT

PCI0

PCI1

PCI2

PCI3

None

None

None

None

DESTINATION

PCH_LOOPBACK

EC LPC

None

None

SATA

SATA0

SATA1

SATA2

SATA3

SATA4

SATA5

DESTINATION

HDD

None

ODD

None

None

None None

Symbol Note :

PCI4

: means Digital Ground

: means Analog Ground

None

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

A

2012/08/22 2013/08/31

2012/08/22 2013/08/31

2012/08/22 2013/08/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

12

13

PCI EXPRESS

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8 None

NC

NC

DESTINATION

10/100 LAN

MINI CARD (WLAN)

None

None

None

None

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-9104P

LA-9104P

LA-9104P

4 57Wednesday, August 29, 2012

4 57Wednesday, August 29, 2012

4 57Wednesday, August 29, 2012

1.0

1.0

1.0

5

(1)PEG_RCOMPO (G4) use 4mil connect to PEG_ICOMPI, then use 4mil connect to RC1.

D D

(2)PEG_ICOMPO use 12mil connect to RC1

PEG_RCOMPO (G4)

PEG_ICOMPI (G3)

Trace length

M

ax is 500 mils

DMI_CRX_PTX_N0<15>

DMI_CRX_PTX_N1<15>

DMI_CRX_PTX_N2<15>

DMI_CRX_PTX_N3<15>

DMI_CRX_PTX_P0<15>

DMI_CRX_PTX_P1<15>

DMI_CRX_PTX_P2<15>

DMI_CRX_PTX_P3<15>

DMI_CTX_PRX_N0<15>

DMI_CTX_PRX_N1<15>

C C

B B

eDP_COMPIO and ICOMPO signals should be shor ted near

balls and route d with typical impedance <25 mohms

DMI_CTX_PRX_N2<15>

DMI_CTX_PRX_N3<15>

DMI_CTX_PRX_P0<15>

DMI_CTX_PRX_P1<15>

DMI_CTX_PRX_P2<15>

DMI_CTX_PRX_P3<15>

FDI_CTX_PRX_N0<15>

FDI_CTX_PRX_N1<15>

FDI_CTX_PRX_N2<15>

FDI_CTX_PRX_N3<15>

FDI_CTX_PRX_N4<15>

FDI_CTX_PRX_N5<15>

FDI_CTX_PRX_N6<15>

FDI_CTX_PRX_N7<15>

FDI_CTX_PRX_P0<15>

FDI_CTX_PRX_P1<15>

FDI_CTX_PRX_P2<15>

FDI_CTX_PRX_P3<15>

FDI_CTX_PRX_P4<15>

FDI_CTX_PRX_P5<15>

FDI_CTX_PRX_P6<15>

FDI_CTX_PRX_P7<15>

FDI_FSYNC0<15>

FDI_FSYNC1<15>

FDI_INT<15>

FDI_LSYNC0<15>

FDI_LSYNC1<15>

+VCCP

RC36 24.9_0402_1%

RC158 10K_0402_5%

1 2

@

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

+EDP_COM

12

PEG_ICOMPO (G1)

UC1A

i5R1@

M2

DMI_RX#[0]

P6

DMI_RX#[1]

P1

DMI_RX#[2]

P10

DMI_RX#[3]

N3

DMI_RX[0]

P7

DMI_RX[1]

P3

DMI_RX[2]

P11

DMI_RX[3]

K1

DMI_TX#[0]

M8

DMI_TX#[1]

N4

DMI_TX#[2]

R2

DMI_TX#[3]

K3

DMI_TX[0]

M7

DMI_TX[1]

P4

DMI_TX[2]

T3

DMI_TX[3]

U7

FDI0_TX#[0]

W11

FDI0_TX#[1]

W1

FDI0_TX#[2]

AA6

FDI0_TX#[3]

W6

FDI1_TX#[0]

V4

FDI1_TX#[1]

Y2

FDI1_TX#[2]

AC9

FDI1_TX#[3]

U6

FDI0_TX[0]

W10

FDI0_TX[1]

W3

FDI0_TX[2]

AA7

FDI0_TX[3]

W7

FDI1_TX[0]

T4

FDI1_TX[1]

AA3

FDI1_TX[2]

AC8

FDI1_TX[3]

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

eDP_COMPIO

AD2

eDP_ICOMPO

AG11

eDP_HPD#

AG4

eDP_AUX#

AF4

eDP_AUX

AC3

eDP_TX#[0]

AC4

eDP_TX#[1]

AE11

eDP_TX#[2]

AE7

eDP_TX#[3]

AC1

eDP_TX[0]

AA4

eDP_TX[1]

AE10

eDP_TX[2]

AE6

eDP_TX[3]

AV8063801058002-SR0N8-L1-1.7G_BGA1023~D

4

R_COMP place close to CPU

width 4 mils

width 12 mils

SA00005K63L

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

DMI Intel(R) FDI

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PCI EXPRESS -- GRAPHICS

eDP

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

R

_COMP

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

VCC_IO

PEG_COMP

PEG_GTX_C_HRX_N7

PEG_GTX_C_HRX_N6

PEG_GTX_C_HRX_N5

PEG_GTX_C_HRX_N4

PEG_GTX_C_HRX_N3

PEG_GTX_C_HRX_N2

PEG_GTX_C_HRX_N1

PEG_GTX_C_HRX_N0

PEG_GTX_C_HRX_P7

PEG_GTX_C_HRX_P6

PEG_GTX_C_HRX_P5

PEG_GTX_C_HRX_P4

PEG_GTX_C_HRX_P3

PEG_GTX_C_HRX_P2

PEG_GTX_C_HRX_P1

PEG_GTX_C_HRX_P0

PEG_HTX_GRX_N7

PEG_HTX_GRX_N6

PEG_HTX_GRX_N5

PEG_HTX_GRX_N4

PEG_HTX_GRX_N3

PEG_HTX_GRX_N2

PEG_HTX_GRX_N1

PEG_HTX_GRX_N0

PEG_HTX_GRX_P7

PEG_HTX_GRX_P6

PEG_HTX_GRX_P5

PEG_HTX_GRX_P4

PEG_HTX_GRX_P3

PEG_HTX_GRX_P2

PEG_HTX_GRX_P1

PEG_HTX_GRX_P0

+VCCP

12

RC2

24.9_0402_1%

1 2

CC9 220nF_0402_16V7KDIS@

1 2

CC10 220nF_0402_16V7KDIS@

1 2

CC11 220nF_0402_16V7KDIS@

1 2

CC12 220nF_0402_16V7KDIS@

1 2

CC13 220nF_0402_16V7KDIS@

1 2

CC14 220nF_0402_16V7KDIS@

1 2

CC15 220nF_0402_16V7KDIS@

1 2

CC16 220nF_0402_16V7KDIS@

1 2

CC25 220nF_0402_16V7KDIS@

1 2

CC26 220nF_0402_16V7KDIS@

1 2

CC27 220nF_0402_16V7KDIS@

1 2

CC28 220nF_0402_16V7KDIS@

1 2

CC29 220nF_0402_16V7KDIS@

1 2

CC30 220nF_0402_16V7KDIS@

1 2

CC31 220nF_0402_16V7KDIS@

1 2

CC32 220nF_0402_16V7KDIS@

3

UC1

i3R1@

SA00005L52L

AV8063801058401-SR0N9-L1-1.8G_BGA1023~D

UC1

i5R3@

UC1

i3R3@

SA00005L53L

AV8063801058401-SR0N9-L1-1.8G_BGA1023~D

SA00005K62L

AV8063801058002-SR0N8-L1-1.7G_BGA1023~D

UC1

CELR1@

S

A00006021L

AV8062701085401-SR0VA-Q0-1.5G_BGA1023~D

UC1

PENR1@

SA00005ZZ1L

AV8062701084801-SR0V5-Q0-1.6G_BGA1023~D

PEG_ICOMPI and RCOMPO signals should be shor ted and routed

with - max leng th = 500 mils - typical imped ance = 43 mohms

PEG_ICOMPO sign als should be routed with - m ax length = 500 mils

- typical imped ance = 14.5 mo hms

PEG_GTX_C_HRX_N7 <24>

PEG_GTX_C_HRX_N6 <24>

PEG_GTX_C_HRX_N5 <24>

PEG_GTX_C_HRX_N4 <24>

PEG_GTX_C_HRX_N3 <24>

PEG_GTX_C_HRX_N2 <24>

PEG_GTX_C_HRX_N1 <24>

PEG_GTX_C_HRX_N0 <24>

PEG_GTX_C_HRX_P7 <24>

PEG_GTX_C_HRX_P6 <24>

PEG_GTX_C_HRX_P5 <24>

PEG_GTX_C_HRX_P4 <24>

PEG_GTX_C_HRX_P3 <24>

PEG_GTX_C_HRX_P2 <24>

PEG_GTX_C_HRX_P1 <24>

PEG_GTX_C_HRX_P0 <24>

PEG_HTX_C_GRX_N7 <24>

PEG_HTX_C_GRX_N6 <24>

PEG_HTX_C_GRX_N5 <24>

PEG_HTX_C_GRX_N4 <24>

PEG_HTX_C_GRX_N3 <24>

PEG_HTX_C_GRX_N2 <24>

PEG_HTX_C_GRX_N1 <24>

PEG_HTX_C_GRX_N0 <24>

PEG_HTX_C_GRX_P7 <24>

PEG_HTX_C_GRX_P6 <24>

PEG_HTX_C_GRX_P5 <24>

PEG_HTX_C_GRX_P4 <24>

PEG_HTX_C_GRX_P3 <24>

PEG_HTX_C_GRX_P2 <24>

PEG_HTX_C_GRX_P1 <24>

PEG_HTX_C_GRX_P0 <24>

UC1

CELR3@

SA00006022L

AV8062701085401-SR0VA-Q0-1.5G_BGA1023~D

UC1

PENR3@

SA00005ZZ2L

AV8062701084801-SR0V5-Q0-1.6G_BGA1023~D

2

UC1

i3VOSR1@

AV8062701313000-SR0U3-J1-1.4G_BGA1023~D

UC1

i7R1@

AV8063801057605-SR0N6-L1-1.9G_BGA1023~D

UC1I

i5R1@

BG17

VSS[181]

BG21

VSS[182]

BG24

VSS[183]

BG28

VSS[184]

BG37

VSS[185]

BG41

VSS[186]

BG45

VSS[187]

BG49

VSS[188]

BG53

VSS[189]

BG9

VSS[190]

C29

VSS[191]

C35

VSS[192]

C40

VSS[193]

D10

VSS[194]

D14

VSS[195]

D18

VSS[196]

D22

VSS[197]

D26

VSS[198]

D29

VSS[199]

D35

VSS[200]

D4

VSS[201]

D40

VSS[202]

D43

VSS[203]

D46

D50

D54

D58

D6

E25

E29

E3

E35

E40

F13

F15

F19

F29

F35

F40

F55

G51

G6

G61

H10

H14

H17

H21

H4

H53

H58

J1

J49

J55

K11

K21

K51

K8

L16

L20

L22

L26

L30

L34

L38

L43

L48

L61

M11

M15

AV8063801058002-SR0N8-L1-1.7G_BGA1023~D

VSS[204]

VSS[205]

VSS[206]

VSS[207]

VSS[208]

VSS[209]

VSS[210]

VSS[211]

VSS[212]

VSS[213]

VSS[214]

VSS[215]

VSS[216]

VSS[217]

VSS[218]

VSS[219]

VSS[220]

VSS[221]

VSS[222]

VSS[223]

VSS[224]

VSS[225]

VSS[226]

VSS[227]

VSS[228]

VSS[229]

VSS[230]

VSS[231]

VSS[232]

VSS[233]

VSS[234]

VSS[235]

VSS[236]

VSS[237]

VSS[238]

VSS[239]

VSS[240]

VSS[241]

VSS[242]

VSS[243]

VSS[244]

VSS[245]

VSS[246]

VSS[247]

VSS[248]

VSS[249]

VSS

SA00005UH1L

SA00005K53L

VSS_NCTF_10

VSS_NCTF_11

NCTF

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

VSS[250]

VSS[251]

VSS[252]

VSS[253]

VSS[254]

VSS[255]

VSS[256]

VSS[257]

VSS[258]

VSS[259]

VSS[260]

VSS[261]

VSS[262]

VSS[263]

VSS[264]

VSS[265]

VSS[266]

VSS[267]

VSS[268]

VSS[269]

VSS[270]

VSS[271]

VSS[272]

VSS[273]

VSS[274]

VSS[275]

VSS[276]

VSS[277]

VSS[278]

VSS[279]

VSS[280]

VSS[281]

VSS[282]

VSS[283]

VSS[284]

VSS[285]

VSS[286]

VSS[287]

VSS[288]

VSS[289]

VSS[290]

VSS[291]

VSS[292]

VSS[293]

VSS[294]

VSS[295]

VSS[296]

VSS[297]

VSS[298]

VSS[299]

VSS[300]

VSS[301]

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

1

UC1

i3VOSR3@

AV8062701313000-SR0U3-J1-1.4G_BGA1023~D

UC1

i7R3@

AV8063801057605-SR0N6-L1-1.9G_BGA1023~D

M4

M58

M6

N1

N17

N21

N25

N28

N33

N36

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W13

W15

W18

W21

W46

W8

Y4

Y47

Y58

Y59

G48

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

@

RC20

1 2

1K_0402_5%

SA00005UH2L

SA00005K52L

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2012/08/22 2013/08/31

2012/08/22 2013/08/31

2012/08/22 2013/08/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

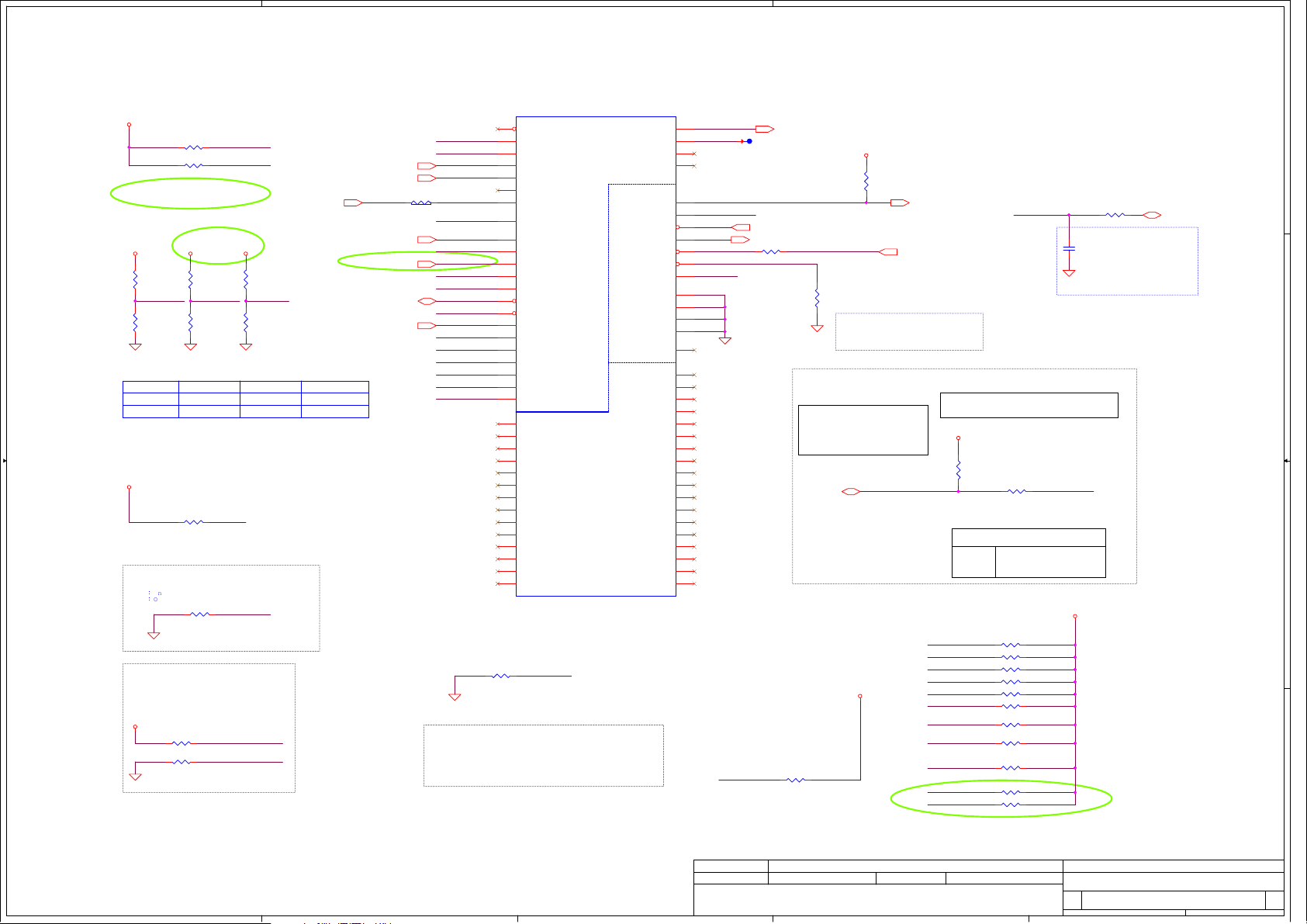

PROCESSOR(1/6) DMI,FDI,PEG

PROCESSOR(1/6) DMI,FDI,PEG

PROCESSOR(1/6) DMI,FDI,PEG

LA-9104P

LA-9104P

LA-9104P

1

5 57Wednesday, August 29, 2012

5 57Wednesday, August 29, 2012

5 57Wednesday, August 29, 2012

1.0

1.0

1.0

5

4

3

2

1

+3VALW

12

D D

CFG10<8>

CFG11<8>

H_CPUPWRGD H_CPUPWRGD_XDP

CFG0<8>

VGATE<15,52>

PCH_JTAG_TCK<13>

The resistor

for HOOK2 shoul d be

placed such tha t the

stub is very sm all

C C

B B

Place on BOTTOM(-4059,5169) area.

VDDPWRGOOD_R

Place close to CPU

A A

on CFG0 net

+VCCP

RC127 56_0402_1%

RC128 49.9_0402_1%~D

RC44 62_0402_5%~D

PROC_DETECT (Processor Detect): pulled to

ground on the processor package. There is no

connection to the processor silicon for this

signal. System board designers may use this

signal to determine if the processor is present

H_PECI

0.1U_0402_10V7K~D

0.1U_0402_25V6K

CC142

1

CC151

@

2

1

@

2

@

RC49

1K_0402_5%

SYS_PWROK_XDP

1 2

1 2

1 2

1 2

PCH_SMBDATA<11,12,14,38>

PCH_SMBCLK<11,12,14,38>

@

1 2

@

1 2

1 2

1 2

0_0402_5% @

H_THERMTRIP#

H_CATERR#

H_PROCHOT#

H_PROCHOT#<40,46>

place RC57 near CPU 300mils ~1530mils

H_THERMTRIP#<17>

place RC129 nea r CPU 250mils ~2530 mils

H_CPUPWRGD<17>

1

CC141

0.1U_0402_25V6K

@

2

ESD request to reserve CC141

12

RC130_0402_5% @

12

RC150_0402_5% @

RC221K_0402_5% @

RC310_0402_5% @

RC381K_0402_5% @

RC340_0402_5% @

RC30

H_SNB_IVB#<17>

RC124 10K_0402_5%@

H_PECI<17,40>

RC57 56_0402_1%

RC130 0_0402_1%

H_PM_SYNC<15>

+VCCP +VCCP

JXDP

1

GND0

XDP_PREQ#_R

XDP_PRDY#_R

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

CFG10_R

CFG11_R

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

CFD_PWRBTN#_XDP

SYS_PWROK_XDP

XDP_TCK1

XDP_TCK_R

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A0

11

OBSDATA_A1

13

GND4

15

OBSDATA_A2

17

OBSDATA_A3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B0

29

OBSDATA_B1

31

GND10

33

OBSDATA_B2

35

OBSDATA_B3

37

GND12

39

PWRGOOD/HOOK0

41

HOOK1

43

VCC_OBS_AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

SAMTE_BSH-030-01-L-D-A

CONN@

SP02000L900

UC1B

F49

PROC_SELECT #

12

H_CATERR#

VR1 TOPOLOGY

1 2

H_PROCHOT#_R

1 2

H_THERMTRIP#_R

@

H_PM_SYNC

1 2

VCCPWRGOOD_0_R

RC25 1K_0402_5%

RC64

1 2

130_0402_1%

BUF_CPU_RST#

VDDPWRGOOD_RVDDPWRGOOD

C57

PROC_DETEC T#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPW RGOOD

BE45

SM_DRAMPWR OK

D44

RESET#

AV8063801058002-SR0N8-L1-1.7G_BGA1023~D

OBSFN_C0

OBSFN_C1

OBSDATA_C0

OBSDATA_C1

OBSDATA_C2

OBSDATA_C3

OBSFN_D0

OBSFN_D1

OBSDATA_D0

OBSDATA_D1

GND11

OBSDATA_D2

OBSDATA_D3

GND13

ITPCLK/HOOK4

ITPCLK#/HOOK5

VCC_OBS_CD

RESET#/HOOK6

DBR#/HOOK7

GND15

TRST#

GND17

i5R1@

2

GND1

4

6

8

GND3

10

12

14

GND5

16

18

20

GND7

22

24

26

GND9

28

30

32

34

36

38

40

CLK_CPU_ITP

42

CLK_CPU_ITP#

44

46

XDP_RST#_RXDP_HOOK2

48

XDP_DBRESET#

50

52

TD0

TDI

TMS

XDP_TDO

54

XDP_TRST#_R

56

XDP_TDI

58

XDP_TMS_R

60

MISC THERMAL PWR MANAGEMENT

CLOCKS

DDR3

JTAG & BPM

RC33 0_0402_5%@

RC37 0_0402_5%@

RC39 0_0402_5%@

DPLL_REF_CL K

DPLL_REF_CL K#

SM_DRAMRST#

MISC

+VCCP

0.1U_0402_16V7K

1

2

Place near JXDP1

1 2

@

RC55 1K_0402_5%

1 2

1 2

1 2

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

0.1U_0402_16V7K

1

CC35

CC36

2

CLK_CPU_ITP <14>

CLK_CPU_ITP# <14>PBTN_OUT#<15,40>

PLT_RST#

PCH_JTAG_TDO <13>

PCH_JTAG_TDI <13>

PCH_JTAG_TMS <13>

J3

H2

AG3

CLK_CPU_DPLL_R

AG1

CLK_CPU_DPLL#_R

Remove DPLL Ref clock (for eDP only)

N59

N58

AT30

H_DRAMRST#

BF44

SM_RCOMP0

BE43

SM_RCOMP1

BG43

SM_RCOMP2

CLK_CPU_DMI <14>

CLK_CPU_DMI# <14>

1 2

RC65 1K_0402_1%

1 2

RC77 1K_0402_1%

H_DRAMRST# <7>

1 2

RC86140_0402_1%

1 2

RC8325.5_0402_1%

1 2

RC85200_0402_1%

DDR3 Compensation Signals

N53

N55

L56

L55

J58

M60

L59

K58

XDP_DBRESET#_R

G58

E55

E59

G55

G59

H60

J59

J61

XDP_PRDY#

XDP_PREQ#

XDP_TCK

XDP_TMS

XDP_TRST#

XDP_TDI_R

XDP_TDO_R

XDP_BPM#0_R

XDP_BPM#1_R

XDP_BPM#2_R

XDP_BPM#3_R

XDP_BPM#4_R

XDP_BPM#5_R

XDP_BPM#6_R

XDP_BPM#7_R

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

1 2

RC125 0_0402_5%@

1 2

RC135 0_0402_5%@

1 2

RC136 0_0402_5%@

1 2

RC137 0_0402_5%@

1 2

RC126 0_0402_5%@

1 2

RC50 0_0402_5%@

1 2

RC92 0_0402_5%@

1 2

RC89 0_0402_5%

1 2

RC95 0_0402_5%@

1 2

RC91 0_0402_5%@

1 2

RC101 0_0402_5%@

1 2

RC102 0_0402_5%@

1 2

RC103 0_0402_5%@

1 2

RC97 0_0402_5%@

1 2

RC88 0_0402_5%@

1 2

RC87 0_0402_5%@

1 2

RC90 0_0402_5%@

1 2

RC96 0_0402_5%@

1 2

RC93 0_0402_5%@

1 2

RC94 0_0402_5%@

PM_DRAM_PWRGD<15>

+3V_PCH

XDP_PRDY#_R

XDP_PREQ#_R

XDP_TCK_R

XDP_TMS_R

XDP_TRST#_R

XDP_TDI

XDP_TDO

XDP_DBRESET#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

CFG12 <8>

CFG13 <8>

CFG14 <8>

CFG15 <8>

PCH_PWROK<15,40>

SYS_PWROK<15>

RC5

1 2

200_0402_1%

+VCCP

H_DRAMRST#

1

@

CC143

0.1U_0402_25V6K

2

Place close to CPU

RC132

0_0402_1%

@

1 2

1 2

RC11 0_0402_1%

RUN_ON_CPU1.5VS3#<10,35>

PLT_RST#<16,32,38,40>

XDP_DBRESET# <15>

+3VS

RC129

@

1 2

0_0402_5%

D_PWG

@

XDP_DBRESET#_R

0.1U_0402_25V6K

Place close to CPU

12

@

RC6

10K_0402_5%

UC2

1

B

2

A

GND3Y

74AHC1G09GW TSSOP 5P

RUN_ON_CPU1.5VS3#

CC144

+3V_PCH

0.1U_0402_16V7K

+1.5V_CPU_VDDQ

CC33

1

12

2

5

VCC

4

RC28

@

39_0402_1%

1 2

13

D

2

QC1

G

+3VALW

UC3

1

5

NC

VCC

2

A

4

GND3Y

SN74LVC1G07DCKR_SC70-5~D

@

2N7002K_SOT23-3

S

0.1U_0402_16V7K

1

CC34

2

BUFO_CPU_RST# BUF_CPU_RST#

PU/PD for JTAG signals

XDP_TMS_R

XDP_TDI_R

XDP_PREQ#

XDP_TDO

XDP_TCK_R

XDP_TRST#_R

XDP_DBRESET#_R

1

VCCPWRGOOD_0_R

2

Avoid stub in t he PWRGD path

while placing r esistors RC25 & RC130

RC8

200_0402_1%

VDDPWRGOOD

RC8

CRB 1.1K

CHECK LIST 0.7 --> 4.75K

INTEL recommand 1.1K

PDG 0.71 rev -- >200

+VCCP

12

RC59

75_0402_5%

RC58

1 2

43_0402_1%

0.1U_0402_16V7K

1

@

2

1 2

RC4751_0402_5%

1 2

RC4651_0402_5%

1 2

RC4851_0402_5% @

1 2

RC10651_0402_5%

1 2

RC10551_0402_5%

1 2

RC10451_0402_5%

+3VS

RC42

1 2

1K_0402_5%

1 2

RC4510K_0402_5%

CC63

+VCCP

12

@

RC62

0_0402_5%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2012/08/22 2013/08/31

2012/08/22 2013/08/31

2012/08/22 2013/08/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(2/6) PM,XDP,CLK

PROCESSOR(2/6) PM,XDP,CLK

PROCESSOR(2/6) PM,XDP,CLK

LA-9104P

LA-9104P

LA-9104P

1

6 57Wednesday, August 29, 2012

6 57Wednesday, August 29, 2012

6 57Wednesday, August 29, 2012

1.0

1.0

1.0

5

UC1C

AP11

AJ10

AR11

AT13

AU13

BA13

BB11

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

i5R1@

AG6

SA_DQ[0]

AJ6

SA_DQ[1]

SA_DQ[2]

AL6

SA_DQ[3]

SA_DQ[4]

AJ8

SA_DQ[5]

AL8

SA_DQ[6]

AL7

SA_DQ[7]

SA_DQ[8]

AP6

SA_DQ[9]

AU6

SA_DQ[10]

AV9

SA_DQ[11]

AR6

SA_DQ[12]

AP8

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

BC7

SA_DQ[16]

BB7

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

BA7

SA_DQ[20]

BA9

SA_DQ[21]

BB9

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR_A_D[0..63]<11>

D D

C C

DDR_A_BS0<11>

DDR_A_BS1<11>

DDR_A_BS2<11>

B B

DDR_A_CAS#<11>

DDR_A_RAS#<11>

DDR_A_WE#<11>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

4

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AU36

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

M_CLK_DDR0

M_CLK_DDR#0

DDR_CKE0_DIMMA

M_CLK_DDR1

M_CLK_DDR#1

DDR_CKE1_DIMMA

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

M_ODT0

M_ODT1

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

M_CLK_DDR0 <11>

M_CLK_DDR#0 <11>

DDR_CKE0_DIMMA <11>

M_CLK_DDR1 <11>

M_CLK_DDR#1 <11>

DDR_CKE1_DIMMA <11>

DDR_CS0_DIMMA# <11>

DDR_CS1_DIMMA# <11>

M_ODT0 <11>

M_ODT1 <11>

DDR_A_DQS#[0..7] <11>

DDR_A_DQS[0..7] <11>

DDR_A_MA[0..15] <11>

3

BD13

BF12

BD10

BD14

BE13

BF16

BE17

BE18

BE21

BE14

BG14

BG18

BF19

BD50

BF48

BD53

BF52

BD49

BE49

BD54

BE53

BF56

BE57

BC59

AY60

BE54

BG54

BA58

AW59

AW58

AU58

AN61

AN59

AU59

AU61

AN58

AR58

AK58

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

UC1D

AL4

SB_DQ[0]

AL1

SB_DQ[1]

AN3

SB_DQ[2]

AR4

SB_DQ[3]

AK4

SB_DQ[4]

AK3

SB_DQ[5]

AN4

SB_DQ[6]

AR1

SB_DQ[7]

AU4

SB_DQ[8]

AT2

SB_DQ[9]

AV4

SB_DQ[10]

BA4

SB_DQ[11]

AU3

SB_DQ[12]

AR3

SB_DQ[13]

AY2

SB_DQ[14]

BA3

SB_DQ[15]

BE9

SB_DQ[16]

BD9

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

BF8

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDR_B_D[0..63]<12>

DDR_B_BS0<12>

DDR_B_BS1<12>

DDR_B_BS2<12>

DDR_B_CAS#<12>

DDR_B_RAS#<12>

DDR_B_WE#<12>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

i5R1@

2

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

M_CLK_DDR2

M_CLK_DDR#2

DDR_CKE2_DIMMB

M_CLK_DDR3

M_CLK_DDR#3

DDR_CKE3_DIMMB

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_ODT2

M_ODT3

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY B

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

M_CLK_DDR2 <12>

M_CLK_DDR#2 <12>

DDR_CKE2_DIMMB <12>

M_CLK_DDR3 <12>

M_CLK_DDR#3 <12>

DDR_CKE3_DIMMB <12>

DDR_CS2_DIMMB# <12>

DDR_CS3_DIMMB# <12>

M_ODT2 <12>

M_ODT3 <12>

DDR_B_DQS#[0..7] <12>

DDR_B_DQS[0..7] <12>

DDR_B_MA[0..15] <12>

1

AV8063801058002-SR0N8-L1-1.7G_BGA1023~D

+1.5V

4

12

RC108

1K_0402_5%

1 2

RC110 1K_0402_5%

1 2

@

RC111 0_0402_1%

DDR3_DRAMRST# <11,12>

DRAMRST_CNTRL_PCH <14>

DRAMRST_CNTRL <11>

Place close to RC110

3

DDR3_DRAMRST#

1

@

CC145

0.1U_0402_25V6K

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1 2

@

RC107 0_0402_5%

QC2

BSS138_SOT23

D

S

13

H_DRAMRST#<6>

A A

5

H_DRAMRST#

4.99K_0402_1%

RC109

12

G

2

1

CC37

.047U_0402_16V7K

2

DDR3_DRAMRST#_R

DRAMRST_CNTRL

AV8063801058002-SR0N8-L1-1.7G_BGA1023~D

Compal Secret Data

Compal Secret Data

2012/08/22 2013/08/31

2012/08/22 2013/08/31

2012/08/22 2013/08/31

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(3/6) DDRIII

PROCESSOR(3/6) DDRIII

PROCESSOR(3/6) DDRIII

LA-9104P

LA-9104P

LA-9104P

1

7 57Wednesday, August 29, 2012

7 57Wednesday, August 29, 2012

7 57Wednesday, August 29, 2012

1.0

1.0

1.0

5

4

3

2

1

D D

UC1E

i5R1@

CFG0<6>

+VCC_CORE

CFG10<6>

CFG11<6>

1 2

1 2

@

RC123

50_0402_1%

CFG12<6>

CFG13<6>

CFG14<6>

CFG15<6>

VCC_VAL_SENSE

VSS_VAL_SENSE

1 2

RC21 1K_0402_5%

+VCC_GFXCORE_AXG

C C

@

RC120

50_0402_1%

B B

1 2

1 2

@

RC119

50_0402_1%

@

RC121

50_0402_1%

VCC_AXG_VAL_SENSE

VSS_AXG_VAL_SENSE

CFG0

T91PAD~D @

CFG2

T92PAD~D @

CFG4

CFG5

CFG6

CFG7

T66PAD~D @

T41PAD~D @

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

T69PAD~D @

T89PAD~D @

@

TP_VCC_DIESENSE

T46PAD~D @

T36PAD~D @

T32PAD~D @

T34PAD~D @

T35PAD~D @

T40PAD~D @

T42PAD~D @

T47PAD~D @ T132 PAD~D@

T71PAD~D @

T72PAD~D @

T51PAD~D @

T68PAD~D @

T49PAD~D @

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

AV8063801058002-SR0N8-L1-1.7G_BGA1023~D

RESERVED

DC_TEST_C 59

DC_TEST_C 61

DC_TEST_D 61

DC_TEST_B D61

DC_TEST_B E61

DC_TEST_B E59

DC_TEST_B G61

DC_TEST_B G59

DC_TEST_B G58

DC_TEST_B G4

DC_TEST_B G3

DC_TEST_B E3

DC_TEST_B G1

DC_TEST_B E1

DC_TEST_B D1

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

DC_TEST_A4

DC_TEST_C 4

DC_TEST_D 3

DC_TEST_D 1

DC_TEST_A58

DC_TEST_A59

DC_TEST_A61

BE7

+SA_DIMM_VREFDQ

BG7

+SB_DIMM_VREFDQ

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

TP_DC_TEST_A4

C4

D3

DC_TEST_C4_D3

D1

TP_DC_TEST_D1

A58

TP_DC_TEST_A58

A59

C59

DC_TEST_A59_C59

A61

C61

DC_TEST_A61_C61

D61

TP_DC_TEST_D61

BD61

TP_DC_TEST_BD61

BE61

BE59

DC_TEST_BE59_BE61

BG61

BG59

DC_TEST_BG59_BG61

BG58

TP_DC_TEST_BG58

BG4

TP_DC_TEST_BG4

BG3

BE3

DC_TEST_BE3_BG3

BG1

BE1

DC_TEST_BE1_BG1

BD1

TP_DC_TEST_BD1

T14 PAD~D@

T15 PAD~D@

T16 PAD~D@

T17 PAD~D@

T22 PAD~D@

T21 PAD~D@

T19 PAD~D@

T20 PAD~D@

T18 PAD~D@

T23 PAD~D@

T28 PAD~D@

T27 PAD~D@

T25 PAD~D@

T26 PAD~D@

T29 PAD~D@

+SA_DIMM_VREFDQ +SA_DIMM_VREFDQ

12

@

RC117

1K_0402_1%

T121 PAD~D@

T118 PAD~D@

T119 PAD~D@

T120 PAD~D@

T122 PAD~D@

T123 PAD~D@

T124 PAD~D@

1K_0402_1%

CFG Straps for Processor

CFG2

PEG Static Lane Reversal - CFG2 is for the 16x

1:(Default) Normal Operation; Lane #

CFG2

RC115

12

@

CFG[6:5]

definition matches socket pin map definition

0:Lane Reversed

*

CFG4

Display Port Presence Strap

1 : Disabled; No Physical Display Port

*

CFG4

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG6

CFG5

RC114

1K_0402_1%

PCIE Port Bifurcation Straps

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

*

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

12

12

12

RC116

1K_0402_1%

RC112

1K_0402_1%@

12

RC113

1K_0402_1%

@

CFG7

12

@

RC118

1K_0402_1%

PEG DEFER TRAINING

1: (Default) PEG Train immediately

*

CFG7

following xxRESETB de assertion

0: PEG Wait for BIOS for training

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2012/08/22 2013/08/31

2012/08/22 2013/08/31

2012/08/22 2013/08/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(4/6) RSVD,CFG

PROCESSOR(4/6) RSVD,CFG

PROCESSOR(4/6) RSVD,CFG

LA-9104P

LA-9104P

LA-9104P

1

8 57Wednesday, August 29, 2012

8 57Wednesday, August 29, 2012

8 57Wednesday, August 29, 2012

of

1.0

1.0

1.0

5

4

3

2

1

AF46

AG48

AG50

AG51

AJ17

AJ21

AJ25

AJ43

AJ47

AK50

AK51

AL14

AL15

AL16

AL20

AL22

AL26

AL45

AL48

AM16

AM17

AM21

AM43

AM47

AN20

AN42

AN45

AN48

AA14

AA15

AB17

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

A44

B43

C44

F43

G43

AN16

AN17

8.5A

+VCCP

+VCCP

1 2

RC140 0_0402_5%@

+VCCP

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

VCCSENSE_R

VSSSENSE_R

+3VS

RC141

10K_0402_5%@

1 2

VCCP_PWRCTRL

1U_0402_6.3V6K

CC573

1

2

RC147 close to CPU

12

RC147

130_0402_1%

1 2

RC142 43_0402_1%<BOM Structure>

1 2

RC146 0_0402_1%@

1 2

RC144 0_0402_1%@

CAD Note: Place the PU

resistors close to CPU

RC147 close to CPU 300~1500mi ls

1 2

RC139 0_0402_1%@

1 2

RC122 0_0402_1%@

12

RC98 10_0402_1%

1 2

RC133 10_0402_1%

Place RC98 close to CPU

VCCP_PWRCTRL Pull high on power side

+VCCP

Note: Place the PU resistors close to CPU

RC145 close to CPU 300~1500mi ls

12

RC145

75_0402_5%

VR_SVID_ALRT# <52>

VR_SVID_CLK <52>

VR_SVID_DAT <52>

+VCC_CORE

12

RC138

100_0402_1%

+VCCP

VCCIO_SENSE <49>

VSSIO_SENSE_R <49>

12

RC131

100_0402_1%

VCCSENSE <52>

VSSSENSE <52>

Iccmax current changed for PD DG Rev0.7

CPU Power Rail Table

Voltage Rail

VCC

VCCIO

VAXG

VCCPLL

VDDQ

VCCSA

+1.5V_MEM 1.5

Description

*

5A to Mem contr oller(+1.5V_CP U_VDDQ)

5-6A to 2 DIMMs /channel

2-5A to +1.5V_R UN & +0.75V_DD R_VTT

Voltage

0.65-1.3

0.0-1.1

0.65-0.9

1.05/1

1.8

1.5

S0 Iccmax

Current (A)

53

8.5

33

1.2

5

6

12-16

*

i5R1@

POWER

CORE SUPPLY

VCCIO[1]

VCCIO[3]

VCCIO[4]

VCCIO[5]

VCCIO[6]

VCCIO[7]

VCCIO[8]

VCCIO[9]

VCCIO[10]

VCCIO[11]

VCCIO[12]

VCCIO[13]

VCCIO[14]

VCCIO[15]

VCCIO[16]

VCCIO[17]

VCCIO[18]

VCCIO[19]

VCCIO[20]

VCCIO[21]

VCCIO[22]

VCCIO[23]

VCCIO[24]

VCCIO[25]

VCCIO[26]

VCCIO[27]

VCCIO[28]

VCCIO[29]

VCCIO[30]

VCCIO[31]

VCCIO[32]

PEG IO AND DDR IO

VCCIO[33]

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

RAILS

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES SVID QUIET

D D

ULV 17W , Max Current

in Turbo Mode or HFM

C C

B B

A A

+VCC_CORE

UC1F

33A

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

AV8063801058002-SR0N8-L1-1.7G_BGA1023~D

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2012/08/22 2013/08/31

2012/08/22 2013/08/31

2012/08/22 2013/08/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(5/6) PWR,BYPASS

PROCESSOR(5/6) PWR,BYPASS

PROCESSOR(5/6) PWR,BYPASS

LA-9104P

LA-9104P

LA-9104P

1

of

9 57Wednesday, August 29, 2012

9 57Wednesday, August 29, 2012

9 57Wednesday, August 29, 2012

1.0

1.0

1.0

5

4

3

2

1

+1.5V_CPU_VDDQ Source

+1.5V +1.5V_CPU_VDDQ

B+_BIAS+3VALW

QC7B

@

CC174

1U_0402_6.3V6K

CC261

1

2

12

RC151

470K_0402_5%

3

5

4

RUN_ON_CPU1.5VS3# <35,6>

+VCC_GFXCORE_AXG

12

1.2A

1U_0402_6.3V6K

1

CC175

2

1U_0402_6.3V6K

CC260

1

2

4

RUN_ON_CPU1.5VS3

33A

6A

12

RC143

100K_0402_5%

CC264

1

2

+1.8VS

330U_D2_2.5VM_R6M~D

1U_0402_6.3V6K

1U_0402_6.3V6K

CC263

1

2

2N7002DW-7-F_SOT363-6

RC76

100_0402_1%

1U_0402_6.3V6K

1

CC176

1

+

2

2

1U_0402_6.3V6K

CC262

1

2

D D

RC149

0_0402_5%

+VCCSA

CC172

1 2

@

1 2

@

RC148

0_0402_1%

VCC_AXG_SENSE<52>

VSS_AXG_SENSE<52>

330U_D2_2VM_R6M~D

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC171

+

2

5

10U_0603_6.3V6M

1

1

CC170

CC169

2

2

SUSP#<35,40,48,49,50>

CPU1.5V_S3_GATE<40>

C C

B B

A A

61

2

1

@

CC40

0.1U_0402_10V7K~D

2

+VCC_GFXCORE_AXG

RC99

100_0402_1%

RC100

100_0402_1%

10U_0603_6.3V6M

1

1

CC183

CC168

2

2

RUN_ON_CPU1.5VS3#

QC7A

2N7002DW-7-F_SOT363-6

12

12

10U_0603_6.3V6M

1

2

QC3

AO4304L_SO8

8

7

6

5

4

0.1U_0603_50V_X7R

12

i5R1@

1

CC39

2

POWER

GRAPHICS

SENSE

LINES

RC150

2M_0402_5%~D

UC1G

AA46

VAXG[1]

AB47

VAXG[2]

AB50

VAXG[3]

AB51

VAXG[4]

AB52

VAXG[5]

AB53

VAXG[6]

AB55

VAXG[7]

AB56

VAXG[8]

AB58

VAXG[9]

AB59

VAXG[10]

AC61

VAXG[11]

AD47

VAXG[12]

AD48

VAXG[13]

AD50

VAXG[14]

AD51

VAXG[15]

AD52

VAXG[16]

AD53

VAXG[17]

AD55

VAXG[18]

AD56

VAXG[19]

AD58

VAXG[20]

AD59

VAXG[21]

AE46

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL[1]

BC1

VCCPLL[2]

BC4

VCCPLL[3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R21

VCCSA[10]

U15

VCCSA[11]