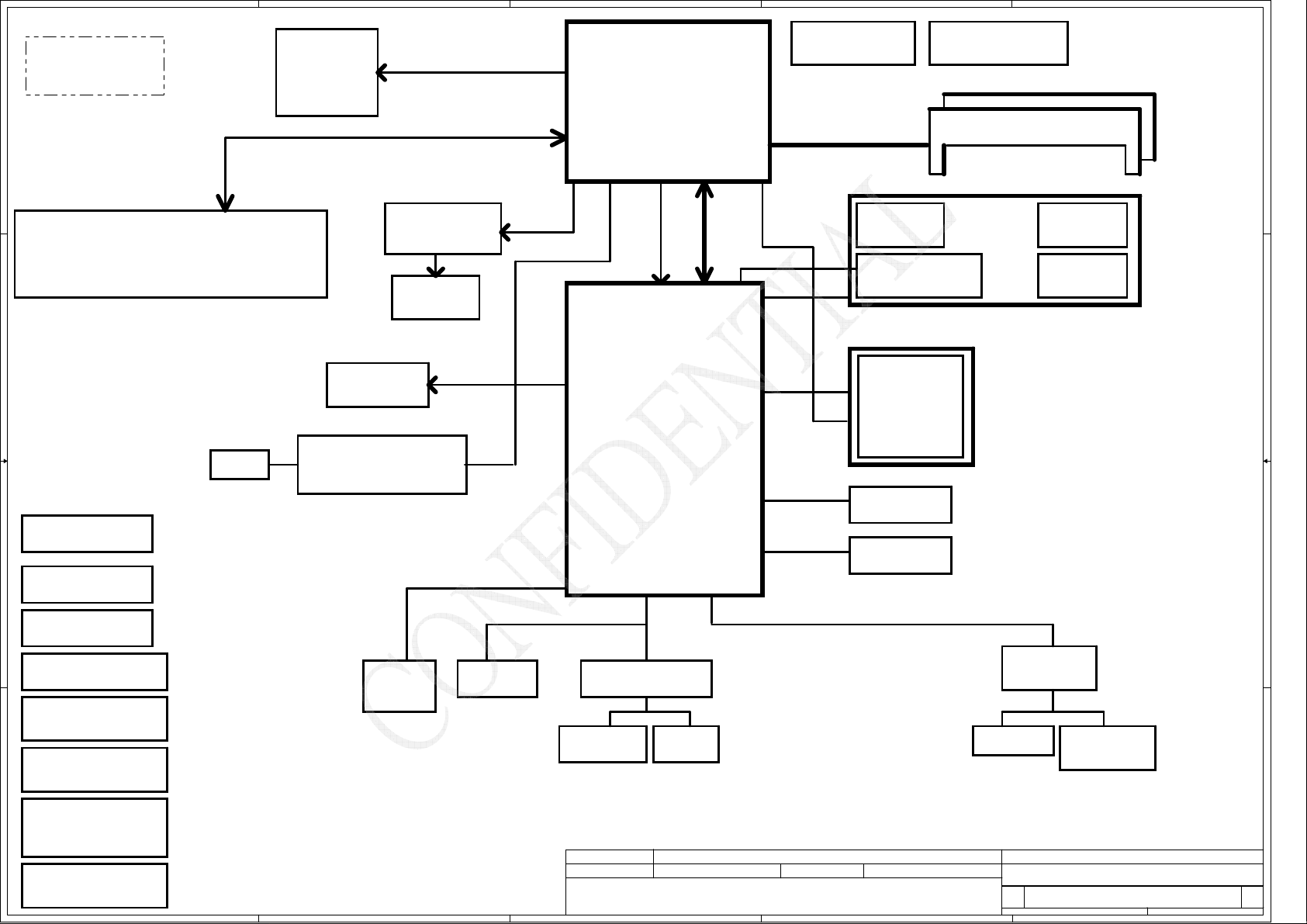

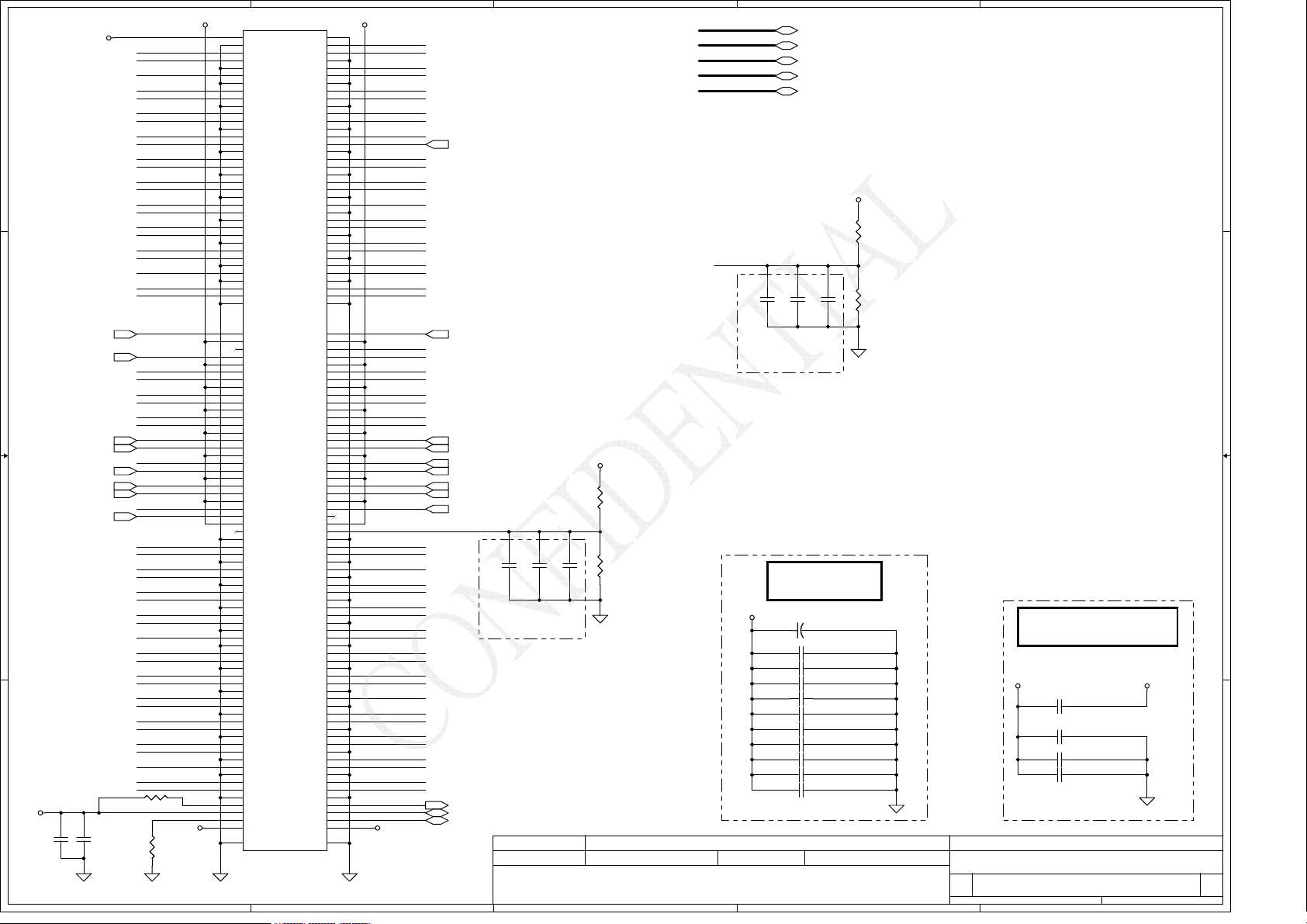

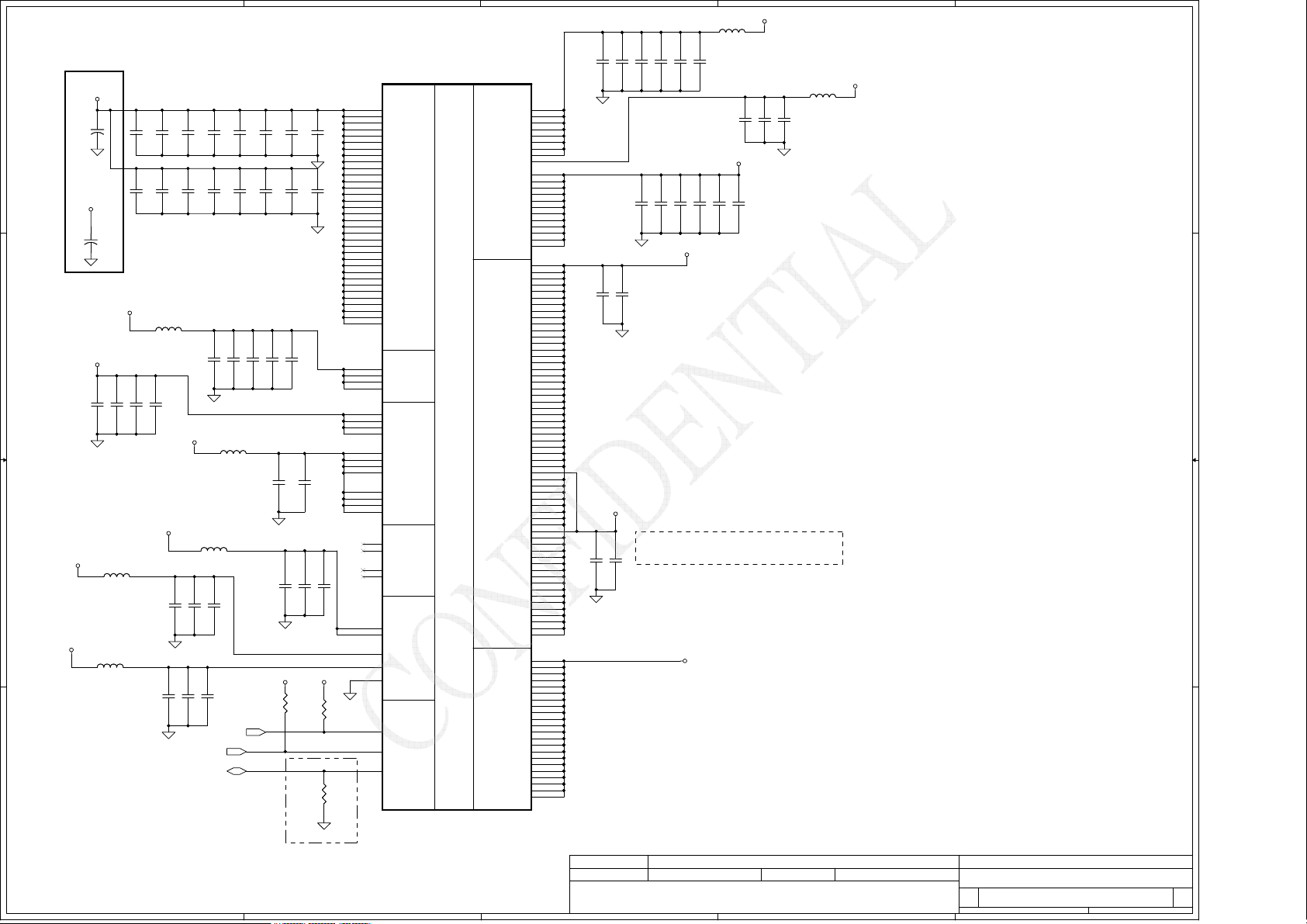

Compal LA-8863P QMLE4 Eureka Discrete, NP355V4C, NP355V5C, LA-8863P QMLE5 Eureka Discrete Schematic

A

B

C

D

E

1 1

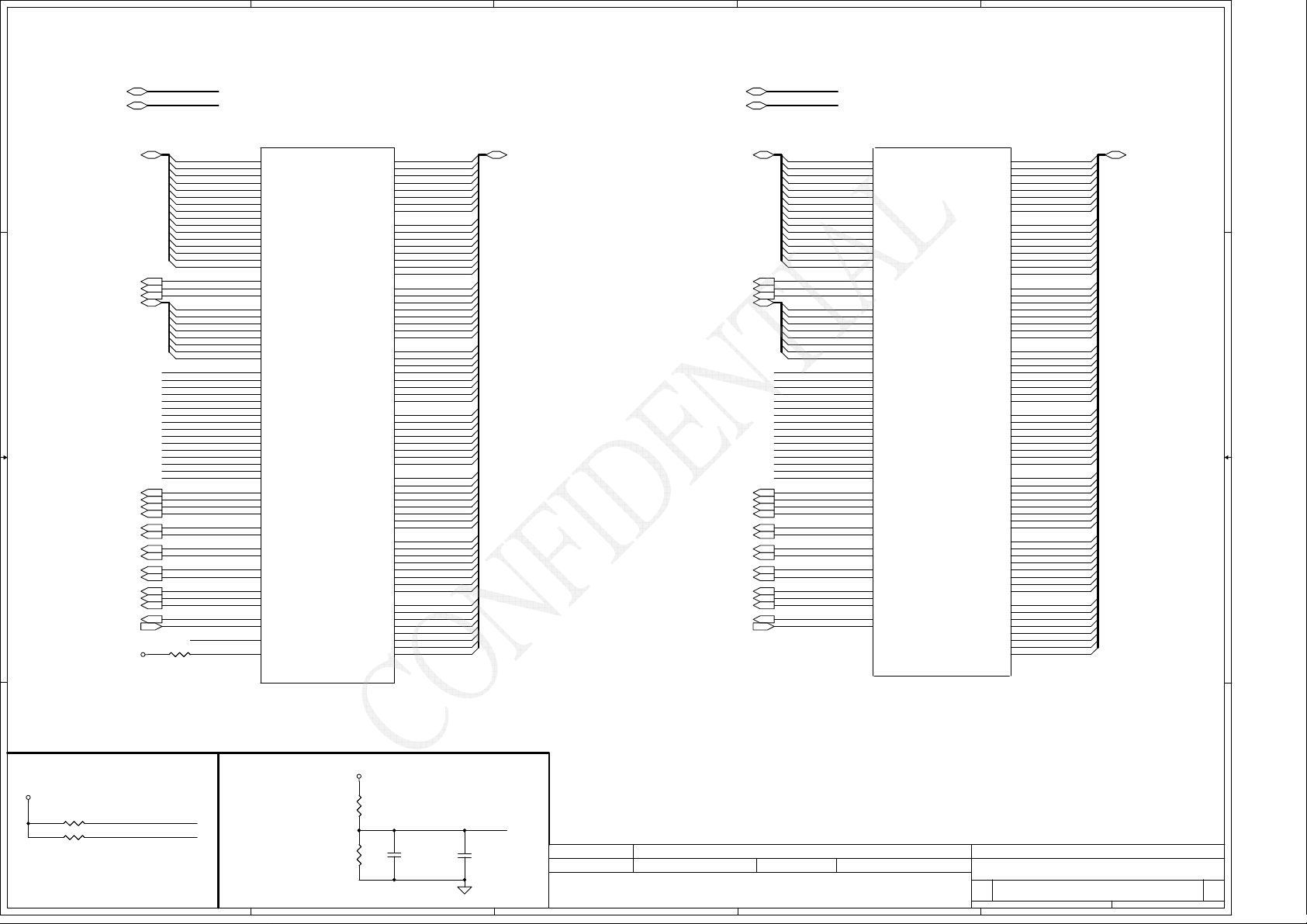

QMLE4/5

2 2

Eureka Discrete

LA-8863P SchematicREV 0.3

3 3

4 4

AMD Trinity APU / Hudson M3 FCH

Thames XT & Chelsea PRO

2012-03-13 Rev 0.3

A

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/11/28 2013/12/31

2011/11/28 2013/12/31

2011/11/28 2013/12/31

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

4019IT

4019IT

4019IT

151Friday, March 23, 2012

151Friday, March 23, 2012

151Friday, March 23, 2012

E

of

of

of

A

A

A

A

B

C

D

E

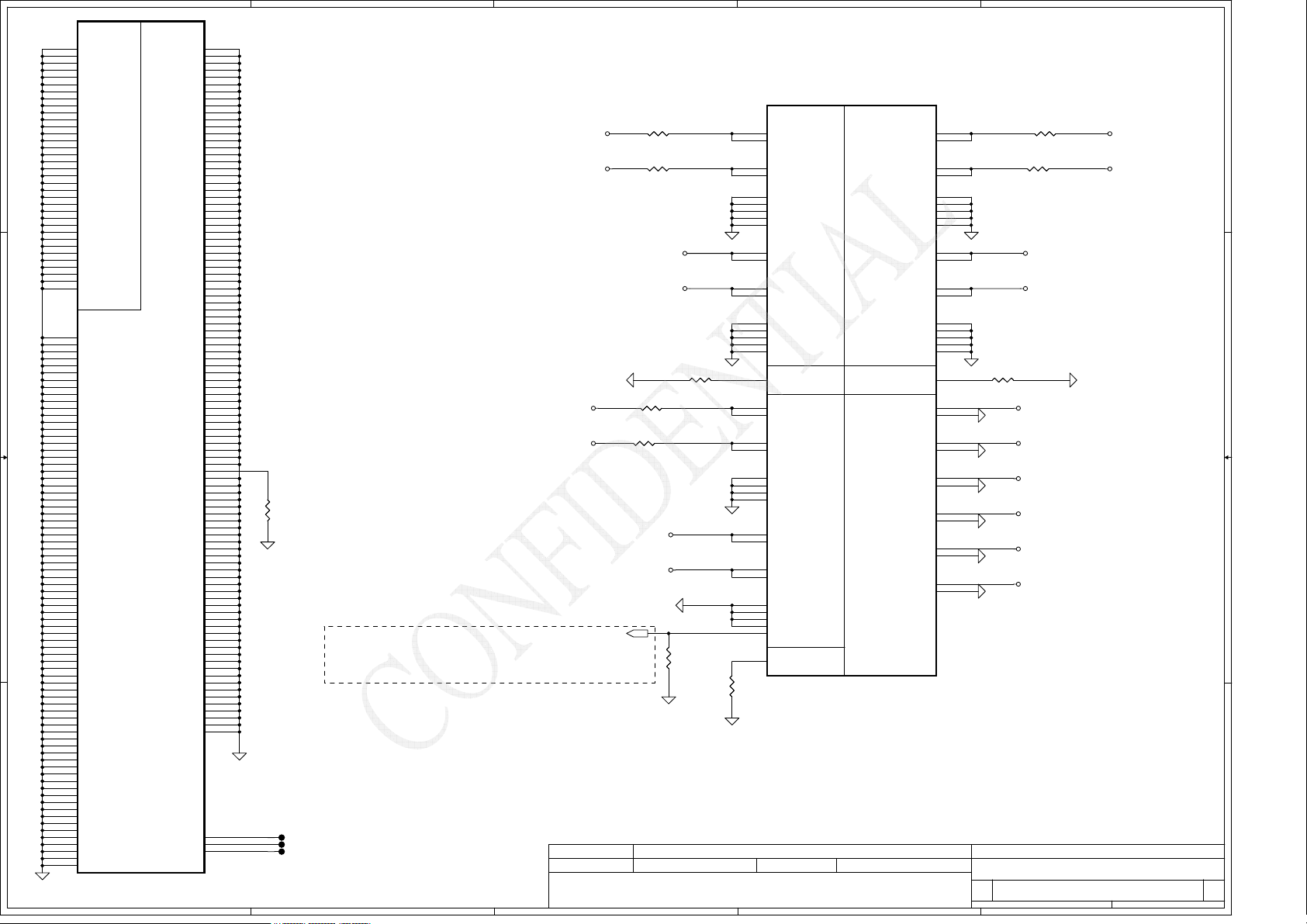

VGA Thermal Sensor

ADM1032ARMZ-2

1 1

page 13

HDMI Conn.

page 24

PCI-Express X16 5GHz

AMD GPU

AMD Thames XT, 128bit with 1GB/2GB DDR3

AMD Chelsea PRO, 128bit with 1GB/2GB DDR3

page 12,13,14,15,16,17,18,19,20

2 2

DP2 X4

LVDS Translator

RTD2136S

page 21

LVDS Conn.

page 22

DP0

(X2)

PCIe X1

1.1V 5GT/s

AMD APU

FS1 Processor

Trinity uPGA-722

35mm*35mm

page 5,6,7,8,9

DP1

(X4)

UMI X4

2.5GT/s

Memory BUS(DDRIII)

Dual Channel

1.5V DDRIII 1066/1333/1600 MT/s

PCIe X1 X1

1.1V 5GT/s

USB3.0

5V 5GT/s

USB

5V 480MHz

USB

5V 480MHz

CRT

page 23

page 5

USB/B Right

USB port 0,1

page 31

USB 3.0

USB3.0 port 0,1

USB2.0 port 10,11

PCIeMini Card

WLAN/BT

AMD FCH

Fan Control

RJ45

page 34

ODD/B

3 3

Audio + CR/B

TP/B

page 30

page 33

page 38

RTL8111F-VB 1G

APU PCIe port 0

page 32

SPI Bus

3.3V 33 MHz

RTL8105E-VD 10/100M

Hudson M3

FCBGA-656

24.5mm*24.5mm

page 25,26,27,28,29

LPC Bus

3.3V 33 MHz

HD Audio

SATA port 0

5V 6GHz(600MB/s)

SATA port 1

5V 6GHz(600MB/s)

3.3V 24MHz

APU PCIe port 1

SATA HDD

SATA ODD

GCLK

SLG3NB270VTR page 31

200pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

Cardreader

Int. Camera

page 34

USB port 8

page 31

SATA port 0

page 30

SATA port 1

page 30

page 10,11

USB port 9

page 33

USB port 5

page 22

HDA Codec

RUSB + Power/B

page 30

SPI ROM

(4MB)

page 27

Debug Port

page 37

ENE KB9012

page 36

ALC259

page 35

RTC CKT.

page 25

Touch Pad

page 38

Int.KBD

page 37

DC/DC Interface CKT.

page 39

4 4

SPK Conn

page 35

JPIO

(HP & MIC)

page 35

Power Circuit DC/DC

page 40,41,42,43,44,45

,46,47,48,49

Power On/Off CKT.

page 30

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/11/28 2013/12/31

2011/11/28 2013/12/31

2011/11/28 2013/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

4019IT

4019IT

4019IT

251Friday, March 23, 2012

251Friday, March 23, 2012

251Friday, March 23, 2012

E

A

A

A

of

of

of

5

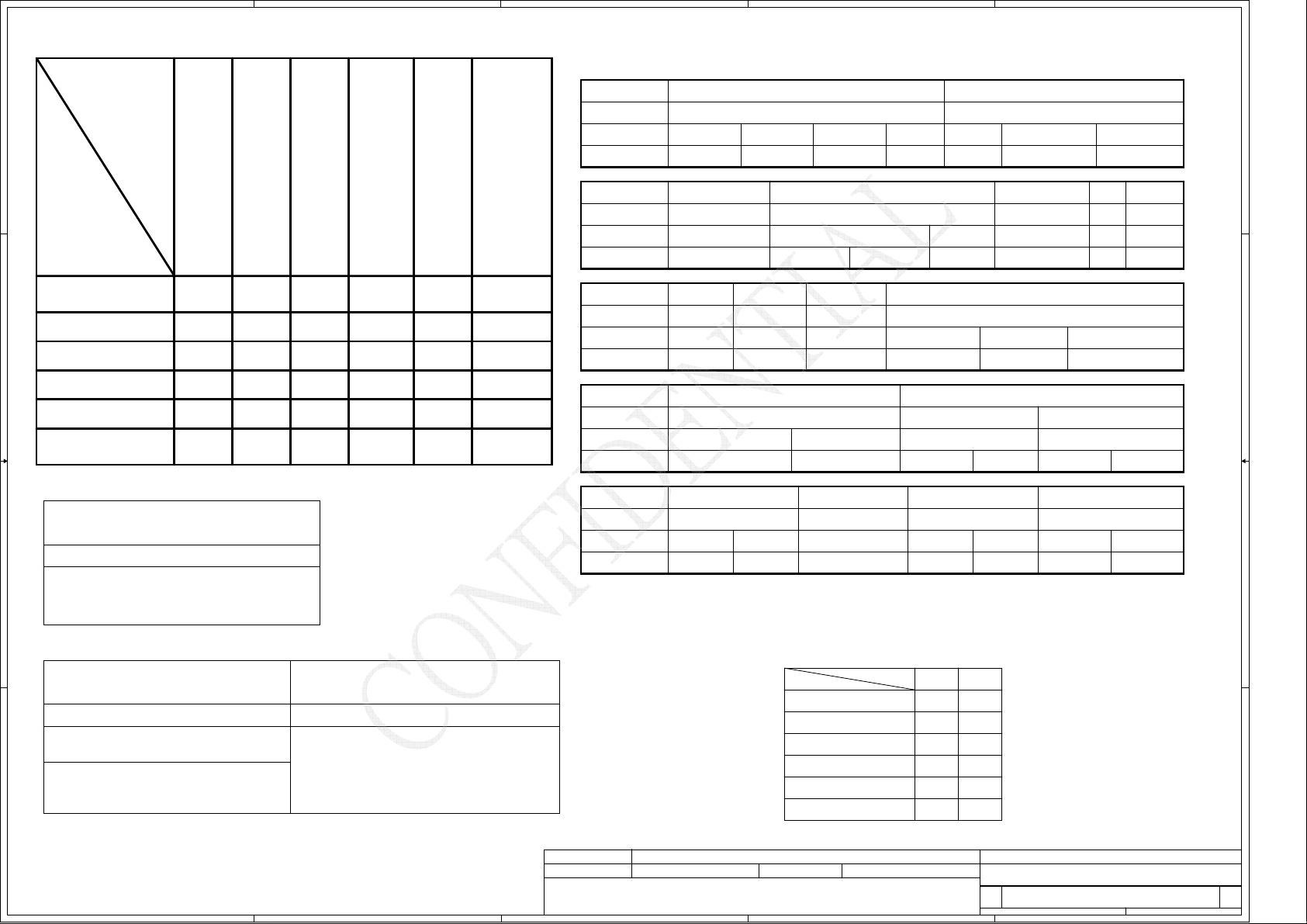

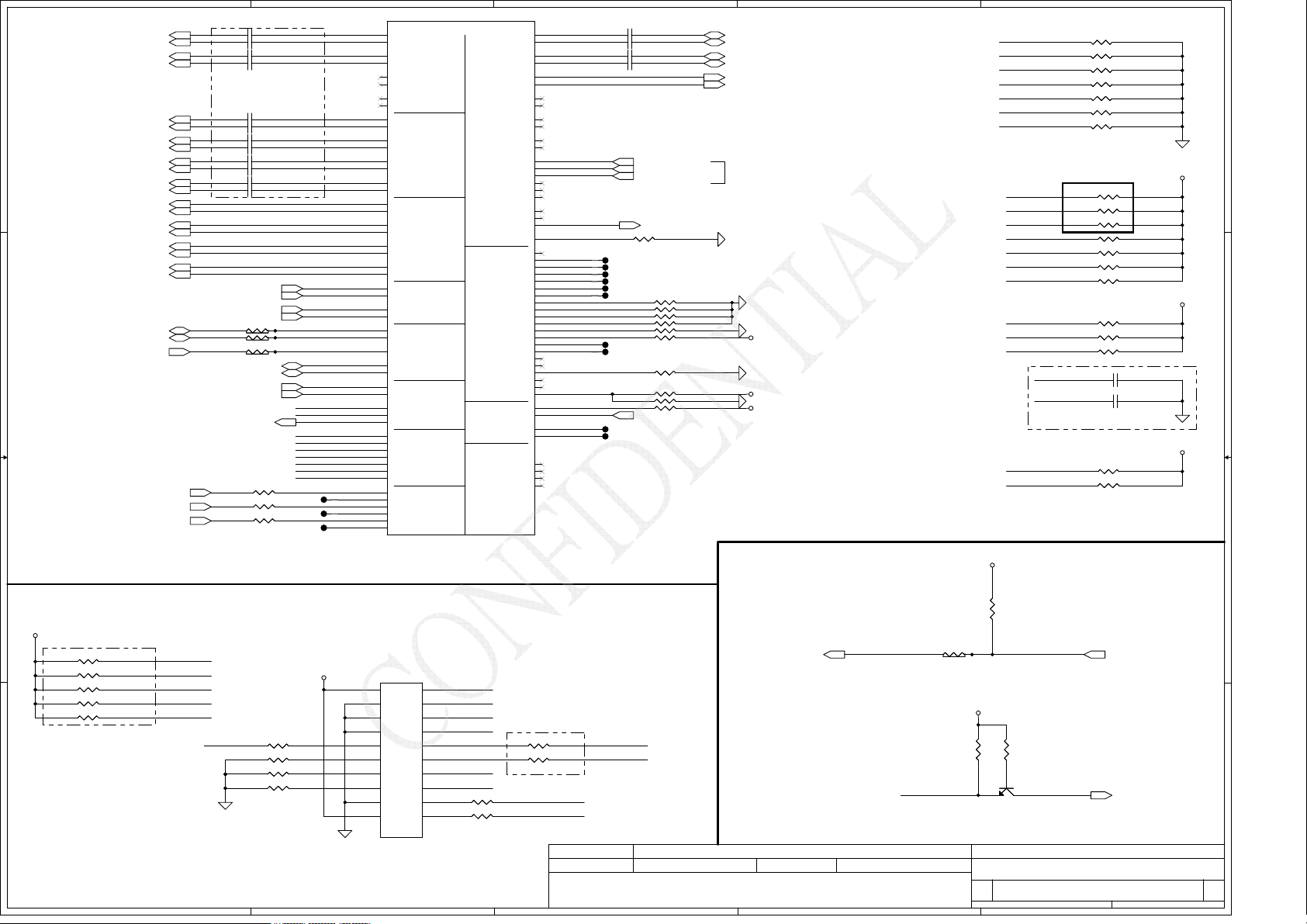

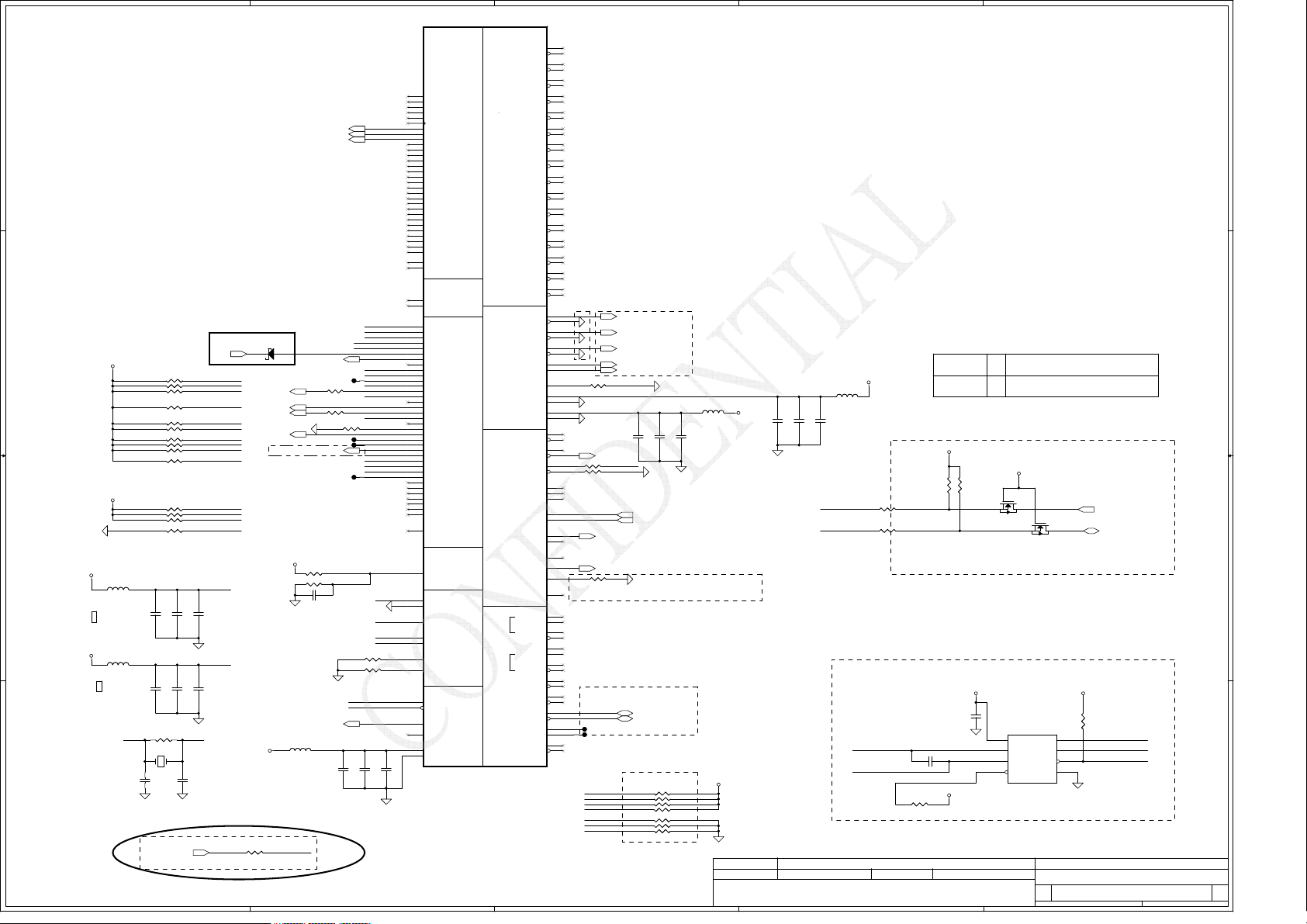

B+

D D

Ipeak=5A, Imax=3.5A, Iocp min=7.9A

SUSP

N-CHANNEL

SI4800

TPS51125A

Ipeak=5A, Imax=3.5A, Iocp min=7.7A

C C

SUSP

N-CHANNEL

SI4800

4

+5VS

LDO

G9191

ODD_PWR

P-CHANNEL

AO-3413

WOL_EN#

P-CHANNEL

AO-3413

SYSON

P-CHANNEL

AO-3413

GPU_PWREN

SY8033BDBC

LCD_ENVDD

P-CHANNEL

AO-3413

DESIGN CURRENT 0.1A

DESIGN CURRENT 5A

DESIGN CURRENT 4A

DESIGN CURRENT 300mA

DESIGN CURRENT 1.6A

DESIGN CURRENT 5A

DESIGN CURRENT 330mA

DESIGN CURRENT 0.2A

DESIGN CURRENT 1.65A

DESIGN CURRENT 4A

DESIGN CURRENT 1.5A

+3VL

+5VALW

+5VS

+3VS_HDP

+5VS_ODD

+3VALW

+3V_LAN

+3V

+1.8VSG

+3VS

+LCD_VDD

3

2

1

PXS_PWREN

POK

G5603RU1U

VR_ON

Ipeak=5.3A, Imax=3.71A, Iocp min=6.814A

P-CHANNEL

AO-3413

SUSP

N-CHANNEL

FDS6676AS

Ipeak=54A, Imax=36A, Iocp min=65A

B B

ISL6267HRZ-T

VR_ON

G5603RU1U

SYSON

G5603RU1U

Ipeak=27.5A, Imax=22A, Iocp min=35A

Ipeak=6.5A, Imax=4.55A, Iocp min=8.553A

Ipeak=20A, Imax=11.2A, Iocp min=24.136A

SUSP

N-CHANNEL

FDS6676AS

+3V

LDO

APL5930KAI-TRG

SUSP

G2992F1U

VGA_PWRGD

A A

VGACORE_EN

N-CHANNEL

FDS6676AS

GPU_PWREN

LDO

APL5930KAI

Ipeak=32.6A, Imax=20.3A, Iocp min=36A

RT8237CZQW

5

4

DESIGN CURRENT 0.3A

DESIGN CURRENT 5.3A

DESIGN CURRENT 4A

DESIGN CURRENT 50A

DESIGN CURRENT 23A

DESIGN CURRENT 6.5A

DESIGN CURRENT 20A

DESIGN CURRENT 2A

DESIGN CURRENT 1A

DESIGN CURRENT 1.5A

DESIGN CURRENT 11A

DESIGN CURRENT 3A

DESIGN CURRENT 32.6A

+3VGS

+1.1VALW

+1.1VS

+CPU_CORE

+CPU_CORE_NB

+1.2VS

+1.5V

+1.5VS

+1.05V

+0.75VS

+1.5VSG

+1.0VSG

+VGA_CORE

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/11/28 2013/12/31

2011/11/28 2013/12/31

2011/11/28 2013/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

4019IT

4019IT

4019IT

1

351Friday, March 23, 2012

351Friday, March 23, 2012

351Friday, March 23, 2012

of

of

of

A

A

A

A

B

C

D

E

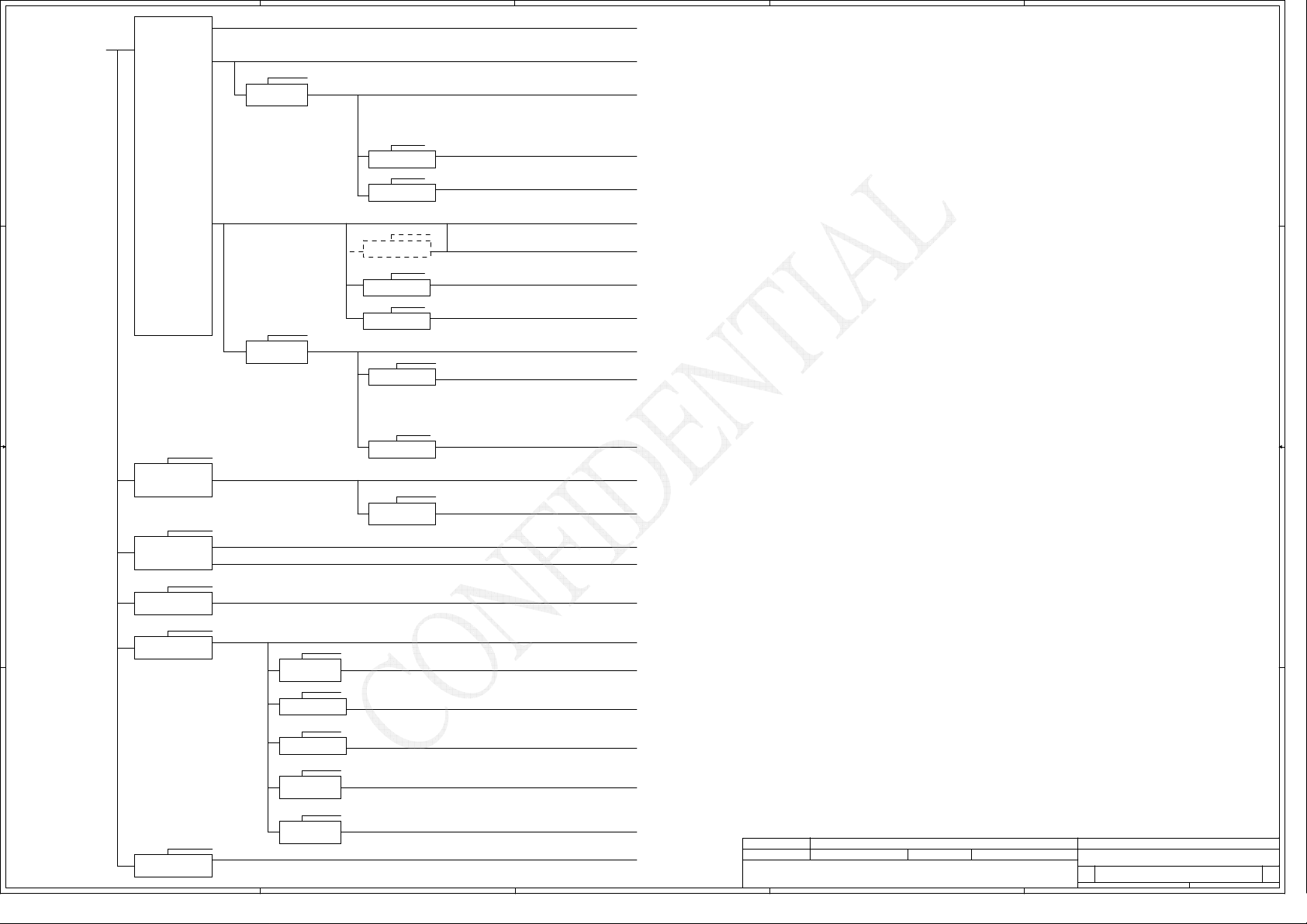

Voltage Rails

1 1

power

plane

State

S0

S1

2 2

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

( O MEANS ON X MEANS OFF )

+RTCVCC

O

O

O

O

O

O

B+

O

O

O

O

O

X

+5VL

+3VL

O

O

O

O

O

X

+5VALW

+3VALW

+1.1VALW

+VSB

O

O

O

O

X

X

+1.5V

+3V

+1.05V

+5VS

+3VS

+2.5VS

+1.5VS

+1.2VS

+1.1VS

+0.75VS

+CPU_CORE

+CPU_CORE_NB

+VGA_CORE

+3VGS

+1.8VSG

+1.5VSG

+1.0VSG

OO

OO

O

X

XX

X

X

XX

BTO Option Table

Function

description

explain

BTO

Function

description

explain

BTO

Function

description

explain

BTO

Function

description

explain

BTO

UMA

PowerXpress

IHDMI@

MINI PCI-E SLOT

PowerXpress Enable

HDMI

HDMI

8105ELDO@ 8111E@

GPIO for PowerXpress

PowerXpress (PXS@)

PXSEN@

COMMON

HDMI@

LAN

LAN

10/100M GIGA

8105ESWR@

Cam & Mic

Cam & Mic

Cam & Mic

CAM@

Crossfire Enable

CROSSEN@

SKU

SKU

UMA

UMA@ UMA@+VGA@+PXS@

FCH GPU

Hudson-M3 Whistler Pro

PowerXpress Discrete

VGA@+DIS@

Panel

Panel (DIS@)

Chipset

WHPROR1@ WHPROR3@HUDM3R1@ HUDM3R3@

Function

FCH SM Bus Address (SCL0/SDA0)

description

explain

HEX

Power

3 3

+3VS

+3VS

+3VS

Device

DDR SO-DIMM 0

DDR SO-DIMM 1

WLAN

EC SM Bus1 Address

HEX HEX

16 H

+3VL

+3VL

Device Address Address

Charger IC 0001 001x b12 H

EC SM Bus3 Address

4 4

+3VS

A8 H

Address

1001 000xb90 H

1001 001xb92 H

BTO

EC SM Bus2 Address

PowerPower

0001 011x bSmart Battery

1010 1000 bLVDS EEPROM

+3VS

+3VS

+3VS GPU External Thermal

+3VS GPU External Thermal

Device

APU Thermal Sensor

GPU Internal Thermal

98 H

82 H

9A H

9A H

1001 100x b

1000 001x b

1001 101x b

1001 101x b

PowerXpress

PowerXpress

BACO mode

BACO@

Non-BACO

NOBACO@

Hudson-M2 Hudson-M3

SIGNAL

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

G3 LOW LOW

SLP_S3#

FCH

FCH

M2@ M3@

SLP_S5#

HIGHHIGH

HIGH HIGH

HIGH

LOW

HIGH

LOW

LOWLOW

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/11/28 2013/12/31

2011/11/28 2013/12/31

2011/11/28 2013/12/31

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

4019IT

4019IT

4019IT

451Friday, March 23, 2012

451Friday, March 23, 2012

451Friday, March 23, 2012

E

A

A

A

of

of

of

A

B

C

D

E

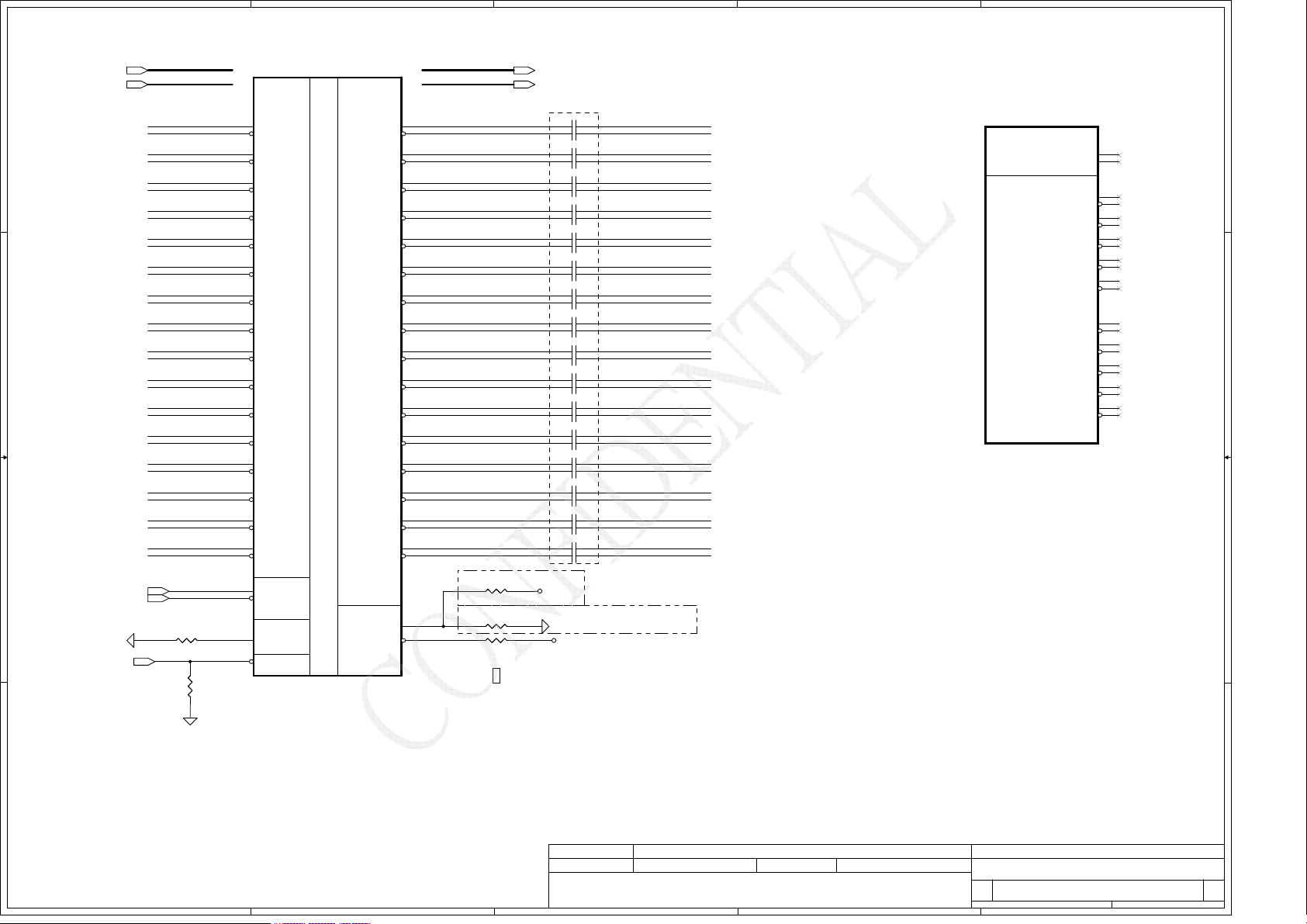

1 1

2 2

LAN

WLAN

PCIE_GTX_C_CRX_P[0..15]<12>

JAPUA

JAPUA

PCI EXPRESS

PCIE_GTX_C_CRX_P0

PCIE_GTX_C_CRX_N0

PCIE_GTX_C_CRX_P1

PCIE_GTX_C_CRX_N1

PCIE_GTX_C_CRX_P2

PCIE_GTX_C_CRX_N2

PCIE_GTX_C_CRX_P3

PCIE_GTX_C_CRX_N3

PCIE_GTX_C_CRX_P4

PCIE_GTX_C_CRX_N4

PCIE_GTX_C_CRX_P5

PCIE_GTX_C_CRX_N5

PCIE_GTX_C_CRX_P6

PCIE_GTX_C_CRX_N6

PCIE_GTX_C_CRX_P7

PCIE_GTX_C_CRX_N7

PCIE_GTX_C_CRX_P8

PCIE_GTX_C_CRX_N8

PCIE_GTX_C_CRX_P9

PCIE_GTX_C_CRX_N9

PCIE_GTX_C_CRX_P10

PCIE_GTX_C_CRX_N10

PCIE_GTX_C_CRX_P11

PCIE_GTX_C_CRX_N11

PCIE_GTX_C_CRX_P12

PCIE_GTX_C_CRX_N12

PCIE_GTX_C_CRX_P13

PCIE_GTX_C_CRX_N13

PCIE_GTX_C_CRX_P14

PCIE_GTX_C_CRX_N14

PCIE_GTX_C_CRX_P15

PCIE_GTX_C_CRX_N15

+1.2VS

PCIE_FRX_C_LANTX_P0

PCIE_FRX_C_LANTX_N0

PCIE_FRX_WLANTX_P1

PCIE_FRX_WLANTX_N1

UMI_MTX_C_FRX_P0

UMI_MTX_C_FRX_N0

UMI_MTX_C_FRX_P1

UMI_MTX_C_FRX_N1

UMI_MTX_C_FRX_P2

UMI_MTX_C_FRX_N2

UMI_MTX_C_FRX_P3

UMI_MTX_C_FRX_N3

1 2

R1 196_0402_1%R1 196_0402_1%

PCIE_FRX_C_LANTX_P0<32>

PCIE_FRX_C_LANTX_N0<32>

PCIE_FRX_WLANTX_P1<31>

PCIE_FRX_WLANTX_N1<31>

UMI_MTX_C_FRX_P0<25>

UMI_MTX_C_FRX_N0<25>

UMI_MTX_C_FRX_P1<25>

UMI_MTX_C_FRX_N1<25>

UMI_MTX_C_FRX_P2<25>

UMI_MTX_C_FRX_N2<25>

UMI_MTX_C_FRX_P3<25>

UMI_MTX_C_FRX_N3<25>

AB8

AB7

AA9

AA8

AA5

AA6

Y8

Y7

W9

W8

W5

W6

V8

V7

U9

U8

U5

U6

T8

T7

R9

R8

R5

R6

P8

P7

N9

N8

N5

N6

M8

M7

AE5

AE6

AD8

AD7

AC9

AC8

AC5

AC6

AG8

AG9

AG6

AG5

AF7

AF8

AE8

AE9

P_ZVDDP P_ZVSS

AG11

PCI EXPRESS

P_GFX_RXP0

P_GFX_RXN0

P_GFX_RXP1

P_GFX_RXN1

P_GFX_RXP2

P_GFX_RXN2

P_GFX_RXP3

P_GFX_RXN3

P_GFX_RXP4

P_GFX_RXN4

P_GFX_RXP5

P_GFX_RXN5

P_GFX_RXP6

P_GFX_RXN6

P_GFX_RXP7

P_GFX_RXN7

P_GFX_RXP8

P_GFX_RXN8

P_GFX_RXP9

P_GFX_RXN9

P_GFX_RXP10

P_GFX_RXN10

P_GFX_RXP11

P_GFX_RXN11

P_GFX_RXP12

P_GFX_RXN12

P_GFX_RXP13

P_GFX_RXN13

P_GFX_RXP14

P_GFX_RXN14

P_GFX_RXP15

P_GFX_RXN15

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_UMI_RXP0

P_UMI_RXN0

P_UMI_RXP1

P_UMI_RXN1

P_UMI_RXP2

P_UMI_RXN2

P_UMI_RXP3

P_UMI_RXN3

P_ZVDDP

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

GPP GRAPHICS

GPP GRAPHICS

UMI

UMI

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

@

@

PCIE_CTX_GRX_P0

AB2

PCIE_CTX_GRX_N0

AB1

PCIE_CTX_GRX_P1

AA3

PCIE_CTX_GRX_N1

AA2

PCIE_CTX_GRX_P2

Y5

PCIE_CTX_GRX_N2

Y4

PCIE_CTX_GRX_P3

Y2

PCIE_CTX_GRX_N3

Y1

PCIE_CTX_GRX_P4

W3

PCIE_CTX_GRX_N4

W2

PCIE_CTX_GRX_P5

V5

PCIE_CTX_GRX_N5

V4

PCIE_CTX_GRX_P6

V2

PCIE_CTX_GRX_N6

V1

PCIE_CTX_GRX_P7

U3

PCIE_CTX_GRX_N7

U2

PCIE_CTX_GRX_P8

T5

PCIE_CTX_GRX_N8

T4

PCIE_CTX_GRX_P9

T2

PCIE_CTX_GRX_N9

T1

PCIE_CTX_GRX_P10

R3

PCIE_CTX_GRX_N10

R2

PCIE_CTX_GRX_P11

P5

PCIE_CTX_GRX_N11

P4

PCIE_CTX_GRX_P12

P2

PCIE_CTX_GRX_N12

P1

PCIE_CTX_GRX_P13

N3

PCIE_CTX_GRX_N13

N2

PCIE_CTX_GRX_P14

M5

PCIE_CTX_GRX_N14

M4

PCIE_CTX_GRX_P15

M2

PCIE_CTX_GRX_N15

M1

PCIE_FTX_LANRX_P0

AD5

PCIE_FTX_LANRX_N0

AD4

PCIE_FTX_WLANRX_P1

AD2

PCIE_FTX_WLANRX_N1

AD1

AC3

AC2

AB5

AB4

UMI_FTX_MRX_P0

AG2

UMI_FTX_MRX_N0

AG3

UMI_FTX_MRX_P1

AF4

UMI_FTX_MRX_N1

AF5

UMI_FTX_MRX_P2

AF1

UMI_FTX_MRX_N2

AF2

UMI_FTX_MRX_P3

AE2

UMI_FTX_MRX_N3

AE3

AH11

1 2

R2 196_0402_1%R2 196_0402_1%

PCIE_CTX_C_GRX_P[0..15] <12>

PCIE_CTX_C_GRX_N[0..15] <12>PCIE_GTX_C_CRX_N[0..15]<12>

C1 0.1U_0402_16V7KC1 0.1U_0402_16V7K

1 2

C2 0.1U_0402_16V7KC2 0.1U_0402_16V7K

1 2

C3 0.1U_0402_16V7KC3 0.1U_0402_16V7K

1 2

C4 0.1U_0402_16V7KC4 0.1U_0402_16V7K

1 2

C5 0.1U_0402_16V7KC5 0.1U_0402_16V7K

1 2

C6 0.1U_0402_16V7KC6 0.1U_0402_16V7K

1 2

C7 0.1U_0402_16V7KC7 0.1U_0402_16V7K

1 2

C8 0.1U_0402_16V7KC8 0.1U_0402_16V7K

1 2

C9 0.1U_0402_16V7KC9 0.1U_0402_16V7K

1 2

C10 0.1U_0402_16V7KC10 0.1U_0402_16V7K

1 2

C11 0.1U_0402_16V7KC11 0.1U_0402_16V7K

1 2

C37 0.1U_0402_16V7KC37 0.1U_0402_16V7K

1 2

C29 0.1U_0402_16V7KC29 0.1U_0402_16V7K

1 2

C35 0.1U_0402_16V7KC35 0.1U_0402_16V7K

1 2

C18 0.1U_0402_16V7KC18 0.1U_0402_16V7K

1 2

C16 0.1U_0402_16V7KC16 0.1U_0402_16V7K

1 2

C22 0.1U_0402_16V7KC22 0.1U_0402_16V7K

1 2

C38 0.1U_0402_16V7KC38 0.1U_0402_16V7K

1 2

C34 0.1U_0402_16V7KC34 0.1U_0402_16V7K

1 2

C20 0.1U_0402_16V7KC20 0.1U_0402_16V7K

1 2

C21 0.1U_0402_16V7KC21 0.1U_0402_16V7K

1 2

C23 0.1U_0402_16V7KC23 0.1U_0402_16V7K

1 2

C33 0.1U_0402_16V7KC33 0.1U_0402_16V7K

1 2

C24 0.1U_0402_16V7KC24 0.1U_0402_16V7K

1 2

C25 0.1U_0402_16V7KC25 0.1U_0402_16V7K

1 2

C26 0.1U_0402_16V7KC26 0.1U_0402_16V7K

1 2

C27 0.1U_0402_16V7KC27 0.1U_0402_16V7K

1 2

C28 0.1U_0402_16V7KC28 0.1U_0402_16V7K

1 2

C31 0.1U_0402_16V7KC31 0.1U_0402_16V7K

1 2

C30 0.1U_0402_16V7KC30 0.1U_0402_16V7K

1 2

C36 0.1U_0402_16V7KC36 0.1U_0402_16V7K

1 2

C32 0.1U_0402_16V7KC32 0.1U_0402_16V7K

1 2

C50 0.1U_0402_16V7KC50 0.1U_0402_16V7K

1 2

C55 0.1U_0402_16V7KC55 0.1U_0402_16V7K

1 2

C51 0.1U_0402_16V7KC51 0.1U_0402_16V7K

1 2

C54 0.1U_0402_16V7KC54 0.1U_0402_16V7K

1 2

C59 0.1U_0402_16V7KC59 0.1U_0402_16V7K

1 2

C60 0.1U_0402_16V7KC60 0.1U_0402_16V7K

1 2

C61 0.1U_0402_16V7KC61 0.1U_0402_16V7K

1 2

C62 0.1U_0402_16V7KC62 0.1U_0402_16V7K

1 2

C122 0.1U_0402_16V7KC122 0.1U_0402_16V7K

1 2

C123 0.1U_0402_16V7KC123 0.1U_0402_16V7K

1 2

C120 0.1U_0402_16V7KC120 0.1U_0402_16V7K

1 2

C121 0.1U_0402_16V7KC121 0.1U_0402_16V7K

1 2

PCIE_CTX_C_GRX_P0

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_N3

PCIE_CTX_C_GRX_P4

PCIE_CTX_C_GRX_N4

PCIE_CTX_C_GRX_P5

PCIE_CTX_C_GRX_N5

PCIE_CTX_C_GRX_P6

PCIE_CTX_C_GRX_N6

PCIE_CTX_C_GRX_P7

PCIE_CTX_C_GRX_N7

PCIE_CTX_C_GRX_P8

PCIE_CTX_C_GRX_N8

PCIE_CTX_C_GRX_P9

PCIE_CTX_C_GRX_N9

PCIE_CTX_C_GRX_P10

PCIE_CTX_C_GRX_N10

PCIE_CTX_C_GRX_P11

PCIE_CTX_C_GRX_N11

PCIE_CTX_C_GRX_P12

PCIE_CTX_C_GRX_N12

PCIE_CTX_C_GRX_P13

PCIE_CTX_C_GRX_N13

PCIE_CTX_C_GRX_P14

PCIE_CTX_C_GRX_N14

PCIE_CTX_C_GRX_P15

PCIE_CTX_C_GRX_N15

PCIE_FTX_C_LANRX_P0 <32>

PCIE_FTX_C_LANRX_N0 <32>

PCIE_FTX_C_WLANRX_P1 <31>

PCIE_FTX_C_WLANRX_N1 <31>

UMI_FTX_C_MRX_P0 <25>

UMI_FTX_C_MRX_N0 <25>

UMI_FTX_C_MRX_P1 <25>

UMI_FTX_C_MRX_N1 <25>

UMI_FTX_C_MRX_P2 <25>

UMI_FTX_C_MRX_N2 <25>

UMI_FTX_C_MRX_P3 <25>

UMI_FTX_C_MRX_N3 <25>

LAN

WLAN

3 3

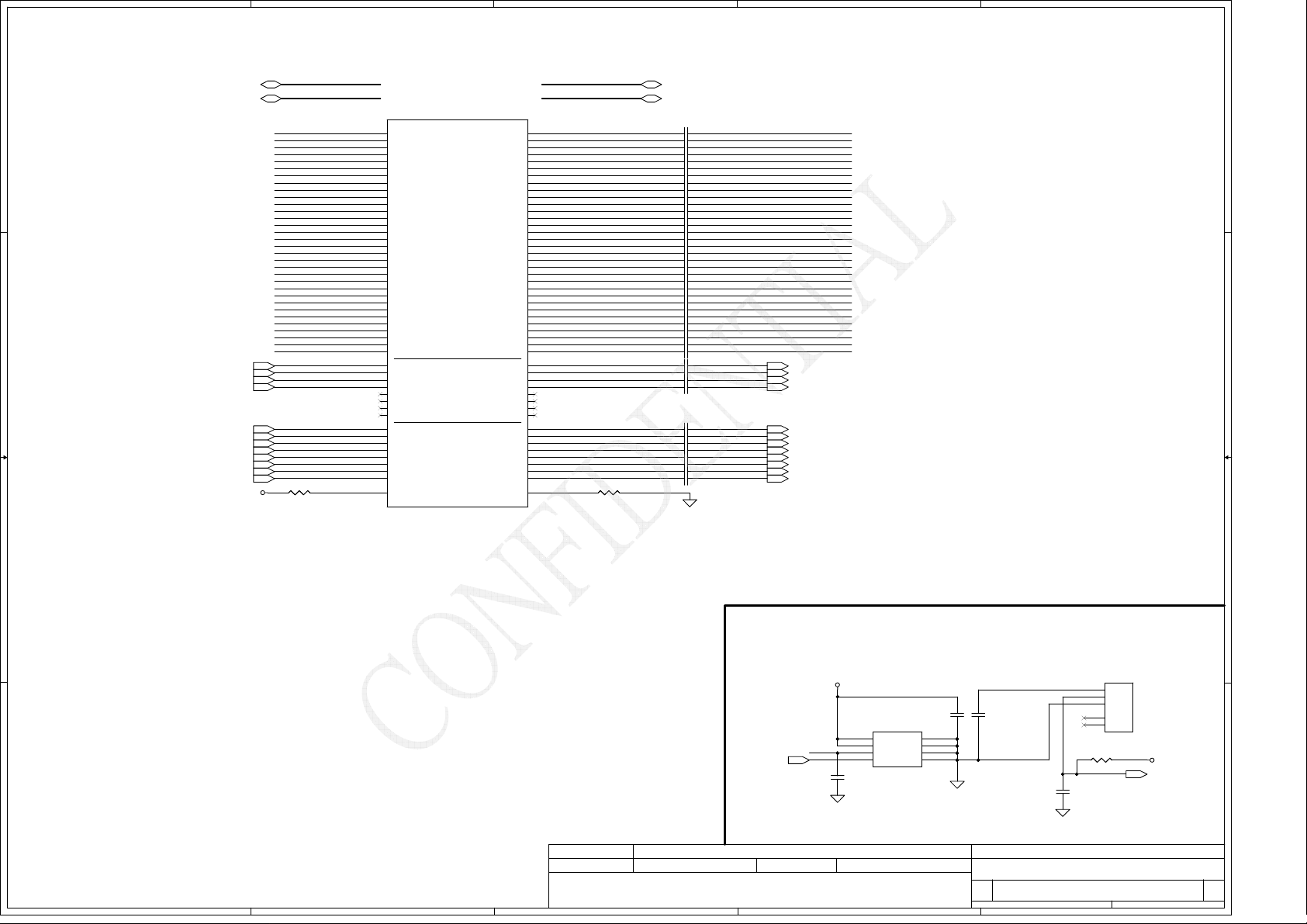

FAN Control Circuit

+5VS

1A

C13

C13

10U_0603_6.3V6M

10U_0603_6.3V6M

U2

U2

1

EN

2

EN_DFAN1<36>

4 4

A

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/11/28 2013/12/31

2011/11/28 2013/12/31

2011/11/28 2013/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

+FAN

10mil

Deciphered Date

Deciphered Date

Deciphered Date

3

4

1

C17

C17

APL5607KI-TRG_SO8

APL5607KI-TRG_SO8

10U_0603_6.3V6M

10U_0603_6.3V6M

2

D

VIN

VOUT

VSET

GND

GND

GND

GND

8

7

6

5

+FAN

2

2

C15

C15

1000P_0402_50V7K

1000P_0402_50V7K

@

@

1

1

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

1

2

3

4

5

ACES_85204-0300N

ACES_85204-0300N

R59 10K_0402_5%R59 10K_0402_5%

1

C14

C14

0.01U_0402_25V7K

0.01U_0402_25V7K

@

@

2

4019IT

4019IT

4019IT

JFAN

E

1

2

3

GND

GND

12

@JFAN

@

+3VS

FAN_SPEED1 <36>

551Friday, March 23, 2012

551Friday, March 23, 2012

551Friday, March 23, 2012

A

A

A

of

of

of

A

B

C

D

E

DDR_A_DQS[0..7]<10>

DDR_A_DQS#[0..7]<10>

1 1

JAPUB

JAPUB

MEMORY CHANNEL A

DDR_A_MA[0..15]<10>

DDR_A_BS0<10>

DDR_A_BS1<10>

DDR_A_BS2<10>

DDR_A_DM[0..7]<10>

2 2

DDR_A_CLK0<10>

DDR_A_CLK0#<10>

DDR_A_CLK1<10>

DDR_A_CLK1#<10>

DDR_A_CKE0<10>

DDR_A_CKE1<10>

DDR_A_ODT0<10>

DDR_A_ODT1<10>

3 3

DDR_A_SCS0#<10>

DDR_A_SCS1#<10>

DDR_A_RAS#<10>

DDR_A_CAS#<10>

DDR_A_WE#<10>

MEM_MA_RST#<10>

MEM_MA_EVENT#<10>

+1.5V

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_CLK0

DDR_A_CLK0#

DDR_A_CLK1

DDR_A_CLK1#

DDR_A_CKE0

DDR_A_CKE1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_SCS0#

DDR_A_SCS1#

DDR_A_RAS#

DDR_A_CAS#

MEM_MA_RST#

MEM_MA_EVENT#

15mil

+MEM_VREF

M_ZVDDIO

1 2

R60 39.2_0402_1%R60 39.2_0402_1%

M21

M22

AA25

AD27

AC23

AD19

AC15

AE26

AD26

AB22

AA22

AB18

AA18

AA14

AA15

AA27

AA26

W24

W23

W20

W21

U20

R20

R21

P22

P21

N24

N23

N20

N21

U23

L24

L21

L20

U24

U21

L23

E14

J17

E21

F25

G14

H14

G18

H18

J21

H21

E27

E26

T21

T22

R23

R24

H28

H27

Y25

V22

V21

H25

T24

MEMORY CHANNEL A

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_CKE0

MA_CKE1

MA_ODT0

MA_ODT1

MA_CS_L0

MA_CS_L1

MA_RAS_L

MA_CAS_L

MA_WE_L

MA_RESET_L

MA_EVENT_L

M_VREF

M_ZVDDIO

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

E13

J13

H15

J15

H13

F13

F15

E15

H17

F17

E19

J19

G16

H16

H19

F19

H20

F21

J23

H23

G20

E20

G22

H22

G24

E25

G27

G26

F23

H24

E28

F27

AB28

AC27

AD25

AA24

AE28

AD28

AB26

AC25

Y23

AA23

Y21

AA20

AB24

AD24

AA21

AC21

AA19

AC19

AC17

AA17

AB20

Y19

AD18

AD17

AA16

Y15

AA13

AC13

Y17

AB16

AB14

Y13

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56DDR_A_WE#

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_D[0..63] <10>

DDR_B_DQS[0..7]<11>

DDR_B_DQS#[0..7]<11>

JAPUC

JAPUC

MEMORY CHANNEL B

DDR_B_MA[0..15]<11>

DDR_B_BS0<11>

DDR_B_BS1<11>

DDR_B_BS2<11>

DDR_B_DM[0..7]<11>

DDR_B_CLK0<11>

DDR_B_CLK0#<11>

DDR_B_CLK1<11>

DDR_B_CLK1#<11>

DDR_B_CKE0<11>

DDR_B_CKE1<11>

DDR_B_ODT0<11>

DDR_B_ODT1<11>

DDR_B_SCS0#<11>

DDR_B_SCS1#<11>

DDR_B_RAS#<11>

DDR_B_CAS#<11>

DDR_B_WE#<11>

MEM_MB_RST#<11>

MEM_MB_EVENT#<11>

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS7

DDR_B_DQS#7

DDR_B_CLK0

DDR_B_CLK0#

DDR_B_CLK1

DDR_B_CLK1#

DDR_B_CKE0

DDR_B_CKE1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_SCS0#

DDR_B_SCS1#

DDR_B_RAS#

DDR_B_CAS#

DDR_B_WE#

MEM_MB_RST#

MEM_MB_EVENT#

M28

M27

M24

M25

W26

AF25

AG22

AH18

AD14

AG24

AG25

AG21

AF21

AG17

AG18

AH14

AG14

W27

T27

P24

P25

N27

N26

L26

U26

L27

K27

K25

K24

U27

T28

K28

D14

A18

A22

C25

C15

B15

E18

D18

E22

D22

B26

A26

R26

R27

P27

P28

J26

J27

Y28

V25

Y27

V24

V27

V28

J25

T25

MEMORY CHANNEL B

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CKE0

MB_CKE1

MB_ODT0

MB_ODT1

MB_CS_L0

MB_CS_L1

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

MB_EVENT_L

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

A14

B14

D16

E16

B13

C13

B16

A16

C17

B18

B20

A20

E17

B17

B19

C19

C21

B22

C23

A24

D20

B21

E23

B23

E24

B25

B27

D28

B24

D24

D26

C27

AG26

AH26

AF23

AG23

AG27

AF27

AH24

AE24

AE22

AH22

AE20

AH20

AD23

AD22

AD21

AD20

AF19

AE18

AE16

AH16

AG20

AG19

AF17

AD16

AG15

AD15

AG13

AD13

AG16

AF15

AE14

AF13

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D[0..63] <11>

EVENT# pull high 0.75V Reference Voltage

+1.5V

4 4

MEM_MA_EVENT#

MEM_MB_EVENT#

A

R15 1K_0402_5%R15 1K_0402_5%

1 2

R61 1K_0402_5%R61 1K_0402_5%

1 2

R64

R64

1K_0402_1%

1K_0402_1%

R65

R65

1K_0402_1%

1K_0402_1%

+1.5V

1 2

1 2

B

1

C124

C124

1000P_0402_50V7K

1000P_0402_50V7K

2

15mil

+MEM_VREF

2

C125

C125

0.1U_0402_16V7K

0.1U_0402_16V7K

1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/11/28 2013/12/31

2011/11/28 2013/12/31

2011/11/28 2013/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

4019IT

4019IT

4019IT

651Friday, March 23, 2012

651Friday, March 23, 2012

651Friday, March 23, 2012

E

of

of

of

A

A

A

A

Close to APU

C56 0.1U_0402_16V7KC56 0.1U_0402_16V7K

1 2

C48 0.1U_0402_16V7KC48 0.1U_0402_16V7K

1 2

C58 0.1U_0402_16V7KC58 0.1U_0402_16V7K

1 2

C53 0.1U_0402_16V7KC53 0.1U_0402_16V7K

1 2

LVDS

DP0_TXP0_C<21>

DP0_TXN0_C<21>

DP0_TXP1_C<21>

DP0_TXN1_C<21>

C63 0.1U_0402_16V7KC63 0.1U_0402_16V7K

1 1

CRT

(To FCH)

HDMI

ML_VGA_TXP0<27>

ML_VGA_TXN0<27>

ML_VGA_TXP1<27>

ML_VGA_TXN1<27>

ML_VGA_TXP2<27>

ML_VGA_TXN2<27>

ML_VGA_TXP3<27>

ML_VGA_TXN3<27>

UMA_HDMI_TX2+<24>

UMA_HDMI_TX2-<24>

UMA_HDMI_TX1+<24>

UMA_HDMI_TX1-<24>

UMA_HDMI_TX0+<24>

UMA_HDMI_TX0-<24>

UMA_HDMI_TXC+<24>

UMA_HDMI_TXC-<24>

100MHz (SS)

100MHz (NSS)

APU_SVC<47>

2 2

3 3

APU_SVD<47>

APU_SVT<47>

APU_VDD_RUN_FB_L<47>

APU_VDDNB_SEN<47>

APU_VDD_SEN<47>

1 2

C64 0.1U_0402_16V7KC64 0.1U_0402_16V7K

1 2

C65 0.1U_0402_16V7KC65 0.1U_0402_16V7K

1 2

C66 0.1U_0402_16V7KC66 0.1U_0402_16V7K

1 2

C67 0.1U_0402_16V7KC67 0.1U_0402_16V7K

1 2

C68 0.1U_0402_16V7KC68 0.1U_0402_16V7K

1 2

C69 0.1U_0402_16V7KC69 0.1U_0402_16V7K

1 2

C70 0.1U_0402_16V7KC70 0.1U_0402_16V7K

1 2

APU_CLKP<25>

APU_CLKN<25>

APU_DISP_CLKP<25>

APU_DISP_CLKN<25>

R31 0_0402_5%@R31 0_0402_5%@

1 2

R32 0_0402_5%@R32 0_0402_5%@

1 2

R33 0_0402_5%@R33 0_0402_5%@

1 2

APU_SIC<9>

APU_SID<9>

APU_RST#<25>

APU_PWRGD<25,47>

APU_ALERT#<27>

R212 0_0402_5%R212 0_0402_5%

1 2

R214 0_0402_5%R214 0_0402_5%

1 2

R215 0_0402_5%R215 0_0402_5%

1 2

APU_PROCHOT#

APU_THERMTRIP#

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

T9T9

T10T10

T13T13

UMA_HDMI_TX2+

UMA_HDMI_TX2-

UMA_HDMI_TX1+

UMA_HDMI_TX1-

UMA_HDMI_TX0+

UMA_HDMI_TX0-

UMA_HDMI_TXC+

UMA_HDMI_TXC-

APU_CLKP

APU_CLKN

APU_DISP_CLKP

APU_DISP_CLKN

APU_SVC_R

APU_SVD_R

APU_SVT_R

APU_SIC

APU_SID

APU_RST#

APU_PWRGD

VDDNB_SENSE

VDD_SENSE

DP0_TXP0

DP0_TXN0

DP0_TXN1

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

VSS_SENSE

B

JAPUD

JAPUD

ANALOG/DISPLAY/MISC

ANALOG/DISPLAY/MISC

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP2_TXP0

DP2_TXN0

DP2_TXP1

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

CLKIN_H

CLKIN_L

DISP_CLKIN_H

DISP_CLKIN_L

SVC

SVD

SVT

SIC

SID

RESET_L

PWROK

PROCHOT_L

THERMTRIP_L

ALERT_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

VSS_SENSE

VDDP_SENSE

VDDNB_SENSE

VDDIO_SENSE

VDD_SENSE

VDDR_SENSE

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

DISPLAY PORT 0

DISPLAY PORT 0

DISPLAY PORT MISC.

DISPLAY PORT MISC.

DISPLAY PORT 2 DISPLAY PORT 1

DISPLAY PORT 2 DISPLAY PORT 1

TEST

TEST

CTRL SER. CLK

CTRL SER. CLK

JTAG

JTAG

SENSE

SENSE

AE11

AD11

AB11

AA11

AG12

AH12

AF10

AB12

AC10

AE12

AF12

L3

L2

K5

K4

K2

K1

J3

J2

H5

H4

H2

H1

G3

G2

F2

F1

L9

L8

L5

L6

K8

K7

J6

J5

B3

A3

C3

H10

J10

F10

G10

F9

G9

H9

B4

C5

A4

A5

C4

B5

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

DP_BLON

DP_DIGON

DP_VARY_BL

DP_AUX_ZVSS

TEST10

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST20

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

DMAACTIVE_L

RSVD

RSVD

TEST6

TEST9

FS1R2

TEST4

TEST5

RSVD1

RSVD2

RSVD3

RSVD4

DP0_AUXP

D1

DP0_AUXN

D2

DP1_AUXP

E1

DP1_AUXN

E2

UMA_HDMI_CLK

D5

UMA_HDMI_DATA

D6

E5

E6

F5

F6

G5

G6

LVDS_HPD

D3

FCH_CRT_HPD

E3

HDMI_HPD

D7

E7

F7

G7

C6

B6

A6

DP_AUX_ZVSS

C1

AD12

M18

N18

F11

G11

H11

J11

APU_TEST18

F12

APU_TEST19

G12

APU_TEST20

J12

APU_TEST24

H12

TEST25_H

AE10

TEST25_L

AD10

L10

M10

P19

R19

APU_TEST31

K22

T19

N19

APU_TEST35

AA12

FS1R2

W10

DMA_ACTIVE#

AC12

P18

R18

Y10

AA10

Y12

K21

C

C47 0.1U_0402_16V7KC47 0.1U_0402_16V7K

1 2

C49 0.1U_0402_16V7KC49 0.1U_0402_16V7K

1 2

C57 0.1U_0402_16V7KC57 0.1U_0402_16V7K

1 2

C52 0.1U_0402_16V7KC52 0.1U_0402_16V7K

1 2

LVDS_HPD <21>

FCH_CRT_HPD <27>

HDMI_HPD <24>

DP_INT_PWM <9>

1 2

R16 150_0402_1%R16 150_0402_1%

T5T5

T6T6

T1T1

T2T2

T3T3

T4T4

R18 1K_0402_5%R18 1K_0402_5%

1 2

R19 1K_0402_5%R19 1K_0402_5%

1 2

R21 1K_0402_5%R21 1K_0402_5%

1 2

R22 1K_0402_5%R22 1K_0402_5%

1 2

R23 510_0402_1%R23 510_0402_1%

1 2

R24 510_0402_1%R24 510_0402_1%

1 2

T7T7

T8T8

R27 39.2_0402_1%R27 39.2_0402_1%

1 2

R28 300_0402_5%R28 300_0402_5%

1 2

R29 300_0402_5%@R29 300_0402_5%@

1 2

R30 10K_0402_5%R30 10K_0402_5%

1 2

DMA_ACTIVE# <25>

T11T11

T12T12

DP0_AUXP_C <21>

DP0_AUXN_C <21>

ML_VGA_AUXP <27>

ML_VGA_AUXN <27>

UMA_HDMI_CLK <24>

UMA_HDMI_DATA <24>

3.3V Tolerance

+1.2VS

Change TEST35 to pull-high

+1.5V

for HDMI issue

+3VALW

D

LVDS

CRT (To FCH)

HDMI

E

DP0_AUXP

DP0_AUXNDP0_TXP1

DP1_AUXP

DP1_AUXN

LVDS_HPD

FCH_CRT_HPD

HDMI_HPD

APU_SVT_R

APU_SVC_R

APU_SVD_RDP_INT_PWM

APU_SIC

APU_SID

APU_ALERT#

DMA_ACTIVE#

DMA_ACTIVE#

APU_RST#

APU_PWRGD

UMA_HDMI_CLK

UMA_HDMI_DATA

Aux signal are re-configured as I2C signals for DDC

APU AUX pin are 3.3V tolerant

+1.5V

R25 1.8K_0402_5%R25 1.8K_0402_5%

R58 1.8K_0402_5%R58 1.8K_0402_5%

R10 1.8K_0402_5%R10 1.8K_0402_5%

R11 1.8K_0402_5%R11 1.8K_0402_5%

R74 100K_0402_5%R74 100K_0402_5%

R75 100K_0402_5%R75 100K_0402_5%

R95 100K_0402_5%R95 100K_0402_5%

R36 1K_0402_5%@R36 1K_0402_5%@

R39 1K_0402_5%@R39 1K_0402_5%@

R41 1K_0402_5%@R41 1K_0402_5%@

R42 1K_0402_5%R42 1K_0402_5%

R44 1K_0402_5%R44 1K_0402_5%

R46 1K_0402_5%R46 1K_0402_5%

R48 1K_0402_5%R48 1K_0402_5%

R57 1K_0402_5%@R57 1K_0402_5%@

R52 300_0402_5%R52 300_0402_5%

R54 300_0402_5%R54 300_0402_5%

APU_RST#

APU_PWRGD

1 2

C126 1000P_0402_50V7K

C126 1000P_0402_50V7K

1 2

C127 1000P_0402_50V7K

C127 1000P_0402_50V7K

R66 4.7K_0402_5%R66 4.7K_0402_5%

R67 4.7K_0402_5%R67 4.7K_0402_5%

12

12

12

12

12

12

12

+1.5V

12

12

12

12

12

12

12

+1.5VS

12

12

12

@

@

@

@

+3VS

12

12

R55

R55

1K_0402_5%

+1.5V

Close to JHDT

R97 1K_0402_5%R97 1K_0402_5%

1 2

R100 1K_0402_5%R100 1K_0402_5%

1 2

R110 1K_0402_5%R110 1K_0402_5%

1 2

R116 1K_0402_5%R116 1K_0402_5%

1 2

R117 1K_0402_5%R117 1K_0402_5%

1 2

4 4

APU_TDI

APU_TCK

APU_TMS

APU_TRST#

APU_DBREQ#

@

@

1 2

R121 0_0402_5%

R121 0_0402_5%

@

@

1 2

R122 10K_0402_5%

R122 10K_0402_5%

@

@

1 2

R123 10K_0402_5%

R123 10K_0402_5%

@

@

1 2

R124 10K_0402_5%

R124 10K_0402_5%

A

HDT Debug conn

+1.5V

JHDT

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

SAMTE_ASP-136446-07-B

SAMTE_ASP-136446-07-B

B

@JHDT

@

2

4

6

8

10

12

14

16

18

20

2

4

6

8

10

12

14

16

18

20

APU_TCK

APU_TMS

APU_TDI

APU_TDO

APU_PWRGD_RR

APU_RST#_R

APU_DBRDY

APU_DBREQ#

Close to APU side, Debug Stuff

R125 0_0402_5%

R125 0_0402_5%

R127 0_0402_5%

R127 0_0402_5%

@

@

1 2

R118 0_0402_5%

R118 0_0402_5%

@

@

1 2

R119 0_0402_5%

R119 0_0402_5%

@

@

1 2

@

@

1 2

APU_TEST19

APU_TEST18

Security Classification

Security Classification

Security Classification

APU_PWRGDAPU_TRST#

APU_RST#

2011/11/28 2013/12/31

2011/11/28 2013/12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/11/28 2013/12/31

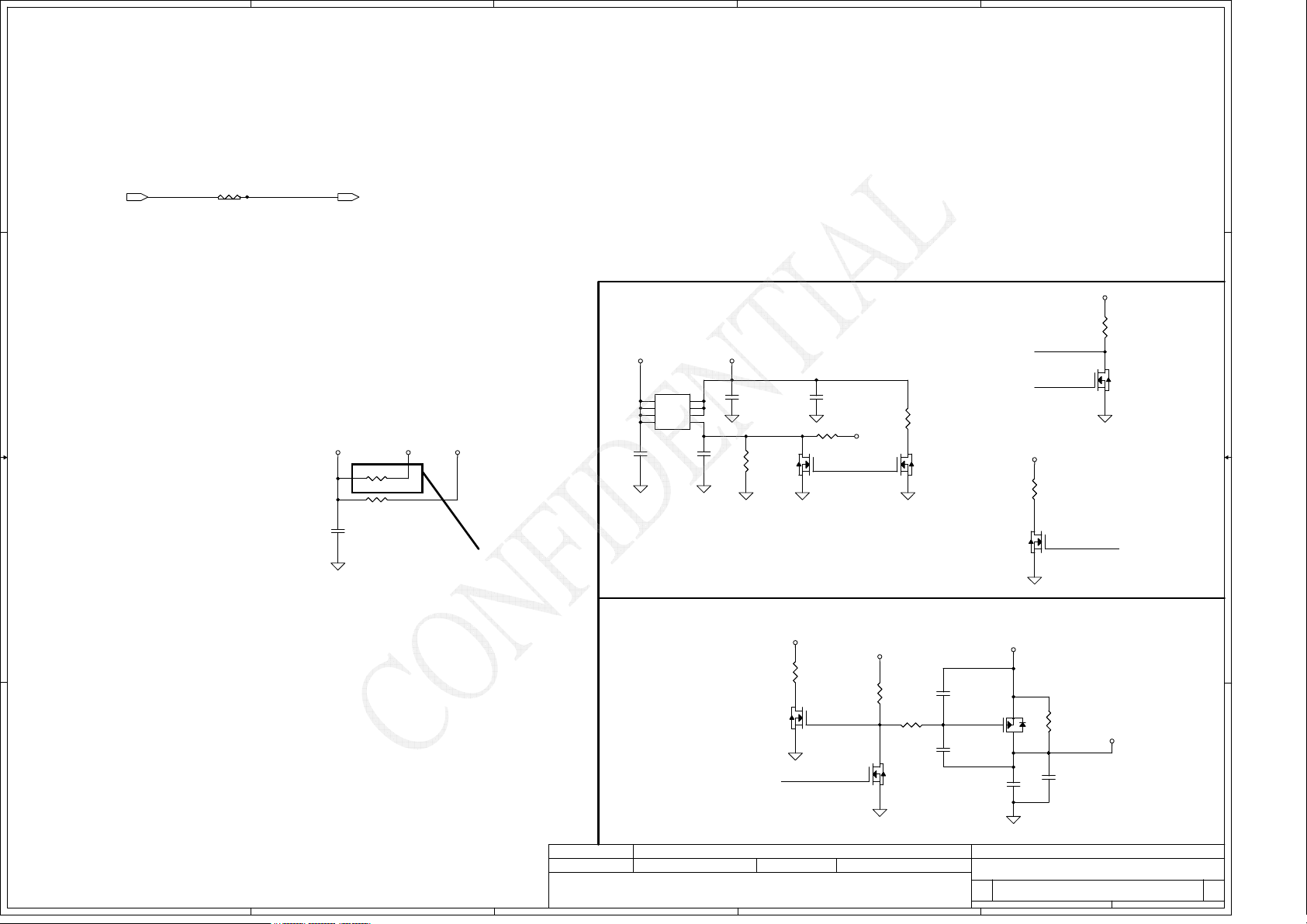

Asserted as an input to force the

processor into the HTC-active state

APU_PROCHOT#

Thermal Shutdown Temperature:

115 degree

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

APU_THERMTRIP#

1K_0402_5%

@

@

1 2

R136 0_0402_5%

R136 0_0402_5%

+1.5V

R68

R68

1K_0402_5%

1K_0402_5%

1 2

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

1 2

12

R69

R69

10K_0402_5%

10K_0402_5%

B

B

2

Q5

Q5

E

E

3 1

C

C

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

4019IT

4019IT

4019IT

H_PROCHOT# <36,47>APU_PROCHOT#<25>

H_THERMTRIP# <26>

751Friday, March 23, 2012

751Friday, March 23, 2012

751Friday, March 23, 2012

E

A

A

A

of

of

of

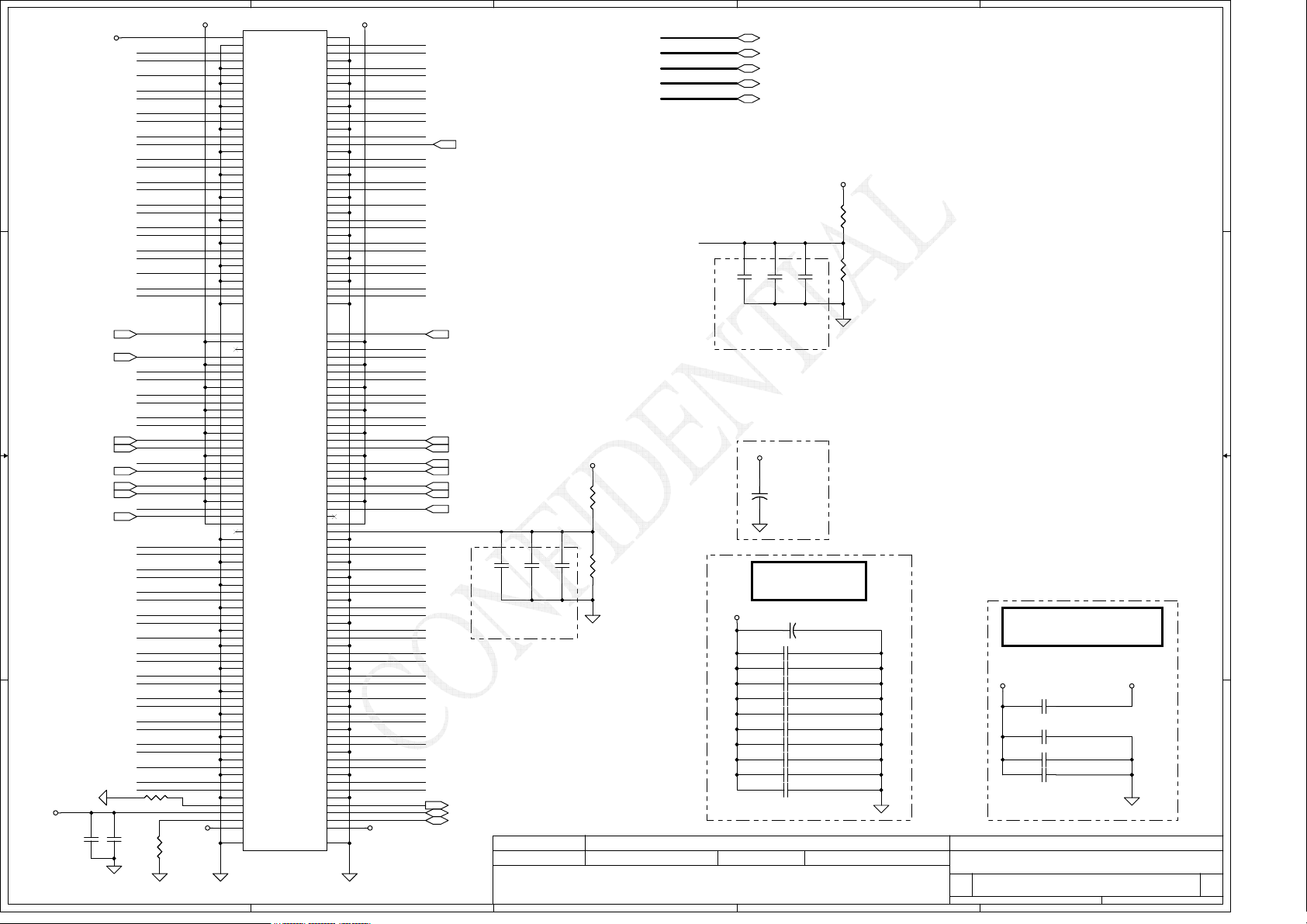

A

+APU_CORE

1 1

2 2

3 3

+2.5VS

L1

L1

1 2

FBMA-L11-201209-300LMA30T

FBMA-L11-201209-300LMA30T

C165

4 4

C165

1

2

C170

C170

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

+APU_CORE_NB

+1.2VS

C164

C164

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

12

2

+1.5V

3300P_0402_50V7K

3300P_0402_50V7K

40mil

+VDDA+VDDA

JAPUE

JAPUE

F8

VDD_1

H6

VDD_2

J1

VDD_3

J14

VDD_4

P6

VDD_5

P10

VDD_6

J16

VDD_7

J18

VDD_8

J9

VDD_9

K19

VDD_10

K3

VDD_11

K17

VDD_12

M3

VDD_13

K6

VDD_14

V10

VDD_15

V18

VDD_16

V3

VDD_17

50A

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VDD_23

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDNB_6

33A

VDDNB_7

VDDNB_8

VDDNB_9

VDDNB_10

VDDNB_11

VDDNB_12

VDDIO_1

VDDIO_2

VDDIO_3

VDDIO_4

VDDIO_5

VDDIO_6

VDDIO_7

VDDIO_8

VDDIO_9

VDDIO_10

VDDIO_11

3.2A

VDDIO_12

VDDIO_13

VDDIO_14

VDDIO_15

VDDIO_16

VDDIO_17

VDDIO_18

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

VDDA

0.75A

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

AA28

AB10

F3

L18

V6

W1

T18

Y14

AA1

AB6

AC1

R1

P3

K10

H3

M19

C8

D10

B8

B12

C9

A9

A10

A8

A11

E10

E11

C10

H26

K20

J28

K23

K26

L22

L25

L28

M20

M23

M26

N22

N25

N28

P20

P23

P26

AH6

AH5

AH4

AH3

AH7

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDD_50

VDD_51

VDD_52

VDD_53

VDD_54

VDD_55

VDD_56

VDD_57

VDD_58

VDD_59

VDD_60

VDD_61

VDD_62

VDDNB_13

VDDNB_14

VDDNB_15

VDDNB_16

VDDNB_17

VDDNB_18

VDDNB_19

VDDNB_20

VDDNB_21

VDDNB_22

VDDNB_23

VDDNB_CAP_1

VDDNB_CAP_2

VDDIO_19

VDDIO_20

VDDIO_21

VDDIO_22

VDDIO_23

VDDIO_24

VDDIO_25

VDDIO_26

VDDIO_27

VDDIO_28

VDDIO_29

VDDIO_30

VDDIO_31

VDDIO_32

VDDIO_33

VDDIO_34

VDDIO_35

VDDIO_36

VDDR_1

VDDR_2

VDDR_3

3.5A5A

VDDR_4

A

+APU_CORE

R11

T10

H8

G1

U11

W11

W13

W15

W17

W19

AB3

AD3

AD6

AE1

L1

Y6

M6

N11

N1

T3

T6

U19

U1

Y16

Y18

Y3

D4

F4

AF6

AF3

L11

C11

C12

D9

D8

D12

D11

B11

A12

B10

E12

B9

K13

K12

T23

T26

U22

U25

U28

Y26

T20

R28

R25

R22

V20

V23

V26

W22

W25

W28

Y24

G28

AG10

AH8

AH9

AH10

@

@

B

C76

C76

B

+1.2VS

+APU_CORE_NB

+VDDNB_CAP

+1.5V

C109

C109

1

2

C72

C72

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

2

2

C117

C117

C110

C110

180P_0402_50V8J

180P_0402_50V8J

1

2

C73

C73

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

+1.5V

C85

C85

1

2

C119

C119

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

2

2

VDDR Decoupling

C115

C115

C111

C111

180P_0402_50V8J

180P_0402_50V8J

1000P_0402_50V7K

1000P_0402_50V7K

1

1

2

2

VDDP Decoupling

C146

C146

C74

C74

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

2

2

C

C91

C89

C89

C88

C86

C86

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

C141

C141

180P_0402_50V8J

180P_0402_50V8J

1

2

C116

C116

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

2

C88

C87

C87

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

C77

C77

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

1

2

2

2

+1.5V

1

C102

C102

2

+1.2VS

C78

C78

C79

C79

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

2

1

2

2

C91

C90

C90

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

1

2

2

C104

C104

C103

C103

180P_0402_50V8J

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

10U_0603_6.3V6M

10U_0603_6.3V6M

180P_0402_50V8J

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

1

2

2

C93

C93

C94

C92

C92

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

2

C131

C131

1

2

C94

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

1

2

2

180P_0402_50V8J

180P_0402_50V8J

If the VSS plane is cut to

create a VDDIO plane,

place across the VDDIO

and VSS plane split

C96

C96

C95

C95

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

1

2

2

D

Co-layout with C100 on PVT

+1.5V

1

+

+

C147

C147

330U_D2_2V_Y

330U_D2_2V_Y

2

C98

C98

C97

C97

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

1

2

2

C130

C130

C99

C99

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

1

1

1

2

2

+

+

C100

C100

330U_2.5V_M_R17

330U_2.5V_M_R17

@

@

2

H=4.2mm

E

JAPUF

JAPUF

J20

VSS_1

L4

VSS_2

R7

VSS_3

W18

VSS_4

A15

VSS_5

AB17

VSS_6

AC22

VSS_7

AE21

VSS_8

AF24

VSS_9

AH23

VSS_10

AH25

VSS_11

B7

VSS_12

C14

VSS_13

C16

VSS_14

C2

VSS_15

C20

VSS_16

C22

VSS_17

C24

VSS_18

C26

VSS_19

C28

VSS_20

D13

VSS_21

D15

VSS_22

D17

VSS_23

D19

VSS_24

D23

VSS_25

D25

VSS_26

D27

VSS_27

E4

VSS_28

E9

VSS_29

F14

VSS_30

F16

VSS_31

F18

VSS_32

F20

VSS_33

F22

VSS_34

F26

VSS_35

F28

VSS_36

G13

VSS_37

G15

VSS_38

G17

VSS_39

G19

VSS_40

G21

VSS_41

G23

VSS_42

G25

VSS_43

G4

VSS_44

J22

VSS_45

J24

VSS_46

J4

VSS_47

J7

VSS_48

K11

VSS_49

K14

VSS_50

K9

VSS_51

AC11

VSS_52

L19

VSS_53

L7

VSS_54

M11

VSS_55

AF11

VSS_56

V19

VSS_57

V9

VSS_58

W16

VSS_59

W4

VSS_60

W7

VSS_61

Y11

VSS_62

Y20

VSS_63

Y22

VSS_64

Y9

VSS_65

A17

VSS_66

A13

VSS_67

K16

VSS_68

F24

VSS_69

G8

VSS_70

H7

VSS_71

J8

VSS_72

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

A19

A21

A23

A25

A7

AA4

AA7

AB13

AB15

AB19

AB21

AB23

AB25

AB27

AB9

AC14

AC16

AC18

AC20

AC24

AC26

AC28

AC4

AC7

AD9

AE13

AE15

AE17

M9

N10

N4

N7

R10

R4

T11

T9

U10

U18

U4

U7

V11

AE19

AE23

AE25

AE27

AE4

AE7

AF14

AF16

AF18

AF20

AF22

AF26

AF28

AF9

AG4

AG7

AH13

AH15

AH17

AH19

AH21

P9

C18

D21

W14

P11

C7

E8

K18

W12

@

@

Demo Board Capacitor

CORE_NB_CAP

22uF x 2

180pF x 1

VDDA

4.7uF x 1

0.22uF x 1

3.3nF x 1

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

4019IT

4019IT

4019IT

VDDIO_SUS

(CPU side)

22uF x 4

4.7uF x 4

0.22uF x 6 +2(split)

180pF x 1 + 2(split)

VDDIO_SUS

(DIMM x2)

100uF x 2

0.1uF x 12

E

851Friday, March 23, 2012

851Friday, March 23, 2012

851Friday, March 23, 2012

A

A

A

of

of

of

C143

C143

C144

C145

C145

180P_0402_50V8J

180P_0402_50V8J

1

2

C144

C75

C75

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

180P_0402_50V8J

180P_0402_50V8J

0.22U_0402_6.3V6K

1000P_0402_50V7K

1000P_0402_50V7K

1

1

1

@

@

2

2

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/11/28 2013/12/31

2011/11/28 2013/12/31

2011/11/28 2013/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

APU_CORE

22uF x 10

0.22uF x 2

0.01uF x 3

180pF x 2

VDDP

0.22uF x 2

180pF x 2

D

CORE_NB

22uF x 2

10uF x 1

0.22uF x 2

180pF x 3

VDDR

0.22uF x 2

1nF x 1

180pF x 2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

5

4

3

2

1

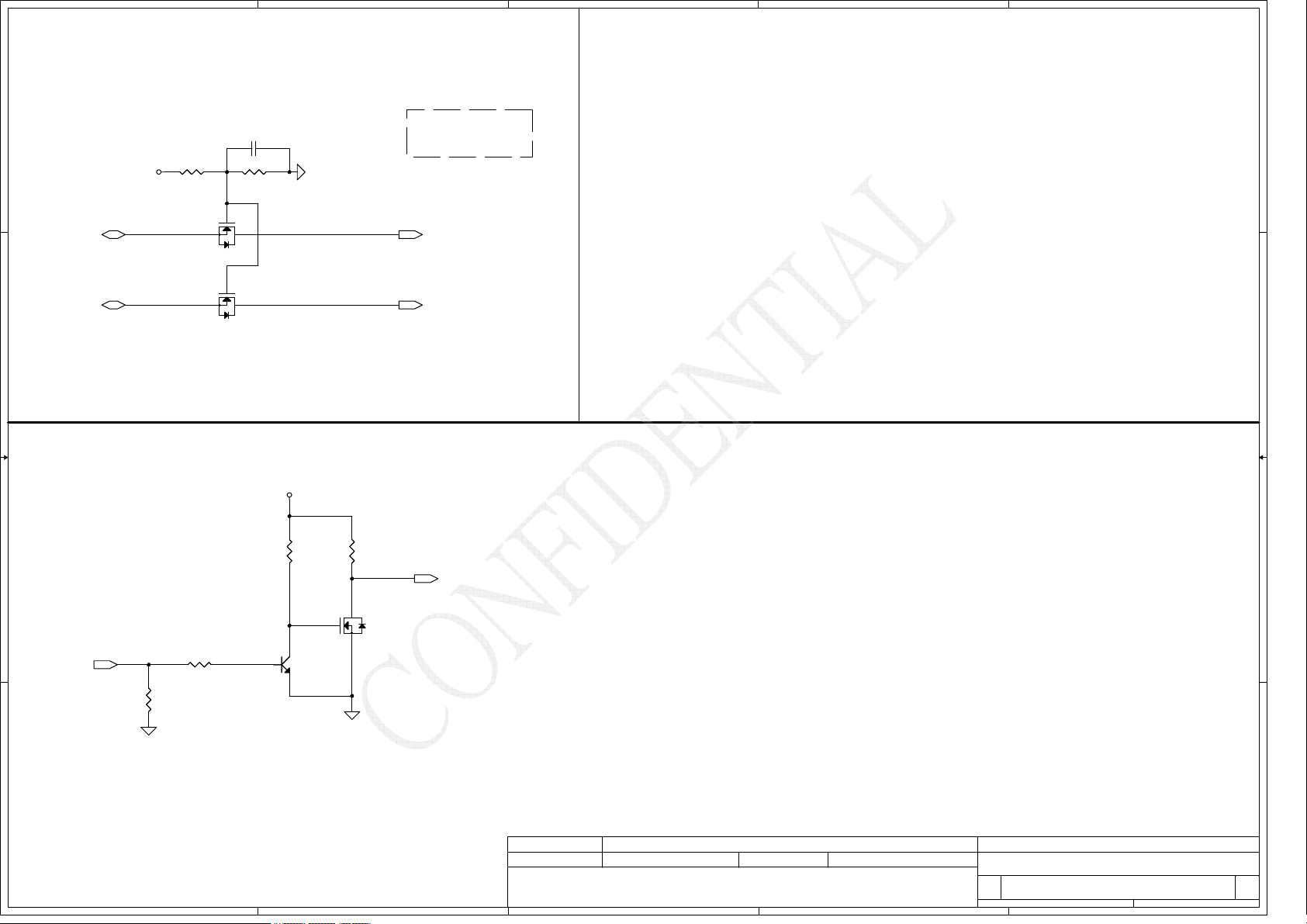

SB-TSI

CPU TSI interface level shift

D D

APU_SID<7>

APU_SIC<7>

C C

+3VS

BSH111_SOT23-3

BSH111_SOT23-3

APU_SIC

BSH111_SOT23-3

BSH111_SOT23-3

R535

R535

1 2

31.6K_0402_1%

31.6K_0402_1%

@

@

C935 0.1U_0402_16V4Z

C935 0.1U_0402_16V4Z

1 2

R536

R536

1 2

30K_0402_1%

30K_0402_1%

Vg = 1.607 V

G

G

2

Q14

Q14

EC_SMB_DA2APU_SID

13

D

S

D

S

G

G

2

Q15

Q15

EC_SMB_CK2

13

D

S

D

S

When APU High -> MOS OFF (Vgs < 0.4V )

APU Low -> MOS ON (Vgs > 1.3V)

BSH111, the Vgs is:

min = 0.4V

Max = 1.3V

EC_SMB_DA2 <13,36>

EC_SMB_CK2 <13,36>

Panel PWM

B B

DP_INT_PWM<7>

A A

1 2

R89 2.2K_0402_5%R89 2.2K_0402_5%

12

R76

R76

4.7K_0402_5%

4.7K_0402_5%

5

+3VS

12

R92

R92

47K_0402_5%

47K_0402_5%

C

C

Q21

Q21

2

B

B

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

E

E

3 1

2

G

G

12

R93

R93

4.7K_0402_5%

4.7K_0402_5%

13

D

D

Q26

Q26

2N7002_SOT23-3

2N7002_SOT23-3

S

S

APU_INVT_PWM <21>

Security Classification

Security Classification

Security Classification

2011/11/28 2013/12/31

2011/11/28 2013/12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/11/28 2013/12/31

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

SCHEMATIC,MB LA-8863

4019IT

4019IT

4019IT

951Friday, March 23, 2012

951Friday, March 23, 2012

951Friday, March 23, 2012

1

A

A

A

of

of

of

5

+VREF_DQA

D D

C C

B B

A A

+3VS

DDR_A_SCS1#<6>

C181

C181

DDR_A_BS2<6>

DDR_A_CLK0<6>

DDR_A_CLK0#<6>

DDR_A_BS0<6>

DDR_A_WE#<6>

DDR_A_CAS#<6>

@

@

1

C182

C182

2

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

R90

R90

10K_0402_5%

10K_0402_5%

1

@

@

2

DDR_A_D0

DDR_A_D1

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_A_CKE0

DDR_A_BS2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_CLK0

DDR_A_CLK0#

DDR_A_MA10

DDR_A_BS0

DDR_A_WE#

DDR_A_CAS#

DDR_A_MA13

DDR_A_SCS1#

DDR_A_D32

DDR_A_D33

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43