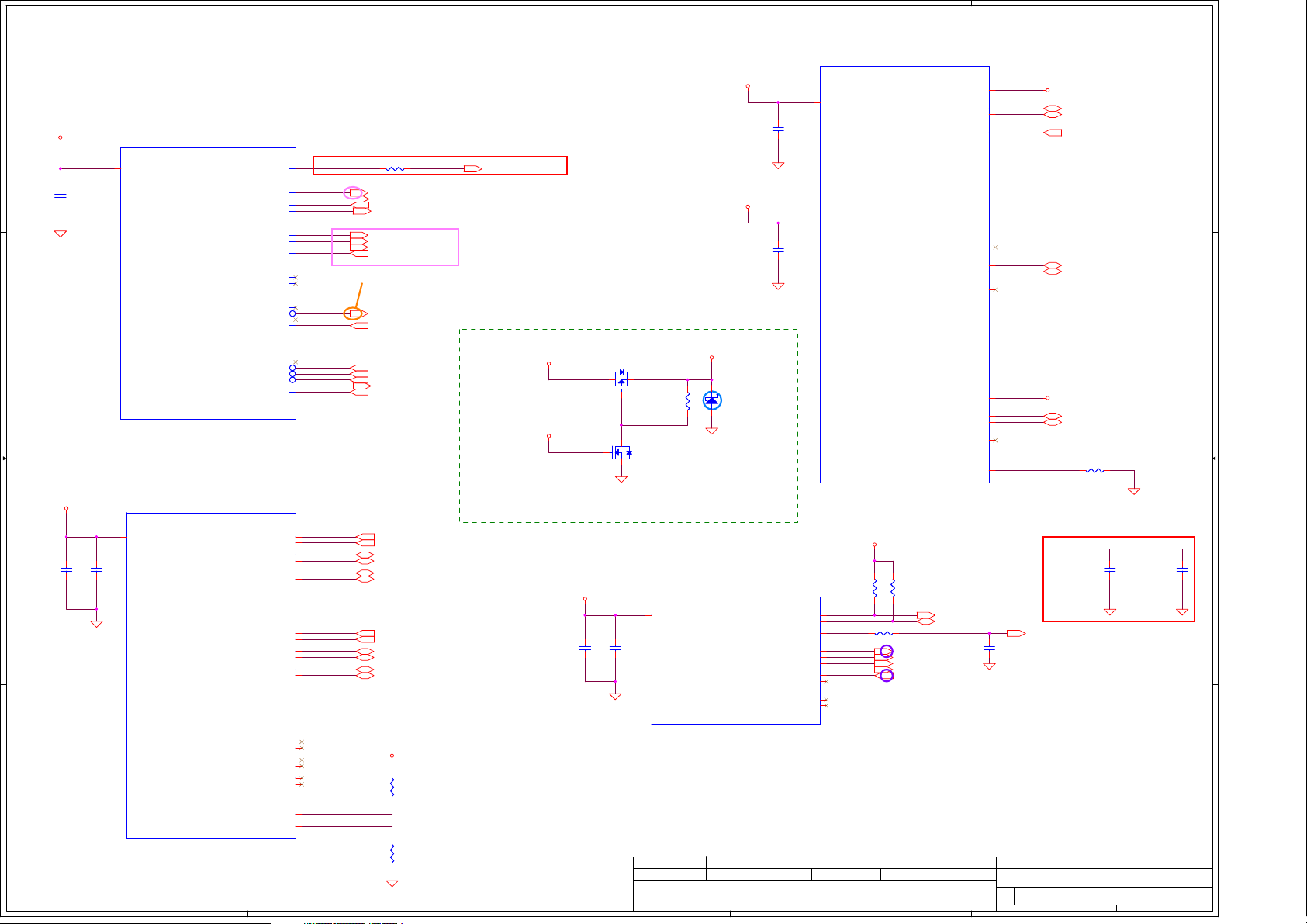

Compal LA-8511P QAJA0 PICASSO M Schematic

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1

Compal Electronics, Inc.

Cover Page

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Wednesday, January 18, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1

Compal Electronics, Inc.

Cover Page

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Wednesday, January 18, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1

Compal Electronics, Inc.

Cover Page

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Wednesday, January 18, 2012

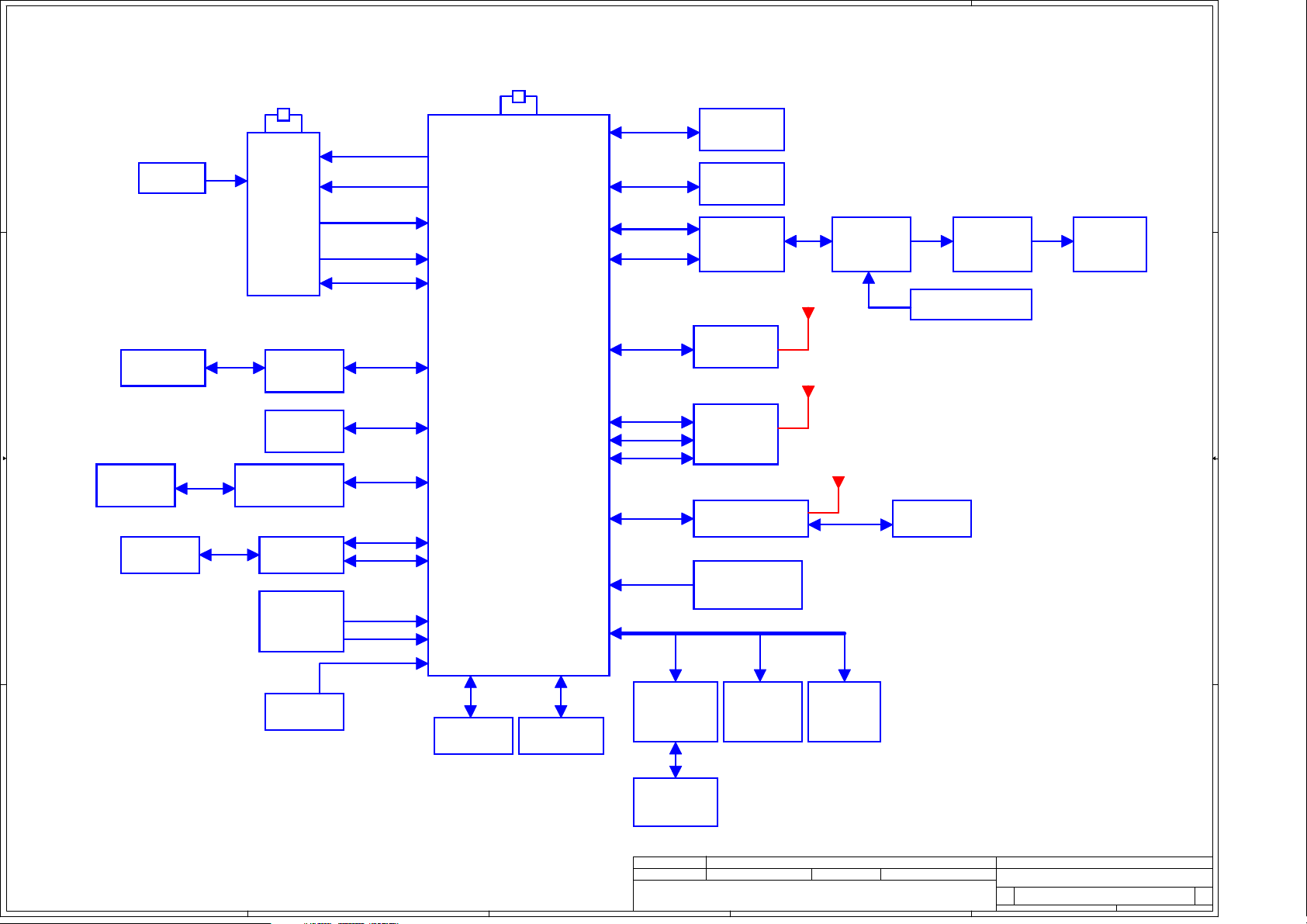

PICASSO M Schematics Document

REV: 1.0

Compal Confidential

2012-01-18

Nvdia(T30S) + LPDDRII

※

The content in this document contains confidential information of Compal Electronics, Inc.

that is protected under all applicable trade secrets laws and regulations.

If you are not the intended recipient or otherwise authorized to receive such information,

please do not copy, distribute or otherwise use the information contained herein and please

destroy this communication accordingly.

QAJA0-LA-8511P

ZZZ0

PCB

MB

ZZZ0

PCB

MB

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

2

Compal Electronics, Inc.

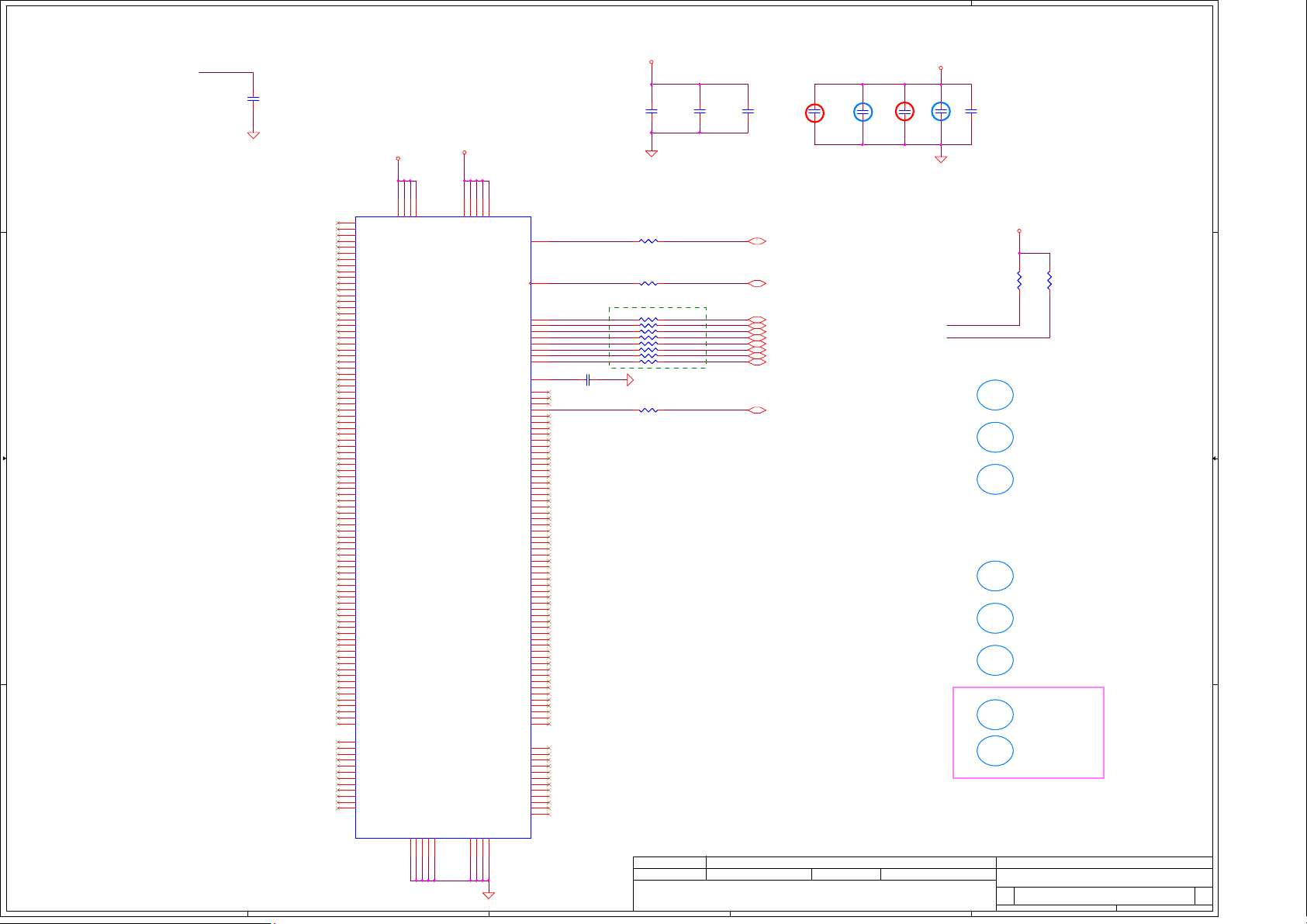

SYSTEM BLOCK

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Wednesday, January 18, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

2

Compal Electronics, Inc.

SYSTEM BLOCK

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Wednesday, January 18, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

2

Compal Electronics, Inc.

SYSTEM BLOCK

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Wednesday, January 18, 2012

Compal Confidential

Model Name : NVIDIA T30S System Block Diagram

Nvidia

T30S

SDIO4

(1.8V)

eMMC

P.11

SDIO1

(3.3V)

Micro SD slot

P.20

LPDDR2

512MB/1GB

P.9

Debug

Test Point

P.7

JTAG

I

2S

UART4

Audience

eS305

P.14 P.15

Audio Codec

WM8903

P.15

Audio AMP

APA2010

P.15

Speaker x 2

(1W)

MIC & Audio Jack

P.15

CIS(MIPI)

Broadcom

BCM47511

P.21

UART2

GPS Antenna

AzureWave

AW-AH660

P.22

BT/WLAN Antenna

UART3

SDIO

DAP

I2C

CAM_I2C CAM_I2C CAM_I2C

P.17

CAMERA

5M(CJAA525)

2M(CBFA152)

Host

Client

Signal Switch

P.20

USB2

3G Modem Module

P.18

3G Modem Antenna

P.20

Micro USB

G-Sensor

KXTF9-4100

IME

P.16

GYRO Sensor

MPU-3050

Light Sensor

STK2203

P.16

E-Compass

AKM8975

Dock/B

P.12

LVDS Transmitter

(V105A)

10.1" LCD

1920*1200

HDMI Switch

(1.8V/3.3V)

P.13

CORE_PWR_REQ

P.31~P.33

PMIC

T

PS659110

CPU_PWR_REQ

PMU_32K_IN

PWR_I2C

SYS_RESET_N

32KHz

VIN

Power ON

HDMI_DDC

SIM Card

P.18

P.19

Micro HDMI

P.13

Touch Panel

Control

Func/B

CAM_I2C

P-Senser

IQS12800100TSR

Dock/B

26MHz

EEPROM

P.10

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

3

Compal Electronics, Inc.

Notes List

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

3

Compal Electronics, Inc.

Notes List

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

3

Compal Electronics, Inc.

Notes List

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

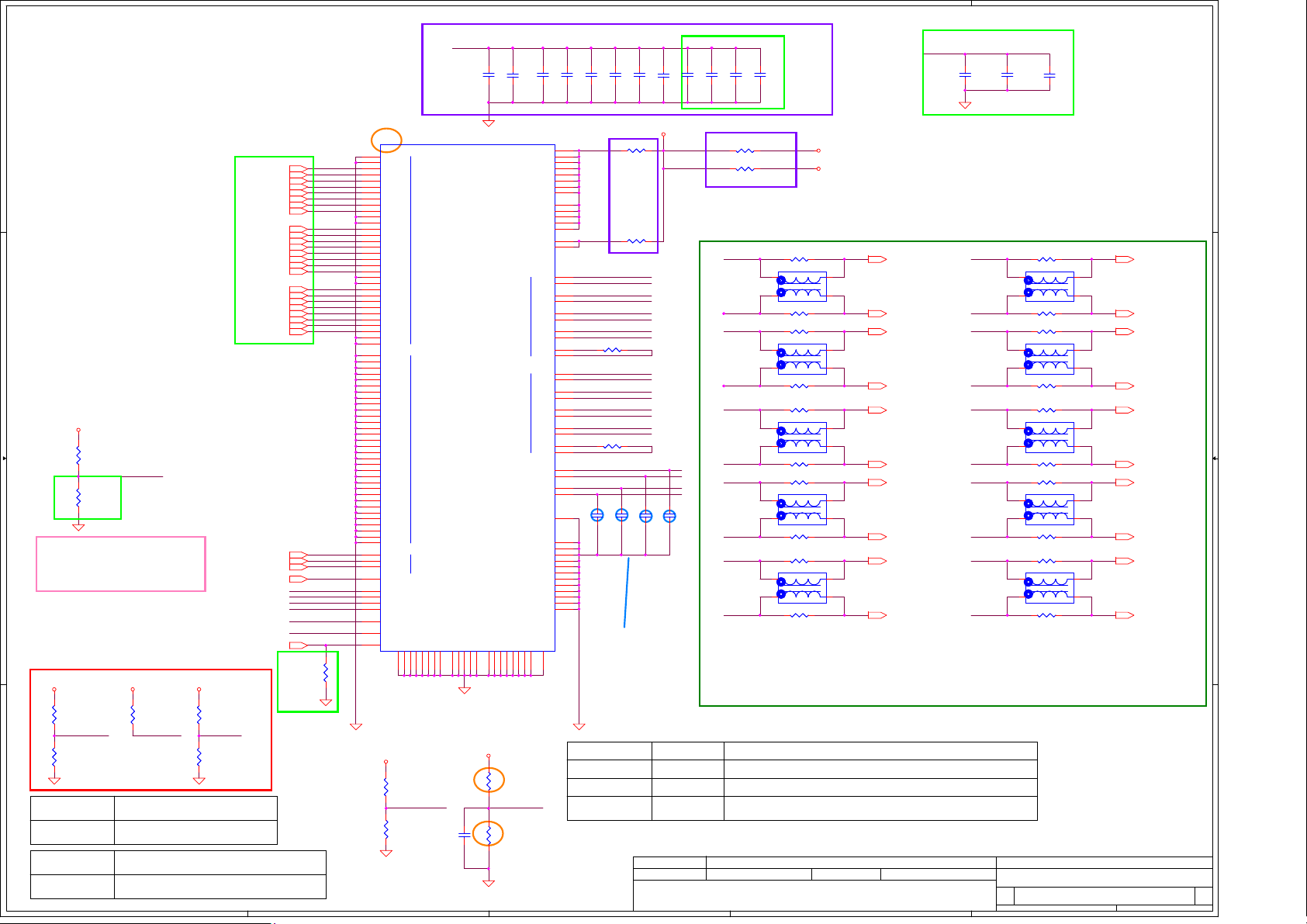

RTC power rail

+VDD_1V2_RTC_TEGRA

VDD_1V2_SOC

+VDD_1V8_PMU_VRTC

+AVDD_3V3_USB_TEGRA

Voltage Rails

VIN

B+

Adapter power supply (19V)

AC or battery power rail for power circuit.

Power for RTC and always-on core logic.

AVDD_PLL power rail

Power Plane Description

+AVDD_1V1_PLL_TEGRA

+5VS

+3VS 3.3V switched power rail for standby mode

1.8V switched power rail for standby mode

USB power rail

+VDD_1V8_SYS_TEGRA System power rail

+VDD_1V8_CAM_TEGRA

+VDD_2V85_EMMC Core voltage for EMMC

VDD_1V8_GEN

+AVDD_3V3_HDMI_S

Core voltage for CAMERA

HDMI power rail

Power for remainder of core logic

+VDD_3V3_DDR_RX_TEGRA DDR RX power rail

5V switched power rail for standby mode

+VDD_LED_BL

+VDD_3V3_SDMMC1_TEGRA

+VDD_VCM_3V3

LED power rail

Micro SD power rail

CAMERA power rail

+VDD_1V2_DDR_MEM DDR power rail

Board ID

Touch Screen

Camera 5M

Camera 2M

Gyro

E Compass

Light Senser

Flash LED

Thermal Senser

ES305

Codec

PMU

TPS62361

BATT Conn

Device Address<Write,Read>

Address<Write,Read>

CAM_I2C < +VDD_1V8_CAM_TEGRA >

PWR_I2C < +VDD_1V8_SYS_TEGRA>

Device

EEPROM (Low level) 0xA0 , 0xA1

0

xA2 , 0xA3EEPROM (High level)

GEN2_I2C / TS_I2C < +VDD_3V3_GMI_TEGRA >

Address<Write,Read>Device

Address<Write,Read>Device

0x98 , 0x99

0x78 , 0x79

0x20 , 0x21

0xD0 , 0xD1

0x18 , 0x19

0x38 , 0x39

0x66 , 0x67

0x98 , 0x99

0x3E

0x34 , 0x35

0x60

0xAA , 0xAB

0x2D

GEN1_I2C <+VDD_1V8_SENSOR >

LVDS strap pin

LPDDR2

PICASSO 2

PICASSO M

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

NV_LCD_PCLK

FORCE_RECOVERY#

NAND_D0

NOR_BOOT

NAND_D4

NAND_D5

NAND_D6

NAND_D7

NAND_D0

3.3V

10MIL

0.1A

EN_HDMI_3V3#

AVDD_HDMI_R

AVDD_HDMI_PLL

HDMI_PROBE

HDMI_RSET

BOOT_PD

NOR_BOOT

NAND_D5

NAND_D6

NAND_D7

NAND_D4

NAND_D5

NAND_D6

NAND_D7

NAND_D4

PCB_ID0

PCB_ID1

PCB_ID2

PCB_ID0

PCB_ID1

PCB_ID2

PCB_ID0

PCB_ID1

PCB_ID2

BOOT_PD

BOOT_PD

GEN2_I2C_SCL

GEN2_I2C_SDA

NV_LCD_PCLK LCD_PCLK_R

TS_PWR_EN

EN_WIFI_VDD

EN_SENSOR_3V3

BOARD_ID0

BOARD_ID1

BOARD_ID1

BOARD_ID0

BOARD_ID0

BOARD_ID1

EN_P_SENSOR

FORCE_RECOVERY#

+VDD_3V3_LCD_TEGRA

+VDD_3V3_GMI_TEGRA

+VDD_3V3_GMI_TEGRA

+AVDD_3V3_HDMI_S

+VDD_1V8_SDMMC4_TEGRA

+AVDD_3V3_HDMI_S

+VDD_3V3_GMI_TEGRA

+VDD_3V3_GMI_TEGRA

+VDD_3V3_GMI_TEGRA

+VDD_3V3_GMI_TEGRA

VDD_1V8_GEN

VDD_1V8_GEN

+3VS

+VDD_3V3_GMI_TEGRA

+VDD_1V8_SYS_TEGRA

LCD_DE <12>

LCD_HSYNC <12>

LCD_VSYNC <12>

LCD_D00 <12>

LCD_D01 <12>

LCD_D02 <12>

LCD_D03 <12>

LCD_D04 <12>

LCD_D05 <12>

LCD_D06 <12>

LCD_D07 <12>

LCD_D08 <12>

LCD_D09 <12>

LCD_D10 <12>

LCD_D11 <12>

LCD_D12 <12>

LCD_D13 <12>

LCD_D14 <12>

LCD_D15 <12>

LCD_D16 <12>

LCD_D17 <12>

DDC_SDA_R <19>

DDC_SCL_R <19>

HDMI_DET_T30S < 19>

GEN2_I2C_SDA <13>

LCD_PWM_OUT <13>

LCD_D18 <12>

LCD_D19 <12>

LCD_D20 <12>

LCD_D21 <12>

LCD_D22 <12>

LCD_D23 <12>

VIB_EN_T30S <20>

HDMI_TXCN <19>

HDMI_TXCP <19>

HDMI_TXD0N <19>

HDMI_TXD0P <19>

HDMI_TXD1N <19>

HDMI_TXD1P <19>

HDMI_TXD2N <19>

HDMI_TXD2P <19>

EMMC_DA0 <11>

EMMC_DA1 <11>

EMMC_DA2 <11>

EMMC_DA3 <11>

EMMC_DA4 <11>

EMMC_DA5 <11>

EMMC_DA6 <11>

EMMC_DA7 <11>

EMMC_CLK <11>

EMMC_CMD <11>

EMMC_RST# <11>

DISPOFF# <13,31>

TS_INT# <13>

CHARGER_STAT <27>

POUT_WIFI < 16>

TEMP_ALERT# <7>

3G_WAKE# <18>

TS_RST# <13>LVDS_SHTDN# <12>

GEN2_I2C_SCL <13>

LCD_PCLK <12>

EN_T30S_FUSE_3V3 <23>

LCD_DCR <13>

POUT_3G <20>

3G_DISABLE# <18>

EN_VDDLCD_T30S <13>

TS_PWR_EN <13>

POUT_3G_1 <20>

EN_WIFI_VDD <22>

EN_SENSOR_3V3 <23>

EN_HDMI_5V0 <19>

VOL_UP#<7,20>

VOL_DOWN#<7,20>

EN_P_SENSOR <20>

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

4

Compal Electronics, Inc.

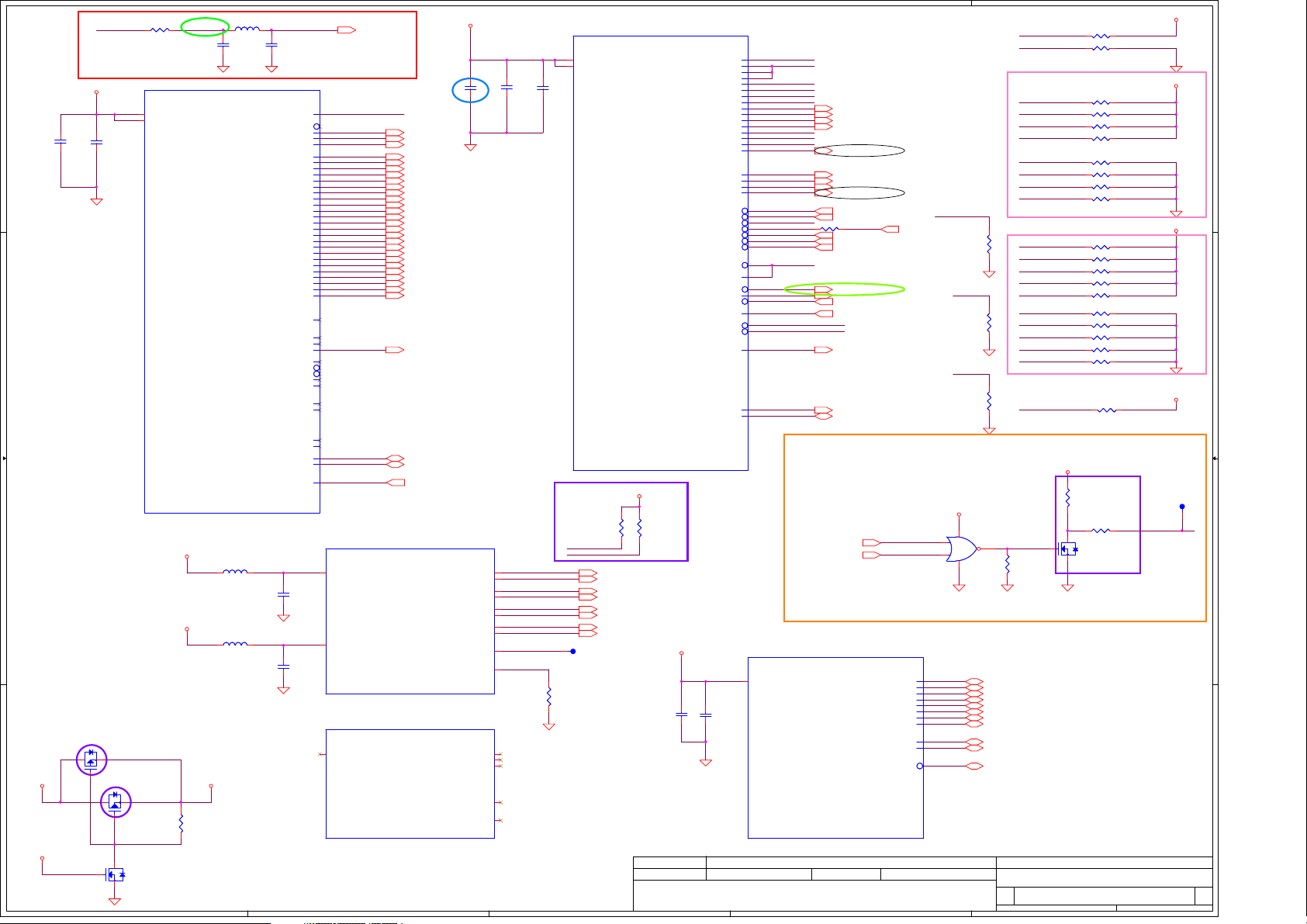

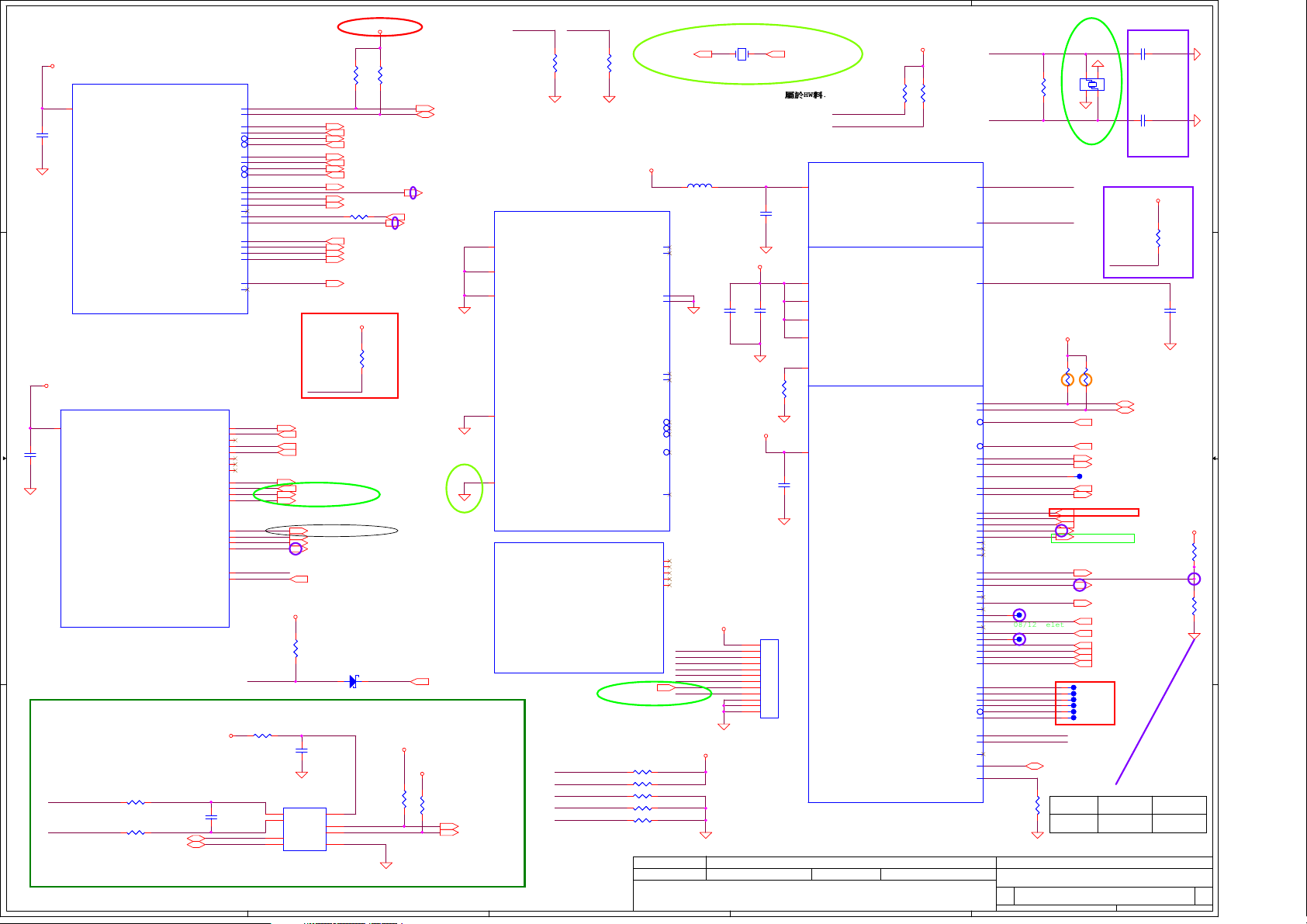

T30S(1/5)LCD/CRT/HDMI/NAND

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

4

Compal Electronics, Inc.

T30S(1/5)LCD/CRT/HDMI/NAND

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

4

Compal Electronics, Inc.

T30S(1/5)LCD/CRT/HDMI/NAND

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

SDMMC4 : eMMC

RF

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

Z

Z

PD

Z

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PU

PU

PU

PD

PU

PD

PD

PD

PU

PU

PD

PU

PU

PD

PU

PD

PU

Z

Z

Z

Z

Z

Z

PU

Z

Z

PU

Z

PU

Z

0

1

1

Z

1

PD

PD

PU

PU

PD

1

PD

1

Z

Z

Z

Z

PU

PU

PU

0

PU

PU

Z

Z

Z

Z

Z

Z

Z

Z

Z

Vth=1.4V

08/16 Change U55 footprint

08/16 Delete U56 footprint

Add

8/22 Change BOM structure

8/22 Change BOM structure to LPDDR2 & EMMC

9/15 Modify R23 from 100K to 47K.

9/15 Add R90 for FORCE_RECOVERY issue

9/19 Modify Q44 part number to SB00000J500 .

9/29 Leakage Issue

Modify R10&R11 from mount to unmount

10/03 Co-lay SOT-23 and SC-7 0

SB93413000000 and SB000009O0 0

11/6 Add for COMPAL EMI request.

R5 100K_0201_5%

X76_ELP_1GB@

R5 100K_0201_5%

X76_ELP_1GB@

12

L2

MPZ1005S300CT_2P

L2

MPZ1005S300CT_2P

1 2

R17

100K_0201_5%

R17

100K_0201_5%

12

9/21 VDAC

(2.8V)

U1J

T30S-R-A3-1.4G_FCCSP681

9/21 VDAC

(2.8V)

U1J

T30S-R-A3-1.4G_FCCSP681

VDAC_RSET

AM12

VDAC_VREF

AN11

VDAC_B

AH12

VDAC_G

AJ13

VDAC_R

AH14

AVDD_VDAC

AD2

R22 100K_0201_5%R22 100K_0201_5%

12

R79 100K_0201_5%

@

R79 100K_0201_5%

@

12

(1.8/3.3V)

4/21 GMI

U1E

T30S-R-A3-1.4G_FCCSP681

(1.8/3.3V)

4/21 GMI

U1E

T30S-R-A3-1.4G_FCCSP681

VDDIO_GMI_2

T12

VDDIO_GMI_1

P12

GEN2_I2C_SDA

E3

GEN2_I2C_SCL

D2

GMI_DQS

L7

GMI_WR*

M6

GMI_OE*

M2

GMI_IORDY

R7

GMI_WP*

L3

GMI_WAIT

N5

GMI_RST*

L5

GMI_CLK

L1

GMI_ADV*

M4

GMI_CS7*

L9

GMI_CS6*

M10

GMI_CS4*

H4

GMI_CS3*

K8

GMI_CS2*

G5

GMI_CS1*

P10

GMI_CS0*

R11

GMI_A19

R9

GMI_A18

N9

GMI_A17

M8

GMI_A16

P8

GMI_AD15

R5

GMI_AD14

P2

GMI_AD13

F4

GMI_AD12

F2

GMI_AD11

J1

GMI_AD10

J5

GMI_AD09

E1

GMI_AD08

G3

GMI_AD07

R3

GMI_AD06

N3

GMI_AD05

P6

GMI_AD04

P4

GMI_AD03

H2

GMI_AD02

J3

GMI_AD01

K6

GMI_AD00

J7

(1.8/3.3V)

8/21 LCD

U1I

T30S-R-A3-1.4G_FCCSP681

(1.8/3.3V)

8/21 LCD

U1I

T30S-R-A3-1.4G_FCCSP681

VDDIO_LCD_2

AH24

VDDIO_LCD_1

AG23

HDMI_INT

AN23

DDC_SDA

AT26

DDC_SCL

AH20

CRT_VSYNC

AJ21

CRT_HSYNC

AK18

LCD_DC1

AP24

LCD_DC0

AL27

LCD_SDIN

AR25

LCD_SDOUT

AM28

LCD_CS1*

AP18

LCD_CS0*

AL23

LCD_SCK

AK26

LCD_PWR2

AN25

LCD_PWR1

AP20

LCD_PWR0

AN17

LCD_M1

AM20

LCD_D23

AM24

LCD_D22

AR27

LCD_D21

AU23

LCD_D20

AN27

LCD_D19

AT24

LCD_D18

AT20

LCD_D17

AJ19

LCD_D16

AM22

LCD_D15

AL21

LCD_D14

AH18

LCD_D13

AJ17

LCD_D12

AT18

LCD_D11

AU27

LCD_D10

AR21

LCD_D09

AM26

LCD_D08

AU21

LCD_D07

AK22

LCD_D06

AK16

LCD_D05

AR23

LCD_D04

AJ23

LCD_D03

AN19

LCD_D02

AM18

LCD_D01

AP26

LCD_D00

AR17

LCD_VSYNC

AL17

LCD_HSYNC

AK20

LCD_DE

AR19

LCD_WR*

AK24

LCD_PCLK

AN21

G

D

S

Q3

BSS138W-7-F_SOT323-3

G

D

S

Q3

BSS138W-7-F_SOT323-3

2

13

R8 100K_0201_5%

R8 100K_0201_5%

12

R100 100K_0201_5%

LTE@

R100 100K_0201_5%

LTE@

12

C147

3300P_0201_16V6K

C147

3300P_0201_16V6K

1

2

R54

1M_0201_1%

R54

1M_0201_1%

12

R11

2.2K_0201_1%

@ R11

2.2K_0201_1%

@

12

R27

1M_0201_1%

R27

1M_0201_1%

12

C7

0.1U_0201_10V6K

C7

0.1U_0201_10V6K

1

2

R63 100K_0201_5%

QAJ70@

R63 100K_0201_5%

QAJ70@

12

R10

2.2K_0201_1%

@R10

2.2K_0201_1%

@

12

R6 100K_0201_5%

R6 100K_0201_5%

12

L49 27NH_LQG15HS27NJ02D_5%_0402L49 27NH_LQG15HS27NJ02D_5%_0402

1 2

C4

0.1U_0201_10V6K

C4

0.1U_0201_10V6K

1

2

C2

0.1U_0201_10V6K

C2

0.1U_0201_10V6K

1

2

C6

0.1U_0201_10V6K

C6

0.1U_0201_10V6K

1

2

C165

12P_0201_50V8J

C165

12P_0201_50V8J

1

2

R158 0_0201_5%R158 0_0201_5%

12

T21 PAD

@

T21 PAD

@

(1.2/1.8V)

5/21 SDMM4

U1F

T30S-R-A3-1.4G_FCCSP681

(1.2/1.8V)

5/21 SDMM4

U1F

T30S-R-A3-1.4G_FCCSP681

VDDIO_SDMMC4

E7

SDMMC4_RST*

B8

SDMMC4_CMD

H10

SDMMC4_CLK

F8

SDMMC4_DAT7

D8

SDMMC4_DAT6

C7

SDMMC4_DAT5

D6

SDMMC4_DAT4

A5

SDMMC4_DAT3

B4

SDMMC4_DAT2

C5

SDMMC4_DAT1

G9

SDMMC4_DAT0

B6

R12

100K_0201_5%

R12

100K_0201_5%

12

R43 100K_0201_5%@R43 100K_0201_5%@

12

L1

MPZ1005S300CT_2P

L1

MPZ1005S300CT_2P

1 2

R87 100K_0201_5%

NH660@

R87 100K_0201_5%

NH660@

12

R84 100K_0201_5%@R84 100K_0201_5%@

12

R88 100K_0201_5%

R88 100K_0201_5%

12

R154 100K_0201_5%

NONLTE@

R154 100K_0201_5%

NONLTE@

12

T1PAD@ T1PAD@

R2 100K_0201_5%R2 100K_0201_5%

12

R78 100K_0201_5%

R78 100K_0201_5%

12

C3

4.7U_0402_6.3V6M

C3

4.7U_0402_6.3V6M

1

2

R453

47_0402_5%

R453

47_0402_5%

12

R152 100K_0201_5%

QAJ50@

R152 100K_0201_5%

QAJ50@

12

C1

4.7U_0402_6.3V6M

C1

4.7U_0402_6.3V6M

1

2

G

D

S

Q2

NTS4101PT1G_SC70-3

@

G

D

S

Q2

NTS4101PT1G_SC70-3

@

2

1 3

R153 100K_0201_5%

AH663@

R153 100K_0201_5%

AH663@

12

C5

4.7U_0402_6.3V6M

C5

4.7U_0402_6.3V6M

1

2

10/21 HDMI

(1.8V)

(3.3V)

U1K

T30S-R-A3-1.4G_FCCSP681

10/21 HDMI

(1.8V)

(3.3V)

U1K

T30S-R-A3-1.4G_FCCSP681

AVDD_HDMI_PLL

AT8

AVDD_HDMI

AP8

HDMI_RSET

AM8

HDMI_PROBE

AR11

HDMI_TXD2P

AT12

HDMI_TXD2N

AU11

HDMI_TXD1P

AP14

HDMI_TXD1N

AR13

HDMI_TXD0P

AN13

HDMI_TXD0N

AP12

HDMI_TXCP

AN9

HDMI_TXCN

AR9

R18

100K_0201_5%

R18

100K_0201_5%

12

R85 100K_0201_5%@R85 100K_0201_5%@

12

C164

12P_0201_50V8J

C164

12P_0201_50V8J

1

2

G

D

S

Q6

AO3413_SOT23-3

G

D

S

Q6

AO3413_SOT23-3

2

1 3

R1 100K_0201_5%R1 100K_0201_5%

12

R23

47K_0201_1%

R23

47K_0201_1%

12

R26

1K_0201_1%

R26

1K_0201_1%

12

C8

0.1U_0201_10V6K

C8

0.1U_0201_10V6K

1

2

R38 100K_0201_5%

X76_SAM_1GB@

R38 100K_0201_5%

X76_SAM_1GB@

12

U55

74AUP1G02GW_TSSOP5

U55

74AUP1G02GW_TSSOP5

B

1

A

2

Y

4

G

3

Vcc

5

R7 100K_0201_5%

R7 100K_0201_5%

12

R89 100K_0201_5%

@

R89 100K_0201_5%

@

12

G

D

S

Q44

S TR DMN3150LW-7 1N SOT-323-3

G

D

S

Q44

S TR DMN3150LW-7 1N SOT-323-3

2

13

R90 47K_0201_1%

R90 47K_0201_1%

1 2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

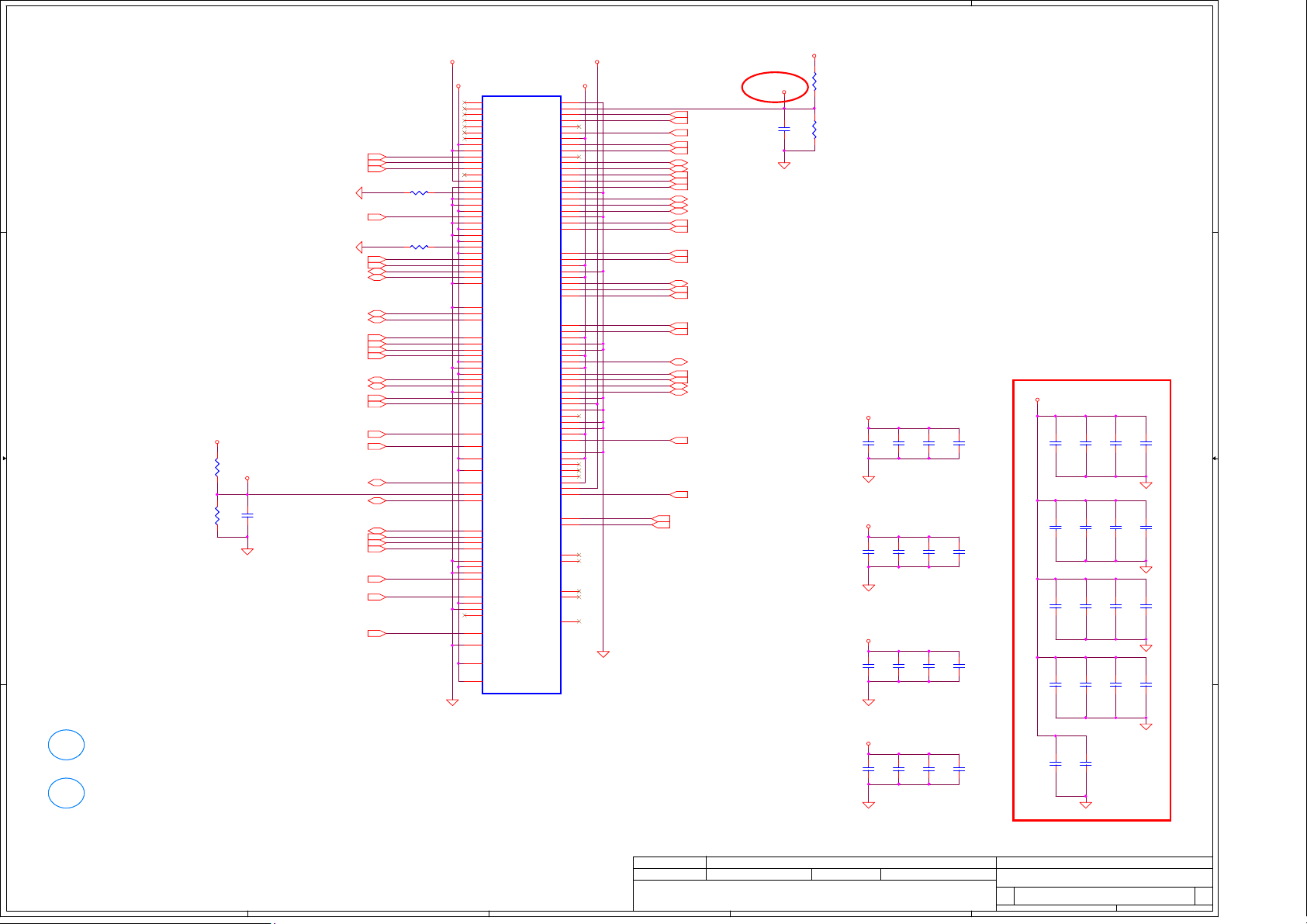

DDR_RESET

DDR_COMP_PD

QUSE2

QUSE3

QUSE0

DDR_COMP_PU

QUSE1

SDMMC1_COMP_PU

SDMMC1_COMP_PD

SDMMC3_COMP_PU

SDMMC3_COMP_PD

+VDD_3V3_SDMMC1_TEGRA

+VDD_3V3_SDMMC1_TEGRA

+VDD_1V8_SDMMC3_TEGRA

+VDD_1V8_SDMMC3_TEGRA

+VDD_3V3_DDR_RX_TEGRA

+VDD_1V0_DDR_HS_TEGRA

VDD_1V2_MEM

VDD_1V2_MEM

VDD_1V2_MEM

DDR_A_D0 <9>

DDR_A_D1 <9>

DDR_A_D2 <9>

DDR_A_D3 <9>

DDR_A_D4 <9>

DDR_A_D5 <9>

DDR_A_D6 <9>

DDR_A_D7 <9>

DDR_A_D8 <9>

DDR_A_D9 <9>

DDR_A_D10 < 9>

DDR_A_D11 < 9>

DDR_A_D12 < 9>

DDR_A_D13 < 9>

DDR_A_D14 < 9>

DDR_A_D15 < 9>

DDR_A_D16 < 9>

DDR_A_D17 < 9>

DDR_A_D18 < 9>

DDR_A_D19 < 9>

DDR_A_D20 < 9>

DDR_A_D21 < 9>

DDR_A_D22 < 9>

DDR_A_D23 < 9>

DDR_A_D24 < 9>

DDR_A_D25 < 9>

DDR_A_D26 < 9>

DDR_A_D27 < 9>

DDR_A_D28 < 9>

DDR_A_D29 < 9>

DDR_A_D30 < 9>

DDR_A_D31 < 9>

DDR_A_DM0 <9>

DDR_A_DM1 <9>

DDR_A_DM2 <9>

DDR_A_DM3 <9>

DDR_A_DQS#0 <9>

DDR_A_DQS#1 <9>

DDR_A_DQS#2 <9>

DDR_A_DQS#3 <9>

DDR_A_DQS0 <9>

DDR_A_DQS1 <9>

DDR_A_DQS2 <9>

DDR_A_DQS3 <9>

DDR_A_MA0 <9>

DDR_A_MA1 <9>

DDR_A_MA2 <9>

DDR_A_MA3 <9>

DDR_A_MA4 <9>

DDR_A_MA5 <9>

DDR_A_MA6 <9>

DDR_A_MA7 <9>

DDR_A_MA8 <9>

DDR_A_MA9 <9>

M_CS#0 <9>

M_CS#1 <9>

M_CKE0 <9>

M_CKE1 <9>

M_CLK_DDR#0 <9>

M_CLK_DDR0 <9>

SDMMC_DAT0 <20>

SDMMC_DAT1 <20>

SDMMC_DAT2 <20>

SDMMC_DAT3 <20>

SDMMC_CLK <20>

SDMMC_CMD <20>

WFMMC_DAT0 <22>

WFMMC_DAT1 <22>

WFMMC_DAT2 <22>

WFMMC_DAT3 <22>

WFMMC_CLK <22>

WFMMC_CMD <22>

CP_GPIO <27>

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

5

Compal Electronics, Inc.

T30S(2/5)OSC/PLL/SYS/DDR

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

5

Compal Electronics, Inc.

T30S(2/5)OSC/PLL/SYS/DDR

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

5

Compal Electronics, Inc.

T30S(2/5)OSC/PLL/SYS/DDR

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

SDMMC1 : SD card

SDMMC3 : WIFI

PU

PU

PU

PU

PU

PU

PD

Z

Z

Z

PU

PU

PU

PU

PU

PU

PU

PU

PU

PU

Acer request

Add U1.U3 GPIO to control Power CP function.

9/22

9/26 Modify BOARD_ID3 from U1.J37 to U1.R37

C18

0.1U_0201_10V6K

C18

0.1U_0201_10V6K

1

2

(1.8/3.0V)

16/21 IC_USB

U1N

T30S-R-A3-1.4G_FCCSP681

(1.8/3.0V)

16/21 IC_USB

U1N

T30S-R-A3-1.4G_FCCSP681

IC_USB_REXT

AD8

IC_USB_DP

AE3

IC_USB_DN

AD4

AVDD_IC_USB

AB8

C19

0.1U_0201_10V6K

C19

0.1U_0201_10V6K

1

2

R29 33.2_0402_1%R29 33.2_0402_1%

1 2

T17PAD@ T17PAD@

C20

0.1U_0201_10V6K

C20

0.1U_0201_10V6K

1

2

15/21 HSIC

(1.2V)

U1M

T30S-R-A3-1.4G_FCCSP681

15/21 HSIC

(1.2V)

U1M

T30S-R-A3-1.4G_FCCSP681

HSIC_REXT

AD10

HSIC_STROBE

AD6

HSIC_DATA

AC5

VDDIO_HSIC

Y2

(1.2/1.25/1.35/1.5V)

(2.8/3.3V)

(1.05V)

3/21 DDR MEMORY

U1D

T30S-R-A3-1.4G_FCCSP681

(1.2/1.25/1.35/1.5V)

(2.8/3.3V)

(1.05V)

3/21 DDR MEMORY

U1D

T30S-R-A3-1.4G_FCCSP681

VDD_DDR_HS_2

L23

VDD_DDR_HS_1

K12

VDD_DDR_RX

A15

VDDIO_DDR_14

T26

VDDIO_DDR_13

R25

VDDIO_DDR_12

P26

VDDIO_DDR_11

N23

VDDIO_DDR_10

N21

VDDIO_DDR_09

N19

VDDIO_DDR_08

N17

VDDIO_DDR_07

N15

VDDIO_DDR_06

M24

VDDIO_DDR_05

M22

VDDIO_DDR_04

M20

VDDIO_DDR_03

M18

VDDIO_DDR_02

M16

VDDIO_DDR_01

M14

DDR_COMP_PD

E15

DDR_COMP_PU

E17

DDR_QUSE3

H16

DDR_QUSE2

G15

DDR_QUSE1

D26

DDR_QUSE0

C27

DDR_RESET

K20

DDR_CLK

C19

DDR_CLK*

D18

DDR_CKE1

E19

DDR_CKE0

B20

DDR_ODT1

L19

DDR_ODT0

G23

DDR_CS1*

D20

DDR_CS0*

C21

DDR_BA2

F22

DDR_BA1

G21

DDR_BA0

F20

DDR_WE*

H22

DDR_CAS*

H20

DDR_RAS*

J21

DDR_A14

J19

DDR_A13

H18

DDR_A12

J17

DDR_A11

G17

DDR_A10

F16

DDR_A09

C17

DDR_A08

B14

DDR_A07

F18

DDR_A06

A17

DDR_A05

B18

DDR_A04

E23

DDR_A03

A23

DDR_A02

E21

DDR_A01

C23

DDR_A00

J23

DDR_DQS3P

F12

DDR_DQS3N

E11

DDR_DQS2P

H26

DDR_DQS2N

K26

DDR_DQS1P

B12

DDR_DQS1N

A11

DDR_DQS0P

A27

DDR_DQS0N

B26

DDR_DM3

J13

DDR_DM2

C29

DDR_DM1

E13

DDR_DM0

F26

DDR_DQ31

E9

DDR_DQ30

C9

DDR_DQ29

G11

DDR_DQ28

H12

DDR_DQ27

J15

DDR_DQ26

L15

DDR_DQ25

F10

DDR_DQ24

K14

DDR_DQ23

J25

DDR_DQ22

H28

DDR_DQ21

G29

DDR_DQ20

E27

DDR_DQ19

H24

DDR_DQ18

G27

DDR_DQ17

K24

DDR_DQ16

D30

DDR_DQ15

A9

DDR_DQ14

D12

DDR_DQ13

C11

DDR_DQ12

C13

DDR_DQ11

H14

DDR_DQ10

D14

DDR_DQ09

C15

DDR_DQ08

F14

DDR_DQ07

F24

DDR_DQ06

D24

DDR_DQ05

C25

DDR_DQ04

A29

DDR_DQ03

E25

DDR_DQ02

B30

DDR_DQ01

F28

DDR_DQ00

E29

C17

4.7U_0402_6.3V6M

C17

4.7U_0402_6.3V6M

1

2

C11

4.7U_0402_6.3V6M

C11

4.7U_0402_6.3V6M

1

2

C23

4.7U_0402_6.3V6M

C23

4.7U_0402_6.3V6M

1

2

R31 33.2_0402_1%

R31 33.2_0402_1%

1 2

C30

0.1U_0201_10V6K

C30

0.1U_0201_10V6K

1

2

C10

4.7U_0402_6.3V6M

C10

4.7U_0402_6.3V6M

1

2

(1.8/2.8~3.3V)

17/21 SDMMC1

U1P

T30S-R-A3-1.4G_FCCSP681

(1.8/2.8~3.3V)

17/21 SDMMC1

U1P

T30S-R-A3-1.4G_FCCSP681

VDDIO_SDMMC1

R1

CLK2_REQ

U5

CLK2_OUT

U3

GPIO_PV3

W9

GPIO_PV2

Y6

SDMMC1_COMP_PD

U9

SDMMC1_COMP_PU

AF10

SDMMC1_CMD

T8

SDMMC1_CLK

T6

SDMMC1_DAT3

Y10

SDMMC1_DAT2

U1

SDMMC1_DAT1

W11

SDMMC1_DAT0

U7

C24

4.7U_0402_6.3V6M

C24

4.7U_0402_6.3V6M

1

2

C12

4.7U_0402_6.3V6M

C12

4.7U_0402_6.3V6M

1

2

C108

0.1U_0201_10V6K

C108

0.1U_0201_10V6K

1

2

R32 33.2_0402_1%

R32 33.2_0402_1%

1 2

R33 0_0201_5%R33 0_0201_5%

1 2

R30 33.2_0402_1%R30 33.2_0402_1%

1 2

C109

0.1U_0201_10V6K

C109

0.1U_0201_10V6K

1

2

C21

0.1U_0201_10V6K

C21

0.1U_0201_10V6K

1

2

C215

33P 50V J NPO 0201

C215

33P 50V J NPO 0201

1

2

C14

0.1U_0201_10V6K

C14

0.1U_0201_10V6K

1

2

C110

0.1U_0201_10V6K

C110

0.1U_0201_10V6K

1

2

C15

0.1U_0201_10V6K

C15

0.1U_0201_10V6K

1

2

C25

0.1U_0201_10V6K

<BOM Structure>

C25

0.1U_0201_10V6K

<BOM Structure>

1

2

R36 49.9_0402_1%R36 49.9_0402_1%

1 2

R35 49.9_0402_1%R35 49.9_0402_1%

1 2

C26

4.7U_0402_6.3V6M

<BOM Structure>

C26

4.7U_0402_6.3V6M

<BOM Structure>

1

2

T3PAD@ T3PAD@

C16

0.1U_0201_10V6K

C16

0.1U_0201_10V6K

1

2

C205

33P 50V J NPO 0201

C205

33P 50V J NPO 0201

1

2

R34 0_0201_5%R34 0_0201_5%

1 2

C22

0.1U_0201_10V6K

C22

0.1U_0201_10V6K

1

2

C13

4.7U_0402_6.3V6M

C13

4.7U_0402_6.3V6M

1

2

6/21 SDMMC3

(1.8/2.8~3.3V)

U1O

T30S-R-A3-1.4G_FCCSP681

<BOM Structure>

6/21 SDMMC3

(1.8/2.8~3.3V)

U1O

T30S-R-A3-1.4G_FCCSP681

<BOM Structure>

VDDIO_SDMMC3

M36

SDMMC3_COMP_PD

N35

SDMMC3_COMP_PU

L35

SDMMC3_CMD

M30

SDMMC3_CLK

J35

SDMMC3_DAT7

M28

SDMMC3_DAT6

M32

SDMMC3_DAT5

N29

SDMMC3_DAT4

J37

SDMMC3_DAT3

P34

SDMMC3_DAT2

M34

SDMMC3_DAT1

L37

SDMMC3_DAT0

N33

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

USB_REXT

DSI_CSI_RUP

DSI_CSI_RDN

3.3V

10MIL

0.1A

EN_T30S_USB1

AUDIO_CLK

CAM_I2C_SCL CAM_I2C_SDA

+T30S_USB1

+AVDD_1V8_USB_PLL_TEGRA

+AVDD_1V2_DSI_CSI_TEGRA

+AVDD_3V3_USB_TEGRA

+VDD_1V8_CAM_TEGRA

+VDD_1V8_CAM_TEGRA

+AVDD_3V3_USB_TEGRA

+T30S_USB1

+VDD_1V8_AUDIO_TEGRA

+AVDD_1V2_DSI_CSI_TEGRA

VBUS_USB

+T30S_USB1

3G_USB_DN <18>

3G_USB_DP <18>

USB1_DN <20>

USB1_DP <20>

5M_CAM_DA1#_R < 17>

5M_CAM_DA1_R <17>

5M_CAM_DA2#_R < 17>

5M_CAM_DA2_R <17>

2M_CAM_DA1#_R < 17>

2M_CAM_DA1_R <17>

CAM_I2C_SDA <17,26,35>

CAM_I2C_SCL <17,26,35>

USB1_ID <20>

CAM_MCLK <17>

CDC_IRQ# <15>

AUDIO_CLK_R <15>

AUDIO_RST# <14>

ENABLE_USB_HOST <20,27>

ES305_INT_R <14>

GYRO_INT_R <16>

LIGHT_INT <20>

HP_DET# <20>

2M_CAM_DA2#_R < 17>

2M_CAM_DA2_R <17>

COMPASS_DRDY <20>

EN_ES305_OSC <14>

5M_CAM_CLK#_R <17>

5M_CAM_CLK_R <17>

2M_CAM_CLK#_R <17>

2M_CAM_CLK_R <17>

5M_CAM_RST# <17>

5M_CAM_PWDN <17>

2M_CAM_PWDN <17>

USB_HOST_DN <20>

USB_HOST_DP <20>

AUDIO_SEL <14>

AUDIO_SCLK2 <14>

AUDIO_FS2 < 14>

AUDIO_DOUT2 <14>

AUDIO_DIN2 <14>

DOCK_DET# <20>

2M_CAM_RST# <17>

BATT_LEARN <27>

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

6

Compal Electronics, Inc.

T30S(3/5)USB/SDIO/UART/AUDIO

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

6

Compal Electronics, Inc.

T30S(3/5)USB/SDIO/UART/AUDIO

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

6

Compal Electronics, Inc.

T30S(3/5)USB/SDIO/UART/AUDIO

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

U1Q is not place on grid , need check connection

USB VBUS overvoltage protection

RF note

RF note

PU

PU

PD

PD

PD

PD

PD

PD

PD

PD

PU

PD

PD

PU

PU

PU

PU

PU

PU

PD

Z

Z

Z

Z

Z

PU

PU

Z

Z

Z

Z

8/24 Modify Off-Page type.

9/26 Swap U1.AM16 to U1.AM10 for WAKE UP issue

10/03 Add D18 on +T30S_USB1 to protect CPU.

SC400003Z00

10/19 Modify D18 from +T30S_ USB1 to VBUS_USB

10/24 Add BATT_LEARN GPIO to Power request.

12/2 Modify D18 from moun to @,Add Zener on samll board.

R45

49.9_0402_1%

R45

49.9_0402_1%

12

R40

2.2K_0201_1%

R40

2.2K_0201_1%

12

C27

4.7U_0402_6.3V6M

C27

4.7U_0402_6.3V6M

1

2

C31

4.7U_0402_6.3V6M

C31

4.7U_0402_6.3V6M

1

2

R39

1K_0201_1%

R39

1K_0201_1%

12

G

D

S

Q5

BSS138W-7-F_SOT323-3

G

D

S

Q5

BSS138W-7-F_SOT323-3

2

13

R37 0_0201_5%R37 0_0201_5%

1 2

D18

BZT52-B5V6S_SOD323-2

@

D18

BZT52-B5V6S_SOD323-2

@

2 1

(1.8/3.3V)

13/21 AUDIO

U1Q

T30S-R-A3-1.4G_FCCSP681

(1.8/3.3V)

13/21 AUDIO

U1Q

T30S-R-A3-1.4G_FCCSP681

VDDIO_AUDIO

G33

SPI2_MISO

E37

SPI2_MOSI

D36

SPI2_CS2*

F30

SPI2_CS1*

B32

SPI2_CS0*

J33

SPI2_SCK

K32

SPI1_MISO

F36

SPI1_MOSI

L33

SPI1_CS0*

H36

SPI1_SCK

G35

SPDIF_OUT

J31

SPDIF_IN

L31

DAP2_DIN

C33

DAP2_DOUT

F34

DAP2_FS

K30

DAP2_SCLK

H34

DAP1_DIN

A33

DAP1_DOUT

D32

DAP1_FS

B34

DAP1_SCLK

L29

CLK1_OUT

E35

R72 0_0201_5%R72 0_0201_5%

1 2

C32

0.1U_0201_10V6K

C32

0.1U_0201_10V6K

1

2

(1.2V)

7/21 DSI/CSI

U1H

T30S-R-A3-1.4G_FCCSP681

(1.2V)

7/21 DSI/CSI

U1H

T30S-R-A3-1.4G_FCCSP681

AVDD_DSI_CSI

AF2

DSI_CSI_RDN

AT4

DSI_CSI_RUP

AG7

DSI_D2AP

AG9

DSI_D2AN

AH8

DSI_D1AP

AM2

DSI_D1AN

AN1

DSI_CLKAP

AK2

DSI_CLKAN

AJ1

CSI_D2BP

AP6

CSI_D2BN

AT6

CSI_D1BP

AL3

CSI_D1BN

AK4

CSI_CLKBP

AN7

CSI_CLKBN

AR7

CSI_D2AP

AK10

CSI_D2AN

AL9

CSI_D1AP

AJ3

CSI_D1AN

AJ5

CSI_CLKAP

AN3

CSI_CLKAN

AP2

C35

0.1U_0201_10V6K

C35

0.1U_0201_10V6K

1

2

C34

4.7U_0402_6.3V6M

C34

4.7U_0402_6.3V6M

1

2

R42

1M_0201_1%

R42

1M_0201_1%

12

C29

0.1U_0201_10V6K

C29

0.1U_0201_10V6K

1

2

C187

39P_0201_50V8J

C187

39P_0201_50V8J

1

2

R41

2.2K_0201_1%

R41

2.2K_0201_1%

12

18/21 CAM

(1.8/2.8 ~ 3.3V)

U1G

T30S-R-A3-1.4G_FCCSP681

18/21 CAM

(1.8/2.8 ~ 3.3V)

U1G

T30S-R-A3-1.4G_FCCSP681

VDDIO_CAM

AL11

GPIO_PCC2

AR15

GPIO_PCC1

AU15

GPIO_PBB7

AT14

GPIO_PBB6

AM16

GPIO_PBB5

AJ15

GPIO_PBB4

AL15

GPIO_PBB3

AM14

GPIO_PBB0

AM10

CAM_MCLK

AG15

CAM_I2C_SDA

AN15

CAM_I2C_SCL

AK14

(1.8V)

(3.3V)

11/21 USB

U1L

T30S-R-A3-1.4G_FCCSP681

(1.8V)

(3.3V)

11/21 USB

U1L

T30S-R-A3-1.4G_FCCSP681

AVDD_USB_PLL

V2

AVDD_USB

AB6

USB_REXT

AE9

USB3_ID

AK12

USB3_DP

AE5

USB3_DN

AF4

USB3_VBUS

AR5

USB2_ID

AJ7

USB2_DP

AG1

USB2_DN

AG3

USB2_VBUS

AH6

USB1_ID

AU5

USB1_DP

AM4

USB1_DN

AL5

USB1_VBUS

AF8

C372

10P_0201_50V8J

C372

10P_0201_50V8J

1

2

C186

39P_0201_50V8J

C186

39P_0201_50V8J

1

2

R44

453_0402_1%

R44

453_0402_1%

12

G

D

S

Q18

AO3413_SOT23-3

G

D

S

Q18

AO3413_SOT23-3

2

1 3

C28

0.1U_0201_10V6K

C28

0.1U_0201_10V6K

1

2

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

T30S_XTAL_IN

T30S_XTAL_OUT

CORE_PWR_REQ

CPU_PWR_REQ

T30S_XTAL_IN

T30S_XTAL_OUT

NV_THERM_DN

NV_THERM_DP

TEST_MODE_EN

SYS_CLK_REQ

PLL_S_PLL_LF

AVDD_OSC

PWR_I2C_SCL

PWR_I2C_SDA

+3VS_TH

THERMD_F_N

THERMD_F_P

NV_THERM_DN

NV_THERM_DP

ON_KEY#

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST#

JTAG_RTCK

JTAG_TDI

JTAG_TMS

JTAG_RTCK

JTAG_TCK

JTAG_TRST#

ON_KEY#

BT_RST# GPS_RESET#

EN_SENSOR_1V8#

JTAG_TRST#

JTAG_TDI

JTAG_TMS

JTAG_TCK

JTAG_RTCK

JTAG_TDO

ONKEY#

DEBUG_UART1_RX_R

PCB_ID3

LINE_OUT_DET#

+VDD_1V8_UART_TEGRA

+VDD_1V8_SYS_TEGRA

+VDD_1V8_SYS_TEGRA

+AVDD_1V1_PLL_TEGRA

+VDD_1V8_BB_TEGRA

+VDD_1V8_SYS_TEGRA

VDD_1V8_PMU_VRTC

+VDD_1V8_SYS_TEGRA

+VDD_1V8_BB_TEGRA

VDD_1V8_GEN

+3VS

+3VS

+VDD_1V8_SENSOR

+VDD_1V8_BB_TEGRA

+VDD_1V8_SYS_TEGRA

+VDD_1V8_SYS_TEGRA

+VDD_1V8_SYS_TEGRA

GEN1_I2C_SDA <16,20>

BT_RST# <22>

GPS_PWRON <21>

GPS_RESET# <18,21>

PWR_I2C_SCL <10,14,15,26,32,34>

PWR_I2C_SDA <10,14,15,26,32,34>

PMU_RESET_OUT_1V8# <32>

PMU_INT# <32>

CORE_PWR_REQ <27,32>

CPU_PWR_REQ < 32>

PMU_CLK_32K <32>

CLK_32K_OUT <22>

HDMI_CEC <19>

AP_OVERHEAT# < 32>

PWR_I2C_SCL<10,14,15,26,32,34>

PWR_I2C_SDA<10,14,15,26,32,34>

AUDIO_UART4_TX <14>

AUDIO_UART4_RX <14>

BT_PCM_IN <22>

BT_PCM_OUT <22>

BT_PCM_SYNC <22>

BT_PCM_CLK <22>

DEBUG_UART1_TX <20>

DEBUG_UART1_RX <20>

BT_UART_CTS# <22>

BT_UART_RTS# <22>

BT_UART_RXD <22>

BT_UART_TXD <22>

GPS_UART_CTS# <21>

GPS_UART_RTS# < 21>

GPS_UART_RXD < 21>

GPS_UART_TXD <21>

TEMP_ALERT# <4>

WF_RST# <22>

GEN1_I2C_SCL <16,20>

BT_IRQ# <22>

BT_WAKEUP <22>

CLK_12M_ES305 <14>

WAKE_UP_ACIN <27>

WF_WAKE# <22>

WAKE_UP_VBUS <27>

SC_LOCK# <20>

VOL_UP# <4,20>

VOL_DOWN# <4,20>

WAKEUP_LED <27>

SHORT_DET <15>

G_ACC_INT <16>

UART_SW <20>

EN_SENSOR_1V8# <23>

SIM_DET <18>

SD_DET# <20>

LINE_OUT_DET# <20>

CAM_LED_EN_NV <35>

BOARD_ID_WP <10>

ONKEY# <20,32>

HOT_RST#<20>

EN_VDD_GPS <21>

PMU_OSC32KOUT <32>PMU_OSC32KIN<32>

DEBUG_UART1_RX <20>

EN_3V3_MODEM <18,30>

EN_CAM_2V8 <17>

EN_CAM_1V8# <23>

BT_PD# <22>

EN_SENSOR_3V3_2 <23>

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

7

Compal Electronics, Inc.

T30S(4/5) UART/OSC/PLL

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

7

Compal Electronics, Inc.

T30S(4/5) UART/OSC/PLL

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

7

Compal Electronics, Inc.

T30S(4/5) UART/OSC/PLL

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

max current is 350uA

VR1 =17mV

Thermal

we not use Audio LDO

Z

Z

PD

Z

PD

Z

PD

Z

PD

Z

Z

0

Z

Z

PU

PU

PU

PU

PU

PU

PU

PU

Z

PU

PU

PU

PU

PU

PU

PU

PU

Z

Z

Z

Z

Z

PD

PD

PD

PD

Z

Z

Z

Z

PD

Z

Z

PD

PD

PD

Z

PU

PU

PU

PU

PU

PU

PU

PU

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

0

PD

Z

PD

Open Drain

For PMU RTCCLK , Load BOM

屬

屬屬

屬屬

屬屬

屬

HW

料

料料

料

.

08/12 Delete EN_ACER_USB_CHARGE

8/25 Modify C36&C37 from 12P to 8P.

Deep Sleep : ON

D

eep Sleep : OFF

9/22

C

hange EN_3V3_MODEM from AE35 to AF36.

9/22 Change EN_3V3_MODEM to AF36

9/22 Swap AD36 & W29 GPIO function.

Default pull up& pull down swap

9/26

Change BT_PD# from Y36 to AJ33

9/26 Change BT_PD# to AJ33

9/26

H LPCB_ID3

Change from J37 to R37.

09/15 Add for Acer request.

9/27

ADD EN_SENSOR_3V3_2 to U1.AA3

9/28 Change Net name from Board_ID3 to PCB_ID3

PICASSO_M PICASSO_2

10/11 Modify C36&C37 from 8P to 10P.

10/19 Modify R51 and R52 to 1K ohm

T6PAD@ T6PAD@

C40

0.1U_0201_10V6K

@

C40

0.1U_0201_10V6K

@

1

2

(1.8/3.3V)

12/21 BB

U1S

T30S-R-A3-1.4G_FCCSP681

(1.8/3.3V)

12/21 BB

U1S

T30S-R-A3-1.4G_FCCSP681

VDDIO_BB

V6

GPIO_PV1

AA5

GPIO_PV0

Y8

DAP3_SCLK

AA3

DAP3_FS

Y4

DAP3_DOUT

W5

DAP3_DIN

AA1

ULPI_STP

V10

ULPI_NXT

AC9

ULPI_DIR

W3

ULPI_CLK

AC1

ULPI_DATA7

AA9

ULPI_DATA6

AF6

ULPI_DATA5

AC11

ULPI_DATA4

V4

ULPI_DATA3

AC3

ULPI_DATA2

V8

ULPI_DATA1

AC7

ULPI_DATA0

AA7

C41

0.1U_0201_10V6K

C41

0.1U_0201_10V6K

1

2

R195

10K_0201_5%

PICASSO_M@

R195

10K_0201_5%

PICASSO_M@

1 2

(1.8/3.3V)

14/21 UART

U1R

T30S-R-A3-1.4G_FCCSP681

(1.8/3.3V)

14/21 UART

U1R

T30S-R-A3-1.4G_FCCSP681

VDDIO_UART

AC37

CLK3_REQ

AF32

CLK3_OUT

AH32

DAP4_SCLK

AL35

DAP4_FS

AF28

DAP4_DOUT

AG35

DAP4_DIN

AF34

GPIO_PU6

AJ33

GPIO_PU5

AG37

GPIO_PU4

AM36

GPIO_PU3

AG33

GPIO_PU2

AN37

GPIO_PU1

AF36

GPIO_PU0

AK34

UART3_CTS*

AJ37

UART3_RTS*

AK36

UART3_RXD

AJ35

UART3_TXD

AE33

UART2_CTS*

AJ31

UART2_RTS*

AG31

UART2_RXD

AG29

UART2_TXD

AN35

GEN1_I2C_SDA

AE29

GEN1_I2C_SCL

AH30

C43

0.1U_0201_10V6K

C43

0.1U_0201_10V6K

1

2

R57

49.9_0402_1%

R57

49.9_0402_1%

1 2

R47

2.2K_0201_1%

R47

2.2K_0201_1%

12

R56

100K_0201_5%

R56

100K_0201_5%

12

R163

10K_0201_5%

PICASSO_2@

R163

10K_0201_5%

PICASSO_2@

1 2

C36

10P_0201_50V8J

C36

10P_0201_50V8J

1 2

(3.3V)

(3.3V)

(1.05V)

(1.05V)

19/21 PEX

(1.05V)

U1T

T30S-R-A3-1.4G_FCCSP681

(3.3V)

(3.3V)

(1.05V)

(1.05V)

19/21 PEX

(1.05V)

U1T

T30S-R-A3-1.4G_FCCSP681

VDDIO_PEX_CTL

AK28

HVDD_PEX

AL29

AVDD_PEX_PLL

AN31

VDD_PEXB

AM30

AVDD_PEXB

AN29

PEX_TERMP

AP36

PEX_WAKE*

AP32

PEX_L2_RST*

AU33

PEX_L2_PRSNT*

AT32

PEX_L2_CLKREQ*

AR31

PEX_CLK3P

AR33

PEX_CLK3N

AT34

PEX_L5_RXP

AR29

PEX_L5_RXN

AP30

PEX_L5_TXP

AU29

PEX_L5_TXN

AT30

R62

0_0201_5%

R62

0_0201_5%

1 2

R164

100K_0201_5%

R164

100K_0201_5%

12

JDBUG1

ACES_87036-1001-CP

CONN@

JDBUG1

ACES_87036-1001-CP

CONN@

9

9

10

10

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

GND

11

GND

12

R91

100K_0201_5%

R91

100K_0201_5%

12

T2PAD@ T2PAD@

D20

RB751V-40_SOD323-2

D20

RB751V-40_SOD323-2

12

R160

10K_0201_5%

R160

10K_0201_5%

1 2

C46

1000P_0201_16V7K

C46

1000P_0201_16V7K

12

T4PAD@ T4PAD@

C44

0.1U_0201_10V6K

C44

0.1U_0201_10V6K

1

2

G

G

Y10

26MHZ_10PF_7M26000039

G

G

Y10

26MHZ_10PF_7M26000039

14

3 2

R77

100K_0201_5%

R77

100K_0201_5%

12

R48

100K_0201_5%

R48

100K_0201_5%

12

R59 100_0201_1%R59 100_0201_1%

12

R162 100K_0201_5%@R162 100K_0201_5%@

12

(1.1V)

(1.8V)

(1.1V)

2/21 OSC, PLL & SYS

(1.1V)

(1.1V)

(1.05V)

(1.8V)

U1C

T30S-R-A3-1.4G_FCCSP681

(1.1V)

(1.8V)

(1.1V)

2/21 OSC, PLL & SYS

(1.1V)

(1.1V)

(1.05V)

(1.8V)

U1C

T30S-R-A3-1.4G_FCCSP681

VDDIO_SYS

Y32

AVDD_PLLE

AF30

AVDD_PLLU_D

AG5

AVDD_PLLM

A21

AVDD_PLLX

K18

AVDD_PLLA_P_C_S

B24

AVDD_OSC

P36

TEST_MODE_EN

V28

HDMI_CEC

V32

OWR

R29

THERM_DP

C31

THERM_DN

E31

JTAG_RTCK

AD34

JTAG_TRST*

W33

JTAG_TMS

AA33

JTAG_TDO

Y28

JTAG_TDI

AC35

JTAG_TCK

AA31

KB_ROW15

AB30

KB_ROW14

P32

KB_ROW13

AC29

KB_ROW12

P30

KB_ROW11

Y36

KB_ROW10

AA29

KB_ROW09

AA37

KB_ROW08

AA35

KB_ROW07

AE35

KB_ROW06

U33

KB_ROW05

V34

KB_ROW04

U35

KB_ROW03

R31

KB_ROW02

W29

KB_ROW01

R37

KB_ROW00

AC33

KB_COL07

W35

KB_COL06

AD30

KB_COL05

Y30

KB_COL04

AC31

KB_COL03

AD36

KB_COL02

AD32

KB_COL01

U29

KB_COL00

U37

CLK_32K_OUT

AB32

CLK_32K_IN

T30

SYS_CLK_REQ

W27

CPU_PWR_REQ

Y34

CORE_PWR_REQ

T32

PWR_INT*

P28

SYS_RESET*

U31

PWR_I2C_SDA

V30

PWR_I2C_SCL

V36

PLL_S_PLL_LF

R27

XTAL_OUT

R35

XTAL_IN

R33

R75

100K_0201_5%

R75

100K_0201_5%

12

C45

0.1U_0201_10V6K

C45

0.1U_0201_10V6K

1

2

R52

1K_0201_1%

R52

1K_0201_1%

12

20/21 SPARE

U1U

T30S-R-A3-1.4G_FCCSP681

20/21 SPARE

U1U

T30S-R-A3-1.4G_FCCSP681

SPARE_4

AL33

SPARE_3

AG19

SPARE_2

AD28

SPARE_1

AC27

SPARE_5

AM34

U4

NCT1008CMT3R2G_WDFN8_2X2

U4

NCT1008CMT3R2G_WDFN8_2X2

THERM#

4

ALERT#

6

SDA

7

SCL

8

GND

5

VDD

1

D+

2

D-

3

T14PAD@ T14PAD@

T7PAD@ T7PAD@

R53

0_0201_5%

R53

0_0201_5%

1 2

R58

100K_0201_5%

R58

100K_0201_5%

12

R155

10K_0201_5%

R155

10K_0201_5%

1 2

R61 100_0201_1%R61 100_0201_1%

12

C38

0.1U_0201_10V6K

C38

0.1U_0201_10V6K

1

2

C39

4.7U_0402_6.3V6M

C39

4.7U_0402_6.3V6M

1

2

T10PAD@ T10PAD@

C37

10P_0201_50V8J

C37

10P_0201_50V8J

1 2

T8PAD@ T8PAD@

T5PAD@ T5PAD@

R149

0_0201_5%

R149

0_0201_5%

1 2

R161 100K_0201_5%R161 100K_0201_5%

12

R46

2.2K_0201_1%

R46

2.2K_0201_1%

12

L3

MPZ1005S300CT_2P

L3

MPZ1005S300CT_2P

1 2

Y1

32.768KHZ_12.5P_1TJF125DP1A000D

Y1

32.768KHZ_12.5P_1TJF125DP1A000D

1 2

C42

0.1U_0201_10V6K

C42

0.1U_0201_10V6K

1

2

R49

100K_0201_5%

R49

100K_0201_5%

12

T9PAD@ T9PAD@

R51

1K_0201_1%

R51

1K_0201_1%

12

R60

100K_0201_5%

R60

100K_0201_5%

12

R50

2M_0201_5%

R50

2M_0201_5%

12

R159

10K_0201_5%

R159

10K_0201_5%

1 2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

VPP_KFUSE

+VDD_1V2_RTC_TEGRA

+VDD_3V3_FUSE_TEGRA

VDD_1V2_SOC

VDD_1V0_GEN

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

8

Compal Electronics, Inc.

T30S(5/5)PWR_GND_NC

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

8

Compal Electronics, Inc.

T30S(5/5)PWR_GND_NC

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

8

Compal Electronics, Inc.

T30S(5/5)PWR_GND_NC

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Tuesday, January 17, 2012

Acer request 07/04

Acer request 07/04

12/12 Modify R65 from @ to mount.

C101

0.1U_0201_10V6K

C101

0.1U_0201_10V6K

1

2

C63

4.7U_0402_6.3V6M

C63

4.7U_0402_6.3V6M

1

2

21/21 GND

U1B

T30S-R-A3-1.4G_FCCSP681

21/21 GND

U1B

T30S-R-A3-1.4G_FCCSP681

GND_191

W7

GND_190

W37

GND_189

W31

GND_188

W23

GND_187

W21

GND_186

W19

GND_185

W17

GND_184

W15

GND_183

W13

GND_182

W1

GND_181

U27

GND_180

U25

GND_179

U23

GND_178

U21

GND_177

U19

GND_176

U17

GND_175

U15

GND_174

U13

GND_173

U11

GND_172

T4

GND_171

T36

GND_170

T34

GND_169

T28

GND_168

T2

GND_167

T10

GND_166

R23

GND_165

R21

GND_164

R19

GND_163

R17

GND_162

R15

GND_161

R13

GND_160

P24

GND_159

N7

GND_158

N37

GND_157

N31

GND_156

N27

GND_155

N25

GND_154

N13

GND_153

N11

GND_152

N1

GND_151

M26

GND_150

M12

GND_149

L27

GND_148

L25

GND_147

L21

GND_146

L17

GND_145

L13

GND_144

L11

GND_143

K4

GND_142

K36

GND_141

K34

GND_140

K28

GND_139

K22

GND_138

K2

GND_137

K16

GND_136

K10

GND_135

J9

GND_134

J29

GND_133

J27

GND_132

J11

GND_131

H8

GND_130

H6

GND_129

H32

GND_128

H30

GND_127

G7

GND_126

G37

GND_125

G31

GND_124

G25

GND_123

G19

GND_122

G13

GND_121

G1

GND_120

F6

GND_119

F32

GND_118

E5

GND_117

E33

GND_116

D4

GND_115

D34

GND_114

D28

GND_113

D22

GND_112

D16

GND_111

D10

GND_110

C37

GND_109

C35

GND_108

C3

GND_107

C1

GND_106

B36

GND_105

B28

GND_104

B22

GND_103

B2

GND_102

B16

GND_101

B10

GND_100

AU7

GND_99

AU35

GND_98

AU31

GND_97

AU3

GND_96

AU25

GND_95

AU19

GND_94

AU13

GND_93

AT36

GND_92

AT28

GND_91

AT22

GND_90

AT2

GND_89

AT16

GND_88

AT10

GND_87

AR37

GND_86

AR35

GND_85

AR3

GND_84

AR1

GND_83

AP4

GND_82

AP34

GND_81

AP28

GND_80

AP22

GND_79

AP16

GND_78

AP10

GND_77

AN5

GND_76

AN33

GND_75

AM6

GND_74

AM32

GND_73

AL7

GND_72

AL37

GND_71

AL31

GND_70

AL25

GND_69

AL19

GND_68

AL13

GND_67

AL1

GND_66

AK8

GND_65

AK6

GND_64

AK32

GND_63

AK30

GND_62

AJ9

GND_61

AJ29

GND_60

AJ27

GND_59

AJ11

GND_58

AH4

GND_57

AH36

GND_56

AH34

GND_55

AH28

GND_54

AH22

GND_53

AH2

GND_52

AH16

GND_51

AH10

GND_50

AG27

GND_49

AG25

GND_48

AG21

GND_47

AG17

GND_46

AG13

GND_45

AG11

GND_44

AF26

GND_43

AF12

GND_42

AE7

GND_41

AE37

GND_40

AE31

GND_39

AE27

GND_38

AE25

GND_37

AE23

GND_36

AE21

GND_35

AE19

GND_34

AE17

GND_33

AE15

GND_32

AE13

GND_31

AE11

GND_30

AE1

GND_29

AC25

GND_28

AC23

GND_27

AC21

GND_26

AC19

GND_25

AC17

GND_24

AC15

GND_23

AC13

GND_22

AB4

GND_21

AB36

GND_20

AB34

GND_19

AB28

GND_18

AB2

GND_17

AB10

GND_16

AA27

GND_15

AA25

GND_14

AA23

GND_13

AA21

GND_12

AA19

GND_11

AA17

GND_10

AA15

GND_9

AA13

GND_8

AA11

GND_7

A7

GND_6

A35

GND_5

A31

GND_4

A3

GND_3

A25

GND_2

A19

GND_1

A13

R64

10K_0201_5%

R64

10K_0201_5%

1 2

C58

4.7U_0402_6.3V6M

C58

4.7U_0402_6.3V6M

1

2

C88

0.1U_0201_10V6K

C88

0.1U_0201_10V6K

1

2

C62

4.7U_0402_6.3V6M

C62

4.7U_0402_6.3V6M

1

2

C104

0.1U_0201_10V6K

C104

0.1U_0201_10V6K

1

2

C48

4.7U_0402_6.3V6M

C48

4.7U_0402_6.3V6M

1

2

(1.0 ~ 1.2V)

1/21 CORE POWER

(0.9 ~ 1.0V)

(1.0 ~ 1.2V)

(3.3V)

(3.3V)

U1A

T30S-R-A3-1.4G_FCCSP681

(1.0 ~ 1.2V)

1/21 CORE POWER

(0.9 ~ 1.0V)

(1.0 ~ 1.2V)

(3.3V)

(3.3V)

U1A

T30S-R-A3-1.4G_FCCSP681

VPP_KFUSE

AU9

VPP_FUSE

AU17

VDD_CORE_34

Y26

VDD_CORE_33

Y24

VDD_CORE_32

Y22

VDD_CORE_31

Y16

VDD_CORE_30

Y14

VDD_CORE_29

Y12

VDD_CORE_28

W25

VDD_CORE_27

V26

VDD_CORE_26

V24

VDD_CORE_25

V22

VDD_CORE_24

V16

VDD_CORE_23

V14

VDD_CORE_22

V12

VDD_CORE_21

T24

VDD_CORE_20

T22

VDD_CORE_19

T18

VDD_CORE_18

T16

VDD_CORE_17

T14

VDD_CORE_16

P22

VDD_CORE_15

P20

VDD_CORE_14

P18

VDD_CORE_13

P16

VDD_CORE_12

P14

VDD_CORE_11

AF24

VDD_CORE_10

AF22

VDD_CORE_09

AF20

VDD_CORE_08

AF18

VDD_CORE_07

AD26

VDD_CORE_06

AD24

VDD_CORE_05

AD22

VDD_CORE_04

AD20

VDD_CORE_03

AB26

VDD_CORE_02

AB24

VDD_CORE_01

AB22

VDD_CPU_16

Y20

VDD_CPU_15

Y18

VDD_CPU_14

V20

VDD_CPU_13

V18

VDD_CPU_12

T20

VDD_CPU_11

AF16

VDD_CPU_10

AF14

VDD_CPU_09

AD18

VDD_CPU_08

AD16

VDD_CPU_07

AD14

VDD_CPU_06

AD12

VDD_CPU_05

AB20

VDD_CPU_04

AB18

VDD_CPU_03

AB16

VDD_CPU_02

AB14

VDD_CPU_01

AB12

VDD_RTC_2

AJ25

VDD_RTC_1

AH26

R65

10K_0201_5%

R65

10K_0201_5%

12

C105

0.1U_0201_10V6K

C105

0.1U_0201_10V6K

1

2

C47

0.1U_0201_10V6K

C47

0.1U_0201_10V6K

1

2

C51

4.7U_0402_6.3V6M

C51

4.7U_0402_6.3V6M

1

2

C64

0.1U_0201_10V6K

C64

0.1U_0201_10V6K

1

2

C106

0.1U_0201_10V6K

C106

0.1U_0201_10V6K

1

2

C59

4.7U_0402_6.3V6M

C59

4.7U_0402_6.3V6M

1

2

C54

0.1U_0201_10V6K

C54

0.1U_0201_10V6K

1

2

C103

0.1U_0201_10V6K

C103

0.1U_0201_10V6K

1

2

C56

4.7U_0402_6.3V6M

C56

4.7U_0402_6.3V6M

1

2

C107

0.1U_0201_10V6K

C107

0.1U_0201_10V6K

1

2

C61

4.7U_0402_6.3V6M

C61

4.7U_0402_6.3V6M

1

2

C53

0.1U_0201_10V6K

C53

0.1U_0201_10V6K

1

2

C60

4.7U_0402_6.3V6M

C60

4.7U_0402_6.3V6M

1

2

C65

0.1U_0201_10V6K

C65

0.1U_0201_10V6K

1

2

C55

4.7U_0402_6.3V6M

C55

4.7U_0402_6.3V6M

1

2

C102

0.1U_0201_10V6K

C102

0.1U_0201_10V6K

1

2

C52

4.7U_0402_6.3V6M

C52

4.7U_0402_6.3V6M

1

2

C50

4.7U_0402_6.3V6M

C50

4.7U_0402_6.3V6M

1

2

C57

4.7U_0402_6.3V6M

C57

4.7U_0402_6.3V6M

1

2

C49

4.7U_0402_6.3V6M

C49

4.7U_0402_6.3V6M

1

2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

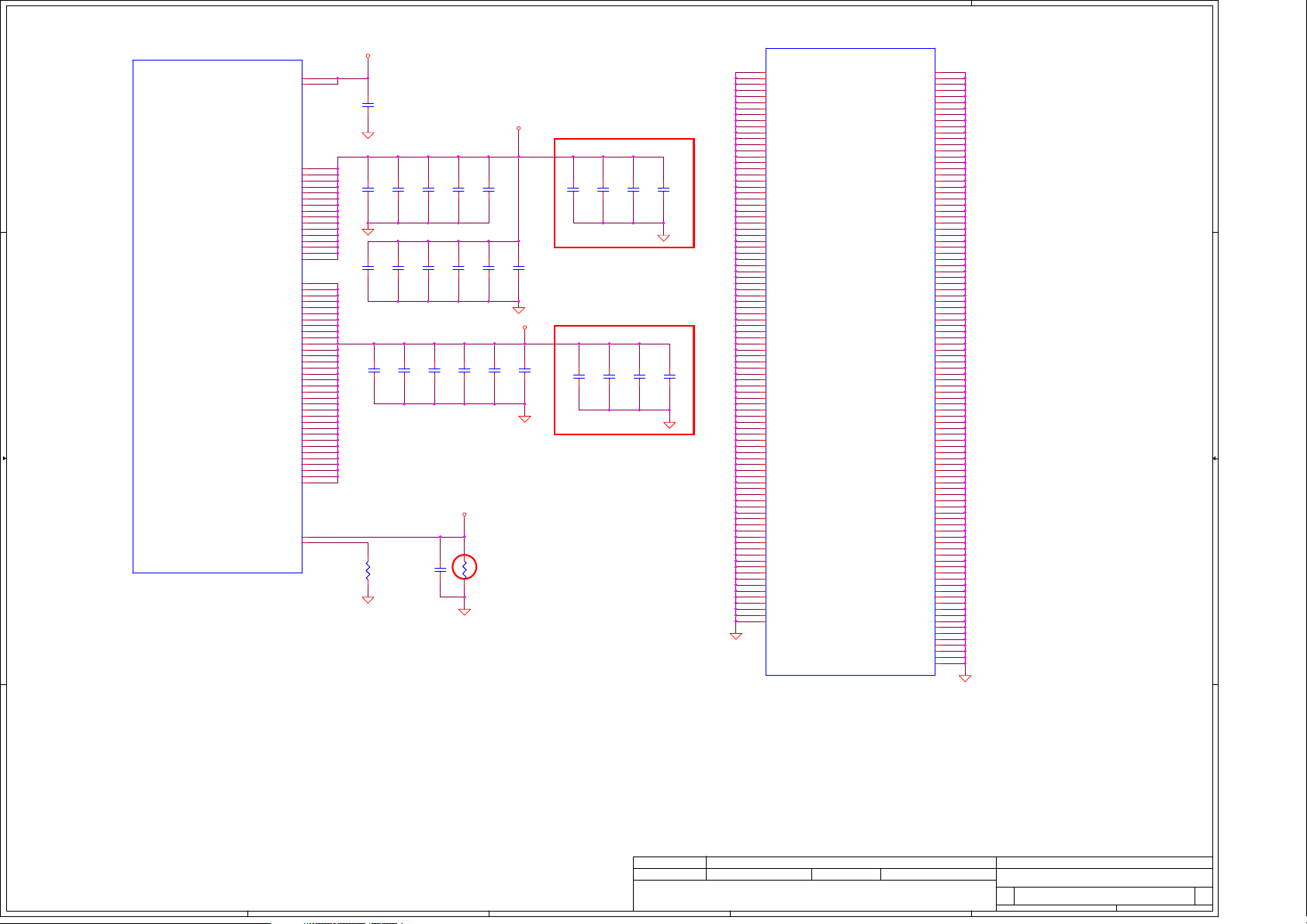

+VDD_1V8_DDR_MEM

+VDD_1V8_DDR_MEM

+VDD_1V8_DDR_MEM

+VDD_1V8_DDR_MEM

+VDD_1V2_DDR_MEM

+VRAM_VREFA

+VDD_1V2_DDR_MEM

+VDD_1V2_DDR_MEM

+VRAM_VREDQ

+VDD_1V2_DDR_MEM

+VDD_1V8_DDR_MEM +VDD_1V8_DDR_MEM

+VDD_1V2_DDR_MEM

DDR_A_D10<5>

DDR_A_D31<5>

DDR_A_D27<5>

DDR_A_D16 < 5>

DDR_A_D23 < 5>

DDR_A_D7 <5>

DDR_A_D13<5>

DDR_A_D11<5>

DDR_A_MA9<5>

DDR_A_MA8<5>

DDR_A_MA7<5>

DDR_A_MA6<5>

DDR_A_MA5<5>

DDR_A_MA4 <5>

DDR_A_MA3 <5>

DDR_A_MA2 <5>

DDR_A_MA1 <5>

DDR_A_MA0 <5>

M_CS#0 <5>

M_CS#1 <5>

M_CLK_DDR0<5>

M_CLK_DDR#0<5>

M_CKE0 <5>

M_CKE1 <5>

DDR_A_DQS3<5>

DDR_A_DQS#3<5>

DDR_A_DQS2 <5>

DDR_A_DQS#2 <5>

DDR_A_DQS1<5>

DDR_A_DQS#1<5>

DDR_A_DQS0 <5>

DDR_A_DQS#0 <5>

DDR_A_DM3<5>

DDR_A_DM2 <5>

DDR_A_DM1<5>

DDR_A_DM0 <5>

DDR_A_D15<5>

DDR_A_D14<5>

DDR_A_D9<5>

DDR_A_D6 <5>

DDR_A_D5 <5>

DDR_A_D22 < 5>

DDR_A_D21 < 5>

DDR_A_D19 < 5>

DDR_A_D28<5>

DDR_A_D17 < 5>

DDR_A_D24<5>

DDR_A_D8<5>

DDR_A_D0 <5>

DDR_A_D12<5>

DDR_A_D29<5>

DDR_A_D18 < 5>

DDR_A_D25<5>

DDR_A_D2 <5>

DDR_A_D1 <5>

DDR_A_D4 <5>

DDR_A_D30<5>

DDR_A_D26<5>

DDR_A_D20 < 5>

DDR_A_D3 <5>

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

9

Compal Electronics, Inc.

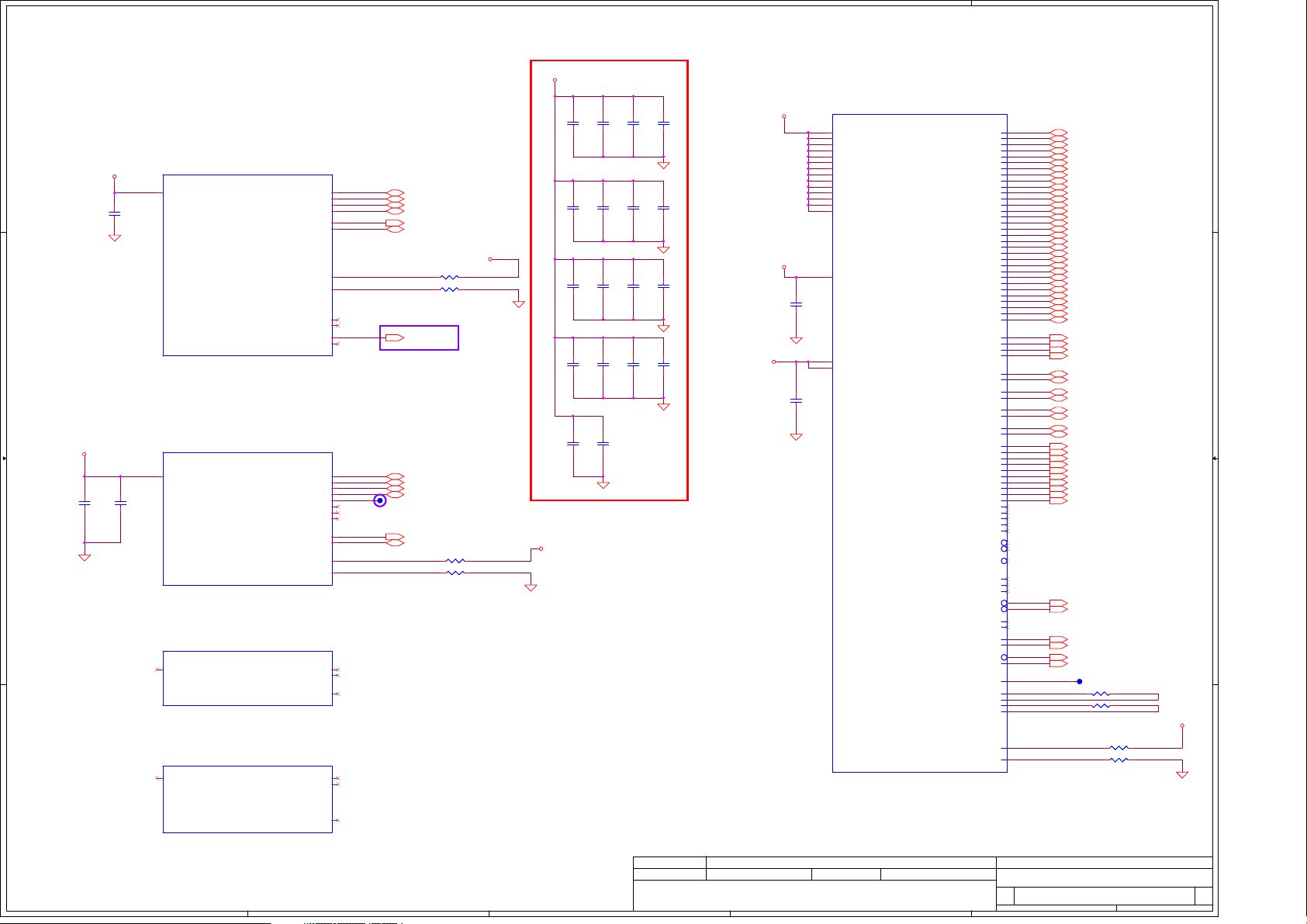

LPDDRII-DEVICE DOWN

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Wednesday, January 18, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

9

Compal Electronics, Inc.

LPDDRII-DEVICE DOWN

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Wednesday, January 18, 2012

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

9

Compal Electronics, Inc.

LPDDRII-DEVICE DOWN

1.0

Picasso 2 R04

38

2012/06/202011/06/20

C

Wednesday, January 18, 2012

( 1GB Samsung )

( 1GB Elpida )

Acer request

Follow NV design

N

ET NAME BALL NAME

A0 P3

A1 N3

A2 M3

A3 M2

A4 M1

A5 G2

A6 F2

A7 F3

A8 E3

A9 E2

CKE0 K1

CKE1 K2

CLK J3

CLK# H3

CS0 L1

CS1 L2

DM0 K5

DM1 H5

DQ0 M9

DQ1 N8

DQ10 F7

DQ11 F9

DQ12 F6

DQ13 G9

DQ14 F8

DQ15 E8

DQ2 M8

DQ3 M7

DQ4 L9

DQ5 L7

DQ6 L8

DQ7 M6