h

MAINTENANCE MANUAL

KY 96A, KY 97A

VHF COMMUNICATION

MANUAL NUMBER 006-05674-0005

TRANSCEIVER

Revision 5, April 2003

WARNING

THE ENCLOSED TECHNICAL DATA IS ELIGIBLE FOR EXPORT UNDER LICENSE

DESIGNATION NLR AND IS TO BE USED SOLELY BY THE INDIVIDUAL/ ORGANIZATION TO WHOM IT IS ADDRESSED. DIVERSION CONTRARY TO U.S. LAW IS PROHIBITED.

COPYRIGHT NOTICE

©1989, 1992, 1994, 1997, 2003 HONEYWELL INTERNATIONAL INC.

REPRODUCTION OF THIS PUBLICATION OR ANY PORTION THEREOF BY ANY

MEANS WITHOUT THE EXPRESS WRITTEN PERMISSION OF HONEYWELL IS

PROHIBITED. FOR FURTHER INFORMATION CONTACT THE MANAGER, TECHNICAL

PUBLICATIONS, HONEYWELL, ONE TECHNOLOGY CENTER, 23500 WEST 105TH

STREET OLATHE KS 66061 TELEPHONE: (913) 782-0400.

B KY 96A, KY 97A

REVISION HISTORY

MAINTENANCE MANUAL

BENDIX/KING

KY 96A, KY 97A

VHF Communication Transceiver

PART NUMBER REV DATE DESCRIPTION

--------------------------------------------------------------------------------------------------------------------006-05674-0005 5 Apr/2003 Incorporated -0020 SW/HW versions.

006-05674-0004 4 Apr/1994 Incorporated IM Rev 3.

006-05674-0003 3 Jan/1994 Revised Section VI.

Incorporated IM Rev 2.

006-05674-0002 2 Oct/1992 Revised Section VI.

006-05674-0001 1 Oct/1989 Incorporated IM Rev 1.

Rev 5, Apr 2003 MM 006-05674-0005.dwd RH-1

B KY 96A, KY 97A

THIS PAGE RESERVED

Rev 5, Apr 2003 MM 006-05674-0005.dwd RH-2

B TABLE OF CONTENTS KY 96A, KY 97A

SECTION IV

THEORY OF OPERATION

Paragraph Page

4.1 General....................................................................................................4-1

4.2 General Circuit Theory.............................................................................4-1

4.3 Detailed Theory of Operation...................................................................4-3

LIST OF ILLUSTRATIONS

Figure Page

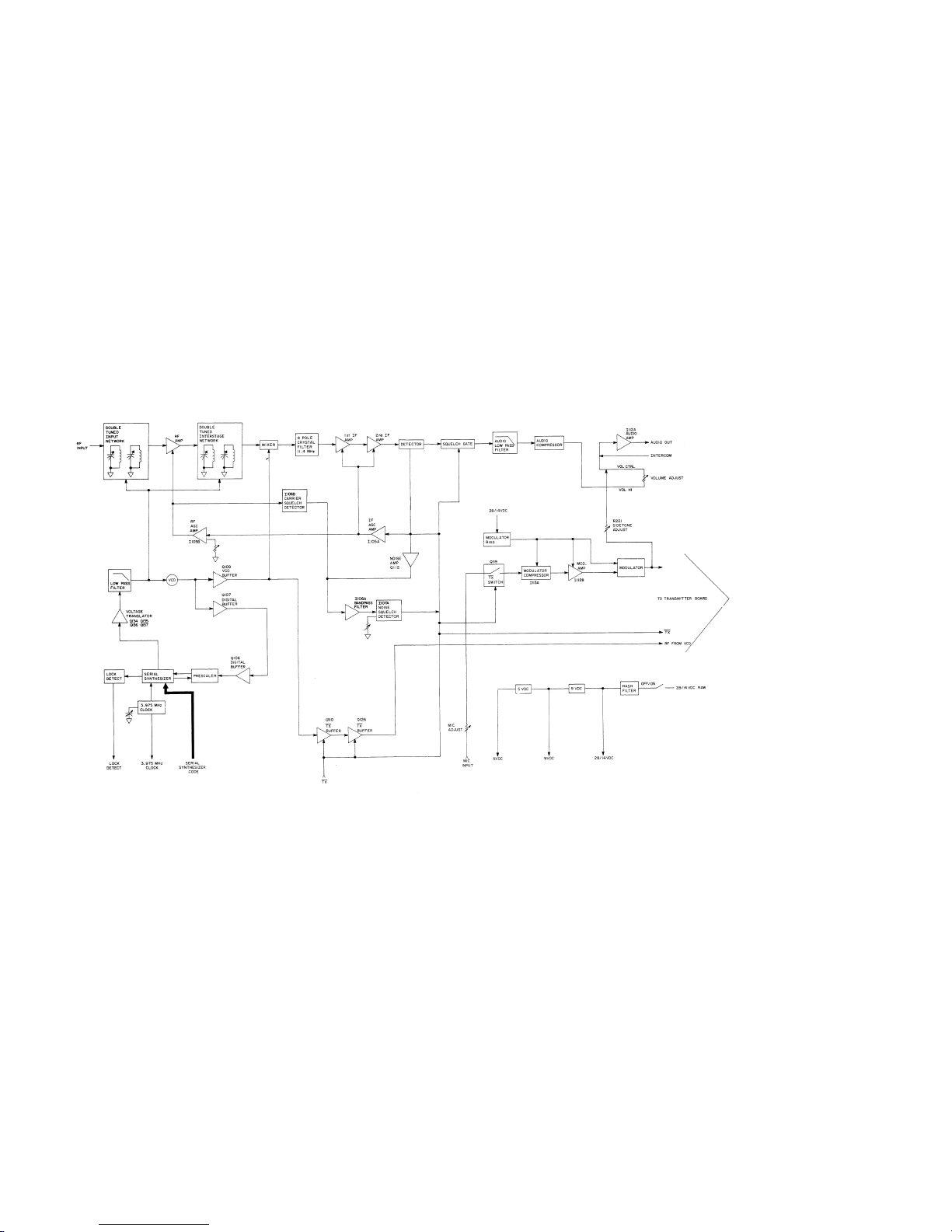

4-1 Receiver Block Diagram ........................................................................4-13

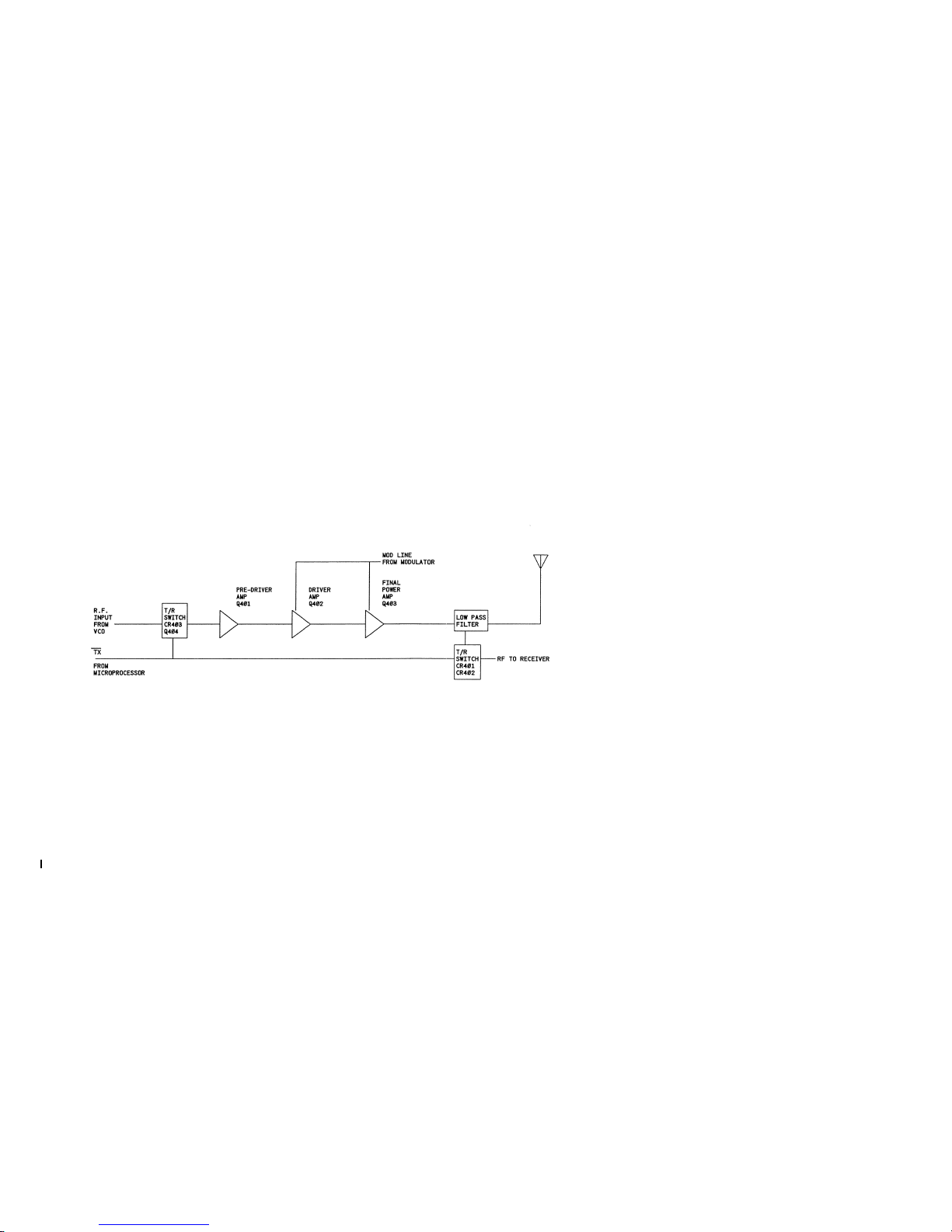

4-2 Transmitter Block Diagram ....................................................................4-15

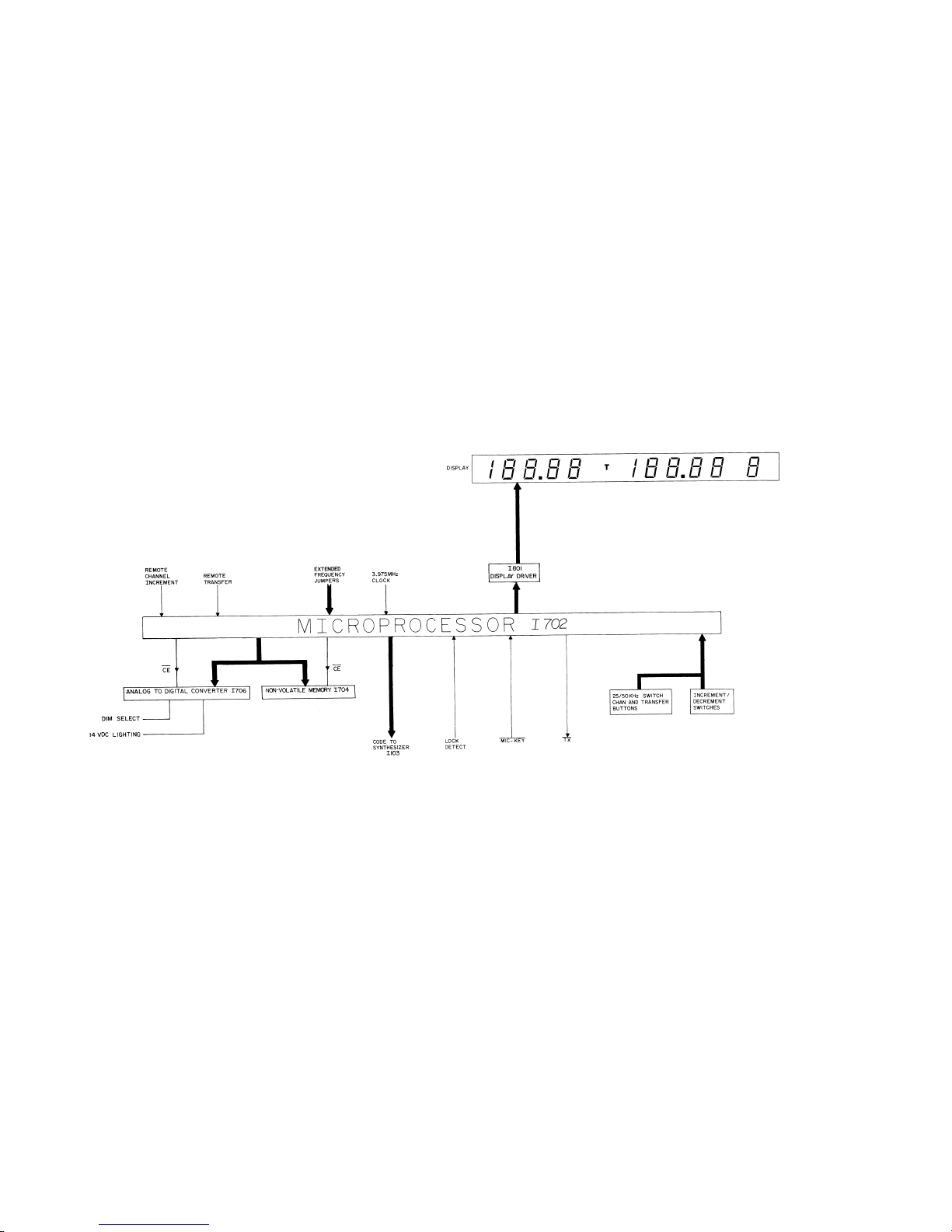

4-3 Microprocessor Block Diagram..............................................................4-17

SECTION V

MAINTENANCE

Paragraph Page

5.1 General Information.................................................................................5-1

5.2 Test Equipment........................................................................................5-1

5.3 Performance Test Procedure...................................................................5-4

5.4 Alignment Procedure ...............................................................................5-9

5.5 Overhaul ................................................................................................5-11

LIST OF TABLES

Table Page

5-1 Required Test Equipment........................................................................5-1

5-2 Optional Test Equipment .........................................................................5-2

LIST OF ILLUSTRATIONS

Figure Page

5-1 Typical Test Equipment Setup................ ................................................5-3

5-2 Linear Detector....................................... ..............................................5-13

5-3 MIC Test Circuit...................................... ..............................................5-13

5-4 40 dB Antennuator.................................. ..............................................5-14

5-5

Bench Test Harness.................................. ..............................................5-15

Rev 5, Apr 2003 MM 006-05674-0005.dwd TOC-1

B TABLE OF CONTENTS KY 96A, KY 97A

SECTION VI

ILLUSTRATED PARTS LIST

Paragraph Page

6.1 Introduction..............................................................................................6-1

6.2 Bill of Material Description .......................................................................6-1

6.3 Software Documentation .........................................................................6-9

6.4 Illustrated Parts List ...............................................................................6-17

6.4.1 KY 96A VHF Communication Transceiver.............................................6-17

6.4.2 KY 97A VHF Communication Transceiver.............................................6-41

6.4.3 KY 96A, KY 97A Unit Software Set .......................................................6-53

6.4.4 LCD Processor Board............................................................................6-57

6.4.5 KY 97A (14V) Modulator Assembly .......................................................6-71

6.4.6 KY 96A (28V) Modulator Assembly .......................................................6-79

6.4.7 LCD Display Board ................................................................................6-87

6.4.8 Transmitter Board................................................................................6-105

6.4.9 Audio Amplifier Board..........................................................................6-135

6.4.10 Main Board ..........................................................................................6-149

LIST OF TABLES

Table Page

6-1 Reference Designator Abbreviations.......................................................6-1

6-2 Description Abbreviations........................................................................6-3

6-3 Unit of Measure Abbreviations.................................................................6-9

LIST OF ILLUSTRATIONS

Figure Page

6-0 Sample Parts List.................................... ..............................................6-13

6-1 KY 96A Final Assembly ..........................(Dwg 300-04268-0000).........6-25

6-1A KY 96A Final Assembly ..........................(Dwg 300-04268-0000).........6-29

6-1B KY 96A Final Assembly ..........................(Dwg 300-04268-0000).........6-33

6-1C KY 96A Final Assembly ..........................(Dwg 300-04268-0000).........6-37

6-2 KY 97A Final Assembly ..........................(Dwg 300-04268-0001).........6-49

6-3 LCD Processor Board Assembly ............(Dwg 300-07475-0000).........6-61

6-3A LCD Processor Board Assembly ............(Dwg 300-07475-0000).........6-63

6-4 LCD Processor Board Schematic...........(Dwg 002-07475-0000).........6-65

6-4A LCD Processor Board Schematic...........(Dwg 002-07475-0000).........6-67

6-4B LCD Processor Board Schematic...........(Dwg 002-07475-0000).........6-69

6-5 KY 97A (14V) Modulator Assembly ........(Dwg 300-04270-0000).........6-75

6-5A KY 97A (14V) Modulator Assembly ........(Dwg 300-04270-0000).........6-77

6-6 KY 96A (28V) Modulator Assembly ........(Dwg 300-04271-0000).........6-83

Rev 5, Apr 2003 MM 006-05674-0005.dwd TOC-2

B TABLE OF CONTENTS KY 96A, KY 97A

6-6A KY 96A (28V) Modulator Assembly ........(Dwg 300-04271-0000).........6-85

6-7 LCD Display Board Assembly.................(Dwg 300-07479-0000).........6-91

6-7A LCD Display Board Assembly.................(Dwg 300-07479-0000).........6-93

6-7B LCD Display Board Assembly.................(Dwg 300-07479-0000).........6-95

6-7C LCD Display Board Assembly.................(Dwg 300-07479-0000).........6-97

6-8 LCD Display Board Schematic ...............(Dwg 002-07479-0000).........6-99

6-8A LCD Display Board Schematic ...............(Dwg 002-07479-0000).......6-101

6-8B LCD Display Board Schematic ...............(Dwg 002-07479-0000).......6-103

6-9 KY 97A (14V) Transmitter Assembly......(Dwg 300-07540-0000).......6-109

6-9A KY 97A (14V) Transmitter Assembly......(Dwg 300-07540-0000).......6-111

6-9B KY 97A (14V) Transmitter Assembly......(Dwg 300-07540-0000).......6-113

6-10 KY 97A (14V) Transmitter Schematic.....(Dwg 002-07540-0000).......6-115

6-10A KY 97A (14V) Transmitter Schematic.....(Dwg 002-07540-0000).......6-117

6-10B KY 97A (14V) Transmitter Schematic.....(Dwg 002-07540-0000).......6-119

6-11 KY 96A (28V) Transmitter Assembly......(Dwg 300-07540-0001).......6-121

6-11A KY 96A (28V) Transmitter Assembly......(Dwg 300-07540-0001).......6-123

6-11B KY 96A (28V) Transmitter Assembly......(Dwg 300-07540-0001).......6-125

6-12 KY 96A (28V) Transmitter Schematic.....(Dwg 002-07540-0001).......6-127

6-12A KY 96A (28V) Transmitter Schematic.....(Dwg 002-07540-0001).......6-129

6-12B KY 96A (28V) Transmitter Schematic.....(Dwg 002-07540-0001).......6-131

6-12C KY 96A (28V) Transmitter Schematic.....(Dwg 002-07540-0001).......6-133

6-13 Audio Amplifier Board Assembly ............(Dwg 300-07797-0000).......6-139

6-13A Audio Amplifier Board Assembly ............(Dwg 300-07797-0000).......6-141

6-14 Audio Amplifier Board Schematic ...........(Dwg 002-07797-0000).......6-143

6-14A Audio Amplifier Board Schematic ...........(Dwg 002-07797-0000).......6-145

6-14B Audio Amplifier Board Schematic ...........(Dwg 002-07797-0000).......6-147

6-15 KY 97A (14V) Main Board Assembly......(Dwg 300-07799-0000).......6-199

6-15A KY 97A (14V) Main Board Assembly......(Dwg 300-07799-0000).......6-203

6-15B KY 97A (14V) Main Board Assembly......(Dwg 300-07799-0000).......6-207

6-15C KY 97A (14V) Main Board Assembly......(Dwg 300-07799-0000).......6-211

6-16 KY 96A (28V) Main Board Assembly......(Dwg 300-07799-0001).......6-215

6-16A KY 96A (28V) Main Board Assembly......(Dwg 300-07799-0001).......6-219

6-16B KY 96A (28V) Main Board Assembly......(Dwg 300-07799-0001).......6-223

6-16C KY 96A (28V) Main Board Assembly......(Dwg 300-07799-0001).......6-227

6-17 KY 96A, KY 97A Main Board Schem......(Dwg 002-07799-0000).......6-231

6-17A KY 96A, KY 97A Main Board Schem......(Dwg 002-07799-0000).......6-249

6-17B KY 96A, KY 97A Main Board Schem......(Dwg 002-07799-0000).......6-261

Rev 5, Apr 2003 MM 006-05674-0005.dwd TOC-3

B TABLE OF CONTENTS KY 96A, KY 97A

APPENDIX S

SOFTWARE/ HARDWARE CONFIGURATION

LIST OF ILLUSTRATIONS

Figure Page

S-1 KY 96A Software/ Hardware Configuration ............................................ S-3

S-2 KY 97A Software/ Hardware Configuration ............................................ S-9

Rev 5, Apr 2003 MM 006-05674-0005.dwd TOC-4

B KY 96A, KY 97A

SECTION IV

THEORY OF OPERATION

4.1 GENERAL

The KY 96A, KY 97A Comm Transceiver is comprised of:

A. A single conversion VHF receiver utilizing a four pole varactor tuned prese-

lector, field effect transistors for the RF amplifier and mixer, an 8 pole monolithic crystal IF filter and integrated circuit IF amplifier.

B. A broadband transmitter with power transistors mounted on a die-cast alu-

minum heat sink followed by a three section elliptic function low pass filter.

C. A control section utilizing a microprocessor to:

1. Increment or decrement the selected frequency.

2. Store the “USE,” “STBY,” and 9 user programmable channels in non-volatile memory.

3. Remote transfer the “USE” and “STBY” frequencies and remote increment

the stored channels.

4. Light the display with a digital liquid crystal readout and control dimming of

the display.

5. Generate frequency code for the synthesizer.

D. A power supply made up of a discrete 9 volt regulator, 3 terminal 5 volt reg-

ulator.

E. A liquid crystal frequency display with variable backlighting and viewing an-

gle.

4.2 GENERAL CIRCUIT THEORY

4.2.1 Receiver

A receiver block diagram is shown in Figure 4-1. The received signal passes through

the low pass filter on the transmitter PC board and the T/R diode to the dual gate field

effect transistor RF amplifier. The desired signal proceeds to the dual gate FET mixer

Q103 where it is converted to 11.4 MHz, and fed through the monolithic crystal filter to

the integrated circuit IF amplifiers followed by the detector. Automatic gain control

voltage is fed back to the first and second IF amplifiers and the RF amplifier to achieve

more than 120 dB of dynamic range. The detected signal is not allowed to pass

through the squelch gate until the input signal has:

A. Exceeded the noise squelch setting or,

B. Exceeded the carrier level setting.

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-1

B KY 96A, KY 97A

It proceeds through the low pass filter which attenuates all audio frequencies above

2.5 kHz. The audio signal is fed through the volume control to the integrated circuit

audio pre-amplifier. Its output will provide more than 100 milliwatts to a headphone,

or to an external audio mixer/amplifier.

An optional 4 ohm audio amplifier provides 4 watts on the 13.75 V units and 8 watts

on the 27.5 V units.

4.2.2 Transmitter/ Modulator

The transmitter block diagram is shown in Figure 4-2. In the transmit mode, the VCO

feeds a signal to the transmitter of the frequency selected in the “USE” display window

on the front panel. The signal is amplified by the broadband transmitter to the 5 watts

level and fed through the elliptic function 3 section low pass filter to the antenna.

Modulation is applied to the power amplifier by series modulating the 27.5 volt line

(13.75 for KY 97A) with mic audio. A small amount of mic audio is also fed to the receiver audio amplifier for sidetone.

4.2.3 Stabilized Master Oscillator

The stabilized master oscillator (SMO) I103 generates the RF drive for the transmitter

as well as the local oscillator for the receiver. The SMO synthesizes frequencies that

are referenced to a 25 kHz signal derived from a 3.975 MHz crystal oscillator. Receive

and transmit codes are fed to the synthesizer by the microprocessor (uP) and represent the frequency indicated in the “USE” window on the front panel.

4.2.4 Microprocessor and Display

Refer to microprocessor block diagram shown in Figure 4-3. The microprocessor (uP)

contains 4 k bytes of permanent Read Only Memory (ROM) for program instruction. A

32 byte non-volatile memory is used externally for frequency information storage. The

uP receives a 3.975 MHz clock signal from the synthesizer PLL IC which is derived

from a 3.975 MHz crystal.

The uP sends a serial 24 bit code to the synthesizer PLL IC (last 20 bits used) to determine the reference divide ratio. A serial 24 bit code (last 20 bits used) is also sent

to determine the divide ration of the “USE” frequency (when changed).

The increment/decrement switches send three pulses to the uP (up, pulse, down) in a

specific sequence to provide the code and validity check for increment and decrement

operations.

Display dimming controls are read through an analog to digital converter allowing the

aircraft lighting bus to dim the display.

The LCD display viewing angle is controlled by I801, which controls the display bias,

thereby controlling the display viewing angle based on inputs from R755, R802, and

Q803.

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-2

B KY 96A, KY 97A

4.3 DETAILED THEORY OF OPERATION

Refer to schematics in Section VI of this manual.

4.3.1 Receiver

4.3.1.1 Antenna Input Circuit

In the receive mode Q101 is switched on, forward biasing the T/R diodes located on

the transmitter board. The desired signal passes through the first pole of the low pass

filter, then to the T/R diodes, and then to the receiver board. C102 steps up the impedance to match the first pole of the preselector.

4.3.1.2 Double Tuned Preselector

The first pole of the preselector is tuned by L101, C103 and CR101A. The signal is

coupled to the second pole of the preselector by L102. The second pole of the preselector is tuned by L103, C106 and CR101B. The matched varactor diodes, CR101A

and CR101B, are tuned to the desired frequency through a large resistor from the VCO

control voltage. The desired signal is coupled to gate 1of the RF amplifier by C107.

4.3.1.3 RF Amplifier Q102

Q102 and the associated parts make up the RF amplifier. The desired signal is applied to gate 1. The RF AGC is applied to gate 2. The RF amplifier has 20 dB of gain

at maximum RF AGC voltage, and 30 dB of attenuation with minimum RF AGC voltage; producing a dynamic range of 50 dB. C114 couples the desired signal to the double tuned interstage.

4.3.1.4 Double Tuned Interstage Network

The first pole of the interstage network is tuned by L105, C115 and CR101C. The signal is coupled to the second pole of the interstage network by L106. The second pole

of the preselector is tuned by L107, C118 and CR101D. The matched varactor diodes,

CR101C and CR101D, are tuned to the desired frequency through a large resistor

from the VCO control voltage. The desired signal is coupled to gate 1 of the mixer

through L133.

4.3.1.5 Mixer Q103

Q103 and the associated parts make up the mixer. The local oscillator signal is fed to

gate 2 at a frequency 11.4 MHz above the desired signal. The level of the local oscillator is between +4 dBm and +7 dBm. The desired signal is now at 11.4 MHz. The

drain of Q103 is tuned to 11.4 MHz by T101 and matched to the crystal filter.

4.3.1.6 Crystal Filter FL101

The crystal filter provides the desired selectivity. The input and output of the filter is

matched to 4100 ohms by T101 and T102 respectively.

4.3.1.7 First IF Amplifier I101

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-3

B KY 96A, KY 97A

The desired signal is coupled from T102 to the first IF amplifier, I101. The first IF amplifier has about 45 dB of gain with 60 dB of dynamic range. IF AGC voltage is applied

to I101 on pin 5 through R124. R124 converts the AGC voltage to an AGC current.

The output is loaded with R245 for stability. T103 is tuned for 11.4 MHz and couples

the signal to the second IF amplifier.

4.3.1.8 Second IF Amplifier I102

The second IF amplifier has about 45 dB of gain with 60 dB of dynamic range. IF AGC

voltage is applied to I102 on pin 5 through R126. R126 converts the AGC voltage to

an AGC current. The output is loaded with R246 for stability. T104 is tuned for 11.4

MHz and couples the signal to the detector.

4.3.1.9 Detector

Transistor Q105 and capacitor C130 makes up the amplitude modulation detector. It

is biased near cutoff by transistor Q104, which the emitter-base junction provides bias

stability and temperature compensation. The demodulated signal is sent to the noise

amp, Q112, IF AGC, I105A, squelch gate, Q116, and to the demodulator buffer, Q131.

4.3.1.10 IF AGC Circuit

AGC voltage is derived from the average value of the detector collector voltage, which

is inversely proportional to the carrier level. The operational amplifier I105A filters out

the audio variations and integrates to the average voltage of the detector. R159 and

R160 set the maximum gain reduction at about 6.6 volts. As the detector collector voltage increases with a decrease in signal level, the AGC voltage decreases which increases the gain in the first and second IF amplifiers. The IF AGC voltage is made

available at TP105 and at the rear connector pin L. The AGC voltage at pin L is reduced by one diode drop (approx. 0.6 V).

4.3.1.11 RF AGC Circuit

The RF AGC voltage is applied to the RF amplifier from I105B. The RF AGC stays at

maximum voltage (maximum gain of amp) until the RF signal level reaches about 12.5

uV. The level at which it attacks is set by R184. When the IF AGC voltage exceeds

the reference voltage set by R184, the RF AGC voltage decreases, decreasing the

gain in the RF amplifier. RF AGC is made available at TP106.

The RF AGC is gated with TX(not) through CR120A such that when the unit transmits,

the RF AGC voltage goes to zero. This provides maximum attenuation in the RF amplifier during transmit.

4.3.1.12 Noise and Carrier Squelch Circuit

The carrier squelch circuit prevents the radio from squelching if an RF carrier greater

than 12.5 uV has been detected. I106B compares the RF AGC voltage, which is inversely proportional to the carrier level, to the reference level set by R183 and R185.

If the RF AGC voltage is greater than the reference level, then the unit is allowed to

squelch; if the noise level is large enough. When the RF AGC voltage is less than the

reference level, the output of I106B goes high; turning on Q140. When Q140 turns on,

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-4

B KY 96A, KY 97A

the input signal to the noise amp is shorted to ground, causing the noise squelch circuit

to be inhibited.

Transistor Q112 amplifies the noise from the collector of the detector and limits its amplitude so that impulse spikes (such as ignition noise) will not be of a higher amplitude

than other noise. The output of Q112 is coupled to a 8 to 10 kHz bandpass filter,

I106A. The output of the bandpass filter is fed to the comparator, I107A. The signal

is compared to the reference level set by R176. When the noise signal is larger than

the reference level the comparator goes high charging C166. If C166 is charged greater than half the supply voltage, then the unit will be squelched.

CR107A and CR110B will squelch the radio in transmit.

4.3.1.13 Squelch Gate

Q116, Q117 and associated parts make up the squelch gate. The audio signal comes

from the detector at TP108; the detector biases Q116. When the unit is squelched the

base of Q117 goes to the supply voltage and its emitter follows. Since the emitters of

Q116 and Q117 are tied together, Q116 becomes reverse biased; attenuating the signal 70 dB.

4.3.1.14 Audio Low Pass Filter

Inductor L110 and its associated capacitors form a low pass elliptical filter. The filter

is at least 20 dB down at 4 kHz and the notch is at least 25 dB down at 4.5 kHz. The

filter does roll off below 350 Hz since the signal is AC coupled in and out of the filter.

The low frequency roll off reduces 60 cycle hum.

4.3.1.15 Audio Compressor

The received signal is coupled through C178 to the input of the compressor amplifier,

I111A. The output is fed to the volume control and to I111B. I111B will begin to discharge C179 when the amplitude to I111B exceeds the voltage across R210. Discharging C179 lowers the gate to source voltage on Q118, which reduces the drain to

source resistance on Q118. As Q118 is turned on, the amplitude at C178 is reduced.

This maintains a constant amplitude out of the compressor amplifier.

4.3.1.16 Audio Amplifier

The audio signal is routed through the volume control R902 to the audio amplifier,

I112A. The signal is amplified approximately 30 dB and capacitive coupled through

C187 to the auto-transformer, T107. The voltage and impedance are stepped up to

provide a minimum of 100 mW of audio power into 500 ohm load; such as headphones

or an audio panel. The sidetone, through R220, and the Mic intercom, through R218,

are also amplified by the audio amplifier.

An optional 4 ohm audio amplifier provides 4 watts on 13.75 V units and 8 watts on

27.5 V units. See audio board section for more details.

4.3.2 Stabilized Master Oscillator (SMO)

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-5

B KY 96A, KY 97A

4.3.2.1 Synthesizer

The stabilized master oscillator is based around synthesizer I103 which is serial programmable by the microprocessor.

A 3.975 MHz crystal is attached to the gate oscillator, and the reference divider divides

it by 159 to produce the 25 kHz reference frequency. The RF frequency is divided by

the internal pre-scaler and divider then compared by the phase detector to the reference frequency. If the frequency is greater than 25 kHz the phase detector will pulse

up once every 40 usec. If the frequency is less than 25 kHz the phase detector will

pulse down. The greater the divided frequency from the reference frequency the wider

the phase detector pulse.

Q133, R137, and C135 integrates the lock detect pulses to send the lock detect signal

to the microprocessor. The reference oscillator is lightly coupled to Q132 which amplifies the 3.975 MHz signal for the microprocessor and I705 on the processor board.

The clock, data and strobe lines are driven from the microprocessor.

4.3.2.2 Voltage Translator

Q134, Q135, Q136, Q137 and their associated parts make up the voltage translator.

The voltage translator translates from five volt pulse to nine volt pulse and inverts the

logic of the pulses. The output of the phase detector is fed to the emitters of Q134 and

Q135. The bases of Q134 and Q135 are biased to about 2 volts so that when the

phase detector is tri-stated, Q134 and Q135 will be off. If the phase detector pulses

low, Q134 will turn on causing Q136 to turn on and a 9 volt pulse to appear at the output of the voltage translator, TP110. If the phase detector pulses high, Q135 will turn

on causing Q137 to turn on pulling the output to ground.

4.3.2.3 Low Pass Filter

The low pass filter is a lead/ lag network with a 2.5 kHz elliptical low pass filter with its

notch at 25 kHz. C235 and C236 make up the elliptical filter. R279, R280, R281, and

C237 make up the lead/ lag network. With this filter, the loop bandwidth is about 300

Hz and the 25 kHz notch is about 130 dB down. The control voltage is fed to the preselector through R136 and to the VCO through L132.

4.3.2.4 Voltage Controlled Oscillator (VCO)

Q108 and its associate parts form a modified Hartley oscillator. The varactor CR101E

is part of a matched set of five varactors so the preselector will track the VCO. C149

determines the range of the tuning voltage, the smaller the capacitor the larger the tuning range must be to maintain the same frequency range. C249 and R299 provide

bias stability. The tuning range is 118.00 MHz at 2.5 V and 151.375 MHz at 8.0 V.

4.3.2.5 VCO Buffer

Q109 and its associated parts form the VCO buffer. The VCO buffer provides isolation

from the transmit buffers and the mixer as well as amplifying the signal to about +7

dBm to the mixer.

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-6

B KY 96A, KY 97A

4.3.2.6 Digital Buffer

Q106, Q107 and their associated parts form the digital buffers. The VCO is very lightly

coupled to the digital buffers through C147 so that noise from the pre-scaler will not

get back to the VCO. The signal is coupled to the pre-scaler through C140 at about

500 mV.

4.3.2.7 Transmit Buffers

The transmit buffers contain two stages of amplification. The RF signal is coupled

through C155 to Q110 and amplified. C157 couples the collector of Q110 to Q126.

Q126 amplifies the signal to approximately 24 dBm. The signal is coupled through

CR117 and C228 to create the transmit drive. The drive level is adjusted for different

transmitters by the resistor R1006. Q111 and Q139 are turned off during receive allowing Q110 and Q126 to be reversed biased. Q127 is also turned off during receive

preventing CR117 from being turned on. During receive the RF signal is reduced by

50 dB.

4.3.3 Modulator

4.3.3.1 Microphone Input Circuit

The microphone is connected to pin K of the rear panel connector. Mic bias is supplied

by R114 and R223. The signal passes through C191 to the Mic Gain control. Q119

is turned on during transmit to pass the signal to the modulator compressor.

4.3.3.2 Modulator Compressor

The audio signal is coupled through C230 to the input of the compressor amplifier,

I113A. The output is fed to the modulator amplifier, I113B will begin to discharge C198

when the output of the modulator exceeds the voltage across R267. Discharging

C198 lowers the gate to source voltage on Q120, which reduces the drain to source

resistance on Q120. As Q120 is turned on the amplitude at C230 is reduced. This

maintains a constant amplitude out of the compressor amplifier. R267 set the modulation level. The bias network R257 and R267 is run off of the mod bias voltage, so

that when the mod bias sags the modulation will decrease preventing distortion.

4.3.3.3 Modulator Amplifier

The output of the compressor amplifier is coupled to the modulator amplifier through

C194. The output is coupled to the modulator through C196 and T108.

4.3.3.4 Modulator Bias

The modulator bias (mod bias) regulates the supply voltage to just below half the supply voltage. Q123 is the regulating transistor and on the 28 volt versions Q122 is used

to buffer the regulating transistor. The KY 96A drops the modulator bias an additional

6.2 volts through CR123. R251, R254, and R256 set the regulated voltage, with R256

being adjustable. CR115 prevents overvoltage problems. RT101, R250, and R252

set the power reduction due to a thermal overload. When RT101 becomes hot, the

resistance goes up reducing the voltage at E113, causing CR114 to turn on, and thus

lowers the bias on Q123.

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-7

B KY 96A, KY 97A

4.3.3.5 Modulator (14 Volts KY 97A)

The audio signal is applied to the primary of T108, which has a 4 to 1 turns ratio. This

steps up the voltage swing on the modulator transistors Q124 and Q125 enough to

make a 0 to 12 V swing to the transmitter final and driver. This output is also fed back

to the modulator compressor. The mod bias is fed to the secondary of T108 providing

the bias to Q125 with R247 being the current limit resistor.

4.3.3.6 Modulator (28 Volts KY 96A)

The audio signal is applied to the primary of T108, which has a 4 to 1 turns ratio. This

steps up the voltage swing to the bases of the modulator transistors Q124 and Q130

enough to make a 1 to 12 V swing on the transmitter final and driver. This output is

also fed back to the modulator compressor. The mod bias is fed to the secondary of

T108 providing the bias to Q124 and Q130 with R247 being the current limit resistor.

4.3.4 Transmitter

4.3.4.1 RF Amplifier

RF is fed from the transmit buffers to the RF amp, on the transmitter board, through a

miniature 50 ohm coaxial cable. The drive level is approximately 15 dBm. During receive the RF is attenuated as the TX(not) line goes high it turns on Q404 shorting the

drive to ground and removing the bias from pin diode CR403 to “OPEN” the input to

Q401. During transmit, the base current is supplied through R401 and CR403 to operate Q401 class A. Transformer T401 is broadband tuned and steps the collector impedance down to the input impedance of the driver.

4.3.4.2 Driver Q402

RF drive is fed through C412 and C437 to the driver, Q402. The driver is operated

class C and the collector is modulated through T402. The collector is broadband tuned

and is coupled to the final by T402.

4.3.4.3 Final

Capacitor C415, C416, and C440 form the input matching network for the final power

amplifier, Q403. The final is operated class C and is modulated at the collector. The

low collector output impedance is stepped up to approximately 50 ohms by transformer T403.

4.3.4.4 Low Pass Filter

A three section elliptical low pass filter is placed between the final and the antenna to

attenuate all harmonics which may be generated in the transmitter. During transmit

the T/R diodes CR401 and CR402 are reversed biased to protect the receiver from 5

watts of power.

4.3.5 Microprocessor

4.3.5.1 Communication to Synthesizer PLL I702

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-8

B KY 96A, KY 97A

The microprocessor (uP), pin 32, sends two 24 bit serial data streams to the synthesizer PLL IC (I103) on the main board. Only the last 20 bits are used by the synthesizer PLL IC. The first stream provides the crystal divide ration and the second provides the frequency to be divided. Each data bit is clocked from pin 33 of the uP. At

the end of each data stream, a high going strobe pulse is sent from pin 28 of the uP to

latch the last 20 bits of data into the synthesizer PLL IC.

When the synthesizer is locked, pin 25 (Lock Detect) of uP is pulled high from the synthesizer PLL IC I103. If pin 29 (Mic key(not)) of uP is low, pin 22 (TX) of the uP is taken

high to turn on the transmitter when synthesizer is in lock. The gate of Q701 must be

pulled low for the uP to take TX high. Then TX is inverted through Q707 to turn on the

transmitter.

4.3.5.2 Communication to Non-Volatile Memory

When the non-volatile memory (I704) is being addressed, pin 24 of the uP is high.

When reading from the memory, a 16 bit serial code/ address stream is sent out on pin

32 of the uP, then a serial 16 bit data stream associated with the address is read back

on pin 31 of the uP. When writing to the memory, a 16 bit serial code/ address stream

followed by a 16 bit serial data stream associated with the address, are sent out of pin

32 of the uP. Only the last 9 bits of the 16 bit code/ address stream are used by the

non-volatile memory. Each bit of the code/ address and data streams is clocked from

pin 33 of the uP.

4.3.5.3 Communication to Analog to Digital Converter

When the analog to digital converter (A/D) (I706) is addressed, pin 23 of the uP is low.

A serial 8 bit address stream is sent to the A/D from pin 32 of the uP requesting conversion data. Simutaneously, a serial 8 bit data stream of the last requested conversion data is received from the A/D on pin 31 of the uP. This makes communication

full duplex. Only the first 4 bits of the address stream are used by the A/D. Each bit

of the address and conversion data streams is clocked from pin 33 of the uP.

The A/D uses a system clock for its conversion time. The 496.875 kHz system clock

is generated from I705, a binary counter. The 3.975 MHz clock signal (synthesizer

PLL IC) on pin 1 of I705 is divided by 8, then output on pin 9 of I705.

4.3.5.4 Microprocessor Reset Circuit

During normal operation the output on pin 13 of I701A is 5 volts DC. The 5 volts DC

on pin 40 (Vdd) of the uP, is produced through the 5 volt regulator I108 on the main

board. On power up, the 9 volts on the input of I108 must reach 7.3 volts DC before

5 volts DC is produced on the output of I108. Therefore, on power up the uP (pin 1) is

held in reset until the 9 volt DC reaches 7.9 volts DC. Pin 11 of I701A must reach 6.2

volts DC to accomplish this. On power down, the 9 volt DC must drop to 7.5 volts DC

before the uP is put into reset.

4.3.5.5 Display

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-9

B KY 96A, KY 97A

The display is a liquid crystal (LCD) type with three sections (“USE,” “STBY,” and

“CHAN”). The “USE” frequency, which is the active frequency, is displayed in the

“USE” window at all times. A standby frequency, which can be exchanged with the

“USE” frequency, is displayed in the “STBY” window when in standby entry mode.

When in channel or program mode, the channel frequency is displayed in the “STBY”

window and the channel number is displayed in the “CHAN” window. When in channel

mode the letters “CH” are displayed between the “CHAN” and “STBY” windows. When

in program mode the letters “PG” are displayed to the left of the “STBY” window. The

letters “TX” are displayed to the right of the “USE” window during transmit.

The uP I702 sends a 112 bit serial stream through pin 10 to pin 1 of I801 (LCD driver)

on the display board. The serial stream contains backplane/ mode and segment information. Each bit is clocked through pin 11 of the uP I702.

The LCD display viewing angle is controlled by the bias provided by I801 to the display. The output of the voltage divider formed by R755, R801, and R802 is applied to

the base of Q803. The collector of Q803 is connected to +5 Vdc, and the emitter is

connected to I801 pin 12 which provides I801 with a reference voltage, which sets the

bias level applied to the display by I801.

The display brightness is controlled in three different ways, dimming through the aircraft 14 or 28 Vdc lighting bus or half brightness all the time.

When the aircraft 14 Vdc lighting dimmer bus is selected, pins 7 and 9 of I702 are low

and pin 8 of I702 is high. This turns on Q704 thereby pulling E705 low which supplies

a ground to 3 of the 6 light bulbs for the LCD display backlighting. Q705 is off allowing

the 14 Vdc lighting voltage to pass through CR703 to E704 to supply +14 Vdc across

two sets of 3 light bulbs in series for the LCD display backlighting.

When the aircraft 14 Vdc Max lighting option is selected, pin 9 of I702 is low and pins

7 and 8 of I702 are high. This causes Q704 and Q705 to be on, placing E704 at

ground and E704 at +14 Vdc.

When the aircraft 28 Vdc lighting dimmer bus is selected, pin 7, 8, and 9 of I702 are

low. This causes Q709 to be on, placing E705 at +28 Vdc.

When the aircraft 28 Vdc Max lighting is selected, pins 7 and 8 of I702 are low and pin

9 of I702 is high. This causes Q702 to be on and Q709 to be on thereby pulling line

E705 to +28 Vdc.

4.3.6 Audio Amplifier Board

The audio amplifier board consists of a summing amplifier and a 4 watt/ 8 watt amplifier.

I1201A and associated parts form the summing amplifier. Three 500 ohm auxiliary inputs are loaded by R1201, R1202, and R1203. The summing amplifier reduces the

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-10

B KY 96A, KY 97A

auxiliary inputs to the desired level to be fed to the Mic Intercom input. C1207 filters

high frequency noise and C1210 filters low frequency noise. The output of the summing amplifier is routed through the main board Mic Intercom input and back through

the main board Comm Audio Out.

Comm Audio In goes through R1214 and is reduced by an inverting amplifier, I1201B,

to prevent distortion through the FET switch, Q1202. The gate of Q1202 is pulled up

by R1219 allowing Q1202 to pass the audio signal. When the TX line is grounded

Q1202 turns off reducing the signal by al least 40 dB.

Q1203, Q1204, Q1205, Q1206, Q1207, and Q1208 form a trans-resistive amplifier

with 18 dB of gain. The feedback resistor, R1237, provides 23 dB of desensitization

to gain changes due to temperature or part variations. CR1202 and CR1203 reduce

crossover distortion. C1219, C1220, C1227, and C1221 reduce the gain above the

audio passband to prevent oscillation. The audio drivers, Q1207 and Q1208, provide

a minimum of 4 watts for 13.75 V units and 8 watts for 27.5 V units into a 4 ohm load.

The output is fused by F1201 to protect the drivers. R1238 is in parallel with the fuse

to provide residual audio in case the fuse blows.

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-11

B KY 96A, KY 97A

THIS PAGE RESERVED

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-12

B KY 96A, KY 97A

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-13

FIGURE 4-1 Receiver Block Diagram

(Dwg No 696-5674-01 Rev 0)

B KY 96A, KY 97A

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-15

FIGURE 4-2 Transmitter Block Diagram

(Dwg No 696-5674-02 Rev 0)

B KY 96A, KY 97A

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 4-17

FIGURE 4-3 Microprocessor Block Diagram

(Dwg No 696-5674-03 Rev 0)

B KY 96A, KY 97A

SECTION V

MAINTENANCE

5.1 GENERAL INFORMATION

This section contains information on tests, alignment, inspection, cleaning, repair and

troubleshooting procedures for the KY 96A, KY 97A.

Before maintenance of the KY 96A, KY 97A is attempted, a thorough understanding

of the theory of operation (Section IV) is recommended.

5.1.1 Standard Test Signal Description

5.1.1.A. “Hard” microvolts indicates use of a 6dB pad between the signal generator

and the receiver. (Example: A receiver with 6 dB S+N/N at 2 uV hard must

have 1 uV of sensitivity).

5.1.1.B. A standard modulator test signal is a 0.4 Vrms, 1 kHz tone, open circuit, with

the network shown in Figure 5-3.

5.1.1.C. A standard audio test signal is an RF carrier amplitude modulated 30% at

1,000 +/- 100 Hz.

5.2 TEST EQUIPMENT

5.2.1 REQUIRED TEST EQUIPMENT

The following test equipment, or equivalent, is required to properly align and test the

KY 96A, KY 97A. All test equipment must be calibrated before attempting alignment.

TABLE 5-1 Required Test Equipment

TYPE CHARACTERISTICS REPRESENTATIVE MODELS

Power Supply 27.5 V @ 6 amps Sorensen SRL 40-6 or equivalent.

RF Signal Generator Boonton Model 211A or equivalent

Audio Signal Generator HP 200CD

Digital Multimeter Fluke 8000A

RF Wattmeter Bird Model 611

Frequency Counter HP 5245L

Audio Wattmeter with Load Eico Model 261

Oscilloscope Tektronix Model 454 or equivalent

RF Signal Generator HP 606A

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 5-1

B KY 96A, KY 97A

TABLE 5-1 Required Test Equipment

TYPE CHARACTERISTICS REPRESENTATIVE MODELS

Linear Detector Figure 5-2

Mic Test Circuit Figure 5-3

40 dB Attenuator Figure 5-4

Bench Test Harness Figure 5-5

TABLE 5-2 Optional Test Equipment

TYPE CHARACTERISTICS REPRESENTATIVE MODELS

Distortion Analyzer

5.2.2 TEST EQUIPMENT SETUP

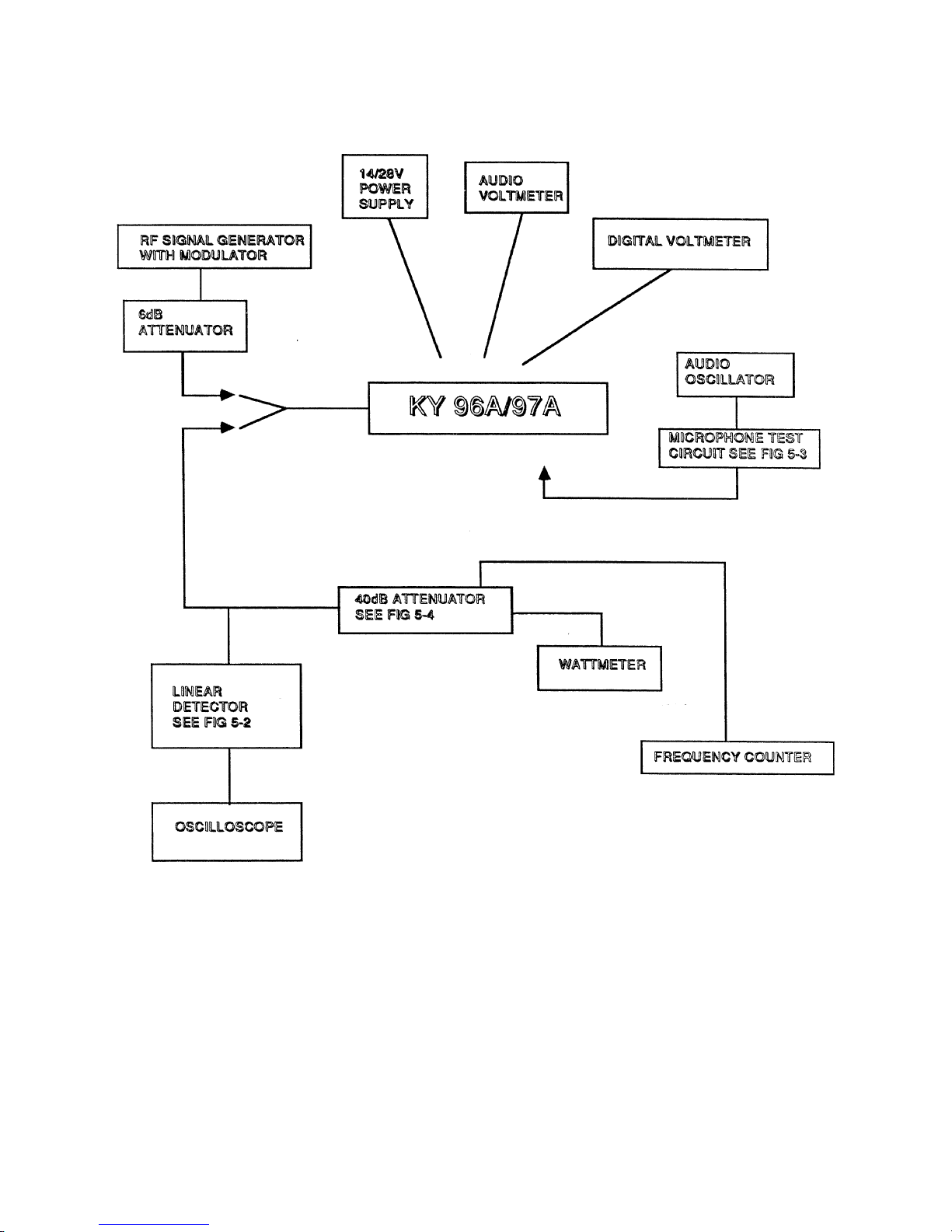

Connect test equipment according to Figure 5-1.

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 5-2

B KY 96A, KY 97A

FIGURE 5-1 Typical Test Equipment Setup

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 5-3

B KY 96A, KY 97A

5.3 PERFORMANCE TEST PROCEDURE

This section is a cover on return-to-service performance test. The unit shall pass this

performance test after removal of covers, modification, alignment, or repair of the unit

before return to service. The performance test can also be used to locate faults within

the radio.

TEST DATA SHEET Serial No. _________

5.3.1 Control Functions

NOTE: The term “OK” indicates that particular function is operating properly.

5.3.1.A. Display: ___OK viewing angle (straight on).

5.3.1.B. Frequency Controls:

Increment Roll Over Characteristics Decrement Roll Under Characteristics

MHz___OK 135 to 118 MHz MHz___OK 118 to 135 MHz

136 to 118 MHz 118 to 136 MHz

kHz___OK 0.975 to 0.000 kHz kHz___OK 0.000 to 0.975 kHz

5.3.1.C. Transfer Button: ___OK (switches from an active to standby frequency).

5.3.1.D. Remote Transfer: ___OK (switches from an active to standby frequency).

5.3.1.E. Chan Button: ___OK (enters channel mode).

5.3.1.F. Remote Channel Increment: ___OK (increments channel).

5.3.1.G. Program Secure: Channel program secured ___OK.

Channel un-program secured ___OK.

5.3.1.H. Dim Select:

open position ___OK (Display brightness follows 13.75 V lighting bus).

grounded position ___OK (Display brightness follows 27.5 V lighting bus).

aircraft supply position ___OK (Display at half brightness).

5.3.1.I. Memory: ___OK.

When unit is turned “OFF” and then back “ON” that the last display status is

the same.

5.3.1.J. 25 kHz Switch: ___OK

The 25 kHz switch increments in steps of 25 kHz.

5.3.2 Receiver

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 5-4

B KY 96A, KY 97A

NOTE: Disable the audio compressor by grounding pin 10 on P96A1, P97A1.

5.3.2.A. Sensitivity:

5.3.2.A.1 Input a 2 uV standard audio test signal into the unit and monitor receiver audio

while switching modulation off.

S+N/N: 118.000 MHz ______ NLT 6dB

126.975 MHz ______ NLT 6dB

135.975 MHz ______ NLT 6dB

[136.975 MHz] _____ NLT 6dB

5.3.2.A.2 Input a 100 uV standard audio test signal into the unit and monitor receiver

audio while switching modulation off.

Quieting: 126.975 MHz ______NLT 25 dB S+N/N.

5.3.2.B. AGC Characteristics: 126.975 MHz ______ NMT 3 dB

With a standard audio test signal vary from 5 uV to 20,000 uV.

5.3.2.C. Selectivity:

Using the AGC voltage produced by a 3 uV standard signal reference, measure and record the frequencies which reproduce the AGC REF voltage at 6

dB and 60 dB above the reference input.

5.3.2.C.1 6 dB Bandwidth:

126.975 MHz:

Above ___ >

___ >

126.985 MHz Below ___ < 126.965 MHz - 25 kHz units

126.9895 MHz ___ < 126.9605 MHz - 50 kHz units

5.3.2.C.2 60 dB Bandwidth:

126.975 MHz:

Above ___ > 126.995 MHz Below ___ < 126.955 MHz - 25 kHz units

___ >

127.015 MHz ___ < 126.935 MHz - 50 kHz units

5.3.2.D. Volume Gain Control: Min___NMT 22mV Max___NLT 7.07V into 500 ohms

With Audio Amp board installed Max___NLT 4.5V into 500 ohms

Input a 100 uV standard audio test signal into the unit. Disable squelch by

pulling the volume knob out and monitor the audio output.

5.3.2.E. Audio Distortion: (Optional)

350 Hz = ___NMT 15% 1 kHz = ___NMT 15% 2.5 kHz = ___NMT 15%

Input a 100 uV 85% modulated signal between 350 Hz and 2500 Hz. The distortion shall be not more than 15% at 7.07 Vrms into 500 ohms. Modulation

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 5-5

B KY 96A, KY 97A

is referenced to 1 kHz, compressor enabled. (This is an optional test that requires a distortion analyzer).

5.3.2.F. Audio Response:

350 Hz = ___NMT 6dB down 1 kHz = ___ 0dB 2.5 kHz = ___NMT 6dB down

Input a 100 uV standard audio test signal into the unit. Disable the audio compressor by grounding pin 10 on P96A1, P97A1. Monitor the receiver output.

5.3.2.G. Compressor: ______NMT +/- 3 dB

Input a 100 uV standard audio test signal into the unit. Vary the modulation

from 30% to 85%.

5.3.2.H. Squelch:

NOTE: Squelch adjustments must be performed in the following order:

5.3.2.H.1 Set the unit to 126.975 MHz.

5.3.2.H.2 Carrier/Noise Squelch set to open at 2 uV (+1 uV, -0.5 uV) and close at NMT

4 dB below the squelch opening.

5.3.2.H.3 Carrier/Noise Squelch _____OK.

5.3.2.H.4 With unit set to 126.975 MHz, input an 8 kHz 85% modulated signal into the

unit. Set the carrier squelch to open at +/- 12.5 uV.

5.3.2.H.5 Carrier Squelch _____OK.

5.3.2.H.6 Intercom: ______ NLT 100 mW into 500 ohm.

Input a 100 mV 1 kHz signal into Mic Intercom, pin K of P96A1, P97A1.

5.3.3 Transmitter

5.3.3.A. RF Power Output:

Connect a wattmeter to the antenna output and record the following unmodulated values.

Set A + input to ______ 13.75 Vdc @ pin 11______

27.5 Vdc @ pin 12 ______

118.00 MHz ______ 5.0 watts Min. 13.75 V units

126.97 MHz ______ 5.0 watts Min. 13.75 V units

135.97 MHz ______ 5.0 watts Min. 13.75 V units

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 5-6

______ 5.0 watts Min. 27.5 V units

______ 5.0 watts Min. 27.5 V units

______ 5.0 watts Min. 27.5 V units

B KY 96A, KY 97A

After 2 minutes continuous key:

NOTE: Units with Mic-key Disable will shut down transmitter after 2 minutes. To ex-

tend transmit time re-key transmitter.

118.00 MHz ______ 1.25 watts Min. 13.75 V units

______ 1.25 watts Min. 27.5 V units

126.97 MHz ______ 1.25 watts Min. 13.75 V units

______ 1.25 watts Min. 27.5 V units

135.97 MHz ______ 1.25 watts Min. 13.75 V units

______ 1.25 watts Min. 27.5 V units

Low Voltage:

With a low line voltage input the following values should be observed:

22 Vdc for 27.5 V units

11 Vdc for 13.75 V units

118.00 MHz ______ 1.25 watts Min. 13.75 V units

______ 1.25 watts Min. 27.5 V units

126.97 MHz ______ 1.25 watts Min. 13.75 V units

______ 1.25 watts Min. 27.5 V units

135.97 MHz ______ 1.25 watts Min. 13.75 V units

______ 1.25 watts Min. 27.5 V units

5.3.3.B. Modulation Capability:

Input a standard modulator test signal into the microphone audio. Using the

linear detector, measure the Tx modulation.

5.3.3.B.1 118.000 MHz ______ NLT 70%

126.97 MHz ______ NLT 70%

135.97 MHz ______ NLT 70%

5.3.3.B.2 Carrier Noise Level:

Modulate the carrier with 70% at 1000 Hz.

Noise on the carrier with modulation removed shall be NLT:

118.00 MHz ___ 40dB 126.97 MHz ___ 40dB 135.95 MHz ___ 40dB

5.3.3.B.3 Demodulated Audio Distortion (Optional):

350 Hz = ___ 15% Max 1 kHz = ___ 15% Max 2.5 kHz = ___ 15% Max

(This is an optional test that requires a distortion analyzer).

5.3.3.B.4 Sidetone Audio Response:

Rev 5, Apr 2003 MM 006-05674-0005.dwd Page 5-7

Loading...

Loading...