Page 1

DESCRIPTION REFERENCE DES BOM OPTIONQTYPART NUMBER CRITICAL

DRAWING

ANGLES

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

DATE

APPD

ENG

DATE

APPD

CK

ECN

ZONE

REV

DO NOT SCALE DRAWING

X.XXX

X.XX

XX

DIMENSIONS ARE IN MILLIMETERS

THIRD ANGLE PROJECTION

D

SIZE

APPLICABLE

NOTED AS

MATERIAL/FINISH

NONE

SCALE

DESIGNER

MFG APPD

DESIGN CK

RELEASE

QA APPD

ENG APPD

DRAFTER

METRIC

OF

SHT

DRAWING NUMBER

TITLE

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

Apple Computer Inc.

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

DESCRIPTION OF CHANGE

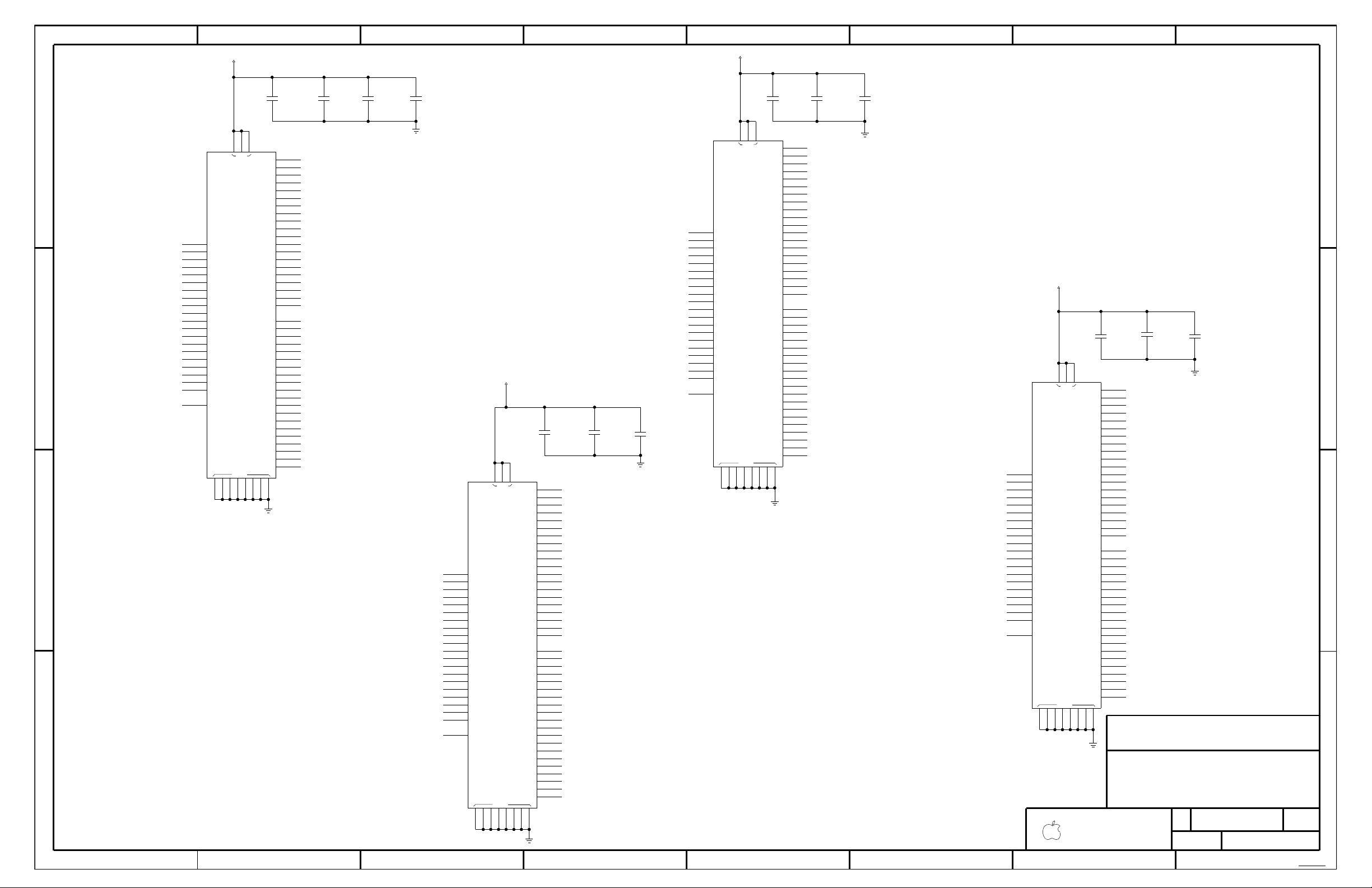

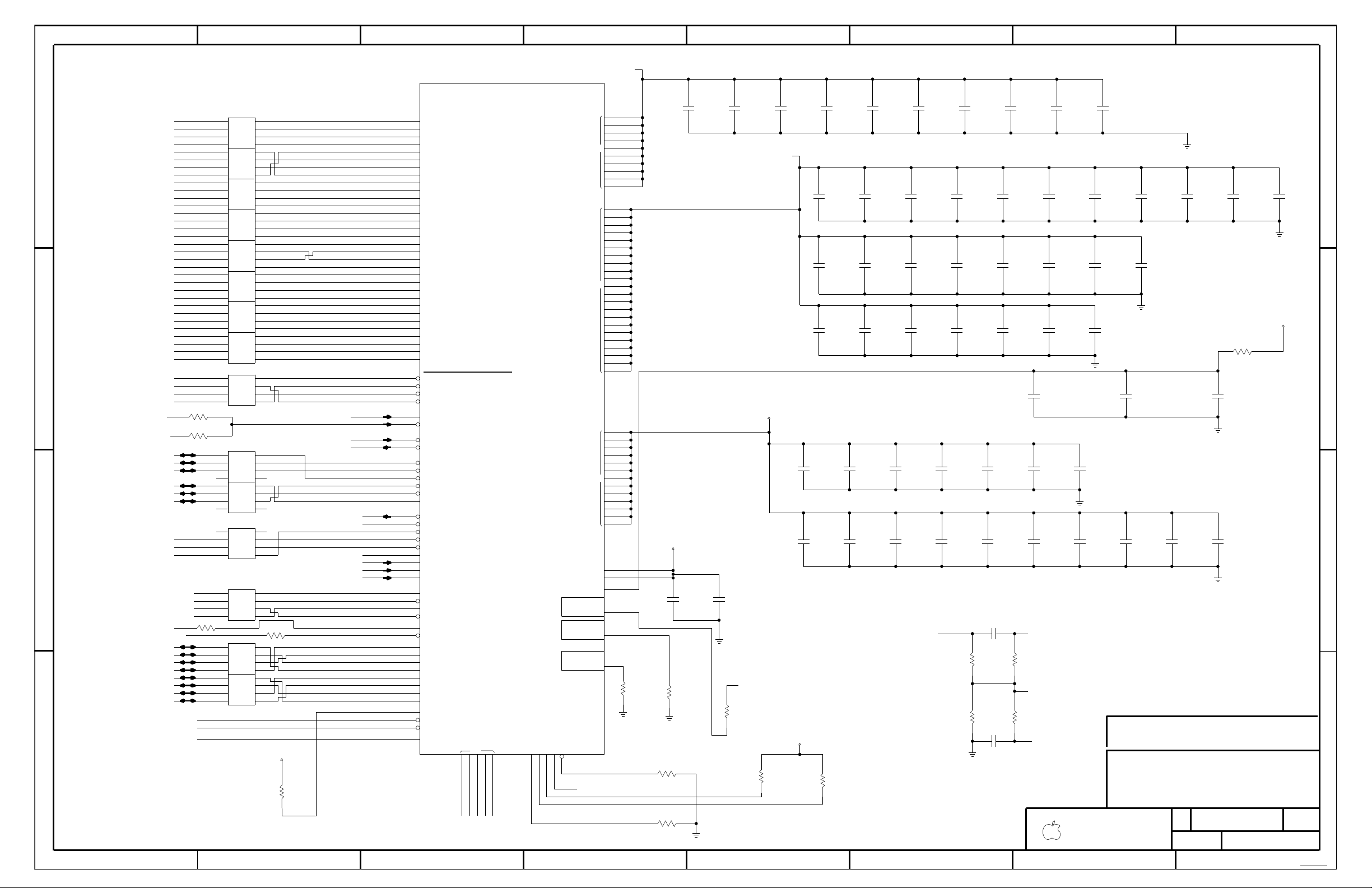

NVIDIA DAC/DVI, CLOCKS & STRAPS (SECTIONS 2 & 5)

14-15

WIRELESS PCI

INTREPID ETHERNET & FIREWIRE (SECTION 4)

PAGE

DVT

CPU LA CONNECTORS, ESP, CPU BYPASS

BLOCK DIAGRAM, SYSTEM, POWER & PCB INFO

TABLE OF CONTENTS

MODEM, BLUETOOTH, KITCHEN SINK & SERIAL DOWNLOAD

INTREPID MAX IF (SECTION 1)

8

AUDIO CODEC & VOLTAGE REGS

35

37

LINE IN/OUT BUFFERS

36

TMDS & EXTERNAL VGA CONNECTORS

INTREPID POWER & BYPASS (SECTION 8 & 9)

24-25

INTREPID AGP (SECTION 3)

NVIDIA POWER-ON RESET CONFIGURATION STRAPS

USB2 CONTROLLER

SCHEMATIC AND PCB SUPPORT

PCB,UL RECOGNIZED, MIN.130 DEG. C TEMP. RATING AND V-0 FLAME RATING PER UL 796

& UL 94. PCB TO BE SILK-SCREENED WITH UL/CUL RECOGNITION MARK, MANUFACTURER’S UL

FILE NUMBER, UL PCB MATERIAL DESIGNATION, TEMPERATURE RATING AND FLAME RATING.

COVER PAGE

MPC7450 MAXBUS

DDR MUXES

1

2,3

4,5

6,7

10-11

12

13

SO-DIMM, BIG DIMM

16

17

18

19

22-23

26-27

28

32

31

30

INTREPID GPIOS, INTERRUPTS & SERIAL PORTS (SECTION 6)

USB POWER & CONNECTORS

INTREPID UATA/IDE (SECTION 5)

+5V/+12V, AUDIO, FW & TMDS POWER CONVERTERS

ETHERNET PHY

FIREWIRE PHY

38

33

34

NET TABLES

POWER MANAGER UNIT

SPEAKER/MIC AMPS

60-64

52-59

45-51

44

42-43

40-41

65-69

PART TABLES

ATA CD/HD CONNECTORS

9

OFF

OFF

SHUTDOWN

RUN

ON

ON

+1.8V_SLEEP

FW_PWR

+12V_SLEEP

+12V_MAIN

+5V_SLEEP

+5V_MAIN

+MAXBUS_SLEEP

+3V_MAIN

+2_5V_MAIN

OFF

OFF

OFF

OFF

OFF

OFF

ON

ON

ON

ON

ON

ON

ON

SLEEP

POWER RAIL DEFINITIONS

ON

ON

ON

ON

ON

OFF

OFF

OFF

OFF

ON

20-21

GRAPHICS MEMORIES

NVIDIA FB SERIES TERMS, CLK DELAYS

NVIDIA FRAME BUFFER (SECTIONS 3 & 4)

Q59 MLB

29

INTREPID PCI, ROM (SECTION 7)

CONSTRAINT TABLES

39

NVIDIA AGP (SECTION 1)

INTREPID DDR CONTROL

CPU SPEED & CONFIG OPTIONS

<XR_PAGE_TITLE>

051-6497 SCHEM,MLB,Q59 SCH1

1

CRITICAL

1

PCB1

LBL,SER #,BARCODE

825-2029

1

PCB1

CRITICAL

DESIGN GUIDE,MCO,IMACG4

056-1158

PCB1

1

CRITICAL

DFM,PNLZN DWG,MLB,Q59

057-0085

820-1550

1

PCB1

CRITICAL

PCB,MLB,IMACG4

630-XXXX,PCBA,H,Q59,EEE XXX

1

HYNIX OMIT630-XXXX

630-XXXX,PCBA,S,Q59,EEE XXX

OMIT

1

SAMSUNG630-XXXX

SCHEM,MLB,Q59

13

01

1

69

ENGINEERING RELEASED

279015

06/06/03

?

051-6497

LAST_MODIFIED=Wed Sep 17 12:11:39 2003

Page 2

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DRAWING

P.34

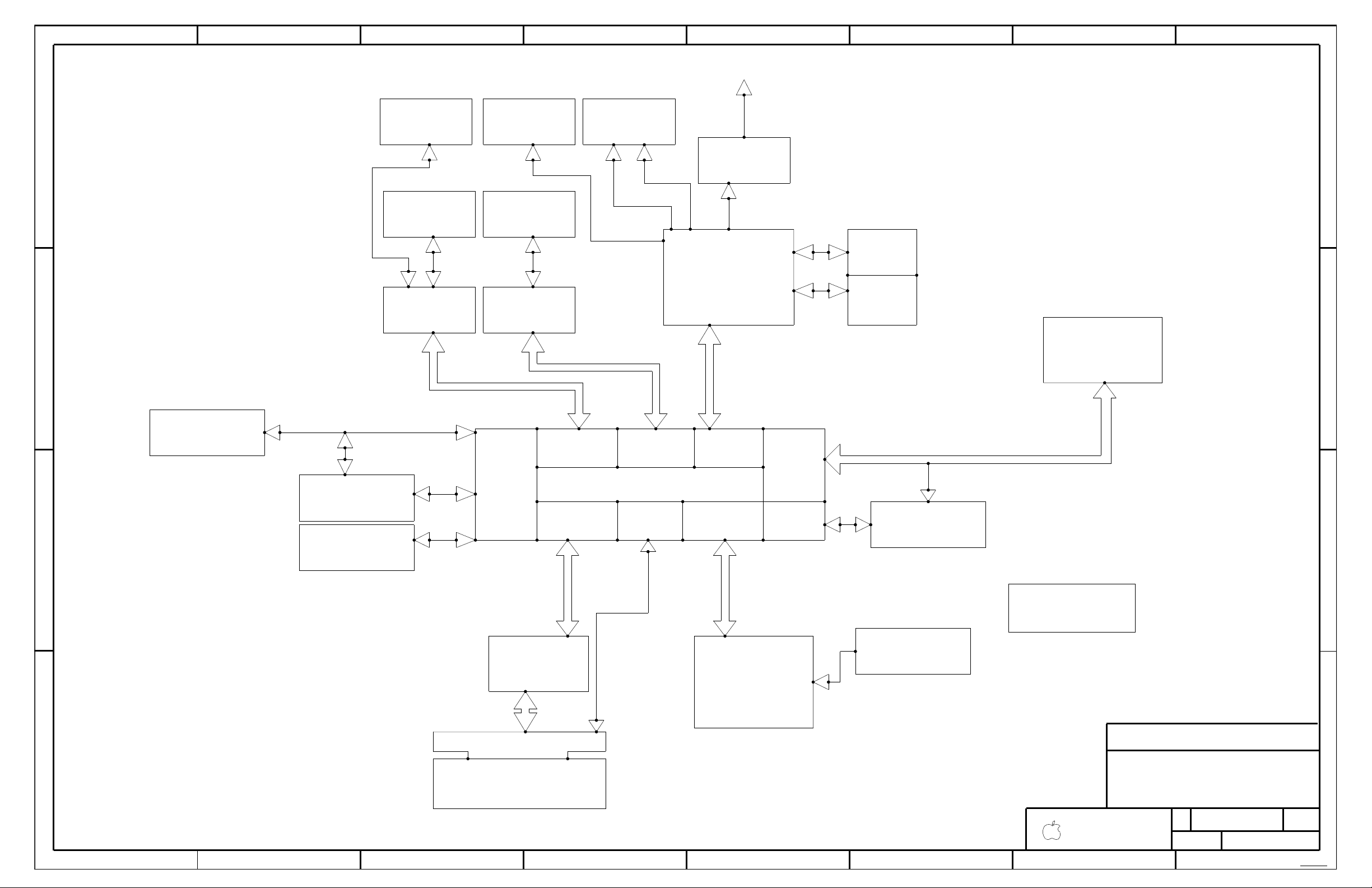

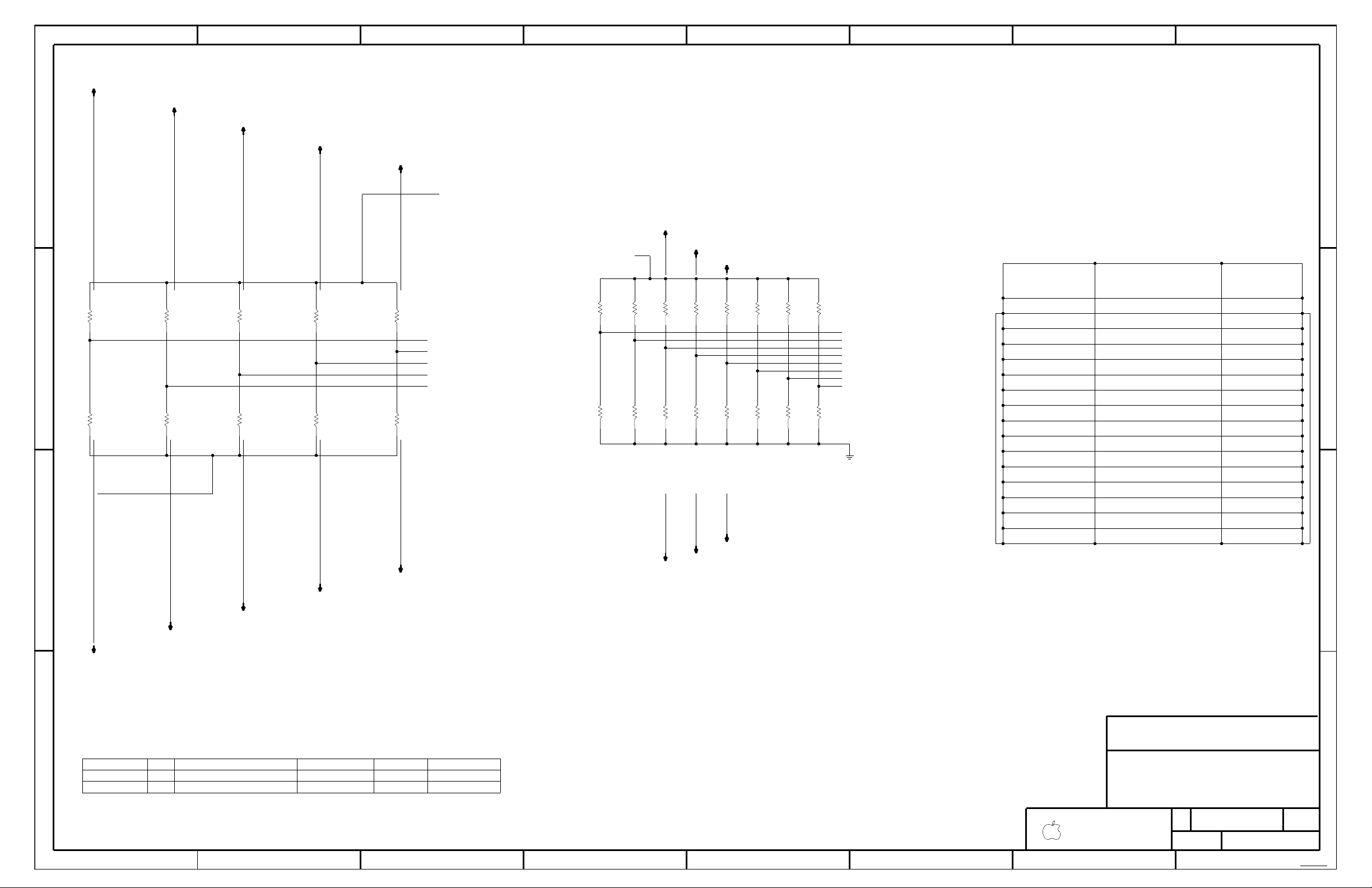

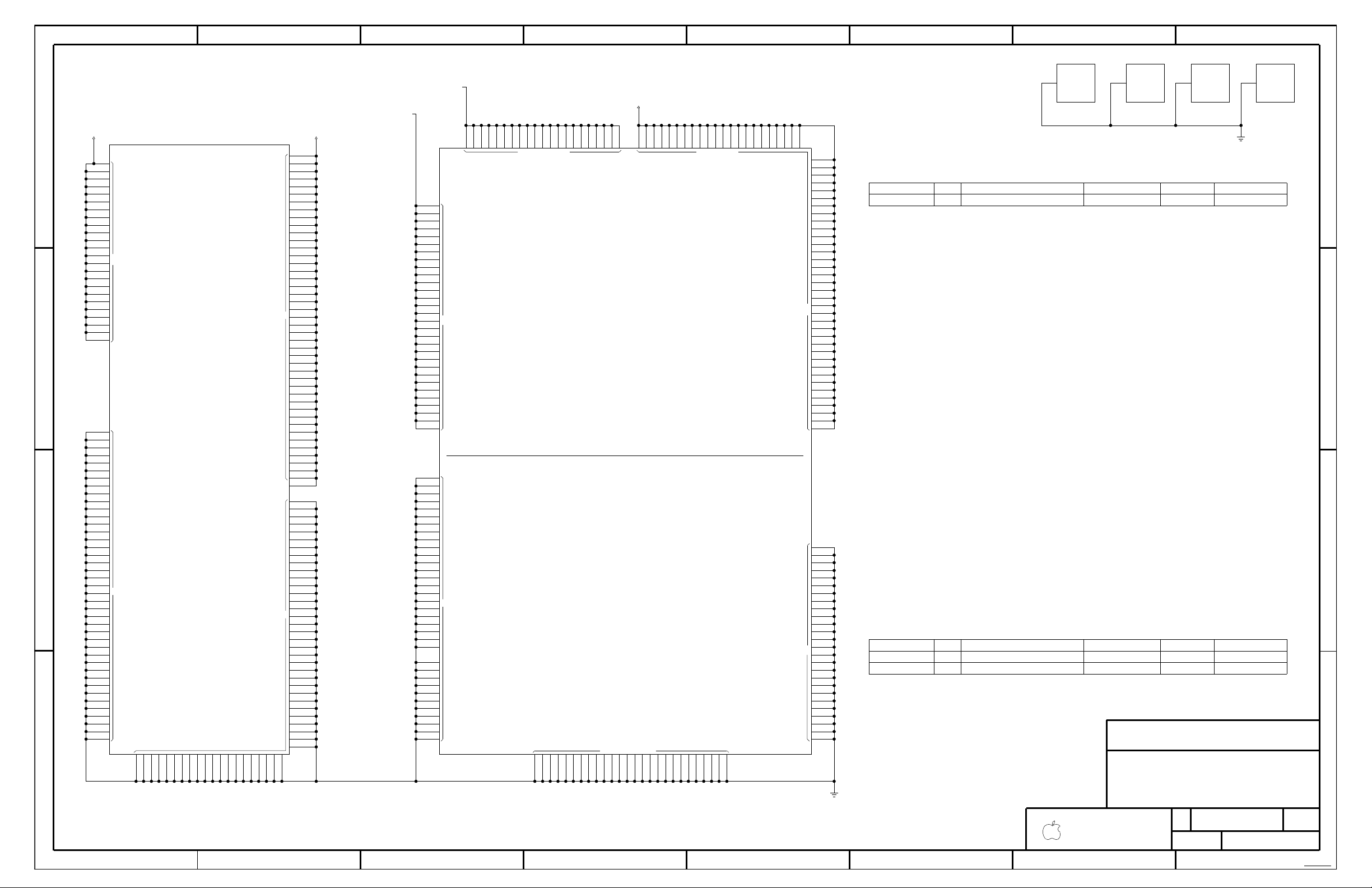

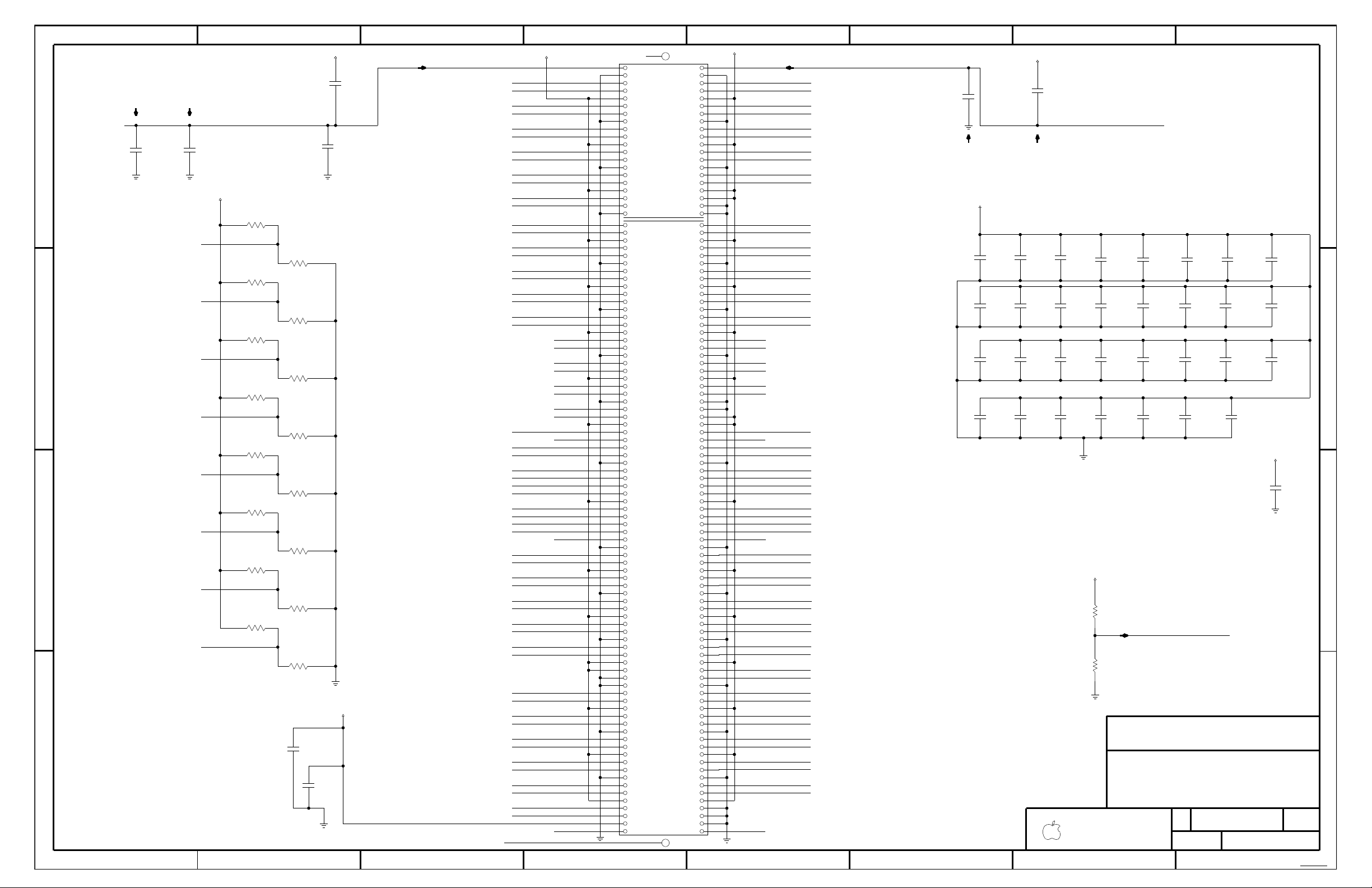

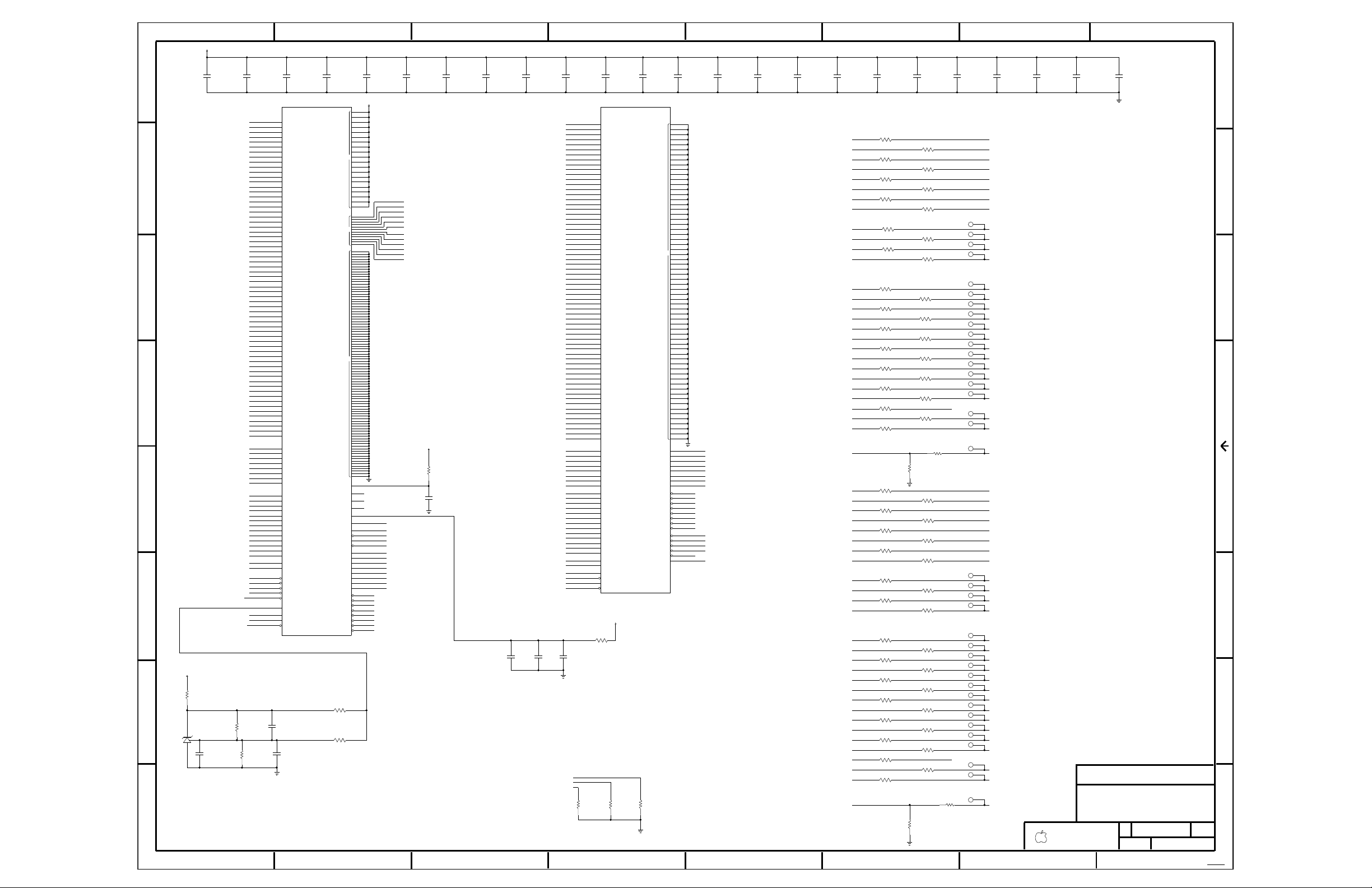

SYSTEM BLOCK

P.31

P.44

P.30

P.6

P.14

P.15

P.13

P.4-5

P.34P.12

P.34

P.16

P.9

P.30

P.30

P.29

P.32

P.28

1394 OHCI

8BIT TX/RX

3.3V

USB

USB2

CONTROL

MODEM

BLUETOOTH

CONN(QTY3)

USB

P.20

P.21

P.31

P.25

VGA

Connector

EDID (I2C)

64MB

NV18B

P.17-27

P.35P.36

P.36 P.35

P.24P.29P.36

KITCHEN

Inverter

DDR SDRAM DIMM 1

DDR SDRAM DIMM 0

DDR MUXES

2.5V

MEMORY BUS

64BITS

167MHZ

FireWire

PHY

Ethernet

DDR MEMORY

400 MB/S

FIREWIRE

I2C

PHY

10/100

INTREPID

ETHERNET

I2C

CPU

64BIT DATA

32BIT ADDRESS

APOLLO

167MHZ

MAXBUS

Config

CPU PLL

MAXBUS

4X AGP

BOOTROM

PCI

66MHZ

NVIDIA

32BITS

1.5V/3.3V

AGP BUS

PCI BUS

BOOT ROM

1M X 8

MEMORY

GRAPHICS

GRAPHICS

MEMORY

(EXTERNAL MEM)

(EXTERNAL MEM)

Connector

Connector

FW - A

Ethernet

Connector

TMDS

Connector

LCD Panel

RGB

VGA/SVIDEO OUT

PMU

WIRELESS

32BITS

SO-DIMM Connector

FW - B

13

2

69

051-6497

<XR_PAGE_TITLE>

LAST_MODIFIED=Wed Sep 17 12:11:39 2003

Page 3

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DRAWING

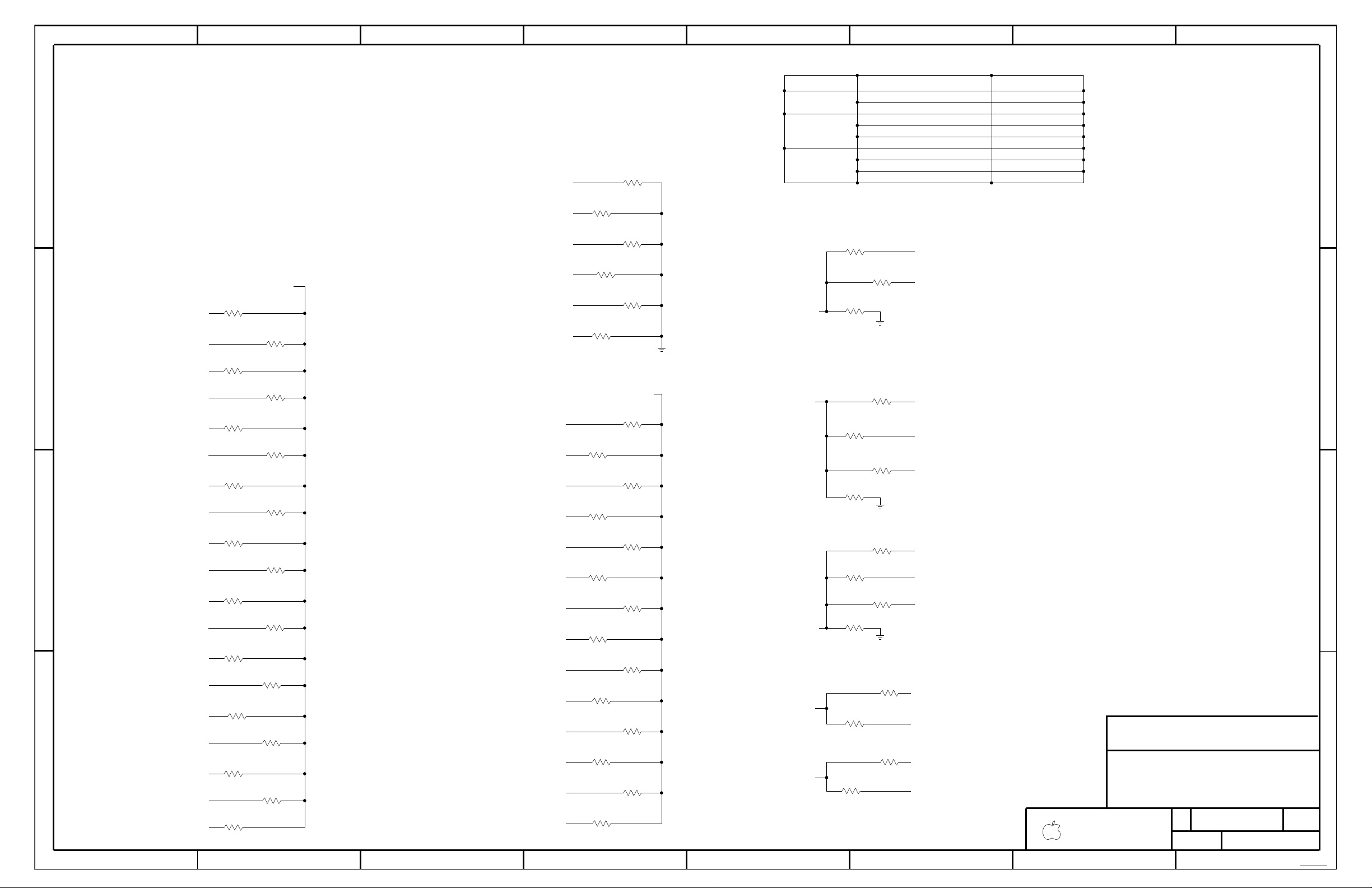

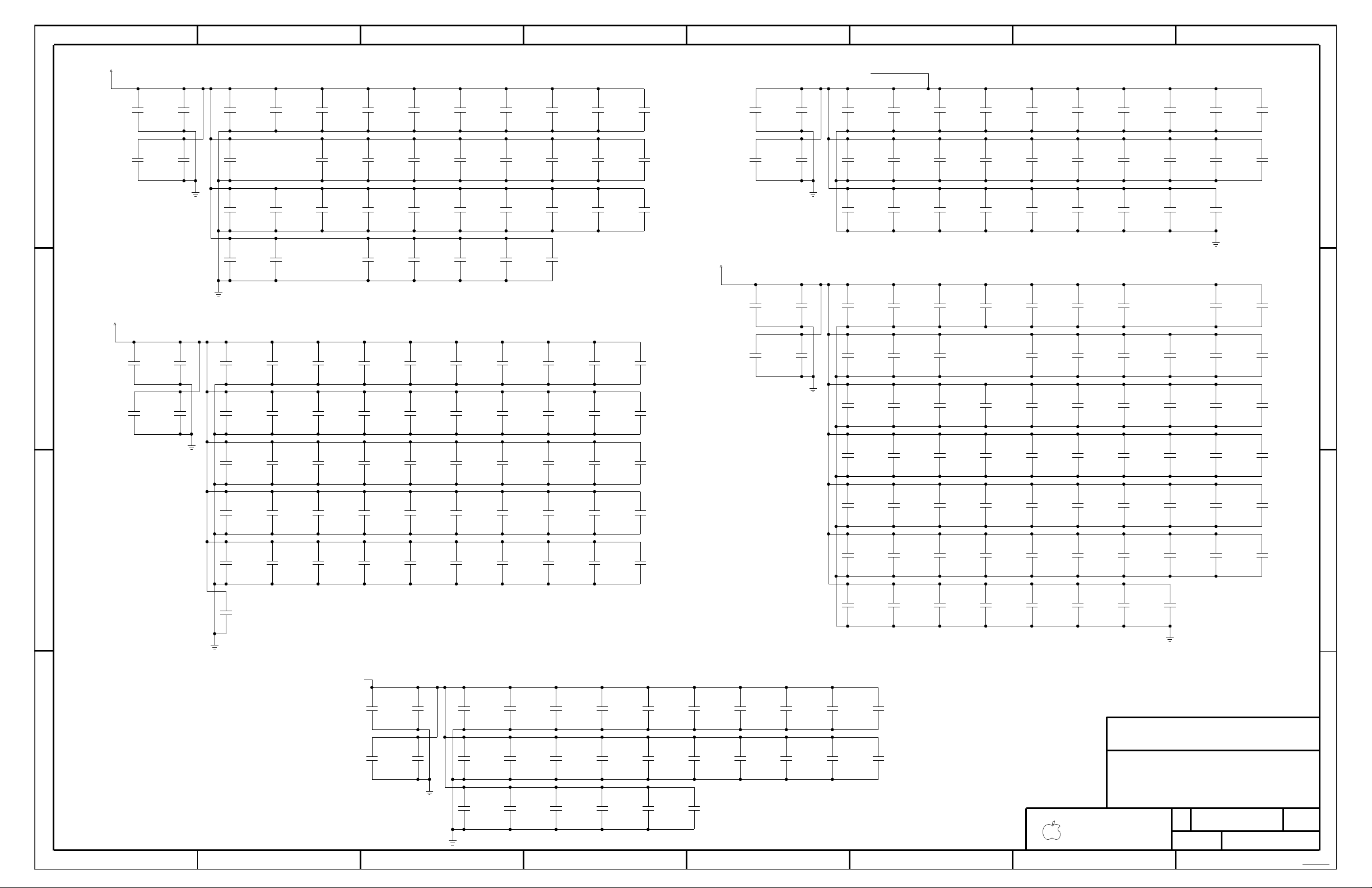

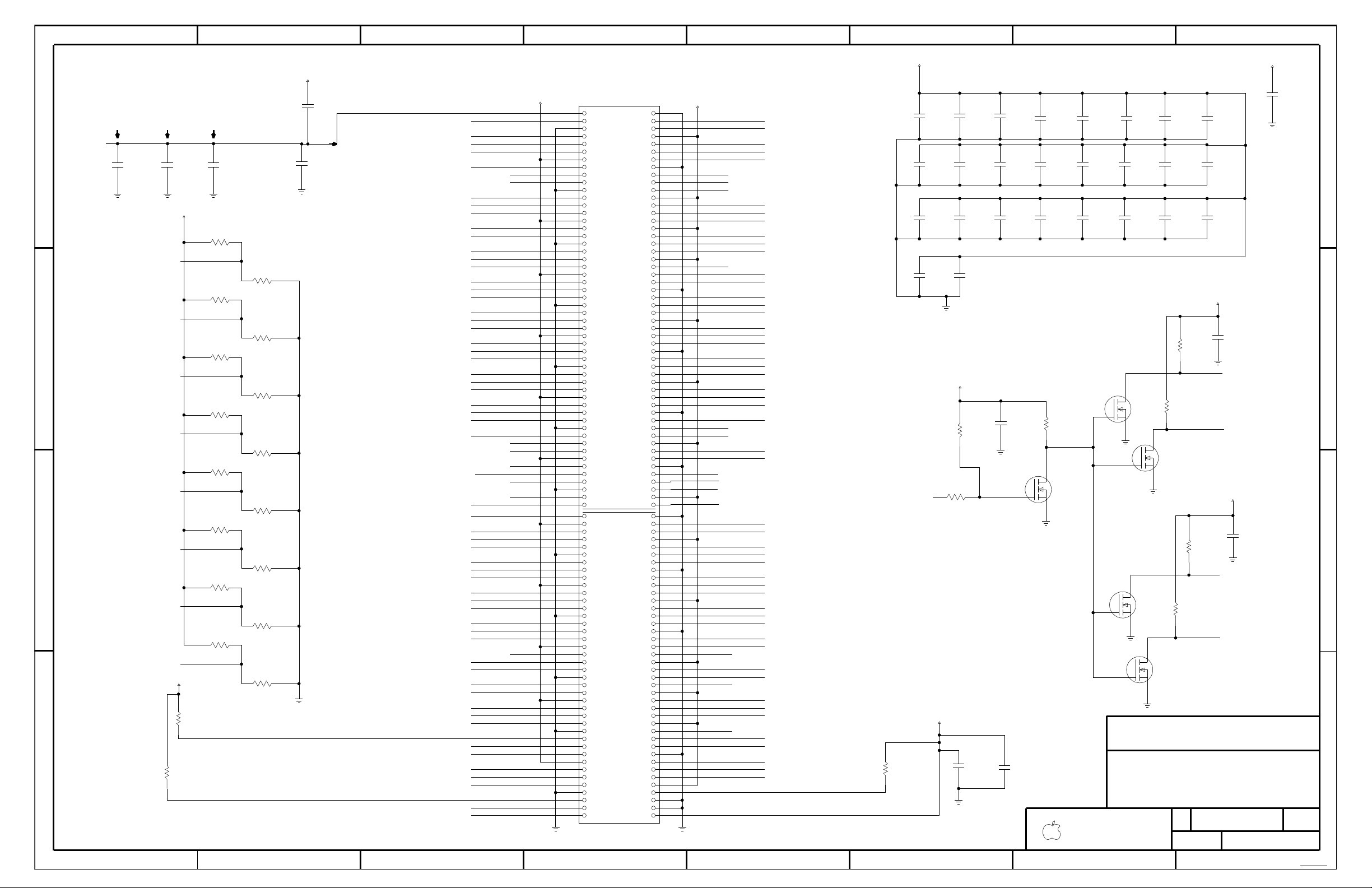

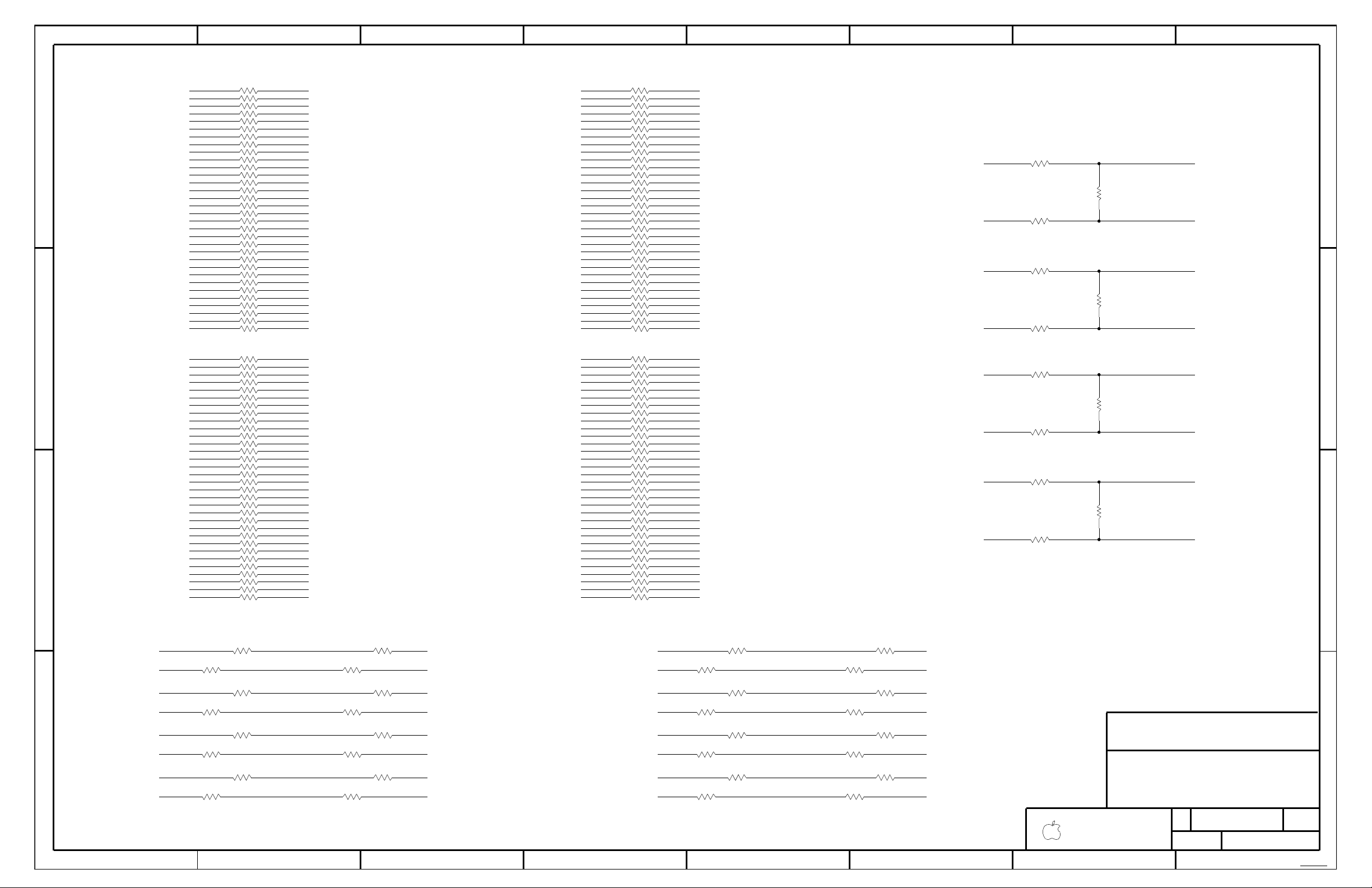

================

8 - SIGNAL-BOTTOM

TOTAL

PREPREG

7 - GROUND2

5 - POWER

1 - SIGNAL-TOP

2 - GROUND1

LAYER

4 - POWER

3 - SIGNAL

6 - SIGNAL

PREPREG

PREPREG

FILLER

FILLER

PREPREG

3

3

0.7

3

4

2.8

3

2.8

17.4

17.4

0.7

1.4

============

62.0

0.7

1.4

0.5

---

---

========

0.5

---

1

0.5

---

---

---

0.5

--1

2

2

---

---

---

4

4

---

=============

------------

--------

(OZ)

(MILS)

THICKNESS COPPER

(MILS)

TRACE WIDTH

3.3V

1.6V

12V

(SC2602)

DC/DC

GRAPHIC

(SWITCH)

FW

CPU

1.55V

2.5V

(SC2602)

(OZ960)

INVERTER

BACKLIGHT

(LTC3707)

DC/DC

DC/DC

DDR

5.1V

(LTC3707)

DUAL

DC/DC

PWR BLOCK,PCB INFO

3.65V

1.5V

1.8V

1.7V

5.1V

5.1V

5.1V

5.1V

LDO

TMDS

(EZ1582)

USB

EXTERNAL

VIDEO

(SWITCH)

HARD

DRIVE

(SWITCH)

OPTICAL

DRIVE

(SWITCH)

INTREPID

(SC2602)

DC/DC

MAXBUS I/O

AGP

(EZ1582)

LDO

LDO

3.3V

(EZ1582)

600V RMS

POWER SYSTEM ARCHITECTURE

+12V

(SWITCH)

--------------

4

4

---

0.7

---

PREPREG

----------------

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

HOLE-VIA-20R10

NOSTUFF

NOSTUFF

HOLE-VIA-20R10

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

NOSTUFF

HOLE-VIA-20R10

HOLE-VIA-20R10

NOSTUFF

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

HOLE-VIA-20R10

NOSTUFF

NOSTUFF

HOLE-VIA-20R10HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

NOSTUFF

HOLE-VIA-20R10

NOSTUFF

HOLE-VIA-20R10

051-6497

13

69

3

<XR_PAGE_TITLE>

ZT46

1

ZT47

1

ZT48

1

ZT49

1

ZT50

1

ZT43

1

ZT42

1

ZT41

1

ZT40

1

ZT39

1

ZT53

1

ZT54

1

ZT55

1

ZT56

1

ZT57

1

ZT63

1

ZT62

1

ZT61

1

ZT60

1

ZT59

1

ZT64

1

ZT65

1

ZT66

1

ZT67

1

ZT68

1

ZT58

1

ZT51

1

ZT44

1

ZT52

1

ZT45

1

LAST_MODIFIED=Wed Sep 17 12:15:39 2003

Page 4

(1 OF 3)

TEST4

TEST3

TEST2

TEST1

TEST0

EXT_QUAL

TBEN

L2TSTCLK

L1TSTCLK

TCK

TMS

TDO

TDI

DTI0

DTI1

DTI2

DTI3

PLL_EXT

PLLCFG3

PLLCFG2

PLLCFG1

PLLCFG0

CLKOUT

SYSCLK

BVSEL

TT3

TT2

TT1

TSIZ0

TSIZ2

TSIZ1

TT4

TT0

A33

A34

A35

AP0

AP3

AP2

AP4

AP1

A25

A24

A23

A26

A27

A28

A29

A30

A31

A32

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A12

A10

A9

A8

A7

A6

A3

A4

A5

A11

A2

A0

A1

OVDD

VDD

GND

AVDD

BR*

BG*

TS*

TRST*

LSSDMODE*

TA*

TEA*

QREQ*

QACK*

CKSTP_IN*

CKSTP_OUT*

INT*

SMI*

MCP*

SRESET*

HRESET*

PMON_IN*

PMON_OUT*

BMODE0*

BMODE1*

TBST*

GBL*

WT*

CI*

AACK*

ARTRY*

SHD0*

HIT*

SHD1*

DRDY*

DBG*

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DESCRIPTION REFERENCE DES BOM OPTIONQTYPART NUMBER CRITICAL

DRAWING

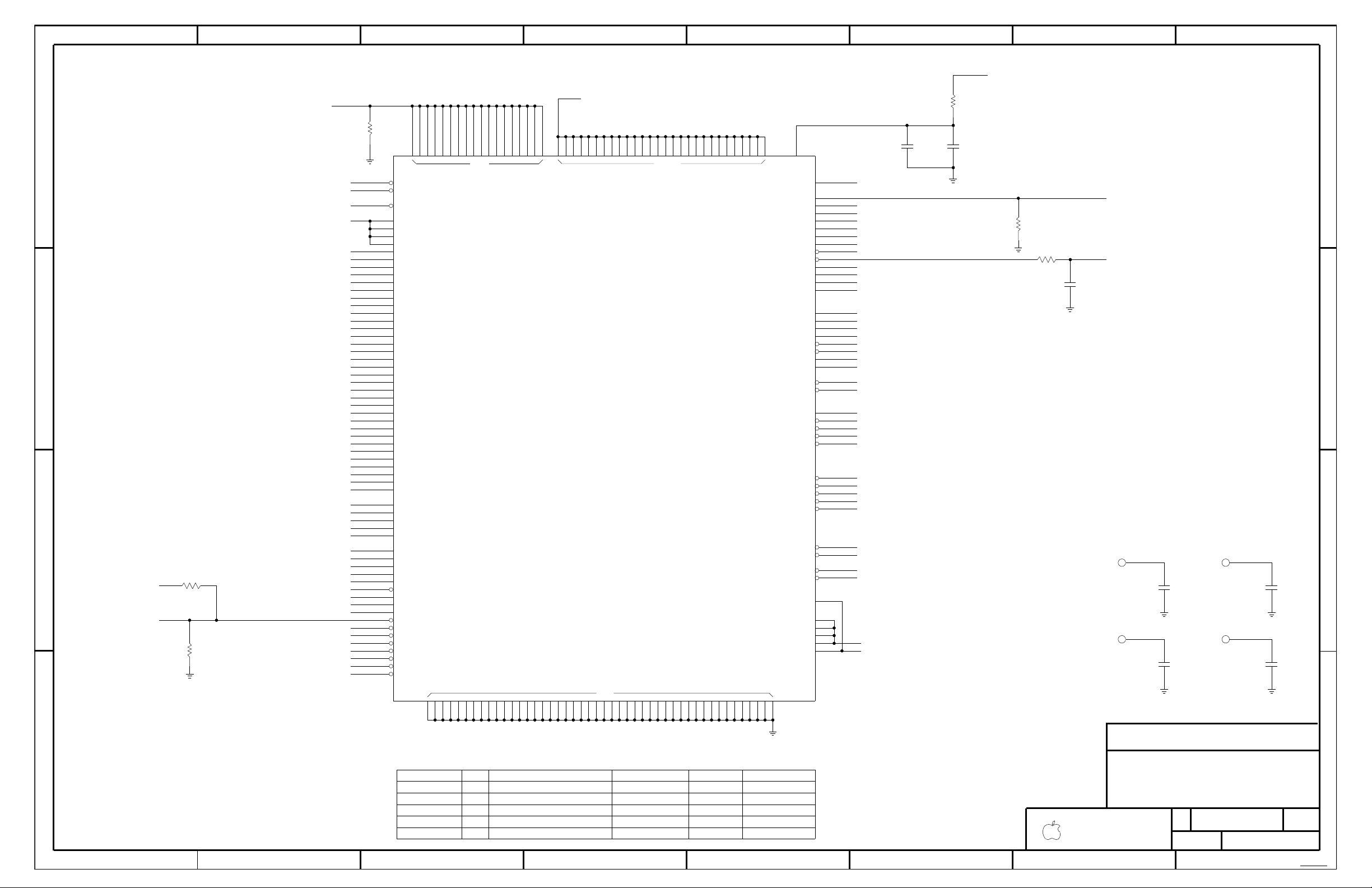

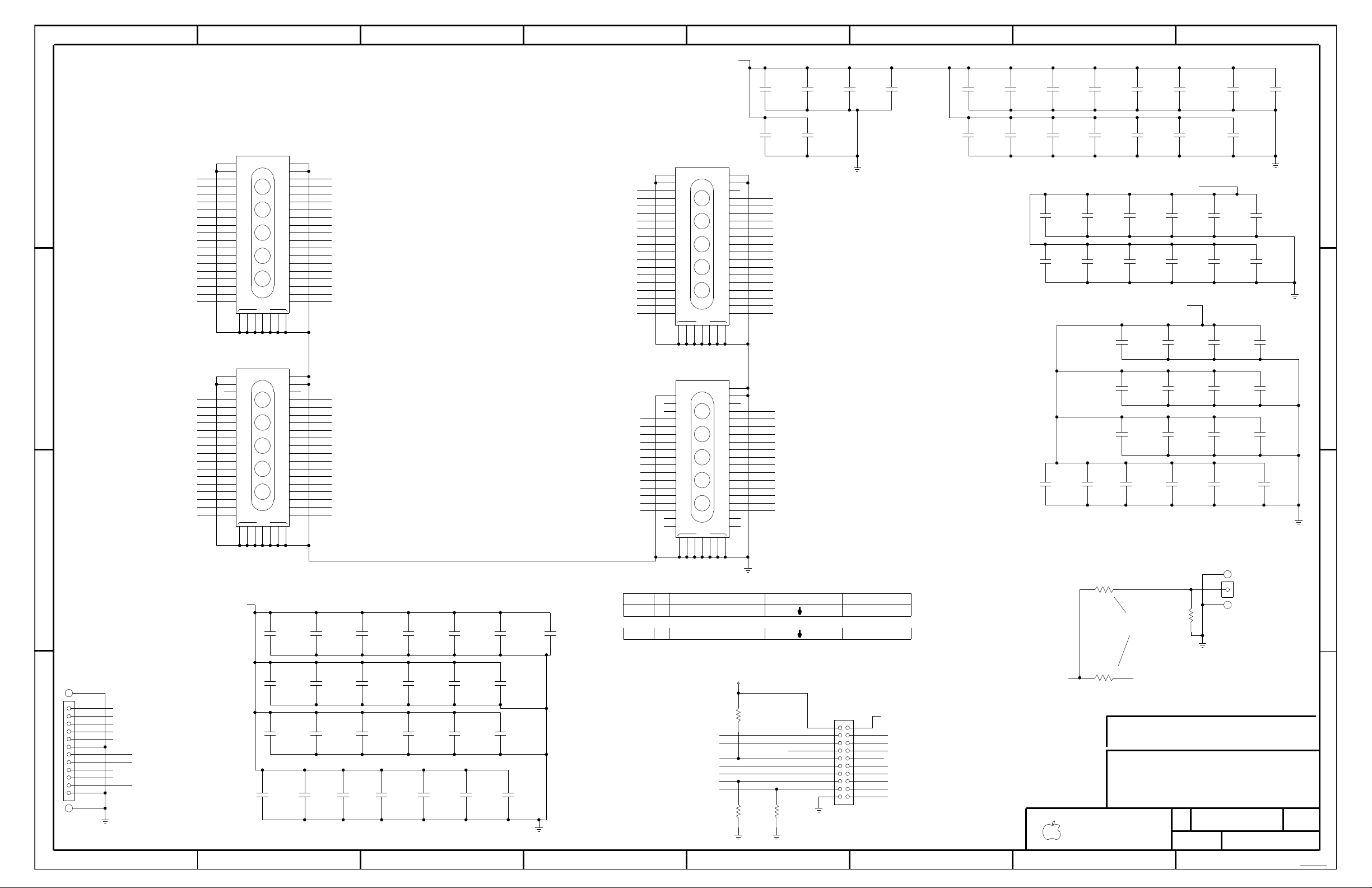

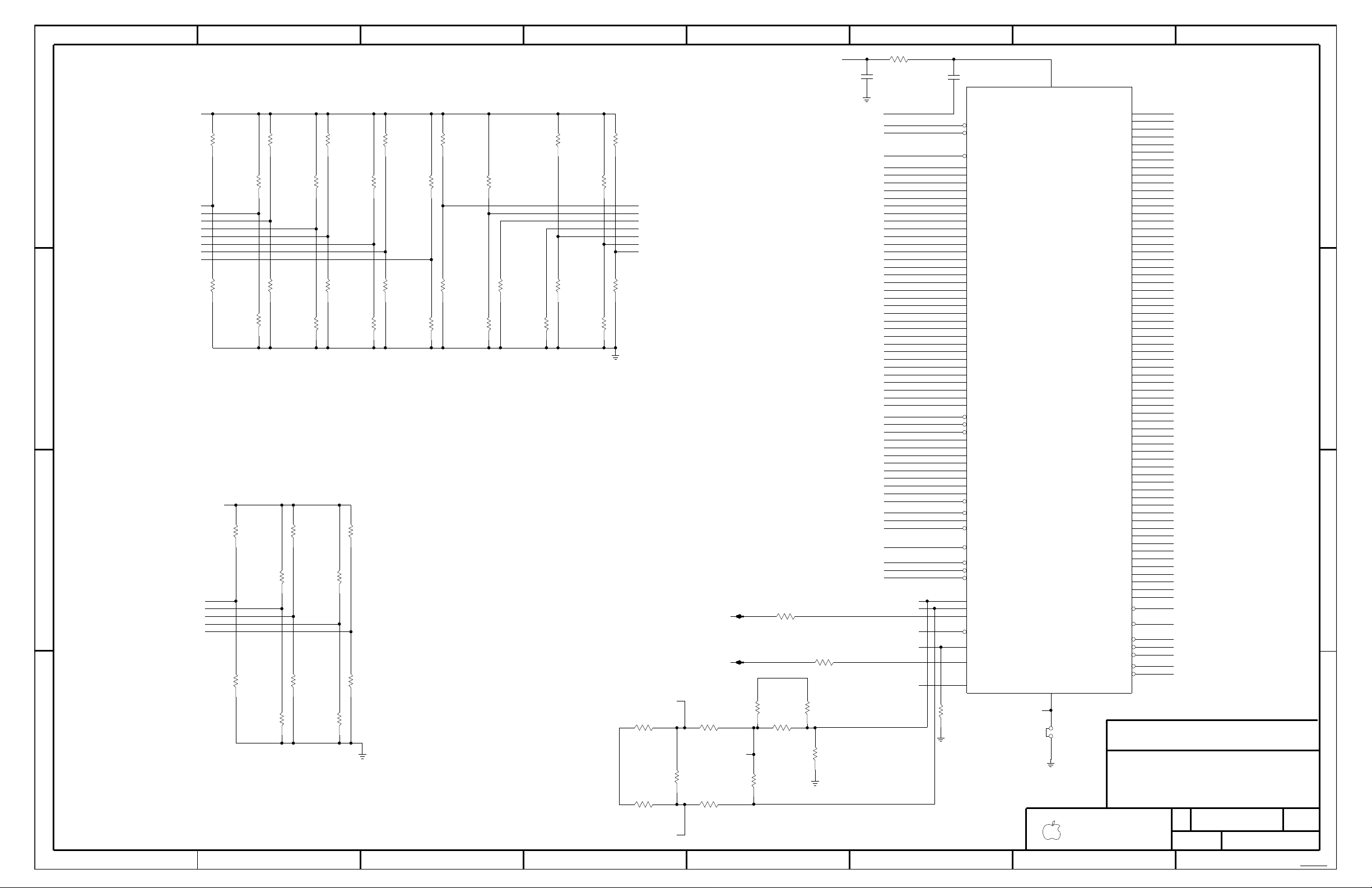

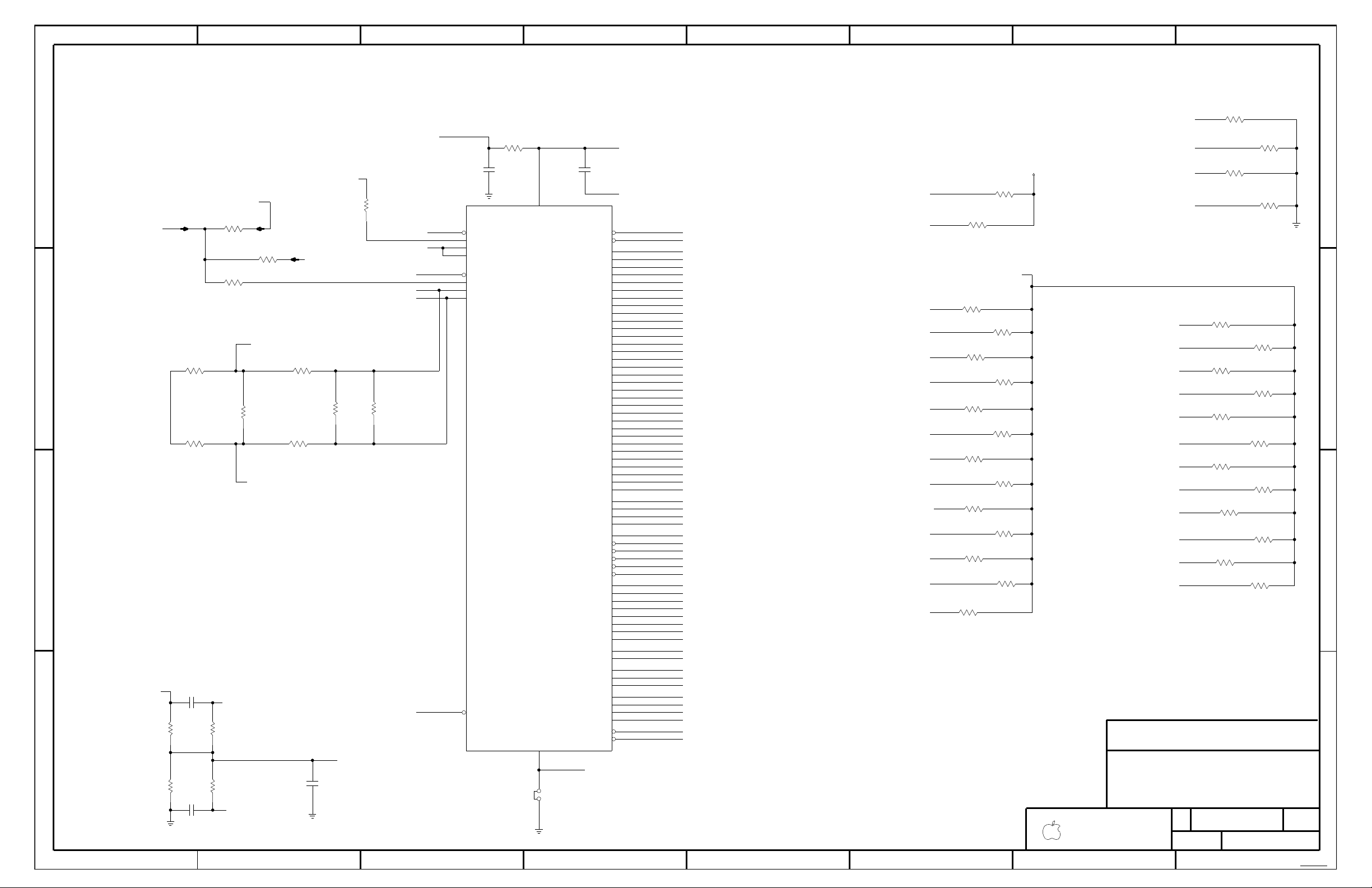

MPC7450 MAXBUS

CPU MECHANICAL PARTS SUPPORT

CPU INTERNAL PLL FILTERING

IBORG PULLS THIS UP, SPEC SAYS TO GROUND IT FOR SW CONTROL

DOWN HARD FOR SNOOPING.

CUT THE TRACE AND YANK

ALL THE TIME. NEED TO

FIXED IN INTREPID VERSION 2.

INTREPID VERSION 1 PULLS GBL

IF NECESSARY

FILTERS A WAKE FROM SLEEP GLITCH

RC GLITCH FILTER

PLACE CLOSE TO PIN

5%

1/16W

MF

402

470

NOSTUFF

402

5%

50V

CERM

10PF

5%

1/16W

MF

402

0

APOLLO_MPC7445_360

SEE_TABLE

BGA

800MHZ

NOSTUFF

402

MF

1/16W

5%

47

INT_V1

1%

1/16W

MF

402

100

INT_V2

5%

1/16W

MF

402

0

1%

1/16W

MF

603

10

275R138

275R138

402

10V

20%

CERM

0.1UF

CERM

20%

10V

402

0.1UF

CERM

20%

10V

402

0.1UF

402

10V

20%

CERM

0.1UF

TH

SL-138X272-292

TH

SL-138X272-292

CERM

20%

10V

402

0.1UF

N20P80%

16V

CERM

805

2.2UF

13

051-6497

4

69

U341

1

875-1475

PAD,THERMAL,CPU,U34

?

870-1113

1

DEVU342

HEAT SINK,CPU,Q26,U34

?

U343870-1114

1

DEV

CLIP,HEAT SINK,CPU,Q26.U34

?

U344

1

DEV

SCREW,MACH,3MM W,8MM L,U34

412-0042

?

835-0251

1

DEVU345NUT,3MM,U34

?

SYSCLK_CPU

NO_TEST

NC_CPU_CLKOUT

NO_TEST

NC_PMON_OUT_L

NO_TEST

NC_CPUAP<0>

NO_TEST

NC_CPUAP<1>

NO_TEST

NC_CPUAP<2>

NO_TEST

NC_CPUAP<3>

NO_TEST

NC_CPUAP<4>

CPU_PULLUP

CPU_PULLDOWN

CPU_PULLDOWN

+MAXBUS_SLEEP

CPU_AVDD

CPU_BUS_VSEL

CPU_PLL_CFG<0>

CPU_PLL_CFG<1>

CPU_PLL_CFG<3>

CPU_PLL_CFG<2>

CPU_DBG_L

CPU_DRDY_L_UF

CPU_PLL_CFGEXT

CPU_EDTI

CPU_DTI<0>

CPU_DTI<1>

CPU_DTI<2>

JTAG_CPU_TDI

JTAG_CPU_TDO

JTAG_CPU_TCK

JTAG_CPU_TMS

JTAG_CPU_TRST_L

CPU_LSSD_MODE

CPU_L1TSTCLK

CPU_L2TSTCLK

CPU_TA_L

CPU_TEA_L

CPU_TBEN

CPU_QACK_L

CPU_QREQ_L

CPU_CHKSTP_IN_L

CPU_CHKSTP_OUT_L

MPIC_CPU_INT_L

CPU_SMI_L

CPU_MCP_L

CPU_HRESET_L

CPU_SRESET_L

CPU_PMONIN_L

CPU_EMODE0_L

CPU_EMODE1_L

CPU_ARTRY_L

CPU_SHD0_L

CPU_HIT_L

CPU_SHD1_L

CPU_BR_L

CPU_BG_L

CPU_TS_L

CPU_ADDR<1>

CPU_ADDR<2>

CPU_ADDR<3>

CPU_ADDR<4>

CPU_ADDR<6>

CPU_ADDR<5>

CPU_ADDR<7>

CPU_ADDR<9>

CPU_ADDR<8>

CPU_ADDR<11>

CPU_ADDR<10>

CPU_ADDR<12>

CPU_ADDR<14>

CPU_ADDR<13>

CPU_ADDR<16>

CPU_ADDR<15>

CPU_ADDR<17>

CPU_ADDR<19>

CPU_ADDR<18>

CPU_ADDR<21>

CPU_ADDR<20>

CPU_ADDR<22>

CPU_ADDR<24>

CPU_ADDR<23>

CPU_ADDR<25>

CPU_ADDR<26>

CPU_ADDR<27>

CPU_ADDR<28>

CPU_ADDR<29>

CPU_ADDR<31>

CPU_ADDR<30>

CPU_TT<0>

CPU_TT<1>

CPU_TT<3>

CPU_TT<2>

CPU_TBST_L

CPU_TSIZ<0>

CPU_TSIZ<2>

CPU_TSIZ<1>

CPU_WT_L

CPU_GBL_L

CPU_CI_L

CPU_AACK_L

CPU_INT_GBL_L

ZT10P1

ZT9P1

ZT8P1

ZT11P1

CPU_DRDY_L

CPU_ADDR<0>

CPU_TT<4>

CPU_VCORE_SLEEP

CPU_VCORE_SLEEP

<XR_PAGE_TITLE>

C1036

1

2

C1035

1

2

R891

1

2

C954

1

2

R850

1 2

U34

E11

H1

D12

L3

G4

T2

F4

V1

J4

R2

K5

W2

C11

J2

K4

N4

J3

M5

P5

N3

T1

V2

U1

G3

N5

W1

B12

C4

G10

B11

F10

L2

D11

D1

C10

G2

R1

C1

E3

H6

F5

G7

N2

A8

M1

G9

F8

D2 B7

J1

A3

B1

H2

M2

R3

G1

K1

P1

N1

A11

E2

B5

H9

H11

H13

J6

J8

J10

J12

K7K3K9

C3

K11

K13

L6

L8

L10

L12

M4M7M9

M11D6M13

N7P3P9

P12R5R14

R17T7T10

D13

U3

U13

U17

V5

V8

V11

V15

E17F3G17

H4

H7

B2

D8

D4

G8

B3

E8

C9

B4

K2L5M3N6P2P8P11R4R13

R16C2T6T9U2

U12

U16V4V7

V10

V14

C12D5E18F2G18H3J5

B8

C8

C7

D7

A7

D9

A9

G5

P4

E4

H5

F9

A2

A10

K6

E1

F11

C6

B9

A4

L1

A12

B6

B10

E10

D10

F1

A5

L4

G6

F7

E7

E5

E6

F6

E9

C5

H8

K12

K14L7L9

L11

L13M8M10

M12

H10

H12J7J9

J11

J13K8K10

D3

R895

1

2

R312

1

2

R311

1 2

R901

1

2

ZH4

1

ZH7

1

C345

1

2

C370

1

2

C369

1

2

C352

1

2

ZH6

1

ZH5

1

LAST_MODIFIED=Wed Sep 17 12:15:40 2003

59C8> 52C6> 46D4<

45D2<>

44D2< 44D1< 44B7<

9D8< 9B7<

8D4< 8D1<

8A3<>

7C7<

59C8>

59D8>

59D8>

7C5<

44D2<

59B6>

59B6>

7C3<

44C2<

52C6>

52C6>

7B3<

56C3>

56C3>

56C3>

56C3>

59C8>

8A3<>

56C3>

56C3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56C3>

56C3>

56C3>

56C3>

56D3>

45D2<>

45D2<>

7A3<

9B1<>

56C3>

56C3>

56C3>

59C8>

59C8>

59C8>

59C8>

9A1<>

9A1<>

56C3>

9B3<

8D5<>

28B5>

7B3<

59C6>

9B3<>

9B3<

9D3<

9D3<>

9D3<>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

9B3<>

9B3<>

9B3<>

9B3<>

9B3<>

56D3>

56D3>

56D3>

9B3<>

9C3<>

9B3<>

56C3>

9B1<

56D3>

9B3<>

8C1<

8C1<

56C3>

7C5<

7C5<

6D6<

8A8<>

8A8<>

8A8<>

8A8<>

8B8<>

8A8<>

9A1<>

9A1<>

9A1<>

8A3<>

59C8>

8A3<>

8A3<>

8A3<>

8C4<>

8B5<>

9A3<>

9B3<>

8B7<>

59C8>

8A3<>

8D7<>

44C4<>

7A5<

8A3<>

8B8<>

8B8<>

8B4<>

8B4<>

8B7<>

9D3<>

9D3<>

9D3<>

9D3<>

9D3<>

9D3<>

9D3<>

9C3<>

9D3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

8B4<>

8B5<>

8B5<>

8B4<>

8B4<>

9B3<>

9B3<>

9B3<>

8B5<>

56C3>

8C5<>

8B5<>

9C3<>

8B5<>

9D3<>

8B4<>

8B7<

8B7<

9A4<

7A5<

4D7<>

4A3<

6C5<

52C6>

7C4<

6C6<

6C6<

6C6<

6C6<

7B7<

56C3>

6C6<

7C5<

8B7<>

8B4<>

8B4<>

7A5<

8A3<>

7D5<

7A5<

7C5<

7B5<

7B4<

7C4<

7C7<

7B7<

7C5<

8B4<>

7D5<

7B5<

7B5<

7A5<

7A5<

7B5<

7A3<

7A5<

7C5<

7A4<

7A4<

7C7<

7B5<

7C7<

7B5<

7C7<

7B7<

7C7<

8B5<>

8B4<>

8B8<>

8B5<>

8C4<>

8B7<>

8B7<>

8B8<>

8C5<>

8C4<>

8B8<>

8B7<>

8B7<>

8B8<>

8B8<>

8B7<>

8B8<>

8B7<>

8C8<>

8C7<>

8B8<>

8C7<>

8B7<>

8C8<>

8B8<>

8C8<>

8C8<>

8C7<>

8C8<>

8C7<>

8C7<>

7A7<

7A7<

7A7<

7A7<

7B7<

8B5<>

8B7<

8B5<>

7A7<

8B5<>

7A7<

7B7<

7B7<

7B7<

8B4<>

7A7<

4D3<

4D7<

Page 5

(2 OF 3)

D0

D60

D61

D62

D63

DP7

DP0

DP1

DP2

DP3

DP4

DP5

DP6

D59

D56

D57

D58

D55

D54

D53

D52

D50

D51

D49

D46

D45

D47

D48

D44

D43

D42

D41

D40

D39

D38

D37

D36

D35

D34

D33

D30

D31

D32

D29

D26

D25

D24

D23

D27

D28

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D1

D2

D3

(3 OF 3)

NC_B14

NC_B13

NC_E12

NC_B18

NC_N19

NC_K17

NC_N18

NC_N12

NC_A6

NC_C13

NC_G11

NC_A14

NC_F12

NC_A13

NC_A18

NC_C14

NC_A15

NC_B16

NC_E13

NC_F13

NC_F14

NC_G12

NC_A17

NC_C15

NC_G14

NC_H14

NC_E14

NC_G13

NC_C16

NC_C17

NC_B17

NC_B15

NC_E15

NC_D14

NC_A19

NC_B19

NC_A16

NC_C18

NC_G15

NC_D15

NC_C19

NC_K16

NC_J17

NC_K18

NC_L18

NC_L19

NC_M18

NC_P16

NC_L16

NC_H15

NC_J16

NC_K19

NC_J15

NC_J19

NC_J18

NC_J14

NC_K15

NC_L14

NC_L17

NC_M15

NC_N17

NC_P19

NC_M16

NC_M19

NC_N16

NC_N13

NC_M17

NC_M14

NC_N14

NC_P18

NC_N15

NC_D19

NC_F15

NC_G19

NC_E16

NC_D17

NC_D16

NC_P15

NC_L15

NC_H19

NC_H18

NC_H17

NC_H16

NC_E19

NC_D18

NC_F16

NC_G16

NC_F19

NC_F17

NC_F18

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DRAWING

MPC7450 - 2

BGA

APOLLO_MPC7445_360

800MHZ

APOLLO_MPC7445_360

BGA

800MHZ

5

69

051-6497

13

NO_TEST

NC_CPUCRUD<0>

NO_TEST

NC_CPUCRUD<1>

NO_TEST

NC_CPUCRUD<2>

NO_TEST

NC_CPUCRUD<3>

NC_CPUCRUD<7>

NO_TEST

NO_TEST

NC_CPUCRUD<15>

NO_TEST

NC_CPUCRUD<16>

NO_TEST

NC_CPUCRUD<18>

NC_CPUCRUD<20>

NO_TEST

NO_TEST

NC_CPUCRUD<21>

NO_TEST

NC_CPUCRUD<22>

NO_TEST

NC_CPUCRUD<23>

NO_TEST

NC_CPUCRUD<25>

NO_TEST

NC_CPUCRUD<26>

NO_TEST

NC_CPUCRUD<27>

NO_TEST

NC_CPUCRUD<28>

NO_TEST

NC_CPUCRUD<29>

NO_TEST

NC_CPUCRUD<31>

NO_TEST

NC_CPUCRUD<32>

NO_TEST

NC_CPUCRUD<33>

NO_TEST

NC_CPUCRUD<37>

NO_TEST

NC_CPUCRUD<38>

NO_TEST

NC_CPUCRUD<40>

NO_TEST

NC_CPUCRUD<41>

NO_TEST

NC_CPUCRUD<42>

NO_TEST

NC_CPUCRUD<44>

NO_TEST

NC_CPUCRUD<45>

NO_TEST

NC_CPUCRUD<46>

NO_TEST

NC_CPUCRUD<47>

NO_TEST

NC_CPUCRUD<48>

NO_TEST

NC_CPUCRUD<49>

NC_CPUCRUD<50>

NO_TEST

NO_TEST

NC_CPUCRUD<51>

NO_TEST

NC_CPUCRUD<52>

NO_TEST

NC_CPUCRUD<53>

NO_TEST

NC_CPUCRUD<55>

NO_TEST

NC_CPUCRUD<56>

NO_TEST

NC_CPUCRUD<58>

NC_CPUCRUD<60>

NO_TEST

NO_TEST

NC_CPUCRUD<61>

NO_TEST

NC_CPUCRUD<62>

NO_TEST

NC_CPUCRUD<63>

NC_CPUCRUD<64>

NO_TEST

NO_TEST

NC_CPUCRUD<65>

NO_TEST

NC_CPUCRUD<66>

NO_TEST

NC_CPUCRUD<67>

NC_CPUCRUD<68>

NO_TEST

NO_TEST

NC_CPUCRUD<69>

NO_TEST

NC_CPUCRUD<70>

NC_CPUCRUD<71>

NO_TEST

NO_TEST

NC_CPUCRUD<74>

NO_TEST

NC_CPUCRUD<75>

NC_CPUCRUD<76>

NO_TEST

NO_TEST

NC_CPUCRUD<77>

NO_TEST

NC_CPUCRUD<78>

NC_CPUCRUD<79>

NO_TEST

NO_TEST

NC_CPUCRUD<80>

NC_CPUCRUD<81>

NO_TEST

NO_TEST

NC_CPUCRUD<85>

NC_CPUCRUD<86>

NO_TEST

NO_TEST

NC_CPUDP<0>

NO_TEST

NC_CPUDP<1>

NO_TEST

NC_CPUDP<2>

NO_TEST

NC_CPUDP<3>

NO_TEST

NC_CPUDP<4>

NO_TEST

NC_CPUDP<5>

NO_TEST

NC_CPUDP<6>

NO_TEST

NC_CPUDP<7>

CPU_DATA<63>

CPU_DATA<62>

CPU_DATA<61>

CPU_DATA<60>

CPU_DATA<59>

CPU_DATA<58>

CPU_DATA<57>

CPU_DATA<56>

CPU_DATA<55>

CPU_DATA<53>

CPU_DATA<54>

CPU_DATA<52>

CPU_DATA<51>

CPU_DATA<50>

CPU_DATA<49>

CPU_DATA<48>

CPU_DATA<46>

CPU_DATA<47>

CPU_DATA<45>

CPU_DATA<44>

CPU_DATA<43>

CPU_DATA<41>

CPU_DATA<42>

CPU_DATA<40>

CPU_DATA<38>

CPU_DATA<39>

CPU_DATA<36>

CPU_DATA<37>

CPU_DATA<35>

CPU_DATA<33>

CPU_DATA<34>

CPU_DATA<32>

CPU_DATA<31>

CPU_DATA<30>

CPU_DATA<29>

CPU_DATA<28>

CPU_DATA<27>

CPU_DATA<26>

CPU_DATA<25>

CPU_DATA<24>

CPU_DATA<23>

CPU_DATA<22>

CPU_DATA<21>

CPU_DATA<20>

CPU_DATA<19>

CPU_DATA<18>

CPU_DATA<17>

CPU_DATA<16>

CPU_DATA<15>

CPU_DATA<14>

CPU_DATA<13>

CPU_DATA<12>

CPU_DATA<11>

CPU_DATA<10>

CPU_DATA<9>

CPU_DATA<7>

CPU_DATA<8>

CPU_DATA<5>

CPU_DATA<6>

CPU_DATA<4>

CPU_DATA<3>

CPU_DATA<2>

CPU_DATA<1>

CPU_DATA<0>

NO_TEST

NC_CPUCRUD<36>

NO_TEST

NC_CPUCRUD<34>

NO_TEST

NC_CPUCRUD<30>

NO_TEST

NC_CPUCRUD<24>

NO_TEST

NC_CPUCRUD<9>

NO_TEST

NC_CPUCRUD<8>

NO_TEST

NC_CPUCRUD<17>

NC_CPUCRUD<10>

NO_TEST

NO_TEST

NC_CPUCRUD<6>

NC_CPUCRUD<14>

NO_TEST

NO_TEST

NC_CPUCRUD<12>

NO_TEST

NC_CPUCRUD<5>

NO_TEST

NC_CPUCRUD<11>

NO_TEST

NC_CPUCRUD<4>

NO_TEST

NC_CPUCRUD<13>

NC_CPUCRUD<19>

NO_TEST

NO_TEST

NC_CPUCRUD<35>

NO_TEST

NC_CPUCRUD<39>

NO_TEST

NC_CPUCRUD<43>

NO_TEST

NC_CPUCRUD<54>

NO_TEST

NC_CPUCRUD<57>

NC_CPUCRUD<59>

NO_TEST

NC_CPUCRUD<72>

NO_TEST

NC_CPUCRUD<73>

NO_TEST

NC_CPUCRUD<82>

NO_TEST

NC_CPUCRUD<84>

NO_TEST

NC_CPUCRUD<87>

NO_TEST

NC_CPUCRUD<89>

NO_TEST

NC_CPUCRUD<88>

NO_TEST

NO_TEST

NC_CPUCRUD<83>

<XR_PAGE_TITLE>

U34

R15

W15

T13

P13

U14

W14

R12

T12

W12

V12

N11

N10

T14

R11

U11

W11

T11

R10

N9

P10

U10

R9

W10

V16

U9

V9

W5

U6

T5

U5

W7

R6

P7

V6

W16

P17

R19

V18

R18

V19

T19

U19

W19

U18

W17

T15

W18

T16

T18

T17

W3

V17

U4

U8

U7

R7

U15

P6

R8

W8

T8

P14

V13

W13

T3

W4

T4

W9

M6

V3

N8

W6

U34

A13

A14

A15

A16

A17

A18

A19

A6

B13

B14

B15

B16

B17

B18

B19

C13

C14

C15

C16

C17

C18

C19

D14

D15

D16

D17

D18

D19

E12

E13

E14

E15

E16

E19

F12

F13

F14

F15

F16

F17

F18

F19

G11

G12

G13

G14

G15

G16

G19

H14

H15

H16

H17

H18

H19

J14

J15

J16

J17

J18

J19

K15

K16

K17

K18

K19

L14

L15

L16

L17

L18

L19

M14

M15

M16

M17

M18

M19

N12

N13

N14

N15

N16

N17

N18

N19

P15

P16

P18

P19

LAST_MODIFIED=Wed Sep 17 12:15:41 2003

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

9C5<

9C5<

9C5<

9D5<

9D5<

9D5<

9D5<

56D3>

9C8<

9C8<

9C8<

9C8<

9D8<

9D8<

9D8<

9D8<

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9C1<>

9B1<>

9C1<>

56D3>

56D3>

9C1<>

56D3>

9C1<>

9C1<>

9C1<>

9C1<>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

9B1<>

8C4<>

8C7<

8C7<>

8C8<>

8C4<

8C4<>

8C5<>

8D7<>

9C1<>

9C1<>

9A7<

9C1<>

9B7<

9B7<

9B7<

9B7<

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

9D1<>

8D5<>

8D4<>

8D4<>

8D8<>

8D8<>

8D4<>

8D5<>

8D8<>

8C5<>

8C7<>

8D7<>

8C5<>

8C8<>

8C8<>

8C4<>

8C5<>

6C4<

6C4<

6C4<

6C4<

6C4<

6C4<

6C4<

6C4<

8D5<>

8D5<>

8D4<>

8D5<>

8D7<>

8D8<>

8D8<>

8D7<>

8D7<>

8C5<>

8C8<>

8D8<>

8C7<>

8C5<>

8D7<>

8D4<>

8C8<>

8C7<>

8C8<>

8C4<>

8C4<>

8C4<>

8C7<>

8C4<>

8C5<>

8C8<>

8C7<>

8C5<>

8C5<>

8C7<>

8C4<>

8C8<>

8C5<>

8C8<>

8C4<>

8C7<>

8C5<>

8C8<>

8C7<>

8C4<>

Page 6

DRAWING

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DESCRIPTION REFERENCE DES BOM OPTIONQTYPART NUMBER CRITICAL

BOMOPTIONS FOR UPPER-SET OF RESISTORS

12.0X

(STUFF FOR 133 AND 167)

(STUFF FOR 133 AND 167)

000: 166.4 MHZ

010: 133.12 MHZ

011: 99.84 MHZ

100: 83.20 MHZ

INTREPID BOOT STRAPS

BITS 40 - 47

(SUPPORTED CPU & BUS SPEEDS)

CPU FREQUENCY CONFIGURATION

PCI0 SOURCE CLOCK

0: PLL4

1: PLL5 (NO SPREAD)

0: PLL4

1: PLL5 (NO SPREAD)

PCI1 SOURCE CLOCK

1: ACTIVE

0: INACTIVE

INTERNALSPREADEN

001: 149.76 MHZ

PLL4MODESEL_NXT[2:0]

SPARE

SPARE

CPU BUS RATIO BITS

CPU_PLL_CFG

133MHZ

(AT BUS FREQUENCY)

CORE FREQUENCY

167MHZ

MULTIPLIER

1 1001 19

1 0001 11

1 1101 1D

1 1100 1C

1 0101 15

1 1011 1B

E 0123 HEX

1 0111 17

0 0101 05

0 1101 0D

0 1001 09

0 1100 0C

1 1010 1A

0 0001 01

0 0010 02

0 1011 0B

1000

1067

933

867

1200

733

800

1333

667

(MHZ)

1333

1250

833

917

1000

1667

1083

1500

1167

1467

1600

2000

1733

1867

2133

2000

1833

2167

2333

2500

2667

(BUS-TO-CORE)

6.5X

6.0X

5.5X

5.0X

8.0X

10.0X

9.0X

7.5X

7.0X

15.0X

13.0X

14.0X

11.0X

16.0X

ARE AUTOMATICALLY SELECTED

WHEN THE ENGINEER SELECTS THE APPROPRIATE CPU AND

BUS SPEED BOM OPTION, THE APPROPRIATE RESISTORS ARE

THE CONFIGURATION RESISTORS BELOW ARE SELF CONFIGURING

CPU SPEED & BUS RATIO SUPPORT

667@133&833@167&733@133&917@167&800@133&1000@167&1067@133&1333@167&1333@133&1667@167&1467@133&1833@167&1600@133&2000@167&1867@133&2333@167&2133@133&2667@167

10K

402

1/16W

MF

1%

SPECIAL CONFIG

1K

MF

1/16W

402

SPECIAL CONFIG

1%

667@133&833@167&733@133&917@167&800@133&1000@167&867@133&1083@167&933@133&1167@167&1000@133&1250@167&1067@133&1333@167

10K

1/16W

MF

402

1%

NOSTUFF

10K

402

MF

1/16W

1%

NOSTUFF

4.7K

5%

MF

402

1/16W

10K

MF

402

1/16W

1%

NOSTUFF

10K

1%

402

1/16W

MF

667@133&733@133&800@133&867@133&933@133&1000@133&1067@133&1200@133&1333@133&1467@133&1600@133&1733@133&1867@133&2000@133&2133@133

10K

402

MF

1/16W

1%

NOSTUFF

4.7K

1/16W

5%

MF

402

10K

1/16W

MF

402

1%

NOSTUFF

4.7K

402

MF

1/16W

5%

833@167&917@167&1000@167&1083@167&1167@167&1250@167&1333@167&1500@167&1667@167&1833@167&2000@167&2167@167&2333@167&2500@167&2667@167

867@133&1083@167&933@133&1167@167&1000@133&1250@167&1200@133&1500@167&1733@133&2167@167&2000@133&2500@167

1K

402

1/16W

MF

SPECIAL CONFIG

1%

10K

NOSTUFF

1%

MF

1/16W

402

10K

NOSTUFF

1%

1/16W

MF

402

4.7K

402

MF

5%

1/16W

4.7K

5%

1/16W

MF

402

4.7K

402

MF

1/16W

5%

4.7K

402

MF

1/16W

5%

4.7K

MF

5%

402

1/16W

800@133&1000@167&867@133&1083@167&1067@133&1333@167&1200@133&1500@167&1733@133&2167@167&1867@133&2333@167&2133@133&2667@167

MF

10K

SPECIAL CONFIG

1%

1/16W

402

10K

SPECIAL CONFIG

1%

402

1/16W

MF

667@133&833@167&933@133&1167@167&1200@133&1500@167&1333@133&1667@167&1600@133&2000@167

667@133&833@167&733@133&917@167&933@133&1167@167&1000@133&1250@167&1333@133&1667@167&1467@133&1833@167&1600@133&2000@167&2000@133&2500@167

1K

402

1/16W

MF

SPECIAL CONFIG

1%

733@133&917@167&800@133&1000@167&867@133&1083@167&1000@133&1250@167&1067@133&1333@167&1467@133&1833@167&1733@133&2167@167&1867@133&2333@167&2000@133&2500@167&2133@133&2667@167

1K

MF

1/16W

402

SPECIAL CONFIG

1%

10K

402

1/16W

MF

1%

667@133&833@167&733@133&917@167&800@133&1000@167&867@133&1083@167&1000@133&1250@167&1200@133&1500@167&1467@133&1833@167&1600@133&2000@167&1733@133&2167@167&2000@133&2500@167&2133@133&2667@167

SPECIAL CONFIG

1K

933@133&1167@167&1067@133&1333@167&1333@133&1667@167&1867@133&2333@167

402

1/16W

MF

SPECIAL CONFIG

1%

10K

MF

1/16W

402

1%

SPECIAL CONFIG

1200@133&1500@167&1333@133&1667@167&1467@133&1833@167&1600@133&2000@167&1733@133&2167@167&1867@133&2333@167&2000@133&2500@167&2133@133&2667@167

13

051-6497

69

6

IC,APOLLO6,SICOH,1.0GHZ,1.5V+30/-130MV,28W,85C

1

1000@167CRITICALU34337S2799

1

IC,APOLLO6,SICOH,1.25GHZ,1.57V+70/-70MV,35W,85C

1250@167CRITICALU34337S2801

CPU_PLL_CFGEXT

CPU_PLL_CFG<1>

CPU_DATA<42>

CPU_DATA<43>

CPU_DATA<44>

CPU_DATA<46>

CPU_DATA<41>

CPU_DATA<45>

CPU_DATA<47>

+MAXBUS_SLEEP

CPU_DATA<40>

+MAXBUS_SLEEP

CPU_PLL_CFG<3>

CPU_PLL_CFG<2>

CPU_PLL_CFG<0>

CPU_PLL_STOP

<XR_PAGE_TITLE>

R379

1

2

R381

1

2

R378

1

2

R376

1

2

R380

1

2

R377

1

2

R374

1

2

R375

1

2

R382

1

2

R383

1

2

R867

1

2

R875

1

2

R356

1

2

R877

1

2

R866

1

2

R874

1

2

R365

1

2

R889

1

2

R357

1

2

R878

1

2

R879

1

2

R364

1

2

R367

1

2

R368

1

2

R887

1

2

R363

1

2

LAST_MODIFIED=Wed Sep 17 12:15:42 2003

59C8>

59C8>

52C6>

52C6>

46D4<

46D4<

45D2<>

45D2<>

44D2<

44D2<

44D1<

44D1<

44B7<

44B7<

9D8<

9D8<

9B7<

9B7<

8D4<

8D4<

8D1<

8D1<

8A3<>

8A3<>

7C7<

7C7<

7C5<

7C5<

7C3<

7C3<

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

7B3<

56D3>

7B3<

9B1<>

9B1<>

9B1<>

9B1<>

9C1<>

9B1<>

9B1<>

7A3<

9C1<>

7A3<

8A8<>

8A8<>

8C5<>

8C4<

8C8<>

8C4<>

8C4<>

8C7<>

8C7<

6C5<

8D7<>

6D6<

8A8<>

8A8<>

8A8<>

4C3<

4D3<

5B4<>

5B4<>

5B4<>

5B4<>

5B4<>

5B4<>

5B4<>

4D5<

5B4<>

4D5<

4C3<

4D3<

4D3<

44B8<

Page 7

DRAWING

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DO NOT USE UNLESS FIX INVERTER BUFFER

BUS MODE

OVDD 2.5V BUS MODE

INV_HRESET 1.5V BUS MODE

0V 1.8V BUS MODE

!hr L | 0 1 | MB+ | 01 | yes unavail

!hr hr | 0 1 | MB+ | 00 | yes unavail

---------+---------+-----+------+------

L H | 1 0 | Max | 00 | yes unavail

<- DEFAULT

L hr | 1 1 | ??? | 00 | yes unavail

H hr | 0 1 | MB+ | 00 | norm unavail

H L | 0 1 | MB+ | 01 | norm unavail

hr hr | 1 1 | ??? | 00 | norm unavail

hr L | 1 1 | ??? | 01 | norm unavail

!hr H | 0 0 | 60x | 00 | yes unavail

!hr !hr | 0 0 | 60x | 01 | yes unavail

L L | 1 1 | ??? | 01 | yes unavail

L !hr | 1 0 | Max | 01 | yes unavail

---------+---------+-----+------+------

BMODE | MSSCR0 | Sys | Vger | Addr

<0> <1> | <16:17> | Bus | ID | Drve

=========+=========+=====+======+======

hr !hr | 1 0 | Max | 01 | norm

H H | 0 0 | 60x | 00 | norm

H !hr | 0 0 | 60x | 01 | norm

---------+---------+-----+------+------

HR H | 1 0 | MAX | 00 | NORM

MAXBUS PULL-UPS

MPC7450 PULL-UPS

CPU_HRESET_H

CPU_L3_VSEL LOW

SIGNAL

CPU_BUS_VSEL

CPU_EMODE0_L

CPU_HRESET_L

CPU_HRESET_L

CPU_HRESET_H

TIED

HIGH

LOW

CPU_HRESET_L or L3_OVDD

1.5V INTERFACE

1.8V INTERFACE

MAX BUS MODE

2.5V INTERFACE

60X BUS MODE

APPLICATION

2.5V INTERFACE

1.5V INTERFACE

1.8V INTERFACE

CPU CONFIG OPTIONS

10K

1/16W

MF

402

1%

1%

1/16W

MF

402

10K

1%

1/16W

MF

402

10K

1%

402

MF

1/16W

10K

1/16W

NOSTUFF

1K

402

MF

1%

402

MF

1K

1/16W

1%

1%

1/16W

MF

402

10K

402

MF

1/16W

1K

1%

5%

SM1

1/16W

10K

5%

1/16W

10K

SM1

1%

402

MF

1/16W

10K

SM1

1/16W

5%

10K

1%

1/16W

MF

402

10K

10K

402

MF

1/16W

1%

10K

1/16W

MF

402

1%

10K

MF

1/16W

402

1%

10K

1/16W

MF

402

1%

10K

402

MF

1/16W

1%

10K

1/16W

MF

402

1%

10K

402

MF

1/16W

1%

10K

1/16W

MF

402

1%

402

MF

1/16W

5%

200

10K

1/16W

MF

402

1%

10K

1/16W

MF

402

1%

10K

402

MF

1/16W

1%

10K

402

MF

1/16W

1%

10K

1/16W

SM1

5%

10K

SM1

5%

1/16W

10K

1/16W

MF

402

1%

10K

5%

1/16W

SM1

10K

1/16W

MF

402

1%

10K

SM1

1/16W

5%

10K

1/16W

MF

402

1%

10K

402

MF

1/16W

1%

5%

1/16W

MF

402

NOSTUFF

10K

402

MF

1/16W

10K

1%

402

MF

1/16W

5%

NOSTUFF

0

402

MF

1/16W

5%

NOSTUFF

10K

MF

1/16W

5%

402

NOSTUFF

0

1/16W

MF

402

5%

CPUBUS_60X

1K

SM1

10K

5%

1/16W

402

MF

1/16W

1K

1%

5%

1/16W

MF

402

NOSTUFF

0

402

MF

1/16W

5%

200

5%

MF

NOSTUFF

0

402

1/16W

5%

1/16W

MF

402

NOSTUFF

200

MF

1/16W

5%

402

NOSTUFF

0

402

MF

1/16W

5%

200

402

MF

1/16W

5%

CPUBUS_MAX

200

5%

1/16W

MF

402

NOSTUFF

200

10K

402

MF

1/16W

1%

402

MF

1/16W

5%

470

1/16W

MF

402

10K

1%

1%

1/16W

MF

402

10K

13

051-6497

69

7

CPU_EMODE1_L

CPU_CHKSTP_IN_L

JTAG_CPU_TMS

JTAG_CPU_TDI

CPU_SMI_L

CPU_PULLUP

CPU_SRESET_L

MPIC_CPU_INT_L

CPU_HRESET_L

CPU_CHKSTP_OUT_L

CPU_MCP_L

CPU_LSSD_MODE

CPU_SHD1_L

CPU_SHD0_L

CPU_TBEN

+MAXBUS_SLEEP

VGER_INV_HRESET

+MAXBUS_SLEEP

CPU_HRESET_L

+MAXBUS_SLEEP

VGER_INV_HRESET

CPU_HRESET_L

+MAXBUS_SLEEP

VGER_INV_HRESET

CPU_HRESET_L

+MAXBUS_SLEEP

+MAXBUS_SLEEP

VGER_INV_HRESET

CPU_EMODE0_L

CPU_L1TSTCLK

CPU_L2TSTCLK

CPU_BUS_VSEL

+MAXBUS_SLEEP

CPU_TS_L

CPU_TA_L

CPU_BR_L

CPU_ARTRY_L

CPU_DRDY_L

CPU_HIT_L

CPU_TEA_L

CPU_AACK_L

CPU_DBG_L

CPU_BG_L

CPU_INT_GBL_L

CPU_TBST_L

CPU_WT_L

CPU_TT<0>

CPU_CI_L

CPU_TT<1>

CPU_TT<2>

CPU_TT<3>

CPU_TT<4>

CPU_QREQ_L

JTAG_CPU_TRST_L

JTAG_CPU_TCK

CPU_EDTI

CPU_PULLDOWN

CPU_PMONIN_L

<XR_PAGE_TITLE>

R848

1 2

R925

1 2

R924

1 2

RP79

4 5

R858

1 2

R859

1 2

R856

1 2

R860

1 2

R857

1 2

R910

1 2

R911

1 2

R921

1 2

R882

1 2

R922

1 2

R909

1 2

RP79

2 7

RP79

3 6

R912

1 2

RP79

1 8

R923

1 2

R347

1 2

R348

1 2

R841

1 2

R346

1 2

R851

1 2

R840

1 2

R845

1 2

R849

1 2

R847

1 2

R846

1 2

R842

1 2

R349

1 2

RP78

2 7

RP78

1 8

R844

1 2

RP78

3 6

R843

1 2

RP78

4 5

R350

1 2

R913

1 2

R918

1 2

R919

1 2

R907

1 2

R916

1 2

R904

1 2

R903

1 2

R915

1 2

R914

1 2

R926

1 2

R920

1 2

R906

1 2

R917

1 2

R905

1 2

R902

1 2

LAST_MODIFIED=Wed Sep 17 12:15:43 2003

59C8>

59C8>

59C8>

59C8>

59C8>

52C6>

52C6>

59C8>

52C6>

52C6>

59C8>

52C6>

46D4<

46D4<

52C6>

46D4<

46D4<

52C6>

46D4<

45D2<>

45D2<>

46D4<

45D2<>

45D2<>

46D4<

45D2<>

44D2<

44D2<

45D2<>

44D2<

44D2<

45D2<>

44D2<

44D1<

44D1<

44D2<

44D1<

44D1<

44D2<

44D1<

44B7<

44B7<

44D1<

44B7<

44B7<

44D1<

44B7<

9D8<

9D8<

44B7<

9D8<

9D8<

44B7<

9D8<

9B7<

9B7<

9D8<

9B7<

9B7<

9D8<

9B7<

8D4<

8D4<

9B7<

8D4<

8D4<

9B7<

8D4<

8D1<

8D1<

8D4<

8D1<

8D1<

8D4<

8D1<

8A3<>

8A3<>

8D1<

8A3<>

8A3<>

8D1<

8A3<>

7C7<

7C7<

59C8>

8A3<>

59C8>

7C7<

7C7<

8A3<>

59C8>

7C7<

7C5<

59C8>

7C5<

44D2<

7C7<

44D2<

7C5<

7C5<

7C5<

44D2<

7C3<

7C3<

44D2<

7C3<

44C2<

7C5<

44C2<

7C3<

7C3<

7C3<

44C2<

7B3<

7B3<

44C2<

7B3<

8A3<>

7C3<

8A3<>

7B3<

7B3<

7B3<

8A3<>

59C8>

7A3<

7A3<

8A3<>

7A3<

44D1>

7B3<

7A3<

44D1>

7B3<

7A3<

7A3<

7A3<

56D3>

56C3>

56D3>

56C3>

56C3>

56C3>

56C3>

56C3>

56C3>

56D3>

56D3>

56C3>

56D3>

56C3>

56D3>

56D3>

56D3>

56D3>

56C3>

59C8>

59C8>

59C6>

28B5>

7B3<

8D5<>

6D6<

44D1>

6D6<

7B3<

6D6<

7C3<

7A5<

6D6<

7C3<

7A5<

6D6<

6D6<

44D1>

6D6<

9D3<>

9A1<>

9D3<

9B3<>

9B1<

9B3<

9A1<>

9B3<>

9B1<>

9D3<>

56C3>

9B3<>

9B3<>

9B3<>

9C3<>

9B3<>

9B3<>

9B3<>

9B3<>

9B3<

59C8>

59C8>

59C8>

8A3<>

8A3<>

44C4<>

8A3<>

8D7<>

7A3<

8A3<>

9A3<>

6C5<

7C3<

6C5<

7A5<

6C5<

7B3<

7A3<

6C5<

7B3<

7A3<

6C5<

6C5<

7B3<

6C5<

8B7<>

8C4<>

8B4<>

8B8<>

8B5<>

8B8<>

8B5<>

8B5<>

8B8<>

8B4<>

9C3<>

8B4<>

8B5<>

8B4<>

8C5<>

8B5<>

8B4<>

8B5<>

8B4<>

8B7<>

8A3<>

8A3<>

4D7<>

4B3<

4B3<

4C3<

4C3<

4B3<

4A3<

4B3<

4B3<

4B3<

4B3>

4B3<

4C3<

4A7<>

4A7<>

4C3<

4D5<

7B3<

4D5<

4B3<

4D5<

7A3<

4B3<

4D5<

7A3<

4B3<

4D5<

4D5<

7A3<

4B3<

4C3<

4C3<

4D3<

4D5<

4D7<>

4C3<

4D7>

4A7<>

4C2<

4A7>

4C3<

4A7<

4C3<

4D7<

4B8<

4B7>

4B7>

4B7<>

4A7>

4B7<>

4B7<>

4B7<>

4B7<>

4C3>

4C3<

4C3<

4C3<

4A3<

4B3<

Page 8

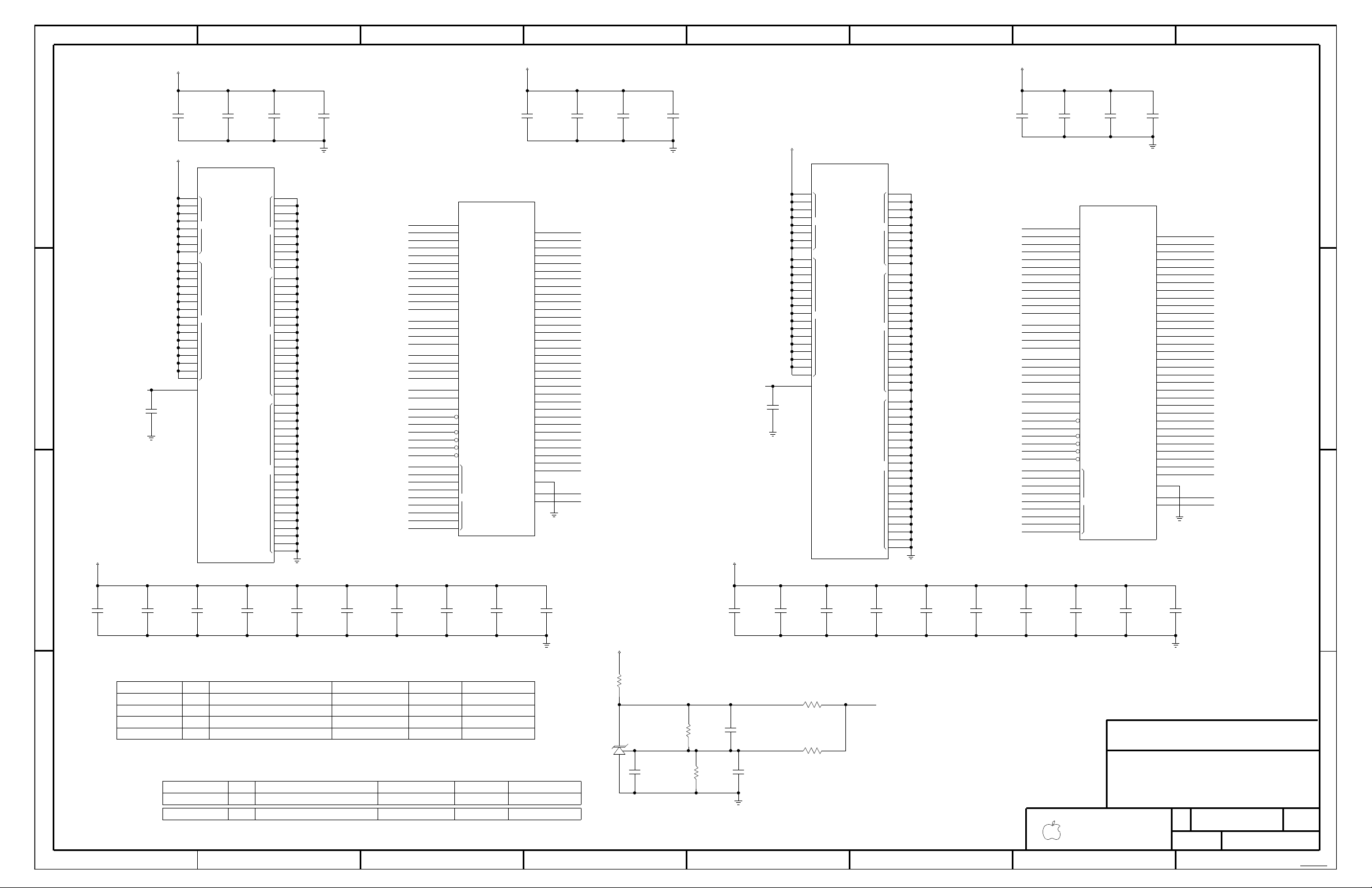

E0_0

E0_1

E0_2

E0_3

E0_4

E0_5

E0_6

E0_7

E1_0

E1_1

E1_2

E1_3

E1_4

E1_5

E1_6

E1_7

Q2

EPROBE

SYM_VER5

E2_0

E2_1

E2_2

E2_3

E2_4

E2_5

E2_6

E2_7

E3_0

E3_1

E3_2

E3_3

E3_4

E3_5

E3_6

E3_7

Q3

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

SYM_VER3

CPROBE

CLK3

C3_7

C3_6

C3_5

C3_4

C3_3

C3_2

C3_1

C3_0

C2_7

C2_6

C2_5

C2_4

C2_3

C2_2

C2_1

C2_0

Q1

C1_7

C1_6

C1_5

C1_4

C1_3

C1_2

C1_1

C1_0

C0_7

C0_6

C0_5

C0_4

C0_3

C0_2

C0_1

C0_0

A3_6

A3_7

CLK0

GND

A3_1

A3_2

A3_3

A3_4

A3_5

A3_0

A2_7

A2_6

A2_5

A2_4

A2_3

A2_2

GND

A2_0

GND

GND

CLK1

A1_7

A1_6

A1_5

A1_4

A1_3

A1_2

A1_1

A1_0

A0_7

A0_6

A0_5

A0_4

A0_3

A0_1

A0_0

GND

APROBE

SYM_VER2

A0_2

A2_1

SYM_VER1

GND

GND

GND

GND

Q0

D3_7

D3_6

D3_5

D3_4

D3_3

D3_2

D3_1

D3_0

D2_7

D2_6

D2_5

D2_4

D2_3

D2_2

D2_1

D2_0

CLK2

D1_7

D1_6

D1_5

D1_4

D1_3

D1_2

D1_1

D1_0

D0_7

D0_6

D0_5

D0_4

D0_3

D0_2

D0_1

D0_0

DPROBE

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_5_ITEM

DRAWING

TABLE_5_ITEM

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

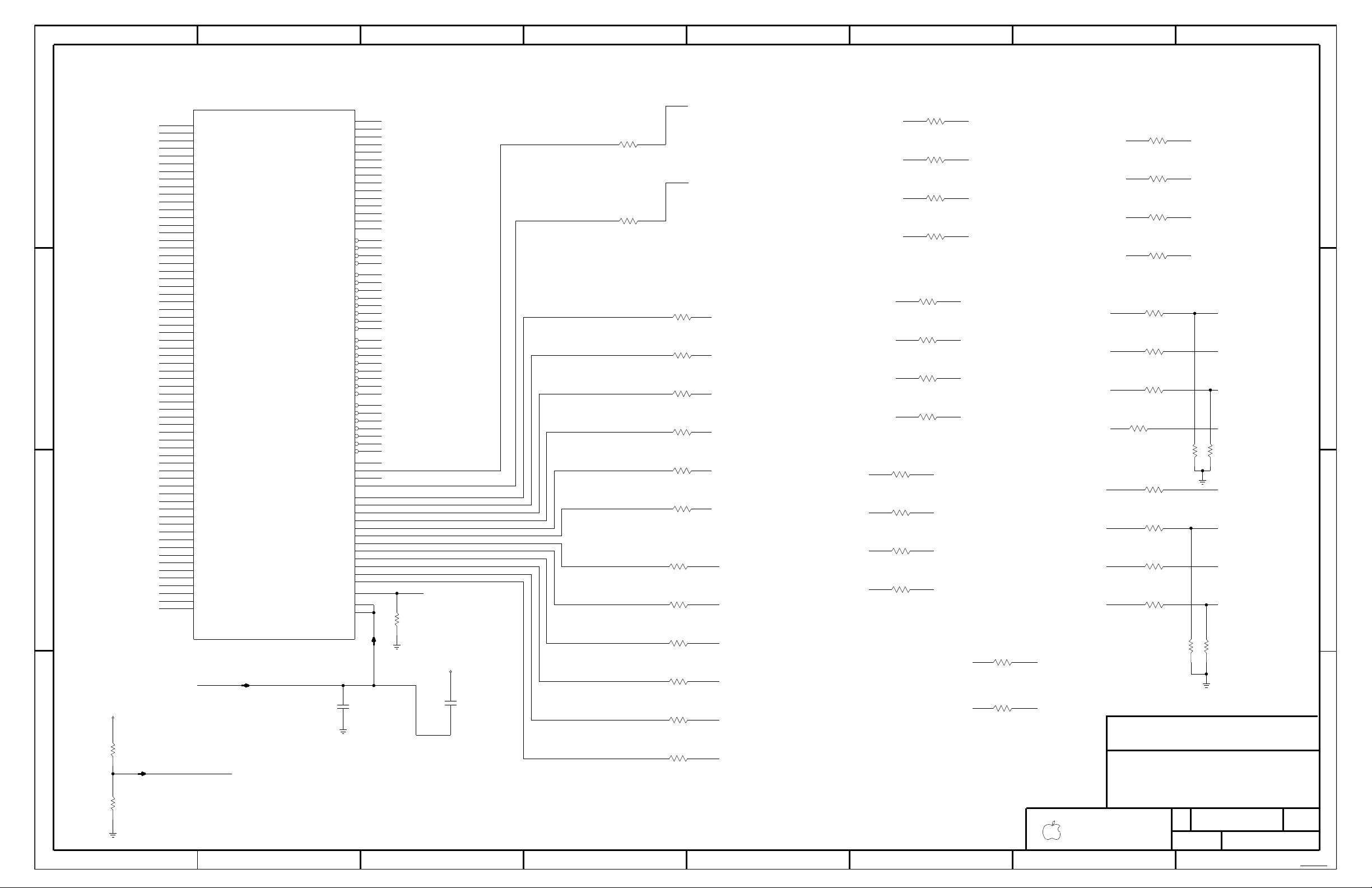

PULLDOWN ON TRST* STRONGER TO OVERCOME POSSIBLE LEAKAGE

CPU CORE DECOUPLING

MAXBUS LOGIC ANALYZER SUPPORT

TO 1K OR LOGIC ANALYZER MAY AFFECT STRAP VALUES

NOTE: INTREPID MAXBUS CONFIG STRAPS MUST DROP

(519-0698)

CLOSE TO INTREPID

PLACE BOTH RESISTORS

INTREPID CLOCK OUTPUT

(518S0104)

(511S0018)

(518S0105)

LA CONS & ESP

FMAX DEBUG CONNECTOR

CPU CORE DECOUPLING

1%

1K

402

MF

1/16W

10K

MF

402

1/16W

1% SM-1

NOSTUFF

CERM

10%

402

6.3V

1UF

SEE_TABLE

10%

CERM

402

1UF

SEE_TABLE

6.3V

10%

CERM

402

6.3V

1UF

SEE_TABLE

6.3V

10%

CERM

402

1UF

SEE_TABLE

10%

402

CERM

6.3V

1UF

SEE_TABLE

6.3V

10%

402

CERM

1UF

SEE_TABLE

0.1UF

CERM

10V

20%

402

0.1UF

CERM

10V

20%

402

0.1UF

CERM

10V

20%

402

0.1UF

CERM

10V

20%

402

0.1UF

CERM

10V

20%

402

0.1UF

CERM

10V

20%

402

0.1UF

402

20%

10V

CERM

0.1UF

402

20%

10V

CERM

0.1UF

CERM

10V

20%

402

0.1UF

CERM

10V

20%

402

0.1UF

402

20%

10V

CERM

0.1UF

402

20%

10V

CERM

CERM

402

SEE_TABLE

10%

6.3V

1UF

CERM

402

6.3V

10%

1UF

SEE_TABLE

10%

6.3V

CERM

402

1UF

SEE_TABLE

10%

CERM

402

6.3V

1UF

SEE_TABLE

1UF

10%

CERM

402

6.3V

SEE_TABLE

402

6.3V

1UF

10%

CERM

SEE_TABLE

6.3V

1UF

402

CERM

10%

SEE_TABLE

1UF

6.3V

402

CERM

10%

SEE_TABLE

1UF

6.3V

CERM

10%

SEE_TABLE

402

CERM

10%

1UF

SEE_TABLE

402

6.3V

SEE_TABLE

1UF

6.3V

10%

CERM

402

SEE_TABLE

CERM

402

10%

6.3V

1UF

805

N20P80%

10UF

10V

Y5V

805

10UF

10V

N20P80%

Y5V

805

10UF

10V

N20P80%

Y5V

805

Y5V

10V

N20P80%

10UF

2.2UF

16V

N20P80%

805

CERM

2.2UF

16V

N20P80%

805

CERM

N20P80%

10V

Y5V

10UF

805

N20P80%

10V

Y5V

10UF

805

Y5V

N20P80%

10V

10UF

805

N20P80%

10V

Y5V

10UF

805

10UF

10V

Y5V

N20P80%

805

10UF

10V

Y5V

N20P80%

805

10UF

10V

Y5V

N20P80%

805

10UF

10V

Y5V

N20P80%

805

CON_38SM_MICTOR

OMIT

SM

CON_38SM_MICTOR

OMIT

SM

CON_38SM_MICTOR

CPU_ADDR<19>

OMIT

SM

CPU_QREQ_L

F-ST-SM

NOSTUFF

U.FL-R_SMT

47

NOSTUFF

402

MF

1/16W

5%

NOSTUFF

402

MF

1/16W

5%

0

5%

1/16W

MF

402

NOSTUFF

22

+3V_MAIN

NOSTUFF

SM12B-SRSS-TB

F-RT-SM

10K

1/16W

MF

402

1%

0.1UF

402

20%

10V

CERM

0.1UF

CERM

10V

20%

402

0.1UF

402

20%

10V

CERM

0.1UF

CERM

10V

20%

402

0.1UF

402

20%

10V

CERM

0.1UF

402

20%

10V

CERM

0.1UF

402

20%

10V

CERM

10V

0.1UF

402

20%

CERM

0.1UF

402

20%

10V

CERM

10V

0.1UF

CERM

20%

402

10V

0.1UF

402

20%

CERM

0.1UF

CERM

10V

20%

402

0.1UF

CERM

10V

20%

402

0.1UF

402

20%

10V

CERM

0.1UF

402

20%

10V

CERM

CON_37SM_MICTOR

OMIT

F-ST-SM

0.1UF

CERM

10V

20%

402

0.1UF

CERM

10V

20%

402

0.1UF

CERM

10V

20%

402402

CERM

0.1UF

10V

20%20%

0.1UF

CERM

10V

402

N20P80%

10V

Y5V

10UF

805

N20P80%

10V

Y5V

10UF

805

N20P80%

10V

Y5V

10UF

805

10UF

N20P80%

10V

Y5V

805

10V

Y5V

805

N20P80%

10UF

10V

Y5V

805

N20P80%

10UF

10V

Y5V

805

N20P80%

10UF

10V

Y5V

805

10UF

N20P80%

10V

Y5V

805

N20P80%

10UF

10V

Y5V

805

N20P80%

10UF

SEE_TABLE

6.3V

CERM

402

1UF

10%

CERM

402

SEE_TABLE

1UF

10%

6.3V

CERM

402

SEE_TABLE

1UF

10%

6.3V

CAP,CER,.22UF,20%,6.3V,0402,X5R

1GHZ_DECOUP

132S0013

C1022,C1027,C1011,C1008,C1010,C1025,C1009,C1002,C1023,C1017,C1031,C997,C996,C1012,C1024,C1001,C1028,C1018,C1096,C1097,C1098

21

1_25GHZ_DECOUP

CAP,CER,1UF,10%,6.3V,0402,X5R

C1022,C1027,C1011,C1008,C1010,C1025,C1009,C1002,C1023,C1017,C1031,C997,C996,C1012,C1024,C1001,C1028,C1018,C1096,C1097,C1098

138S0541 21

8 69

051-6497

13

CPU_VCORE_SLEEP

+MAXBUS_SLEEP

JTAG_ASIC_TRST_L

JTAG_ASIC_TCK

JTAG_ASIC_TMS

JTAG_ASIC_TDO

CPU_BR_L

CPU_DATA<54>

CPU_ADDR<31>

CPU_ADDR<28>

CPU_ADDR<22>

CPU_ADDR<21>

CPU_ADDR<24>

CPU_TS_L

CPU_ADDR<15>

CPU_ADDR<14>

CPU_DTI<0>

CPU_ADDR<7>

CPU_ADDR<12>

CPU_TSIZ<2>

CPU_ADDR<5>

CPU_ADDR<17>

CPU_ADDR<20>

CPU_ADDR<16>

CPU_ARTRY_L

CPU_ADDR<10>

CPU_ADDR<13>

CPU_HIT_L

CPU_ADDR<3>

CPU_ADDR<9>

CPU_ADDR<26>

CPU_ADDR<29>

CPU_ADDR<27>

CPU_ADDR<18>

CPU_ADDR<23>

CPU_ADDR<25>

CPU_DBG_L

MPIC_CPU_INT_L

CPU_DATA<35>

CPU_DATA<32>

CPU_DATA<40>

CPU_DATA<31>

CPU_DATA<25>

CPU_DATA<27>

CPU_DATA<22>

CPU_DATA<17>

CPU_DATA<10>

CPU_DATA<13>

CPU_DATA<1>

CPU_DATA<4>

CPU_DATA<53>

CPU_DATA<47>

CPU_DATA<45>

CPU_DATA<23>

CPU_DATA<21>

CPU_DATA<14>

CPU_DATA<50>

CPU_DATA<2>

CPU_DATA<5>

CPU_DATA<51>

CPU_DATA<7>

CPU_DATA<44>

SYSCLK_LA

CPU_DATA<34>

CPU_DATA<56>

CPU_DATA<59>

CPU_DATA<33>

CPU_DATA<60>

CPU_DATA<28>

CPU_DATA<29>

CPU_TT<1>

CPU_TEA_L

CPU_ADDR<4>

CPU_TSIZ<1>

CPU_CI_L

CPU_ADDR<8>

CPU_AACK_L

CPU_GBL_L

CPU_DRDY_L

CPU_TT<3>

CPU_WT_L

CPU_TSIZ<0>

CPU_ADDR<1>

CPU_DTI<2>

CPU_QACK_L

CPU_BG_L

CPU_TT<2>

CPU_DTI<1>

CPU_TBST_L

CPU_ADDR<0>

CPU_TT<4>

CPU_ADDR<2>

CPU_TT<0>

CPU_TA_L

CPU_ADDR<6>

CPU_ADDR<11>

CPU_DATA<58>

CPU_DATA<36>

CPU_DATA<62>

CPU_DATA<61>

CPU_DATA<24>

CPU_DATA<41>

CPU_DATA<9>

CPU_DATA<19>

CPU_DATA<20>

CPU_DATA<16>

CPU_DATA<18>

CPU_DATA<49>

CPU_DATA<6>

CPU_DATA<0>

CPU_DATA<43>

CPU_DATA<46>

CPU_DATA<8>

CPU_DATA<15>

CPU_DATA<55>

CPU_DATA<11>

CPU_DATA<3>

CPU_DATA<12>

CPU_DATA<52>

CPU_DATA<42>

CPU_DATA<48>

CPU_CHKSTP_OUT_L

CPU_DATA<37>

CPU_DATA<39>

CPU_DATA<38>

CPU_DATA<63>

CPU_DATA<57>

CPU_DATA<30>

CPU_DATA<26>

INT_CLOCK_OUT

SYSCLK_LA

INT_ANALYZER_CLK

JTAG_CPU_TRST_L

JTAG_CPU_TCK

JTAG_CPU_TDO

JTAG_CPU_TDI

JTAG_CPU_TMS

NC_JTAG10

NO_TEST

CPU_SRESET_L

CPU_HRESET_L

CPU_CHKSTP_OUT_L

NO_TEST

NC_JTAG7

+MAXBUS_SLEEP

NC_FMAX8

NO_TEST

NC_FMAX7

NO_TEST

NC_RESET_BUTTON_L

NO_TEST

+MAXBUS_SLEEP

CPU_ADDR<30>

CPU_PLL_CFGEXT

CPU_PLL_CFG<1>

CPU_PLL_CFG<2>

CPU_PLL_CFG<3>

CPU_PLL_CFG<0>

PWR_SWITCH*

PMU_RST*

CPU_VCORE_SLEEP

NO_TEST

NC_LCENABLE

NO_TEST

NC_TESTMODE

JTAG_ASIC_TDI

<XR_PAGE_TITLE>

R940

1

2

R937

1

2

J22

1

10

11 12

13 14

15 16

17 18

19

2

20

3 4

5 6

7 8

9

C1022

1

2

C1027

1

2

C1011

1

2

C1008

1

2

C1010

1

2

C1025

1

2

C972

1

2

C981

1

2

C980

1

2

C973

1

2

C993

1

2

C990

1

2

C994

1

2

C1007

1

2

C961

1

2

C1020

1

2

C1021

1

2

C967

1

2

C997

1

2

C1031

1

2

C1017

1

2

C1023

1

2

C1002

1

2

C1009

1

2

C1018

1

2

C1028

1

2

C1001

1

2

C1024

1

2

C1012

1

2

C996

1

2

C350

1

2

C958

1

2

C983

1

2

C992

1

2

C969

1

2

C353

1

2

C1033

1

2

C1037

1

2

C976

1

2

C1040

1

2

C1042

1

2

C1032

1

2

C364

1

2

C1016

1

2

J30

39404142434445

1

10

11

12

13

14

15

16

17

18

19

2

20

21

22

23

24

25

26

27

28

29

3

30

31

32

33

34

35

36

37

38

4

5

6

7

8

9

J20

39404142434445

1

10

11

12

13

14

15

16

17

18

19

2

20

21

22

23

24

25

26

27

28

29

3

30

31

32

33

34

35

36

37

38

4

5

6

7

8

9

J31

39404142434445

1

10

11

12

13

14

15

16

17

18

19

2

20

21

22

23

24

25

26

27

28

29

3

30

31

32

33

34

35

36

37

38

4

5

6

7

8

9

J27

3

2

1

R308

1

2

R314

1 2

R313

2 1

J32

14

13

1

10

11

12

2

3

4

5

6

7

8

9

R939

1

2

C999

1

2

C991

1

2

C1013

1

2

C995

1

2

C982

1

2

C998

1

2

C1043

1

2

C987

1

2

C1026

1

2

C1014

1

2

C988

1

2

C1041

1

2

C974

1

2

C1003

1

2

C977

1

2

J19

39 40 41 42 43 44 45

10

11

12

13

14

15

16

17

18

19

2

20

21

22

23

24

25

26

27

28

29

3

30

31

32

33

34

35

36

37

38

4

5

6

7

8

9

C1910

1

2

C1904

1

2

C1903

1

2

C1902

1

2

C1901

1

2

C1911

1

2

C1912

1

2

C1913

1

2

C1914

1

2

C598

1

2

C1054

1

2

C1055

1

2

C1056

1

2

C1057

1

2

C1058

1

2

C1097

1

2

C1096

1

2

C1098

1

2

LAST_MODIFIED=Wed Sep 17 12:15:45 2003

59C8>

59C8>

59C8>

52C6>

52C6>

52C6>

46D4<

46D4<

46D4<

45D2<>

45D2<>

45D2<>

44D2<

44D2<

44D2<

44D1<

44D1<

44D1<

44B7<

44B7<

44B7<

9D8<

9D8<

9D8<

9B7<

9B7<

9B7<

8D1<

8D4<

8D4<

8A3<>

8D1<

8A3<>

7C7<

7C7<

7C7<

59D8>

7C5<

59C8>

7C5<

7C5<

59D8>

59B6>

7C3<

44D2<

7C3<

7C3<

59B6>

52C6>

7B3<

59A8>

44C2<

7B3<

7B3<

52C6>

56C3>

45D2<>

7A3<

59D8>

56D3>

56D3>

56D3>

56C3>

56C3>

56C3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56C3>

56C3>

56C3>

56C3>

56D3>

56C3>

56D3>

56D3>

56D3>

56D3>

56D3>

56C3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

59C8>

56D3>

56D3>

56B3>

7B3<

59C8>

7A3<

7A3<

59D6>

45D2<>

56D3>

9B3<

8B7<

6D6<

59D8>

35B4<>

9D3<

9C8<

56D3>

56D3>

56D3>

56D3>

56D3>

9D3<>

56D3>

56D3>

56C3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

9B3<>

56D3>

56D3>

9B3<

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

9B1<>

28B5>

9C1<>

9C1<>

9C1<>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

56D3>

9C8<

9B1<>

9B1<>

56D3>

56D3>

56D3>

9D8<

56D3>

56D3>

9D8<

56D3>

9B1<>

9C1<>

56D3>

9D5<

9C1<>

9D5<

56D3>

56D3>

9B3<>

9A1<>

56D3>

56D3>

9C3<>

56D3>

9B3<>

9B1<

9B3<>

9B3<>

56D3>

56D3>

56C3>

56C3>

9D3<>

9B3<>

56C3>

9B3<>

56D3>

9B3<>

56D3>

9B3<>

9A1<>

56D3>

56D3>

9D5<

9C1<>

9C5<

9C5<

56D3>

9C1<>

56D3>

56D3>

56D3>

56D3>

56D3>

9D8<

56D3>

56D3>

9B1<>

9B1<>

56D3>

56D3>

9C8<

56D3>

56D3>

56D3>

9C8<

9B1<>

9D8<

8A3<>

56D3>

56D3>

56D3>

9C5<

9D5<

56D3>

56D3>

54A7<

59C8>

59C8>

59C8>

59C8>

59C6>

7A5<

8D5<>

6D6<

6D6<

56D3>

59D6>

44B5<>

8C1<

59D8>

9C3<>

7D5<

4D7<

6C5<

59C8>

35C4<

35A2<

59D8>

7C7<

9B1<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

7C7<

9C3<>

9C3<>

9A1<>

9D3<>

9C3<>

9B3<>

9D3<>

9C3<>

9C3<>

9C3<>

7C7<

9C3<>

9C3<>

7C7<

9D3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

9C3<>

7B7<

7A5<

9B7<

9B7<

6C4<

9C1<>

9C1<>

9C1<>

9C1<>

9C1<>

9D1<>

9D1<>

9D1<>

9D1<>

9B1<>

6C4<

6C4<

9C1<>

9C1<>

9D1<>

9B1<>

9D1<>

9D1<>

9B1<>

9D1<>

6C4<

56B3>

9B7<

9B1<>

9B1<>

9B7<

9B1<>

9C1<>

9C1<>

7A7<

7B7<

9D3<>

9B3<>

7A7<

9D3<>

7B7<

56C3>

7B7<

7A7<

7A7<

9B3<>

9D3<>

9A1<>

9B3<>

7B7<

7A7<

9A1<>

7B7<

9D3<>

7A7<

9D3<>

7A7<

7C7<

9D3<>

9C3<>

9B1<>

9A7<

9B1<>

9B1<>

9C1<>

6C4<

9D1<>

9C1<>

9C1<>

9C1<>

9C1<>

9B1<>

9D1<>

9D1<>

6C4<

6C4<

9D1<>

9D1<>

9B1<>

9D1<>

9D1<>

9D1<>

9B1<>

6C4<

9B1<>

7B5<

9C1<>

9C1<>

9C1<>

9B1<>

9B1<>

9C1<>

9C1<>

56B3> 16C7<

7C5<

7D5<

59C8>

7A5<

7A5<

7A5<

7A3<

7B5<

6C5<

6C5<

9C3<>

6C6<

6C6<

6C6<

6C6<

6C6<

44C5<>

44A5<>

4D7<

34B7<

4C7<>

4C3>

4D3<

4D5<

34B7<

34B7<

34B7<

35B4<>

4D7>

5B4<>

4B7<>

4B7<>

4C7<>

4C7<>

4B7<>

4D7<>

4C7<>

4C7<>

4C3<

4C7<>

4C7<>

4B7>

4C7<>

4C7<>

4C7<>

4C7<>

4A7<>

4C7<>

4C7<>

4A7>

4C7<>

4C7<>

4B7<>

4B7<>

4B7<>

4C7<>

4C7<>

4B7<>

4C3<

4B3<

5C4<>

5C4<>

5B4<>

5C4<>

5C4<>

5C4<>

5C4<>

5C4<>

5D4<>

5C4<>

5D4<>

5D4<>

5B4<>

5B4<>

5B4<>

5C4<>

5C4<>

5C4<>

5B4<>

5D4<>

5D4<>

5B4<>

5D4<>

5B4<>

8A2<

5C4<>

5B4<>

5B4<>

5C4<>

5B4<>

5C4<>

5C4<>

4B7<>

4C3<

4C7<>

4B7>

4A7>

4C7<>

4A7<

4B8<>

4C2<

4B7<>

4B7>

4B7>

4C7<>

4C3<

4C3<

4D7<

4B7<>

4C3<

4B7>

4C7<>

4B7<>

4C7<>

4B7<>

4C3<

4C7<>

4C7<>

5B4<>

5C4<>

5B4<>

5B4<>

5C4<>

5B4<>

5D4<>

5C4<>

5C4<>

5C4<>

5C4<>

5B4<>

5D4<>

5D4<>

5B4<>

5B4<>

5D4<>

5C4<>

5B4<>

5C4<>

5D4<>

5C4<>

5B4<>

5B4<>

5B4<>

4B3>

5B4<>

5B4<>

5B4<>

5A4<>

5B4<>

5C4<>

5C4<>

56B3>

8D8<>

9B4<

4C3<

4C3<

4C3>

4C3<

4C3<

4B3<

4B3<

4B3>

4D5<

4D5<

4B7<>

4C3<

4D3<

4D3<

4C3<

4D3<

44B1<

29B3<>

4D3<

28C6<

Page 9

(PLL6)

VSSA_7

(PLL6)

VDD15A_7

D_42

D_41

D_40

D_39

D_38

D_44

D_43

D_45

D_46

D_47

D_48

D_52

D_51

D_50

D_49

D_53

D_55

D_54

D_56

D_57

D_58

D_60

D_59

D_62

D_61

D_63

DBG

DRDY

DTI_0

TEA

TA

DTI_2

DTI_1

D_1

D_0

D_2

D_6

D_5

D_4

D_3

D_7

D_11

D_10

D_9

D_8

D_12

D_14

D_13

D_15

D_16

D_17

D_22

D_21

D_20

D_19

D_18

D_23

D_24

D_25

D_26

D_27

D_32

D_31

D_30

D_29

D_28

D_34

D_33

D_35

D_36

D_37

BR

(1 OF 9)

MAXBUS

INTERFACE

TS

BG

A_0

A_1

A_2

A_3

A_4

A_5

A_9

A_6

A_7

A_8

A_10

A_14

A_13

A_12

A_11

A_20

A_16