Apple d Schematics

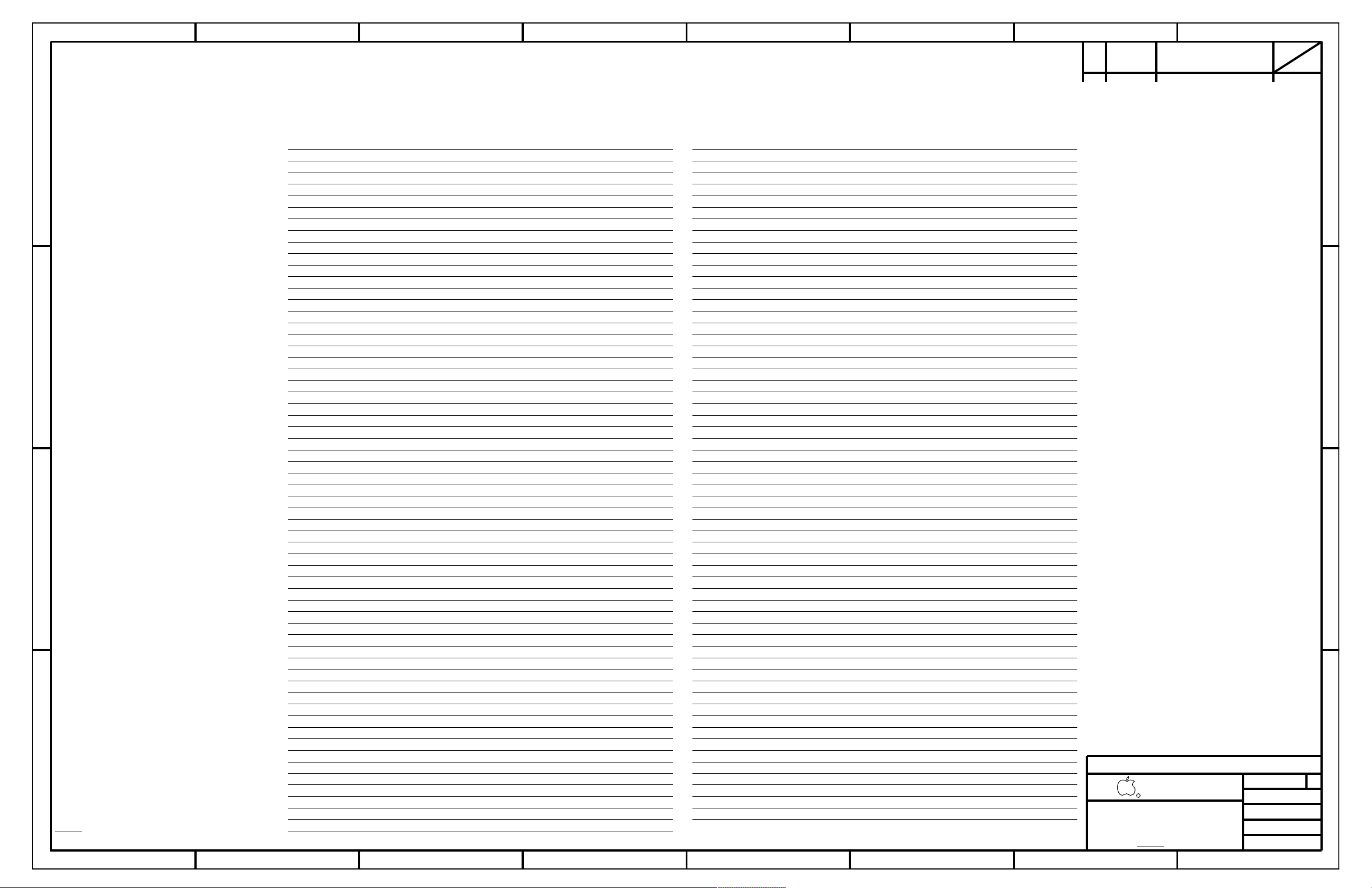

TABLE_TABLEOFCONTENTS_ITEM

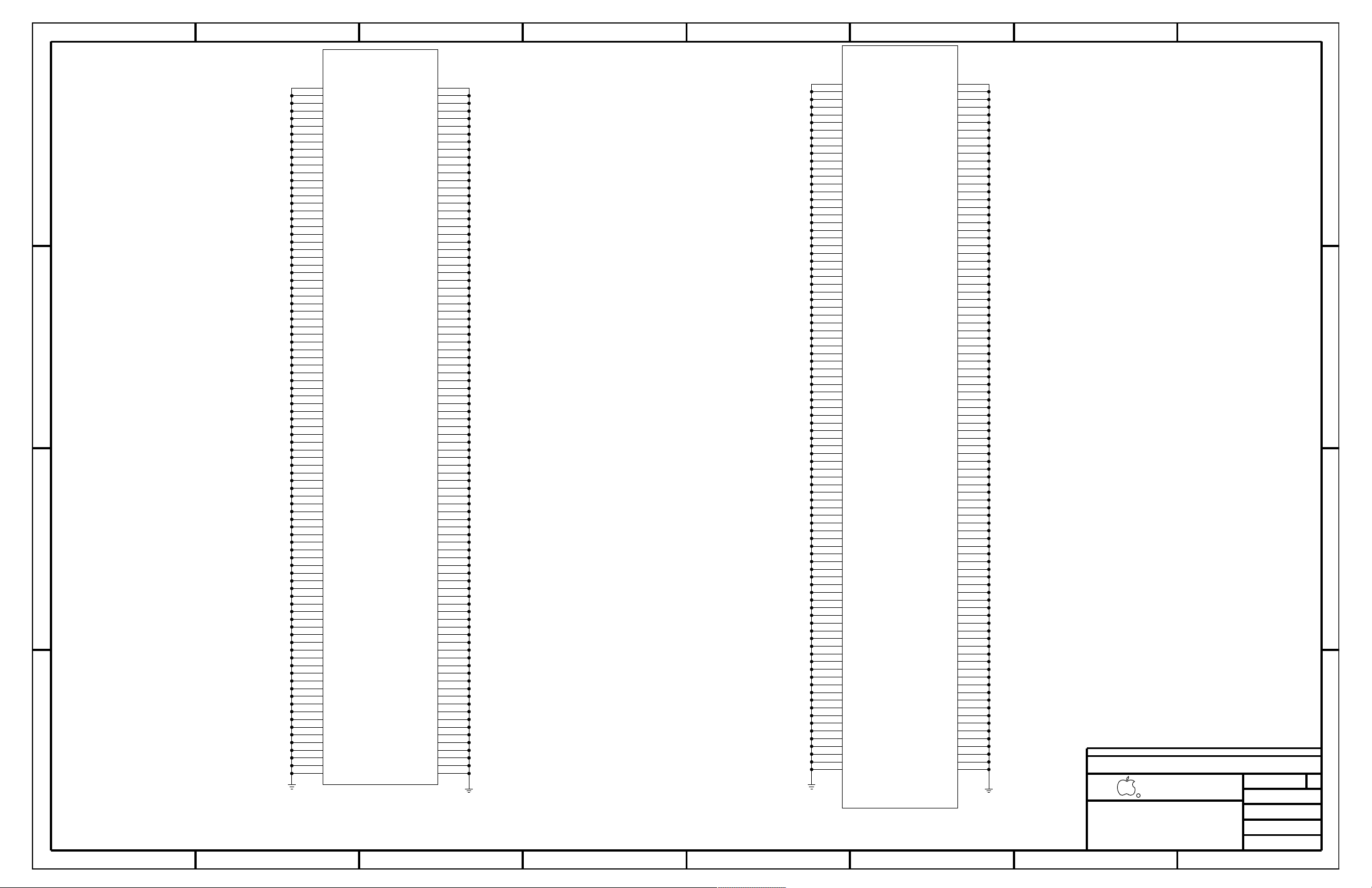

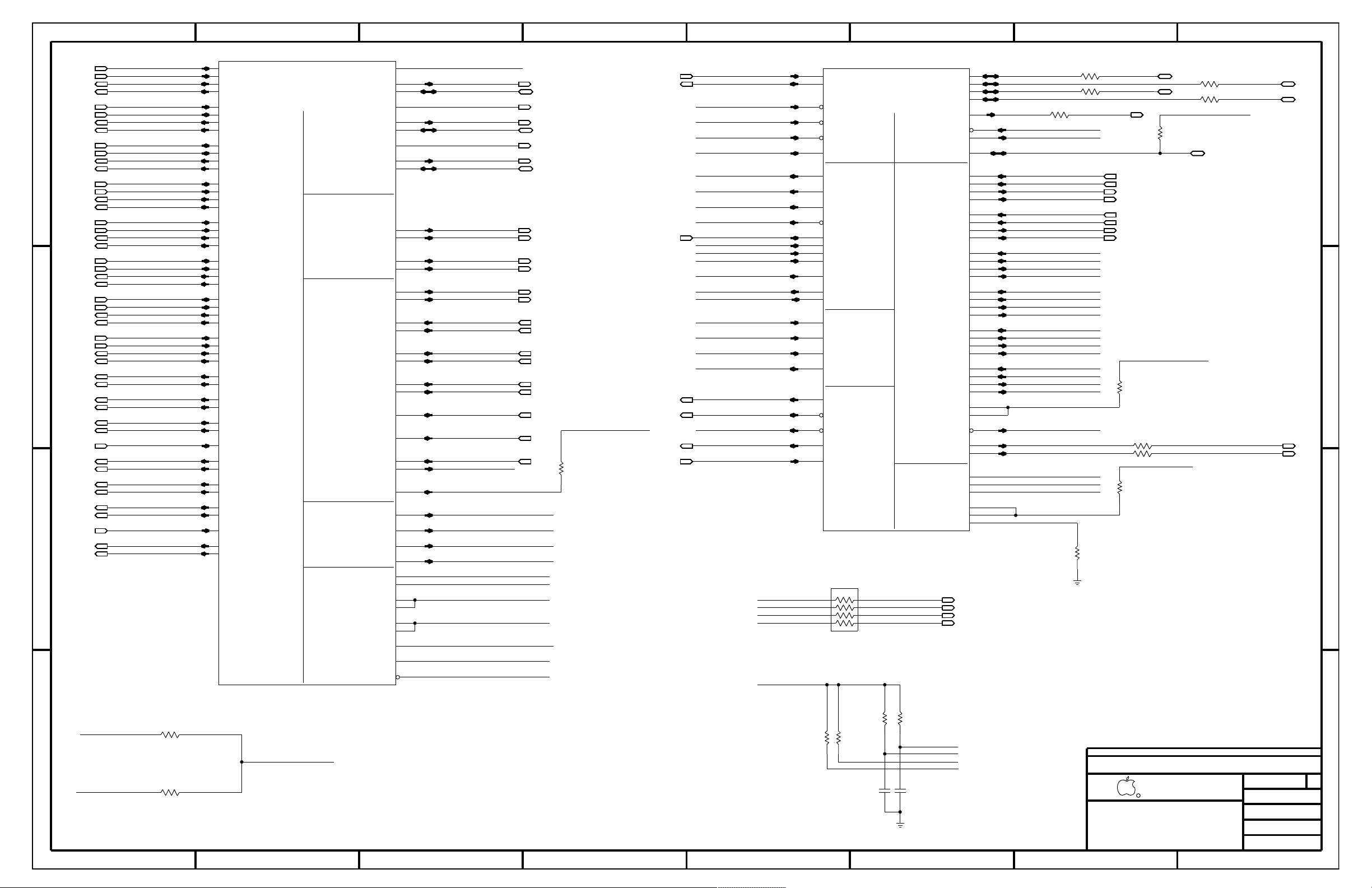

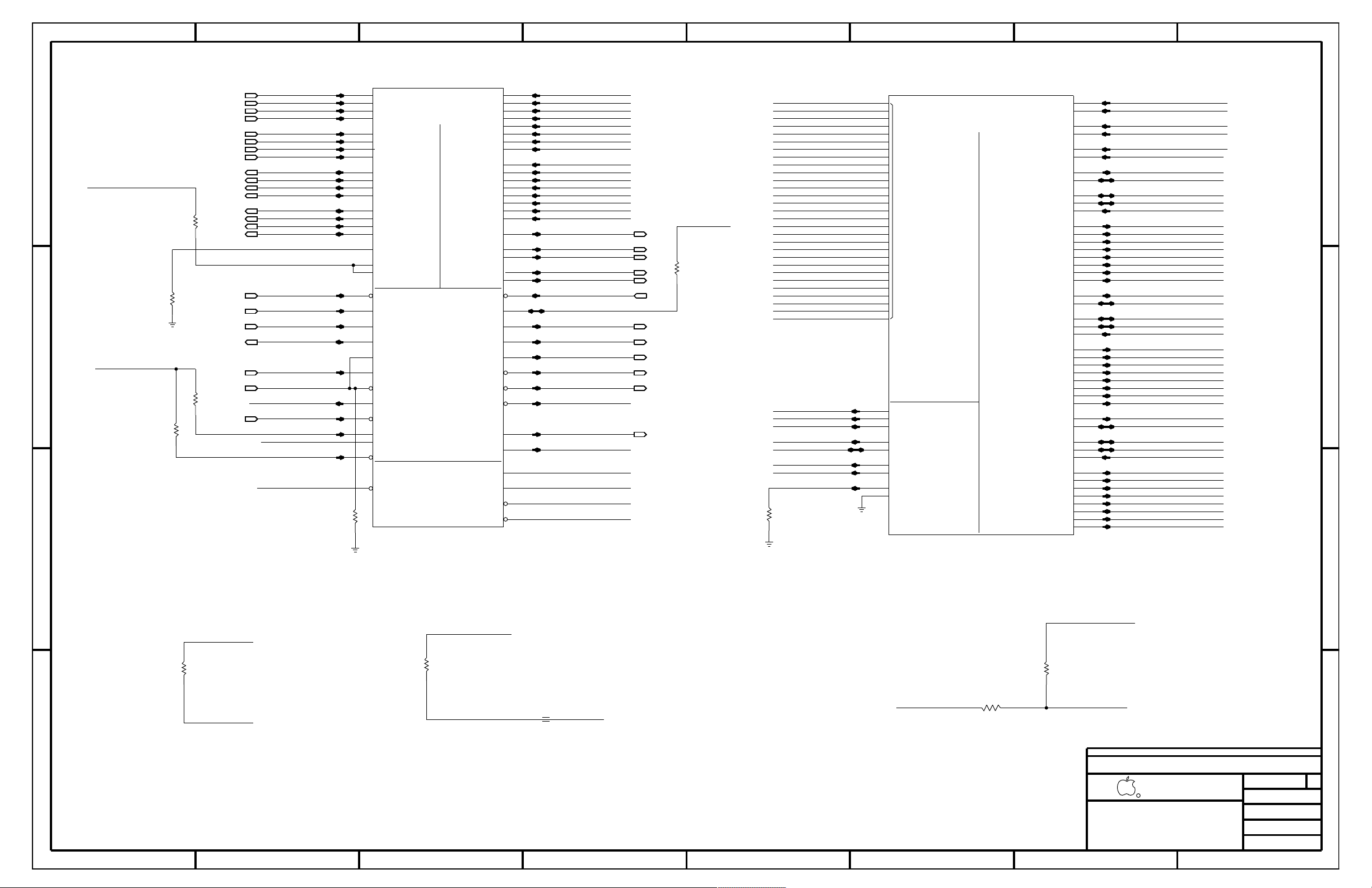

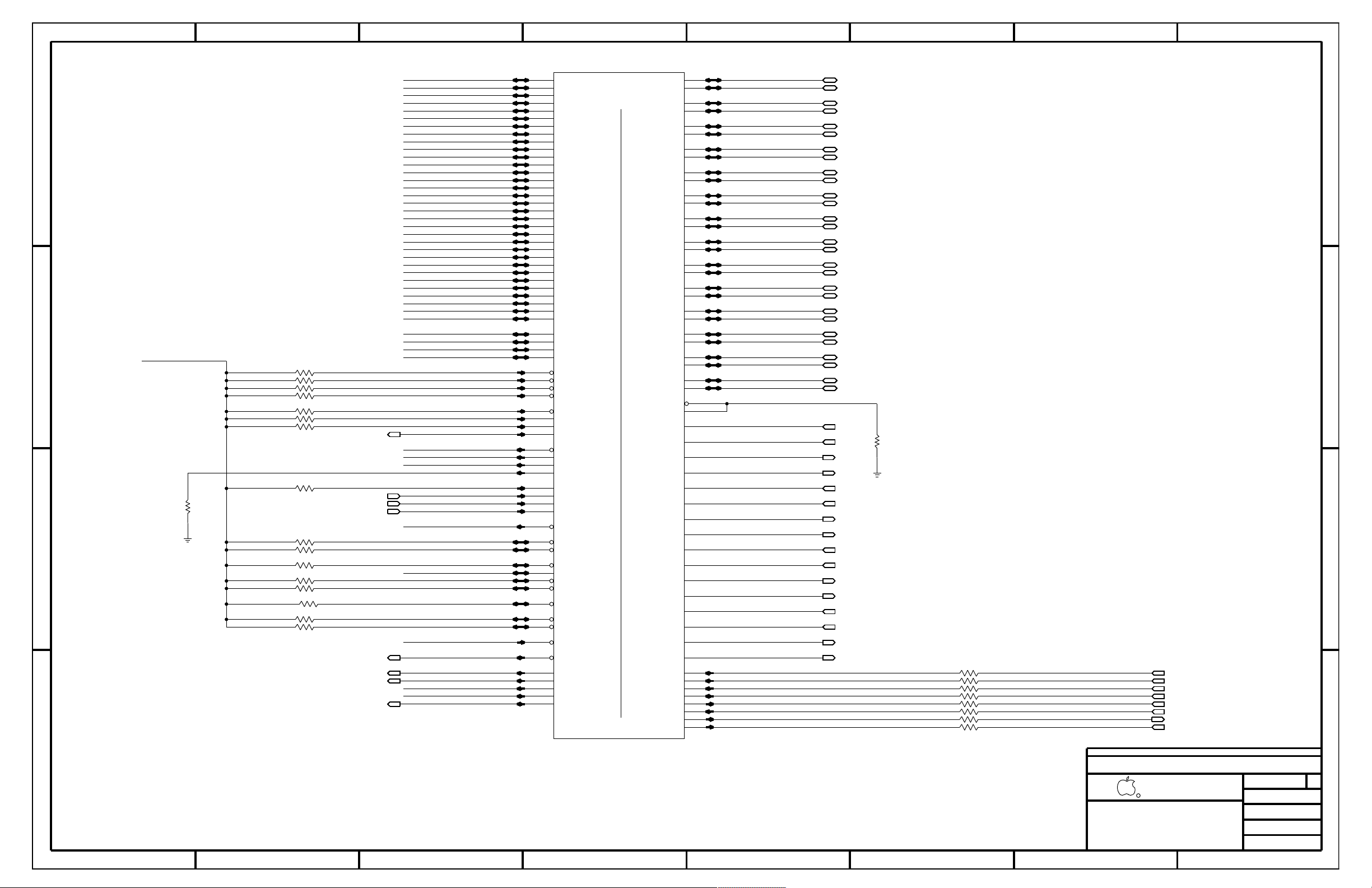

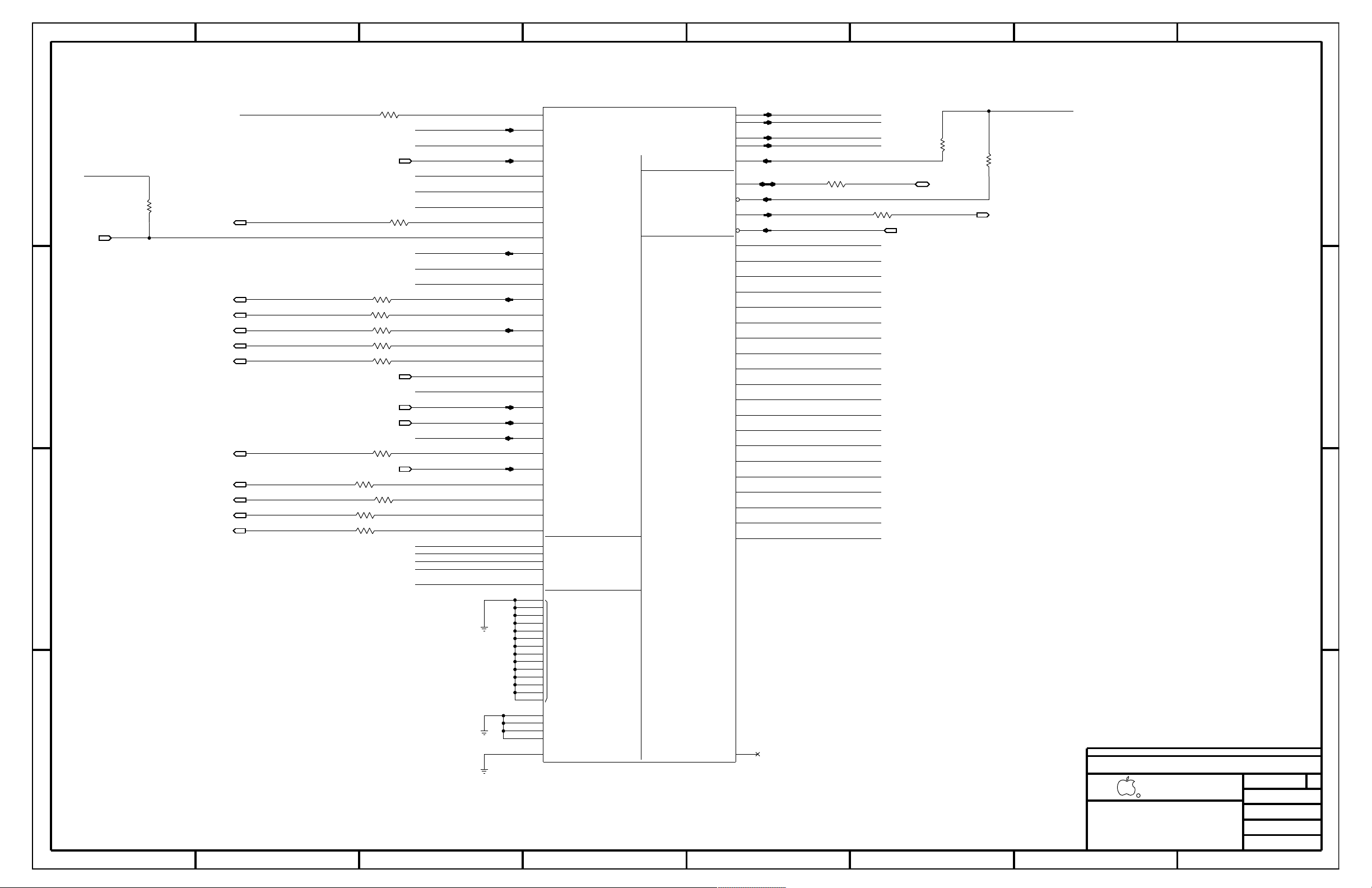

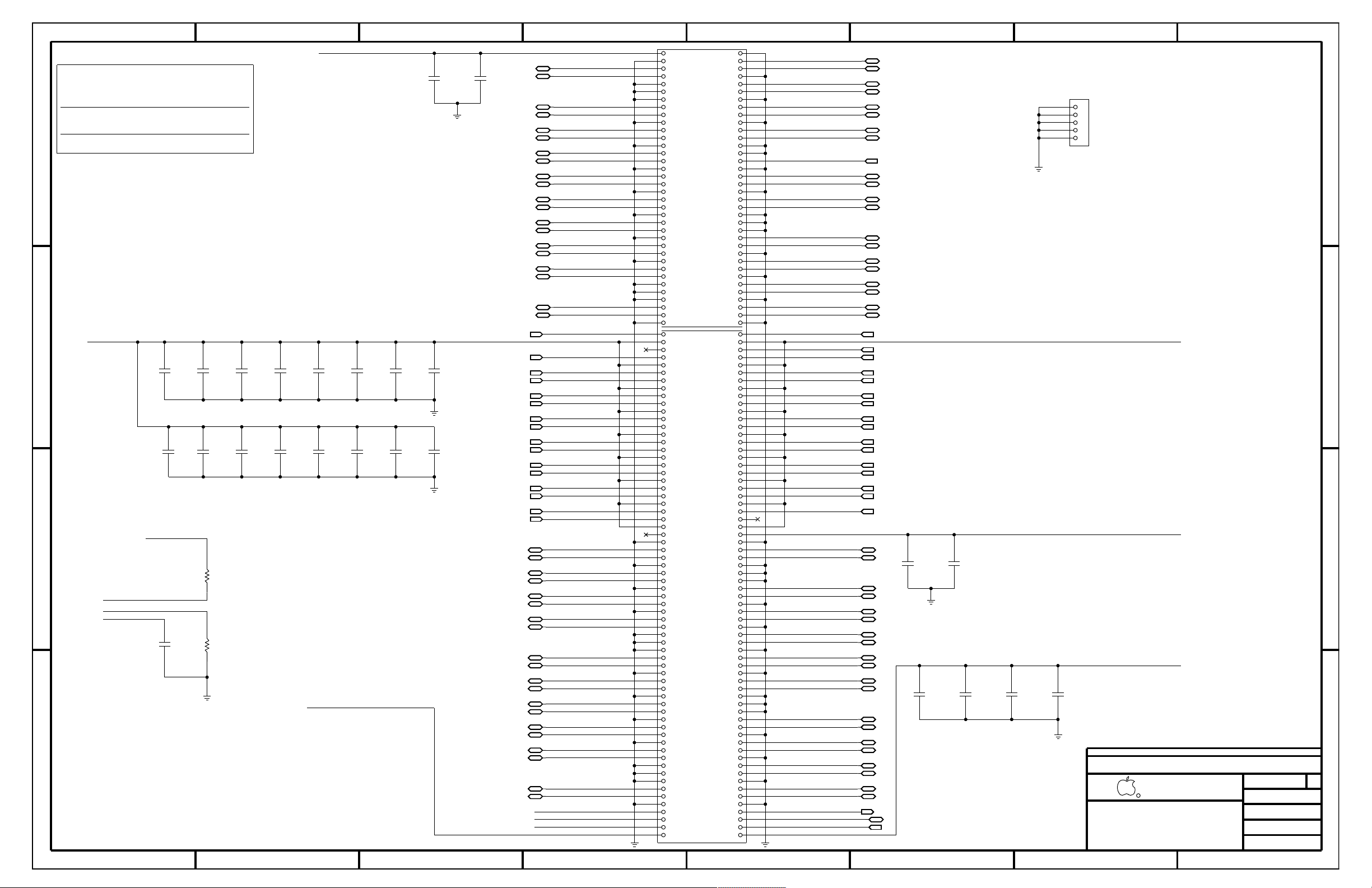

DRAWING

DRAWING

TABLE_TABLEOFCONTENTS_ITEM

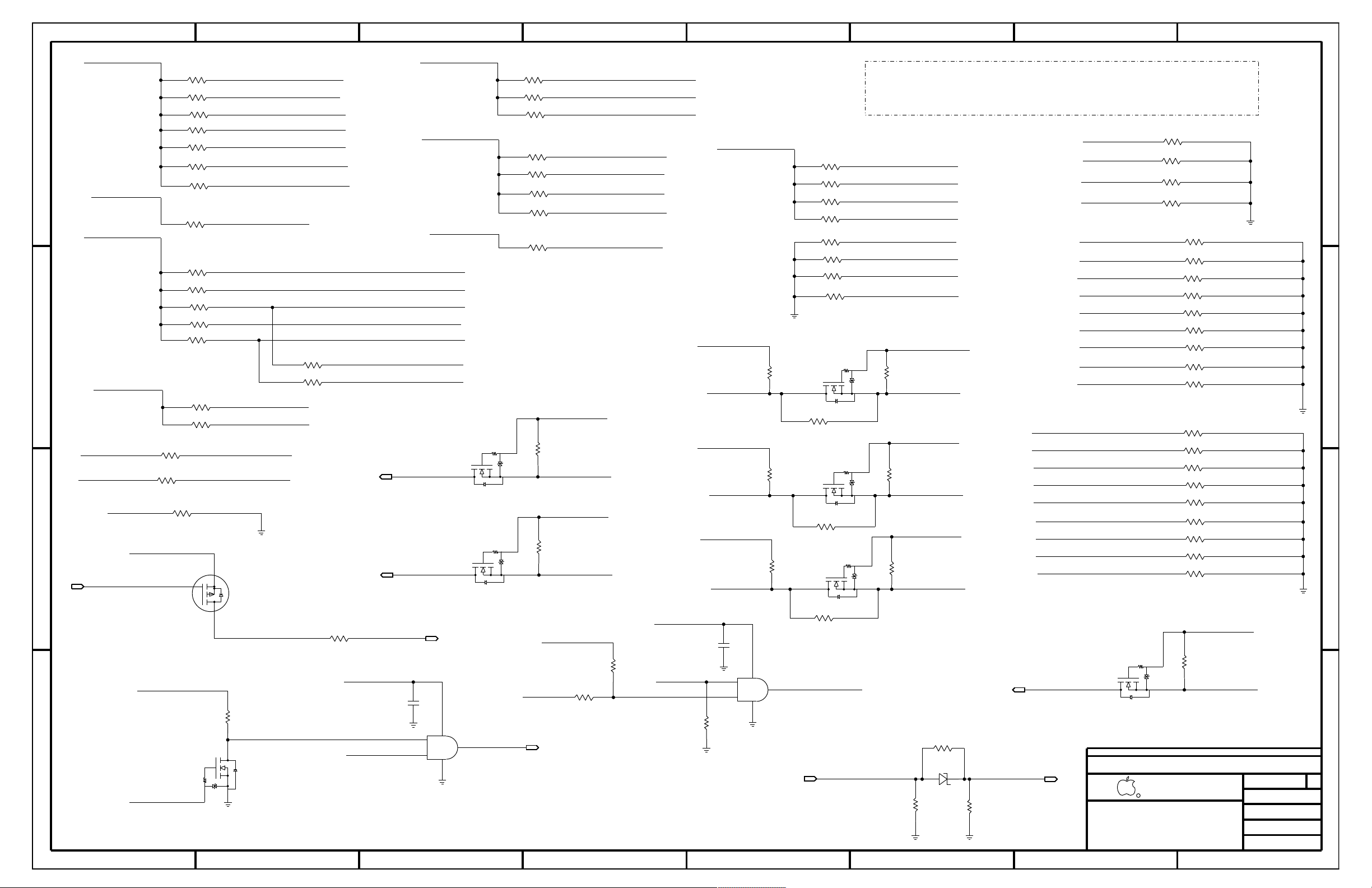

TABLE_TABLEOFCONTENTS_HEAD TABLE_TABLEOFCONTENTS_HEAD

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

PROPRIETARY PROPERTY OF APPLE INC.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

DESCRIPTION OF REVISION

CK

APPD

21

1245678

B

D

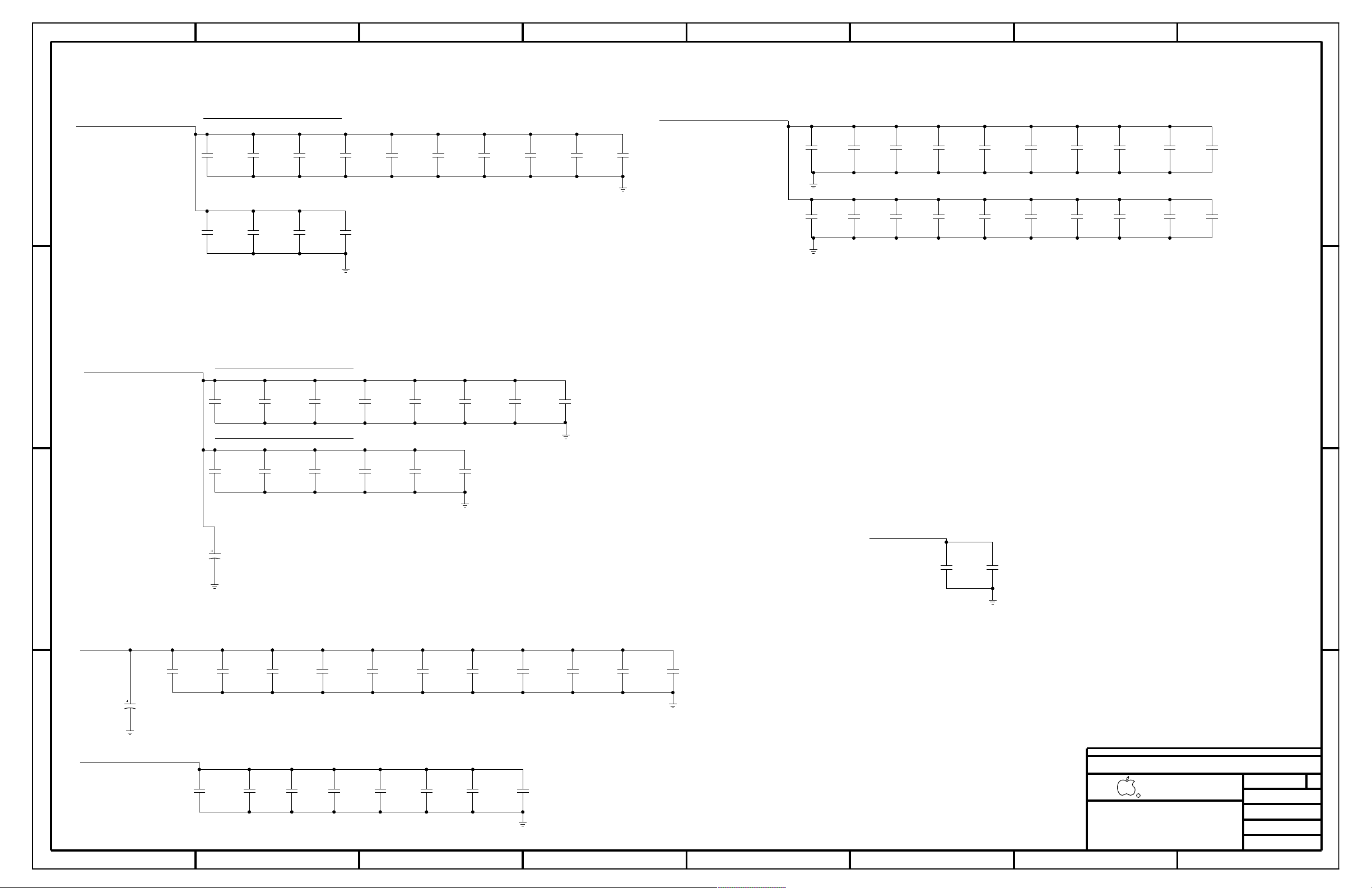

6543

C

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

THE INFORMATION CONTAINED HEREIN IS THE

C

A

D

DATE

R

SHEET

Apple Inc.

THE POSESSOR AGREES TO THE FOLLOWING:

DRAWING TITLE

D

SIZE

REVISION

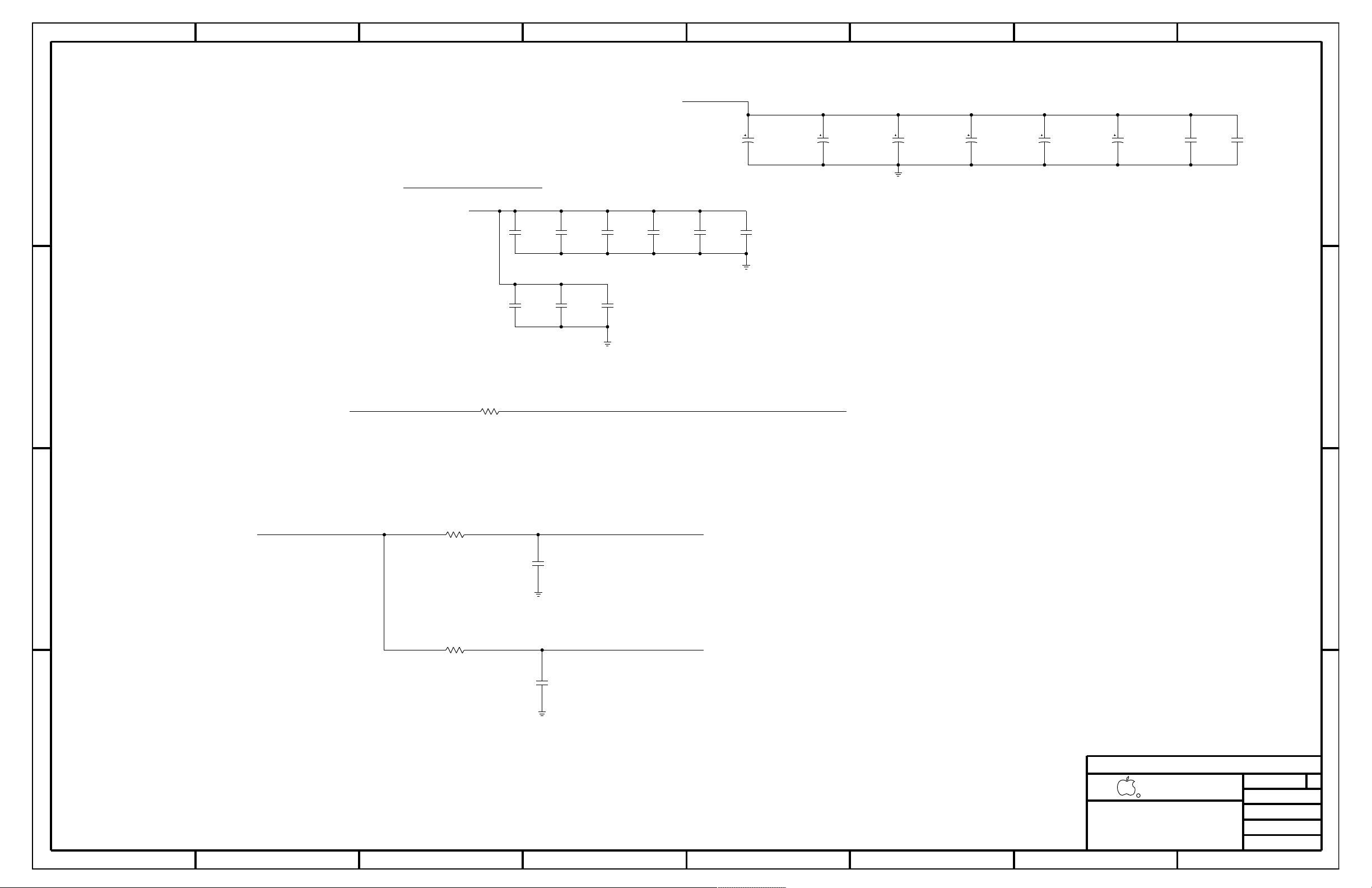

DRAWING NUMBER

BRANCH

REV ECN

7

B

3

II NOT TO REPRODUCE OR COPY IT

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

IV ALL RIGHTS RESERVED

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

8

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

D8 MLB

1 OF 117

2012-08-28

ENGINEERING RELEASED

1 OF 143

7.0.0

051-9504

7

0001607307

prefsb

60

65

D8_DIRK

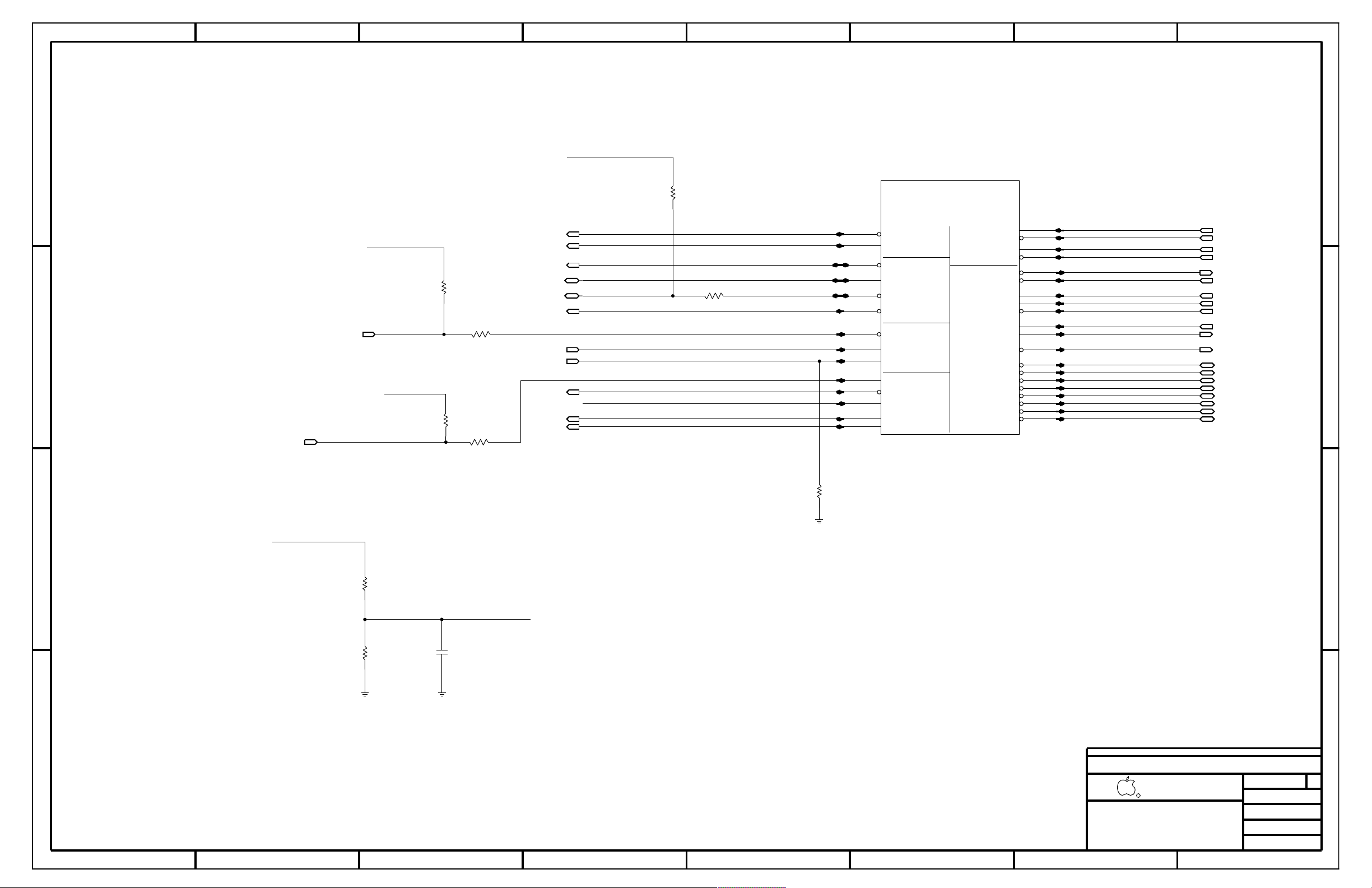

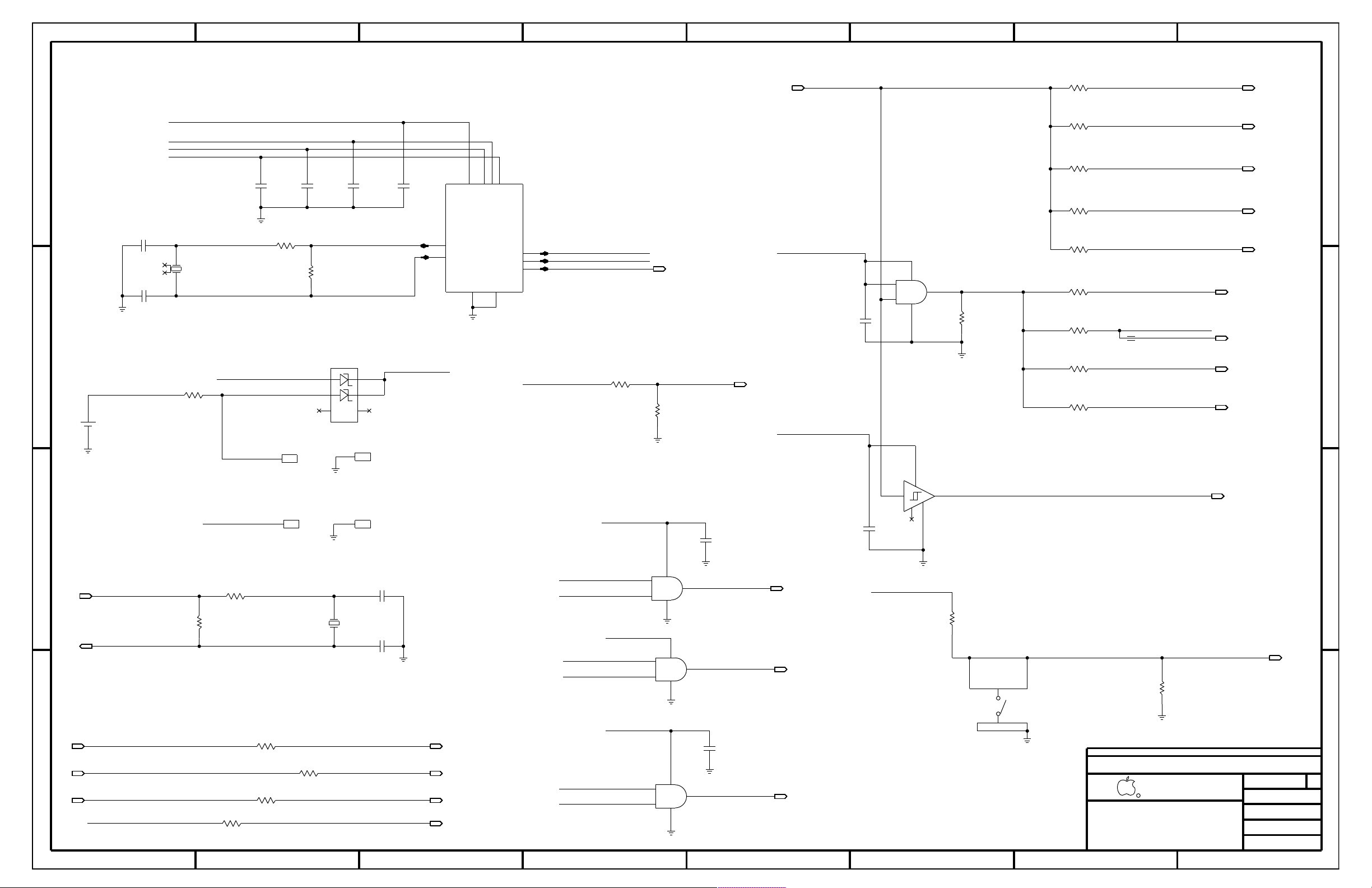

AUDIO: Jack, Mikey, CHS Switch

06/29/2012

TITLE=K22

ABBREV=DRAWING

LAST_MODIFIED=Mon Aug 27 13:24:34 2012

LAST_MODIFIED=Mon Aug 27 13:24:34 2012

N/A

1

1

MASTER

Table of Contents

Contents

Date

(.csa)

SyncPage Sync

Date

Page

(.csa)

Contents

SCH,D8,MLB

61

66

D8_DAVID

Audio: Spkr/Mic Conn.

06/13/2012

62

67

D8_DAVID

AUDIO: Detects/Grounding

06/13/2012

63

68

D8_DAVID

AUDIO: Speaker ID

06/13/2012

64

69

D8_MARK

PM Regulator Enables

04/23/2012

65

70

D8_MARK

PM Power Good

04/23/2012

66

71

D8_MLB

VReg CPU Core/AXG Cntl

02/28/2012

67

72

D8_MLB

VReg CPU Core Phases

02/28/2012

68

73

D8_MLB

VReg CPU AXG Phases

02/28/2012

69

74

D8_KOSECOFF

VReg CPU 1.05V S0

02/25/2012

70

75

D8_KOSECOFF

VReg CPU VccSA S0

02/25/2012

71

76

D8_MLB

VReg 3.3V S5/5V S4

02/28/2012

72

77

D8_KOSECOFF

VReg VDDQ and 1.8V S0

02/25/2012

73

78

D8_MLB

VREG 3.42V G3HOT

04/11/2012

74

79

D8_MLB

FET-Controlled S0 and S4

05/14/2012

75

80

D8_AARON

KEPLER PCI-E

03/13/2012

76

81

D8_YAN

KEPLER CORE/FB POWER

04/09/2012

77

82

D8_YAN

KEPLER FRAME BUFFER I/F

05/15/2012

78

83

D8_YAN

GPU SIGNAL & POWER ALIASES

04/09/2012

79

84

D8_YAN

GDDR5 Frame Buffer A

04/09/2012

80

85

D8_YAN

GDDR5 Frame Buffer B

04/09/2012

81

86

D8_YAN

KEPLER EDP/DP/GPIO

04/09/2012

82

87

D8_YAN

KEPLER GPIOS,CLK & STRAPS

07/27/2012

83

88

D8_YAN

KEPLER PEX PWR/GNDS

04/09/2012

84

92

D8_AARON

Internal DP MUXing

03/13/2012

85

93

D7_MLB

TBT DDC Crossbar

03/15/2012

86

94

D8_AARON

Thunderbolt Connector A

03/13/2012

87

95

D8_MLB

Internal DP Support

03/21/2012

88

96

D8_AARON

Thunderbolt Connector B

03/13/2012

89

97

D8_MLB

Backlight Controller MCU

04/23/2012

90

98

D8_MLB

Backlight LED Driver

04/23/2012

91

99

D8_MLB

Backlight Controller

04/23/2012

92

114

D8_MLB

VReg GPU Core Phases

02/28/2012

93

115

D8_MLB

VReg GPU Core Phases

02/25/2012

94

116

D8_MLB

VREG GPU CORE PHASE 4

02/06/2012

95

117

D8_MLB

GPU VDDQ AND 1V05 GPU/PCH/TBT VREGS

04/18/2012

96

120

D8_KOSECOFF

D8 RULE DEFINITIONS

03/19/2012

97

121

D8_KOSECOFF

DDR3 Constraints

03/19/2012

98

122

D8_AARON

CPU PCIe Constraints

03/13/2012

99

123

D8_ROSITA

CPU MISC/DMI/FDI/XDP Constraints

03/23/2012

100

124

D8_MARK

SATA/FDI/XDP Constraints

02/10/2012

101

125

D8_MARK

PCH and BR Constraints

02/10/2012

102

126

D8_KOSECOFF

USB/Camera Constraints

06/22/2012

103

127

D8_MARK

SMBus/Sensor Constraints

04/23/2012

104

128

D8_MARK

VReg Constraints

02/10/2012

105

129

D8_MARK

CPU VReg Constraints

02/10/2012

106

130

D8_MARK

Platform VReg Constraints

02/10/2012

107

131

D8_AARON

TBT/DP Constraints

03/13/2012

108

132

D8_AARON

GDDR5/GPU Constraints

03/13/2012

109

134

D8_MLB

BLC Constraints

12/19/2011

110

135

D8_MARK

GPU VREG CONSTRAINTS

02/10/2012

111

136

D8_FIYIN

ETHERNET/SD CONSTRAINTS

07/02/2012

112

138

D8_MARK

AUTO-CONSTRAINTS 1

04/23/2012

113

139

D8_MARK

AUTO-CONSTRAINTS 2

04/23/2012

114

140

D8_MARK

AUTO-CONSTRAINTS 3

04/23/2012

115

141

D8_MARK

AUTO-CONSTRAINTS 4

04/23/2012

116

142

D8_MARK

AUTO-CONSTRAINTS 5

04/23/2012

117

143

D8_MARK

AUTO-CONSTRAINTS 6

04/23/2012

01/05/2012

2

2

D8_MLB

System Block Diagram

04/23/2012

3

3

D8_MARK

Power Block Diagram

12/19/2011

4

4

D8_MLB

BOM Configuration

06/22/2012

5

5

D8_TAVYS

DEBUG LEDS

06/20/2012

6

6

D8_DOUG

Power Connectors/Aliases

03/25/2012

7

7

D8_MLB

Holes/PD parts

04/02/2012

8

8

D8_MLB_ULTIMATE

Unused Signal Aliases

08/23/2011

9

9

K70_MLB

Signal Aliases

03/23/2012

10

10

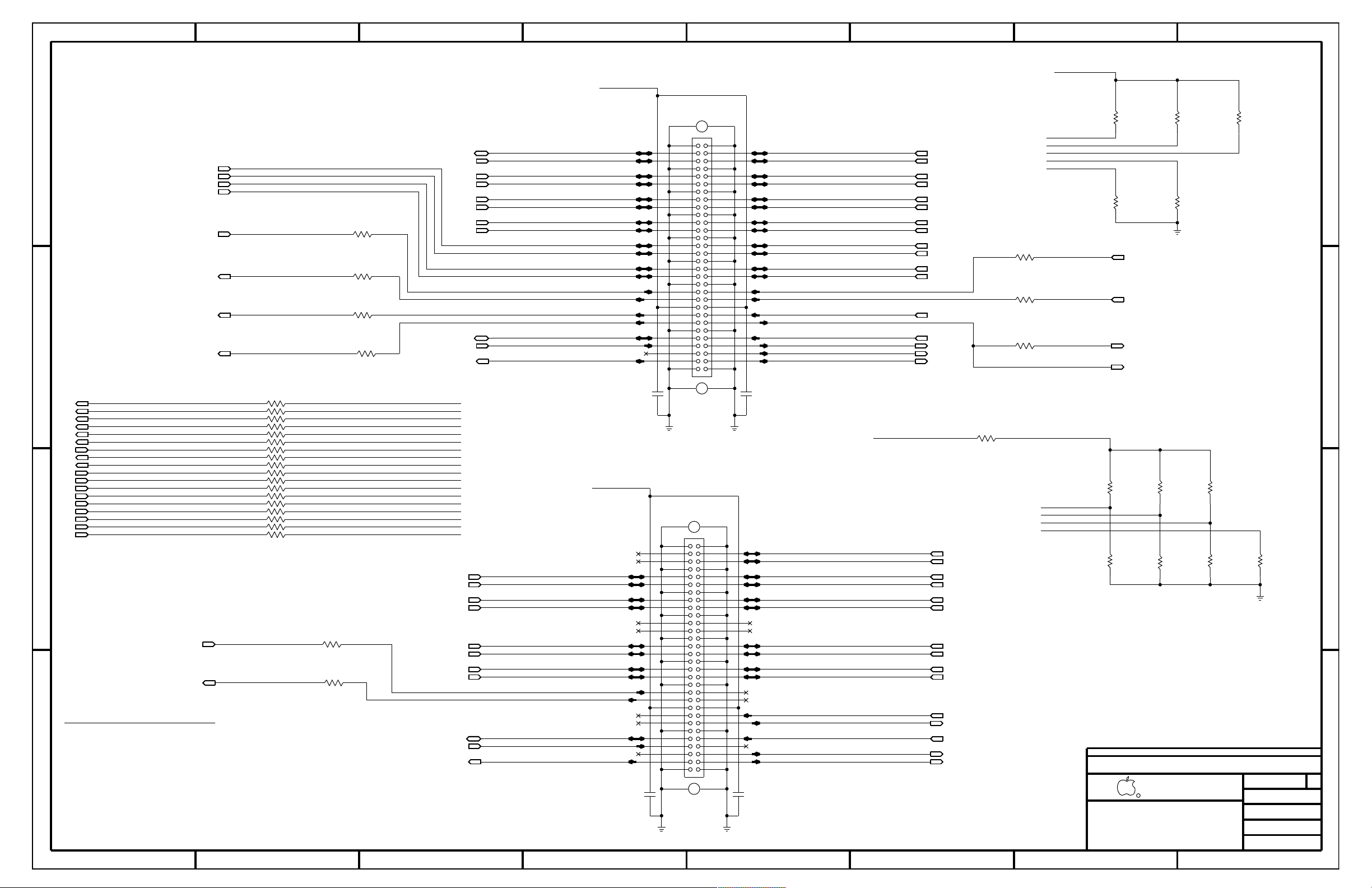

D8_ROSITA

CPU DMI/PEG/FDI/RSVD

03/15/2012

11

11

D7_MLB

CPU CLOCK/MISC/JTAG

03/15/2012

12

12

D7_MLB

CPU DDR3 INTERFACES

03/15/2012

13

13

D7_MLB

CPU POWER

03/15/2012

14

14

D7_MLB

CPU GROUNDS

03/29/2012

15

15

D8_MLB

STRAPS,PULL UPS,PULL DOWNS FOR PCH AND CPU

12/20/2011

16

16

D7_MLB

CPU NON-GFX DECOUPLING

01/26/2012

17

17

D8_KOSECOFF

GFX DECOUPLING & PCH PWR ALIAS

N/A

18

18

D8_MLB

PCH SATA/PCIE/CLK/LPC/SPI

03/15/2012

19

19

D7_MLB

PCH DMI/FDI/GRAPHICS

03/15/2012

20

20

D7_MLB

PCH PCI/USB

N/A

21

21

D8_MLB

PCH MISC

N/A

22

22

D8_MLB

PCH POWER

03/15/2012

23

23

D7_MLB

PCH GROUNDS

N/A

24

24

D8_MLB

PCH DECOUPLING

01/26/2012

25

25

D7_MLB

CPU and PCH XDP

N/A

26

26

D8_MLB

CHIPSET SUPPORT

03/23/2012

27

27

D8_ROSITA

USB 2.0 HUB (BT/SMC)

04/23/2012

28

28

D8_MARK

CPU Memory S3 Support

03/19/2012

29

29

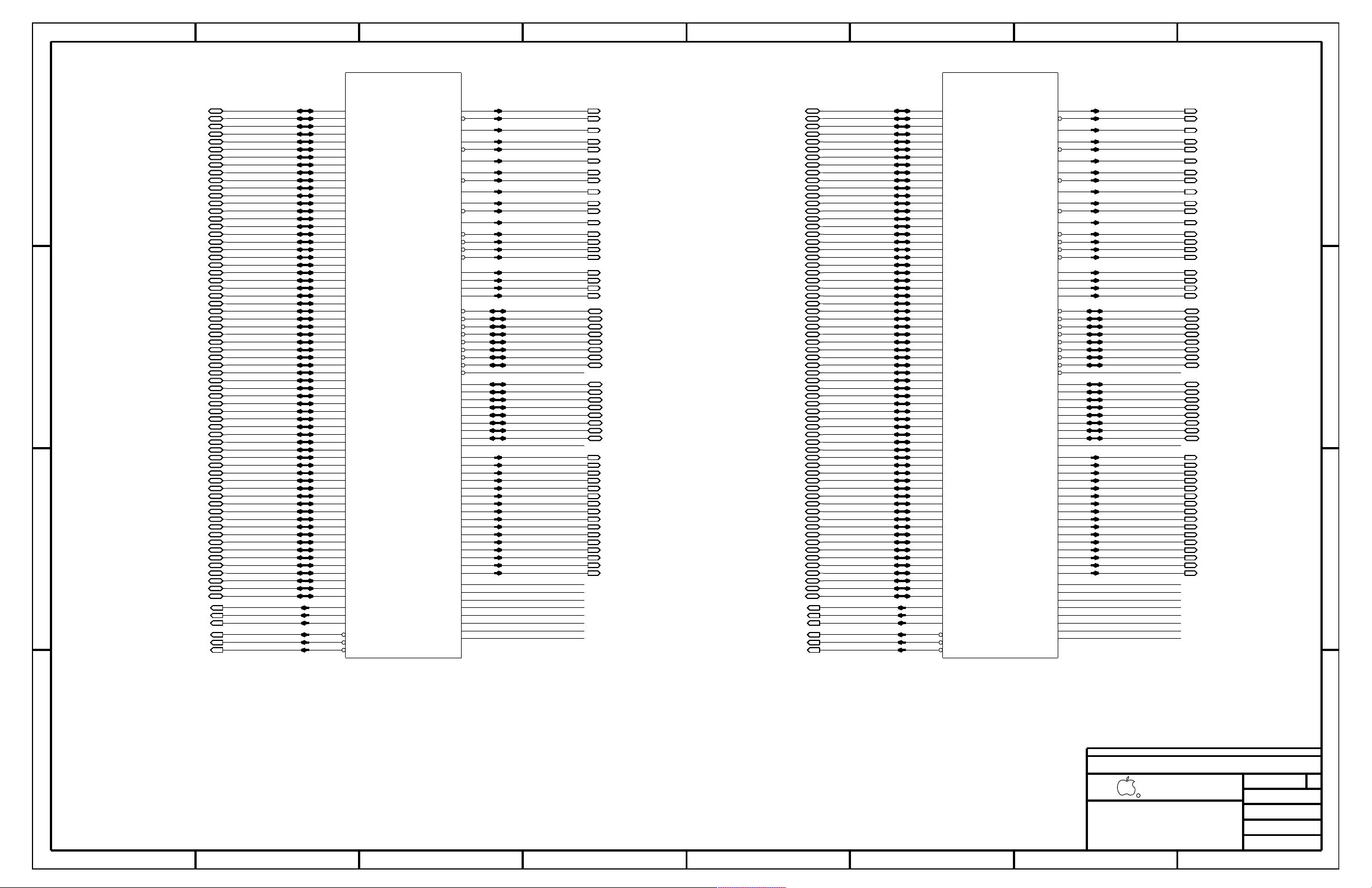

D8_KOSECOFF

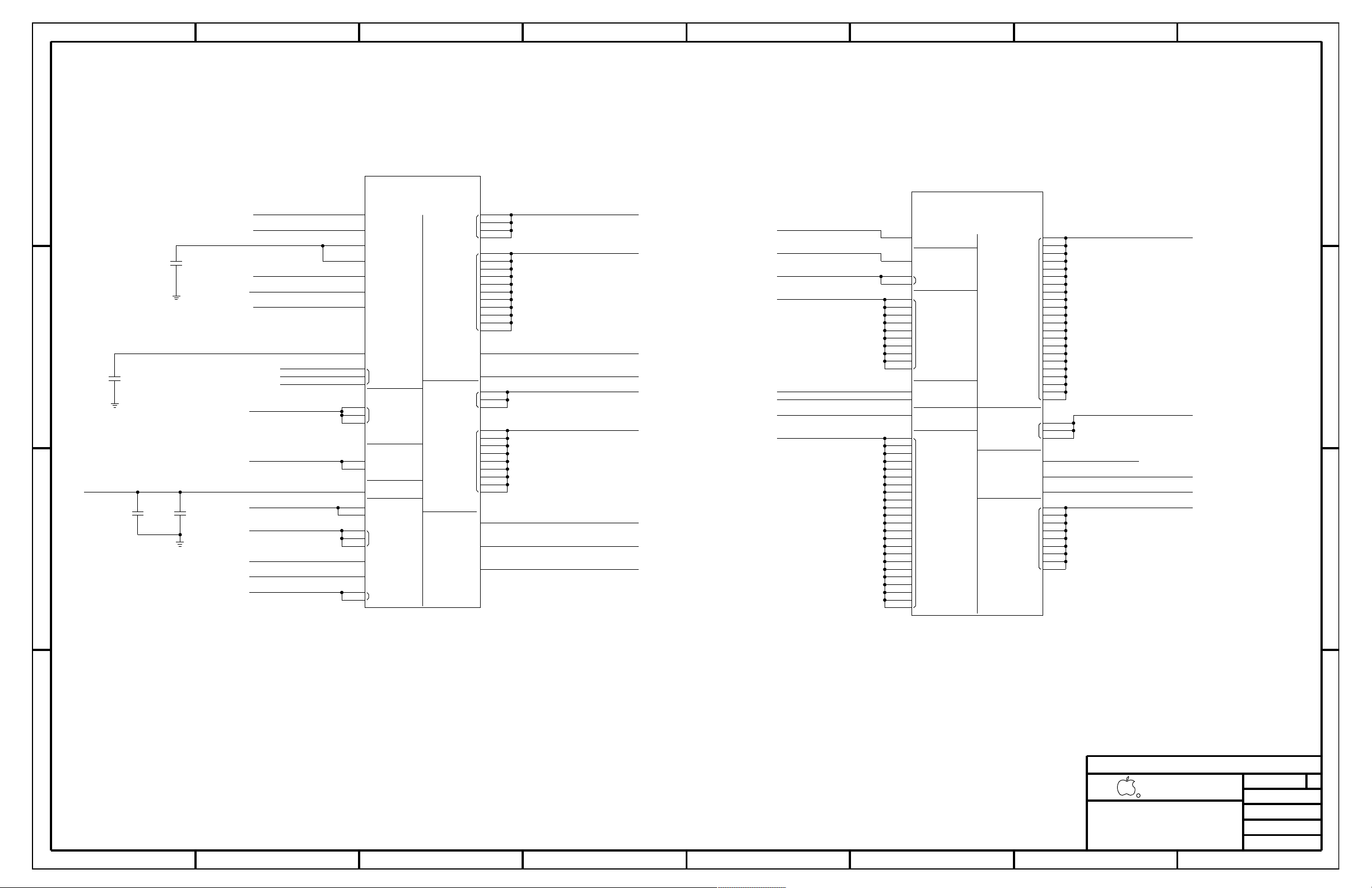

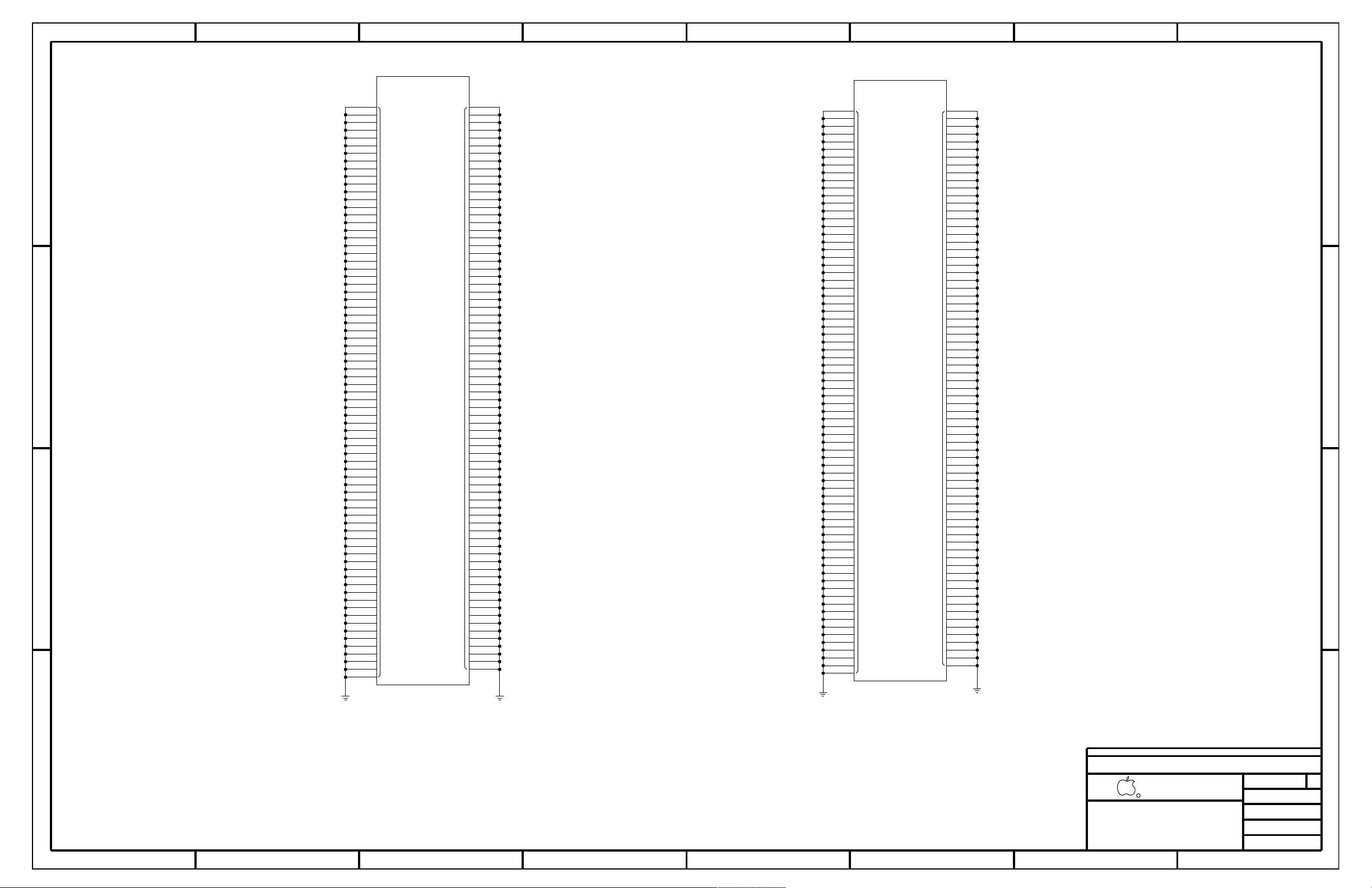

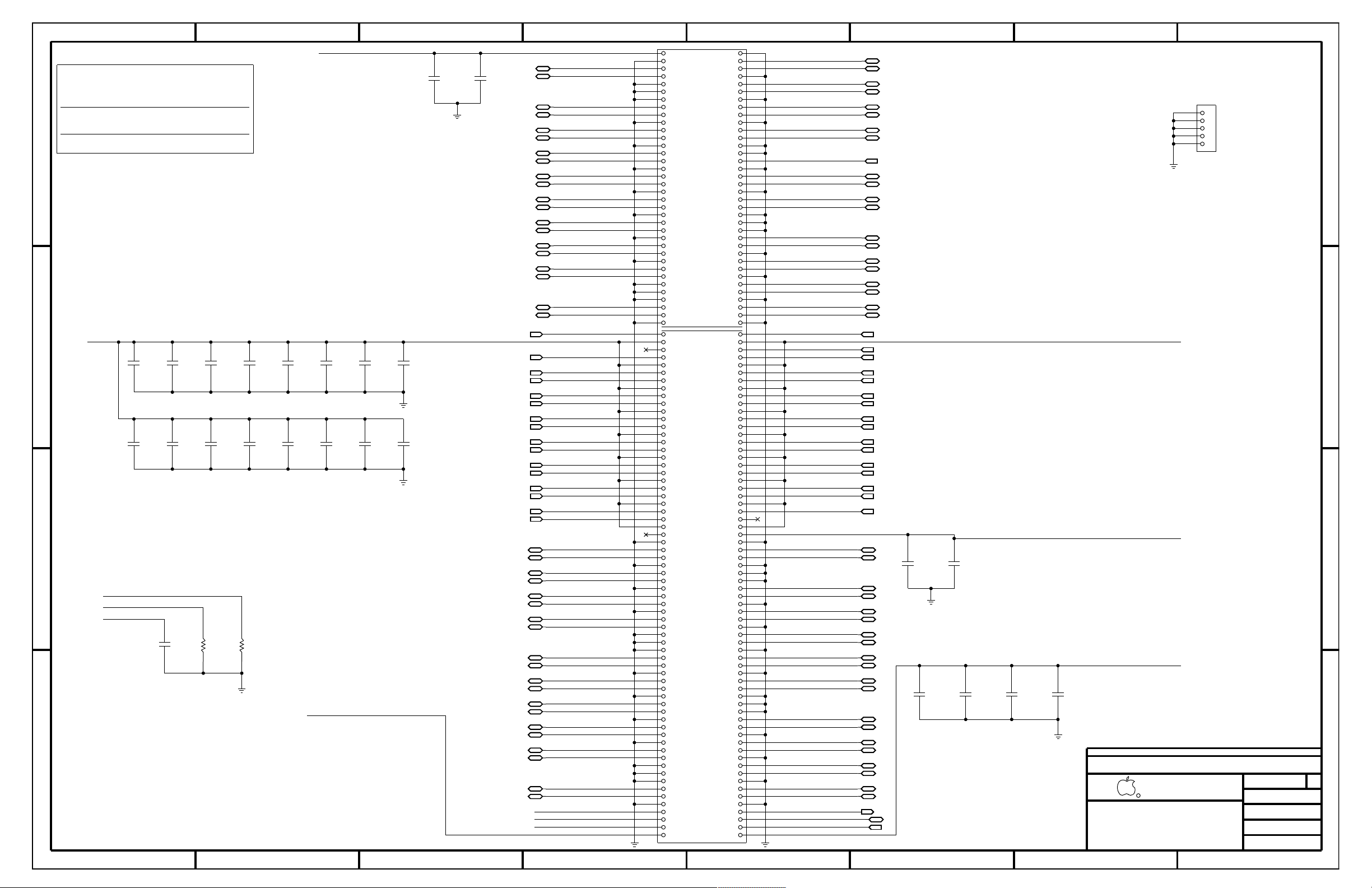

DDR3 SO-DIMM Connector A Slot0

03/19/2012

30

30

D8_KOSECOFF

DDR3 SO-DIMM Connector A Slot1

03/19/2012

31

31

D8_KOSECOFF

DDR3 SO-DIMM CONNECTOR B SLOT0

03/19/2012

32

32

D8_KOSECOFF

DDR3 SO-DIMM CONNECTOR B SLOT1

03/19/2012

33

33

D8_KOSECOFF

DDR3 ALIASES AND BITSWAPS

03/19/2012

34

34

D8_KOSECOFF

DDR3/FRAMEBUF VREF MARGINING

07/02/2012

35

35

D8_FIYIN

AIRPORT/BT

N/A

36

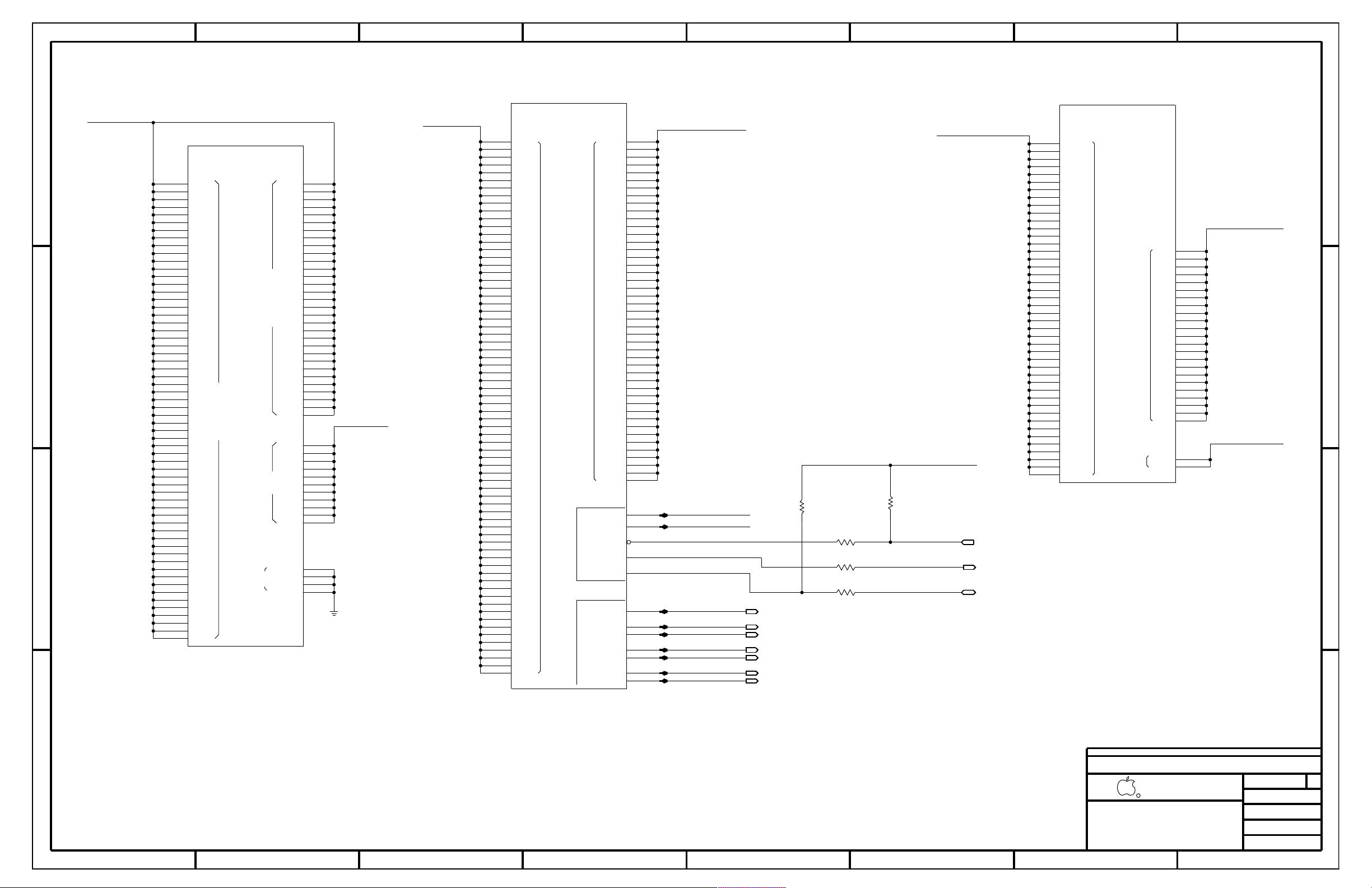

36

D8_MLB

Thunderbolt Host (1 of 2)

03/15/2012

37

37

D7_MLB

Thunderbolt Host (2 of 2)

03/15/2012

38

38

D7_MLB

Thunderbolt Power Support

07/02/2012

39

39

D8_FIYIN

ETHERNET PHY (CAESAR IV+)

07/02/2012

40

40

D8_FIYIN

Ethernet Support & Connector

07/02/2012

41

41

D8_FIYIN

SD READER CONNECTOR

03/23/2012

42

42

D8_ROSITA

Camera Controller

03/15/2012

43

43

D7_MLB

Camera Controller Support

01/31/2012

45

44

D8_JERRY

SATA Connectors

03/23/2012

46

45

D8_ROSITA

EXTERNAL USB PORTS A & B

03/23/2012

47

46

D8_ROSITA

EXTERNAL USB PORTS C & D

03/22/2012

49

47

D8_MARK

SMC

07/19/2012

50

48

D8_DOUG

SMC Support

N/A

51

49

D8_MLB

SPI and Debug Connector

06/22/2012

52

50

D8_TAVYS

SMBus Connections

06/20/2012

53

51

D8_DOUG

I and V Sense 1

02/25/2012

54

52

D8_JERRY

HDD/SSD Temp Sense

06/07/2012

55

53

D8_DOUG

Temperature Sensors

07/19/2012

56

54

D8_DOUG

System Fan

04/23/2012

59

55

D8_MARK

I and V Sense 2

06/13/2012

61

56

D8_DAVID

AUDIO: CODEC/REGULATORS

06/13/2012

62

57

D8_DAVID

AUDIO: HEADPHONE AMP

06/13/2012

63

58

D8_DAVID

AUDIO: LEFT SPKR AMP

06/13/2012

64

59

D8_DAVID

AUDIO: RIGHT SPKR AMP

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

System Block diagram can be found on Kismet

PATH: Kismet > K70/72 > Block Diagrams > K70 Block Diagram

D8_MLB

01/05/2012

System Block Diagram

prefsb

051-9504

7.0.0

2 OF 143

2 OF 117

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

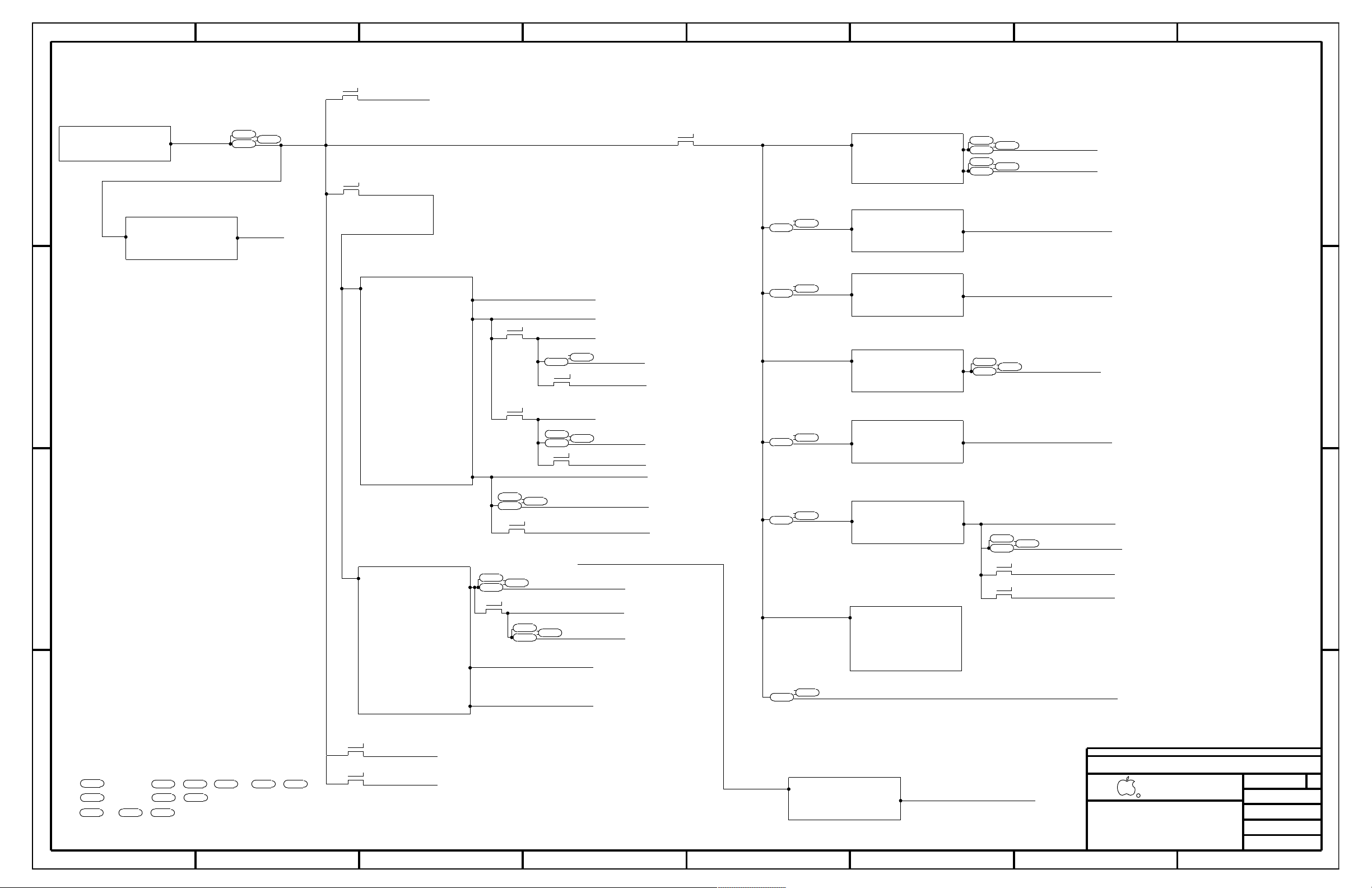

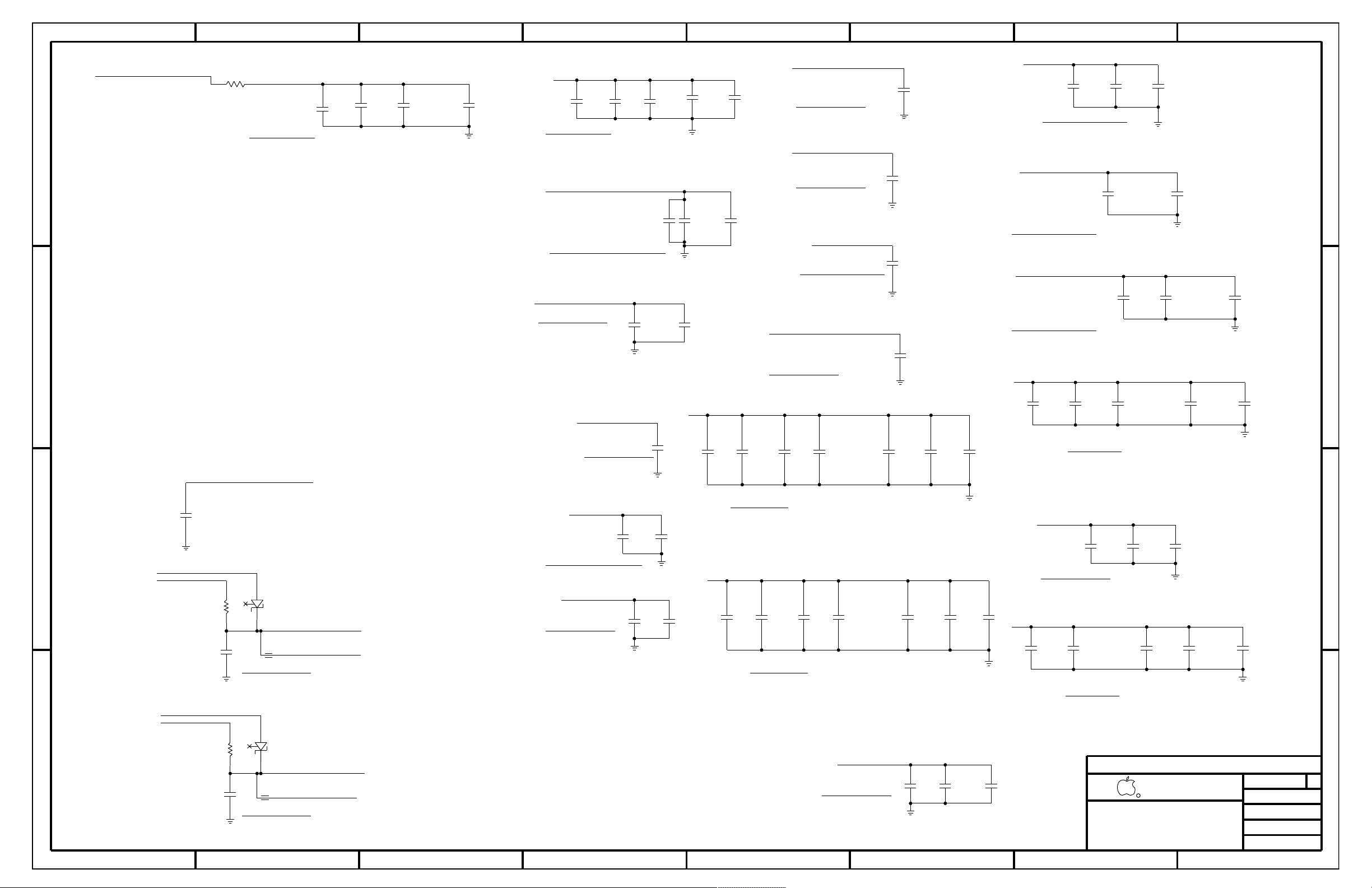

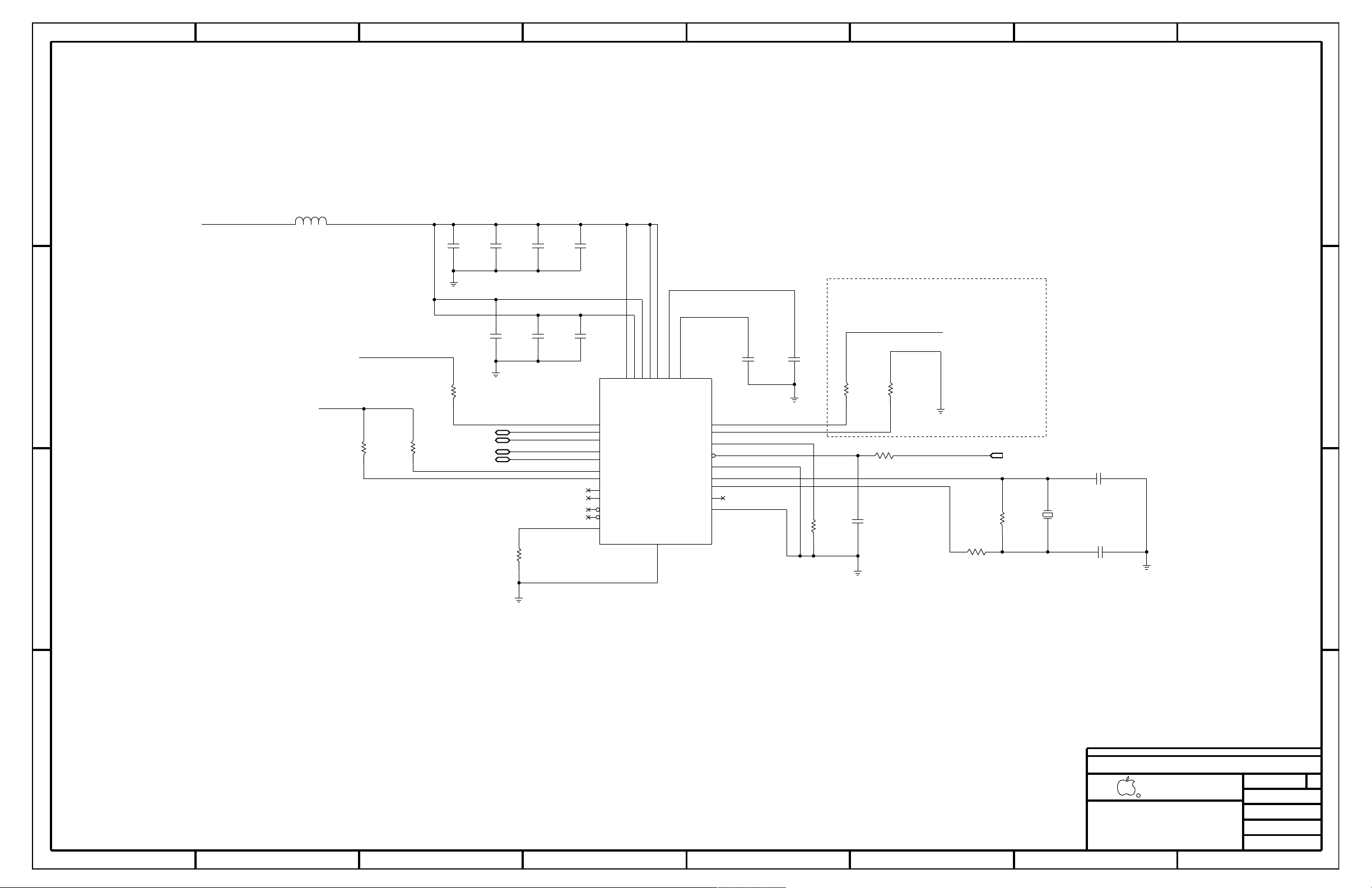

Regulator

U7600

PP3V42_G3H

IW0R

Fan

TBT IO

Speaker amps

GPU

LCD

PPVCCSA_S0

PP1V05_S0_CPU

PPVCORE_S0_CPU

PPVAXG_S0

PPFBVDDQ_S0_GPU

PPVCORE_S0_GPU

GPU (Core)

GPU (FB)

CPU (AXG)

CPU

CPU (Core)

CPU (VccIO)

PP1V05_TBTCIO

PP1V05_TBTLC

P1V05_S0_PCH

P1V05_S0

TBT Router

TBT Router

GPU (IOVDD, PLLVDD)

PCH (VCC, VccIO)

PP12V_S0_HDD

HDD (12V)

PH0R

PGTR

=

=

PH02+PH05

=

PCTR

SMC, RTC, MojoMux

PP12V_G3H

en

Regulator

VD2R

PR1R

IR1R

RegS0

Vin

UB700

en

S0

1V05

SD Card, DP Mux, DP X-bar

VD2R

PG0F

VD2R

IG0F

PC0S

Regulator

S0

FBVDDQ

GPU

3.3V

PCH, PwrCtl

Regulator

U7801

Reg

Vin

G3H G3H

3V42

VccIO

S0S0 Reg

Vin

en

Regulator

U7400

Bootrom, PCH, SMC, XDP,

Audio, LCD TCON, SnsCtl, VRD, PCH

PP5V_S0

VRegCtl, SnsCtl

Audio, PCH

PP5V_S0_HDD

HDD (5V)

PP5V_S4

CAM, USB Ports, VRegCtl

PH05

IH05

VH05

SSD

PP3V3_S0_SSD

PH1R

IW1R

V3V3

PP3V3_S0

VG0C

VC0C

USB Hub, SMC, TBT I/O

PP3V3_S4_ENET

PP3V3_S4

WIFI

PP3V3_S4_AP

PW0R

V3V3

SD Card, USB Mux, VRD, PwrCtl

PP3V3_TBTLC

TBT Router

Ethernet

IC0S

S4RegS4

en 5V

S0LDOS0

en

VTT

VTT

LDO S3

S3Reg

en

S3

Regulator

U7700

Vin

VDDQ

IM0R

VM0R

PM0R

PPDDRVTT_S0

DIMM (VTT)

DIMM VREF Margining CA

IC0M

VC0M

PC0M

PPDDRVTT_S3

PP1V5_S0

PPVDDQ_S3_DDR

PP1V5_S0_CPU_MEM

CPU (Mem)

Audio

DIMM (1V5)

Vin

PH02

IH02

VD2R

UB750

Regulator

Loads

IN1R

VN1R

PN1R

en

S0 Reg

GPU

S0

UB400

Vin

en

S0Reg

IG0C

PG0C

U7100

Vin

S0

Regulator

AXG

VC0G

IC0G

PC0G

S0Reg

Core

IC0C

PC0C

en

Reg

VccSA

S0

VD2R

VD2R

IC0I

PC0I

Regulator

U7500

Vin

PPHV_SW_TBTAPWR

PPHV_SW_TBTBPWR

TBT Port A

TBT Port B

PD2R

ID2R

Supply Module

PP5V_S0

en

Vin

S0

U7750

Regulator

Reg S0

1.8V

PP1V8_S0_REG

CPU PLL

en

PP12V_S5

S5Reg

Vin

PP5V_S5

PP12V_S0_BLC

S5 LDO5VS5

PP12V_ACDC

12V

G3H

AC/DC

Reg

ALS, CAM, BT

en

PP3V3_S5

S0

PP12V_S0

S0Reg

PC0I

+

PC0S

+

)

PC0MPC0G

+

PC0C

(

+

5.7 (GK104/GK107_BLENDED_CONSTANT)

+

PG0F

+

PG0C

1.176 *

1.176 *

High-side Component Total Power Keys

SYNC_DATE=04/23/2012

SYNC_MASTER=D8_MARK

Power Block Diagram

prefsb

051-9504

7.0.0

3 OF 143

3 OF 117

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_BOMGROUP_ITEM

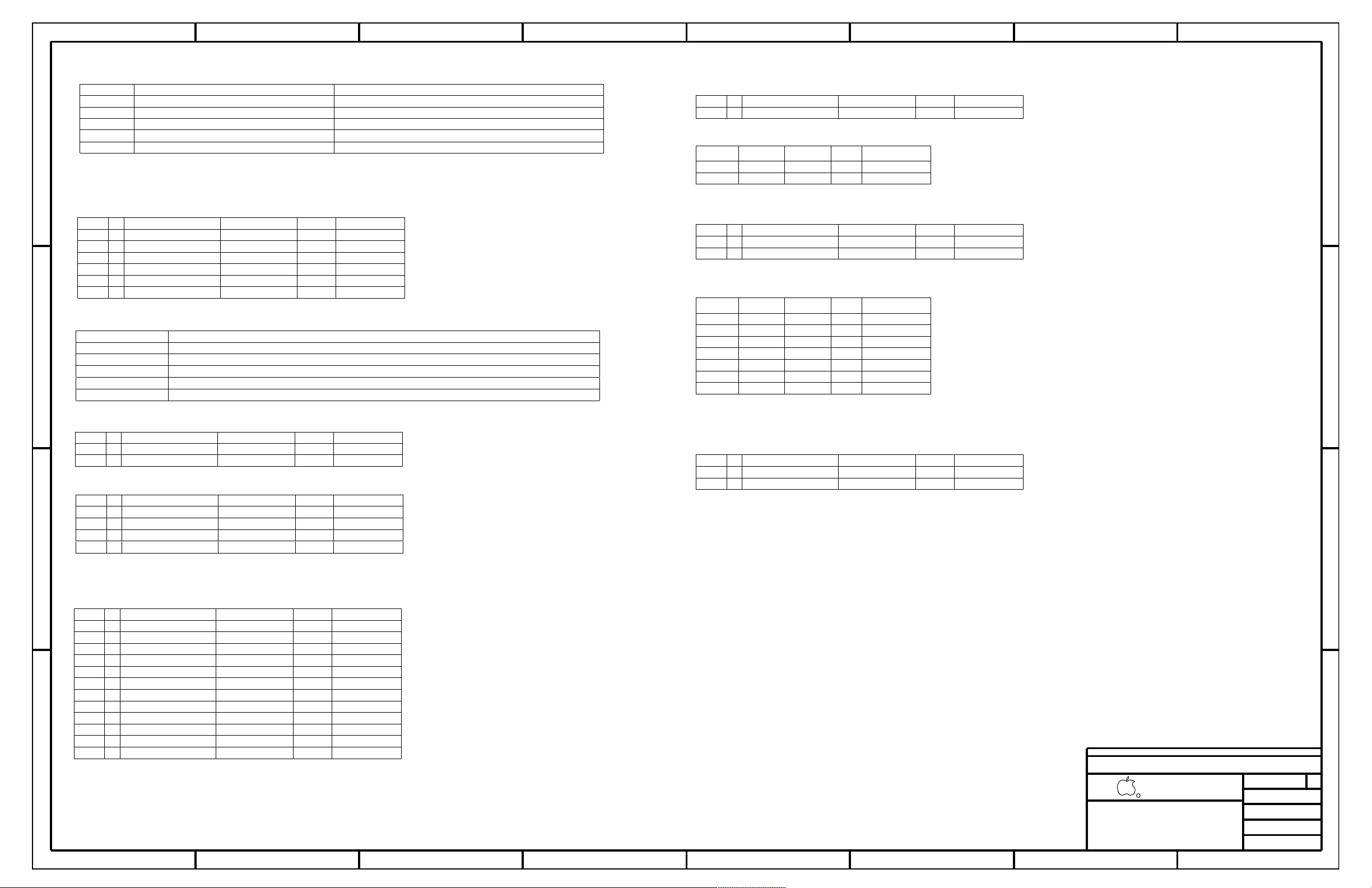

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

BOM OPTIONS

BOM NAME

BOM NUMBER

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_5_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

BOM Groups

CPUs

Programmable Parts

ALTERNATE:335S0854

ASICs

ALTERNATE:335S0812

BOM Variants

CPU SOCKET ALTERNATES

D8 SCHEMATIC / PCB #’S

CPU SOCKET

D8 ALTERNATES

VRAM MODULE PARTS

Bar Code Labels / EEEE #’s

D8_COMMON,D8,CPU:4C_3P1GHZ,GPU:107EGE,FB:BOTH_SAMSUNG,EEEE:F49T

639-3952

PCBA,MLB,3.1G,4C,GK107,SAM,D8

D8_COMMON,D8,CPU:4C_2P9GHZ,GPU:107EGE,FB:BOTH_HYNIX,EEEE:F653

639-4092

PCBA,MLB,2.9G,4C,GK107,HYN.D8

639-4093

D8_COMMON,D8,CPU:4C_3P1GHZ,GPU:107EGE,FB:BOTH_HYNIX,EEEE:F654

PCBA,MLB,3.1G,4C,GK107,HYN.D8

PCBA,MLB,DEV,D8

085-4433

DEVELOPMENT,D8_DEVEL

IC, GPU, NV GK107-GE-PS-A2

337S4280

U8000

CRITICAL

GPU:107EGE

1

825-7896

LABEL,MLB,2D

EEEE_DHNM

CRITICAL

1

EEEE:DHNM

CRITICAL

FB:BOTH_SAMSUNG

333S0619

IC,SGRAM,GDDR5,32MX32,1.5GHz,G-DIE,HF

U8400,U8450,U8500,U8550

4

333S0620

4

IC,GDDR5,32MX32,1.5GHZ,VEGA 44NM,B-DIE

FB:BOTH_HYNIX

U8400,U8450,U8500,U8550

CRITICAL

377S0147

ALL

USB diodes

377S0126

U3990

CRITICAL

CIVROM:PROG

1

341S3645

IC,ENET 1MBIT, SPI,ROM, V1.13 D8

CAMROM:BLANK

CRITICAL

1

U4202

335S0852

IC,FLASH,SPI,1MBIT,3V3

338S1098

U4900

SMC:BLANK

IC,SMC,LX4FS1AH5BBCIGA3

1

CRITICAL

SMC:PROGCRITICAL

1

U4900

341S3394

IC,PROGRMD,SMC,A3,V2.2A32,D8

CRITICAL

U4202

CAMROM:PROG

1

341S3675

IC,CAMERA FLASH,V7228,D7/D8

511S0071

ALL

511S0073

TYCO SOCKET

511S0073

ALL

511S0072

FOXCONN SOCKET

U1000

511S0073 CRITICAL

1

SOCKET,MOLEX,LGA1155,CPU-LF

D8_COMMON,D8,CPU:4C_2P9GHZ,GPU:107EGE,FB:BOTH_SAMSUNG,EEEE:F2FR

639-3816

PCBA,MLB,2.9G,4C,GK107,SAM,D8

157S0084

Enet Magnetics

ALL

157S0058

IC,BCM57766A1,ENET&SD,8X8

343S0616

1

U3900

CRITICAL

IC,TBT,CR-4C,B1,PRQ,288 FCBGA,12X12MM

338S1113

U3600

CRITICAL

1

IC,PANTHER POINT,C1,SLJC7,PRQ,BD82Z77

337S4277

U1800

CRITICAL

1

1

337S3978

CRITICAL

BLCMCU:BLANK

U9700

IC,BLC MCU LPC2132FBD64/01, LQFP64

TBTROM:PROG

CRITICAL

1

U3690

341S3672

IC,EEPROM,CR,V14.1 (B1),D8

1

CRITICAL

U3690

TBTROM:BLANK

IC,EEPROM,SERIAL,8KB,MLP8

335S0865

U9700

BLCMCU:PROG

CRITICAL

341S3674

IC,BLC,MCU, PRPOGRAMMED, V0204, D8

1

1

U3990

CRITICAL

CIVROM:BLANK

335S0862

IC,SERIAL FLASH,2MBIT, 2.7V, REF F

335S0807

1

BOOTROM:BLANK

CRITICAL

U5110

IC,64 MBIT SPI SERIAL FLASH

CRITICAL

BOOTROM:PROG

1

U5110

IC,PROGRMD,EFI ROM,V00FC,D7/D8

341S3673

376S0975

ALL

376S1081

P/NCH DUAL FET

PCBF,MLB,D8

CRITICALPCB1

1

D8820-3298

1

CRITICALSCH1 D8SCH,MLB,D8051-9504

341S3644

U3990

CIVROM

341S3645

150UF CAPS BLK

128S0368128S0365

ALL

102S0880

0.010 OHM,1%,1206

102S0879

ALL

ALL

138S0804

2.2UF CAPS SOFT

138S0803

825-7896

LABEL,MLB,2D

EEEE_F2FR

1

CRITICAL

EEEE:F2FR

LABEL,MLB,2D

CRITICAL

1

EEEE:F49VEEEE_F49V

825-7896

337S4372 CRITICAL

1

CPU

IVB,SR0T9,PRQ,N0,3.1,65W,4+1,1.1,6M,LGA

CPU:4C_3P1GHZ

BOM Configuration

SYNC_MASTER=D8_MLB

SYNC_DATE=12/19/2011

1

LABEL,MLB,2D

CRITICAL

EEEE:F653EEEE_F653

825-7896

337S4355

CPU

1

CRITICAL

IVB,SR0TA,PRQ,N1,2.9,65W,4+1,1.1,6M,LGA

CPU:4C_2P9GHZ

D8_DEVEL

XDP_CONN,LPCPLUS,VREFMRGN:EXT,DEVEL_AUDIO,TEMPSNSDEV

SMC:PROG,BOOTROM:PROG,TBTROM:PROG,CIVROM:PROG,CAMROM:PROG,BLCMCU:PROG

D8_PROGPARTS

XDP,RSMRST:GATE,SPEAKERID,VREF:CPU,TBTHV:P12V,FBA,FBB

D8_COMMON1

D8_PRODUCTION

VREFMRGN:N,PRODUCTION

D8_COMMON

COMMON,ALTERNATE,D8_COMMON1,D8_PROGPARTS,D8_PRODUCTION

825-7896

EEEE:F654EEEE_F654

CRITICAL

LABEL,MLB,2D

1

825-7896

LABEL,MLB,2D

EEEE_F49T

CRITICAL

1

EEEE:F49T

prefsb

051-9504

7.0.0

4 OF 143

4 OF 117

IN

G

D

S

IN

G

D

S

IN

G

D

S

IN

G

D

S

G

D

S

IN

IN

G

D

S

IN

G

D

S

IN

G

D

S

IN

G

D

S

IN

G

D

S

IN

G

D

S

IN

G

D

S

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

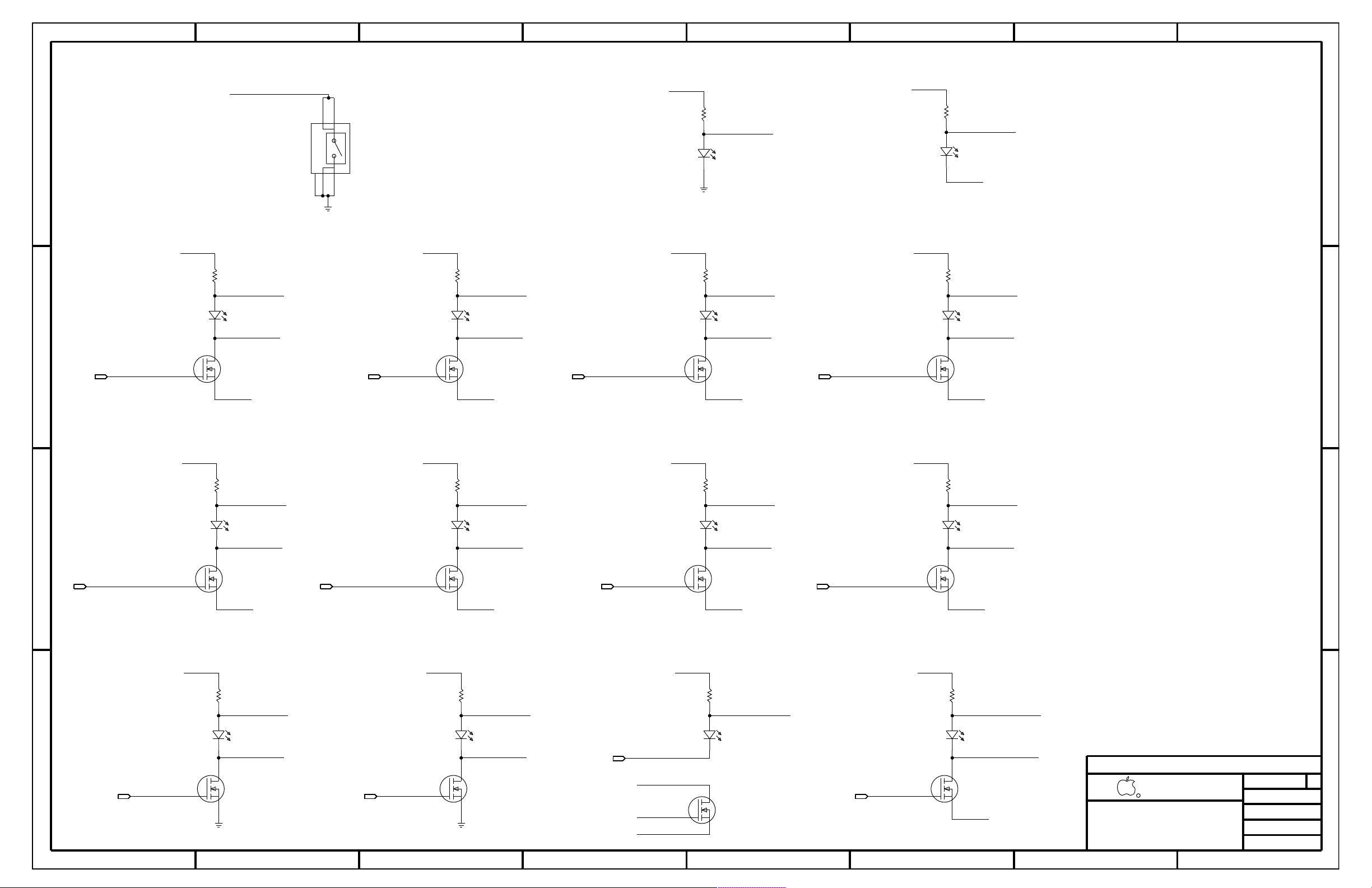

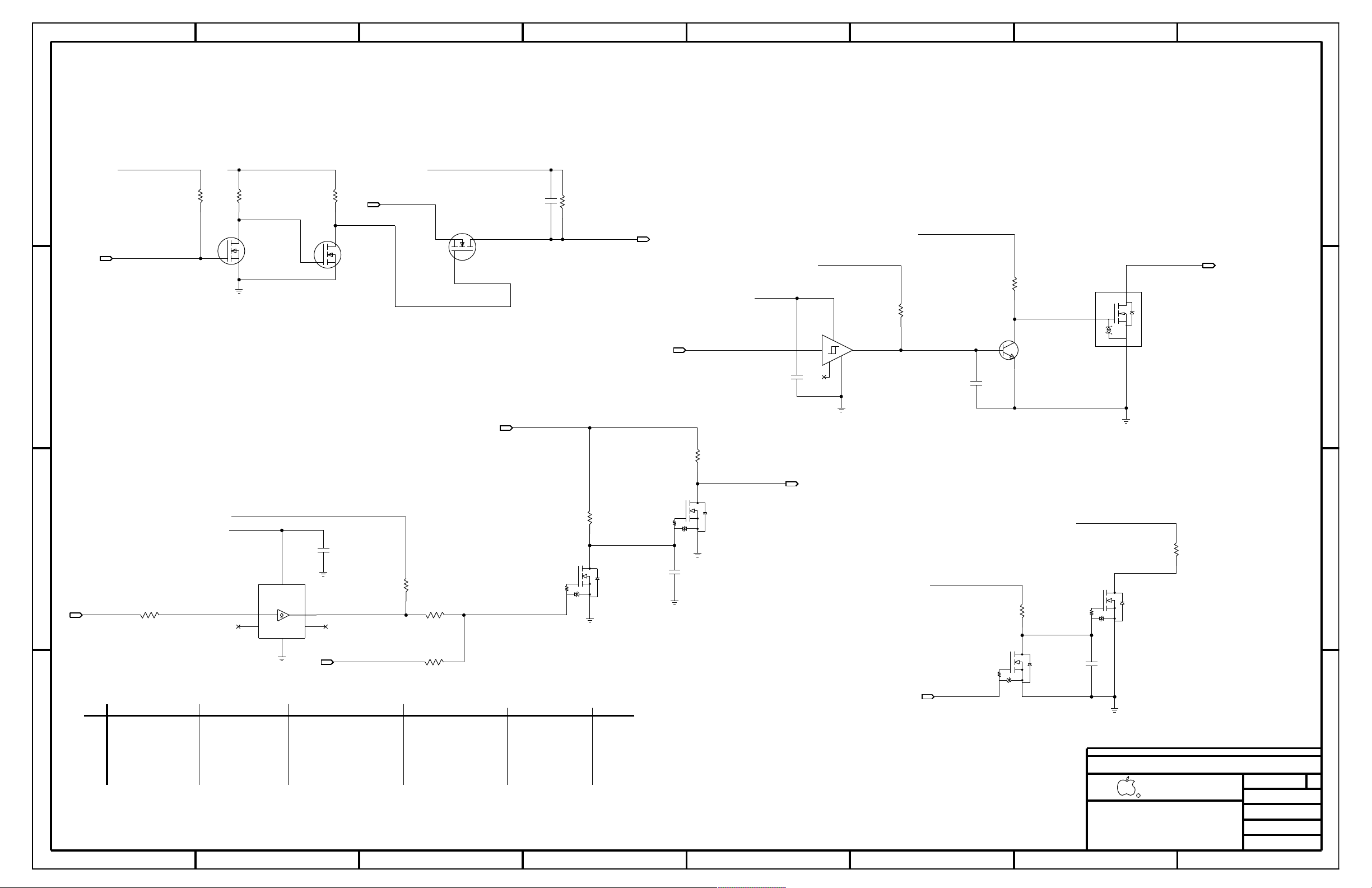

MEM 1V5_S3 LED

LED GND ISOLATION SWITCH

ALL_SYS_PWRGD LED

S5 LED

CPU 1V05_S0 LED

S4 (SLEEP) LED

GPU FBVDD LED

CPU VCORE LED

BLC_EN LED

CPU AXG LED

PCH/GPU 1V05 LED

GPU_GOOD LED VIDEO_ON LED

GPU VCORE LED

SLP_S3 LED

APN: 705S0137

64 69

115

5%

1/16W

1K

402

R507

DEVELOPMENT

MF-LF

2.0X1.25MM-SM

GREEN-3.6MCD

LED507

DEVELOPMENT

SOT-363

Q507

2N7002DW-X-G

DEVELOPMENT

64 95

115

402

MF-LF

5%

1/16W

1K

R502

DEVELOPMENT

2.0X1.25MM-SM

GREEN-3.6MCD

LED502

DEVELOPMENT

1/16W

MF-LF

5%

402

1K

R512

LED512

GREEN-3.6MCD

SILK_PART=3

2.0X1.25MM-SM

PLACE_SIDE=BOTTOM

2N7002DW-X-G

SOT-363

Q511

1/16W

1K

5%

402

R511

MF-LF

SILK_PART=2

LED511

PLACE_SIDE=BOTTOM

GREEN-3.6MCD

2.0X1.25MM-SM

21 99

Q511

SOT-363

2N7002DW-X-G

47 65

112

MF-LF

402

1K

5%

1/16W

R501

2.0X1.25MM-SM

SILK_PART=1

LED501

PLACE_SIDE=BOTTOM

GREEN-3.6MCD

5%

1/16W

R513

1K

MF-LF

402

GREEN-3.6MCD

2.0X1.25MM-SM

LED513

SILK_PART=4

PLACE_SIDE=BOTTOM

SOT-363

2N7002DW-X-G

Q513

1/16W

MF-LF

5%

1K

402

R514

DEVELOPMENT

2.0X1.25MM-SM

GREEN-3.6MCD

LED514

DEVELOPMENT

SOT-363

2N7002DW-X-G

Q513

DEVELOPMENT

89

87

107

SM

SW500

KMT221GLHS

DEVELOPMENT

1/16W

1K

5%

R505

402

MF-LF

DEVELOPMENT

GREEN-3.6MCD

2.0X1.25MM-SM

LED505

DEVELOPMENT

SOT-363

Q505

2N7002DW-X-G

DEVELOPMENT

64 92

110

402

MF-LF

1/16W

5%

R506

1K

DEVELOPMENT

GREEN-3.6MCD

2.0X1.25MM-SM

LED506

DEVELOPMENT

Q505

SOT-363

2N7002DW-X-G

DEVELOPMENT

64 95

115

402

5%

1K

1/16W

MF-LF

R503

DEVELOPMENT

LED503

2.0X1.25MM-SM

GREEN-3.6MCD

DEVELOPMENT

SOT-363

Q503

2N7002DW-X-G

DEVELOPMENT

64 72

115

1/16W

MF-LF

5%

1K

402

R504

DEVELOPMENT

GREEN-3.6MCD

LED504

DEVELOPMENT

2.0X1.25MM-SM

2N7002DW-X-G

Q503

SOT-363

DEVELOPMENT

15 19 28 40 47 48 64

115

5%

1K

MF-LF

1/16W

402

R510

DEVELOPMENT

2.0X1.25MM-SM

GREEN-3.6MCD

LED510

DEVELOPMENT

GREEN-3.6MCD

LED509

2.0X1.25MM-SM

DEVELOPMENT

402

1K

5%

1/16W

MF-LF

R509

DEVELOPMENT

SOT-363

2N7002DW-X-G

Q509

DEVELOPMENT

25 65 66

115

Q509

SOT-363

2N7002DW-X-G

DEVELOPMENT

1/16W

MF-LF

5%

1K

402

R508

DEVELOPMENT

GREEN-3.6MCD

LED508

DEVELOPMENT

2.0X1.25MM-SM

66

116

2N7002DW-X-G

Q507

DEVELOPMENT

SOT-363

SYNC_MASTER=D8_TAVYS

DEBUG LEDS

SYNC_DATE=06/22/2012

ALL_SYS_PWRGD

PM_LED_A_PGOOD_REG_GPUCORE_S0

=PP3V3_S5_LED

GPU_GOOD

PM_LED_K_ALL_SYS_PWRGD

PM_LED_K_GPU_GOOD

=PP3V3_S4_LED =PP3V3_S0_LED =PP3V3_S0_LED

PM_LED_A_VIDEO_ON

VIDEO_ON_L

NO_TEST=TRUE

NC_Q513_1

NO_TEST=TRUE

NC_Q513_6

NC_Q513_2

NO_TEST=TRUE

PM_PGOOD_REG_P1V05_S0

=PP3V3_S0_LED

PM_PGOOD_REG_VDDQ_S3

=PP3V3_S5_LED

PM_LED_A_PGOOD_REG_VDDQ_S3

PM_LED_K_PGOOD_REG_VDDQ_S3

LED_GND

PM_LED_K_PGOOD_REG_P1V05

LED_GND

PM_LED_A_PGOOD_REG_P1V05

PM_PGOOD_REG_CPU_P1V05_S0

LED_GND

PM_SLP_S3_L

=PP3V3_S0_LED

PM_LED_K_PGOOD_CPU_P1V05_S0

LED_GND

PM_LED_K_SLP_S3

PM_LED_A_SLP_S3

REG_CPUAXG_PGOOD

LED_GND

PM_PGOOD_REG_GPUCORE_S0

PM_LED_A_CPUAXG_PGOOD

PM_LED_K_CPUAXG_PGOOD

=PP3V3_S0_LED

LED_GND

PM_LED_K_PGOOD_REG_GPUCORE_S0

=PP3V3_S5_LED

PM_PGOOD_REG_CPUCORE_S0

PM_PGOOD_REG_FBVDDQ_S0

BLC_GOOD

LED_GND

=PP3V3_S0_LED

LED_GND

PM_LED_K_BLC_GOOD

PM_LED_A_BLC_GOOD

PM_LED_K_PGOOD_CPUCORE_S0

PM_LED_A_PGOOD_CPUCORE_S0

=PP3V3_S0_LED

LED_GND

PM_LED_K_PGOOD_REG_FBVDDQ_S0

=PP3V3_S5_LED

PM_LED_A_PGOOD_REG_FBVDDQ_S0

LED_GND

=PP3V3_S4_LED

PM_LED_A_S4

PM_LED_A_PGOOD_CPU_P1V05_S0

PM_LED_A_GPU_GOOD

PM_LED_A_ALL_SYS_PWRGD

PM_LED_A_S5

=PP3V3_S5_LED

MIN_NECK_WIDTH=0.2 MM

LED_GND

MIN_LINE_WIDTH=0.3 MM

prefsb

051-9504

7.0.0

5 OF 143

5 OF 117

1

2

K

A

6

2

1

1

2

K

A

1

2

K

A

3

5

4

1

2

K

A

6

2

1

1

2

K

A

1

2

K

A

6

2

1

1

2

K

A

3

5

4

13

24

5

1

2

K

A

6

2

1

1

2

K

A

3

5

4

1

2

K

A

6

2

1

1

2

K

A

3

5

4

1

2

K

A

K

A

1

2

3

5

4

6

2

1

1

2

K

A

3

5

4

5 6

115

5 6 5 6 5 6

115

5 6

5 6

5

5 5

5 6

5

115

115

5

115

115

5 6

5

5 6

5

5 6

5

115

115

5 6

5

5 6

5

5 6

115

115 115

115

5 6

5

OUT

OUT

OUT

IN

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

FILTER ADDED TO BURSTMODE_EN_L TO PASS SURGE RDAR://11059712

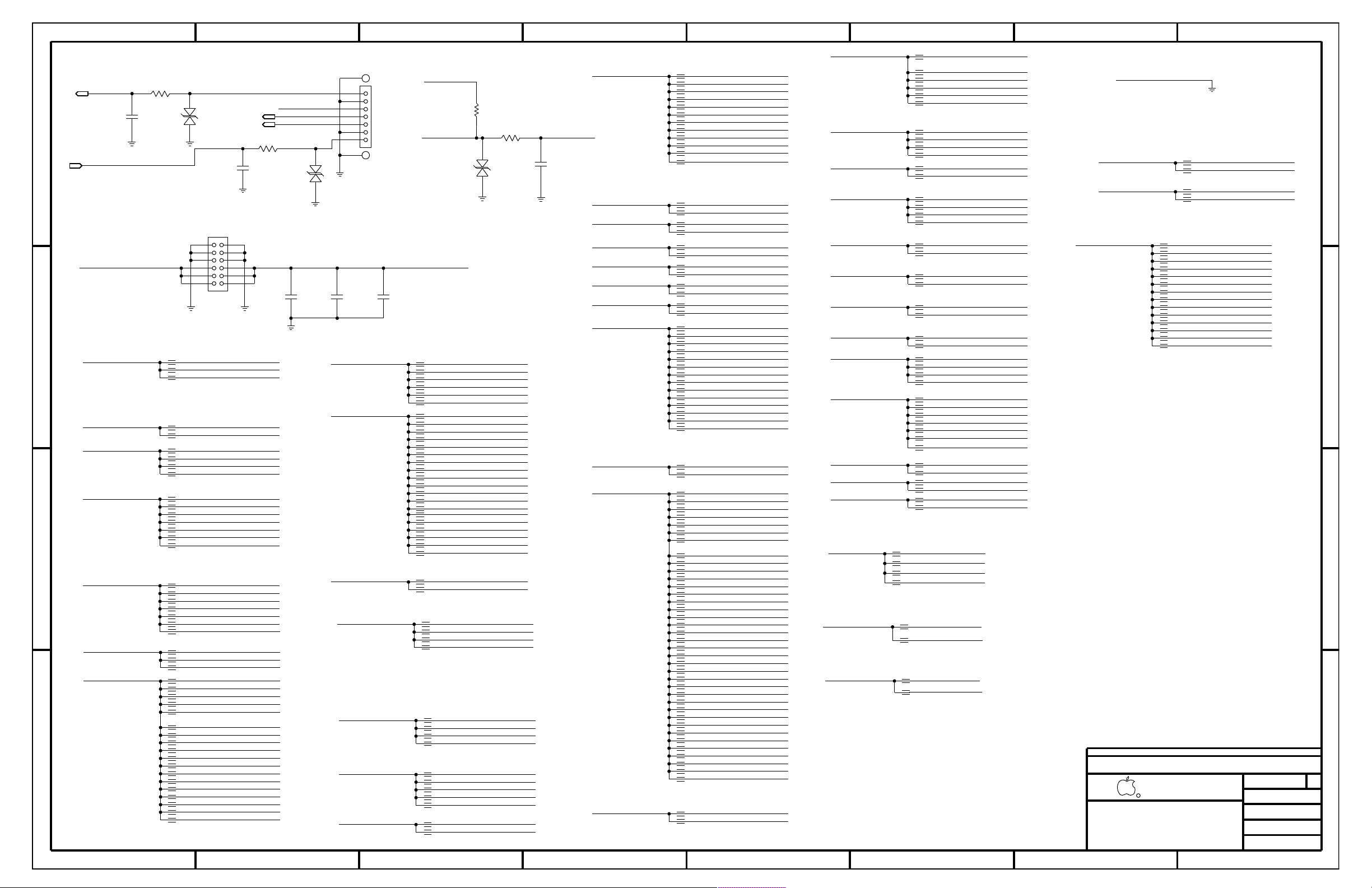

MLB to AC-DC Supplemental Signal Connector

MLB to AC-DC Connector

S5 Rails

On when in S5

G3 Rails

518-0389

518S0863

Always on: Keeps the PCH RTC alive

THIS IS 1.5V RAIL

THIS IS 1.5V RAIL

THIS IS 1.5V RAIL

S3 Rails

Enabled when system is in run or sleep

GPU Rails (S0)

Enabled when system is in run

Ground/Common

S0 Rails

Enabled when system is in run

Enabled when Thunderbolt cable is plugged in

Thunderbolt Rails (S0)

G3H Rails

On with AC/DC plugged in

Enabled when system has AC and is in run or sleep

S4 Rails

J600.5:10MM

EMC

25V

5%

402

NP0-C0G

1000PF

C603

J600.5:10MM

EMC

402

25V

5%

C602

1000PF

NP0-C0G

C601

10%

805

X5R

25V

10UF

J600.4:10MM

53

117

J601

504050-0791

M-RT-SM

SILK_PART=PWRSIG

PLACE_NEAR=J601.3:30MM

R603

402

1/16W

MF-LF

10K

5%

53

117

5%

R606

PLACE_NEAR=J601.1:3MM

1/16W

402

MF-LF

1K

6.8V-100PF

402

D600

PLACE_NEAR=J601.1:3MM

48

116

MF-LF

PLACE_NEAR=J601.3:3MM

1K

402

R604

1/16W

5%

PLACE_NEAR=R604.2:3MM

C604

20%

X7R-CERM

0402

0.01UF

16V

PLACE_NEAR=J601.1:4MM

402

6.8V-100PF

D601

48 71

112

PLACE_NEAR=J601.7:3MM

R600

5%

402

1/16W

1K

MF-LF

PLACE_NEAR=J601.7:3MM

D602

6.8V-100PF

402

43045-1201

CRITICAL

M-RT-TH-1

J600

PLACE_NEAR=R606.1:3MM

X7R-CERM

16V

10%

C600

0.1UF

0402

PLACE_NEAR=R600.1:3MM

16V

0402

X7R-CERM

0.1UF

10%

C605

SYNC_MASTER=D8_DOUG

Power Connectors/Aliases

SYNC_DATE=06/20/2012

PP1V8_S0

MAKE_BASE=TRUE

=PP1V8_S0_PCH_VCC_VRM

=PP1V8_S0_PCH_CLK

PP1V8_S0_REG

=PP1V8_S0_CPU_PLL

=PP1V8_S0_PCH

=PP1V8_S0_PCH_VCC_DFTERM

=PP1V5_S0_DP

PP1V5_S0_CPU_MEM_SNS

=PP1V5_S0_CPU_MEM

=PP12V_S0_FAN

=PP12V_S0_HDD_PWR

=PP12V_S0_REG_CPU_P1V05_PWR

SMC_ACDC_ID

PP12V_S0

MAKE_BASE=TRUE

=PP12V_S0_PWRCTL

=PP12V_S0_REG_P1V05_PWR

=PP12V_S0_REG_CPU_VCCSA_PWR

=PP5V_S0_VRD

MAKE_BASE=TRUE

PP5V_S0

=PP12V_S0_REG_CPUCORE

=PP12V_S0_LCD

=PP12V_S0_REG_GPUCORE

=PP12V_S0_FBVDDQ_PWR

PP12V_S0_FET

=PP12V_S0_AUDIO_SPKRAMP

PP5V_S4_REG

=PP5V_S4_REG_VDDQ_S3

=PP3V3_S0_VRD

TSNS_ACDC_N

TSNS_ACDC_P

PWR_BTN_R

MAKE_BASE=TRUE

PP3V3_G3

MAKE_BASE=TRUE

PP12V_G3H

MAKE_BASE=TRUE

PP3V42_G3H

SMC_ACDC_ID_R

SMC_ACDC_ID_R

=PP3V3_G3H_LPCPLUS

=PPVIN_G3H_SMCVREF

PP3V42_G3H_REG

=PP3V3_G3H_BT

=PP12V_G3H_FET_P12V_S5

=PP3V3_G3_PCH

PP12V_ACDC

MAKE_BASE=TRUE

=PP3V3_S0_PCH_GPIO

=PP3V3_S0_PCH_VCC_GPIO

=PP3V3_S0_PCH_VCC_ADAC

=PP3V3_S0_PCH_STRAPS

PP12V_S5_FET

=PP3V3_TBT_CLK

PPVCCSA_S0_REG

PPCPUAXG_S0_REG

PPCPUCORE_S0_REG

=PP3V3_S0_SMBUS_TCON

PP3V3_S0_SSD_SNS

=PP3V3_S0_TBTPWRCTL

=PP3V3_S0_SMC

=PP3V3_S0_SMBUS_SMC

=PP5V_S0_HDD_PWR

=PP3V3_S0_DP

=PP3V3_S0_ENET

=PP3V3_S0_FAN

=PP3V3_S0_GPU

=PP3V3_S0_INTDPMUX

=PP3V3_S0_LED

=PP3V3_S0_MEM_A_SPD

=PP3V3_S0_PCH

=PP3V3_S0_PCH_VCC

PP5V_S0_HDD_SNS

=PP5V_S0_HDD

=PP3V3_S0_GPU_IFPX_PLLVDD

PP3V3_S0_FET

=PP1V05_S0_GPU_IFPEF_IOVDD

=PP1V05_S0_GPU_PEX_PLLVDD

=PP1V05_S0_GPU_PEX_IOVDD

=PP1V05_S0_GPU_IFPCD_IOVDD

=PP1V05_S0_PCH_PWR

=PP1V05_S0_P1V05TBTFET

PP1V05_S0_REG

=PPVCCIO_S0_CPU

=PPVCCIO_S0_SMC

=PPVCCIO_S0_XDP

PP1V05_S0_CPU_REG

=PPVAXG_S0_CPU

=PPVCORE_S0_CPU

=PPVCCSA_S0_CPU

PPDDRVREF_DQ_MEM_B

=PPDDRVREF_DQ_MEM_B

PPDDRVREF_CA_MEM_B

=PP3V3_TBTLC_RTR

PP12V_S0_REG_CPU_P1V05_SNS

=PP1V05_S0_PCH_VCCIO_DMI

=PPDDRVREF_CA_MEM_B

PP5V_S0_FET

=PP12V_S0_REG_P1V05

=PP12V_S0_REG_VCCSA

=PPDDRVTT_S0_MEM_A

=PPDDRVTT_S0_MEM_B

=PP1V5_S0_CPU_MEM_PWR

=PPVCORE_S0_GPU

=PP1V05_S0_PCH_VCCIO_USB

PPDDRVREF_DQ_MEM_A

=PP3V3_S0_MEM_B_SPD

=PP3V3_S0_AUDIO

=PP3V3_S0_AUDIO_DIG

PP12V_S0_REG_CPU_VCCSA_SNS

=PP5V_S0_REG_P1V05

PP12V_S0_REG_P1V05_SNS

=PPDDRVREF_CA_MEM_A

PP1V05_S0_PCH_SNS

=PP1V05_S0_PCH

=PPDDRVREF_DQ_MEM_A

=PP1V05_S0_PCH_VCC_DMI

=PP1V05_S0_PCH_VCC_DIFFCLK

=PP1V05_S0_PCH_VCC_ADPLL

=PP1V05_S0_PCH_VCCIO_SATA

=PP1V05_S0_PCH_VCCIO_PCIE

=PP1V05_S0_PCH_VCCCLKDMI

=PP1V05_S0_PCH_VCC_SSC

=PP1V05_S0_PCH_V_PROC_IO

=PP1V35_S0_GPU_FBVDDQ

PPGPUCORE_S0_REG

=PP3V3_S0_PCH_PM

=PP3V3_S0_P3V3TBTFET

PP1V5R1V35_S0_GPU_REG

=PP5V_S0_REG_FBVDDQ

=PP1V05_S0_PCH_VCC_CORE

=PP1V05_S0_PCH_VCC_ASW

PP1V5_S0_FET

=PP1V5_S0_AUD_DIG

=PP3V3_S0_GPU_MISC

=PP3V3_S0_GPU_VDD33

PP12V_S0_FBVDDQ_SNS

=PP3V3_S0_PCH_VCC_PCI

=PP3V3_S0_SDCARD

=PP3V3_S0_RSTBUF

=PP3V3_S0_SSD_PWR

=PPDDRVTT_S0_CLAMP

=PP12V_S0_REG_FBVDDQ

=PP12V_S0_BLC

=PP12V_S0_HDD

PP12V_S0_BLC_FET

PPDDRVTT_S0_LDO

PP12V_S0_HDD_SNS

=PP12V_S0_REG_CPU_P1V05

=PP3V3_S0_PWRCTL

=PP3V3_S0_PCH_VCC_HVCMOS

=PP3V3_S0_LED_SATA

PP5V_S0_HDD

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PPDDRVTT_S0

PPDDRVREF_DQ_MEM_A_S3

MAKE_BASE=TRUE

PP1V5_S0

MAKE_BASE=TRUE

PPVCORE_S0_GPU

MAKE_BASE=TRUE

PP12V_S0_FBVDDQ

MAKE_BASE=TRUE

PP1V05_TBTLC

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PPFBVDDQ_S0_GPU

MAKE_BASE=TRUE

PP12V_S0_CPU_P1V05

PP12V_S0_VCCSA

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PPDDRVREF_CA_MEM_A_S3

MAKE_BASE=TRUE

PP3V3_S0_SSD

MAKE_BASE=TRUE

PP12V_S0_BLC

MAKE_BASE=TRUE

PP12V_S0_HDD

PPDDRVREF_CA_MEM_B_S3

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PPVAXG_S0

MAKE_BASE=TRUE

PPVCCSA_S0

PPVCORE_S0_CPU

MAKE_BASE=TRUE

PP1V05_S0_CPU

MAKE_BASE=TRUE

PP1V05_S0_PCH

MAKE_BASE=TRUE

PPDDRVREF_DQ_MEM_B_S3

MAKE_BASE=TRUE

PP1V05_S0

MAKE_BASE=TRUE

PP1V5_S0_CPU_MEM

MAKE_BASE=TRUE

PP12V_S0_P1V05

MAKE_BASE=TRUE

PP3V3_TBTLC

MAKE_BASE=TRUE

=PP3V3_TBT_PCH_GPIO

=PP3V3_S0_SENSE

=PP3V3_S0_SMBUS

=PP3V3_TBTLC_FET

=PP1V05_TBTCIO_RTR

=PP1V05_TBTLC_RTR

=PP1V05_TBTLC_FET

=PP3V3_S0_BLC

=PP1V05_TBTCIO_FET

PP1V05_TBTCIO

MAKE_BASE=TRUE

PPVDDQ_S3

MAKE_BASE=TRUE

PPVDDQ_S3_DDR

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PPDDRVTT_S3

=PP5V_S4_MEMRESET

PP3V3_S4_FET

=PP3V3_S4_ALS

=PP3V3_S4_AP_PWR

=PP3V3_S4_ENET

=PP3V3_S4_LED

=PP3V3_S4_MEMRESET

=PP3V3_S4_PWRCTL

=PP3V3_S4_PM

=PP3V3_S4_SENSE

=PP3V3_S4_SMBUS_SMC

=PP3V3_S4_SMC

=PP3V3_S4_TBT

PP3V3_S4_AP_SNS

=PP3V3_S4_AP

PP3V3_S4_ENET_FET

=PP3V3_S4_ENET_SYSCLK

=PP3V3_S4_ENET_FET

=PP3V3_S4_ENET_CLK

PPVDDQ_S3_REG

=PPVDDQ_S3_FET_VDDQ_S0

=PPVDDQ_S3_DDR_PWR

=PPVDDQ_S3_LDO_DDRVTT

PPVDDQ_S3_DDR_SNS

=PPVDDQ_S3_DDR_VREF

=PPVDDQ_S3_MEM_A

=PPVDDQ_S3_MEM_B

=PPVDDQ_S3_MEMRESET

PPDDRVTT_S3_LDO

=PPDDRVTT_S3_VREFCA

PP3V3_G3_RTC

=PP3V3_G3_PCH_RTC

=PP12V_G3H_PWR

PP12V_G3H_SNS

=PP12V_G3H_P3V42

=PP12V_S5_REG_P3V3P5V_S5

=PP12V_S5_REG_VDDQ_S3

=PP5V_S0_REG_CPU_P1V05

=PP5V_S0_REG_CPUCORE

=PP5V_S0_LPCPLUS

=PP5V_S0_ISENSE

=PP5V_S0_PCH

=PP5V_S0_REG_P1V8

=PP5V_S0_REG_VCCSA

=PP5V_S0_AUDIO

=PP5V_S0_BLC

BURSTMODE_EN_R_L

PPDDRVREF_CA_MEM_A

=PP3V3_S0_SSD

=PP3V3_S0_VRD

PP3V3_S0

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PP5V_S4

PP12V_G3H_ACDC

MAKE_BASE=TRUE

PP3V3_S4_ENET

=PP3V3_S4_CAMERA

=PP5V_S4_USB

=PP5V_S4_FET_P5V_S0

=PP5V_S4_CAMERA

PP3V3_S4_AP

MAKE_BASE=TRUE

PP12V_G3H_ACDC

=PP12V_S5_PWRCTL

=PPHV_SW_TBTAPWRSW

MAKE_BASE=TRUE

PP3V3_S5

=PP5V_S5_PWRCTL

PP5V_S5_LDO

=PP5V_S5_PCH

PP3V3_S5_REG

=PP3V3_S5_FET_P3V3_S0

=PP3V3_S5_FET_P3V3_S4

=PP3V3_S5_SMC

=PP3V3_S5_LED

=PP3V3_S5_PCH_STRAPS

=PP3V3_S5_PCH

=PP3V3_S5_PCH_VCCSUS_HDA

=PP3V3_S5_PCH_VCC_DSW

=PP3V3_S5_PCH_VCCSUS_USB

=PP3V3_S5_PWRCTL

=PP3V3_S5_ROM

=PP3V3_S5_PCH_VCC_SPI

=PP3V3_S5_VRD

=PP3V3_S5_XDP

=PP3V3_S5_SMC_USBMUX

=PP3V3_S5_SDCARD

=PP3V3_S5_SENSE

=PPHV_SW_TBTBPWRSW

=PP12V_S5_SNS

PP12V_S5

MAKE_BASE=TRUE

=PP3V3_G3H_SMC_USBMUX

=PP3V3_G3H_SMC

MAKE_BASE=TRUE

PP5V_S5

=PP3V3_G3H_RTC_D

=PP12V_G3H_FET_P12V_S0

PP12V_G3H_ACDC

PWR_BTN

BURSTMODE_EN_L

=PP3V3_S4_SMBUS

=PP3V3_S4_USB_HUB

=PP3V3_S4_TBTAPWRSW

=PP3V3_S4_TBTBPWRSW

=PP3V3_S4_VREFMRGN

=PP3V3_S4_AUDIO_DIG

MAKE_BASE=TRUE

PP3V3_S4

GND

MAKE_BASE=TRUE

prefsb

051-9504

7.0.0

6 OF 143

6 OF 117

2

1

2

1

2

1

8

9

4

2

3

5

6

7

1

1

2

12

1

2

12

2

1

1

2

12

1

2

1

2

3

4

5

6

12

7

8

10

11

9

2

1

2

1

106

24

26

72

13 16

19

22 24

84

51

11 13 16

54

51

55

48

116

106

65

55

55

72 92

106

67

87

92

51

74

58 59

71

72

6

66 69 70 72 92 95

116

106

106

106

6

116

6

116

49

48

73

35

74

18 19

106

15 19 20 38

22 24

17

15

74

26

70

17 68

67 68

50

51

38

48 51 82

50

51

85 87

39

54

78 92

84

5

29 30

18 21 24

22 24

51

52

78

74

78

78

78

78

51

38

95

10 11 13 16 28 66

48

25

69

13 17 51 66

13 16 51 66

13 16

34

31 32

34

15 36 37 38 50

55

22 24

31 32

74

95

70

29 30

31 32

51

51 78

22 24

34

31 32

42 56 58 59 62

60

55

95

55

29 30

51

18 29 30

22 24

22 24

17

18 22 24

18 19 22 24

22 24

22 24

22 24

78

93 94

26

38

95

110

95

22 24

22 24

74

56

78

78

51

22 24

41

26

51

28

95

91

52

74

72

51

69

28 74

22 24

15 44

106

106

106

106

110

106

38

104

106

106

106

106

106

106

106

106

105

104

105

104

104

106

104

106

106

106

15

51 52 53 55

50

38

37

37

38

89

38

104

106

106

106

28

74

42

55

40

5

28

65 72 74

28

51

50

48

36 37 38 86 88

55

15 35

40

26

39 40

26

72

74

51

72

51

34

29 30

31 32

28

72

34

26

115

22

51

51

73

71

72

69

66

49

51

24

72

70

56 63

91

34

44

6

66 69 70 72 92 95

106

106

6

106

42 43

45 46

74

42

106

6

64 65 74

86

106

71

71

24

71

74

74

48

5

15

19 24 26

22 24

22 24

22 24

64 65

49

22 24

71

25

45 46

41

51

88

51

106

45

47 48 50

106

26

74

6

50

27

48 86

48 88

34

60

106

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

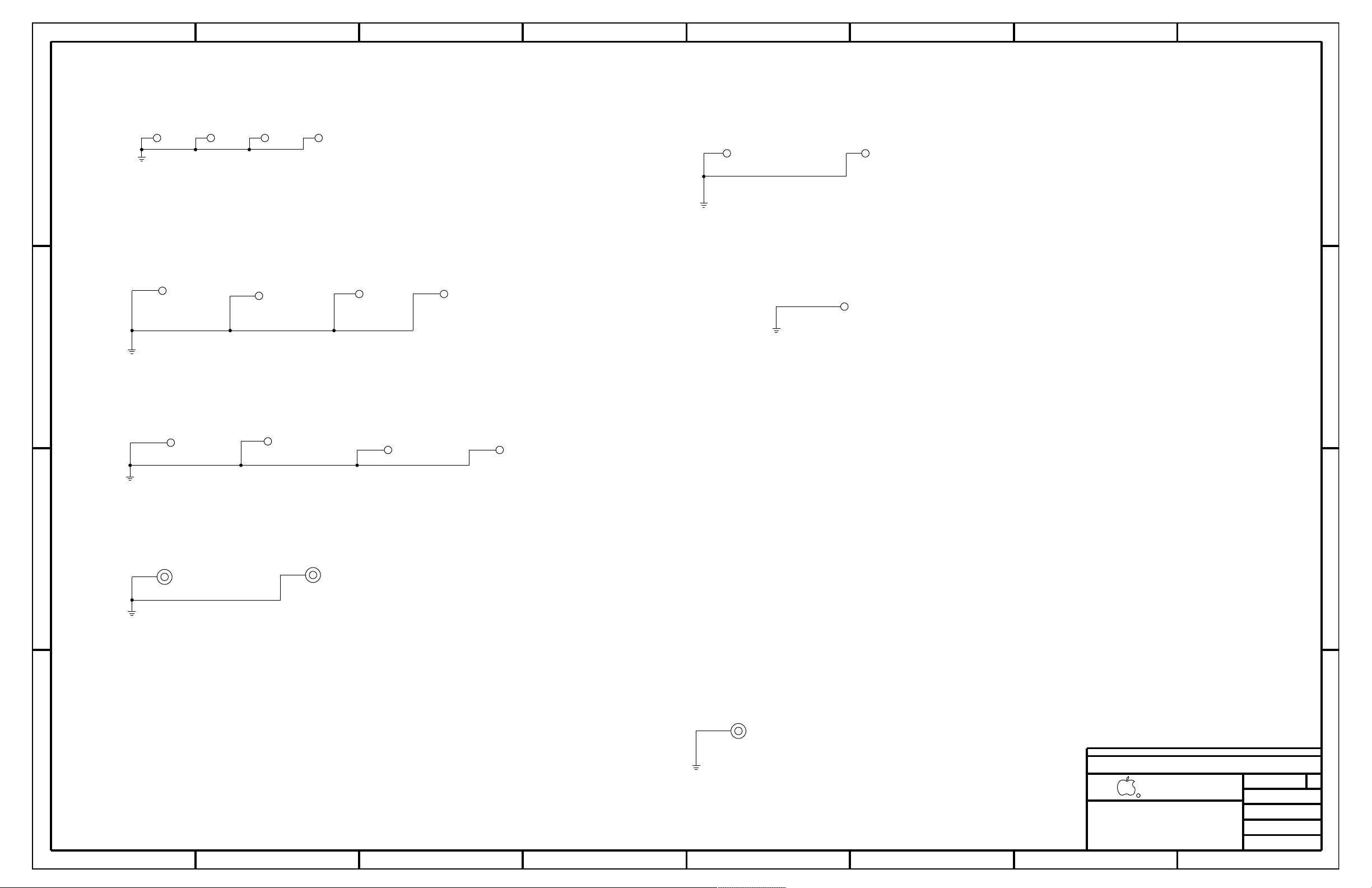

GPU HEATSINK MOUNTING FEATURES

(998-5013. PLATED HOLE, 3.2MM DIA, 6MM PAD TOP/BOT)

998-4640 (PLATED HOLES, 10MM DIA, 12MM PAD)

HEATPIPE MTG HOLES

WIRELESS CARD MTG HOLES

998-4938 (PLATED HOLES, 1.9MM INNER DIAMETER, 4.3MM PAD)

APN: 860-1461

860-1487 (PCB STANDOFF)

SSD STANDOFF

Rear Cover

Rear Cover

998-5014 (PLATED HOLES, 4MM DRILL, 8.5MM TOP, 8MM BOT)

4MM PLATED HOLES (998-4158)

CPU Heatsink

ZH0700

8P5R5-NSP

OMIT

8P5R5-NSP

OMIT

ZH0701 ZH0702

8P5R5-NSP

OMIT

8P5R5-NSP

OMIT

ZH0703

STDOFF-4.5OD2.2ID-5.6H-SM

NUT0713

CRITICAL

ZH0715

STDOFF-7.14OD16.45H-TH-1.5-5.2

CRITICAL

STDOFF-7.14OD16.45H-TH-1.5-5.2

CRITICAL

ZH0718

ZH0722

CRITICAL

5P5R1P9-4P3B-NSP

CRITICAL

5P5R1P9-4P3B-NSP

ZH0721

10R12

ZH0726

6P0R3P2-NSP

CRITICAL

ZH0725

CRITICAL

6P0R3P2-NSP

ZH0724

6P0R3P2-NSP

CRITICAL

ZH0723

ZH0717

8P5R4P0-8P0B-NSP

CRITICAL

ZH0716

8P5R4P0-8P0B-NSP

CRITICAL

CRITICAL

8P5R4P0-8P0B-NSP

ZH0714

CRITICAL

8P5R4P0-8P0B-NSP

ZH0713

CRITICAL

ZH0720

6P0R3P2-NSP

SYNC_MASTER=D8_MLB

Holes/PD parts

SYNC_DATE=03/25/2012

prefsb

051-9504

7.0.0

7 OF 143

7 OF 117

1111

1

1

1

11

1

11

1

11

1

1

1

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

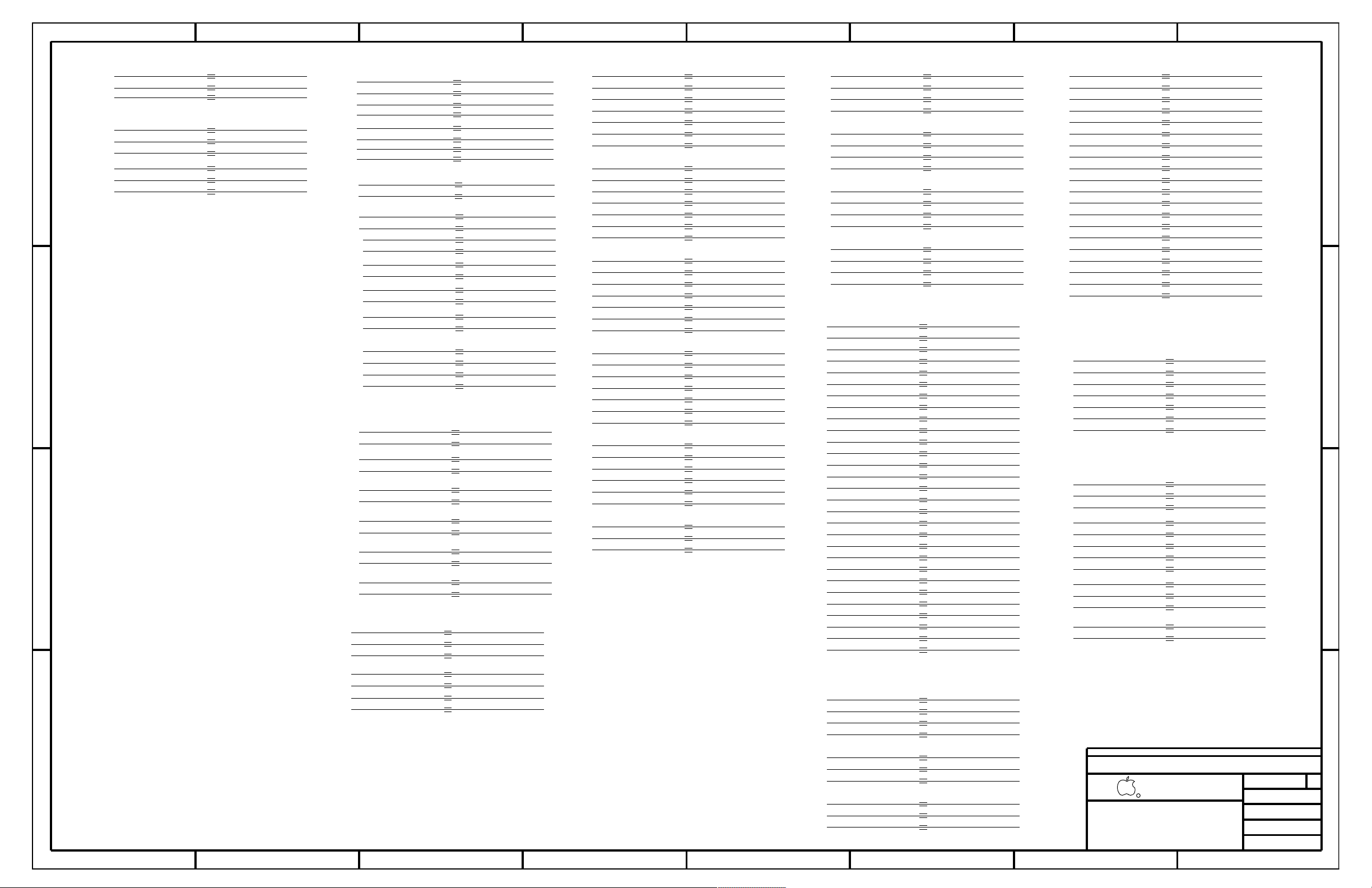

PCH Clocks

PCH PCIe

PCH USB

CPU Memory

PCH PCI

PCH Unused Display

PCH Test Points

PCH SATA

PCH and CPU FDI

PCH Miscellaneous

CPU Reserved

PCH Reserved

SYNC_DATE=04/02/2012

Unused Signal Aliases

SYNC_MASTER=D8_MLB_ULTIMATE

TP_MEM_A_DQS_P<8>

TP_MEM_A_DQ_CB<7..0>

NC_DMI_MIDBUS_CLK100NX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCIE2_R2D_CNX

MAKE_BASE=TRUE

NO_TEST=TRUE

TP_PCIE2_R2D_CN

TP_PCIE2_R2D_CP

TP_PCI_CLK33M_OUT2

TP_PCI_CLK33M_OUT3

TP_PCH_PWM3

TP_PCH_SST

TP_PCH_RESERVE_0

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_C_AUXNX

DP_IG_C_MLP<3..0>

NC_PCIE_CLK100M_PE5NX

NO_TEST=TRUE

MAKE_BASE=TRUE

TP_PCIE_CLK100M_PE5N

TP_PCIE_CLK100M_PE6P

DMI_MIDBUS_CLK100M_N

NC_DMI_MIDBUS_CLK100PX

MAKE_BASE=TRUE

NO_TEST=TRUE

DMI_MIDBUS_CLK100M_P

TP_PCIE_CLK100M_PE0N

TP_PCIE2_D2RP

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PE_TNX<3..0>

DP_IG_D_CTRL_DATA

DP_IG_D_HPD

TP_PCIE1_D2RN

TP_PCIE1_R2D_CN

TP_MEM_B_DQ_CB<7..0>

CPU_CFG<15..12>

TP_CPU_RSVD<46..19>

TP_CPU_RSVD<16..1>

TP_SATA_D_R2D_CN

TP_SATA_D_R2D_CP

TP_SATA_D_D2RN

TP_SATA_E_D2RN

TP_SATA_F_R2D_CN

TP_MEM_A_DQS_N<8>

TP_PCH_PWM0

TP_HDA_SDIN2

PCH_FDI_FSYNC<1..0>

PCH_FDI_LSYNC<1..0>

PCH_FDI_INT

PCH_FDI_RX_N<7..0>

PCH_FDI_RX_P<7..0>

TP_CPU_FDI_TX_N<7..0>

TP_CPU_FDI_TX_P<7..0>

TP_SDVO_STALLP

TP_SDVO_INTN

TP_CPU_FDI_FSYNC<1..0>

TP_CPU_FDI_LSYNC<1..0>

TP_CPU_FDI_INT

TP_PCH_CL_DATA1

TP_PCH_CL_CLK1

TP_HDA_SDIN3

TP_PCH_RESERVE_8

TP_PCH_L_VDD_EN

TP_PCH_L_BKLTEN

TP_PCH_RESERVE_27

TP_PCH_RESERVE_25

DP_IG_C_MLN<3..0>

DP_IG_B_DDC_DATA

DP_IG_C_AUX_N

TP_SDVO_INTP

TP_PCH_CL_RST1

TP_PCH_PWM2

TP_PCH_PWM1

TP_PCH_RESERVE_20

TP_PCH_RESERVE_23

TP_PCH_RESERVE_7

TP_PCH_RESERVE_19

TP_PCH_RESERVE_21

TP_PCH_RESERVE_28

TP_PCH_RESERVE_24

TP_PCH_RESERVE_17

TP_PCH_RESERVE_18

TP_PCH_RESERVE_15

TP_PCH_RESERVE_16

TP_PCH_RESERVE_14

TP_PCH_RESERVE_13

TP_PCH_RESERVE_12

TP_PCH_RESERVE_10

TP_PCH_RESERVE_11

TP_PCH_RESERVE_9

TP_PCH_RESERVE_5

TP_PCH_RESERVE_6

TP_PCH_RESERVE_3

TP_PCH_RESERVE_4

TP_SDVO_TVCLKINP

DP_IG_C_AUX_P

DP_IG_C_CTRL_CLK

TP_PCH_L_BKLTCTL

TP_SDVO_STALLN

DP_IG_D_MLP<3..0>

TP_SDVO_TVCLKINN

DP_IG_D_AUXN

DP_IG_D_AUXP

DP_IG_D_MLN<3..0>

TP_SATA_F_D2RP

TP_CRT_IG_DDC_DATA

TP_CRT_IG_VSYNC

TP_CRT_IG_BLUE

TP_CRT_IG_RED

TP_CRT_IG_GREEN

TP_SATA_E_R2D_CP

TP_SATA_C_D2RN

TP_SATA_C_D2RP

TP_SATA_C_R2D_CN

TP_PCH_TP20

TP_PCH_TP19

TP_PCH_TP18

TP_PCH_TP17

TP_PCH_TP16

TP_PCH_TP15

TP_PCH_TP13

TP_PCH_TP14

TP_PCH_TP12

TP_PCH_TP11

TP_PCH_TP10

TP_PCH_TP9

TP_PCH_TP8

TP_PCH_TP7

TP_PCH_TP6

TP_PCH_TP5

TP_PCH_TP4

TP_PCH_TP3

TP_SATA_D_D2RP

TP_PCH_TP2

TP_SATA_C_R2D_CP

TP_SATA_E_D2RP

DP_IG_C_HPD

DP_IG_D_CTRL_CLK

DP_IG_C_CTRL_DATA

TP_LPC_DREQ0_L

TP_PCH_INIT3V3_L

TP_HDA_SDIN1

TP_CRT_IG_HSYNC

TP_SATA_F_R2D_CP

TP_PCH_RESERVE_22

TP_PCH_RESERVE_26

TP_SATA_E_R2D_CN

TP_PCH_TP1

TP_SATA_F_D2RN

DP_IG_B_DDC_CLK

TP_PCI_AD<31..0>

TP_PCI_C_BE_L<3..0>

TP_PCI_PAR

TP_PCI_RESET_L

TP_PCH_PCI_GNT0_L

TP_PCH_RESERVE_2

TP_PCH_RESERVE_1

DP_IG_B_AUX_P

DP_IG_B_MLN<3..0>

DP_IG_B_MLP<3..0>TP_MEM_B_DQS_N<8>

TP_MEM_B_DQS_P<8>

DP_IG_B_HPD

TP_PCIE_CLK100M_PE6N

TP_PCIE_CLK100M_PE7P

TP_PE_TX_N<3..0>

TP_PE_RX_N<3..0>

TP_PE_TX_P<3..0>

TP_PE_RX_P<3..0>

USB_PCH_4_P

USB_PCH_6_N

USB_PCH_6_P

USB_PCH_11_P

USB_PCH_12_P

USB_PCH_12_N

USB_PCH_13_P

USB_PCH_13_N

TP_PCH_CLKOUT_DPP

TP_PCIE_CLK100M_PE7N

TP_PCIE2_D2RN

TP_PCIE1_D2RP

TP_CRT_IG_DDC_CLK

TP_PCIE1_R2D_CP

DP_IG_B_AUX_N

MAKE_BASE=TRUE

NC_PCIE2_R2D_PNX

NO_TEST=TRUE

NO_TEST=TRUE

NC_PCIE1_D2RNX

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_MEM_B_DQSNX<8>

MAKE_BASE=TRUE

NC_CPU_RSVD<46..19>

NO_TEST=TRUE

NC_PCH_RESERVE_6

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_C_R2D_CNX

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_D_R2D_CNX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_PWM0

NC_HDA_SDIN3

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_FDI_INT

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SDVO_TVCLKINNX

MAKE_BASE=TRUE

NC_PCH_FDI_FSYNC<1..0>

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_D_AUXPX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_CPU_FDI_LSYNC<1..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_FDI_FSYNC<1..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_FDI_RPX<7..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_FDI_RNX<7..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_FDI_TPX<7..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_L_BKLTEN

NC_PCH_L_VDD_EN

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCI_CLK33M_OUT2

MAKE_BASE=TRUE

NC_PCH_CL_CLK1

NO_TEST=TRUE

NC_PCH_L_BKLTCTL

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NC_PCI_CLK33M_OUT3

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_CL_RST1

NO_TEST=TRUE

NO_TEST=TRUE

NC_PCH_CL_DATA1

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_SST

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NC_PCH_PWM3

NO_TEST=TRUE

NO_TEST=TRUE

NC_PCH_PWM2

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_PWM1

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_D_AUXNX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_D_MLPX<3..0>

NC_PCH_FDI_LSYNC<1..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

NC_CPU_FDI_INT

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_CPU_FDI_TNX<7..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_17

NO_TEST=TRUE

NC_PCH_RESERVE_18

MAKE_BASE=TRUE

NC_PCH_RESERVE_14

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_13

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_12

MAKE_BASE=TRUE

NC_PCH_RESERVE_10

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_11

NC_PCH_RESERVE_9

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_8

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_7

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_5

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_3

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_4

MAKE_BASE=TRUE

NC_PCH_RESERVE_2

NO_TEST=TRUE

NC_PCH_RESERVE_0

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_1

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SDVO_STALLNX

NC_DP_IG_C_HPD

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_D_CTRL_CLK

MAKE_BASE=TRUE

NC_DP_IG_D_HPD

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_D_MLNX<3..0>

NO_TEST=TRUE

NC_DP_IG_C_CTRL_CLK

MAKE_BASE=TRUE

NC_DP_IG_C_CTRL_DATA

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_C_MLPX<3..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_C_MLNX<3..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_F_D2RPX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_F_D2RNX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_F_R2D_CPX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_B_CTRL_CLK

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_B_MLPX<3..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_B_MLNX<3..0>

NC_CRT_IG_DDC_CLK

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CRT_IG_VSYNC

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CRT_IG_BLUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CRT_IG_HSYNC

NC_CRT_IG_RED

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CRT_IG_GREEN

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_E_D2RNX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_E_R2D_CPX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_D_D2RPX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_D_D2RNX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_D_R2D_CPX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_C_D2RNX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_C_D2RPX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP19

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP18

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP17

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP16

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP15

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP13

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP14

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP12

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP11

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP10

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP9

MAKE_BASE=TRUE

NC_PCH_TP8

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP7

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP6

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP5

MAKE_BASE=TRUE

NC_PCH_TP4

NO_TEST=TRUE

NO_TEST=TRUE

NC_PCH_TP1

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NC_PCH_TP2

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP3

NC_CRT_IG_DDC_DATA

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_C_AUXPX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_B_HPD

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_B_AUXPX

NC_PCI_AD<31..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCI_PAR

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

NC_PCI_C_BE_L<3..0>

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NC_PCI_RESET_L

NO_TEST=TRUE

NC_PCI_GNT0_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_LPC_DREQ0_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_INIT3V3_L

NC_HDA_SDIN1

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

NC_HDA_SDIN2

MAKE_BASE=TRUE

NC_CPU_RSVD<16..1>

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_D_CTRL_DATA

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SDVO_STALLPX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SDVO_INTNX

MAKE_BASE=TRUE

NC_MEM_A_DQ_CB<7..0>

NO_TEST=TRUE

NC_MEM_B_DQ_CB<7..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SDVO_TVCLKINPX

MAKE_BASE=TRUE

NC_SDVO_INTPX

NO_TEST=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_27

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_16

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_15

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_E_D2RPX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_F_R2D_CNX

NO_TEST=TRUE

NC_PCH_RESERVE_19

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_20

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_21

MAKE_BASE=TRUE

NC_PCH_RESERVE_22

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_E_R2D_CNX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_23

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_24

NO_TEST=TRUE

NC_PCH_RESERVE_25

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_26

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_28

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP20

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_B_CTRL_DATA

MAKE_BASE=TRUE

NC_MEM_A_DQSNX<8>

NO_TEST=TRUE

NC_MEM_A_DQSPX<8>

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_B_AUXNX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_C_R2D_CPX

MAKE_BASE=TRUE

TP_CPU_CFG<15..12>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_MEM_B_DQSPX<8>

MAKE_BASE=TRUE

NC_PCIE_CLK100M_PE4PX

NO_TEST=TRUE

NC_PCIE_CLK100M_PE4NX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCIE_CLK100M_PE5PX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCIE_CLK100M_PE6NX

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

NC_PCIE_CLK100M_PE6PX

MAKE_BASE=TRUE

NC_PCIE_CLK100M_PE7PX

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCIE_CLK100M_PE7NX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PE_RNX<3..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PE_TPX<3..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PE_RPX<3..0>

NC_USB_PCH_4NX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_USB_PCH_4PX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_USB_PCH_5PX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_USB_PCH_5NX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_USB_PCH_6NX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_USB_PCH_6PX

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_USB_PCH_11PX

NC_USB_PCH_11NX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_USB_PCH_12PX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_USB_PCH_12NX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_USB_PCH_13PX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_USB_PCH_13NX

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_CLKOUT_DPNX

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCIE2_D2RNX

NO_TEST=TRUE

NC_PCIE2_D2RPX

MAKE_BASE=TRUE

NC_PCIE1_D2RPX

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCIE1_R2D_CNX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCIE1_R2D_CPX

TP_PCIE_CLK100M_PE5P

NC_PCH_CLKOUT_DPPX

NO_TEST=TRUE

MAKE_BASE=TRUE

TP_PCH_CLKOUT_DPN

USB_PCH_4_N

USB_PCH_5_N

USB_PCH_5_P

USB_PCH_11_N

NO_TEST=TRUE

NC_PCH_GPIO65_CLKOUTFLEX1

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_GPIO66_CLKOUTFLEX2

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_GPIO67_CLKOUTFLEX3TP_PCH_GPIO67_CLKOUTFLEX3

TP_PCH_GPIO66_CLKOUTFLEX2

TP_PCH_GPIO65_CLKOUTFLEX1

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_GPIO64_CLKOUTFLEX0TP_PCH_GPIO64_CLKOUTFLEX0

PCH_CLK25M_XTALOUT

NO_TEST=TRUE

NC_PCH_CLK25M_XTALOUT

MAKE_BASE=TRUE

NC_PCIE_CLK100M_PE0PX

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCIE_CLK100M_PE0NX

NO_TEST=TRUE

MAKE_BASE=TRUE

TP_PCIE_CLK100M_PE4P

TP_PCIE_CLK100M_PE4N

TP_PCIE_CLK100M_PE0P

prefsb

051-9504

7.0.0

8 OF 143

8 OF 117

12

12

18

18

20

20

21

21

19

19

18

21

18

18

18

18

19

19

18

18

12

10

10

10

18

18

18

18

18

12

21

18

19

19

19

19

19

10

10

19

19

10

10

10

18

18

18

19

18

18

19

19

19

19

19

19

18

21

21

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

18

19

19

19

19

19

19

18

19

19

19

19

19

18

18

18

18

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

18

21 18

18

19

19

19

18

19

18

19

18

19

19

18

21

18

19

20

20

20

20

20

19

19

19

19

19 12

12

19

21

21

10

10

10

10

20

20

20

20

20

20

20

20

18

21

18

18

19

18

19

18

18

20

20

20

20

18

18

18

18

18

18

18

18

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

ALIASES (BLANK)

SYNC_MASTER=K70_MLB

SYNC_DATE=08/23/2011

Signal Aliases

prefsb

051-9504

7.0.0

9 OF 143

9 OF 117

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

DMI_TX_1*

PE_TX_3*

PE_TX_3

PE_TX_2*

PE_TX_2

PE_TX_1*

PE_TX_1

PE_TX_0*

PE_TX_0

PE_RX_3*

PE_RX_3

PE_RX_2*

PE_RX_2

PE_RX_1*

PE_RX_1

PE_RX_0*

PE_RX_0

PEG_TX_15*

PEG_TX_15

PEG_TX_14*

PEG_TX_14

PEG_TX_13*

PEG_TX_13

PEG_TX_12*

PEG_TX_12

PEG_TX_11*

PEG_TX_11

PEG_TX_10*

PEG_TX_10

PEG_TX_9*

PEG_TX_9

PEG_TX_8*

PEG_TX_8

PEG_TX_7*

PEG_TX_7

PEG_TX_6

PEG_TX_5*

PEG_TX_5

PEG_TX_4*

PEG_TX_4

PEG_TX_3*

PEG_TX_3

PEG_TX_2*

PEG_TX_2

PEG_TX_1*

PEG_TX_1

PEG_TX_0*

PEG_TX_0

PEG_RX_15*

PEG_RX_15

PEG_RX_13*

PEG_RX_12

PEG_RX_11*

PEG_RX_11

PEG_RX_10

PEG_RX_9

PEG_RX_8

PEG_RX_7

PEG_RX_6

PEG_RX_5

PEG_RX_4*

PEG_RX_4

PEG_RX_3*

PEG_RX_3

PEG_RX_2

PEG_RX_1*

PEG_RX_0

FDI_TX_7*

FDI_TX_7

FDI_TX_6*

FDI_TX_6

FDI_TX_5*

FDI_TX_5

FDI_TX_4*

FDI_TX_4

FDI_TX_3*

FDI_TX_3

FDI_TX_2*

FDI_TX_2

FDI_TX_1*

FDI_TX_1

FDI_TX_0*

FDI_TX_0

FDI_LSYNC_1

FDI_LSYNC_0

FDI_FSYNC_1

FDI_FSYNC_0

DMI_TX_3*

DMI_TX_3

DMI_TX_2*

DMI_TX_2

DMI_TX_1

DMI_TX_0*

DMI_TX_0

DMI_RX_3*

DMI_RX_3

DMI_RX_2*

DMI_RX_2

DMI_RX_1

DMI_RX_0*

FDI_COMPIO

FDI_ICOMPO

FDI_INT

PEG_COMPI

PEG_ICOMPO

PEG_RX_1

PEG_RX_14*

PEG_RX_12*

PEG_RX_6*

PEG_RX_13

PEG_RX_14

PEG_RCOMPO

PEG_RX_10*

PEG_RX_9*

PEG_RX_8*

PEG_RX_7*

PEG_RX_2*

PEG_RX_0*

PEG_RX_5*

PEG_TX_6*

DMI_RX_0

DMI_RX_1*

SYM 1 OF 10

FLEXIBLE DISPLAY INTERFACE

PCI EXPRESS -- GRAPHICS

DMI

PCI EXPRESS

RSVD_NCTF_AV1

RSVD_NCTF_AW2

RSVD_NCTF_AY3

RSVD_NCTF_B39

NCTF_AW38

NCTF_AU40

NCTF_D1

NCTF_C2

NCTF_A38

CFG_8

RSVD_J34

RSVD_J33

RSVD_J31

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

RSVD_K9

RSVD_K31

RSVD_K34

RSVD_L9

RSVD_L31

RSVD_L33

RSVD_L34

RSVD_M34

RSVD_N33

RSVD_N34

RSVD_P35

RSVD_P37

RSVD_P39

RSVD_R34

RSVD_R36

RSVD_R38

RSVD_R40

RSVD_AB6

RSVD_AB7

RSVD_AD34

RSVD_AD35

RSVD_AD37

RSVD_AE6

RSVD_AF4

RSVD_AG4

RSVD_AJ11

RSVD_AJ29

RSVD_AJ30

RSVD_AJ31

RSVD_AN20

RSVD_AP20

RSVD_AT11

RSVD_AT14

RSVD_AU10

RSVD_AV34

RSVD_AW34

RSVD_AY10

RSVD_J9

RSVD_H8

RSVD_H7

RSVD_C38

RSVD_D38

RSVD_C39

SYM 5 OF 10

RESERVED

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

(Available for Workstation only)

CFG [6:5] PCIE BIFURCATION 11 = 1 X16 (DEFAULT) 10 = 2 X8 01 = RSVD 00 = 1 X8, 2 X4

CFG [3] PCIE STATIC X4 LANE REVERSAL 1 = NORMAL OPERATION 0 = LANES REVERSED

CFG [1:0] RESERVED CONFIGURATION LANE

( IVY BRIDGE EDS #473717 TABLE 6-5 )

CFG [17:7] RESERVED CONFIGURATION LANE

CFG [4] RESERVED CONFIGURATION LANE

INTEL SUGGESTS TO KEEP THESE TPS

ThermDA

ThermDC

(Unused)

ROUTE B5 TO R1010.1 AS A SEPERATE 12 MIL TRACE.

SHORT B4 & C4 TOGETHER, ROUTE AS A SINGLE 4 MIL TRACE TO R1010.1

CFG [2] PCIE STATIC X16 LANE REVERSAL 1 = NORMAL OPERATION 0 = LANES REVERSED

19 99

19 99

19 99

19 99

19 99

19 99

19 99

19 99

19 99

19 99

19 99

19 99

19 99

19 99

19 99

19 99

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

75 98

402

MF-LF

24.9

1%

PLACE_NEAR=U1000.B4:12.7MM

R1010

1/16W

25 99

25 99

8

8

8

8

25 99

25 99

25 99

25 99

25 99

15 25 99

15 25 99

25 99

15 25 99

15 25 99

25 99

25 99

BGA-SKT-K70

IVY-BRIDGE

OMIT_TABLE

U1000

BGA-SKT-K70

OMIT_TABLE

IVY-BRIDGE

U1000

PLACE_NEAR=U1000.AE2:6.3MM

MF-LF

1/16W

402

5%

0

R1011

CPU DMI/PEG/FDI/RSVD

SYNC_DATE=03/23/2012

SYNC_MASTER=D8_ROSITA

CPU_FDI_COMPIO

TP_PE_TX_P<3>

TP_PE_TX_P<2>

TP_CPU_FDI_TX_N<2>

PEG_D2R_C_P<5>

CPU_PEG_COMP

PEG_D2R_C_N<1>

PEG_D2R_C_N<2>

PEG_D2R_C_N<3>

=PPVCCIO_S0_CPU

PEG_D2R_C_P<3>

PEG_D2R_C_N<12>

PEG_D2R_C_N<11>

PEG_D2R_C_N<5>

CPU_CFG<7>

TP_PE_RX_P<1>

TP_CPU_FDI_TX_P<7>

TP_CPU_FDI_TX_P<2>

TP_PE_RX_N<0>

TP_PE_RX_N<3>

TP_PE_RX_P<2>

PEG_R2D_P<14>

TP_CPU_FDI_TX_P<4>

PEG_D2R_C_P<14>

TP_PE_TX_P<0>

DMI_S2N_N<3>

DMI_S2N_N<0>

PEG_R2D_P<11>

PEG_R2D_P<13>

PEG_R2D_P<7>

PEG_D2R_C_N<15>

PEG_D2R_C_P<0>

DMI_S2N_P<2>

DMI_N2S_P<2>

PEG_D2R_C_N<8>

CPU_CFG<15>

PEG_D2R_C_N<4>

CPU_CFG<0>

CPU_CFG<3>

TP_CPU_RSVD<16>

PEG_D2R_C_N<14>

PEG_D2R_C_P<2>

PEG_D2R_C_N<6>

DMI_S2N_P<1>

TP_CPU_FDI_TX_N<6>

PEG_R2D_P<0>

DMI_N2S_N<0>

TP_CPU_FDI_TX_N<3>

TP_CPU_RSVD<30>

DMI_N2S_N<2>

PEG_D2R_C_N<13>

TP_CPU_FDI_FSYNC<1>

TP_PE_RX_P<0>