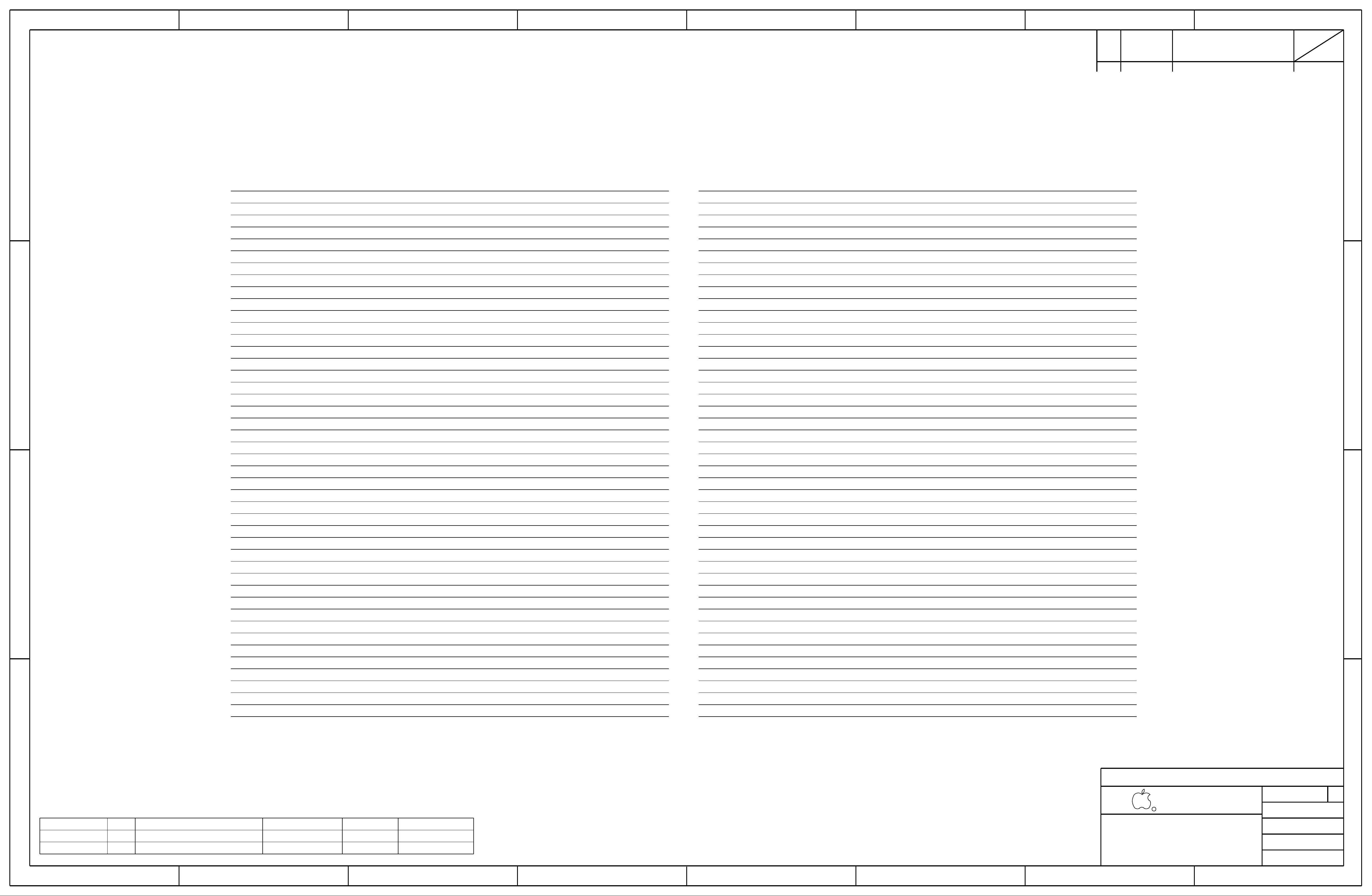

ALIASES RESOLVED

PRODUCT SAFETY REQUIREMENTS:

Schematic / PCB #'s

PCB TO BE SILK-SCREENED WITH UL/CUL RECOGNITION MARK, MANUFACTURER'S UL FILE

PCB, UL RECOGNIZED, MIN. 130-C TEMP. RATING AND V-0 FLAME RATING PER UL 796 & UL 94.

NUMBER, UL PCB MATERIAL DESIGNATION, 130-C TEMP. RATING AND V-0 FLAME RATING.

X260 MLB - CBB

1 OF 67

page76

DEVMLB

page80

page81

15

DEVMLB

05/11/2015

DEVMLB

16

17

page103

J92_DEVMLB

page30

page38

DEVMLB

72

31

page14

05/18/2015

10/24/2012

07/08/2014

DEVMLB

page90

page1010

page16

DEVMLB

page93

page105

J92_LAYOUT_STUDY_MLB

05/11/2015

page19

DEVMLB

page79

DEVMLB

page48

DEVMLB

04/14/2015

J92_DEVMLB

DEVMLB

page31

J72_MLB

page2

page83

page84

page85

10/24/2012

page17

DEVMLB

J43_MLBpage102

42

page69

page67

63

DEVMLB

DEVMLB

DEVMLB

J43_MLB

10/24/2012

page82

LAST_MODIFICATION=Thu Sep 10 15:22:41 2015

page20

67

66

page72

page71

page63

page120

<SYNC_MASTER69>

<SYNC_MASTER70>

07/23/2013

05/11/2015

05/11/2015

05/06/2015

30

05/11/2015

page6

page7

page9

39

page39

page37

page12

DEVMLB

DEVMLB

page50

05/11/2015

page4

DEVMLB

04/14/2015

05/11/2015

04/14/2015

05/11/2015

page91

<SYNC_MASTER76>

24

<SYNC_DATE80>

04/14/2015

04/14/2015

DEVMLB

4

4

<CSA_PAGE69>

63

05/11/2015

page3

page5

page8

page11

page13

page25

page52

page53

page54

page55

page61

page64

page87

page100

page104

3

5

6

7

8

9

11

12

13

14

18

19

20

21

22

23

25

26

27

28

29

30

32

33

34

35

36

37

38

40

43

44

45

46

47

48

49

50

51

52

53

54

55

56

60

61

62

64

65

1

86

DEVMLB

DEVMLB

<CSA_PAGE82>

<CSA_PAGE81>

<CSA_PAGE80>

<CSA_PAGE79>

<CSA_PAGE78>

<SYNC_MASTER90>

<SYNC_MASTER89>

<SYNC_MASTER87>

<SYNC_MASTER86>

<SYNC_MASTER85>

<SYNC_MASTER84>

<SYNC_MASTER83>

<SYNC_MASTER82>

<SYNC_MASTER81>

<SYNC_MASTER79>

<SYNC_MASTER74>

05/11/2015

05/13/2015

05/06/2015

05/11/2015

05/11/2015

04/30/2015

DEVMLB

DEVMLB

DEVMLB

DEVMLB

05/11/2015

05/13/2015

05/13/2015

05/13/2015

05/11/2015

DEVMLB

DEVMLB

79

80

81

82

76

78

J43_MLB

MASTER

J43_MLB

DEVMLB

10/24/2012

MASTER

10/24/2012

6

5

3

2

83

90

87

88

85

84

DEVMLB

DEVMLB

04/14/2015

DEVMLB

05/06/2015

DEVMLB

DEVMLB

DEVMLB

DEVMLB

05/11/2015

05/11/2015

05/11/2015

04/14/2015

05/11/2015

05/13/2015

05/13/2015

04/14/2015

04/09/2015

05/11/2015

05/11/2015

05/11/2015

04/14/2015

05/11/2015

DEVMLB

DEVMLB

03/16/2015

05/11/2015

05/11/2015

DEVMLB

<SYNC_MASTER41>

DEVMLB

05/11/2015

03/16/2015

7

8

10

11

12

13

14

15

16

17

19

20

53

52

51

50

48

40

39

38

37

31

25

23

54

74

71

70

67

64

62

61

55

J92_DEVMLB

J41_MLB

<SYNC_MASTER71>

<SYNC_MASTER72>

<SYNC_MASTER73>

100

102

103

104

105

120

130

<CSA_PAGE70>

<CSA_PAGE71>

<CSA_PAGE72>

<CSA_PAGE73>

<CSA_PAGE74>

<CSA_PAGE75>

<CSA_PAGE76>

<CSA_PAGE77>

9

07/08/2014

MASTER

<SYNC_DATE69>

<SYNC_DATE70>

<SYNC_DATE71>

<SYNC_DATE72>

<SYNC_DATE73>

<SYNC_DATE74>

<SYNC_DATE75>

<SYNC_DATE76>

<SYNC_DATE77>

<SYNC_DATE78>

<SYNC_DATE79>

<SYNC_DATE81>

<SYNC_DATE82>

<SYNC_DATE83>

<SYNC_DATE84>

<SYNC_DATE85>

<SYNC_DATE86>

<SYNC_DATE87>

<SYNC_DATE88>

<SYNC_DATE90>

DEVMLB

91

93

96

<SYNC_MASTER75>

<SYNC_MASTER77>

DEVMLB

03/16/2015

<SYNC_DATE89>

<CSA_PAGE83>

<CSA_PAGE84>

<CSA_PAGE85>

<CSA_PAGE86>

<CSA_PAGE87>

<CSA_PAGE88>

<CSA_PAGE89>

<CSA_PAGE90>

69

41

page74

page70

page96

05/11/2015

DEVMLB

page1

DEVMLB

DEVMLB

DEVMLB

DEVMLB

03/16/2015

<SYNC_MASTER80>

22

05/11/2015

DEVMLB

DEVMLB

59

58

<SYNC_MASTER88>

J92_DEVMLB

57

DEVMLB

DEVMLBpage86

05/11/2015

04/30/2015

<SYNC_MASTER78>

page51

page40

page22

04/14/2015

page130

05/04/2015

page15

page88

1

2

05/11/2015 03/16/2015

DEVMLB

DEVMLB

DEVMLB

DEVMLB

MASTER

page23

page78

DEVMLB

<PART_DESCRIPTION>

<SCH_NUM>

<ECODATE><ECN><REV> <ECO_DESCRIPTION>

1 OF 130

<BRANCH>

<E4LABEL>

PCBF,MLB,X260820-00244 1 PCB CRITICAL

Table of Contents [1]

CRITICALSCHEM,MLB,X2601 SCH051-00532

PROPRIETARY PROPERTY OF APPLE INC.

REVISION

ECNREV DESCRIPTION OF REVISION

DRAWING TITLE

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

CK

APPD

2 1

1245678

B

D

6 5 4 3

C

A

PAGE

C

A

D

DATE

R

SHEET

D

SIZEDRAWING NUMBER

BRANCH

7

B

3

II NOT TO REPRODUCE OR COPY IT

IV ALL RIGHTS RESERVED

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

8

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

NOTICE OF PROPRIETARY PROPERTY:

Apple Inc.

<CSA>

DATEPAGE

<CSA>

DATE

PAGE CONTENTS SYNC

SYNCCONTENTS

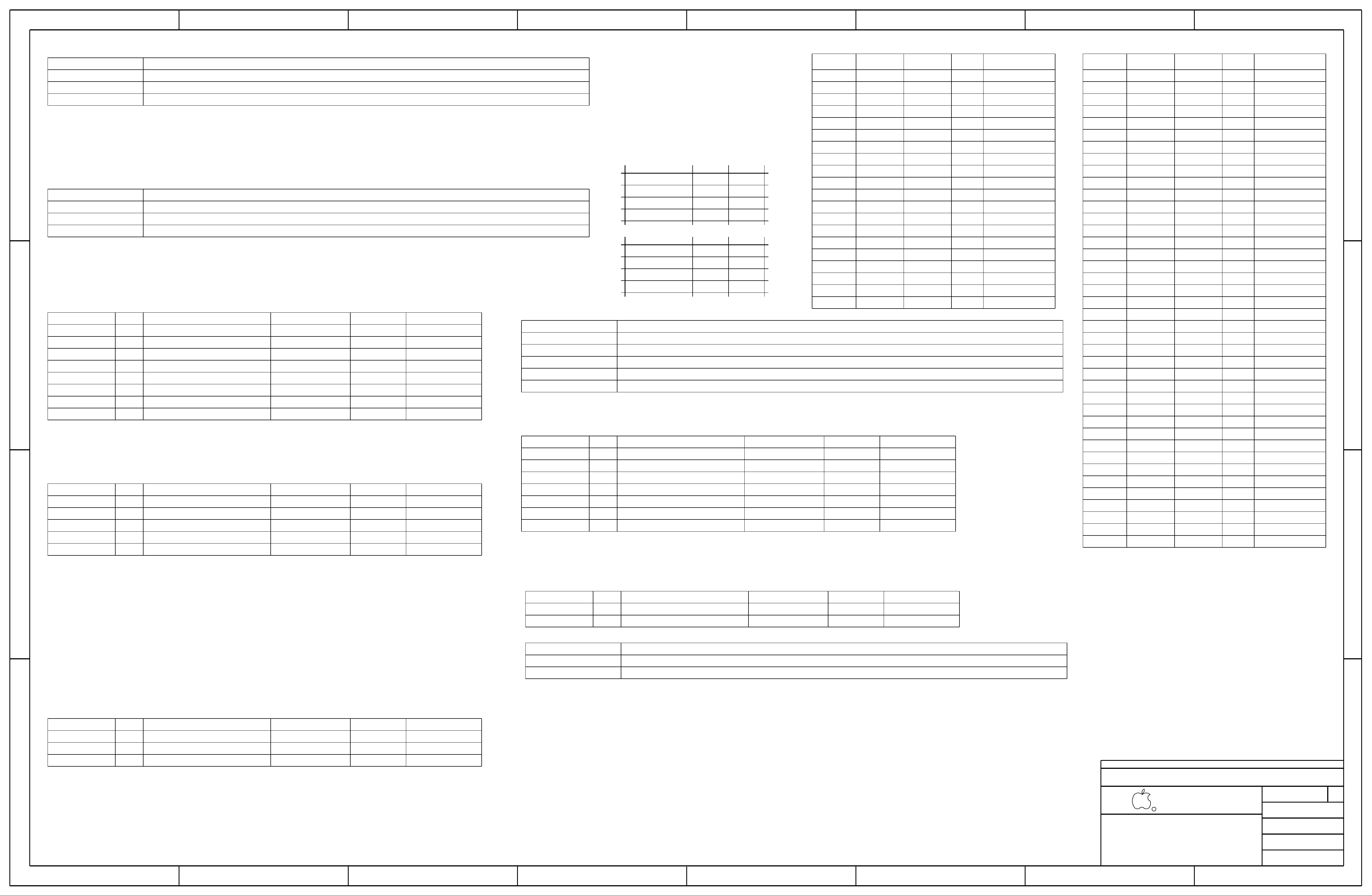

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

HYNIX

0

0

Programmable Parts

in a binary fashion (ID0 is the LSb). IDx is high if not set low in the BOM table.

Board ID should start all-high (first build), and each new build increment stuffing

Module Parts

VENDOR

1

Board IDs

Module Parts

CFG 2

DRAM Parts

0

SIZE

0

0

CFG 1

1

1

1

1

0

1

0

2GB

1

SAMSUNG

0

MICRON

18GB

CFG 0

ELPIDA

4GB DDP

SSD Configs

BOM Groups

4GB QDP

CFG 3

CPU DRAM CFG Chart

Alternate Parts

SSD Parts

CPU DRAM SPD Straps

2 OF 67

2 OF 130

<E4LABEL>

<SCH_NUM>

<BRANCH>

BOM Configuration [2]

SYNC_DATE=06/09/2015SYNC_MASTER=X260_ERIC

UPCROM:BLANKCRITICAL

IC,SPI SERIAL FLASH,8MBIT,3.0V,CSP,8P

335S00084 1 U3090

UPCROM:PROG

IC,NVM (VXXX) CBB, X260

341S00466 U3090 CRITICAL1

SSD:512GB_SAND NAND:256GB_SAND,CAPACITY2,SANDISK_1Y

CRITICALU8600

1 S3X:B0

IC,S3-X,B0

337S00175

U9100,U9120 CRITICAL

335S1030

NAND,TOG DDR2,2CH,64GB,1YNM,3.3V,LGA60

NAND:64GB2

NAND,TOG DDR2,2CH,128GB,1YNM,3.3V,LGA60

U9100,U9120 CRITICAL

NAND:128GB335S00050 2

NEC alt to Kemet

128S00039 128S00038 ALL

ALL

Cyntec alt to Murata

152S00362 152S1129

ALL138S0831138S00049

Kyocera alt to Murata

ALL138S0831138S00032

Taiyo alt to Murata

Taiyo alt to Murata

ALL138S1086138S00087

TFT alt to Cyntec

ALL107S00056107S00086

ALL

Chilisin alt to Cyntec

152S00220152S00347

ALL

Taiyo alt to Murata

138S0943138S00090

Samsung alt to Murata

138S0739 ALL138S0706

ALL

Kyocera alt to Murata

138S0945 138S0706

Murata alt to TDK

155S00008 ALL155S00011

311S0612 ALL

Diodes alt to NXP

311S00057

ALL

Semtech alt to TI

353S4296353S00773

107S0284107S00021 ALL

TFT alt to Cyntec

107S0276

TFT alt to Cyntec

107S00020 ALL

338S00175 ALL338S1264

Broadcom alt packaging

333S00030

Hynix alt to Micron

ALL333S00016

311S00004 ALL

OnSemi alt to NXP

311S0370

ALL

Kyocera alt to TXC

197S00053 197S00050

197S00050

Murata alt to TXC

ALL197S00055

155S0706 155S0302 ALL

Taiyo alt to Murata

ALL

Murata alt to TDK

155S0361155S0741

155S00165

Taiyo alt to TDK

ALL155S0382

155S00166 155S0391

TDK alt to Murata

ALL

155S00155

TDK alt to Murata

ALL155S0441

ALL

Murata alt to Cyntec

152S00343 152S1682

138S00077 138S00035 ALL

Taiyo alt to Murata

337S00174 337S00175

S3X B0 alt to A0

ALLS3X:B0

ALL

ONSemi alt to TI

353S2208353S00714

353S00712 ALL353S2216

OnSemi alt to TI

152S00028

Murata alt to Taiyo Yuden

ALL152S1751

138S00073 138S00047 ALL

Murata alt to Taiyo

132S00012 132S0401

Multi alt to Taiyo

ALL

138S0772 ALL

Taiyo alt to Murata

138S00013

Rohm alt to Sanyo

128S00010 ALL128S00031

Kemet alt to Sanyo

ALL128S00010128S00011

NEC alt to Sanyo

ALL128S00026 128S00010

ALL128S00029 128S00015

Rohm alt to Sanyo

128S00015 ALL128S00009

Kemet alt to Sanyo

ALL128S00015128S00007

NEC alt to Sanyo

ALL138S0705

Samsung alt to Murata

138S0786

ALL

ROHM alt to NEC

128S00020128S00021

152S00224

Vishay alt to Cyntec

152S00098 ALL

152S2037

Cyntec new alt to Cyntec

ALL152S00311

376S1080 ALL376S0820

Diodes alt to OnSemi

128S0397 128S0325 ALL

Kemet alt to Sanyo

TDK alt to Murata

107S0085 ALL107S00070

376S00007 376S1179

AOS alt to Vishay

ALL

128S0487128S00012

ROHM alt to NEC

ALL

Polytronics alt to Wayon

740S0190 ALL740S00005

Sanyo alt to NEC

128S0487 ALL128S0296

Kemet alt to Sanyo

740S00004 ALL740S0134

ALL128S00041128S00044

Rubycon alt to Sanyo

107S0249

TFT alt to Cyntec

ALL107S0251

ALL376S0604

Diodes alt to Fairchild

376S1053

372S0186 372S0185 ALL

NXP alt to Diodes

Murata alt to Taiyo Yuden

138S0703 138S0648 ALL

NXP alt for Diodes single

ALL376S1089 376S1128

NXP alt for Diodes dual

376S1129 376S0855 ALL

376S00074

Toshiba alt for Diodes dual

ALL376S0855

DRAM_TYPE:ELPIDA_8GB

DRAM:ELP_8GB

RAMCFG0_L,RAMCFG1_L,DRAM_TYPE:HYNIX_8GB

DRAM:HYN_8GB

DRAM:SAM_8GB

RAMCFG0_L,DRAM_TYPE:SAMSUNG_8GB

SSD:256GB_SAND NAND:128GB_SAND,CAPACITY0,CAPACITY1,SANDISK_1Y

NAND:256GB,CAPACITY2SSD:512GB

MLB_DEBUG:ENG DEBUGLED

BOARDID1_LBUILD:CBB

SSDRAM:4GBIT

CRITICALU8600_POP_DRAM

333S00017 1

IC,LPDDR3-1600,128MX8,1.8V,25NM,276 POP

BUILD:PROTO1 BOARDID0_L

BOOTROM_MIC:BLANK

CRITICAL335S1029 U61001

64 MBIT SPI QUAD I/O FLASH,CSP,3.3V,QUAD IO

BOOTROM_WIN:BLANK

335S1009 CRITICALU6100

64 MBIT SPI QUAD I/O FLASH,CSP,3.3V,QUAD IO

1

BOOTROM_MAC:BLANK

CRITICAL335S1010 U61001

64 MBIT SPI QUAD I/O FLASH,CSP,3.3V,QUAD IO

NAND:64GB,CAPACITY1SSD:128GB

2

CRITICALU9100,U9120

NAND,TOG DDR2,2CH,256GB,1YNM,3.3V,LGA60

335S00122 NAND:256GB_SAND

IC,CD3215,USB PWR SWITCH,A1,6X6MM,BGA96

UPC:A1

U3100

CRITICAL1353S00660

IC,EFI ROM (VXXX) CBB,X260

341S00465 CRITICALU6100 BOOTROM:PROG1

NAND,TOG DDR2,2CH,128GB,1YNM,3.3V,LGA60

CRITICAL

2

U9100,U9120

335S00121 NAND:128GB_SAND

NAND,TOG DDR2,2CH,256GB,1YNM,3.3V,LGA60

U9100,U9120

NAND:256GB

CRITICAL

335S00051 2

CRITICAL

IC,CPU,SKY,SR2EH,PRQ,D1,2/2,1.3,5W,.85,B1515

337S00209 CPU:1.3GHZU05001

IC,CPU,SKY,SR2EM,PRQ,D1,2/2,1.2,5W,.85,B1515

337S00208 CPU:1.2GHZU0500 CRITICAL1

1 U0500

IC,CPU,SKY,SR2EN,PRQ,D1,2/2,1.1,5W,.85,B1515

337S00207 CPU:1.1GHZCRITICAL

IC,SDRAM,LPDDR-1866,32GBIT,253B FBGA

333S00054

CRITICAL

2

DRAM_TYPE:ELPIDA_8GB

U2300,U2500

CRITICALU2300,U2500

2333S00053

IC,SDRAM,LPDDR-1866,32GBIT,253B FBGA DRAM_TYPE:HYNIX_8GB

U2300,U2500

IC,SDRAM,LPDDR-1866,32GBIT,253B FBGA

2

CRITICAL

333S00052

DRAM_TYPE:SAMSUNG_8GB

CRITICAL

IC,SMC-B1,EXTERNAL (V2.33A2) PROTO 1,X260

341S00431 SMC:PROGU50001

NAND:128GB,CAPACITY0,CAPACITY1SSD:256GB

U7800

CRITICAL1338S00168 PMIC:A0D

IC,PMU,P650839A0D,7X7MM,BGA168

LABEL

LABEL,BARCODE,2D,1D,CONFIG,MLB,X260

825-00162 1

J11/J13 MLB DYMAX ADHESIVE 29993-SC 0.4G

GLUE CRITICAL1946-3892

IC,SMC12-B1,40MHZ/50DMIPS MCU,7X7,168BGA

U5000338S1231 CRITICAL SMC:BLANK1

CAM_FREQ:24M,CAM_XTAL:NO,SSDRAM:4GBIT,S3X:B0,UPC:A1,PCH24M:SUS,EQ:4CH,PMIC:A0D,BSSB_GPIO

MLB_MISC

MLB_COMMON ALTERNATE,COMMON,MLB_MISC,MLB_DEBUG:ENG,MLB_PROGPARTS,BUILD:CBB

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_HEAD

BOM GROUP BOM OPTIONS

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

TABLE_BOMGROUP_ITEM

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_HEAD

BOM GROUP BOM OPTIONS

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_HEAD

BOM GROUP BOM OPTIONS

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

PART NUMBER

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

PART NUMBER

TABLE_ALT_ITEM

TABLE_ALT_ITEM

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

TABLE_BOMGROUP_ITEM

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

TABLE_BOMGROUP_HEAD

BOM GROUP BOM OPTIONS

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

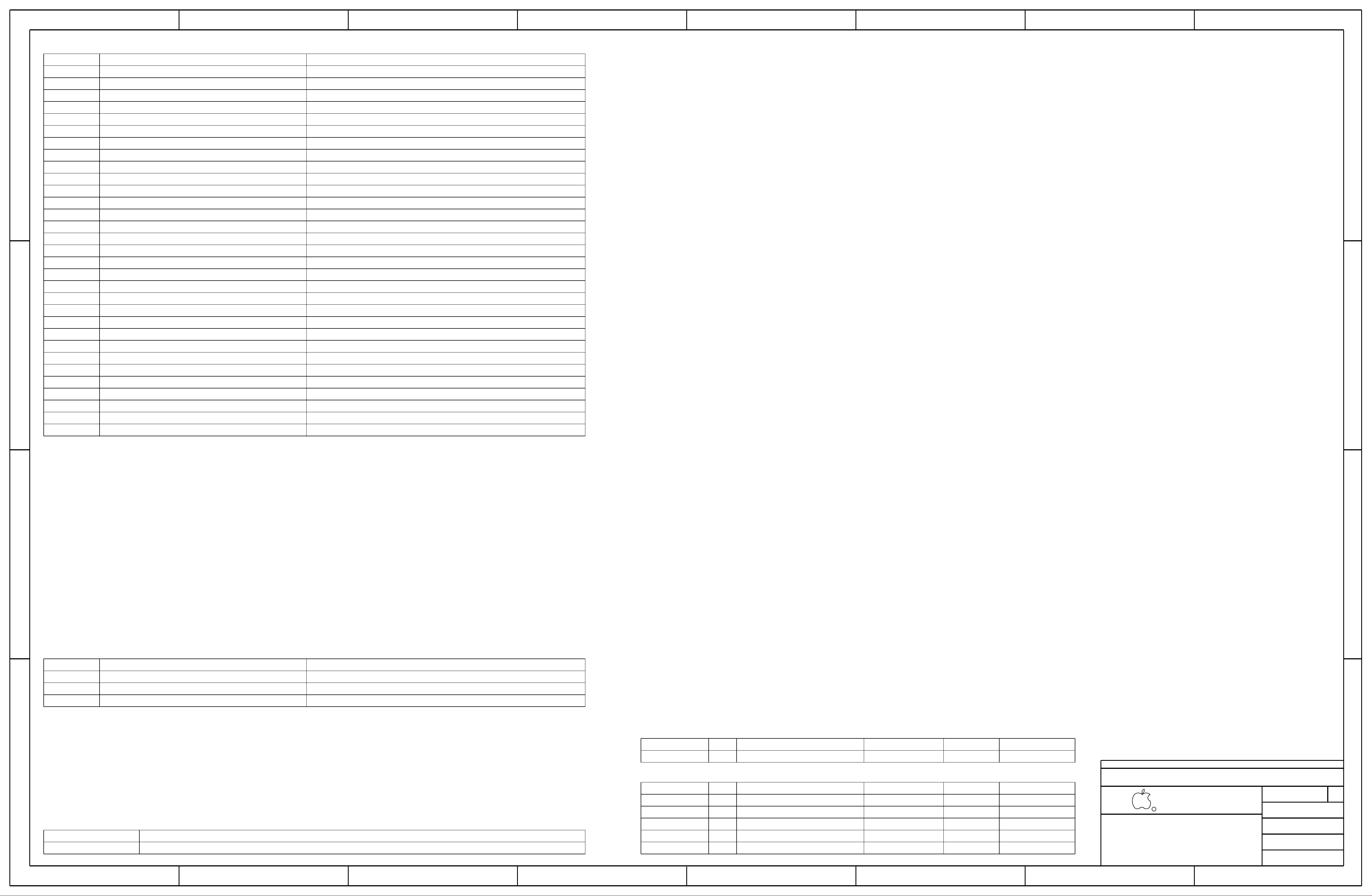

BOM Groups

Programmable Parts

Common BOM

Partial & development BOMs

Top level BOM Variants

3 OF 67

3 OF 130

<E4LABEL>

<SCH_NUM>

<BRANCH>

939-01880

ALTERNATE,CMN,DRAM:SAM_8GB,SSD:512GB_SAND,WIFI:FCC

PCBA,MLB,NO CPU,SA 8GB,SAND 512G,WIFI FCC,X260

939-01879

ALTERNATE,CMN,DRAM:SAM_8GB,SSD:512GB,WIFI:FCC

PCBA,MLB,NO CPU,SA 8GB,TOSH 512G,WIFI FCC,X260

CRITICAL1 WIFI:FCC341S00346 U3780

WIFI ROM (PXXXX) PROTO0,WW1,X260

685-00073 CMN PTS,PCBA,MLB,X260

MLB_COMMON

MLB_PROGPARTS BOOTROM:PROG,BT:PROG,SMC:PROG,UPCROM:PROG

CRITICAL1 WIFI:APACU3780341S00348

WIFI ROM (PXXXX) PROTO0,WW3,X260

CRITICAL1 WIFI:INDU3780341S00349

WIFI ROM (PXXXX) PROTO0,IND,X260

CRITICAL1 WIFI:ETSIU3780341S00347

WIFI ROM (PXXXX) PROTO0,WW2,X260

CRITICAL1 CMNCMNPTS685-00073

CMN PTS,PCBA,MLB,X260

1 BT:PROGCRITICAL341S00345 U3770

BT ROM (VXX) PROTO0,X260

PCBA,MLB,1.3GHZ,EL 8GB,TOSH 256G,WIFI FCC,X260

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,SSD:256GB,WIFI:FCC

639-6664

639-6670 PCBA,MLB,1.1GHZ,HY 8GB,TOSH 128G,WIFI FCC,X260

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:HYN_8GB,SSD:128GB,WIFI:FCC

PCBA,MLB,1.2GHZ,SA 8GB,TOSH 512G,WIFI APAC,X260639-6672

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:SAM_8GB,SSD:512GB,WIFI:APAC

PCBA,MLB,1.3GHZ,EL 8GB,TOSH 512G,WIFI FCC,X260

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,SSD:512GB,WIFI:FCC

639-6665

PCBA,MLB,1.3GHZ,HY 8GB,TOSH 256G,WIFI FCC,X260639-6666

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:HYN_8GB,SSD:256GB,WIFI:FCC

PCBA,MLB,1.2GHZ,EL 8GB,TOSH 256G,WIFI ETSI,X260639-6671

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,SSD:256GB,WIFI:ETSI

PCBA,MLB,1.3GHZ,SA 8GB,TOSH 512G,WIFI FCC,X260639-6669

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:SAM_8GB,SSD:512GB,WIFI:FCC

PCBA,MLB,1.3GHZ,SA 8GB,TOSH 256G,WIFI FCC,X260639-6668

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:SAM_8GB,SSD:256GB,WIFI:FCC

PCBA,MLB,1.3GHZ,HY 8GB,TOSH 512G,WIFI FCC,X260639-6667

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:HYN_8GB,SSD:512GB,WIFI:FCC

639-6678

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:HYN_8GB,SSD:512GB_SAND,WIFI:FCC

PCBA,MLB,1.3GHZ,HY 8GB,SAND 512G,WIFI FCC,X260

639-6676

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,SSD:256GB_SAND,WIFI:FCC

PCBA,MLB,1.2GHZ,EL 8GB,SAND 256G,WIFI FCC,X260

639-6677

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:SAM_8GB,SSD:512GB_SAND,WIFI:FCC

PCBA,MLB,1.3GHZ,SA 8GB,SAND 512G,WIFI FCC,X260

639-6675

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:SAM_8GB,SSD:512GB_SAND,WIFI:APAC

PCBA,MLB,1.3GHZ,SA 8GB,SAND 512G,WIFI APAC,X260

639-6674

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:ELP_8GB,SSD:256GB_SAND,WIFI:FCC

PCBA,MLB,1.3GHZ,EL 8GB,SAND 256G,WIFI FCC,X260

639-6673

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:ELP_8GB,SSD:256GB_SAND,WIFI:ETSI

PCBA,MLB,1.2GHZ,EL 8GB,SAND 256G,WIFI ETSI,X260

PCBA,MLB,1.1GHZ,HY 8GB,TOSH 512G,WIFI FCC,X260

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:HYN_8GB,SSD:512GB,WIFI:FCC

639-6680

639-6682

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:SAM_8GB,SSD:256GB_SAND,WIFI:FCC

PCBA,MLB,1.2GHZ,SA 8GB,SAND 256G,WIFI FCC,X260

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:SAM_8GB,SSD:256GB_SAND,WIFI:IND

PCBA,MLB,1.2GHZ,SA 8GB,SAND 256G,WIFI IND,X260639-6685

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:SAM_8GB,SSD:512GB_SAND,WIFI:ETSI

PCBA,MLB,1.1GHZ,SA 8GB,SAND 512G,WIFI ETSI,X260639-6684

PCBA,MLB,1.3GHZ,SA 8GB,SAND 256G,WIFI FCC,X260

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:SAM_8GB,SSD:256GB_SAND,WIFI:FCC

639-6683

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:HYN_8GB,SSD:512GB_SAND,WIFI:FCC

639-6679 PCBA,MLB,1.2GHZ,HY 8GB,SAND 512G,WIFI FCC,X260

PCBA,MLB,1.3GHZ,HY 8GB,TOSH 128G,WIFI FCC,X260639-6686

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:HYN_8GB,SSD:128GB,WIFI:FCC

ALTERNATE,CMN,CPU:1.3GHZ,DRAM:SAM_8GB,SSD:128GB,WIFI:FCC

PCBA,MLB,1.3GHZ,SA 8GB,TOSH 128G,WIFI FCC,X260639-6694

PCBA,MLB,1.2GHZ,HY 8GB,TOSH 256G,WIFI FCC,X260

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:HYN_8GB,SSD:256GB,WIFI:FCC

639-6681

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:SAM_8GB,SSD:512GB_SAND,WIFI:FCC

PCBA,MLB,1.1GHZ,SA 8GB,SAND 512G,WIFI FCC,X260639-6690

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:HYN_8GB,SSD:128GB,WIFI:FCC

PCBA,MLB,1.2GHZ,HY 8GB,TOSH 128G,WIFI FCC,X260639-6691

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:SAM_8GB,SSD:128GB,WIFI:FCC

PCBA,MLB,1.2GHZ,SA 8GB,TOSH 128G,WIFI FCC,X260639-6692

ALTERNATE,CMN,CPU:1.2GHZ,DRAM:SAM_8GB,SSD:512GB,WIFI:FCC

PCBA,MLB,1.2GHZ,SA 8GB,TOSH 512G,WIFI FCC,X260639-6693

639-6689 PCBA,MLB,1.1GHZ,SA 8GB,SAND 256G,WIFI FCC,X260

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:SAM_8GB,SSD:256GB_SAND,WIFI:FCC

639-6688 PCBA,MLB,1.1GHZ,HY 8GB,TOSH 256G,WIFI FCC,X260

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:HYN_8GB,SSD:256GB,WIFI:FCC

639-6687 PCBA,MLB,1.1GHZ,SA 8GB,TOSH 128G,WIFI FCC,X260

ALTERNATE,CMN,CPU:1.1GHZ,DRAM:SAM_8GB,SSD:128GB,WIFI:FCC

X260 BOM Variants

SYNC_MASTER=J43_MLB SYNC_DATE=10/24/2012

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_HEAD

BOM GROUP BOM OPTIONS

TABLE_BOMGROUP_HEAD

BOM NUMBER BOM NAME BOM OPTIONS

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_HEAD

BOM NUMBER BOM NAME BOM OPTIONS

SSD EMI CANs

DRAM EMI CAN

WIFI EMI CAN

860-00324

860-00329

USB-C BTB Connector BossCPU Heat Spreader Bosses

4 OF 67

4 OF 130

<E4LABEL>

<SCH_NUM>

<BRANCH>

SH04001 CRITICAL

CAN,EMI,WIFI,X261

806-7064

SH04031 CRITICAL

FENCE,EMI,SSD,TOP,X261

806-00889

1 CRITICAL870-00998

MYLAR,SHIM,MLB,X261

MYLAR_SHIM

CRITICAL1 SH0402806-04848

CAN,EMI,DRAM,X260

SH04041 CRITICAL806-05622

FENCE,EMI,SSD,BTM,X260

CRITICAL1 SSD_TAPE_BTM870-01557 TAPE,CONDUCTIVE,SSD,REEL,X260

CRITICAL1870-00878 SSD_TAPE_TOPTAPE,CONDUCTIVE,SSD,REEL,X261

PD PARTS

SYNC_DATE=10/24/2012SYNC_MASTER=J43_MLB

Z0405

1

3.7OD1.85ID-1.5H-SM

1

Z0404

3.7OD1.85ID-1.5H-SM

1

Z0403

3.7OD1.85ID-1.5H-SM

1

Z0406

2.73OD1.15ID-0.814H-SM

1

SH0404

SM

OMIT_TABLE

SHLD-CAN-EMI-SSD-BTM-X261

1

SM

OMIT_TABLE

SH0403

SHLD-FENCE-SSD-TOP-X261

1

SM

OMIT_TABLE

SH0402

SHLD-CAN-EMI-DRAM-X261

SHLD-J92-EMI-CAN-WIFI

1

SH0400

SM

OMIT_TABLE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

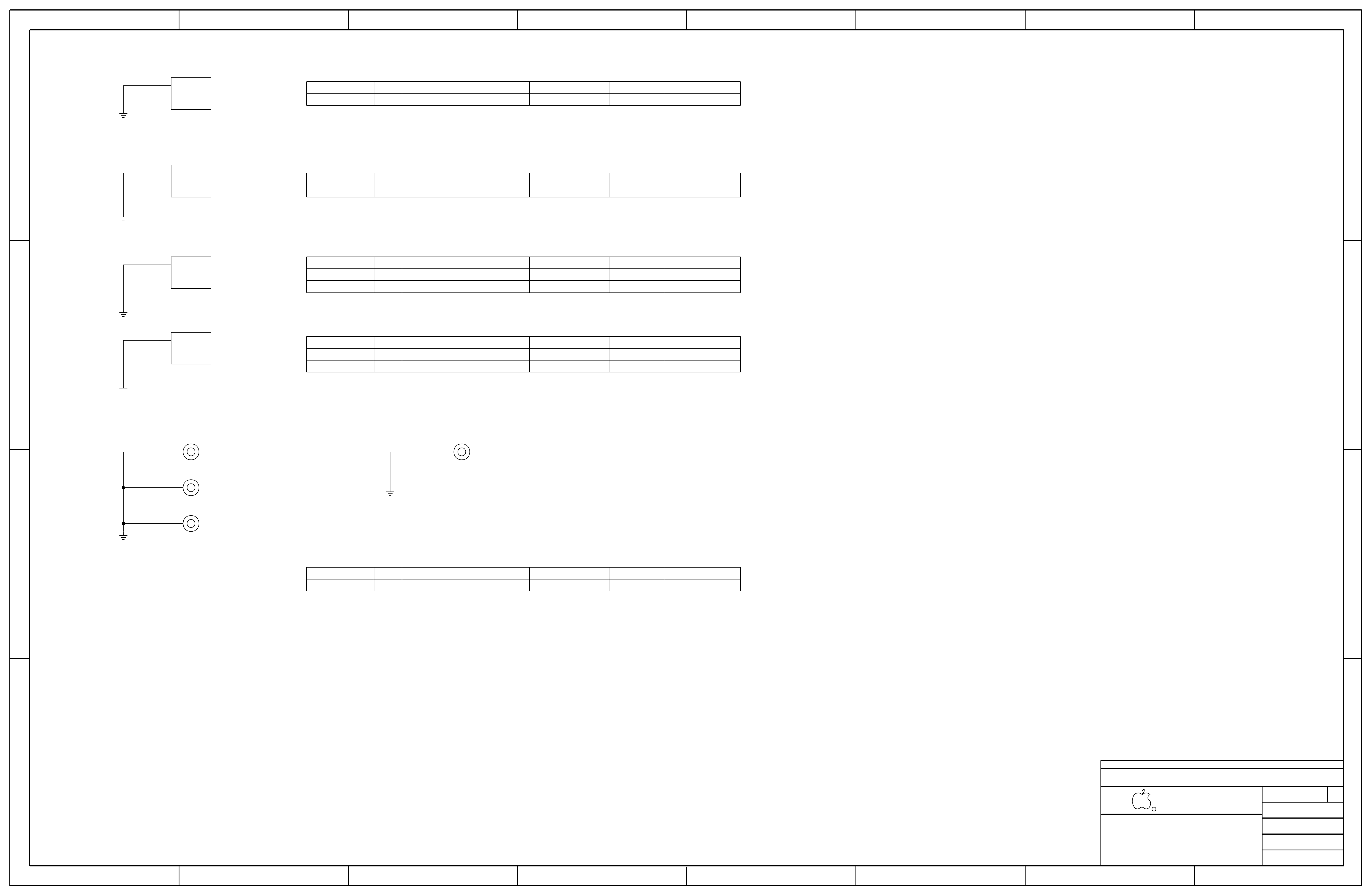

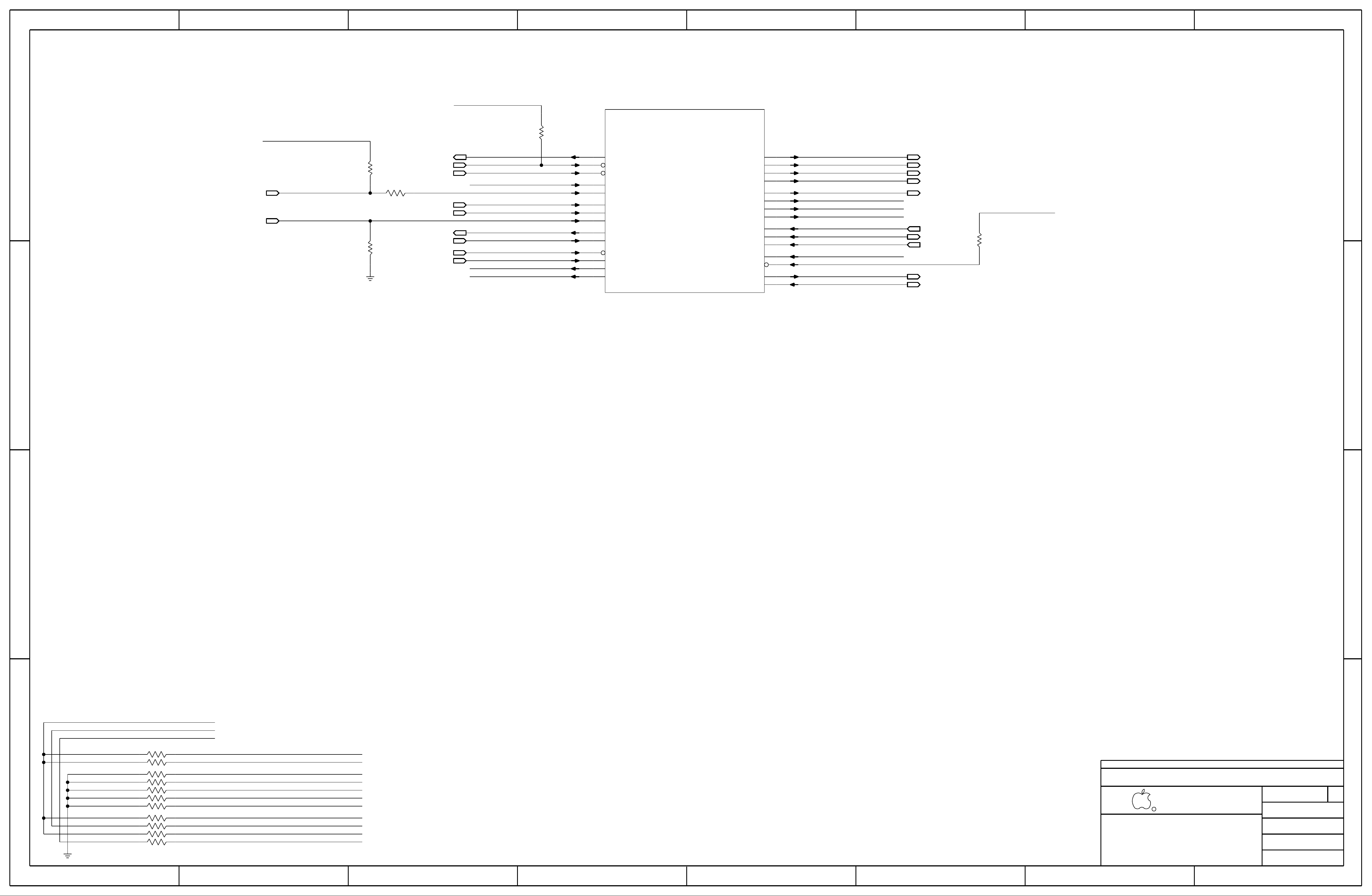

DDI Port Assignments:

Internal panel

GPP_E20: JTAG_TBT_T_TMS

GPP_E18: JTAG_TBT_X_TMS'Ridge systems:

USBC Sink 0

USBC Sink 1

(IPD-PLTRST#)

(IPD-PLTRST#)

(IPD-PLTRST#)

eDP Port Assignment:

<SCH_NUM>

<E4LABEL>

5 OF 67

5 OF 130

<BRANCH>

JTAG_ISP_TDO

NC_DP_DDI2_ML_CP<2>

NC_DP_DDI2_ML_CN<3>

PP3V3_S0

TP_EDP_DISP_UTIL

DP_INT_AUXCH_C_P

NC_DP_DDI2_AUXCH_CN

DP_INT_ML_C_N<1>

DP_INT_ML_C_N<2>

DP_INT_AUXCH_C_N

DP_INT_ML_C_N<3>

DP_INT_ML_C_P<3>

DP_INT_ML_C_P<2>

DP_XA_ML_C_N<1>

DP_XA_ML_C_P<0>

DP_INT_ML_C_N<0>

NC_DP_DDI2_ML_CN<1>

EDP_BKLT_EN

NC_DP_DDI2_ML_CP<3>

PCH_UPC_XA_SWD_DATA

DP_DDI2_HPD

NC_DP_DDI2_AUXCH_CP

DP_XA_AUXCH_C_P

DP_XA_AUXCH_C_N

DP_INT_ML_C_P<1>DP_XA_ML_C_P<1>

NC_DP_DDI2_ML_CN<0>

NC_DP_DDI2_ML_CP<1>

DP_XA_ML_C_N<0>

NC_DP_DDI2_ML_CN<2>

DP_XA_ML_C_P<3>

DP_XA_ML_C_N<3>

PCH_UPC_XA_SWD_CLK

PCH_DDPB_CTRLDATA

NC_PCH_DDPC_CTRLDATA

EDP_BKLT_PWM

EDP_PANEL_PWRMCP_EDP_RCOMP

PPVCCIO_S0

PLT_RST_L

EDP_BKLT_EN

DP_INT_HPD

DP_DDI1_HPD

NC_DP_DDI2_ML_CP<0>

TP_PCH_GPP_E15

SSD_RESET_L

PCH_UPC_XA_SWD_CLK

TBT_POC_RESET

PCH_UPC_XA_SWD_DATA

DP_DDI1_HPD

DP_DDI2_HPD

EDP_PANEL_PWR

JTAG_ISP_TDO

DP_INT_HPD

DP_XA_ML_C_N<2>

DP_XA_ML_C_P<2>

TBT_POC_RESET

DP_INT_ML_C_P<0>

SYNC_DATE=05/11/2015SYNC_MASTER=DEVMLB

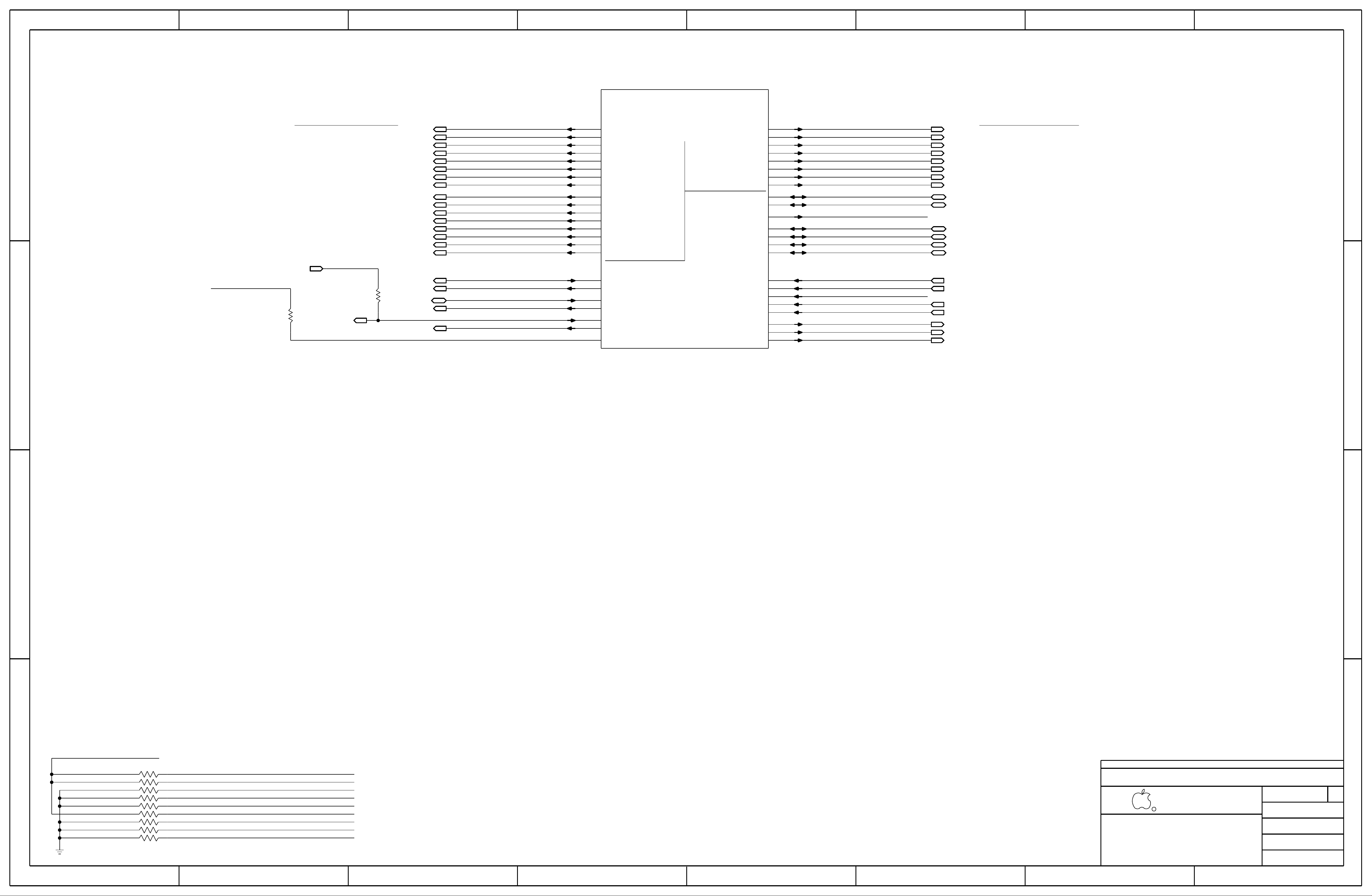

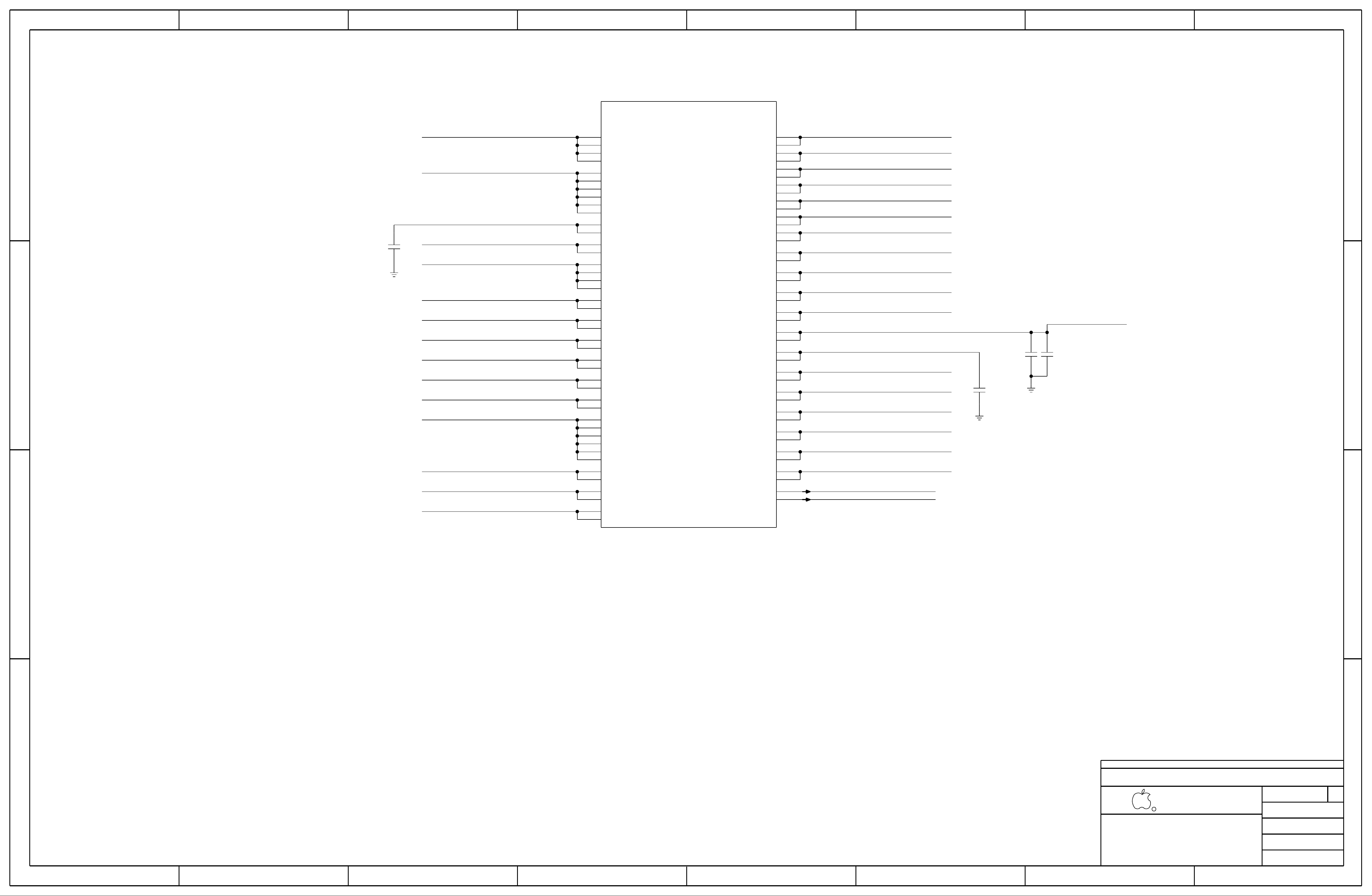

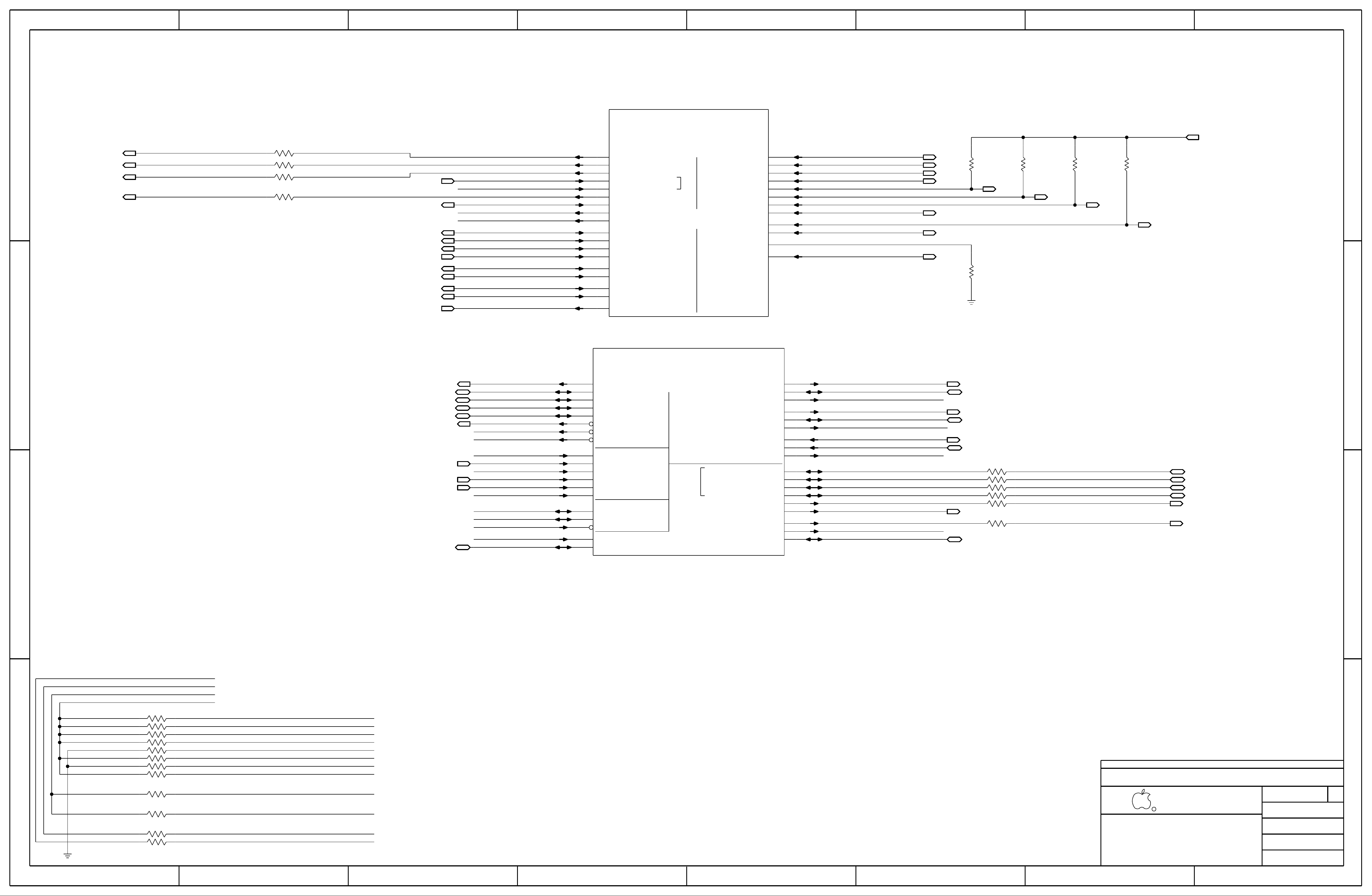

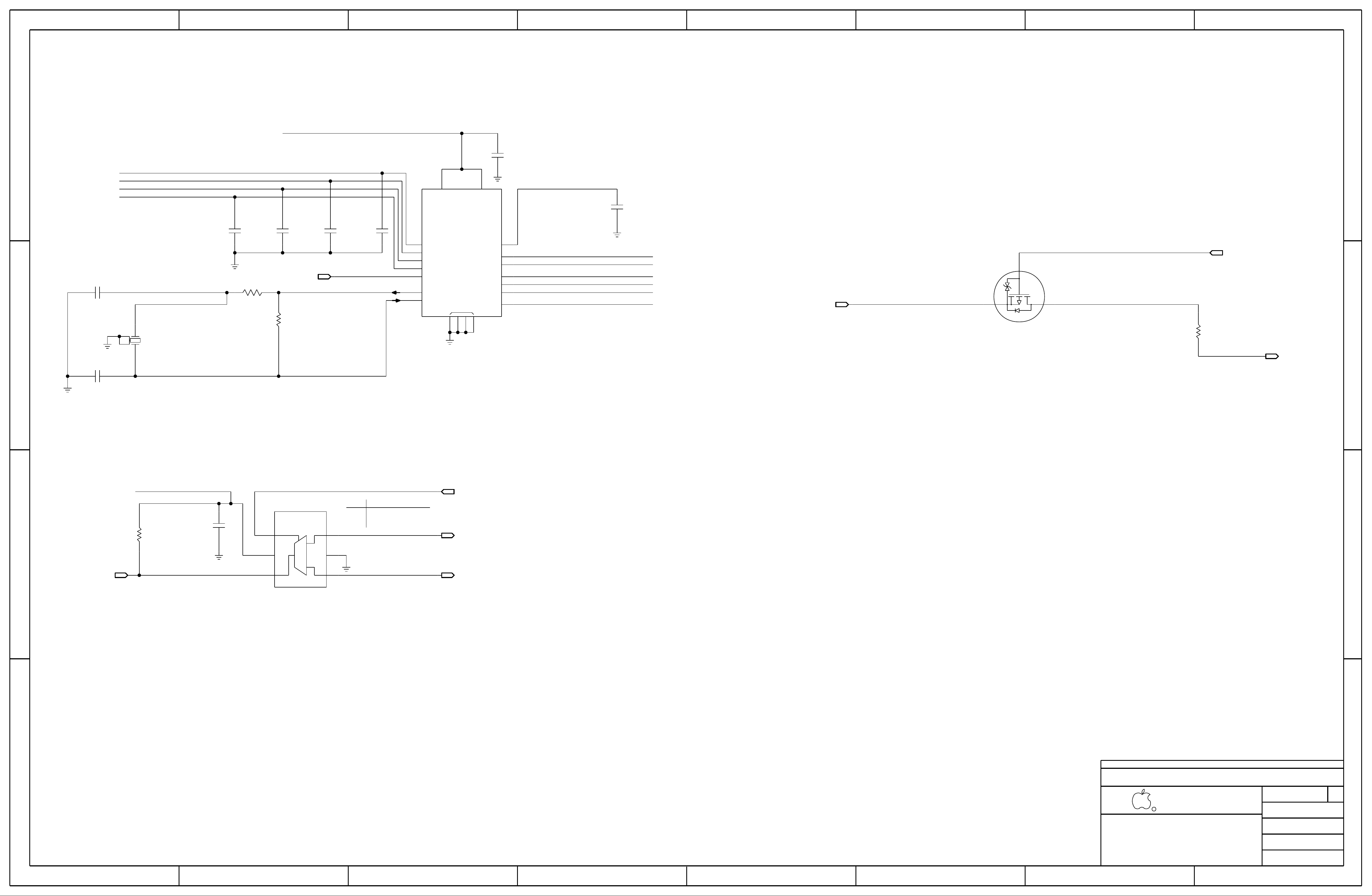

BOM_COST_GROUP=CPU & CHIPSET

CPU GFX

64

64

64

64

64

64

60 23

60 23

60 23

60 23

60 23

60 23

60 23

60 23

2

1

R0520

PLACE_NEAR=U0500.A50:15.24mm

24.9

1%

MF

1/20W

201

21

R0584

1/32W 01005

100K

MF5%

21

R0580

1/32W 01005

100K

MF5%

21

R0581

1/32W 01005

100K

MF5%

21

R0515

1/32W 01005

100K

MF5%

21

R0583

1/32W 01005

10K

MF5%

64 5

65 30 26 19 15 14

2

1

R0514

1/32W

01005

100K

MF

5%

64 5

59

21

R0510

1/32W 01005

10K

MF5%

21

R0512

1/32W 01005

10K

MF5%

21

R0590

1/32W 01005

100K

MF5%

21

R0591

1/32W 01005

100K

MF5%

53 5

65 53

52 5

63

23 5

19

23 5

60 23

64

64

60 23

19 5

64 5

53 5

L4

M5

F4

H4

H6

L6

A7

F6

M7

L10

C11

D3

F43

G46

G44

F45

H43

J46

J44

H45

A50

A40

D4

B6

G42

J42

D43

D41

C44

C42

B43

B41

A44

A42

G40

J40

D47

D45

A48

C46

B47

B45

C48

A46

F41

H41

U0500

CRITICAL

OMIT_TABLE

SKL-Y

BGA

SKL-Y-ULX

53

53

53

53

53

53

53

53

53

53

64

64

67 61 53 51 50 46 39 35 34

33 31 27 26 23 19 17 16 15 14 6

52 5

61 47 11 8

23 5

64 5

23 5

19 5

64 5

53 5

64 5

53 5

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

BI

OUT

OUT

BI

BI

BI

BI

IN

IN

IN

SYM 1 OF 20

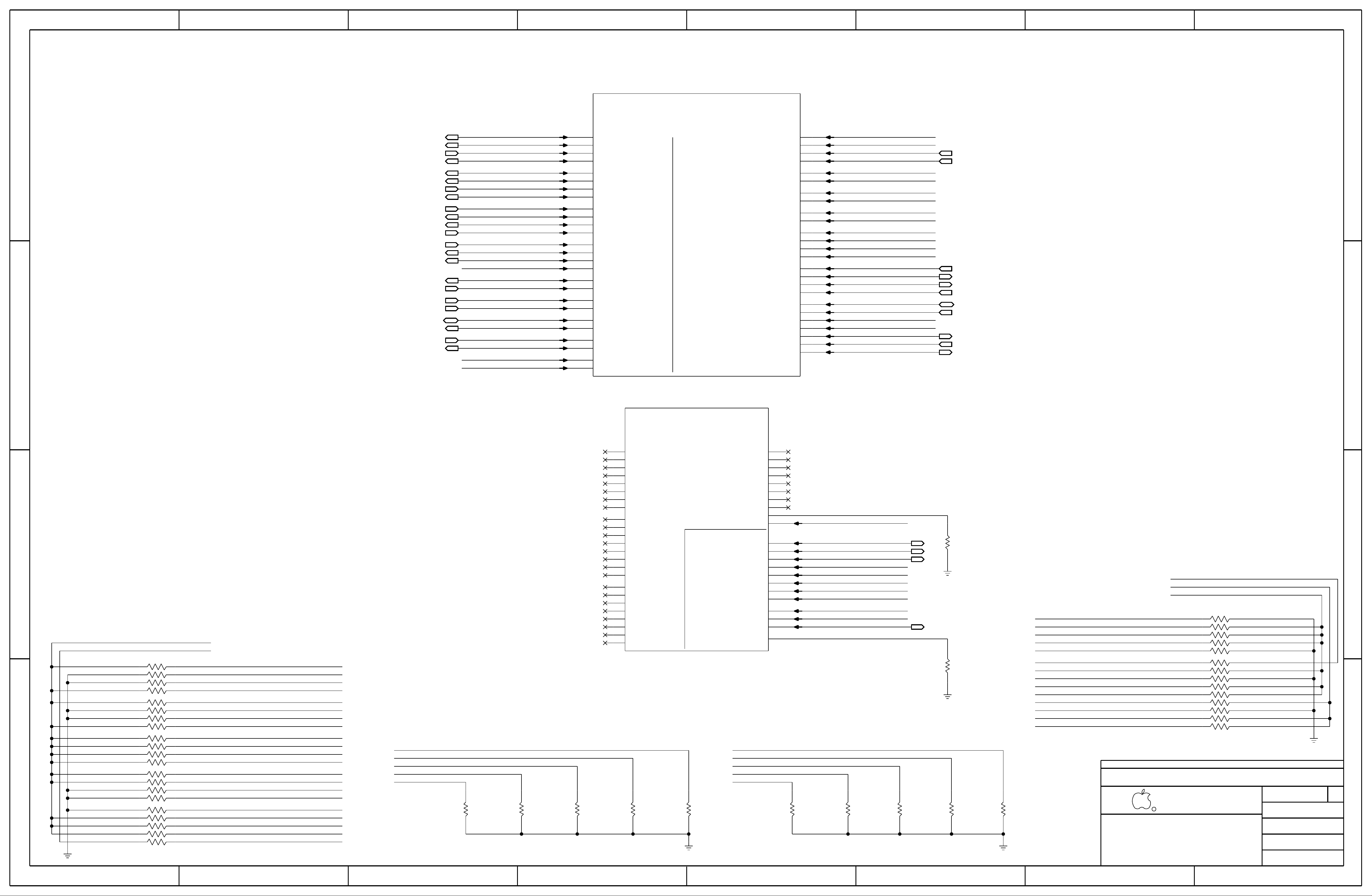

DDI

DISPLAY SIDEBANDS

EDP

DISPLAY

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_AUXP

EDP_AUXN

DDI1_TXN0

GPP_E23

GPP_E22

EDP_VDDEN

EDP_BKLCTL

EDP_BKLEN

GPP_E17/EDP_HPD

GPP_E16/DDPE_HPD3

GPP_E15/DDPD_HPD2

GPP_E14/DDPC_HPD1

GPP_E13/DDPB_HPD0

DDI2_AUXP

DDI2_AUXN

DDI1_AUXP

DDI1_AUXN

EDP_DISP_UTIL

EDP_TXN3

EDP_TXP3

EDP_TXP2

DDI1_TXN1

DDI1_TXN3

EDP_RCOMP

GPP_E20/DDPC_CTRLCLK

DDI1_TXP1

DDI1_TXP3

DDI2_TXN0

DDI2_TXN2

DDI2_TXP2

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI1_TXN2

DDI1_TXP0

DDI2_TXN3

EDP_TXN0

DDI2_TXP3

GPP_E18/DDPB_CTRLCLK

GPP_E19/DDPB_CTRLDATA

GPP_E21/DDPC_CTRLDATA

DDI1_TXP2

BI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

(IPD)

(IPD)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

.

(IPD)

6 OF 67

6 OF 130

<E4LABEL>

<SCH_NUM>

<BRANCH>

TP_XDP_PCH_OBSFN_C1

TP_XDP_PCH_OBSDATA_A3

BT_PWRRST_L

BT_TIMESTAMP

TP_MCP_RSVD_BJ17

TP_MCP_RSVD_BJ15

TP_MCP_RSVD_M27

TP_MCP_RSVD_L28

TP_MCP_RSVD_L24

TP_MCP_RSVD_M25

TP_MCP_RSVD_BE19

TP_MCP_RSVD_BA23

TP_MCP_RSVD_AY22

TP_MCP_RSVD_BN1

TP_MCP_RSVD_D49

TP_ITP_PMODE

CPU_CFG_RCOMP

TP_MCP_RSVD_BF18

TP_MCP_RSVD_AY18

TP_MCP_RSVD_BA17

NC_CPU_CFG0

NC_CPU_CFG10

NC_CPU_CFG1

TP_CPU_CFG3

NC_CPU_CFG2

CPU_CFG<4>

NC_CPU_CFG5

NC_CPU_CFG8

NC_CPU_CFG6

NC_CPU_CFG7

NC_CPU_CFG9

NC_CPU_CFG13

NC_CPU_CFG12

NC_CPU_CFG11

NC_CPU_CFG14

NC_CPU_CFG15

NC_CPU_CFG17

NC_CPU_CFG16

NC_CPU_CFG18

NC_CPU_CFG19

TP_MCP_RSVD_BL64

TP_MCP_RSVD_BG47

PP3V3_S0

XDP_CPUPCH_TDO

XDP_CPUPCH_TCK

XDP_CPUPCH_TRST_L

XDP_CPUPCH_TDI

TP_XDP_PCH_TCK

XDP_CPUPCH_TRST_L

XDP_CPUPCH_TMS

XDP_CPUPCH_TDO

XDP_CPUPCH_TDI

XDP_CPUPCH_TCK

TP_XDP_BPM_L<1>

CPU_PROCHOT_R_L

TP_XDP_BPM_L<0>

TP_XDP_BPM_L<2>

TP_XDP_BPM_L<3>

CPU_PROCHOT_L

PP1V_S0SW

CPU_OPI_RCOMP

CPU_PECI

PM_THRMTRIP_L

CPU_CATERR_L

PP1V_S3

XDP_CPUPCH_TMS

BT_TIMESTAMP

BT_PWRRST_L

PCH_OPI_COMP

SYNC_DATE=05/11/2015SYNC_MASTER=DEVMLB

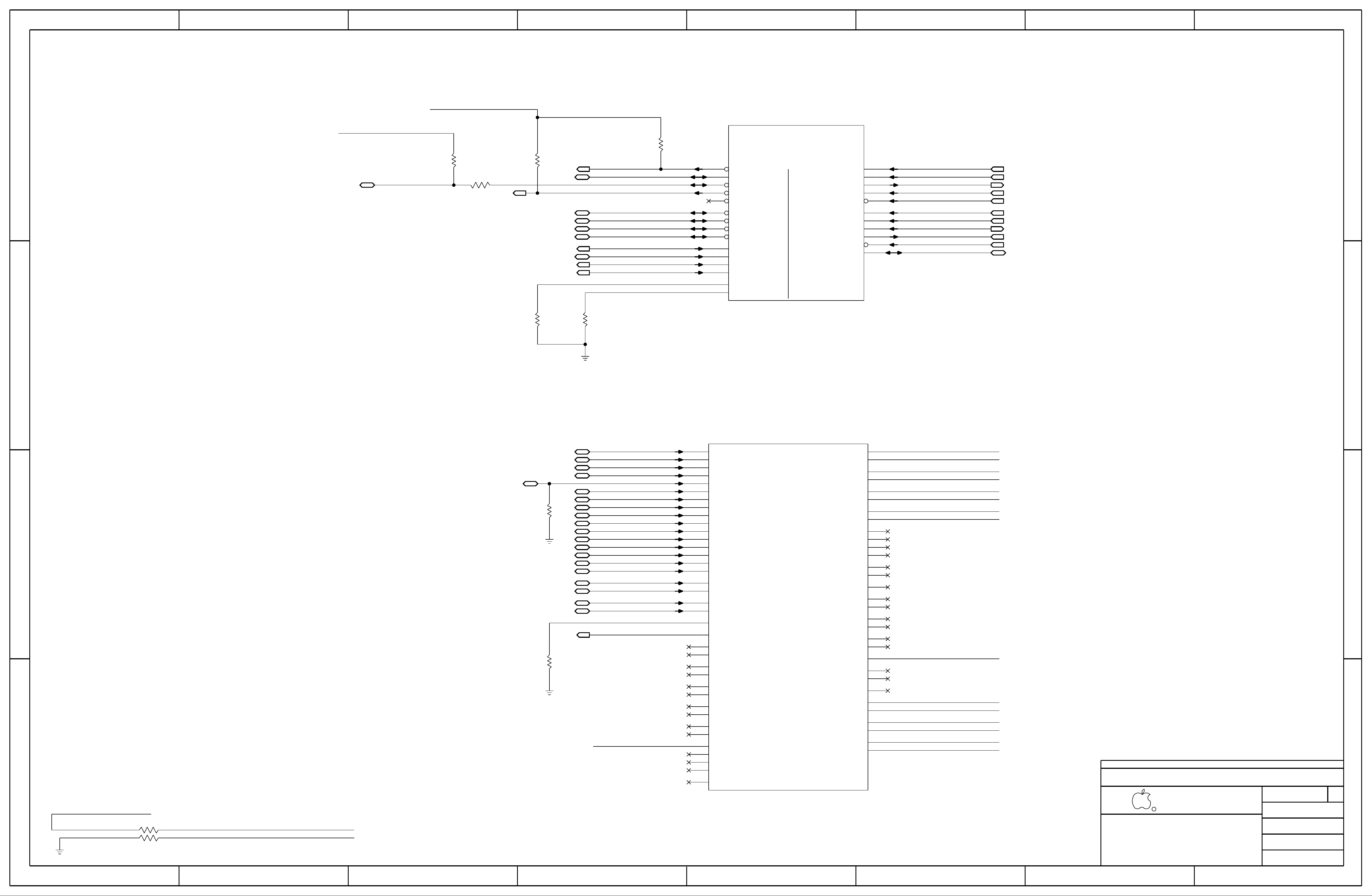

CPU Misc/JTAG/CFG/RSVD

BOM_COST_GROUP=CPU & CHIPSET

2

1

1/32W

01005

MF

5%

1.00K

R0634

64 6

64 6

21

R0619

1/32W 01005

100K

MF5%

21

R0618

1/32W 01005

100K

MF5%

2

1

R0613

49.9

1%

MF

1/20W

201

H47

B62

J48

F47

C52

H49

G50

F51

J50

H51

C59

G48

C54

D53

BN17

F49

A52

B51

C50

B53

B49

M9

E11

BC11

BD8

U0500

CRITICAL

BGA

OMIT_TABLE

SKL-Y-ULX

SKL-Y

BP16

63

63

63

2

1

R0680

49.9

1%

MF

1/20W

201

63

63

63

63

63

63

63

63

63

63

63

63

63

63

63

64

63

63

63

63

2

1

R0621

49.9

PLACE_NEAR=U0500.BP16:2.54mm

1%

MF

1/20W

201

2

1

R0620

49.9

PLACE_NEAR=U0500.BN17:2.54mm

1%

MF

1/20W

201

2

1

R0612

1/32W

01005

1.00K

MF

5%

31 30

63 6

63 6

63 6

63 6

63 6

63

63

63

63

63

42 31 30

2

1

R0610

1/32W

01005

1.00K

MF

5%

2 1

R0611

499

1%

MF

1/20W

201

31

65 30

63 6

63 6

63 6

63 6

63 6

OMIT_TABLE

CRITICAL

SKL-Y-ULX

U0500

G52

F53

J52

H53

H55

D55

C56

F55

D61

G58

D57

F61

J60

J58

H61

H59

J54

G54

G56

J56

A60

AH7

B3

B4

BA21

BB14

BC19

BE19

BF18

BN3

BP3

F1

F3

H12

K12

L16

L18

L22

L24

L28

M15

M17

M23

M25

M27

P13

R12

BA17

BG47

BL64

BA23

AY22

BGA

SKL-Y

AY18

A54

L26

M19

L20

M21

D49

BD18

BJ15

BJ17

AY20

BN1

L36

L38

BB18

BA19

67 61 53 51 50 46 39 35 34

33 31 27 26 23 19 17 16 15 14 5

63 61 50 12 8

61 50 42 31 15 12 8

64 6

64 6

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

OUT

OUT

CPU MISC

JTAG

SYM 4 OF 20

PROC_TDI

PROC_TDO

GPP_B4/CPU_GP3

GPP_B3/CPU_GP2

GPP_E7/CPU_GP1

GPP_E3/CPU_GP0

BPM2*

BPM1*

SKTOCC*

PECI

PCH_OPIRCOMP

PROC_POPIRCOMP

BPM3*

CATERR*

PROCHOT*

THERMTRIP*

BPM0*

PROC_TCK

PCH_TRST*

JTAGX

PCH_JTAG_TMS

PCH_JTAG_TDO

PCH_JTAG_TDI

PCH_JTAG_TCK

PROC_TRST*

PROC_TMS

BI

OUT

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

NC

BI

IN

IN

OUT

IN

IN

BI

BI

BI

BI

BI

BI

OUT

OUT

IN

IN

IN

IN

SYM 12 OF 20

RESERVED SIGNALS

CFG0

CFG10

RSVD

RSVD

RSVD

RSVD

CFG1

CFG3

CFG2

CFG4

CFG5

CFG8

CFG6

CFG7

CFG9

CFG13

CFG12

CFG11

CFG14

CFG15

CFG17

CFG16

CFG18

RSVD

CFG19

RSVD

RSVD

RSVD

RSVD

ITP_PMODE

CFG_RCOMP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

TP1

TP2

RSVD

RSVD

RSVD

RSVD

RSVD

TP4

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

TP5

TP6

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

7 OF 67

7 OF 130

<E4LABEL>

<SCH_NUM>

<BRANCH>

CPU_SM_RCOMP<0>

MEM_B_DQ<42>

MEM_B_DQ<41>

MEM_B_DQ<39>

MEM_B_DQ<38>

MEM_B_DQ<37>

CPU_SM_RCOMP<2>

MEM_B_DQ<44>

MEM_A_CAA<1>

MEM_A_CAA<2>

MEM_A_CAB<0>

MEM_A_CAA<0>

MEM_A_CS_L<1>MEM_A_DQ<10>

MEM_B_DQS_N<7>

MEM_A_DQ<16>

MEM_A_DQ<8>

MEM_A_DQ<63>

MEM_A_DQ<62>

MEM_A_DQ<61>

MEM_A_DQ<60>

MEM_A_DQ<59>

MEM_A_DQ<58>

MEM_A_DQ<57>

MEM_A_DQ<56>

MEM_A_DQ<55>

MEM_A_DQ<54>

MEM_A_DQ<53>

MEM_A_DQ<52>

MEM_A_DQ<51>

MEM_A_DQ<50>

MEM_A_DQ<49>

MEM_A_DQ<48>

MEM_A_DQ<47>

MEM_A_DQ<46>

MEM_A_DQ<45>

MEM_A_DQ<44>

MEM_A_DQ<43>

MEM_A_DQ<42>

MEM_A_DQ<41>

MEM_A_DQ<40>

MEM_A_DQ<39>

MEM_A_DQ<38>

MEM_A_DQ<37>

MEM_A_DQ<36>

MEM_A_DQ<35>

MEM_A_DQ<34>

MEM_A_DQ<33>

MEM_A_DQ<32>

MEM_A_DQ<31>

MEM_A_DQ<30>

MEM_A_DQ<29>

MEM_A_DQ<28>

MEM_A_DQ<27>

MEM_A_DQ<26>

MEM_A_DQ<25>

MEM_A_DQ<24>

MEM_A_DQ<23>

MEM_A_DQ<22>

MEM_A_DQ<21>

MEM_A_DQ<20>

MEM_A_DQ<19>

MEM_A_DQ<18>

MEM_A_DQ<17>

MEM_A_DQ<15>

MEM_A_DQ<14>

MEM_A_DQ<13>

MEM_A_DQ<12>

MEM_A_DQ<11>

MEM_A_DQ<9>

MEM_A_DQ<7>

MEM_A_DQ<6>

MEM_A_DQ<5>

MEM_A_DQ<4>

MEM_A_DQ<3>

MEM_A_DQ<2>

MEM_A_DQ<1>

MEM_A_DQ<0>

MEM_A_CS_L<0>

MEM_A_CKE<3>

MEM_A_CKE<2>

MEM_A_CKE<1>

MEM_A_CKE<0>

MEM_A_CLK_P<1>

MEM_A_CLK_N<1>

MEM_A_CLK_P<0>

TP_CPU_MEMVTT_PWR_EN

CPU_DIMMA_VREFDQ

CPU_DIMMB_VREFDQ

CPU_DIMM_VREFCA

MEM_A_DQS_P<7>

MEM_A_DQS_N<6>

MEM_A_DQS_P<6>

MEM_A_DQS_N<7>

MEM_A_DQS_N<5>

MEM_A_DQS_P<5>

MEM_A_DQS_P<4>

MEM_A_DQS_N<4>

MEM_A_DQS_P<3>

MEM_A_DQS_N<2>

MEM_A_DQS_P<2>

MEM_A_DQS_N<3>

MEM_A_DQS_N<1>

MEM_A_DQS_P<1>

MEM_A_DQS_N<0>

MEM_A_DQS_P<0>

MEM_A_CAB<8>

MEM_A_CAB<9>

MEM_A_CAB<7>

MEM_A_CAB<6>

MEM_A_CAB<5>

MEM_A_CAB<3>

MEM_A_CAB<4>

MEM_A_CAB<2>

MEM_A_CAB<1>

MEM_A_CAA<7>

MEM_A_CAA<9>

MEM_A_CAA<8>

MEM_A_CAA<5>

MEM_A_CAA<6>

MEM_A_CAA<4>

MEM_A_CAA<3>

MEM_A_ODT<0>

MEM_A_CLK_N<0>

MEM_B_DQ<63>

MEM_B_DQ<62>

MEM_B_DQ<61>

MEM_B_DQ<60>

MEM_B_DQ<59>

MEM_B_DQ<58>

MEM_B_DQ<57>

MEM_B_DQ<56>

MEM_B_DQ<55>

MEM_B_DQ<54>

MEM_B_DQ<53>

MEM_B_DQ<52>

MEM_B_DQ<51>

MEM_B_DQ<50>

MEM_B_DQ<49>

MEM_B_DQ<48>

MEM_B_DQ<47>

MEM_B_DQ<46>

MEM_B_DQ<45>

MEM_B_DQ<43>

MEM_B_DQ<40>

MEM_B_DQ<36>

MEM_B_DQ<35>

MEM_B_DQ<34>

MEM_B_DQ<33>

MEM_B_DQ<32>

MEM_B_DQ<31>

MEM_B_DQ<30>

MEM_B_DQ<29>

MEM_B_DQ<28>

MEM_B_DQ<27>

MEM_B_DQ<26>

MEM_B_DQ<25>

MEM_B_DQ<24>

MEM_B_DQ<23>

MEM_B_DQ<22>

MEM_B_DQ<21>

MEM_B_DQ<20>

MEM_B_DQ<19>

MEM_B_DQ<18>

MEM_B_DQ<17>

MEM_B_DQ<16>

MEM_B_DQ<15>

MEM_B_DQ<14>

MEM_B_DQ<13>

MEM_B_DQ<12>

MEM_B_DQ<11>

MEM_B_DQ<10>

MEM_B_DQ<9>

MEM_B_DQ<8>

MEM_B_DQ<7>

MEM_B_DQ<6>

MEM_B_DQ<5>

MEM_B_DQ<4>

MEM_B_DQ<3>

MEM_B_DQ<2>

MEM_B_DQ<1>

MEM_B_DQ<0>

MEM_B_DQS_P<7>

MEM_B_DQS_N<6>

MEM_B_DQS_P<6>

MEM_B_DQS_N<5>

MEM_B_DQS_P<5>

MEM_B_DQS_P<4>

MEM_B_DQS_N<4>

MEM_B_DQS_P<3>

MEM_B_DQS_N<3>

MEM_B_DQS_N<2>

MEM_B_DQS_P<2>

MEM_B_DQS_N<1>

MEM_B_DQS_P<1>

MEM_B_DQS_P<0>

MEM_B_DQS_N<0>

MEM_B_CAB<7>

MEM_B_CAB<8>

MEM_B_CAB<9>

MEM_B_CAB<5>

MEM_B_CAB<6>

MEM_B_CAB<2>

MEM_B_CAB<3>

MEM_B_CAB<4>

MEM_B_CAB<0>

MEM_B_CAB<1>

MEM_B_CAA<9>

MEM_B_CAA<8>

MEM_B_CAA<7>

MEM_B_CAA<5>

MEM_B_CAA<6>

MEM_B_CAA<4>

MEM_B_CAA<3>

MEM_B_CAA<2>

MEM_B_CAA<0>

MEM_B_CAA<1>

MEM_B_CS_L<1>

MEM_B_ODT<0>

MEM_B_CS_L<0>

MEM_B_CKE<3>

MEM_B_CKE<1>

MEM_B_CKE<0>

MEM_B_CKE<2>

MEM_B_CLK_N<1>

MEM_B_CLK_P<1>

MEM_B_CLK_P<0>

MEM_B_CLK_N<0>

CPU_SM_RCOMP<1>

SYNC_DATE=04/14/2015SYNC_MASTER=DEVMLB

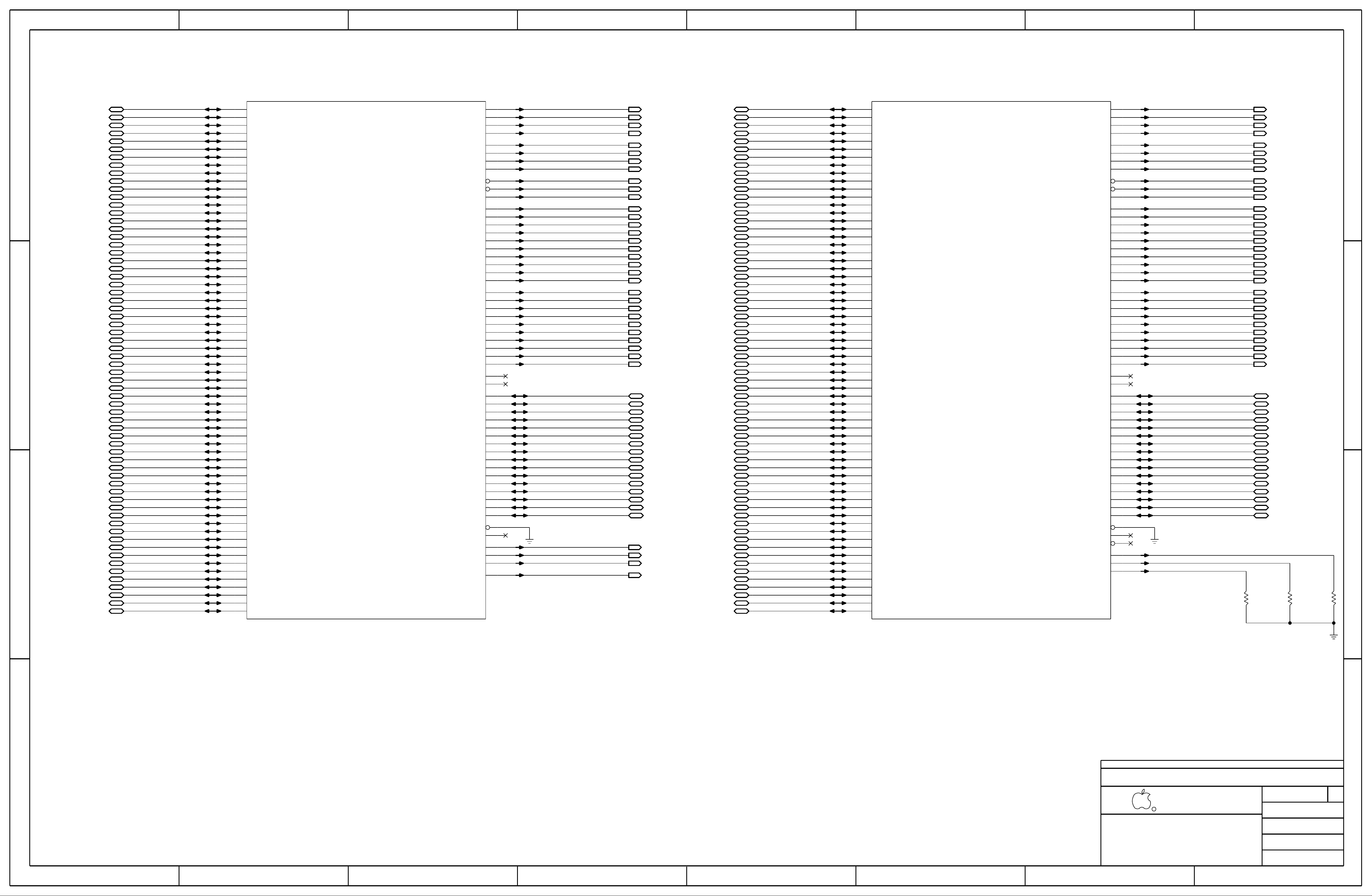

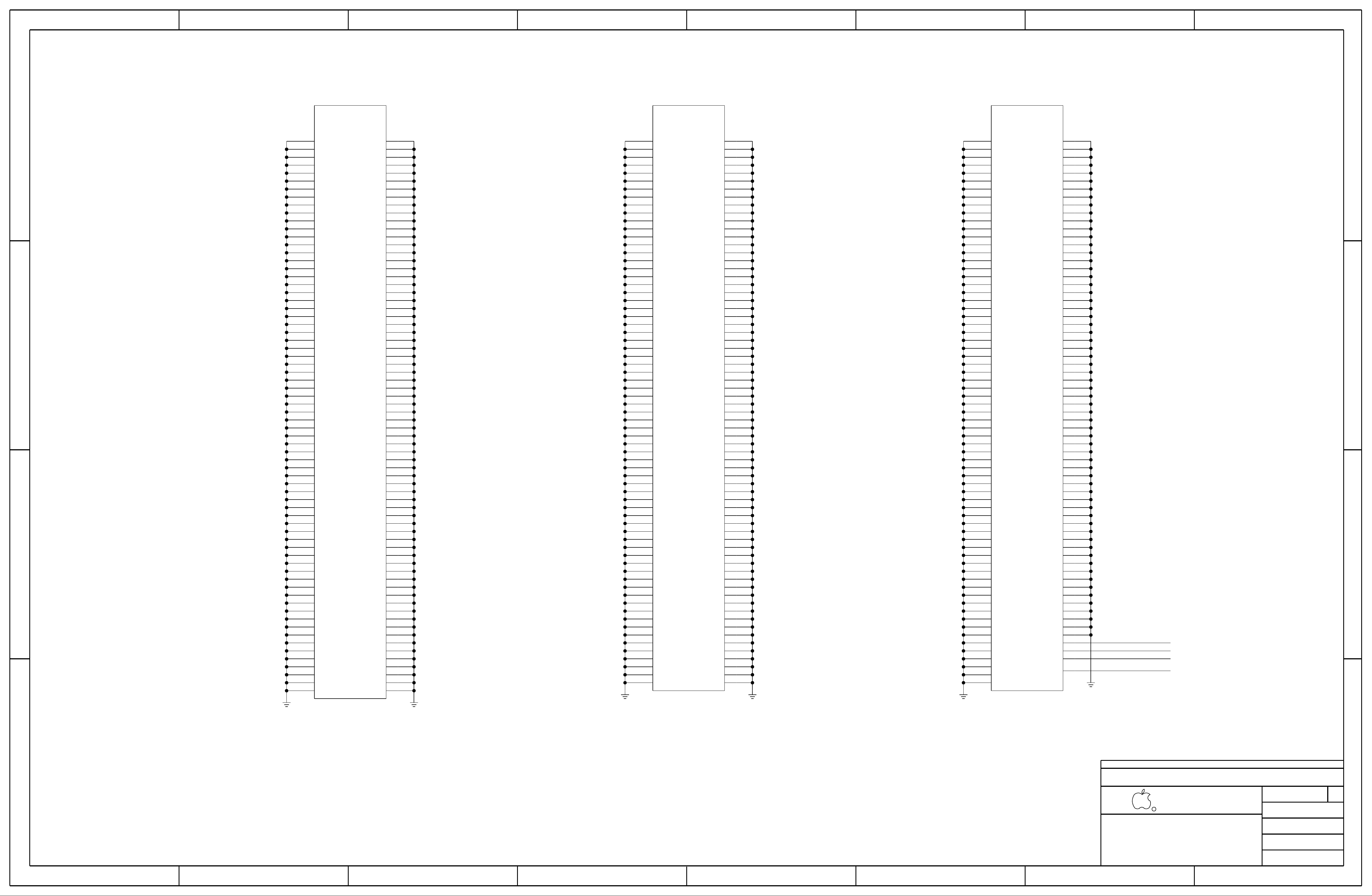

CPU LPDDR3 Interface

BOM_COST_GROUP=CPU & CHIPSET

62 22

62 22

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

65 21

21

21

21

65 21

21

21

21

21

21

21

65 21

65 21

22

22

22

22

22

22

22

22

22

65 22

22

22

22

22

22

22

65 22

22

65 22

22

22

65 22

22

22

22

65 22

22

22

22

22

22

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

65 62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

BF36

BC31

BG35

BD36

BF30

BC33

BF34

BC37

BE37

BG37

BN35

BM34

BJ35

BJ37

BN37

BG31

BL37

BM32

BN31

BK30

BP20

BJ33

BM30

BD34

BC64

BJ64

BF64

BD30

BC35

BK34

BJ31

BD22

BF26

BK22

BM26

BF22

BD26

BM22

BK26

BE21

BC21

BG23

BE23

BC23

BG21

BD24

BF24

BC25

BE25

BE27

BG27

BC27

BG25

BD28

BF28

BL21

BJ21

BN23

BL23

BJ23

BN21

BK24

BM24

BJ27

BJ25

BL27

BN25

BL25

BK28

BN27

BM28

BF32

BM36

BD32

BK36

BH30

BG33

BK32

BN33

BK40

BM44

BF44

BF40

BM40

BK44

BD44

BD40

BJ39

BL39

BL41

BK42

BN39

BJ41

BN41

BM42

BJ43

BJ45

BL45

BN43

BK46

BL43

BM46

BN45

BF46

BE45

BE43

BC45

BG45

BG43

BD46

BC43

BE41

BG39

BD42

BF42

BE39

BG41

BC39

BC41

U0500

BGA

SKL-Y

CRITICAL

OMIT_TABLE

SKL-Y-ULX

AV62

BN58

BM59

BL61

BB61

BN62

AV60

BJ61

BL62

BK59

BG61

BD61

BD59

BA56

AV58

AW57

AV56

BF62

AW55

AW59

BJ57

AW63

BG57

BN47

AR53

AW53

BM50

BK54

AJ55

AP58

BK50

BM54

AJ57

AP56

BM48

BK48

BN51

BN49

BJ49

BL49

BJ51

BL51

BK52

BM52

BN53

BN55

BL53

BJ53

BL55

BJ55

AG57

AG55

AK56

AK58

AH56

AH58

AL57

AL55

AM56

AM58

AT58

AR57

AN55

AN57

AR55

AT56

AN53

BM56

BN61

BL57

BB63

BD50

BF54

AP60

AJ63

BF50

BD54

AP62

AJ61

BD48

BF48

BG49

BG51

BE49

BC49

BE51

BC51

BF52

BD52

BG55

BC53

BE53

BG53

BC55

BE55

AT62

AR63

AN63

AN61

AR61

AT60

AM62

AM60

AL63

AL61

AG63

AH62

AK60

AK62

AH60

AG61

BA62

BC60

BA60

BC62

AW61

BE57

BC58

BB57

U0500

BGA

SKL-Y

OMIT_TABLE

SKL-Y-ULX

CRITICAL

63

2

1

R0750

PLACE_NEAR=U0500.BF64:12.7mm

1%

201

1/20W

MF

200

2

1

R0751

PLACE_NEAR=U0500.BJ64:12.7mm

MF

1%

201

1/20W

80.6

2

1

R0752

PLACE_NEAR=U0500.BC64:12.7mm

MF

1/20W

201

1%

162

20

20

20

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

62 21

65 62 21

62 21

65 62 21

62 21

62 21

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

62 22

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

BI

BI

NC

NC

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

NC

NC

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

DDR CH - B

SYM 3 OF 20

DDR1_CAA2

DDR1_CAA3

DDR1_CAA4

DDR1_CAB0

DDR1_CAA9

DDR1_CAA8

DDR1_CAA1

DDR1_CAA0

DDR1_CAA6

DDR0_DQSN4/DDR1_DQSN0

DDR0_DQSP4/DDR1_DQSP0

DDR0_DQSN5/DDR1_DQSN1

DDR0_DQSP5/DDR1_DQSP1

DDR1_CS0*

DDR1_CS1*

DDR1_ODT0

DDR1_CAB9

DDR1_CAB8

DDR1_CAB7

DDR1_CAB6

DDR1_CAB5

DDR1_CAB4

DDR1_CAB2

DDR1_CAB1

DDR1_CAA7

DDR1_CAA5

DDR0_DQ32/DDR1_DQ0

DDR0_DQSN7/DDR1_DQSN5

DDR0_DQSP7/DDR1_DQSP5

DDR0_DQSP6/DDR1_DQSP4

DDR0_DQSN6/DDR1_DQSN4

DDR1_DQSP5/DDR1_DQSP3

DDR1_DQSN5/DDR1_DQSN3

DDR1_DQSN4/DDR1_DQSN2

DDR1_DQSP4/DDR1_DQSP2

DDR1_MA3

DDR1_MA4

DDR1_DQSN7

DDR1_DQSN6

DDR1_DQSP6

DRAM_RESET*

DDR1_ALERT*

DDR_RCOMP2

DDR_RCOMP0

DDR_RCOMP1

DDR1_DQSP7

DDR1_PAR

DDR1_CKE3

DDR1_CKE1

DDR1_CKE2

DDR1_CKN1

DDR1_CKP1

DDR1_CKP0

DDR1_CKN0

DDR1_DQ63

DDR1_DQ62

DDR1_DQ61

DDR1_DQ60

DDR1_DQ59

DDR1_DQ58

DDR1_DQ57

DDR1_DQ55

DDR1_DQ56

DDR1_DQ52

DDR1_DQ53

DDR1_DQ54

DDR1_DQ51

DDR1_DQ50

DDR0_DQ63/DDR1_DQ47

DDR1_DQ48

DDR1_DQ49

DDR0_DQ62/DDR1_DQ46

DDR0_DQ61/DDR1_DQ45

DDR0_DQ58/DDR1_DQ42

DDR0_DQ59/DDR1_DQ43

DDR0_DQ60/DDR1_DQ44

DDR0_DQ57/DDR1_DQ41

DDR0_DQ56/DDR1_DQ40

DDR0_DQ55/DDR1_DQ39

DDR0_DQ54/DDR1_DQ38

DDR0_DQ53/DDR1_DQ37

DDR0_DQ52/DDR1_DQ36

DDR0_DQ51/DDR1_DQ35

DDR0_DQ50/DDR1_DQ34

DDR0_DQ49/DDR1_DQ33

DDR0_DQ48/DDR1_DQ32

DDR1_DQ45/DDR1_DQ29

DDR1_DQ46/DDR1_DQ30

DDR1_DQ47/DDR1_DQ31

DDR1_DQ44/DDR1_DQ28

DDR1_DQ43/DDR1_DQ27

DDR1_DQ40/DDR1_DQ24

DDR1_DQ42/DDR1_DQ26

DDR1_DQ39/DDR1_DQ23

DDR1_DQ38/DDR1_DQ22

DDR1_DQ37/DDR1_DQ21

DDR1_DQ36/DDR1_DQ20

DDR1_DQ35/DDR1_DQ19

DDR1_DQ34/DDR1_DQ18

DDR1_DQ33/DDR1_DQ17

DDR1_DQ32/DDR1_DQ16

DDR0_DQ46/DDR1_DQ14

DDR0_DQ47/DDR1_DQ15

DDR0_DQ43/DDR1_DQ11

DDR0_DQ44/DDR1_DQ12

DDR0_DQ45/DDR1_DQ13

DDR0_DQ42/DDR1_DQ10

DDR0_DQ41/DDR1_DQ9

DDR0_DQ38/DDR1_DQ6

DDR0_DQ39/DDR1_DQ7

DDR0_DQ40/DDR1_DQ8

DDR0_DQ36/DDR1_DQ4

DDR0_DQ37/DDR1_DQ5

DDR0_DQ33/DDR1_DQ1

DDR0_DQ34/DDR1_DQ2

DDR0_DQ35/DDR1_DQ3

DDR1_CKE0

DDR1_DQ41/DDR1_DQ25

DDR1_CAB3

DDR CH - A

SYM 2 OF 20

DDR0_CAB0

DDR0_CAA9

DDR0_CAA8

DDR0_CAB5

DDR0_CAA2

DDR0_CAA3

DDR0_CAA4

DDR0_CAA5

DDR0_CAA6

DDR0_CAA7

DDR0_CAB1

DDR0_CAB2

DDR0_CAB3

DDR0_CAB4

DDR0_CS1*

DDR0_ODT0

DDR0_DQ1

DDR1_DQ13/DDR0_DQ29

DDR0_DQ3

DDR0_DQ5

DDR0_CAB9

DDR0_CAB8

DDR0_CAB6

DDR0_CAB7

DDR0_CAA1

DDR0_CAA0

DDR0_DQ2

DDR0_DQ0

DDR0_DQ4

DDR0_DQ6

DDR0_DQ7

DDR0_DQ8

DDR0_DQ10

DDR0_DQ15

DDR0_CKE0

DDR0_CKE1

DDR0_CKE2

DDR0_CKN1

DDR0_DQ9

DDR0_DQ11

DDR0_DQ12

DDR0_DQ13

DDR0_DQ14

DDR1_DQ0/DDR0_DQ16

DDR1_DQ1/DDR0_DQ17

DDR1_DQ2/DDR0_DQ18

DDR1_DQ4/DDR0_DQ20

DDR1_DQ3/DDR0_DQ19

DDR1_DQ5/DDR0_DQ21

DDR1_DQ7/DDR0_DQ23

DDR1_DQ6/DDR0_DQ22

DDR1_DQ8/DDR0_DQ24

DDR1_DQ9/DDR0_DQ25

DDR1_DQ10/DDR0_DQ26

DDR1_DQ12/DDR0_DQ28

DDR1_DQ11/DDR0_DQ27

DDR1_DQ14/DDR0_DQ30

DDR0_DQ17/DDR0_DQ33

DDR0_DQ16/DDR0_DQ32

DDR0_DQ20/DDR0_DQ36

DDR0_DQ19/DDR0_DQ35

DDR0_DQ18/DDR0_DQ34

DDR0_DQ22/DDR0_DQ38

DDR0_DQ21/DDR0_DQ37

DDR0_DQ23/DDR0_DQ39

DDR0_DQ25/DDR0_DQ41

DDR0_DQ24/DDR0_DQ40

DDR0_DQ27/DDR0_DQ43

DDR0_DQ30/DDR0_DQ46

DDR0_DQ29/DDR0_DQ45

DDR0_DQ31/DDR0_DQ47

DDR1_DQ16/DDR0_DQ48

DDR1_DQ17/DDR0_DQ49

DDR1_DQ19/DDR0_DQ51

DDR1_DQ18/DDR0_DQ50

DDR1_DQ20/DDR0_DQ52

DDR1_DQ21/DDR0_DQ53

DDR1_DQ22/DDR0_DQ54

DDR1_DQ24/DDR0_DQ56

DDR1_DQ23/DDR0_DQ55

DDR1_DQ25/DDR0_DQ57

DDR1_DQ26/DDR0_DQ58

DDR1_DQ27/DDR0_DQ59

DDR1_DQ29/DDR0_DQ61

DDR1_DQ28/DDR0_DQ60

DDR1_DQ30/DDR0_DQ62

DDR1_DQ31/DDR0_DQ63

DDR1_DQ15/DDR0_DQ31

DDR0_DQ28/DDR0_DQ44

DDR0_DQ26/DDR0_DQ42

DDR0_CKN0

DDR0_CKP0

DDR0_CKP1

DDR0_CKE3

DDR0_CS0*

DDR0_PAR

DDR_VREF_CA

DDR1_VREF_DQ

DDR0_VREF_DQ

DDR_VTT_CNTL

DDR0_ALERT*

DDR0_MA3

DDR0_MA4

DDR0_DQSP0

DDR0_DQSN0

DDR0_DQSP1

DDR0_DQSN1

DDR1_DQSN1/DDR0_DQSN3

DDR1_DQSP0/DDR0_DQSP2

DDR1_DQSN0/DDR0_DQSN2

DDR1_DQSP1/DDR0_DQSP3

DDR0_DQSN2/DDR0_DQSN4

DDR0_DQSP2/DDR0_DQSP4

DDR0_DQSP3/DDR0_DQSP5

DDR0_DQSN3/DDR0_DQSN5

DDR1_DQSN3/DDR0_DQSN7

DDR1_DQSP2/DDR0_DQSP6

DDR1_DQSN2/DDR0_DQSN6

DDR1_DQSP3/DDR0_DQSP7

OUT

NC

NCNC

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

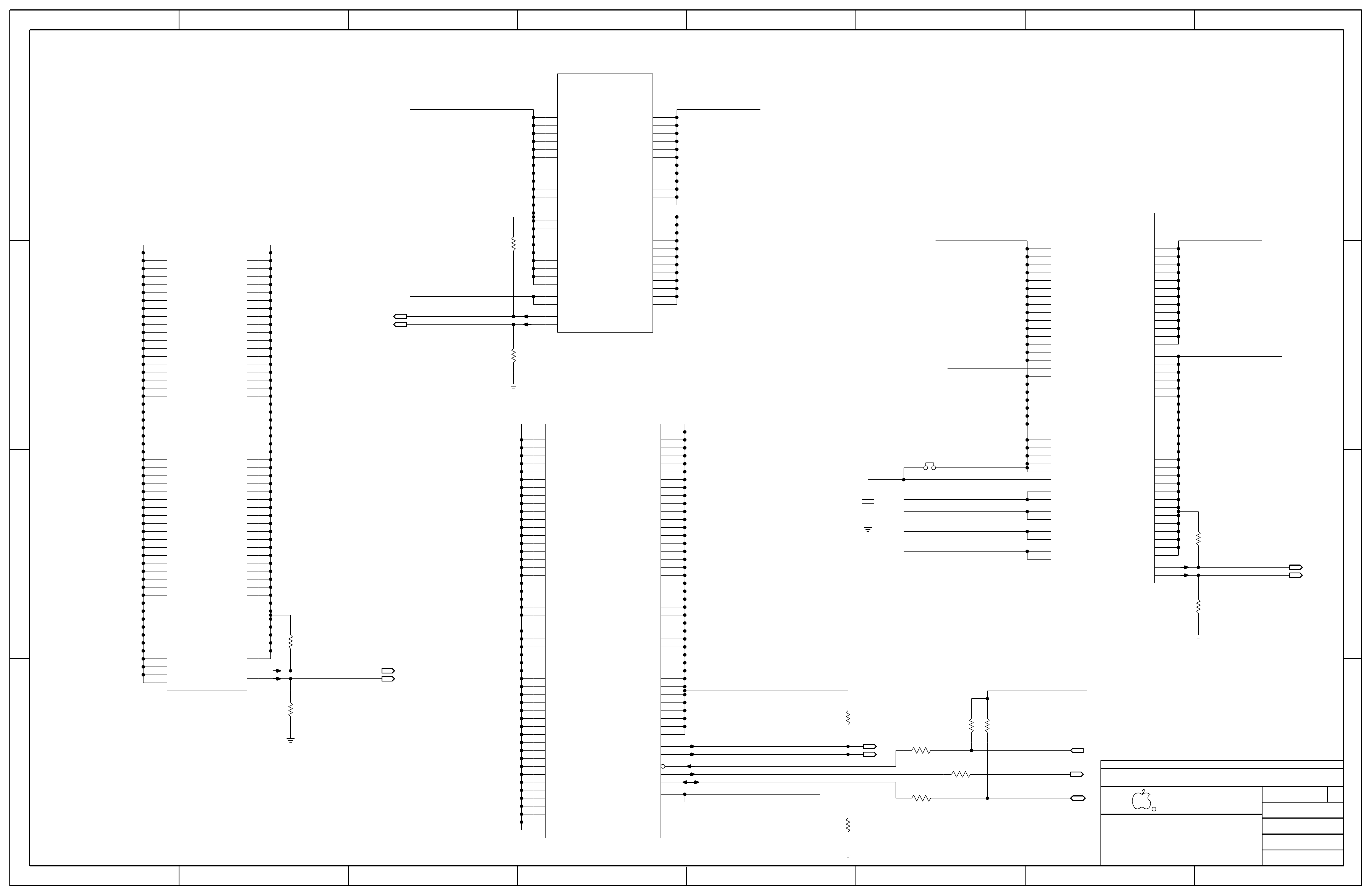

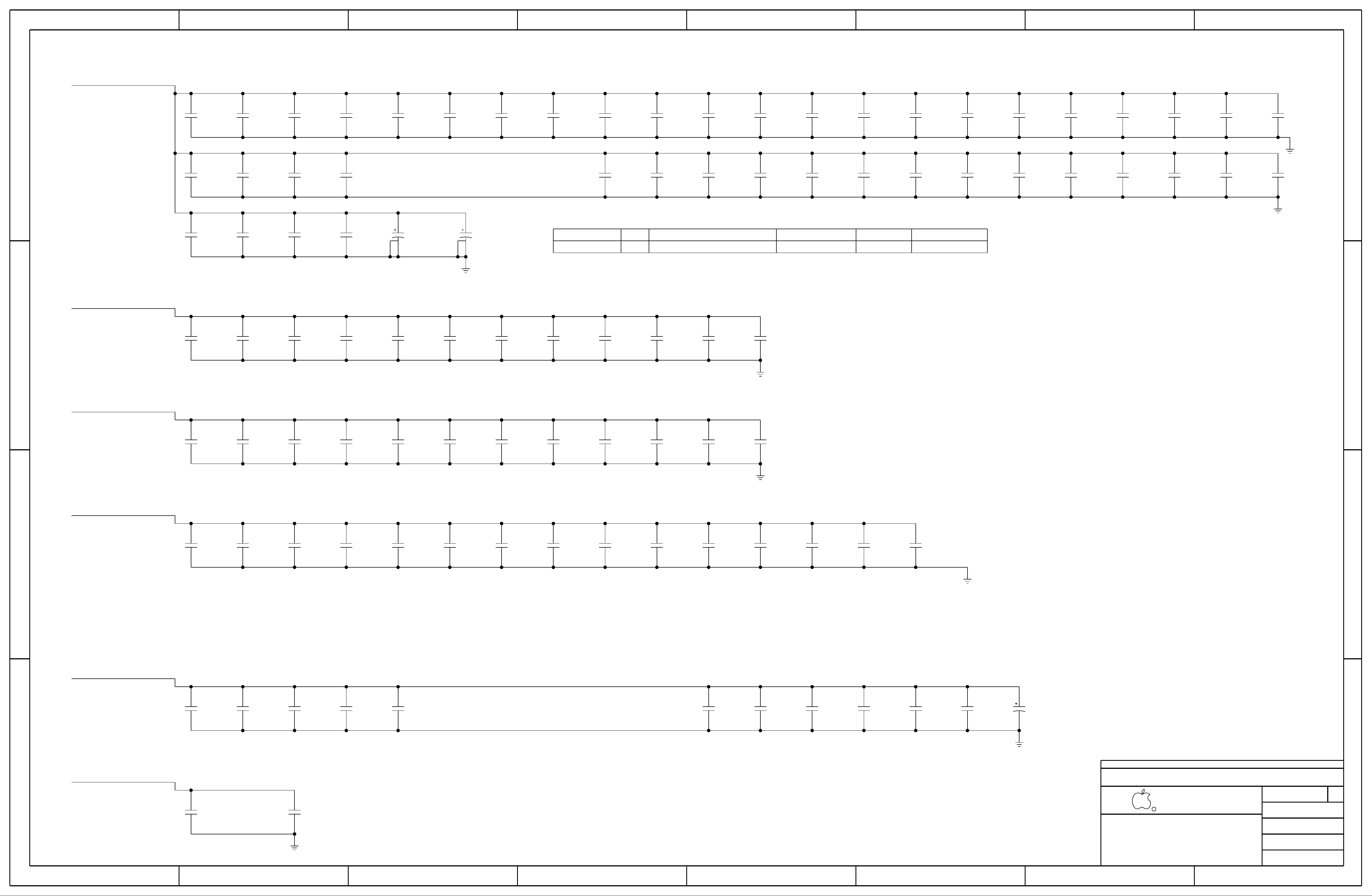

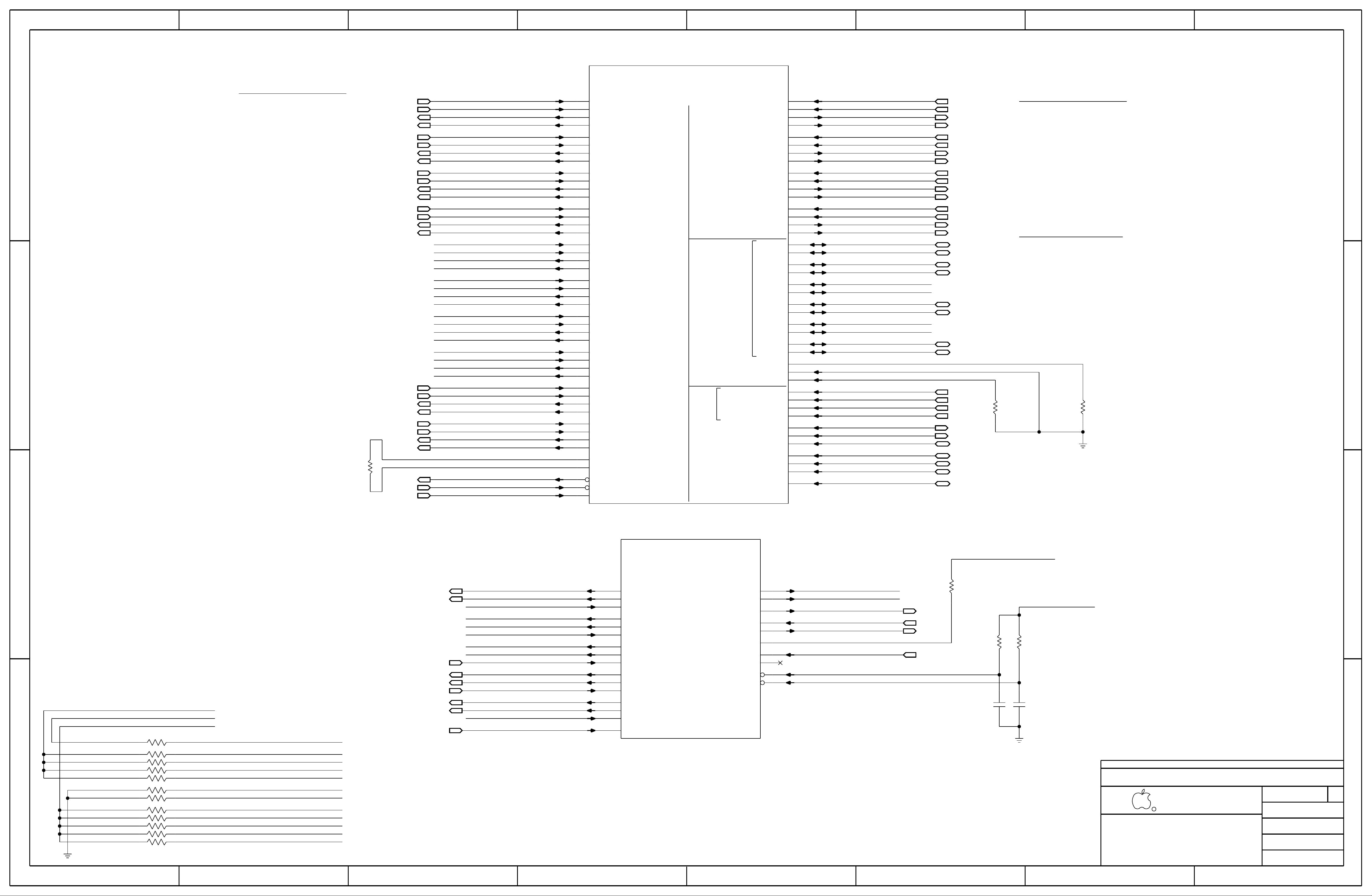

plane to BGA pads

R0802.2:

R0800.2:

R0811.1:

VCCIO breakdown per 4/20/15 email from Srini

SKL-ULX current estimates from Skylake Processor EDS vol 1, doc #544924, v0.94

320mA Max

3.78A Max

be isolated from local

VCCIO & VCCIO_DDR must

2A Max

24A Max

24A Max

NOTE: Aliases not used on CPU supply outputs

to avoid any extraneous connections.

1nH trace filter

VCCSA & VCCSA_DDR must

be isolated from VR

output to BGA pads

1.75A Max

1.185A Max

VDDQC must implement

8 OF 130

<E4LABEL>

<SCH_NUM>

<BRANCH>

8 OF 67

VOLTAGE=1.5V

11

MIN_NECK_WIDTH=0.2000

MIN_LINE_WIDTH=0.2000

VOLTAGE=1.2V

MIN_NECK_WIDTH=0.2000

MIN_LINE_WIDTH=0.2000

VOLTAGE=1.5V

11

MIN_NECK_WIDTH=0.2000

MIN_LINE_WIDTH=0.2000

PPVCCG1_S0_CPU

PP1V2_S0_CPU_VDDQC

TP_MCP_DC_B64

TP_MCP_DC_A64 TP_MCP_DC_BP64

TP_MCP_DC_BN64

PP1V_S0SW

CPU_VCCSASENSE_N

CPU_VCCGTSENSE_P

CPU_VCCGTSENSE_N

PPVCORE_S0_CPU

CPU_VCCIOSENSE_N

CPU_VCCIOSENSE_P

PP1V_S3

PPVCORE_S0_GT PPVCORE_S0_GT

PPVCCSA_S0

PPVCCIO_S0

PP1V_S3

PP1V2_S3 PPVCCIO_S0

PP1V2_S0SW

PPVCCG0_S0_CPU

CPU_VIDSOUT_R

CPU_VIDALERT_R_L

PPVCORE_S0_CPU

PP1V_S3

CPU_VCCSENSE_N

CPU_VCCSENSE_P

CPU_VIDALERT_L

CPU_VIDSOUT

CPU_VIDSCLK_R CPU_VIDSCLK

PP1V_S0SW

PPVCCSA_DDR_S0

CPU_VCCSASENSE_P

SYNC_DATE=05/11/2015SYNC_MASTER=DEVMLB

BOM_COST_GROUP=CPU & CHIPSET

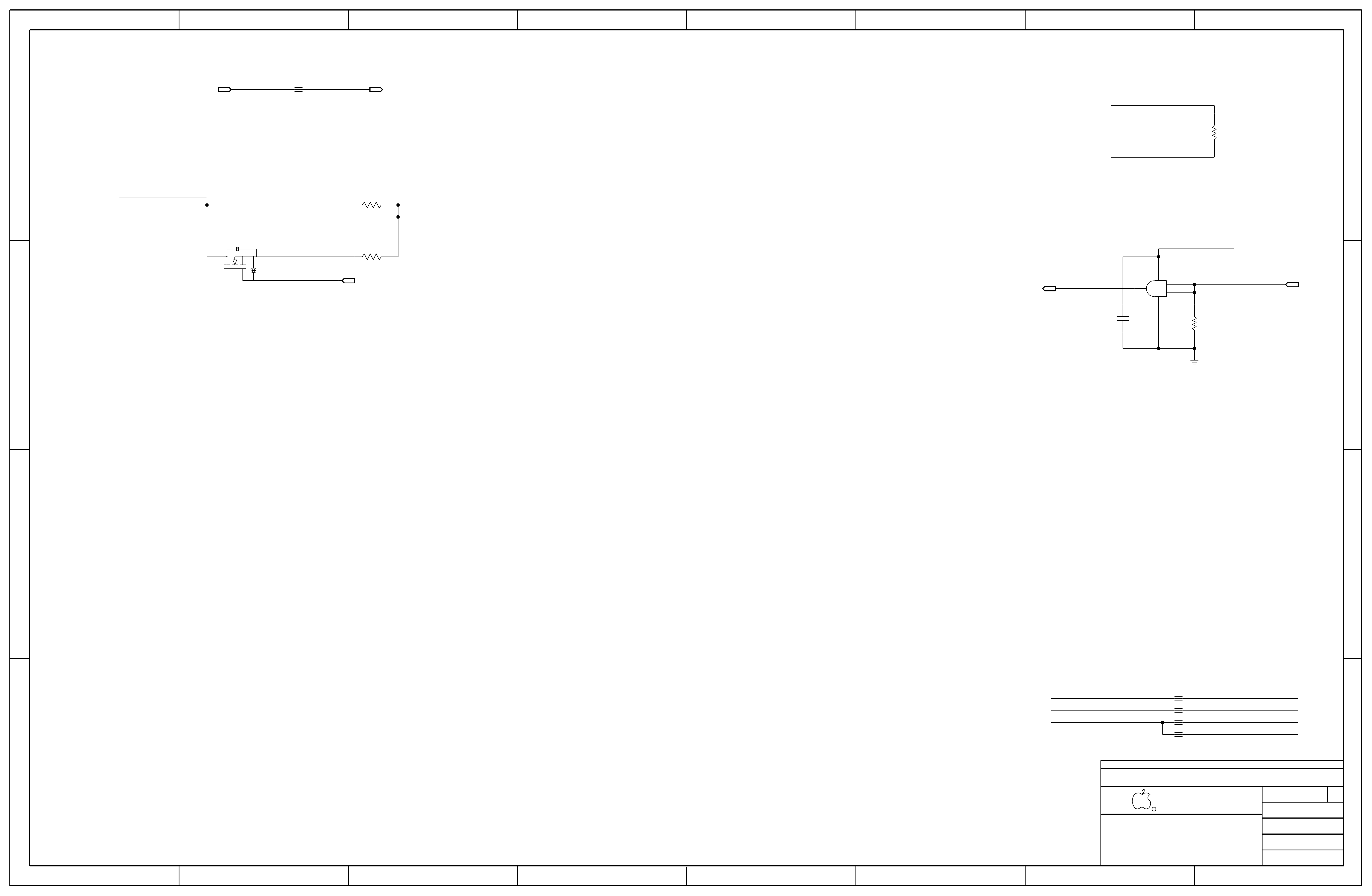

CPU Power

42

42

2

1

R0861

PLACE_NEAR=U0500.R30:50.8mm

1/32W

01005

100

MF

5%

2

1

R0860

PLACE_NEAR=U0500.N30:50.8mm

1/32W

01005

100

MF

5%

2

1

R0840

PLACE_NEAR=U0500.AT26:50.8mm

1/32W

01005

100

MF

5%

2

1

R0841

PLACE_NEAR=U0500.AN24:50.8mm

1/32W

01005

100

MF

5%

47

47

2

1

C0850

BYPASS=U0500.BA39::0.59mm

10%

0201

X5R-CERM

10V

0.1UF

21

XW0850

SM

2

1

R0831

PLACE_NEAR=U0500.P52:50.8mm

1/32W

01005

100

MF

5%

2

1

R0830

PLACE_NEAR=U0500.N52:50.8mm

1/32W

01005

100

MF

5%

42

42

21

R0812

0

0201

MF

1/20W

5%

21

R0810

220

1%

MF

1/20W

201

21

R0811

0

0201

PLACE_NEAR=U0500.A56:12.7mm

MF

1/20W

5%

2

1

R0800

56

PLACE_NEAR=U0500.B58:12.7mm

1%

MF

1/20W

201

2

1

R0802

PLACE_NEAR=U0500.A58:12.7mm

100

1%

MF

1/20W

201

42

42

42

2

1

R0821

PLACE_NEAR=U0500.L32:50.8mm

1/32W

01005

100

MF

5%

2

1

R0820

PLACE_NEAR=U0500.L34:50.8mm

1/32W

01005

100

MF

5%

42

42

N28

Y30

Y29

V29

T30

T29

M29

R29

N30

M31

L30

AT30

AT29

AR29

AN30

AN29

AL29

AK30

AK29

AH29

AF30

AF29

AE29

AC30

AC29

AA29

AR38

AR35

AN38

AN35

AL38

AL35

AK38

AK35

AH38

AH35

AF38

AF35

Y38

Y35

V38

V35

T38

T35

R38

R35

AC38

AC35

AA38

AA35

U0500

SKL-Y-ULX

BGA

CRITICAL

OMIT_TABLE

SKL-Y

AR24

BA39

BP64

BP58

BP56

BP50

BP48

BP42

BP40

BP34

BP32

BP26

BP24

BN64

BA51

BA49

BA47

BA45

BA43

BA41

BA37

BA35

BA33

BA31

BA29

BA27

BA25

AV64

AT64

AK64

AH64

T26

R26

Y26

V26

T27

R27

AF27

AE27

AT24

AW51

AW49

AW47

AW45

AW43

AW41

AW39

AW37

AW35

AW33

AW31

AW29

AW27

AV50

AV48

AV46

AV44

AV42

AV40

AV38

AV36

AV34

AV32

AV30

AV28

AV26

AT26

AR26

AN26

AL26

AK26

AH26

AF26

AF24

AE26

AE24

AE23

AC24

AC23

U0500

OMIT_TABLE

CRITICAL

SKL-Y-ULX

SKL-Y

BGA

P52

Y64

Y62

Y60

Y58

Y56

Y54

Y51

Y50

Y49

Y47

Y46

Y44

Y43

W63

W61

W59

W57

W55

W53

V64

V62

V60

V58

V56

V54

U63

U61

U59

U57

U55

U53

T54

T51

T50

T49

T47

T46

T44

T43

N52

R53

R51

N50

N48

N46

N44

AT51

AT50

AT49

AT47

AT46

AT44

AT43

AN51

AN50

AN49

AN47

AN46

AN44

AN43

AK51

AK50

AK49

AK47

AK46

AK44

AK43

AJ53

AG53

AF51

AF50

AF49

AF47

AF46

AF44

AF43

AE63

AE61

AE59

AE57

AE55

AE53

AD64

AD62

AD60

AD58

AD56

AD54

AC63

AC61

AC59

AC57

AC55

AC53

AC51

AC50

AC49

AC47

AC46

AC44

AC43

AB64

AB62

AB60

AB58

AB56

AB54

AA53

U0500

OMIT_TABLE

SKL-Y-ULX

CRITICAL

SKL-Y

BGA

B58

L32

A58

A56

AC26

AA26

Y41

Y32

V41

V32

T41

T32

L34

R63

R61

R59

R57

R41

R32

P64

P62

P60

P58

P56

N63

N61

N59

N57

N55

N54

N42

N40

N38

N36

N34

N32

M64

M62

M60

M58

M56

M53

M51

M49

M47

M45

M43

M41

M39

M37

M35

M33

L63

L54

L52

L50

L48

L46

L44

L42

L40

J64

H63

F64

D64

B64

AT41

AT40

AT38

AT36

AT35

AT33

AT32

AR41

AR32

AN41

AN32

AL41

AL32

AK41

AK32

AH41

AH32

AF41

AF32

AE41

AE40

AE38

AE36

AE35

AE33

AE32

AC41

AC32

AA41

AA32

A64

U0500

SKL-Y-ULX

OMIT_TABLE

CRITICAL

SKL-Y

BGA

63

61 50 12 8 6

61 43 34 11 8

61 50 42 31 15 12 8 6

61 44

34 12 8 61 44 34 12 8

61 43 11

61 47 11 8 5

61 50 42 31

15 12 8 6

61 50 47 22 21 20 12 61 47 11 8 5

61 50 12

61 43 34 11 8

61 50 42 31 15 12 8 6

63 61

50 12 8 6

61 43 11

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

OUT

OUT

OUT

OUT

OUT

OUT

BI

OUT

IN

OUT

OUT

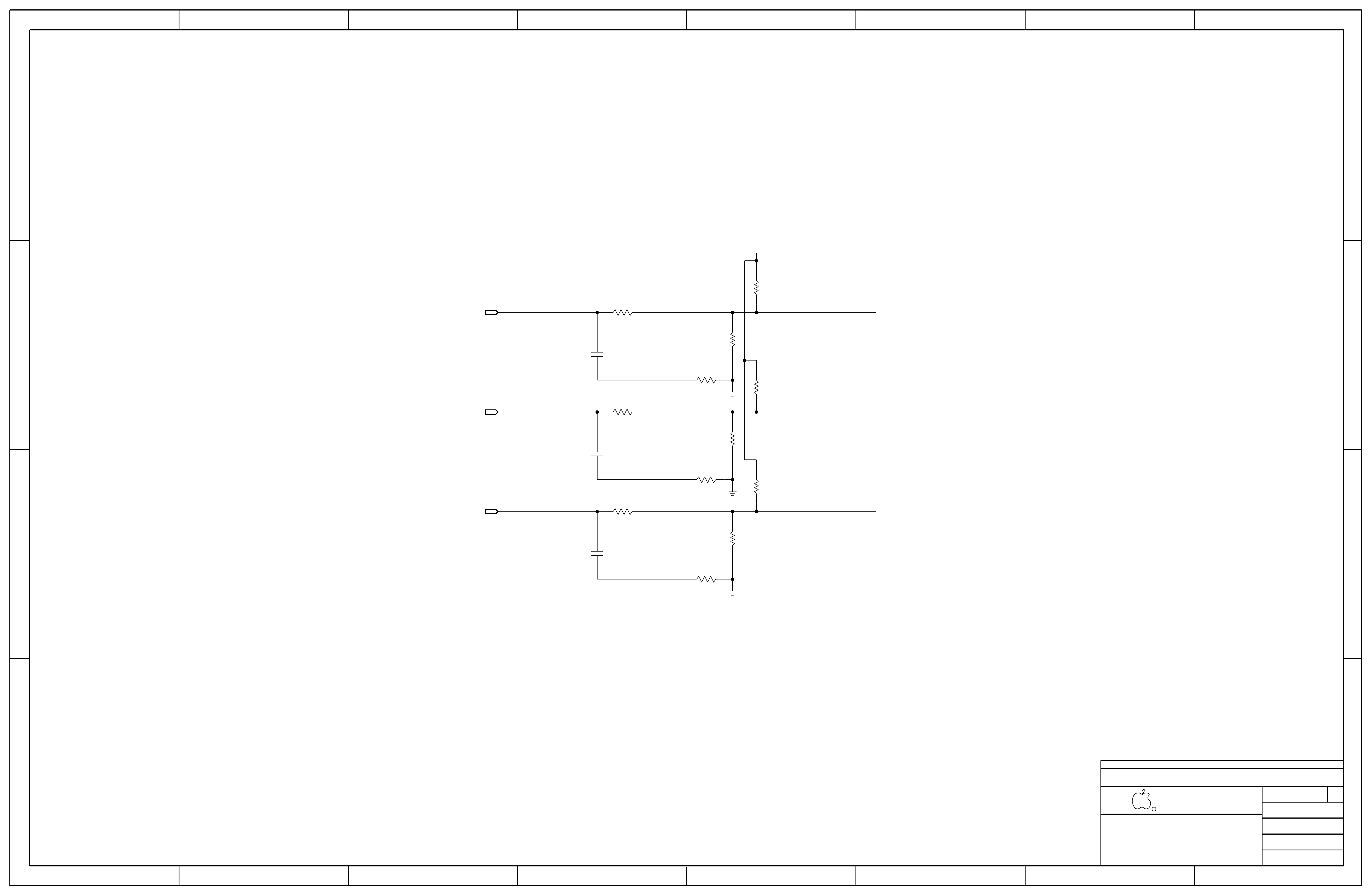

CPU POWER 4 OF 4

SYM 16 OF 20

VCCG0

VCCG0

VCCG0

VCCG0

VCCG0

VCCG0

VCCG0

VCCG0

VCCG1

VCCG1

VCCG0

VCCG1

VCCG0

VCCG0

VCCG0

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCSA_SENSE

VCCSA_DDR

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VSSSA_SENSE

VCCSA_DDR

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

CPU POWER 3 OF 4

SYM 15 OF 20

VDDQ

VDDQ

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VSSIO_SENSE

VCCIO_SENSE

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VDDQ

VCCPLL

VCCPLL

VCCPLL_OC

VCCPLL_OC

VCCSTG

VCCSTG

VCCST

VCCST

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VDDQ

SYM 14 OF 20

CPU POWER 2 OF 4

VSSGT_SENSE

VCCGT_SENSE

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

CPU POWER 1 OF 4

SYM 13 OF 20

VCCSTG

VCCSTG

VIDALERT*

VIDSCK

VIDSOUT

VCC

VCC

VCC

VCC

VCC

VCC

VCC_SENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS_SENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCVCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

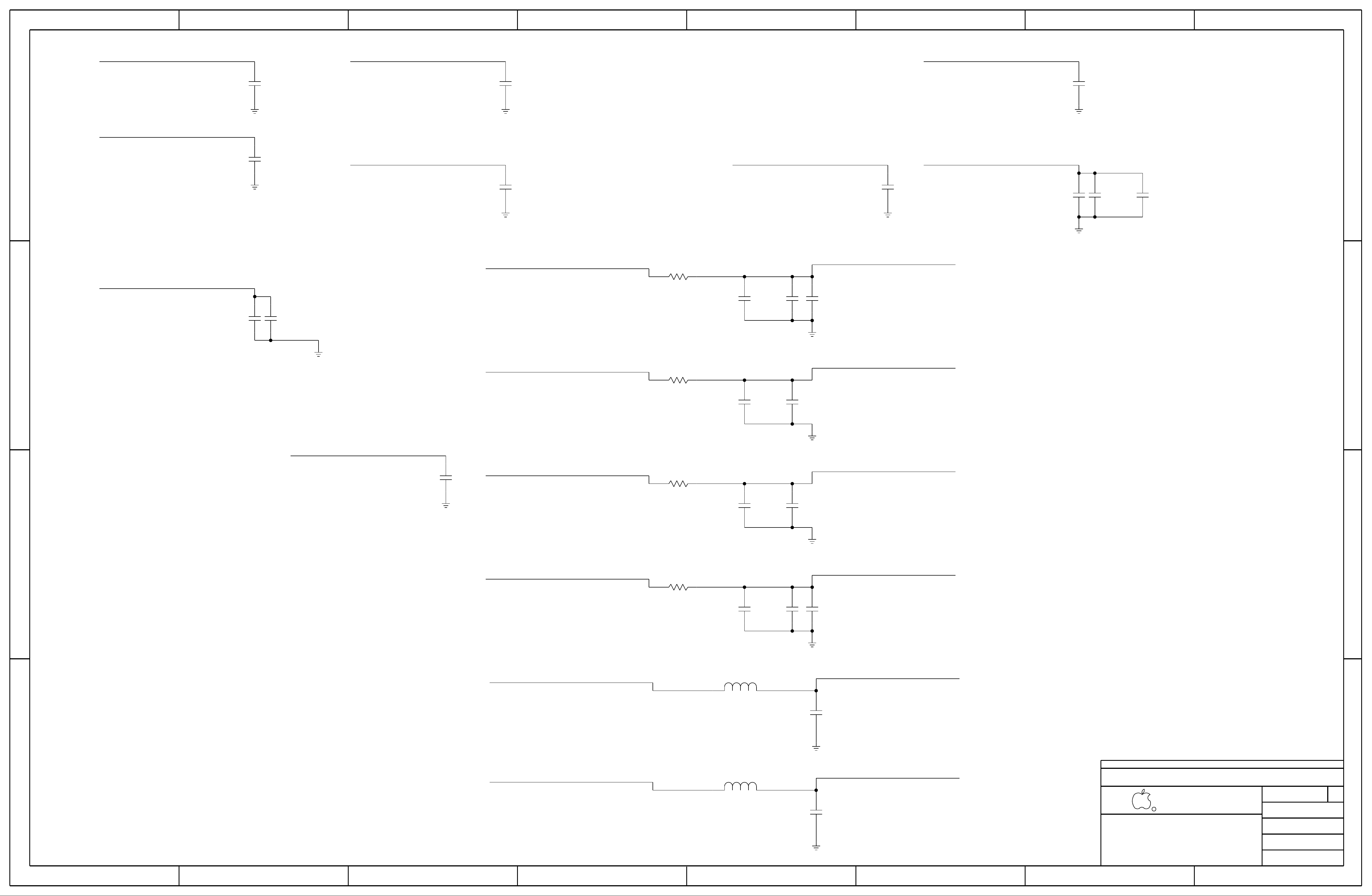

24mA Max

33/161mA @ 3.3/1.8V Max

6/3mA @ 3.3/1.8V Max

4/2mA @ 3.3/1.8V Max

6/2mA @ 3.3/1.8V Max

8/3mA @ 3.3/1.8V Max

20/9mA @ 3.3/1.8V Max

Must not exceed

35mA Max

<1mA Max

<1mA Max

6mA Max

6mA Max

1mA Max

29mA Max

33mA Max

10mA Max

41/56mA @ 3.3/1.8V Max

68/36/33mA @ 3.3/1.8/1.5V Max

Project specific (X260 TBD)

1.1A Max

370mA Max

See EDS Table 10-5

168mA Max

88mA Max

71mA Max

22mA Max

26mA Max

55mA Max

74mA Max

11/7mA @ 3.3/1.8V Max

0.565A Max

33mA Max

VCCAMPHYPLL_1P0 and VCCPRIM_1P0 / VCCPRIM_3P3 breakdowns from Srini email 4/13/15

SPT-LP current estimates from Sunrise Point-LP PCH EDS vol 1, doc #545659, v1.2. NOTE: Aliases not used on CPU supply outputs

to avoid any extraneous connections.

3.2V max

4mA Max

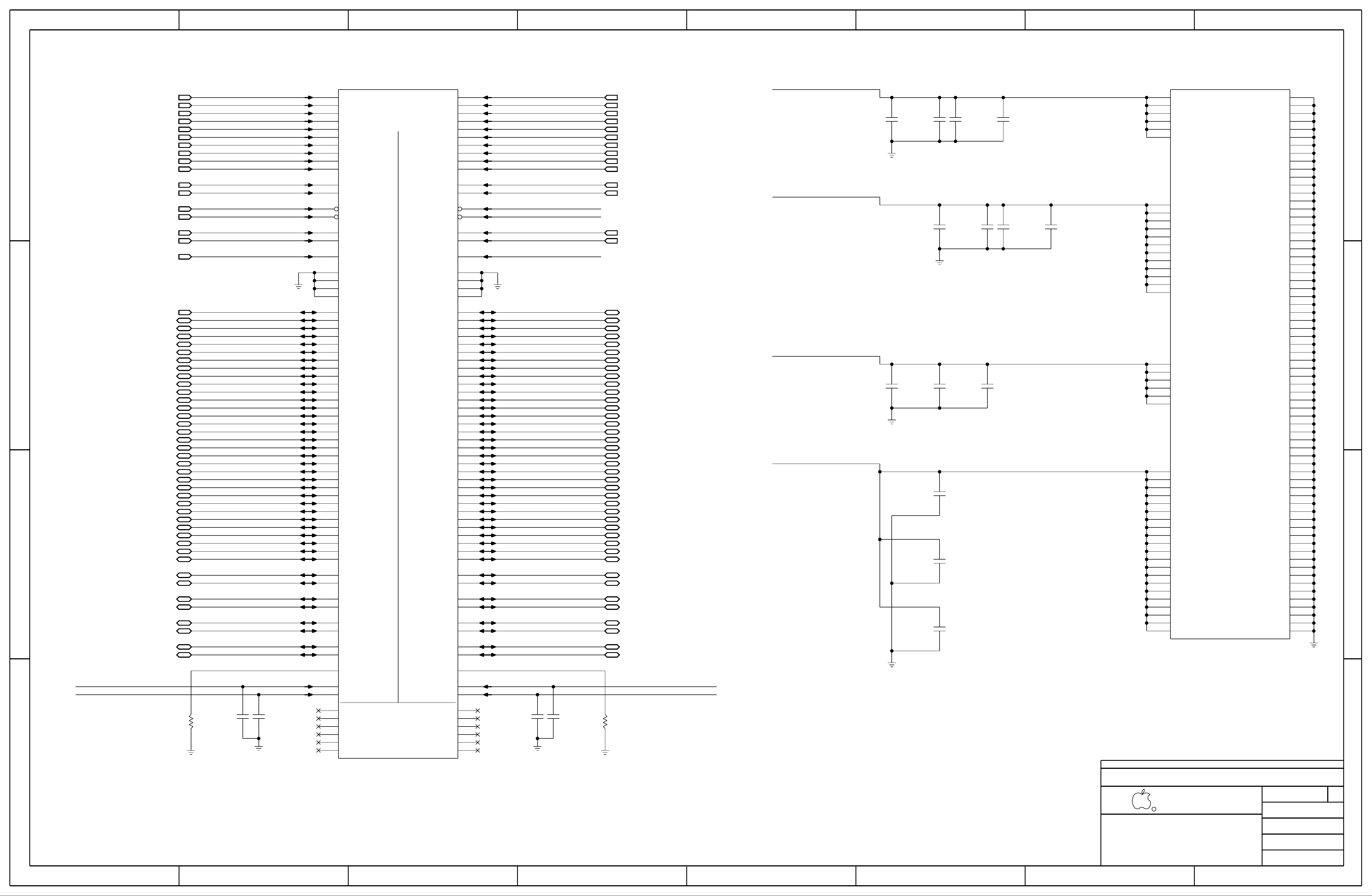

9 OF 67

9 OF 130

<E4LABEL>

<SCH_NUM>

<BRANCH>

VOLTAGE=1.0V

MIN_LINE_WIDTH=0.2000

MIN_NECK_WIDTH=0.2000

VOLTAGE=1.0V

MIN_LINE_WIDTH=0.2000

MIN_NECK_WIDTH=0.2000

PP1V_SUS

PP1V_SUS_PCH_VCCCLK4

PP1V_SUS_PCH_VCCCLK5

PP1V_SUSSW_HSIO

PP1V_SUS

PP1V_S5_PCH_DCPDSW

PP1V8_SUS

PP3V3_SUS

PPVRTC_G3H

PP1V_SUSSW_HSIO

PP1V_SUS

PP3V3_SUS

PP1V_SUSSW_HSIO

PP3V3_SUS

PP3V3_S5

PP1V_SUS_PCH_VCCAPLL

PP3V3R1V8R1V5_S0_PCH_VCCHDA

PP1V_SUSSW_PCH_VCCAMPHYPLL

PP1V_SUS

PP1V_SUS

PP1V_SUS

PP1V_SUS_PCH_VCCCLK3

PP3V3_SUS

PP1V_SUS

TP_PCH_CORE_VID<1>

TP_PCH_CORE_VID<0>

PPVCORE_SUS_PCH

PP1V_SUS

PP3V3_SUS

PP1V8_SUS

PP3V3_SUS

PP3V3_SUS

PP3V3_SUS

PP3V3_SUS

PP3V3_SUS

PPVOUT_S0_PCH_DCPRTC

SYNC_DATE=05/11/2015SYNC_MASTER=DEVMLB

BOM_COST_GROUP=CPU & CHIPSET

PCH Power

2

1

C0901

BYPASS=U0500.AR19::2.10mm

X5R

0201-1

1.0UF

6.3V

20%

2

1

C0900

BYPASS=U0500.AT19::2.10mm

0.1UF

10V

10%

X5R-CERM

0201

2

1

C0910

BYPASS=U0500.AT18::1.08mm

0.1UF

10V

10%

X5R-CERM

0201

V16

V15

R16

R15

AR23

AN23

AL23

AK23

AA23

AA21

AV15

AT15

AL19

AK19

AT19

AR19

AT16

AR16

AF19

AF18

AE19

AE18

AK21

AH21

AD1

AC2

AT21

AR21

AL18

AK18

AH19

AH18

AH15

AH13

AA16

AA15

AP13

AN15

AP1

AN2

AB1

AA2

AG2

AF1

AJ2

AH1

AW2

AV1

AU2

AT1

U2

T16

T15

T1

W2

V1

AV22

AT23

AM13

AL15

T19

R19

R23

R21

Y21

V21

Y23

V23

Y19

V19

Y18

V18

AE16

AE15

AA19

AA18

BB12

BA13

AV18

AT18

AM1

AL2

U0500

SKL-Y-ULX

CRITICAL

OMIT_TABLE

SKL-Y

BGA

2

1

C0920

BYPASS=U0500.AL2::5.32mm

X5R

0201-1

1.0UF

6.3V

20%

61 50 48 19 16 13 9

13

13

61 50 13 9

61 50 48 19

16 13 9

61 50 48 33 24 17 13 9

61 50 49 46 36 17 16 14 13 9

61 46 16 15

61 50 13 9

61 50 48 19 16 13 9

61 50 49 46 36 17 16 14 13 9

61 50 13 9

61 50 49 46 36 17 16 14 13 9

67 61

60 59 50 49 48 46 45 18 15 13

13

13

13

61 50 48 19 16 13 9

61 50 48 19 16 13 9

61

50 48 19

16 13 9

13

61 50 49 46 36 17 16 14 13 9

61 50 48 19 16 13 9

61 48

61 50 48 19 16 13 9

61 50 49 46 36 17 16 14 13 9

61 50 48 33 24 17 13 9

61 50 49 46 36 17 16 14 13 9

61 50 49 46 36 17 16 14 13 9

61 50 49 46 36 17 16 14

13 9

61 50 49 46 36 17 16 14 13 9

61 50 49 46 36 17 16 14 13 9

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

PCH POWER

SYM 17 OF 20

DCPRTC

VCCCLK1

VCCCLK1

VCCCLK2

VCCCLK2

VCCCLK3

VCCCLK3

GPP_B0/CORE_VID0

GPP_B1/CORE_VID1

VCCCLK4

VCCCLK4

VCCCLK5

VCCCLK5

VCCCLK6

VCCCLK6

VCCPGPPA

VCCPRIM_3P3

VCCPRIM_3P3

VCCPGPPA

VCCPGPPC

VCCPGPPC

VCCPGPPB

VCCPGPPB

VCCPGPPD

VCCPGPPG

VCCPGPPG

VCCPGPPF

VCCPGPPF

VCCPGPPE

VCCPGPPE

VCCPGPPD

VCCPRIM_1P0

VCCRTCPRIM_3P3

VCCPRIM_1P0

VCCRTCPRIM_3P3

VCCRTC

VCCATS

VCCATS

VCCRTC

DCPRTC

VCCAMPHYPLL_1P0

VCCAMPHYPLL_1P0

VCCMPHYGT_1P0

VCCMPHYAON_1P0

VCCMPHYGT_1P0

VCCMPHYGT_1P0

VCCAPLL_1P0

VCCAPLL_1P0

VCCPRIM_1P0

VCCPRIM_3P3

VCCPRIM_1P0

VCCPRIM_3P3

VCCSRAM_1P0

VCCSRAM_1P0

VCCSRAM_1P0

VCCSRAM_1P0

VCCSRAM_1P0

VCCSRAM_1P0

VCCSPI

VCCSPI

VCCHDA

VCCHDA

VCCDSW_3P3

VCCDSW_3P3

VCCPRIM_1P0

VCCPRIM_1P0

VCCPRIM_1P0

VCCPRIM_1P0

VCCPRIM_1P0

VCCPRIM_1P0

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

DCPDSW_1P0

DCPDSW_1P0

VCCMPHYAON_1P0

VCCMPHYGT_1P0

VCCAPLLEBB_1P0

VCCAPLLEBB_1P0

<BRANCH>

<SCH_NUM>

<E4LABEL>

10 OF 130

10 OF 67

TP_MCP_DC_D1

TP_MCP_DC_A5

TP_MCP_DC_BP62

TP_MCP_DC_BP1

SYNC_DATE=04/14/2015SYNC_MASTER=DEVMLB

CPU & PCH Grounds

BOM_COST_GROUP=CPU & CHIPSET

Y27

Y13

Y11

Y5

Y3

V49

V47

V40

V36

V13

T58

T56

T24

T23

R47

R46

R36

R18

R8

R6

R4

R2

P54

N26

N18

N16

L59

L57

K51

K49

K41

K39

K31

K29

K21

K19

J62

J7

G14

F62

E52

E50

E42

E40

E32

E30

E22

E20

D62

D8

D1

C40

C14

BP62

BP52

BP46

BP30

BP28

BP1

BN29

BM38

BM14

BM11

BL33