Page 1

RocketIO™

Transceiver

User Guide

UG024 (v1.5) October 16, 2002

R

Page 2

R

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

"Xilinx" and the Xilinx logo are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved.

CoolRunner, RocketChips, Rocket IP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, XC5210 are registered

Trademarks of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator,

CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and Beyond!,

HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroBlaze, MicroVia, MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, RocketIO, SelectIO, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, VirtexII Pro, Wave Table, WebFITTER, WebPACK, WebPOWERED, XABEL, XACT-Floorplanner, XACT-Performance, XACTstep Advanced, XACTstep

Foundry, XAM, XAPP, X-BLOX +, XC designated products, XChecker, XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP and ZERO+ are trademarks of Xilinx, Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both:

IBM IBM Logo PowerPC PowerPC Logo Blue Logic CoreConnect CodePack

All other trademarks are the property of their respective owners.

Xilinx does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license

under its patents, copyrights, or maskwork rights or any rights of others. Xilinx reserves the right to make changes, at any time, in order to

improve reliability, function or design and to supply the best product possible. Xilinx will not assume responsibility for the use of any circuitry

described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or information shown or described herein

"as is." By providing the design, code, or information as one possible implementation of a feature, application, or standard, Xilinx makes no representation that such implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your

implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of any such implementation, including but not

limited to any warranties or representations that the implementation is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx assumes no obligation to correct any errors contained herein or to advise any user of this

text of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or software support

or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the

written consent of the appropriate Xilinx officer is prohibited.

Copyright 2002 Xilinx, Inc. All Rights Reserved.

RocketIO™ Transceiver User Guide www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778

Page 3

RocketIO™ Transceiver User Guide

UG024 (v1.5) October 16, 2002

The following table shows the revision history for this document.

Date Version Revision

11/20/01 1.0 Initial Xilinx release.

01/23/02 1.1 Updated for typographical and other errors found during review.

02/25/02 1.2 Part of Virtex-II Pro™ Developer’s Kit (March 2002 Release)

07/11/02 1.3 Updated PCB Design Requirements, Chapter 4. Added Timing Model as Appendix A,

changed Cell Models to Appendix B.

09/27/02 1.4

• Added additional IMPORTANT NOTES regarding ISE revisions at the beginning of

Chapter 1

• Added material in section CRC Operation, Chapter 3

• Added section Other Important Design Notes, Chapter 3

• New pre-emphasis eye diagrams in section Pre-emphasis Techniques, Chapter 4

• Numerous parameter additions previously shown as “TBD” in MGT Package Pins,

Chapter 5

10/16/02 1.5 • Corrected pinouts in Tabl e 5- 2, FF1152 package, device column 2VP20/30, LOC

Constraints rows GT_X0_Y0 and GT_X0_Y1.

• Corrected section CRC Latency and Tab le 3-1 5 to express latency in terms of

TXUSRCLK and RXUSRCLK cycles.

• Corrected sequence of packet elements in Figure 3-16.

UG024 (v1.5) October 16, 2002 www.xilinx.com RocketIO™ Transceiver User Guide

1-800-255-7778

Page 4

RocketIO™ Transceiver User Guide www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778

Page 5

Contents

Schedule of Figures................................................................................................................... 9

Schedule of Tables ................................................................................................................... 11

Chapter 1: Introduction

RocketIO Features................................................................................................................... 13

In This User Guide ................................................................................................................. 14

Naming Conventions............................................................................................................. 14

For More Information............................................................................................................ 14

Chapter 2: RocketIO Transceiver Overview

Basic Architecture and Capabilities................................................................................ 15

Clock Synthesizer ................................................................................................................... 17

Clock and Data Recovery..................................................................................................... 18

Transmitter................................................................................................................................. 18

FPGA Transmit Interface...................................................................................................... 18

8B/10B Encoder..................................................................................................................... 18

Disparity Control................................................................................................................... 18

Transmit FIFO........................................................................................................................ 19

Serializer ................................................................................................................................. 19

Receiver........................................................................................................................................ 19

Deserializer............................................................................................................................. 19

Receiver Termination............................................................................................................20

8B/10B Decoder..................................................................................................................... 20

Loopback..................................................................................................................................... 20

Elastic and Transmitter Buffers ........................................................................................ 21

Receiver Buffer....................................................................................................................... 21

Clock Correction.................................................................................................................... 21

Channel Bonding................................................................................................................... 22

Transmitter Buffer................................................................................................................. 23

CRC................................................................................................................................................ 23

Reset/Power Down ................................................................................................................. 23

Transmit Termination ........................................................................................................ 19

Pre-emphasis Circuit and Swing Control.............................................................................. 19

Chapter 3: Digital Design Considerations

List of Available Ports........................................................................................................... 25

Primitive Attributes ............................................................................................................... 29

Modifiable Primitives ........................................................................................................... 33

Byte Mapping............................................................................................................................ 38

Clocking....................................................................................................................................... 38

Clock Signals.......................................................................................................................... 38

Clock Ratio ............................................................................................................................. 39

Digital Clock Manager (DCM) Examples .......................................................................... 39

Example 1: Two-Byte Clock................................................................................................. 40

Example 2: Four-Byte Clock ................................................................................................ 43

Example 3: One-Byte Clock ................................................................................................. 46

UG024 (v1.5) October 16, 2002 www.xilinx.com 5

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 6

R

BREFCLK................................................................................................................................ 50

Half-Rate Clocking Scheme ................................................................................................. 52

Multiplexed Clocking Scheme............................................................................................. 53

Data Path Latency ................................................................................................................. 53

Transmitter Latency ........................................................................................................... 53

Receiver Latency ................................................................................................................ 54

Clock Dependency ................................................................................................................54

Resets............................................................................................................................................ 54

RocketIO Transceiver Instantiations.............................................................................. 56

HDL Code Examples .......................................................................................................... 56

PLL Operation and Clock Recovery................................................................................ 56

Clock Correction Count........................................................................................................ 56

RX_LOSS_OF_SYNC_FSM .................................................................................................. 57

SYNC_ACQUIRED (RXLOSSOFSYNC = 00) ................................................................... 57

RESYNC (RXLOSSOFSYNC = 01).................................................................................... 57

LOSS_OF_SYNC (RXLOSSOFSYNC = 10) ....................................................................... 57

8B/10B Operation.................................................................................................................. 57

Vitesse Disparity Example ................................................................................................... 59

Transmitting Vitesse Channel Bonding Sequence.................................................................. 60

Receiving Vitesse Channel Bonding Sequence....................................................................... 60

Status Signals............................................................................................................................ 61

8B/10B Encoding...................................................................................................................... 61

8B/10B Serial Output Format.............................................................................................. 69

HDL Code Examples: Transceiver Bypassing of 8B/10B Encoding .......................................... 70

CRC Operation ......................................................................................................................... 70

CRC Generation..................................................................................................................... 70

CRC Latency........................................................................................................................... 71

CRC Limitations .................................................................................................................... 71

CRC Modes............................................................................................................................. 71

USER_MODE................................................................................................................... 71

FIBRECHANNEL ............................................................................................................. 72

ETHERNET ...................................................................................................................... 72

INFINIBAND ................................................................................................................... 72

Channel Bonding (Channel-to-Channel Alignment) ............................................. 73

HDL Code Examples: Channel Bonding ............................................................................... 74

Other Important Design Notes ......................................................................................... 75

Receive Data Path 32-bit Alignment................................................................................... 75

32-bit Alignment Design ...................................................................................................... 76

Verilog .............................................................................................................................. 76

VHDL............................................................................................................................... 79

Chapter 4: Analog Design Considerations

Serial I/O Description ........................................................................................................... 83

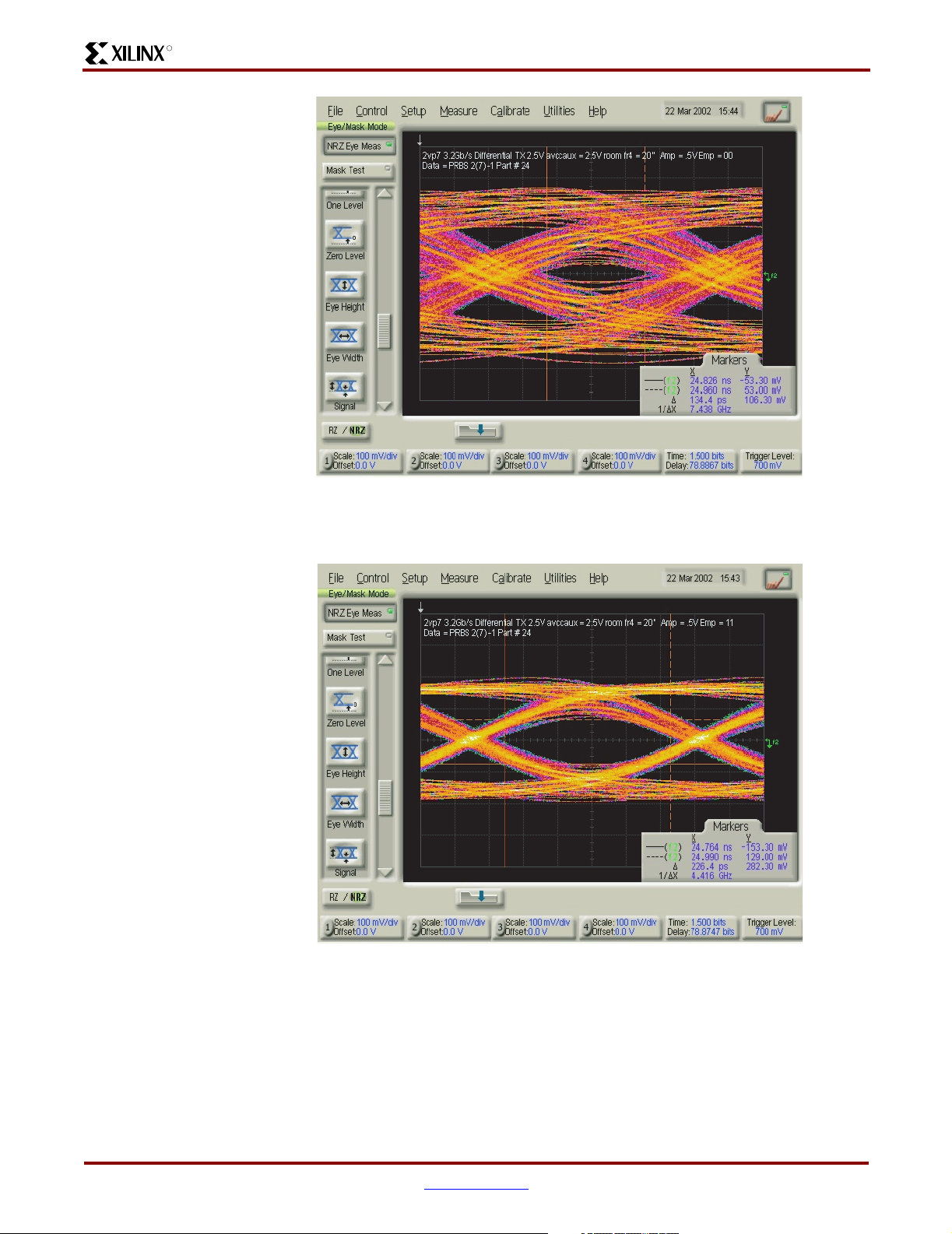

Pre-emphasis Techniques.................................................................................................... 84

Differential Receiver ............................................................................................................. 87

Jitter............................................................................................................................................... 87

Total Jitter (DJ + RJ)............................................................................................................... 87

Deterministic Jitter (DJ) ..................................................................................................... 87

Random Jitter (RJ).............................................................................................................. 87

Clock and Data Recovery..................................................................................................... 87

PCB Design Requirements ................................................................................................. 89

Power Conditioning..............................................................................................................89

Voltage Regulation ............................................................................................................. 89

Passive Filtering................................................................................................................. 90

6 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 7

High-Speed Serial Trace Design.......................................................................................... 91

Routing Serial Traces ......................................................................................................... 91

Differential Trace Design .................................................................................................... 92

AC and DC Coupling ......................................................................................................... 93

Reference Clock ..................................................................................................................... 94

Epson EG-2121CA 2.5V (LVPECL outputs) ........................................................................ 94

Pletronics LV1145B (LVDS outputs)................................................................................... 94

Other Important Design Notes ......................................................................................... 95

Powering the RocketIO Transceivers ................................................................................. 95

The POWERDOWN Port ..................................................................................................... 95

Chapter 5: Simulation and Implementation

Simulation Models ................................................................................................................. 97

SmartModels .......................................................................................................................... 97

HSPICE ................................................................................................................................... 97

Implementation Tools........................................................................................................... 97

Synthesis ................................................................................................................................. 97

Par............................................................................................................................................ 97

UCF Example ......................................................................................................................... 98

Implementing Clock Schemes ............................................................................................. 98

MGT Package Pins.................................................................................................................. 99

Diagnostic Signals ................................................................................................................ 102

LOOPBACK ......................................................................................................................... 102

R

Appendix A: RocketIO Transceiver Timing Model

Timing Parameters................................................................................................................ 104

Setup/Hold Times of Inputs Relative to Clock .............................................................. 105

Clock to Output Delays ...................................................................................................... 105

Clock Pulse Width...............................................................................................................105

Timing Parameter Tables and Diagram...................................................................... 106

Appendix B: RocketIO Transceiver Cell Models

Summary ................................................................................................................................... 109

Verilog Module Declarations .......................................................................................... 109

GT_AURORA_1................................................................................................................... 109

GT_AURORA_2................................................................................................................... 110

GT_AURORA_4................................................................................................................... 111

GT_CUSTOM.......................................................................................................................112

GT_ETHERNET_1............................................................................................................... 113

GT_ETHERNET_2............................................................................................................... 114

GT_ETHERNET_4............................................................................................................... 114

GT_FIBRE_CHAN_1........................................................................................................... 115

GT_FIBRE_CHAN_2........................................................................................................... 116

GT_FIBRE_CHAN_4........................................................................................................... 117

GT_INFINIBAND_1 ........................................................................................................... 118

GT_INFINIBAND_2 ........................................................................................................... 119

GT_INFINIBAND_4 ........................................................................................................... 120

GT_XAUI_1 .......................................................................................................................... 121

GT_XAUI_2 .......................................................................................................................... 122

GT_XAUI_4 .......................................................................................................................... 122

UG024 (v1.5) October 16, 2002 www.xilinx.com 7

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 8

R

8 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 9

Figures

Chapter 1: Introduction

Chapter 2: RocketIO Transceiver Overview

Figure 2-1: RocketIO Transceiver Block Diagram ................................................................. 16

Figure 2-2: Clock Correction in Receiver ................................................................................. 21

Figure 2-3: Channel Bonding (Alignment) .............................................................................. 22

Chapter 3: Digital Design Considerations

Figure 3-1: Two-Byte Clock ........................................................................................................ 40

Figure 3-2: Four-Byte Clock........................................................................................................ 43

Figure 3-3: One-Byte Clock......................................................................................................... 46

Figure 3-4: REFCLK/BREFCLK Selection Logic ..................................................................... 50

Figure 3-5: One-Byte Data Path Clocks, SERDES_10B = TRUE.......................................... 52

Figure 3-6: Two-Byte Data Path Clocks, SERDES_10B = TRUE ......................................... 52

Figure 3-7: Four-Byte Data Path Clocks, SERDES_10B = TRUE ......................................... 52

Figure 3-8: Multiplexed REFCLK .............................................................................................. 53

Figure 3-9: 8B/10B Data Flow ..................................................................................................... 58

Figure 3-10: 10-Bit TX Data Map with 8B/10B Bypassed ...................................................... 59

Figure 3-11: 10-Bit RX Data Map with 8B/10B Bypassed...................................................... 59

Figure 3-12: 8B/10B Parallel to Serial Conversion.................................................................. 69

Figure 3-13: 4-Byte Serial Structure........................................................................................... 70

Figure 3-14: CRC Packet Format ................................................................................................ 71

Figure 3-15: USER_MODE / FIBRE_CHANNEL Mode ........................................................ 72

Figure 3-16: Ethernet Mode ........................................................................................................ 72

Figure 3-17: Infiniband Mode .................................................................................................... 73

Figure 3-18: Local Route Header................................................................................................ 73

Figure 3-19: RXDATA Aligned Correctly ................................................................................ 75

Figure 3-20: Realignment of RXDATA..................................................................................... 76

Chapter 4: Analog Design Considerations

Figure 4-1: Differential Amplifier............................................................................................. 83

Figure 4-2: Alternating K28.5+ with No Pre-Emphasis......................................................... 85

Figure 4-3: K28.5+ with Pre-Emphasis...................................................................................... 85

Figure 4-5: Eye Diagram, 33% Pre-Emphasis .......................................................................... 86

Figure 4-4: Eye Diagram, 10% Pre-Emphasis .......................................................................... 86

Figure 4-6: Power Supply Circuit Using LT1963 Regulator ................................................. 89

Figure 4-7: Power Filtering Network for One Transceiver................................................... 90

Figure 4-8: Example Power Filtering PCB Layout for Four MGTs, Top Layer................. 91

UG024 (v1.5) October 16, 2002 www.xilinx.com 9

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 10

R

Figure 4-9: Example Power Filtering PCB Layout for Four MGTs, Bottom Layer........... 91

Figure 4-10: Single-Ended Trace Geometry............................................................................. 92

Figure 4-11: Microstrip Edge-Coupled Differential Pair...................................................... 93

Figure 4-12: Stripline Edge-Coupled Differential Pair......................................................... 93

Figure 4-13: AC-Coupled Serial Link ....................................................................................... 93

Figure 4-14: DC-Coupled Serial Link ....................................................................................... 94

Figure 4-15: LVPECL Reference Clock Oscillator Interface................................................. 94

Figure 4-16: LVDS Reference Clock Oscillator Interface ..................................................... 94

Chapter 5: Simulation and Implementation

Figure 5-1: 2VP2 Implementation.............................................................................................. 98

Figure 5-2: 2VP50 Implementation............................................................................................ 98

Appendix A: RocketIO Transceiver Timing Model

Figure A-1: RocketIO Transceiver Block Diagram .............................................................. 104

Figure A-2: RocketIO Transceiver Timing Relative to Clock Edge.................................. 108

Appendix B: RocketIO Transceiver Cell Models

10 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 11

Ta ble s

Chapter 1: Introduction

Chapter 2: RocketIO Transceiver Overview

Chapter 3: Digital Design Considerations

Table 2-1: RocketIO Cores........................................................................................................... 15

Table 2-2: Communications Standards Supported by RocketIO Transceiver.................. 15

Table 2-3: Serial Baud Rates and the SERDES_10B Attribute ............................................. 16

Table 2-4: Supported RocketIO Transceiver Primitives........................................................ 17

Table 2-5: Running Disparity Control...................................................................................... 18

Table 2-6: Loopback Options...................................................................................................... 20

Table 2-7: Reset and Power Control Descriptions.................................................................. 24

Table 2-8: Power Control Descriptions..................................................................................... 24

Table 3-1: GT_CUSTOM

GT_INFINIBAND, and GT_XAUI Primitive Ports .......................................................... 25

Table 3-2: RocketIO Transceiver Attributes ............................................................................ 29

Table 3-3: Default Attribute Values: GT_AURORA, GT_CUSTOM, GT_ETHERNET . 33

Table 3-4: Default Attribute Values: GT_FIBRE_CHAN, GT_INFINIBAND,

and GT_XAUI........................................................................................................................... 35

Table 3-5: Control/Status Bus Association to Data Bus Byte Paths..................................... 38

Table 3-6: Clock Ports................................................................................................................... 38

Table 3-7: Data Width Clock Ratios .......................................................................................... 39

Table 3-8: DCM Outputs for Different DATA_WIDTHs .................................................... 39

Table 3-9: BREFCLK Pin Numbers............................................................................................ 51

Table 3-10: Clock Correction Sequence / Data Correlation for 16-Bit Data Port .............. 56

Table 3-11: RXCLKCORCNT Definition ................................................................................. 56

Table 3-12: 8B/10B Bypassed Signal Significance .................................................................. 58

Table 3-13: Valid Data Characters ............................................................................................. 61

Table 3-14: Valid Control “K” Characters................................................................................ 69

Table 3-15: Effects of CRC on Transceiver Latency ............................................................... 71

Table 3-16: Global and Local Headers ...................................................................................... 73

Table 3-17: Bonded Channel Connections............................................................................... 74

Table 3-18: Master/Slave Channel Bonding Attribute Settings........................................... 74

Table 3-19: 32-bit RXDATA, Aligned versus Misaligned ..................................................... 75

(1)

, GT_AURORA, GT_FIBRE_CHAN

(2)

, GT_ETHERNET

(2)

,

Chapter 4: Analog Design Considerations

Table 4-1: Differential Transmitter Parameters...................................................................... 84

Table 4-2: Pre-emphasis Values ................................................................................................. 84

Table 4-3: Differential Receiver Parameters............................................................................ 87

UG024 (v1.5) October 16, 2002 www.xilinx.com 11

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 12

R

Table 4-4: CDR Parameters ......................................................................................................... 88

Table 4-5: Transceiver Power Supplies .................................................................................... 89

Chapter 5: Simulation and Implementation

Table 5-1: LOC Grid & Package Pins Correlation for FG256, FG456, and FF672 ............. 99

Table 5-2: LOC Grid & Package Pins Correlation for FF896 and FF1152 ........................... 99

Table 5-3: LOC Grid & Package Pins Correlation for FF1517 and FF1704....................... 100

Table 5-4: LOOPBACK Modes................................................................................................. 102

Appendix A: RocketIO Transceiver Timing Model

Table A-1: RocketIO Clock Descriptions............................................................................... 103

Table A-2: Parameters Relative to the RX User Clock (RXUSRCLK) ............................... 106

Table A-3: Parameters Relative to the RX User Clock2 (RXUSRCLK2) ........................... 106

Table A-4: Parameters Relative to the TX User Clock2 (TXUSRCLK2)............................ 107

Table A-5: Miscellaneous Clock Parameters ......................................................................... 107

Appendix B: RocketIO Transceiver Cell Models

12 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 13

R

Introduction

IMPORTANT NOTES

This document assumes use of ISE v5.1.x.

• If running ISE v4.x.x, the following modifications must be made:

1. Remove the ports BREFCLK and BREFCLK2.

2. Remove the REF_CLK_V_SEL attribute.

• If running ISE v4.1.x, the following additional modifications must be made:

1. Remove the port ENMCOMMAALIGN and replace its function by adding

2. Remove the port ENPCOMMAALIGN and replace its function by adding

3. Where a High is indicated for a removed port, set the corresponding

4. Change the attribute name TERMINATION_IMP to RX_TERM_IMP.

Chapter 1

the attribute MCOMMA_ALIGN.

the attribute PCOMMA_ALIGN.

attribute to TRUE; where a Low is indicated, set the corresponding

attribute to FALSE.

RocketIO Features

The RocketIO™ transceiver’s flexible, programmable features allow a multi-gigabit serial

transceiver to be easily integrated into any Virtex-II Pro design:

• Variable speed full-duplex transceiver, allowing 622 Mb/s to 3.125 Gb/s baud

transfer rates

• Monolithic clock synthesis and clock recovery system, eliminating the need for

external components

• Automatic lock-to-reference function

• Serial output differential swing can be programmed at five levels from 800 mV to

1600 mV (peak-peak), allowing compatibility with other serial system voltage levels.

• Four levels of programmable pre-emphasis

• AC and DC coupling

• Programmable on-chip termination of 50Ω or 75Ω (eliminating the need for external

termination resistors)

• Serial and parallel TX to RX internal loopback modes for testing operability

• Programmable comma detection to allow for any protocol and detection of any 10-bit

character.

UG024 (v1.5) October 16, 2002 www.xilinx.com 13

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 14

R

In This User Guide

The RocketIO Transceiver User Guide contains these sections:

• Chapter 1, Introduction — This chapter.

• Chapter 2, RocketIO Transceiver Overview — An overview of the transceiver’s

capabilities and how it works.

• Chapter 3, Digital Design Considerations — Ports and attributes for the six provided

communications protocol primitives; VHDL/Verilog code examples for clocking and

reset schemes; transceiver instantiation; 8B/10B encoding; CRC; channel bonding.

• Chapter 4, Analog Design Considerations — RocketIO serial overview; pre-

emphasis; jitter; clock/data recovery; PCB design requirements.

• Chapter 5, Simulation and Implementation — Simulation models; implementation

tools; debugging and diagnostics.

• Appendix B, RocketIO Transceiver Cell Models — Verilog module declarations

associated with each of the sixteen RocketIO communication standard

implementations.

Naming Conventions

Input and output ports of the RocketIO transceiver primitives are denoted in upper-case

letters. Attributes of the RocketIO transceiver are denoted in upper-case letters with

underscores. Trailing numbers in primitive names denote the byte width of the data path.

These values are preset and not modifiable. When assumed to be the same frequency,

RXUSRCLK and TXUSRCLK are referred to as USRCLK and can be used interchangeably.

This also holds true for RXUSRCLK2, TXUSRCLK2, and USRCLK2.

Chapter 1: Introduction

Comma Definition

A comma is a “K” character used by the transceiver to align the serial data on a

byte/half-word boundary (depending on the protocol used), so that the serial data is

correctly decoded into parallel data.

For More Information

For a complete menu of online information resources available on the Xilinx website, visit

http://www.xilinx.com/virtex2pro/

For a comprehensive listing of available tutorials and resources on network technologies

and communications protocols, visit http://www.iol.unh.edu/training/

.

.

14 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 15

R

RocketIO Transceiver Overview

Basic Architecture and Capabilities

The RocketIO transceiver is based on Mindspeed’s SkyRail™ technology. Figure 2-1,

page 16, depicts an overall block diagram of the transceiver. Up to 24 transceiver modules

are available on a single Virtex-II Pro FPGA, depending on the part being used. Ta bl e 2 - 1

shows the RocketIO cores available by device.

Table 2-1: RocketIO Cores

Device RocketIO Cores Device RocketIO Cores

XC2VP2 4 XC2VP40 0 or 12

Chapter 2

XC2VP4 4 XC2VP50 0 or 16

XC2VP7 8 XC2VP70 20

XC2VP20 8 XC2VP100 0 or 20

XC2VP30 8 XC2VP125 0, 20, or 24

The transceiver module is designed to operate at any serial bit rate in the range of

622 Mb/s to 3.125 Gb/s per channel, including the specific bit rates used by the

communications standards listed in Ta bl e 2- 2. The serial bit rate need not be configured in

the transceiver, as the operating frequency is implied by the received data, the reference

clock applied, and the SERDES_10B attribute (Tab le 2-3 , pa g e 1 6).

Table 2-2: Communications Standards Supported by RocketIO Transceiver

Mode

Fibre Channel 1

Gbit Ethernet 1 1.25

XAUI (10-Gbit Ethernet) 4 3.125

Infiniband 1, 4, 12 2.5

Channels

(Lanes)

(1)

I/O Bit Rate

(Gb/s)

1.06

2.12

Aurora (Xilinx protocol) 1, 2, 3, 4, ... 0.622 – 3.125

Custom Mode 1, 2, 3, 4, ... 0.622 – 3.125

Notes:

1. One channel is considered to be one transceiver.

UG024 (v1.5) October 16, 2002 www.xilinx.com 15

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 16

R

PACKAGE

PINS

Chapter 2: RocketIO Transceiver Overview

Table 2-3: Serial Baud Rates and the SERDES_10B Attribute

SERDES_10B Serial Baud Rate

False 800 Mb/s – 3.125 Gb/s

True 622 Mb/s – 1.0 Gb/s

MULTI-GIGABIT TRANSCEIVER CORE

FPGA FABRIC

AVCCAUXRX

VTRX

RXP

RXN

TXP

TXN

GNDA

AVCCAUXTX

VTTX

2.5V RX

Termination Supply RX

Deserializer

Manager

Serial Loopback Path

Serializer

TX/RX GND

2.5V TX

Termination Supply TX

Clock

Power Down

Comma

Detect

Realign

Parallel Loopback Path

Output

Polarity

8B/10B

Decoder

TX

FIFO

Check

Elastic

Buffer

Channel Bonding

and

Clock Correction

8B/10B

Encoder

CRC

RX

CRC

POWERDOWN

RXRECCLK

RXPOLARITY

RXREALIGN

RXCOMMADET

ENPCOMMAALIGN

ENMCOMMAALIGN

RXCHECKINGCRC

RXCRCERR

RXDATA[15:0]

RXDATA[31:16]

RXNOTINTABLE[3:0]

RXDISPERR[3:0]

RXCHARISK[3:0]

RXCHARISCOMMA[3:0]

RXRUNDISP[3:0]

RXBUFSTATUS[1:0]

ENCHANSYNC

CHBONDDONE

CHBONDI[3:0]

CHBONDO[3:0]

RXLOSSOFSYNC

RXCLKCORCNT

TXBUFERR

TXFORCECRCERR

TXDATA[15:0]

TXDATA[31:16]

TXBYPASS8B10B[3:0]

TXCHARISK[3:0]

TXCHARDISPMODE[3:0]

TXCHARDISPVAL[3:0]

TXKERR[3:0]

TXRUNDISP[3:0]

TXPOLARITY

TXINHIBIT

LOOPBACK[1:0]

TXRESET

RXRESET

REFCLK

REFCLK2

REFCLKSEL

BREFCLK

BREFCLK2

RXUSRCLK

RXUSRCLK2

TXUSRCLK

TXUSRCLK2

DS083-2_04_090402

Figure 2-1: RocketIO Transceiver Block Diagram

16 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 17

Clock Synthesizer

R

Ta bl e 2 - 4 lists the 16 gigabit transceiver primitives provided. These primitives carry

attributes set to default values for the communications protocols listed in Ta bl e 2 -2 . Data

widths of one, two, and four bytes are selectable for each protocol.

Table 2-4: Supported RocketIO Transceiver Primitives

Primitives Description Primitive Description

GT_CUSTOM Fully customizable

by user

GT_FIBRE_CHAN_1 Fibre Channel,

1-byte data path

GT_FIBRE_CHAN_2 Fibre Channel,

2-byte data path

GT_FIBRE_CHAN_4 Fibre Channel,

4-byte data path

GT_ETHERNET_1 Gigabit Ethernet,

1-byte data path

GT_ETHERNET_2 Gigabit Ethernet,

2-byte data path

GT_ETHERNET_4 Gigabit Ethernet,

4-byte data path

GT_XAUI_1 10-Gb Ethernet,

1-byte data path

GT_XAUI_2 10-Gb Ethernet,

2-byte data path

GT_XAUI_4 10-Gb Ethernet,

4-byte data path

GT_INFINIBAND_1 Infiniband, 1-byte

data path

GT_INFINIBAND_2 Infiniband, 2-byte

data path

GT_INFINIBAND_4 Infiniband, 4-byte

data path

GT_AURORA_1 Xilinx protocol,

1-byte data path

GT_AURORA_2 Xilinx protocol,

2-byte data path

GT_AURORA_4 Xilinx protocol,

4-byte data path

There are two ways to modify the RocketIO transceiver:

• Static properties can be set through attributes in the HDL code. Use of attributes are

covered in detail in Primitive Attributes, page 29.

• Dynamic changes can be made by the ports of the primitives

The RocketIO transceiver consists of the Physical Media Attachment (PMA) and Physical

Coding Sublayer (PCS). The PMA contains the serializer/deserializer (SERDES), TX and

RX buffers, clock generator, and clock recovery circuitry. The PCS contains the 8B/10B

encoder/decoder and the elastic buffer supporting channel bonding and clock correction.

The PCS also handles Cyclic Redundancy Check (CRC). Refer again to Figure 2-1, showing

the RocketIO transceiver top-level block diagram and FPGA interface signals.

Clock Synthesizer

Synchronous serial data reception is facilitated by a clock/data recovery circuit. This

circuit uses a fully monolithic Phase-Locked Loop (PLL), which does not require any

external components. The clock/data recovery circuit extracts both phase and frequency

from the incoming data stream. The recovered clock is presented on output RXRECCLK at

1/20 of the serial received data rate.

The gigabit transceiver multiplies the reference frequency provided on the reference clock

input (REFCLK) by 20.

No fixed phase relationship is assumed between REFCLK, RXRECCLK, and/or any other

clock that is not tied to either of these clocks. When the 4-byte or 1-byte receiver data path

is used, RXUSRCLK and RXUSRCLK2 have different frequencies (1:2), and each edge of

the slower clock is aligned to a falling edge of the faster clock. The same relationships

apply to TXUSRCLK and TXUSRCLK2. See the section entitled Clocking, page 38, for

details.

UG024 (v1.5) October 16, 2002 www.xilinx.com 17

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 18

R

Clock and Data Recovery

The clock/data recovery (CDR) circuits lock to the reference clock automatically if the data

is not present. For proper operation, frequency variations of REFCLK, TXUSRCLK,

RXUSRCLK, and the incoming stream (RXRECCLK) must not exceed

It is critical to keep power supply noise low in order to minimize common and differential

noise modes into the clock/data recovery circuitry. See PCB Design Requirements,

page 89, for more details.

Transmitter

FPGA Transmit Interface

The FPGA can send either one, two, or four characters of data to the transmitter. Each

character can be either 8 bits or 10 bits wide. If 8-bit data is applied, the additional inputs

become control signals for the 8B/10B encoder. When the 8B/10B encoder is bypassed, the

10-bit character order is:

TXCHARDISPMODE[0]

TXCHARDISPVAL[0]

TXDATA[7:0]

Refer to Figure 3-10, page 59, for a graphical representation of the transmitted 10-bit

character.

Chapter 2: RocketIO Transceiver Overview

±100 ppm.

8B/10B Encoder

A bypassable 8B/10B encoder is included. The encoder uses the same 256 data characters

and 12 control characters that are used for Gigabit Ethernet, XAUI, Fibre Channel, and

InfiniBand.

The encoder accepts 8 bits of data along with a K-character signal for a total of 9 bits per

character applied. If the K-character signal is High, the data is encoded into one of the 12

possible K-characters available in the 8B/10B code. If the K-character input is Low, the 8

bits are encoded as standard data. If the K-character input is High, and a user applies other

than one of the 12 possible combinations, TXKERR indicates the error.

Disparity Control

The 8B/10B encoder is initialized with a negative running disparity.

TXRUNDISP signals the transmitter’s current running disparity.

Bits TXCHARDISPMODE and TXCHARDISPVAL control the generation of running

disparity before each byte, as shown in Ta bl e 2 -5 .

Table 2-5: Running Disparity Control

{txchardispmode,

txchardispval}

Function

00 Maintain running disparity normally

01

Invert normally generated running disparity before

encoding this byte

10 Set negative running disparity before encoding this byte

11 Set positive running disparity before encoding this byte

For example, the transceiver can generate the sequence

K28.5+ K28.5+ K28.5– K28.5–

or

K28.5– K28.5– K28.5+ K28.5+

18 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 19

Receiver

R

by specifying inverted running disparity for the second and fourth bytes.

Transmit FIFO

Proper operation of the circuit is only possible if the FPGA clock (TXUSRCLK) is

frequency-locked to the reference clock (REFCLK). Phase variations up to one clock cycle

are allowable. The FIFO has a depth of four. Overflow or underflow conditions are

detected and signaled at the interface.

Serializer

The multi-gigabit transceiver multiplies the reference frequency provided on the reference

clock input (REFCLK) by 20. Data is converted from parallel to serial format and

transmitted on the TXP and TXN differential outputs.

The electrical polarity of TXP and TXN can be interchanged through the TXPOLARITY

port. This option can either be programmed or controlled by an input at the FPGA core TX

interface. This facilitates recovery from situations where printed circuit board traces have

been reversed.

Transmit Termination

On-chip termination is provided at the transmitter, eliminating the need for external

termination. Programmable options exist for 50Ω (default) and 75Ω termination.

Receiver

Deserializer

Pre-emphasis Circuit and Swing Control

Four selectable levels of pre-emphasis, including default pre-emphasis, are available.

Optimizing this setting allows the transceiver to drive up to 20 inches of FR4 at the

maximum baud rate.

The programmable output swing control can adjust the differential output level between

800 mV and 1600 mV (differential peak-to-peak) in four increments of 200 mV.

The RocketIO transceiver core accepts serial differential data on its RXP and RXN inputs.

The clock/data recovery circuit extracts clock phase and frequency from the incoming data

stream and re-times incoming data to this clock. The recovered clock is presented on

output RXRECCLK at 1/20 of the received serial data rate.

The receiver is capable of handling either transition-rich 8B/10B streams or scrambled

streams, and can withstand a string of up to 75 non-transitioning bits without an error.

Word alignment is dependent on the state of comma detect bits. If comma detect is

enabled, the transceiver recognizes up to two 10-bit preprogrammed characters. Upon

detection of the character or characters, the comma detect output is driven High and the

data is synchronously aligned. If a comma is detected and the data is aligned, no further

alignment alteration takes place. If a comma is received and realignment is necessary, the

data is realigned and an indication is given at the RX FPGA interface. The realignment

indicator is a distinct output. The transceiver continuously monitors the data for the

presence of the 10-bit character(s). Upon each occurrence of the 10-bit character, the data is

checked for word alignment. If comma detect is disabled, the data is not aligned to any

particular pattern. The programmable option allows a user to align data on comma+,

comma–, both, or a unique user-defined and programmed sequence.

The electrical polarity of RXP and RXN can be interchanged through the RXPOLARITY

port. This can be useful in the event that printed circuit board traces have been reversed.

UG024 (v1.5) October 16, 2002 www.xilinx.com 19

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 20

R

Receiver Termination

On-chip termination is provided at the receiver, eliminating the need for external

termination. The receiver includes programmable on-chip termination circuitry for 50Ω

(default) or 75Ω impedance.

8B/10B Decoder

An optional 8B/10B decoder is included. A programmable option allows the decoder to be

bypassed. (See HDL Code Examples: Transceiver Bypassing of 8B/10B Encoding,

page 70.) When the 8B/10B decoder is bypassed, the 10-bit character order is:

RXCHARISK[0]

RXRUNDISP[0]

RXDATA[7:0]

Refer to Figure 3-11, page 59, for a graphical representation of the received 10-bit character.

The decoder uses the same table that is used for Gigabit Ethernet, Fibre Channel and

InfiniBand. In addition to decoding all data and K-characters, the decoder has several extra

features. The decoder separately detects both “disparity errors” and “out-of-band” errors.

A disparity error occurs when a 10-bit character is received that exists within the 8B/10B

table, but has an incorrect disparity. An out-of-band error occurs when a 10-bit character is

received that does not exist within the 8B/10B table. It is possible to obtain an out-of-band

error without having a disparity error. The proper disparity is always computed for both

legal and illegal characters. The current running disparity is available at the RXRUNDISP

signal.

The 8B/10B decoder performs a unique operation if out-of-band data is detected. If out-ofband data is detected, the decoder signals the error and passes the illegal 10-bits through

and places them on the outputs. This can be used for debugging purposes if desired.

The decoder also signals reception of one of the 12 valid K-characters. In addition, a

programmable comma detect is included. The comma detect signal registers a comma on the

receipt of any comma+, comma–, or both. Since the comma is defined as a 7-bit character, this

includes several out-of-band characters. Another option allows the decoder to detect only

the three defined commas (K28.1, K28.5, and K28.7) as comma+, comma–, or both. In total,

there are six possible options, three for valid commas and three for "any comma".

Note that all bytes (1, 2, or 4) at the RX FPGA interface each have their own individual

8B/10B indicators (K-character, disparity error, out-of-band error, current running

disparity, and comma detect).

Chapter 2: RocketIO Transceiver Overview

Loopback

To facilitate testing without having the need to either apply patterns or measure data at

GHz rates, two programmable loopback features are available.

One option, serial loopback, places the gigabit transceiver into a state where transmit data

is directly fed back to the receiver. An important point to note is that the feedback path is

at the output pads of the transmitter. This tests the entirety of the transmitter and receiver.

The second loopback path is a parallel path that checks the digital circuitry. When the

parallel option is enabled, the serial loopback path is disabled. However, the transmitter

outputs remain active and data is transmitted over a link. If TXINHIBIT is asserted, TXN is

forced to 1 and TXP is forced to 0 until TXINHIBIT is de-asserted.

The two loopback options are shown in Ta bl e 2- 6.

Table 2-6: Loopback Options

LOOPBACK[1:0] Description

LOOPBACK[1] External serial loopback

LOOPBACK[0] Internal parallel loopback

20 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 21

Elastic and Transmitter Buffers

Elastic and Transmitter Buffers

Both the transmitter and the receiver include buffers (FIFOs) in the data path. This section

gives the reasons for including the buffers and outlines their operation.

Receiver Buffer

The receiver buffer is required for two reasons:

• To accommodate the slight difference in frequency between the recovered clock

RXRECCLK and the internal FPGA core clock RXUSRCLK (clock correction)

• To allow realignment of the input stream to ensure proper alignment of data being

read through multiple transceivers (channel bonding)

The receiver uses an elastic buffer, where "elastic" refers to the ability to modify the read

pointer for clock correction and channel bonding.

Clock Correction

Clock RXRECCLK (the recovered clock) reflects the data rate of the incoming data. Clock

RXUSRCLK defines the rate at which the FPGA core consumes the data. Ideally, these rates

are identical. However, since the clocks typically have different sources, one of the clocks is

faster than the other. The receiver buffer accommodates this difference between the clock

rates. See Figure 2-2.

Nominally, the buffer is always half full. This is shown in the top buffer, Figure 2-2, where

the shaded area represents buffered data not yet read. Received data is inserted via the

write pointer under control of RXRECCLK. The FPGA core reads data via the read pointer

under control of RXUSRCLK. The half full/half empty condition of the buffer gives a

cushion for the differing clock rates. This operation continues indefinitely, regardless of

whether or not "meaningful" data is being received. When there is no meaningful data to

be received, the incoming data consists of IDLE characters or other padding.

R

Read

RXUSRCLK

Read

Removable sequence

"Nominal" condition: buffer half-full

Read

Buffer less than half -full (emptying)

Repeatable sequence

Buffer more than half-full (filling up)

Write

Write

RXRECCLK

Write

DS083-2_15_100901

Figure 2-2: Clock Correction in Receiver

If RXUSRCLK is faster than RXRECCLK, the buffer becomes more empty over time. The

clock correction logic corrects for this by decrementing the read pointer to reread a

repeatable byte sequence. This is shown in the middle buffer, Figure 2-2, where the solid

read pointer decrements to the value represented by the dashed pointer. By decrementing

the read pointer instead of incrementing it in the usual fashion, the buffer is partially

refilled. The transceiver inserts a single repeatable byte sequence when necessary to refill a

buffer. If the byte sequence length is greater than one, and if attribute

CLK_COR_REPEAT_WAIT is 0, then the transceiver can repeat the same sequence

multiple times until the buffer is refilled to the half-full condition.

UG024 (v1.5) October 16, 2002 www.xilinx.com 21

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 22

R

Similarly, if RXUSRCLK is slower than RXRECCLK, the buffer fills up over time. The clock

correction logic corrects for this by incrementing the read pointer to skip over a removable

byte sequence that need not appear in the final FPGA core byte stream. This is shown in the

bottom buffer, Figure 2-2, where the solid read pointer increments to the value represented

by the dashed pointer. This accelerates the emptying of the buffer, preventing its overflow.

The transceiver design skips a single byte sequence, when necessary, to partially empty a

buffer. If attribute CLK_COR_REPEAT_WAIT is 0, the transceiver can also skip two

consecutive removable byte sequences in one step, to further empty the buffer, when

necessary.

These operations require the clock correction logic to recognize a byte sequence that can be

freely repeated or omitted in the incoming data stream. This sequence is generally an IDLE

sequence, or other sequence comprised of special values that occur in the gaps separating

packets of meaningful data. These gaps are required to occur sufficiently often to facilitate

the timely execution of clock correction.

Channel Bonding

Some gigabit I/O standards such as Infiniband specify the use of multiple transceivers in

parallel for even higher data rates. Words of data are split into bytes, with each byte sent

over a separate channel (transceiver). See Figure 2-3.

Chapter 2: RocketIO Transceiver Overview

In Transmitters:

Full word SSSS sent over four channels, one byte per channel

PQRS T

PQRS T

PQRS T

PQRS T

Read

RXUSRCLK

PQRS T

PQRS T

PQRS T

PQRS T

Before channel bonding After channel bonding

Channel (lane) 0

Channel (lane) 1

Channel (lane) 2

Channel (lane) 3

In Receivers:

Read

RXUSRCLK

PQRS T

PQRS T

PQRS T

PQRS T

DS083-2_16_010202

Figure 2-3: Channel Bonding (Alignment)

The top half of the figure shows the transmission of words split across four transceivers

(channels or lanes). PPPP, QQQQ, RRRR, SSSS, and TTTT represent words sent over the

four channels.

The bottom-left portion of the figure shows the initial situation in the FPGA’s receivers at

the other end of the four channels. Due to variations in transmission delay—especially if

the channels are routed through repeaters—the FPGA core might not correctly assemble

the bytes into complete words. The bottom-left illustration shows the incorrect assembly of

data words PQPP, QRQQ, RSRR, etc.

To support correction of this misalignment, the data stream includes special byte

sequences that define corresponding points in the several channels. In the bottom half of

Figure 2-3, the shaded "P" bytes represent these special characters. Each receiver

22 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 23

CRC

CRC

R

recognizes the "P" channel bonding character, and remembers its location in the buffer. At

some point, one transceiver designated as the master instructs all the transceivers to align

to the channel bonding character "P" (or to some location relative to the channel bonding

character). After this operation, the words transmitted to the FPGA core are properly

aligned: RRRR, SSSS, TTTT, etc., as shown in the bottom-right portion of Figure 2-3. To

ensure that the channels remain properly aligned following the channel bonding

operation, the master transceiver must also control the clock correction operations

described in the previous section for all channel-bonded transceivers.

Transmitter Buffer

The transmitter buffer’s write pointer (TXUSRCLK) is frequency-locked to its read pointer

(REFCLK). Therefore, clock correction and channel bonding are not required. The purpose

of the transmitter's buffer is to accommodate a phase difference between TXUSRCLK and

REFCLK. A simple FIFO suffices for this purpose. A FIFO depth of four permits reliable

operation with simple detection of overflow or underflow, which might occur if the clocks

are not frequency-locked.

The RocketIO transceiver CRC logic supports the 32-bit invariant CRC calculation used by

Infiniband, FibreChannel, and Gigabit Ethernet.

On the transmitter side, the CRC logic recognizes where the CRC bytes should be inserted

and replaces four placeholder bytes at the tail of a data packet with the computed CRC. For

Gigabit Ethernet and FibreChannel, transmitter CRC can adjust certain trailing bytes to

generate the required running disparity at the end of the packet.

On the receiver side, the CRC logic verifies the received CRC value, supporting the same

standards as above.

The CRC logic also supports a user mode, with a simple data packet structure beginning

and ending with user-defined SOP and EOP characters.

There are limitations to the CRC support provided by the RocketIO transceiver core:

• It is for single-channel use only. Computation and byte-striping of CRC across

multiple bonded channels is not supported. For that usage, the CRC logic can be

implemented in the FPGA fabric.

• The RocketIO transceiver does not compute the 16-bit variant CRC used for

Infiniband. Therefore, RocketIO CRC does not fulfill the Infiniband CRC requirement.

Infiniband CRC can be computed in the FPGA fabric.

Reset/Power Down

The receiver and transmitter have their own synchronous reset inputs. The transmitter

reset recenters the transmission FIFO and resets all transmitter registers and the 8B/10B

encoder. The receiver reset recenters the receiver elastic buffer and resets all receiver

registers and the 8B/10B decoder. Neither reset signal has any effect on the PLLs.

UG024 (v1.5) October 16, 2002 www.xilinx.com 23

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 24

R

Chapter 2: RocketIO Transceiver Overview

Additional reset and power control descriptions are given in Ta bl e 2 -7 and Ta bl e 2 -8 .

Table 2-7: Reset and Power Control Descriptions

Ports Description

RXRESET Synchronous receive system reset recenters the receiver elastic

buffer, and resets the 8B/10B decoder, comma detect, channel

bonding, clock correction logic, and other receiver registers. The

PLL is unaffected.

TXRESET Synchronous transmit system reset recenters the transmission

FIFO, and resets the 8B/10B encoder and other transmission

registers. The PLL is unaffected.

POWERDOWN Shuts down the transceiver (both RX and TX sides).

In POWERDOWN mode, transmit output pins TXP/TXN are

undriven, but biased by the state of transmit termination

supply VTTX. If VTTX is unpowered, TXP/TXN float to a highimpedance state. Receive input pins RXP/RXN respond

similarly to the state of receive termination supply VTRX.

Table 2-8: Power Control Descriptions

POWERDOWN Transceiver Status

0 Transceiver in operation

1 Transceiver temporarily powered down

24 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 25

R

Digital Design Considerations

List of Available Ports

The RocketIO transceiver primitives contain 50 ports, with the exception of the 46-port

GT_ETHERNET and GT_FIBRE_CHAN primitives. The differential serial data ports

(RXN, RXP, TXN, and TXP) are connected directly to external pads; the remaining 46 ports

are all accessible from the FPGA logic (42 ports for GT_ETHERNET and

GT_FIBRE_CHAN).

Ta bl e 3 - 1 contains the port descriptions of all primitives.

Chapter 3

Table 3-1: GT_CUSTOM

GT_INFINIBAND, and GT_XAUI Primitive Ports

Port I/O

BREFCLK(5)

BREFCLK2(5)

CHBONDDONE

CHBONDI

CHBONDO

CONFIGENABLE

CONFIGIN

CONFIGOUT

ENCHANSYNC

(2)

(2)

(2)

(2)

(1)

, GT_AURORA, GT_FIBRE_CHAN

Port

Size

I 1 This high quality reference clock uses dedicated routing to improve jitter

for serial speeds 2.5 Gb/s or greater.

I 1 Alternative to BREFCLK.

O 1 Indicates a receiver has successfully completed channel bonding when

asserted High.

I 4 The channel bonding control that is used only by "slaves" which is driven

by a transceiver's CHBONDO port.

O 4 Channel bonding control that passes channel bonding and clock correction

control to other transceivers.

I 1 Reconfiguration enable input (unused)

I 1 Data input for reconfiguring transceiver (unused)

O 1 Data output for configuration readback (unused)

I 1 Comes from the core to the transceiver and enables the transceiver to

perform channel bonding

(2)

, GT_ETHERNET

Definition

(2)

,

ENMCOMMAALIGN

ENPCOMMAALIGN

LOOPBACK

UG024 (v1.5) October 16, 2002 www.xilinx.com 25

RocketIO™ Transceiver User Guide 1-800-255-7778

I 1 Selects realignment of incoming serial bitstream on minus-comma. High

realigns serial bitstream byte boundary when minus-comma is detected.

I 1 Selects realignment of incoming serial bitstream on plus-comma. High

realigns serial bitstream byte boundary when plus-comma is detected.

I 2 Selects the two loopback test modes. Bit 1 is for serial loopback and bit 0 is

for internal parallel loopback.

Page 26

R

Chapter 3: Digital Design Considerations

Table 3-1: GT_CUSTOM

(1)

, GT_AURORA, GT_FIBRE_CHAN

GT_INFINIBAND, and GT_XAUI Primitive Ports (Continued)

Port I/O

POWERDOWN

Port

Size

I 1 Shuts down both the receiver and transmitter sides of the transceiver when

asserted High. This decreases the power consumption while the

transceiver is shut down. This input is asynchronous.

REFCLK

I 1 High-quality reference clock driving transmission (reading TX FIFO, and

multiplied for parallel/serial conversion) and clock recovery. REFCLK

frequency is accurate to ± 100 ppm. This clock originates off the device, is

routed through fabric interconnect, and is selected by the REFCLKSEL.

REFCLK2

REFCLKSEL

I 1 An alternative to REFCLK. Can be selected by the REFCLKSEL.

I 1 Selects the reference clock to use REFCLK or REFCLK2. Deasserted is

REFCLK. Asserted is REFCLK2.

RXBUFSTATUS

O 2 Receiver elastic buffer status. Bit 1 indicates if an overflow/underflow

error has occurred when asserted High. Bit 0 indicates if the buffer is at

least half-full when asserted High.

RXCHARISCOMMA

RXCHARISK

(3)

(3)

O 1, 2, 4 Similar to RXCHARISK except that the data is a comma.

O 1, 2, 4 If 8B/10B decoding is enabled, it indicates that the received data is a "K"

character when asserted High. Included in Byte-mapping. If 8B/10B

decoding is bypassed, it remains as the first bit received (Bit "a") of the

10-bit encoded data (see Figure 3-11).

(2)

, GT_ETHERNET

Definition

(2)

,

RXCHECKINGCRC

RXCLKCORCNT

RXCOMMADET

RXCRCERR

RXDATA

RXDISPERR

RXLOSSOFSYNC

RXN

RXNOTINTABLE

RXP

(3)

(4)

(3)

(4)

O 1 CRC status for the receiver. Asserts High to indicate that the receiver has

recognized the end of a data packet. Only meaningful if RX_CRC_USE =

TRUE.

O 3 Status that denotes occurrence of clock correction or channel bonding. This

status is synchronized on the incoming RXDATA. See Clock Correction

Count, page 56.

O 1 Signals that a comma has been detected in the data stream.

O 1 Indicates if the CRC code is incorrect when asserted High. Only

meaningful if RX_CRC_USE = TRUE.

O 8,16,32 Up to four bytes of decoded (8B/10B encoding) or encoded (8B/10B

bypassed) receive data.

O 1, 2, 4 If 8B/10B encoding is enabled it indicates whether a disparity error has

occurred on the serial line. Included in Byte-mapping scheme.

O 2 Status related to byte-stream synchronization (RX_LOSS_OF_SYNC_FSM)

If RX_LOSS_OF_SYNC_FSM = TRUE, this outputs the state of the FSM.

Bit 1 signals a loss of sync.

Bit 0 indicates a resync state.

If RX_LOSS_OF_SYNC_FSM = FALSE, this indicates if received data is

invalid (Bit 1) and if the channel bonding sequence is recognized (Bit 0).

I 1 Serial differential port (FPGA external)

O 1, 2, 4 Status of encoded data when the data is not a valid character when

asserted High. Applies to the byte-mapping scheme.

I 1 Serial differential port (FPGA external)

26 www.xilinx.com UG024 (v1.5) October 16, 2002

1-800-255-7778 RocketIO™ Transceiver User Guide

Page 27

List of Available Ports

R

Table 3-1: GT_CUSTOM

(1)

, GT_AURORA, GT_FIBRE_CHAN

GT_INFINIBAND, and GT_XAUI Primitive Ports (Continued)

Port I/O

RXPOLARITY

Port

Size

I 1 Similar to TXPOLARITY, but for RXN and RXP. When deasserted, assumes

regular polarity. When asserted, reverses polarity.

RXREALIGN

O 1 Signal from the PMA denoting that the byte alignment with the serial data

stream changed due to a comma detection. Asserted High when alignment

occurs.

RXRECCLK

RXRESET

O 1 Recovered clock that is divided by 20.

I 1 Synchronous RX system reset that "recenters" the receive elastic buffer. It

also resets 8B/10B decoder, comma detect, channel bonding, clock

correction logic, and other internal receive registers. It does not reset the

receiver PLL.

RXRUNDISP

(3)

O 1, 2, 4 Signals the running disparity (0 = negative, 1 = positive) in the received

serial data. If 8B/10B encoding is bypassed, it remains as the second bit

received (Bit "b") of the 10-bit encoded data (see Figure 3-11).

RXUSRCLK

I 1 Clock from a DCM that is used for reading the RX elastic buffer. It also

clocks CHBONDI and CHBONDO in and out of the transceiver. Typically,

the same as TXUSRCLK.

(2)

, GT_ETHERNET

Definition

(2)

,

RXUSRCLK2

TXBUFERR

TXBYPASS8B10B

TXCHARDISPMODE

TXCHARDISPVAL

TXCHARISK

TXDATA

(3)

(3)

(3)

(3)

I 1 Clock output from a DCM that clocks the receiver data and status between

the transceiver and the FPGA core. Typically the same as TXUSRCLK2.

The relationship between RXUSRCLK and RXUSRCLK2 depends on the

width of the RXDATA.

O 1 Provides status of the transmission FIFO. If asserted High, an

overflow/underflow has occurred. When this bit becomes set, it can only

be reset by asserting TXRESET.

I 1, 2, 4 This control signal determines whether the 8B/10B encoding is enabled or

bypassed. If the signal is asserted High, the encoding is bypassed. This

creates a 10-bit interface to the FPGA core. See the 8B/10B section for more

details.

(3)

I 1, 2, 4 If 8B/10B encoding is enabled, this bus determines what mode of disparity

is to be sent. When 8B/10B is bypassed, this becomes the first bit

transmitted (Bit "a") of the 10-bit encoded TXDATA bus section (see

Figure 3-10) for each byte specified by the byte-mapping.

I 1, 2, 4 If 8B/10B encoding is enabled, this bus determines what type of disparity

is to be sent. When 8B/10B is bypassed, this becomes the second bit

transmitted (Bit "b") of the 10-bit encoded TXDATA bus section (see

Figure 3-10) for each byte specified by the byte-mapping section.

I 1, 2, 4 If 8B/10B encoding is enabled, this control bus determines if the

transmitted data is a "K" character or a Data character. A logic High

indicating a K-character.

I 8,16,32 Transmit data that can be 1, 2, or 4 bytes wide, depending on the primitive

used. TXDATA [7:0] is always the last byte transmitted. The position of the

first byte depends on selected TX data path width.

UG024 (v1.5) October 16, 2002 www.xilinx.com 27

RocketIO™ Transceiver User Guide 1-800-255-7778

Page 28

R

Chapter 3: Digital Design Considerations

Table 3-1: GT_CUSTOM

(1)

, GT_AURORA, GT_FIBRE_CHAN

GT_INFINIBAND, and GT_XAUI Primitive Ports (Continued)

Port I/O

TXFORCECRCERR

Port

Size

I 1 Specifies whether to insert error in computed CRC.

When TXFORCECRCERR = TRUE, the transmitter corrupts the correctly

computed CRC value by XORing with the bits specified in attribute

TX_CRC_FORCE_VALUE. This input can be used to test detection of CRC

errors at the receiver.

TXINHIBIT

I 1 If a logic High, the TX differential pairs are forced to be a constant 1/0.

TXN = 1, TXP = 0

TXKERR

(3)

O 1, 2, 4 If 8B/10B encoding is enabled, this signal indicates (asserted High) when

the "K" character to be transmitted is not a valid "K" character. Bits

correspond to the byte-mapping scheme.

(4)

TXN

(4)

TXP

TXPOLARITY

O 1 Transmit differential port (FPGA external)

O 1 Transmit differential port (FPGA external)

I 1 Specifies whether or not to invert the final transmitter output. Able to

reverse the polarity on the TXN and TXP lines. Deasserted sets regular

polarity. Asserted reverses polarity.

TXRESET

I 1 Synchronous TX system reset that “recenters” the transmit elastic buffer. It

also resets 8B/10B encoder and other internal transmission registers. It

does not reset the transmission PLL.

TXRUNDISP

(3)

O 1, 2, 4 Signals the running disparity after this byte is encoded. Zero equals

negative disparity and positive disparity for a one.

(2)

, GT_ETHERNET

Definition

(2)

,

TXUSRCLK

I 1 Clock output from a DCM that is clocked with the REFCLK (or other

reference clock). This clock is used for writing the TX buffer and is

frequency-locked to the REFCLK.

TXUSRCLK2

I 1 Clock output from a DCM that clocks transmission data and status and