Xilinx VCU1525 User Manual

VCU1525

Reconfigurable

Acceleration Platform

User Guide

UG1268 (v1.3) August 7, 2018

Revision History

The following table shows the revision history for this document.

Date |

Version |

Revision |

08/07/2018 |

1.3 |

Revised Step 4: Program the Base Platform. |

|

|

|

07/09/2018 |

1.2 |

Revised Board Features, Board Specifications, Table 2-1, Installing the VCU1525 Board |

|

|

in a Server Chassis, and Figure 3-11. Removed Xilinx constraints file information. |

|

|

Added Appendix A, Board Installation. |

04/02/2018 |

1.1 |

Revised Board Specifications and Installing the VCU1525 Board in a Server Chassis. |

|

|

Updated Table 2-1, Table 2-2, and Table 3-9. Revised paragraph after Table 3-2. |

|

|

Added Figure 3-13. Updated Figure 3-14, Figure 3-15, and Figure 3-16. Revised |

|

|

Appendix B, Regulatory and Compliance Information. |

11/13/2017 |

1.0 |

Initial Xilinx release. |

|

|

|

VCU1525 Acceleration Platform User Guide

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

Send Feedback |

2 |

|

|

Table of Contents

Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Chapter 1: Introduction

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Board Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Board Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Environmental . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Operating Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Chapter2: Board Setup and Configuration

Board Component Location. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Default Switch Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Installing the VCU1525 Board in a Server Chassis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

FPGA Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Chapter3: Board Component Descriptions

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Component Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Virtex UltraScale+ XCVU9P-L2FSGD2104E FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 I/O Voltage Rails . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 DDR4 DIMM Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18 Quad SPI Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19 USB JTAG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20 FT4232HQ USB-UART Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21 Clock Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24 System Clock and QSFP0 Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26 QSFP1 Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Programmable MGT and User Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 GTY Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30 PCI Express Endpoint Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32 28 Gb/s QSFP+ Module Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33 I2C Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34 Status LEDs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38 User I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39 Board Management Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39 Board Management Controller Voltage Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43 VCU1525 Board Power System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

VCU1525 Acceleration Platform User Guide

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

Send Feedback |

3 |

|

|

Monitoring Voltage and Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Vccint Regulator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Cooling Fan Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

AppendixA: Board Installation

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Installing a Board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Step 1: Set Up the Card and Computer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48 Step 2: Prepare Board Installation Files. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49 Step 3: Install Board Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50 Step 4: Program the Base Platform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50 Step 5: Verify Successful Board Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Debugging the Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

SDx Debug Command Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53 dmatest Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54 Example Output using VCU1525 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54 Failure to Create a Compute Program. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55 Useful Debug Operating System Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56 Other OS Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

AppendixB: Regulatory and Compliance Information

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

CE Directives. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

CE Standards. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Electromagnetic Compatibility. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Safety . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Markings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

AppendixC: Additional Resources and Legal Notices

Xilinx Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Documentation Navigator and Design Hubs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

VCU1525 Acceleration Platform User Guide |

|

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

Send Feedback |

4 |

|

|

Chapter 1

Introduction

Overview

The VCU1525 Reconfigurable Acceleration Platform is a peripheral component interconnect express (PCIe®) Gen3 x16 compliant board featuring the Xilinx® Virtex® UltraScale+™ XCVU9P-L2FSGD2104E FPGA. This Xilinx FPGA-based PCIe accelerator board is designed to accelerate compute-intensive applications like machine learning, data analytics, and video processing.

The VCU1525 board is available in both active and passive cooling configurations and designed to be used in cloud data center servers.

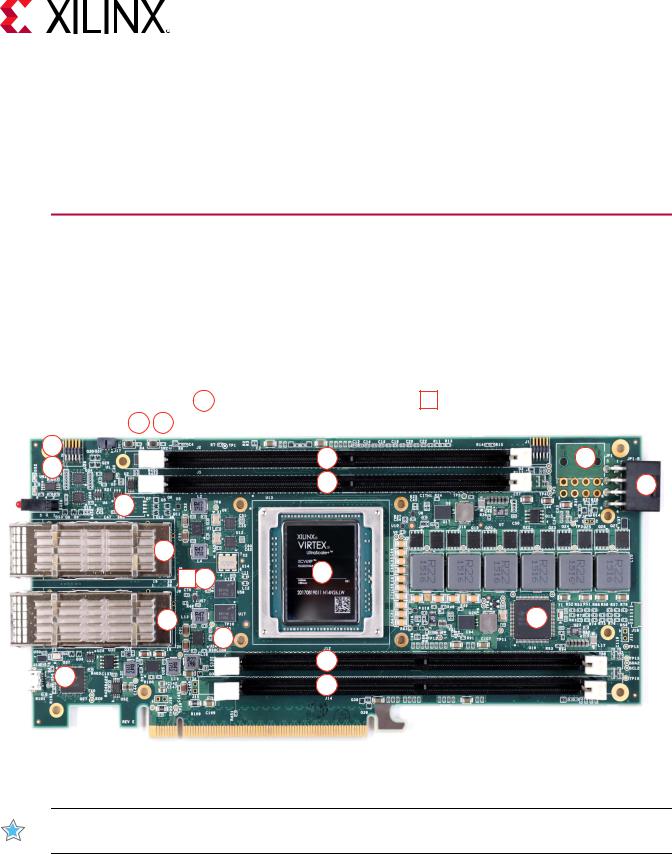

Figure 1-1 shows the VCU1525 active cooling configuration (PC applications).

X20017-110217

Figure 1-1: VCU1525 Reconfigurable Acceleration Platform (Active Cooling)

VCU1525 Acceleration Platform User Guide |

|

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

Send Feedback |

5 |

|

|

Chapter 1: Introduction

Figure 1-2 shows the VCU1525 passive cooling configuration (data center server applications).

X20018-110217

Figure 1-2: VCU1525 Reconfigurable Acceleration Platform (Passive Cooling)

CAUTION! The VCU1525 board with passive cooling is designed to be installed into a data center server, where controlled air flow provides direct cooling. The VCU1525 board with active cooling is designed to be installed into a PC environment where the air flow is uncontrolled, hence this configuration has the heat sink and fan enclosure cover installed to provide appropriate cooling. In either cooling configuration, due to the board enclosure, switches are not accessible, nor are LEDs visible (except the triple-LED module DS3 which protrudes through the left front end PCIe bracket). Board details revealed in this user guide are provided to aid understanding of board features. If the cooling enclosure is removed from either configuration of the board and it is powered-up, external fan cooling airflow MUST be applied to prevent over-temperature shut-down and possible damage to the board electronics.

See Appendix C, Additional Resources and Legal Notices for references to documents, files, and resources relevant to the VCU1525 board.

VCU1525 Acceleration Platform User Guide

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

Send Feedback |

6 |

|

|

Chapter 1: Introduction

Block Diagram

A block diagram of the VCU1525 board is shown in Figure 1-3.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

244-pin DIMM interface |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64-bit + ECC dual rank support |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x4/x8 UDIMM support |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C0 |

PC4-2400 compatible |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Clocks |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

244-pin DIMM interface |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64-bit + ECC dual rank support |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x4/x8 UDIMM support |

|

|

||

|

|

XADC |

|

|

|

|

|

|

|

|

|

|

C2 |

PC4-2400 compatible |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

244-pin DIMM interface |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

LEDs |

|

|

|

|

|

|

|

|

|

|

|

64-bit + ECC dual rank support |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

x4/x8 UDIMM support |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

VU9P |

|

|

|

|

|

C3 |

PC4-2400 compatible |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

QSFP #2 |

|

|

|

D2104 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

244-pin DIMM interface |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64-bit + ECC dual rank support |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x4/x8 UDIMM support |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

QSFP #1 |

|

|

|

|

|

|

|

|

|

|

|

C1 |

PC4-2400 compatible |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

QSPI1 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIP SW |

|

POWER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

PCIe GEN1/2/3 x 1/2/4/8/16 |

|

|

QSPI2 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

PCIe GEN4 x 8 |

|

|

|

|

|

|

|

|

|

|

|

X19964-110617 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Figure 1-3: VCU1525 Board Block Diagram

VCU1525 Acceleration Platform User Guide

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

Send Feedback |

7 |

|

|

Chapter 1: Introduction

Board Features

The VCU1525 board features are listed in this section. Detailed information for each feature is provided in Component Descriptions in Chapter 3.

•Virtex UltraScale+ XCVU9P-L2FSGD2104E FPGA

•Memory (four independent dual-rank DDR4 interfaces)

°48 gigabyte (GB) DDR4 memory

°4x DDR4 16 GB, 2400 mega-transfers per second (MT/s), 64-bit with error correcting code (ECC) DIMM

°x4/x8 unregistered dual inline memory module (UDIMM) support

•Configuration options

°1 gigabit (Gb) Quad Serial Peripheral Interface (SPI) flash memory

°Micro-AB universal serial bus (USB) J13 JTAG configuration port (FT4232HQ U65 bridge)

•76 GTY transceivers (19 Quads)

°16-lane PCI Express (16 GTY)

°Two QSFP28 100G interfaces (8 GTY)

°52 GTY not used

•Clock sources

°Two Si5335A Quad clock generators

°Si570 I2C programmable LVDS clock generator

•USB-to-UART FT4232HQ bridge with Micro-AB USB connector

•PCIe integrated Endpoint block connectivity

°Gen1, 2 or 3 x1/x2/x4/x8/x16

°Gen4 x8

•I2C bus

•Status LEDs

•User I/O (4-pole user dual-inline package (DIP) SW3, CPU_RESET PB SW1)

•Power management with system management bus (SMBus) voltage, current, and temperature monitoring

•Dynamic power sourcing based on external power supplied

•75W PCIe slot functional with 35 A max VCCINT current PCIe slot power only

VCU1525 Acceleration Platform User Guide

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

Send Feedback |

8 |

|

|

Chapter 1: Introduction

•150 W PCIe slot functional with 110 A max VCCINT current PCIe slot power and 6-pin PCIe Aux power cable connected

•225 W PCIe slot functional with 160 A max VCCINT current PCIe slot power and 8-pin PCIe Aux power cable connected

•Two QSFP28 100G interfaces

•Onboard reprogrammable flash configuration memory

•Front panel JTAG and universal asynchronous receiver-transmitter (UART) access through the USB port

•FPGA configurable over USB/JTAG and Quad SPI configuration flash memory

•Thermal management with variable rate fan for minimal fan noise

Board Specifications

Dimensions

Height: 4.2 inch (10.67 cm)

PCB thickness (±5%): 0.062 inch (0.157 cm)

Board length, passive heat sink: 9.2 inch (23.4 cm)

Board length, active heat sink: 11.4 inch (29 cm)

Board thickness with heat sink enclosure installed:

Active: 1.52 inch (3.86 cm)

Passive: 1.44 inch (3.66 cm)

Dual slot PCIe full-length, full height form-factor compliant

Note: A 3D model of this board is not available.

Environmental

Temperature

Operating: 0°C to +45°C

Storage: –25°C to +60°C

VCU1525 Acceleration Platform User Guide

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

Send Feedback |

9 |

|

|

Chapter 1: Introduction

Humidity

10% to 90% non-condensing

Operating Voltage

PCIe slot +12 VDC, +3.3 VDC, +3.3 VAUXDC, External +12 VDC

VCU1525 Acceleration Platform User Guide |

|

Send Feedback |

10 |

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

|

|

|

|

Chapter 2

Board Setup and Configuration

Board Component Location

Figure 2-1 shows the location of components on the VCU1525 board. Each component shown is keyed to Table 2-1. Table 2-1 identifies the components, references the respective schematic page numbers, and links to a detailed functional description of the component and board features in Chapter 3, Board Component Descriptions.

|

00 |

Round callout references a component |

00 Square callout references a component |

|

|

on the front side of the board |

on the back side of the board |

19 |

20 |

|

|

8 |

|

5 |

16 |

9 |

|

||

|

|

|

|

|

|

4 |

17 |

18 |

|

|

|

13

1

12 12

14 |

15 |

6

2

7

3

X19972-031618

Figure 2-1: VCU1525 Board Components

IMPORTANT: Figure 2-1 is for visual reference only and might not reflect the current revision of the board.

VCU1525 Acceleration Platform User Guide |

|

Send Feedback |

11 |

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

|

|

|

|

Chapter 2: Board Setup and Configuration

CAUTION! The VCU1525 board can be damaged by electrostatic discharge (ESD). Follow standard ESD prevention measures when handling the board.

Table 2-1: VCU1525 Board Component Descriptions

Number |

Ref. Des. |

Feature |

Notes |

Schematic |

|

(Link) |

Page |

||||

|

|

|

|||

1 |

U13 |

Virtex UltraScale+ |

XCVU9P-L2FSGD2104E |

— |

|

|

|

XCVU9P-L2FSGD2104E FPGA |

|

|

|

2 |

J14 |

C0 DDR4 72-bit DIMM memory |

Micron MTA18ASF2G72PZ-2G3B1IG |

33 |

|

|

|

(16 GB) |

|

|

|

|

|

(DDR4 DIMM Memory) |

|

|

|

|

|

|

|

|

|

3 |

J12 |

C1 DDR4 72-bit DIMM memory |

Micron MTA18ASF2G72PZ-2G3B1IG |

34 |

|

|

|

(16 GB) |

|

|

|

|

|

(DDR4 DIMM Memory) |

|

|

|

|

|

|

|

|

|

4 |

J5 |

C2 DDR4 72-bit DIMM memory |

Micron MTA18ASF2G72PZ-2G3B1IG |

35 |

|

|

|

(16 GB) |

|

|

|

|

|

(DDR4 DIMM Memory) |

|

|

|

|

|

|

|

|

|

5 |

J2 |

C3 DDR4 72-bit DIMM memory |

Micron MTA18ASF2G72PZ-2G3B1IG |

36 |

|

|

|

(16 GB) |

|

|

|

|

|

(DDR4 DIMM Memory) |

|

|

|

|

|

|

|

|

|

6 |

U17, U58 |

Quad SPI Flash Memory (1Gb total) |

Micron MT25QU01GBBA8E12-0SIT |

12 |

|

|

|

|

|

|

|

7 |

U27, J13 |

USB JTAG bridge w/ USB Micro-AB |

FTDI FT4232HQ-REEL |

31 |

|

|

|

connector |

HIROSE ZX62D-AB-5P8 |

|

|

|

|

(FT4232HQ USB-UART Interface) |

|

||

|

|

|

|

||

|

|

|

|

|

|

8 |

J1 |

SMBUS 2X5 1.27mm pitch connector |

SAMTEC FTSH-105-01-F-D-K |

16 |

|

|

|

(Monitoring Voltage and Current) |

|

|

|

|

|

|

|

|

|

9 |

J3 |

BMC CTLR. JTAG 2 X 5 1.27 mm pitch |

SAMTEC FTSH-105-01-F-D-K |

24 |

|

|

|

connector |

|

|

|

|

|

(Figure 3-18 U19 MSP432 I2C |

|

|

|

|

|

Connectivity) |

|

|

|

10 |

U9 |

SYSCLK_300 300MHz, QSFP0_CLOCK |

SI5335A-B06201-GM |

23 |

|

|

|

156.25MHz, 1.8V LVDS |

|

|

|

|

|

(System Clock and QSFP0 Clock) |

|

|

|

|

|

|

|

|

|

11 |

U12 |

QSFP1_CLOCK 156.25MHz, 1.8V |

SI5335A-B06201-GM |

27 |

|

|

|

LVDS (QSFP1 Clock) |

|

|

|

12 |

U14, U43 |

USER_SI570_CLOCK, 156.25MHz, |

Silicon Labs SI570BAB000544DG |

23 |

|

|

|

3.3V LVDS |

Silicon Labs SI53340-B-GM |

|

|

|

|

+1 to 4 clock buffer |

|

||

|

|

|

|

||

|

|

(Programmable MGT and User |

|

|

|

|

|

Clock) |

|

|

|

13 |

J7 |

QSFP0 (28 Gb/s QSFP+ Module |

AMPHENOL FS1-Z38-20Z6-60 |

23 |

|

|

|

Connectors) |

|

|

|

14 |

J9 |

QSFP1 (28 Gb/s QSFP+ Module |

AMPHENOL FS1-Z38-20Z6-60 |

27 |

|

|

|

Connectors) |

|

|

VCU1525 Acceleration Platform User Guide |

|

Send Feedback |

12 |

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

|

|

|

|

Chapter 2: Board Setup and Configuration

Table 2-1: VCU1525 Board Component Descriptions (Cont’d)

Number |

Ref. Des. |

Feature |

Notes |

Schematic |

|||

(Link) |

Page |

||||||

|

|

|

|

||||

15 |

|

U19 |

Board Management Controller |

TI MSP432P401RIPZ |

24 |

|

|

|

|

|

(BMC) |

|

|

|

|

16 |

|

JP1 |

Auxiliary 12V power connector |

LIGHT JIE AARRA001-08MTTRH |

17 |

|

|

|

|

|

(Vccint Regulator Circuit) |

|

|

|

|

17 |

|

J4 |

Cooling Fan Connector |

JST SALES S4B-PH-K-S(LF)(SN) |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Default Switch Settings

Default switch settings are listed in Table 2-2. Switch locations are shown in Figure 2-1.

Table 2-2: Default Switch Settings

Switch |

Function |

Default |

Comments |

Figure 2-1 Callout |

Schematic Page |

SW3 |

4-pole GPIO DIP |

ON, ON, ON, ON |

4-pole user DIP |

18 |

11 |

|

|

|

|

|

|

Table 2-3 shows other visible switch locations.

Table 2-3: Other Visible Switches

Component |

Function |

Comments |

Figure 2-1 Callout |

Schematic Page |

SW1 |

Pushbutton switch |

CPU_RESET_B |

19 |

11 |

|

|

|

|

|

SW2 |

Pushbutton switch |

PROGRAM_B |

20 |

11 |

|

|

|

|

|

Installing the VCU1525 Board in a Server Chassis

Because each server or PC vendors hardware is different, for physical card installation guidance, see the manufacturer’s PCIe card installation instructions.

For programming and start-up details, see Appendix A, Board Installation.

VCU1525 Acceleration Platform User Guide |

|

Send Feedback |

13 |

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

|

|

|

|

Chapter 2: Board Setup and Configuration

FPGA Configuration

The VCU1525 board supports two UltraScale+ FPGA configuration modes:

•Quad SPI flash memory

•JTAG using USB JTAG configuration port (USB J13/FT4232H U27)

The FPGA bank 0 mode pins are hardwired to M[2:0] = 001 Master SPI mode with pull-up/down resistors.

At power up, the FPGA is configured by the Quad SPI NOR Flash U17 device (Micron MT25QU01GBBA8E12-0SIT) with the FPGA_CCLK operating at clock rate of 105 MHz (EMCCLK) using the Master Serial Configuration mode.

The Quad SPI flash memory NOR device has a capacity of 1 Gb.

While the FPGA default mode selects Quad SPI configuration, JTAG mode overrides it if invoked. JTAG mode is always available independent of the Mode pin settings.

M0 is pulled up, however it is also connected to the I2C I/O port U2 PCA9536 device (port P1, pin 2). This connection allows M0 to be driven low by the MSP432 U19 BMC over I2C (via the I2C PCS9536 U2 port expander), disabling the Master SPI mode.

For complete details on configuring the FPGA, see UltraScale Architecture Configuration User Guide (UG570) [Ref 1].

Table 2-4: Configuration Modes

Configuration Mode |

M[2:0] |

Bus Width |

CCLKL Direction |

Master SPI |

001 |

x1, x2, x4 |

FPGA output |

|

|

|

|

JTAG |

Not applicable - JTAG overrides |

x1 |

Not applicable |

|

|

|

|

VCU1525 Acceleration Platform User Guide |

|

Send Feedback |

14 |

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

|

|

|

|

Chapter 2: Board Setup and Configuration

The configuration circuit is shown in Figure 2-2.

X19973-103017

Figure 2-2: VCU1525 Configuration Circuit

VCU1525 Acceleration Platform User Guide |

|

Send Feedback |

15 |

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

|

|

|

|

Chapter 3

Board Component Descriptions

Overview

This chapter provides a detailed functional description of board components and features. Table 2-1 identifies the components, references the respective schematic page numbers, and links to the corresponding detailed functional description in this chapter. Component locations are shown in Table 2-1.

Component Descriptions

Virtex UltraScale+ XCVU9P-L2FSGD2104E FPGA

[Figure 2-1, callout 1]

The VCU1525 board is populated with the Virtex® UltraScale+™ XCVU9P-L2FSGD2104E FPGA.

For more information on Virtex UltraScale+ FPGAs, see Virtex UltraScale+ FPGA Data Sheet: DC and AC Switching Characteristics (DS923) [Ref 2].

I/O Voltage Rails

There are 13 I/O banks available on the XCVU9P-L2FSGD2104E FPGA and the VCU1525 board.

VCU1525 Acceleration Platform User Guide |

|

Send Feedback |

16 |

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

|

|

|

|

Chapter 3: Board Component Descriptions

Figure 3-1 shows the XCVU9P-L2FSGD2104E bank arrangement.

MGTY233 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGTY133 |

|

|

|

72 |

73 |

|

74 |

71 |

70 |

|

69 |

|

|

|

|

|

|

||||||||||

MGTY232 |

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

MGTY131 |

||||||||||||||||||

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGTY231 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGTY130 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

MGTY230 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGTY129 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

MGTY229 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGTY128 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

MGTY228 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGTY123 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

MGTY227 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGTY122 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

MGTY226 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGTY121 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

MGTY225 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGTY224 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGTY120 |

|

67 |

|

|

|

64 |

|

65 |

|

61 |

62 |

|

63 |

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X19971-103017

Figure 3-1: XCVU9P-L2FSGD2104E Bank Arrangement

VCU1525 Acceleration Platform User Guide |

|

Send Feedback |

17 |

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

|

|

|

|

Chapter 3: Board Component Descriptions

The voltages applied to the XCVU9P-L2FSGD2104E U13 FPGA I/O banks are listed in Table 3-1.

Table 3-1: I/O Bank Voltage Rails

XCVU9P-L2FSGD2104E |

Power Net Name |

Voltage |

|

Connected To |

Bank 61 |

VCC1V2_BTM |

1.2V |

DDR4 C0 DQ[0:15], DQ[40:55] |

|

|

|

|

|

|

Bank 62 |

VCC1V2_BTM |

1.2V |

DDR4 C0 DQ[16:39], DQ[56:63] |

|

|

|

|

|

|

Bank 63 |

VCC1V2_BTM |

1.2V |

DDR4 C0 DQ[64:71], ADDR/CTRL |

|

|

|

|

|

|

Bank 64 |

VCC1V2_BTM |

1.2V |

USB, QSFP0,QSFP1, I2C, GPIO_MSP, SW_DP |

|

|

|

|

|

|

Bank 65 |

VCC1V2_BTM |

1.2V |

DDR4 C1 DQ[64:71], ADDR/CTRL |

|

|

|

|

|

|

Bank 66 |

VCC1V2_BTM |

1.2V |

DDR4 C1 |

DQ[32:63] |

|

|

|

|

|

Bank 67 |

VCC1V8_BTM |

1.2V |

DDR4 C1 |

DQ[0:31] |

|

|

|

|

|

Bank 69 |

VCC1V2_TOP |

1.2V |

DDR4_C2 DQ[32:71] |

|

|

|

|

|

|

Bank 70 |

VCC1V2_TOP |

1.2V |

DDR4 C2 |

DQ[40:47], ADDR/CTRL |

|

|

|

|

|

Bank 71 |

VCC1V2_TOP |

1.2V |

DDR4_C2 DQ[0:31 |

|

|

|

|

|

|

Bank 72 |

VCC1V2_TOP |

1.2V |

DDR4 C3 |

DQ[64:71], ADDR/CTRL |

|

|

|

|

|

Bank 73 |

VCC1V2_TOP |

1.2V |

DDR4_C3 DQ[16:31], DQ[40:55] |

|

|

|

|

|

|

Bank 74 |

VCC1V2_TOP |

1.2V |

DDR4_C3 DQ[0:15], DQ[32:39], DQ[56:63] |

|

|

|

|

|

|

DDR4 DIMM Memory

[Figure 2-1, callout 2, 3, 4, 5]

Four independent dual-rank DDR4 interfaces are available on the VCU1525 board. The VCU1525 board is populated with four socketed single-rank Micron MTA18ASF2G72PZ-2G3B1IG or Samsung M393A2K40BB1-CRC 16GB DDR4 UDIMMs. Each DDR4 is 72-bits wide (64-bits plus support for ECC).

Memory interface-to-FPGA bank assignment is shown in Table 3-1. The DDR4 0.6V VTT termination voltages are sourced from four independent TI TPS51200DR regulator circuits.

The VCU1525 DDR4 memory interfaces adhere to the constraints guidelines documented in the "DDR3/DDR4 Design Guidelines" section of the UltraScale Architecture-Based FPGAs Memory IP LogiCORE IP Product Guide (PG150) [Ref 3]. The VCU1525 board DDR4 memory interfaces are 40 Ω impedance implementations.

For more details about the Micron DDR4 DIMM, see the Micron MTA18ASF2G72PZ-2G3B1IG data sheet at the Micron website [Ref 7].

For more details about the Samsung DDR4 DIMM, see the Samsung M393A2K40BB1-CRC data sheet at the Samsung website [Ref 8].

VCU1525 Acceleration Platform User Guide |

|

Send Feedback |

18 |

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

|

|

|

|

Chapter 3: Board Component Descriptions

Quad SPI Flash Memory

[Figure 2-1, callout 6]

Two Quad Serial Peripheral Interface (SPI) flash memory devices of the same type and wired in parallel are provided on the VCU1525 board (U17 and U58). A field effect transistor (FET) switch structure (U57 and U61) implements a chip-select enable mechanism, controlled by the MSP432 board management controller (BMC). Only one Quad SPI device can be enabled at a time.

The default selected (bank 0 configuration) Quad SPI flash memory is U17. Each Quad SPI device provides 1 Gb of nonvolatile storage.

•Part number: MT25QU01GBB8E12-0SIT (Micron)

•Supply voltage: 1.8V

•Datapath width: 4 bits

•Data rate: variable

Figure 3-2 shows the linear Quad SPI flash memory circuitry on the VCU1525 board. For more flash memory details, see the Micron MT25QU01GBB8E12-0SIT data sheet at the Micron website [Ref 7].

Figure 3-2: Quad SPI 1Gb Flash Memory

VCU1525 Acceleration Platform User Guide

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

X20038-110617

Send Feedback |

19 |

|

|

Chapter 3: Board Component Descriptions

For details on bank 0 pins, see UltraScale Architecture Configuration User Guide (UG570) [Ref 1].

USB JTAG Interface

[Figure 2-1, callout 7]

The VCU1525 board XCVU9P-L2FSGD2104E FPGA U13 is the only component in the Joint Test Action Group (JTAG) chain. JTAG configuration is available through the USB-to-JTAG FTDI FT4232HQ U27 bridge device connected to Micro-AB USB connector J13. The FTDI JTAG signals are level-shifted through TXBN0304 device U35. The PCIe 16-lane edge connector CN1 JTAG port is connected in parallel through level-shifter U34. GPIO port 3 of the U19 MSP432 BMC is also connected through level-shifter U33. Each level-shifter enable pin is controlled by the BMC to allow only one JTAG connection at a time.

JTAG configuration is allowed at any time regardless of the FPGA mode pin settings.

The JTAG chain block diagram is shown in Figure 3-3.

|

U27 |

|

U35 |

|

|

U13R |

|

|

FT4232HQ |

|

TXBN0304 |

|

|

XCVU9PFSGD2104 |

|

J13 |

ADBUS0 |

FT TCK |

A1 |

B1 |

TCK |

TCK |

|

|

FT TDO |

TDI |

|

||||

|

ADBUS1 |

A3 |

B3 |

TDI |

BANK 0 |

||

|

FT TDI |

TDO |

|||||

USB AB |

ADBUS2 |

A2 |

B2 |

TDO |

|

||

FT TMS |

TMS |

|

|||||

|

ADBUS3 |

A4 |

B4 |

TMS |

|

||

|

FT OE |

|

|

||||

|

ADBUS5 |

OE_B |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

3.3V L/S 1.8V |

|

|

|

|

|

U19 |

|

U33 |

|

|

|

|

|

MSP432 |

|

TXBN0304 |

|

|

|

|

|

P3_0 |

|

MSP TCK |

A1 |

B1 |

|

|

|

|

TCK |

|

|

|

|

|

MSP TDI |

|

|

|

|

TDI |

|

|

|

|||

GPIO |

P3_1 |

|

A3 |

B3 |

|

|

|

|

|

|

|

||

|

MSP TDO |

|

|

|

|

TDO |

|

|

|

||||

P3_2 |

|

A2 |

B2 |

|

|

|

|

|

|

|

|||

PORT |

P3_3 |

|

MSP TMS |

A4 |

B4 |

|

|

|

|

TMS |

|

|

|

|

MSP EN |

|

|

|

|

|

|||||||

|

P3_4 |

|

OE_B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

P10_4 |

|

|

3.3V L/S 1.8V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

BD. MGMT. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CONTROLLER |

|

|

|

|

|

|

|

|

|

|

|

|

|

CN1 |

|

|

|

U34 |

|

|

|

|

|

|

|

|

|

PCIe EDGE |

|

PEX OE |

TXBN0304 |

|

|

|

|

|

|

|

|

|

|

|

|

|

OE_B |

|

|

|

|

|

|

|

|

|

|

|

|

|

PEX TCK |

|

|

|

|

|

TCK |

|

|

|

|

|

A5 |

|

A1 |

B1 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

TDI |

|

|

|

||||

|

|

PEX TDI |

|

|

|

||||||||

|

A6 |

|

A3 |

B3 |

|

|

|

|

|

|

|

||

|

|

PEX TDO |

|

|

|

|

TDO |

|

|

|

|||

|

A7 |

|

A2 |

B2 |

|

|

|

|

|

|

|

||

|

A8 |

|

PEX TMS |

A4 |

B4 |

|

|

|

|

TMS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

3.3V L/S 1.8V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X19965-031418

Figure 3-3: VCU1525 JTAG Chain Block Diagram

VCU1525 Acceleration Platform User Guide |

|

Send Feedback |

20 |

UG1268 (v1.3) August 7, 2018 |

www.xilinx.com |

|

|

|

|

Loading...

Loading...