5-59

FAST AND LS TTL DATA

BCD TO 7-SEGMENT

DECODER

The SN54/74LS48 is a BCD to 7-Segment Decoder consisting of NAND

gates, input buffers and seven AND-OR-INVERT gates. Seven NAND gates

and one driver are connected in pairs to make BCD data and its complement

available to the seven decoding AND-OR-INVERT gates. The remaining

NAND gate and three input buffers provide lamp test, blanking input/rippleblanking input for the LS48.

The circuit accepts 4-bit binary-coded-decimal (BCD) and, depending on

the state of the auxiliary inputs, decodes this data to drive other components.

The relative positive logic output levels, as well as conditions required at the

auxiliary inputs, are shown in the truth tables.

The LS48 circuit incorporates automatic leading and/or trailing edge

zero-blanking control (RBI and RBO). Lamp Test (LT) may be activated any

time when the BI /RBO node is HIGH. Both devices contain an overriding

blanking input (BI) which can be used to control the lamp intensity by varying

the frequency and duty cycle of the BI input signal or to inhibit the outputs.

• Lamp Intensity Modulation Capability (BI/RBO)

• Internal Pull-Ups Eliminate Need for External Resistors

• Input Clamp Diodes Eliminate High-Speed Termination Effects

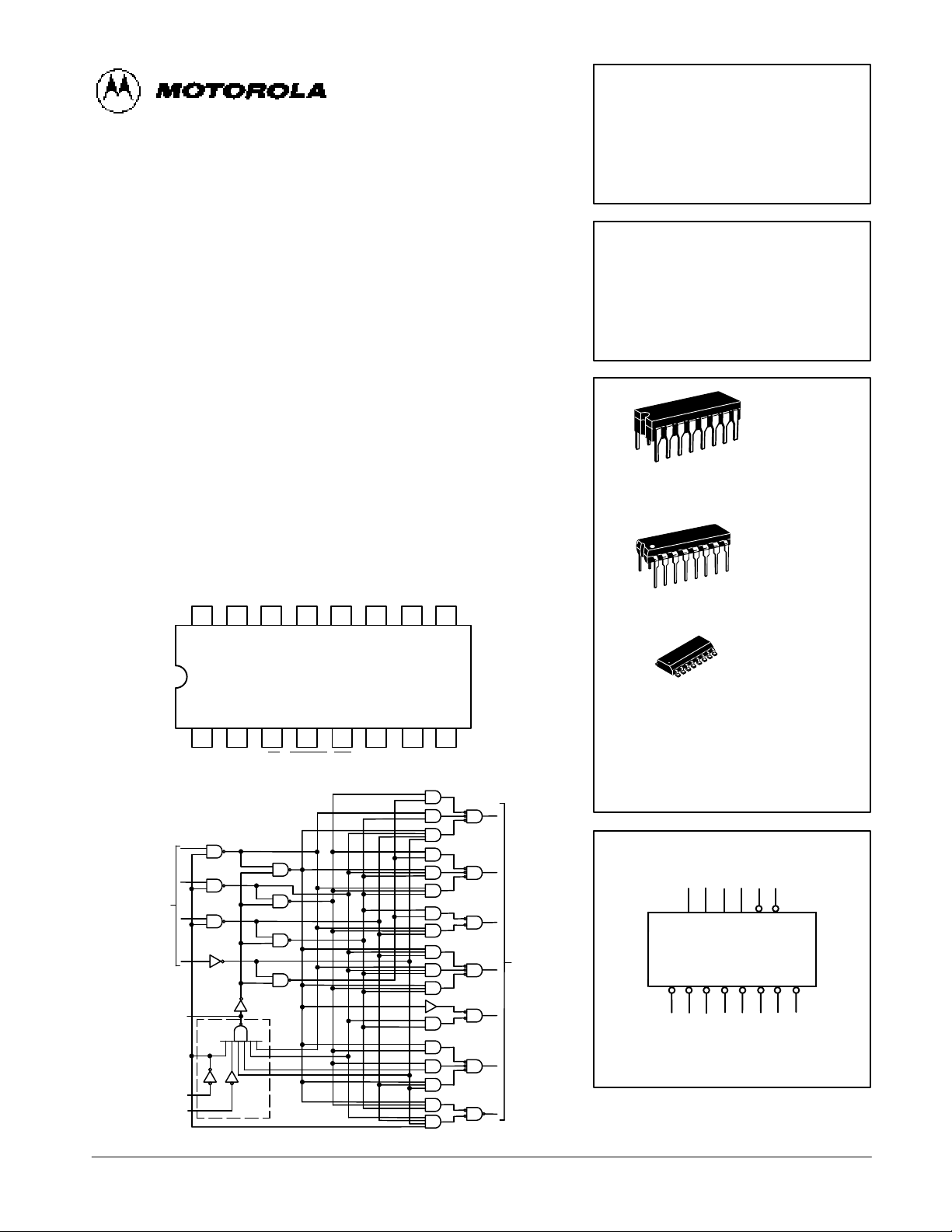

14 13 12 11 10 9

1 2 3 4 5 6

V

CC

7

16 15

8

f g a b c d e

B C LT

BI/RBO RBI D A GND

CONNECTION DIAGRAM DIP (TOP VIEW)

LOGIC DIAGRAM

INPUT

BLANKING INPUT OR

RIPPLE-BLANKING

OUTPUT

RIPPLE-BLANKING

INPUT

LAMP-TEST

INPUT

A

B

C

D

a

b

c

d

e

f

g

OUTPUT

SN54/74LS48

BCD TO 7-SEGMENT

DECODER

LOW POWER SCHOTTKY

J SUFFIX

CERAMIC

CASE 620-09

N SUFFIX

PLASTIC

CASE 648-08

16

1

16

1

ORDERING INFORMATION

SN54LSXXJ Ceramic

SN74LSXXN Plastic

SN74LSXXD SOIC

16

1

D SUFFIX

SOIC

CASE 751B-03

LOGIC SYMBOL

VCC = PIN 16

GND = PIN 8

7 1 2 6 3 5

13 12 11 10 9 15 14 4

A B C D LT RBI

a b c d e f g

BI/

RBO

SN54/74LS48

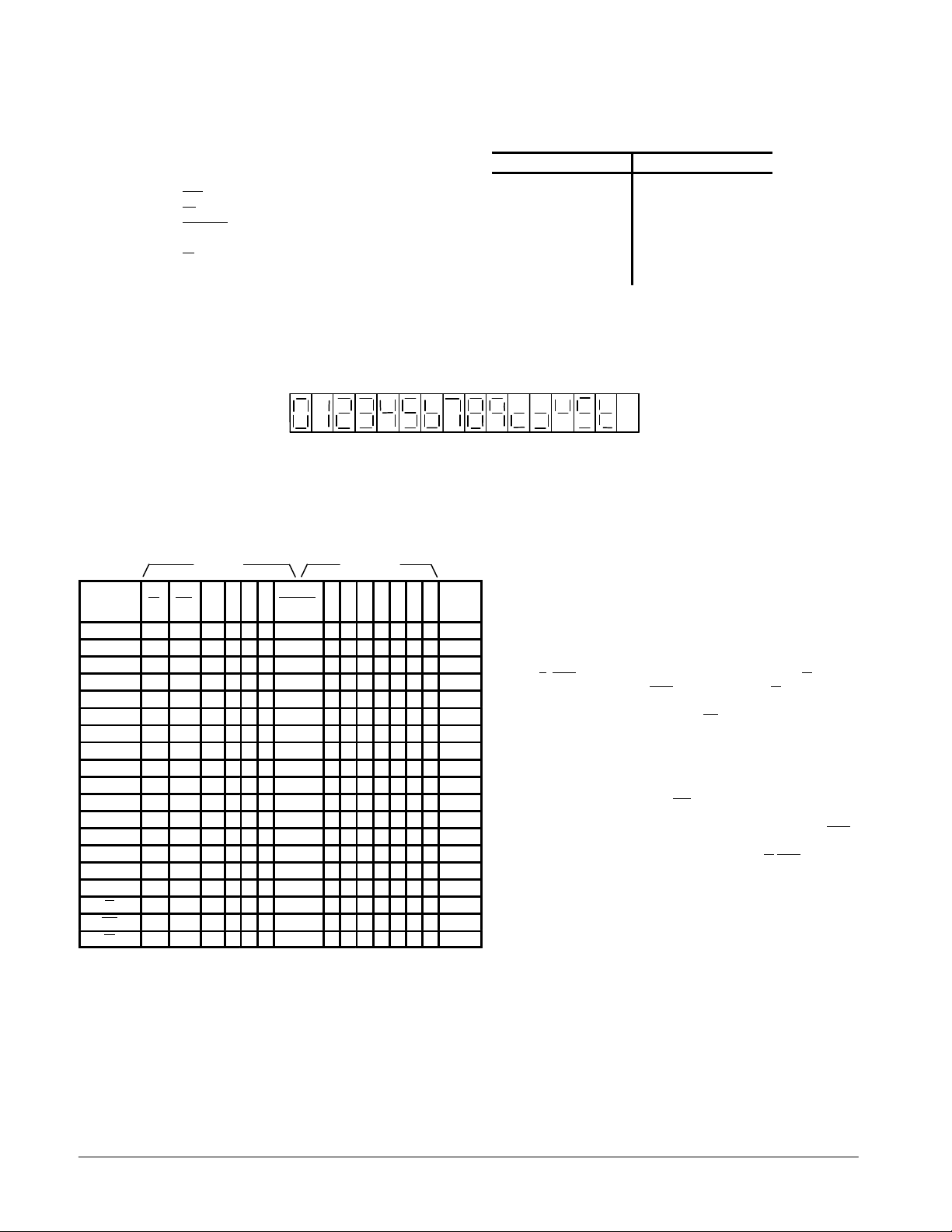

NUMERICAL DESIGNATIONS — RESULTANT DISPLAYS

0 1 2 3 4 5 6 7 8 9 10 11 12 13

NOTES:

(1) B

I/RBO is wired-AND logic serving as blanking input (BI) and/or

ripple-blanking output (RBO

). The blanking out (BI) must be open

or held at a HIGH level when output functions 0 through 15 are

desired, and ripple-blanking input (RB

I) must be open or at a HIGH

level if blanking of a decimal 0 is not desired. X=input may be HIGH

or LOW.

(2) When a LOW level is applied to the blanking input (forced condition)

all segment outputs go to a LOW level, regardless of the state of any

other input condition.

(3) When ripple-blanking input (RBI

) and inputs A, B, C, and D are at

LOW level, with the lamp test input at HIGH level, all segment

outputs go to a HIGH level and the ripple-blanking output (RBO

)

goes to a LOW level (response condition).

(4) When the blanking input/ripple-blanking output (BI

/RBO) is open or

held at a HIGH level, and a LOW level is applied to lamp-test input,

all segment outputs go to a LOW level.

TRUTH TABLE

SN54/74LS48

INPUTS OUTPUTS

5-60

FAST AND LS TTL DATA

SN54/74LS48

PIN NAMES LOADING (Note a)

HIGH

LOW

A, B, C, D

RBI

LT

BI/RBO

BI

BCD Inputs

Ripple-Blanking (Active Low) Input

Lamp-Test (Active Low) Input

Blanking Input or RippleBlanking Output (Active Low)

Blanking (Active Low) Input

0.5 U.L.

0.5 U.L.

0.5 U.L.

0.5 U.L.

1.2 U.L.

0.5 U.L.

Open-Collector

0.25 U.L.

0.25 U.L.

0.25 U.L.

0.75 U.L.

2(1) U.L.

0.25 U.L.

3.75 (1.25) U.L. (48)

NOTES:

a) Unit Load (U.L.) = 40 µA HIGH/1.6 mA LOW

b) Outut current measured at V

OUT

= 0.5 V

Output LOW drive factor is SN54LS/74LS48: 1.25 U.L. for Military (54), 3.75 U.L. for Commercial (74).

DECIMAL

OR

FUNCTION

LT RBI D C B A BI /RBO a b c d e f g NOTE

0 H H L L L L H H H H H H H L 1

1 H X L L L H H L H H L L L L 1

2 H X L L H L H H H L H H L H

3 H X L L H H H H H H H L L H

4 H X L H L L H L H H L L H H

5 H X L H L H H H L H H L H H

6 H X L H H L H L L H H H H H

7 H X L H H H H H H H L L L L

8 H X H L L L H H H H H H H H

9 H X H L L H H H H H L L H H

10 H X H L H L H L L L H H L H

11 H X H L H H H L L H H L L H

12 H X H H L L H L H L L L H H

13 H X H H L H H H L L H L H H

14 H X H H H L H L L L H H H H

15 H X H H H H H L L L L L L L

BI X X X X X X L L L L L L L L 2

RBI H L L L L L L L L L L L L L 3

LT L X X X X X H H H H H H H H 4

14 15

5-61

FAST AND LS TTL DATA

SN54/74LS48

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 54

74

4.5

4.75

5.0

5.0

5.5

5.25

V

T

A

Operating Ambient Temperature Range 54

74

–55

0

25

25

125

70

°C

I

OH

Output Current — High a to g 54, 74 –100 µA

I

OH

Output Current — High BI/RBO 54, 74 –50 µA

I

OL

Output Current — Low a to g 54

74

2.0

6.0

mA

I

OL

Output Current — Low BI/RBO

BI/RBO

54

74

1.6

3.2

mA

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

Symbol

Parameter

Min Typ Max

Unit

Test Conditions

V

IH

Input HIGH Voltage 2.0 V

Guaranteed Input HIGH Voltage for

All Inputs

54 0.7

VILInput LOW Voltage

74 0.8

V

Guaranteed Input LOW Voltage for

All Inputs

V

IK

Input Clamp Diode Voltage –1.5 V VCC = MIN, IIN = –18 mA

CC

= MIN, IOH = –50 µA,

VOHOutput HIGH Voltage

2.4

4.2

µA

VCC = MIN, IOH = –50 µA,

VIN = VIH or U.L. per Truth Table

I

O

Output Current a to g –1.3 –2.0 mA

VCC = MIN, VO = 0.85 V

Input Conditioner as for V

OH

54, 74 0.4 V IOL = 2.0 mA

CC

= MIN, VIH = 2.0 V

VOLOutput LOW Voltage a to g

74 0.5 V IOL = 6.0 mA

VCC = MIN, VIH = 2.0 V

VIL = VIL MAX

54, 74 0.4 V IOL = 1.6 mA

CC

= MAX, VIH = 2.0 V

V

OL

Output LOW Voltage

BI/RBO

74 0.5 V IOL = 3.2 mA

VCC = MAX, VIH = 2.0 V

VIL = VIL MAX

20 µA VCC = MAX, VIN = 2.7 V

I

IH

Input HIGH Current

(Except BI/RBO

)

0.1 mA VCC = MAX, VIN = 7.0 V

I

IL

Input LOW Current

(Except BI/RBO

)

–0.4 mA VCC = MAX, VIN = 0.4 V

I

IL

Input LOW Current BI/RBO –1.2 mA VCC = MAX, VIN = 0.4 V

I

CC

Power Supply Current 25 38 mA VCC = MAX

I

OS

Short Circuit Current BI/RBO (Note 1) –0.3 –2.0 mA VCC = MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

AC CHARACTERISTICS (V

CC

= 5.0 V, TA = 25°C)

Limits

Symbol

Parameter

Min Typ Max

Unit

Test Conditions

t

PHL

Propagation Delay Time, HIGH-to-LOW

Level Output from A Input

100 ns

t

PLH

Propagation Delay Time, LOW-to-HIGH

Level Output from A Input

100 ns

CL = 15 pF, RL = 4.0 kΩ

t

PHL

Propagation Delay Time, HIGH-to-LOW

Level Output from RBI

Input

100 ns

t

PLH

Propagation Delay Time, LOW-to-HIGH

Level Output from RBI

Input

100 ns

CL = 15 pF, RL = 6.0 kΩ

Guaranteed Input LOW Voltage for

V

Output LOW Voltage

Input HIGH Current

V

V

Loading...

Loading...