Page 1

AVR 2650 harman/kardon

121

A3S56D30FTP

A3S56D40FTP

256M Double Data Rate Synchronous DRAM

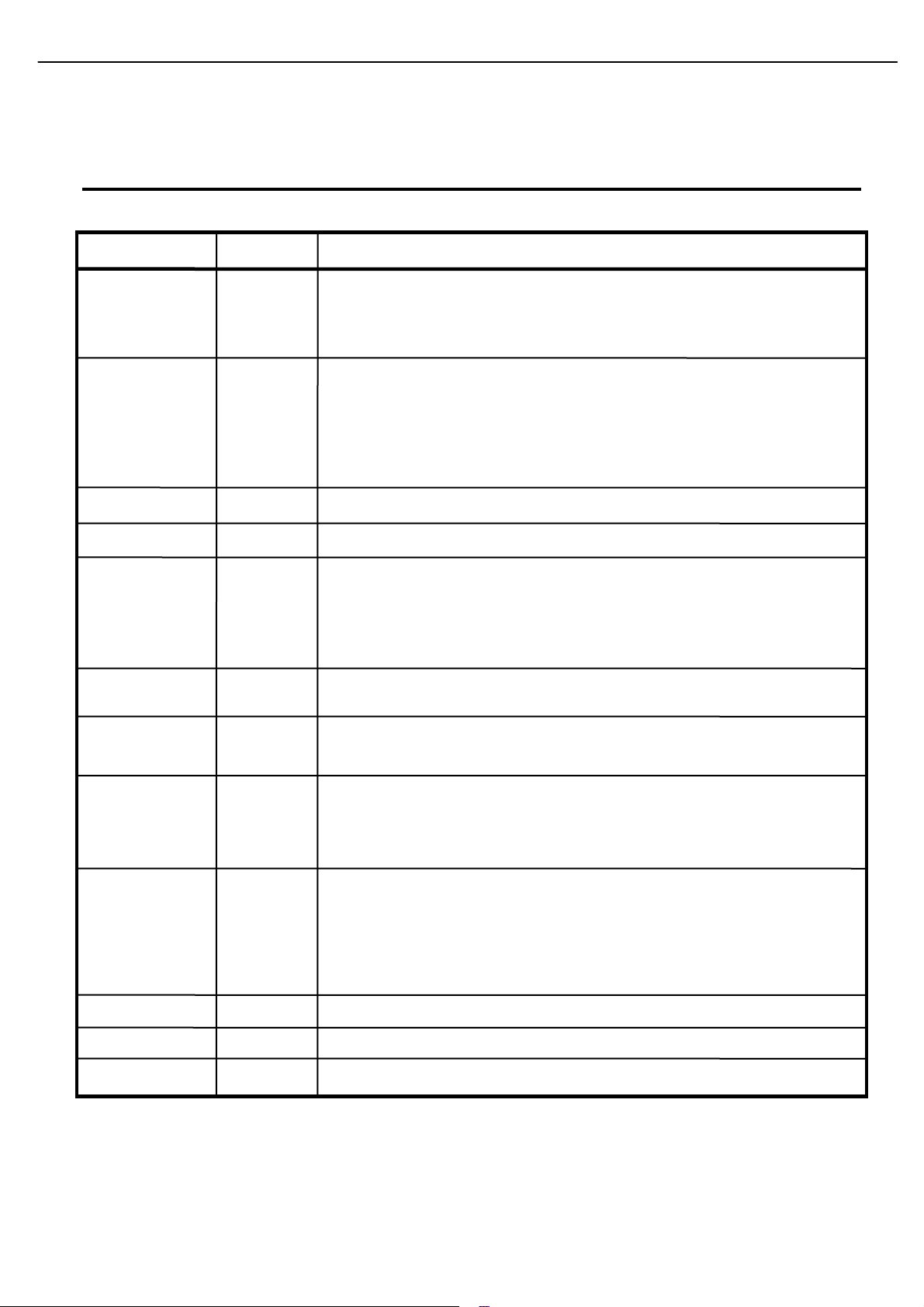

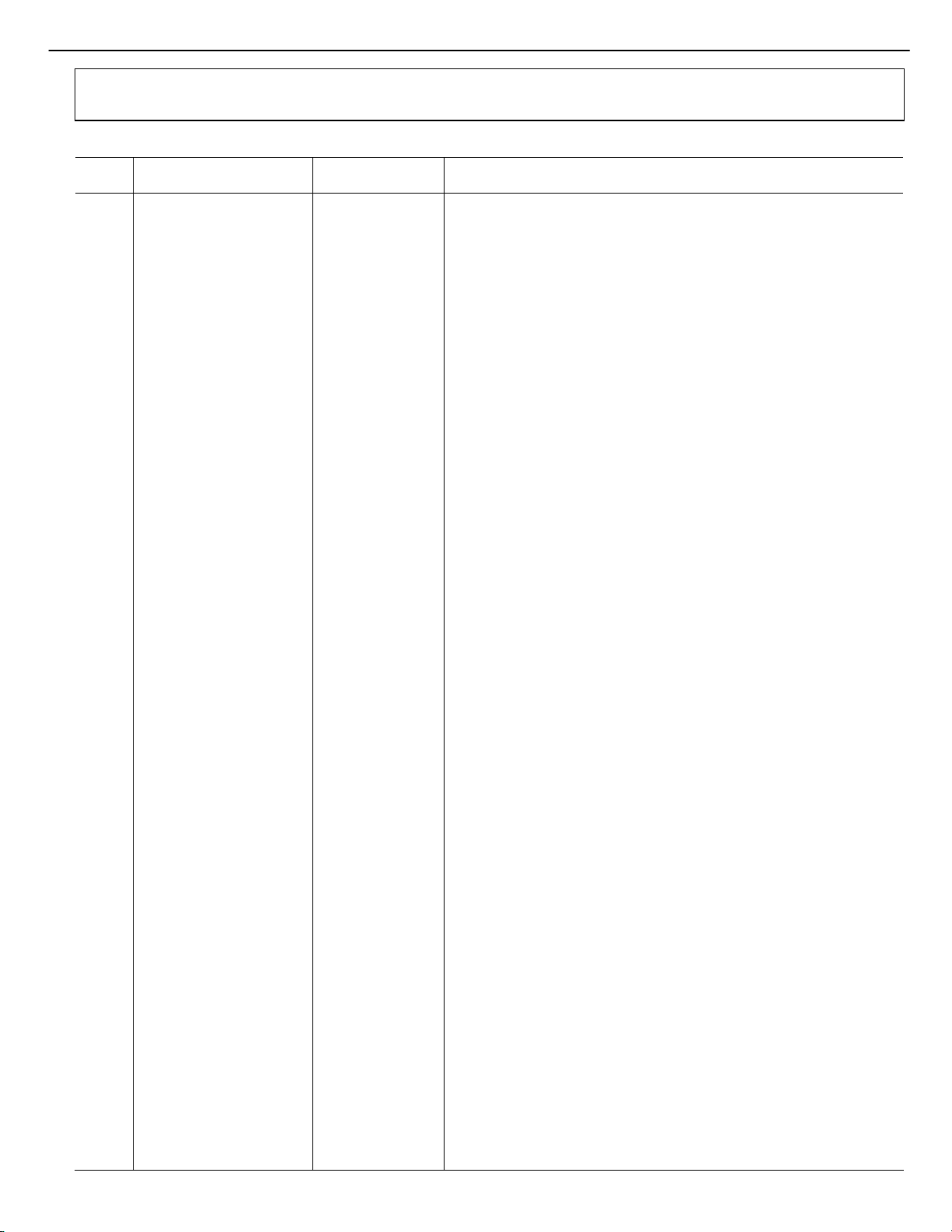

PIN FUNCTION

SYMBOL TYPE DESCRIPTION

Clock: CLK and /CLK are differential clock inputs. All address and control

CLK, /CLK Input

CKE

Input

input signals are sampled on the crossing of the positive edge of CLK and

negative edge of /CLK. Output (read) data is referenced to the crossings of

CLK and /CLK (both directions of crossing).

Clock Enable: CKE controls Power Down and Self Refresh.

Taking CKE LOW provides Precharge Power Down or Self Refresh (all banks idle),

or Active Power Down (row active in any bank).

Taking CKE HIGH provides Power Down exit or Self Refresh exit.

After Self Refresh is started, CKE becomes asynchronous input.

Power Down and Self Refresh is maintained as long as CKE is LOW.

/CS Input Chip Select: When /CS is HIGH, any command means No Operation.

/RAS, /CAS, /WE Input Combination of /RAS, /CAS, /WE defines basic commands.

A0-12 specify the Row / Column Address in conjunction with BA0,1. The

Row Address is specified by A0-12. The Column Address is specified by

A0-12 Input

BA0,1 Input

DQ0-7 (x8),

DQ0-15 (x16),

DQS (x8)

UDQS, LDQS (x16)

DM (x8)

UDM, LDM (x16)

Input / Output

Input / Output

Input

A0-9(x8) and A0-8(x16). A10 is also used to indicate precharge

option. When A10 is HIGH at a Read / Write command, an Auto Precharge

is performed. When A10 is HIGH at a Precharge command, all banks are precharged.

Bank Address: BA0,1 specifies one of four banks to which a command is applied.

BA0,1 must be set with Active, Precharge, Read, Write commands.

Data Input/Output: Data bus

Data Strobe: Output with read data, input with write data. Edge-aligned

with read data, centered in write data. Used to capture write data.

For the x16, LDQS corresponds to the data on DQ0-DQ7; UDQS

correspond to the data on DQ8-DQ15

Input Data Mask: DM is an input mask signal for write data. Input data

is masked when DM is sampled HIGH along with that input data

during a write access. DM is sampled on both edges of DQS.

Although DM pins are input only, the DM loading matches the DQ

and DQS loading. For the x16, LDM corresponds to the data on DQ0-DQ7;

UDM corresponds to the data on DQ8-DQ15.

Vdd, Vss Power Supply Power Supply for the memory array and peripheral circuitry.

VddQ, VssQ Power Supply VddQ and VssQ are supplied to DQ, DQS buffers.

VREF Input SSTL_2 reference voltage.

Page 2

AVR 2650 harman/kardon

122

12-Bit, 170 MHz Video and Graphics Digitizer with

3D Comb Filter Decoder and

Quad HDMI 1.4 Fast Switching Receiver

PRELIMINARY

FEATURES

Quad HDMI 1.4 Fast Switching Receiver

170 MHz Video and Graphics Digitizer

3D Comb Filter Video Decoder

SCART Fast Blank Support

Adaptive HDMI Equaliser

Integrated CEC Controller

HDMI Repeater Support

Advanced VBI data slicer

Video and Graphics Digitizer

Four 170 MHz, 12-bit ADCs,

12-channel analog input mux

525i-/625i-component analog input

525p-/625p-component progressive scan support

720p-/1080i-/1080p-component HDTV support

Low refresh rates (24/25/30 Hz) support for 720p/1080p

Digitizes RGB graphics up to 1600 × 1200 at 60 Hz (UXGA)

3D Video Decoder

NTSC/PAL/SECAM color standards support

NTSC/PAL 2D/3D motion detecting comb filter

Advanced time-base correction (TBC) with frame

synchronization

Interlaced-to-progressive conversion for 525i and 625i

IF compensation filters

Vertical peaking and horizontal peaking filters

Robust synchronization extraction for poor video source

4:1 HDMI 1.4 225 MHz Receiver

Fast-Switching of HDMI ports

2:2 HEAC muxing support

2 HEAC channel support

2 Ethernet Interfaces for HEC Support

SPDIF interface for ARC support.

3D Video format support including frame packing 1080p

24Hz, 720p 50 Hz, 720p 60Hz

Full colorimetry support including sYCC601, Adobe RGB,

Adobe YCC 601

36-/30-bit Deep Color and 24-bit color support

HDCP 1.3 support with internal HDCP Keys

+5V Detect and Hot plug assert for each HDMI port

Full HDMI Audio Support including HBR, DSD, DST

Advanced Audio mute feature

Flexible digital audio output interfaces

ADV7844

Supports up to 5 SPDIF outputs,

Supports up to 4 I2S outputs

General

Highly flexible 36-bit pixel output interface

Internal EDID RAM for HDMI and graphics

Dual STDI (standard identification) function support

Any-to-any, 3 × 3 color space conversion (CSC) matrix

2 programmable interrupt request output pins

Simultaneous analog processing and HDMI monitoring

APPLICATIONS

Advanced TVs

PDP HDTVs

LCD TVs (HDTV ready)

LCD/DLP® rear projection HDTVs

CRT HDTVs

LCoS™ HDTVs

AVR video receivers

LCD/DLP front projectors

HDTV STBs with PVR

Projectors

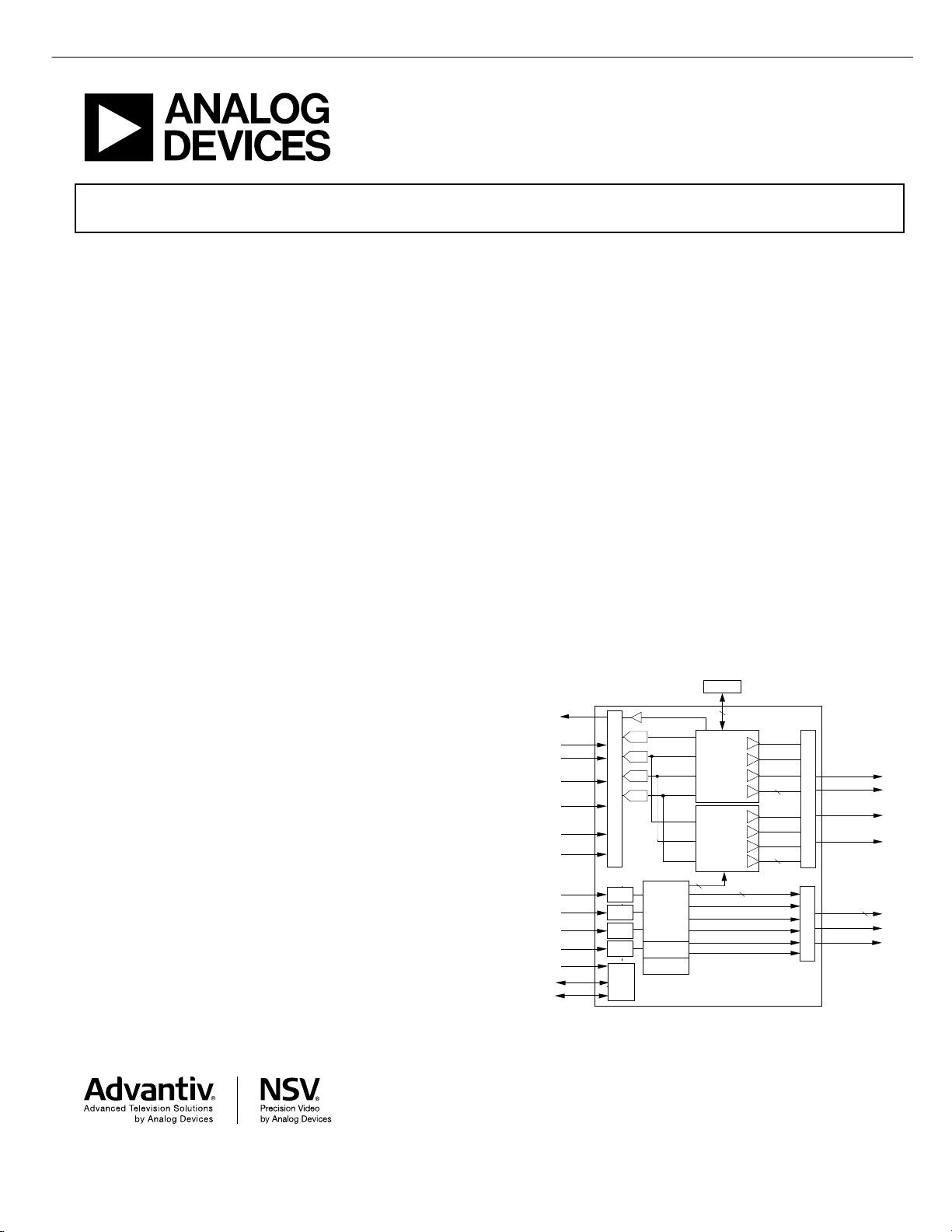

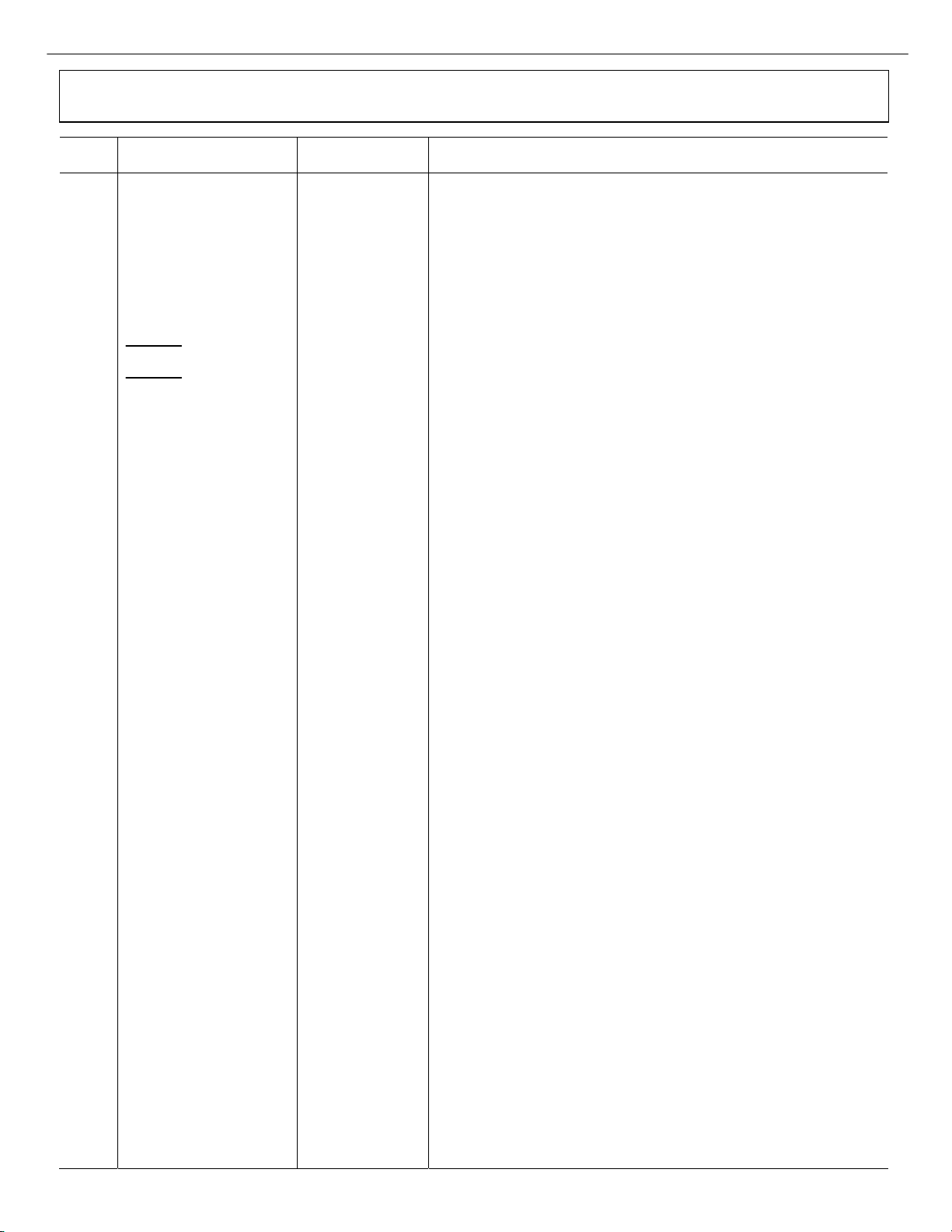

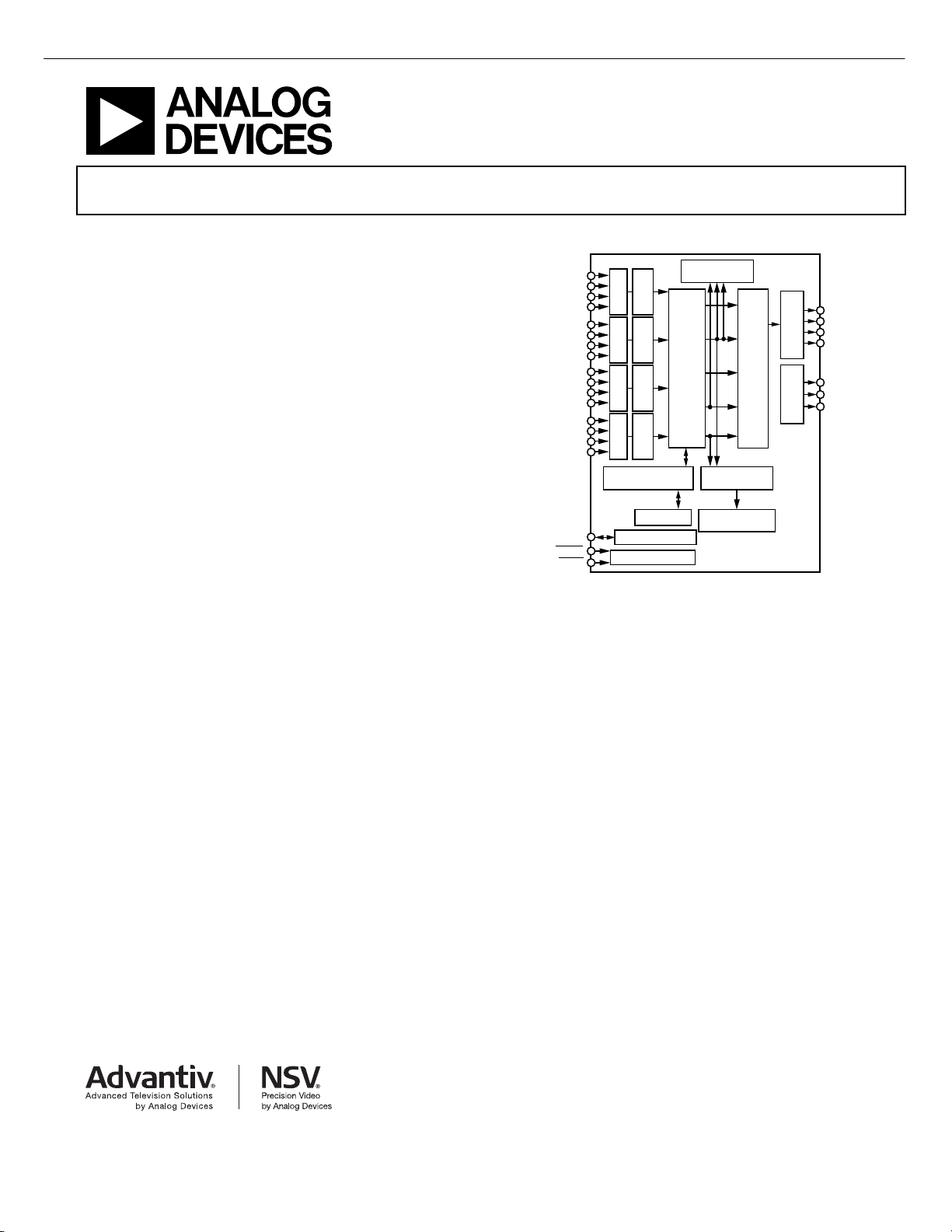

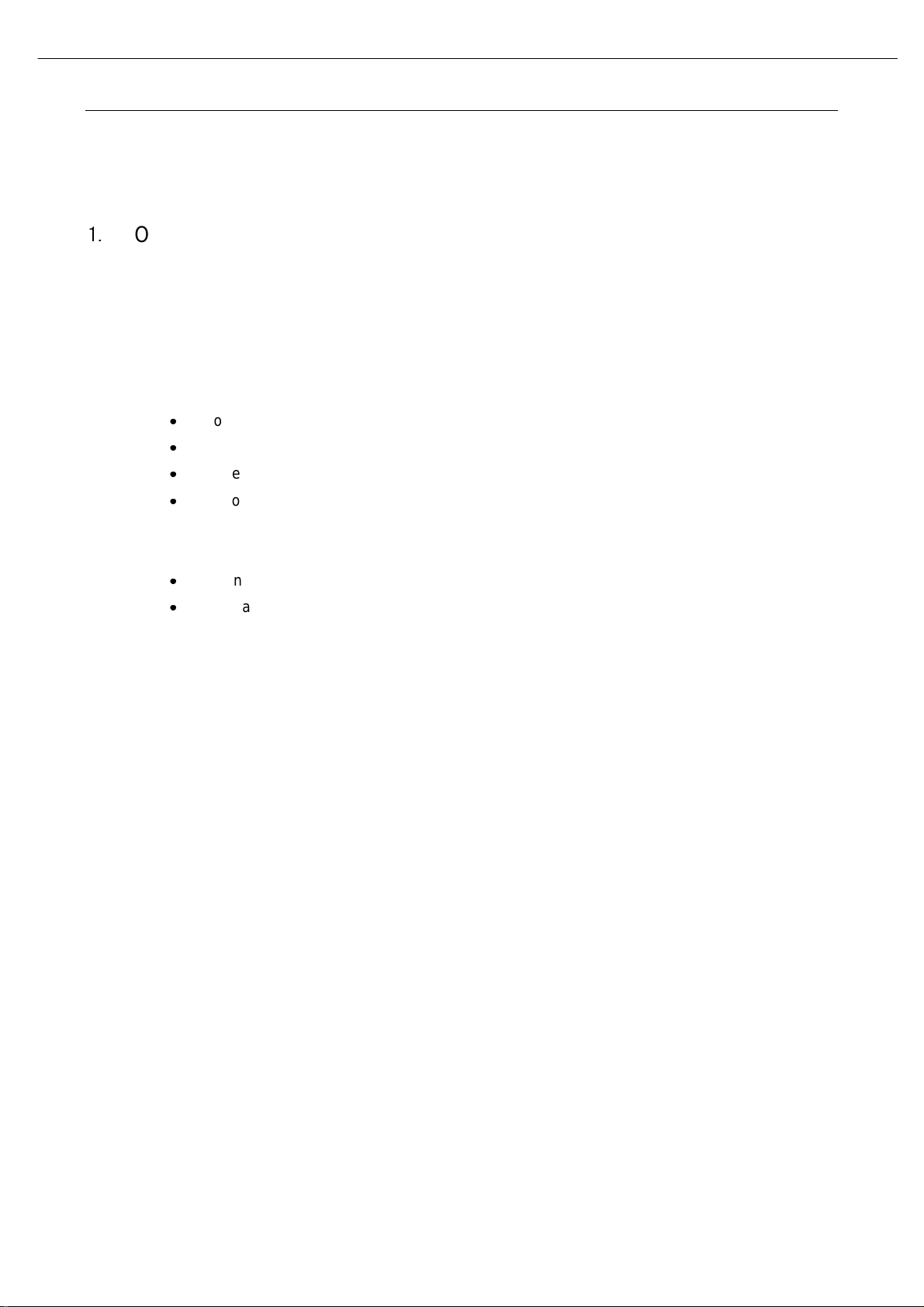

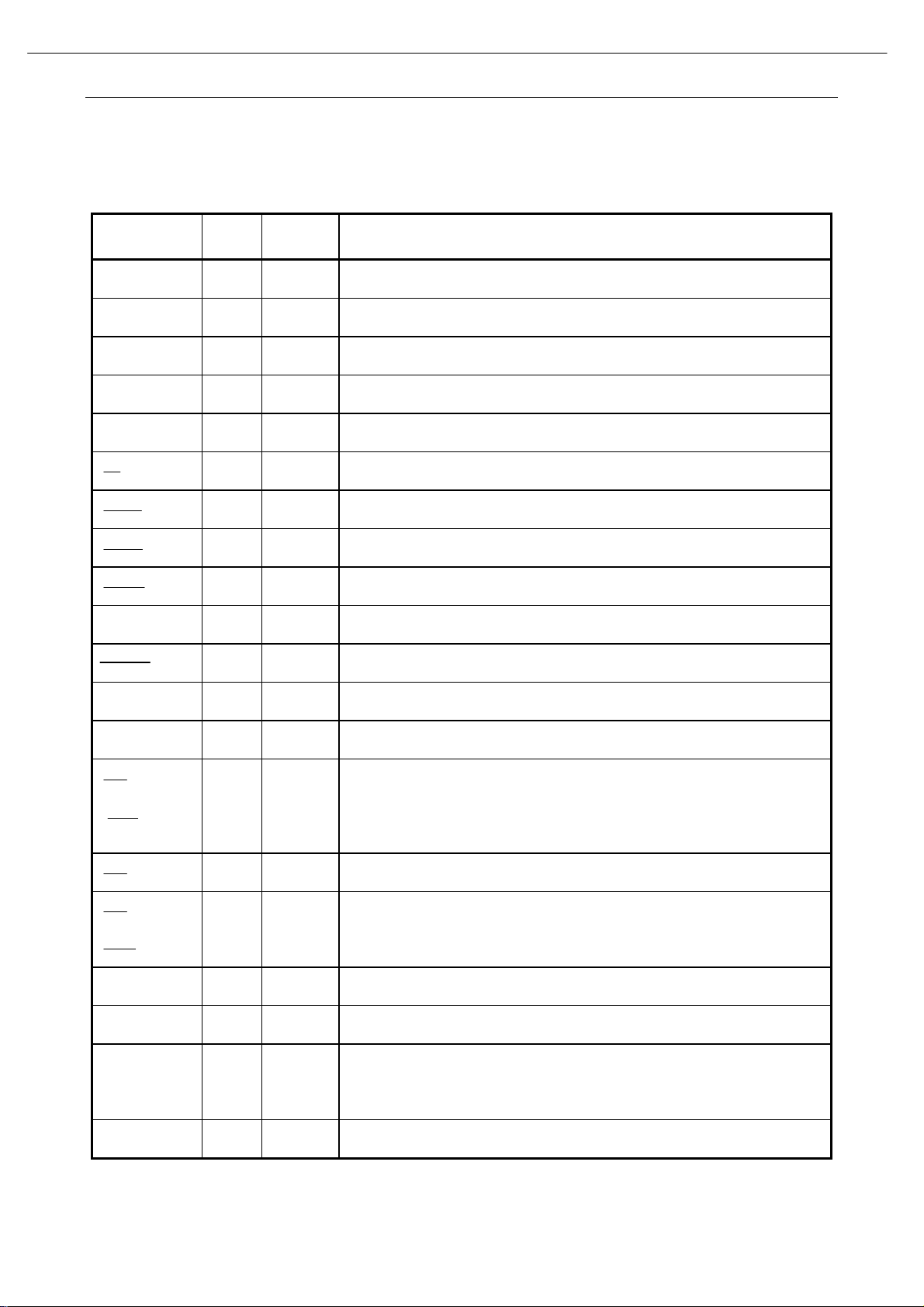

FUNCTIONAL BLOCK DIAGRAM

SDRAM

SCART

CVBS

SCART RGB

+CVBS

CVBS

SD/PS

YPbPr

HD YPbPr

GRAPHICS

RGB

HDMI 1

HDMI 2

HDMI 3

HDMI 4

SPDIF

ETHERNET 1

ETHERNET 2

YC

INPUT MUX

TMDS

DDC

TMDS

DDC

TMDS

DDC

TMDS

DDC

HEAC

ADC

ADC

ADC

ADC

SCART G

SCART B

SCART R

DEEP

COLOR

HDMI Rx

FAST

SWITCH

HDCP

KEYS

CVBS

CVBS

Y/G

Pb/B

Pr/R

Figure 1.

48

SDP

CVBS 3D YC

S-VIDEO

SCART

CP

YPbPr

525p/625p

720p/1080i

1080p/UXGA

RGB

36

4

HS/VS

FIELD/DE

CLK

DATA

HS/VS

FIELD/DE

CLK

DATA

I2S

SPDIF

DSD

HBR

MCLK

SCLK

ADV7844

HS/VS

FIELD/DE

CLK

OUTPUT MUX

36-BIT YCbCr

/RGB

AUDIO

OUTPUT

MCLK

SCLK

OUTPUT MUX

TO AUDIO

PROCESSOR

5

Page 3

AVR 2650 harman/kardon

123

ADV7844 PRELIMINARY

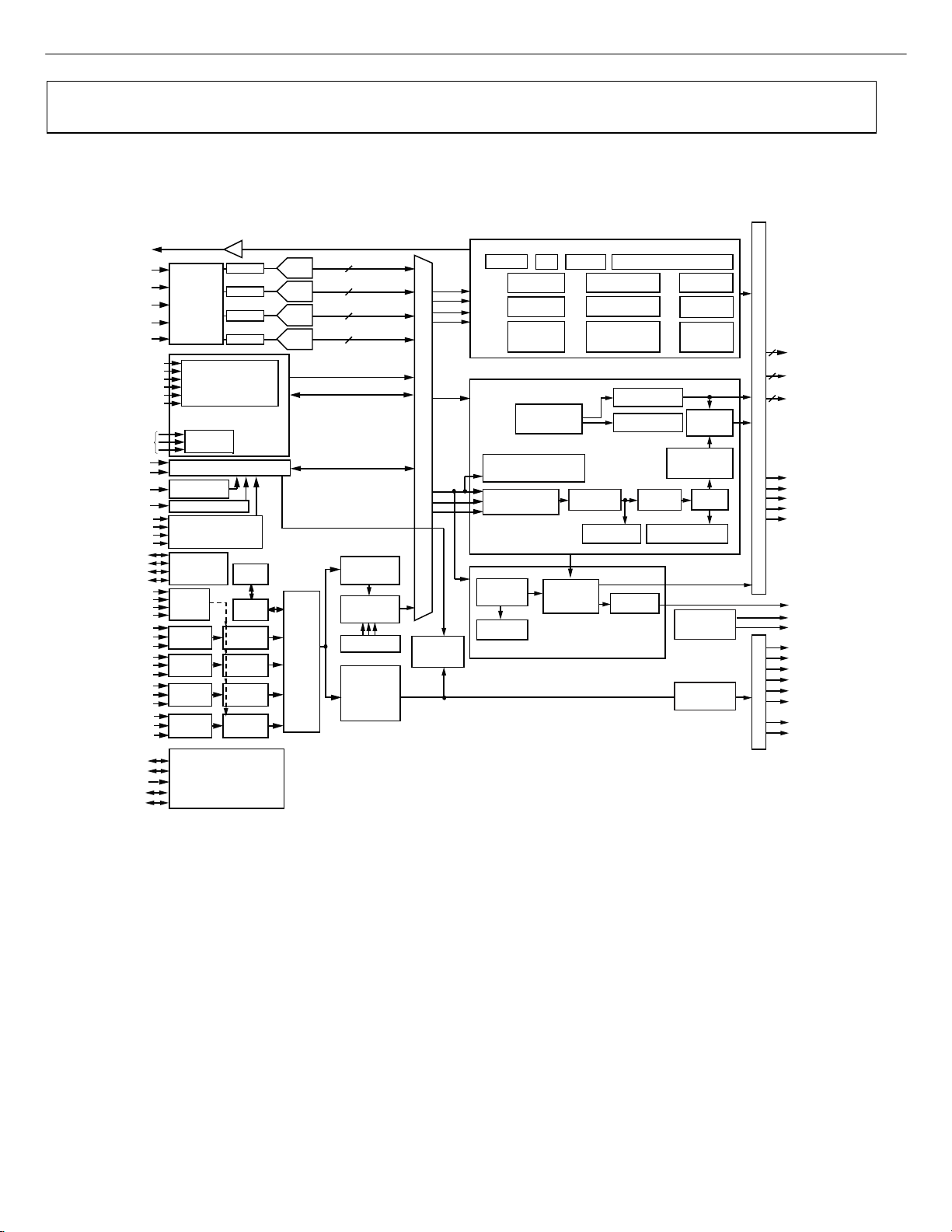

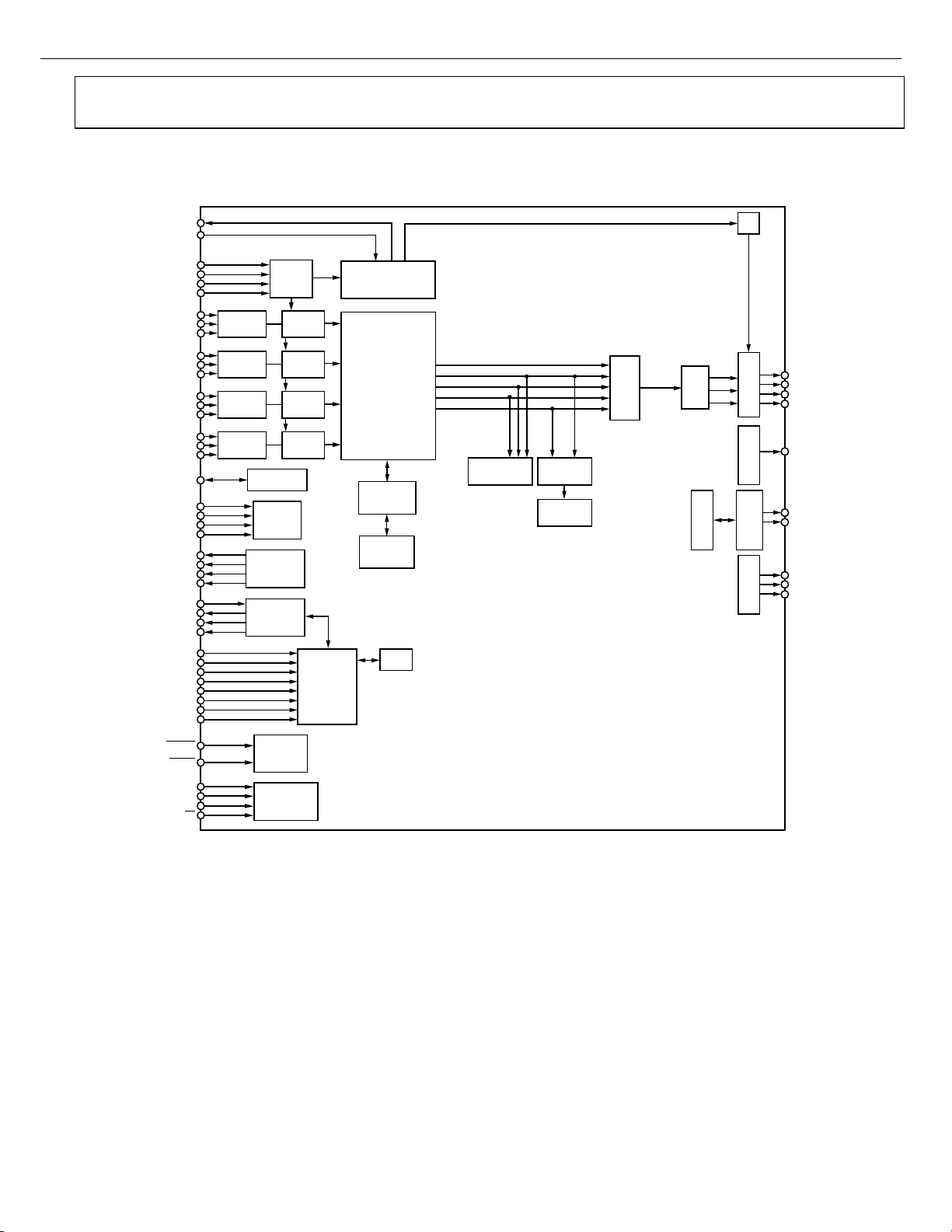

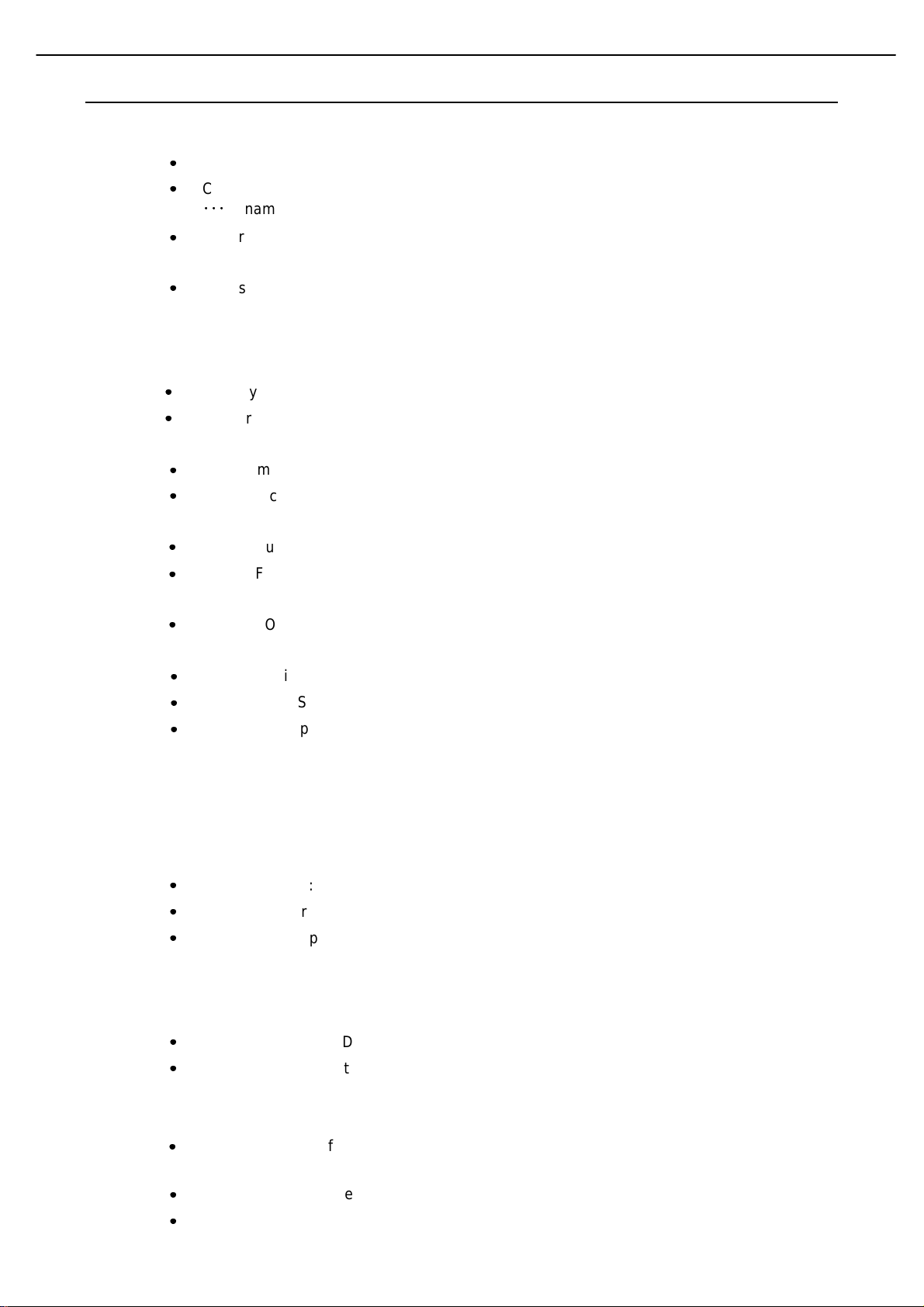

DETAILED FUNCTIONAL BLOCK DIAGRAM

AOUT

CVBS

SCART RGB

YPrPb

RGB

HS_IN1

VS_IN1

HS_IN2/TRI5

VS_IN2/TRI6

TRI1 TO

TRI4

SCL

SDA

AVLINK

CEC

RXA_5V / HPDA

RXB_5V / HPDB

RXC_5V / HPDC

RXD_5V / HPDD

DDCA_SDA / DDCA_SCL

DDCB_SDA / DDCB_SCL

DDCC_SDA / DDCC_SCL

DDCD_SDA / DDCD_SCL

RXA_C±

RXB_C±

RXC_C±

RXD_C±

RXA_0±

RXA_1±

RXA_2±

RXB_0±

RXB_1±

RXB_2±

RXC_0±

RXC_1±

RXC_2±

RXD_0±

RXD_1±

RXD_2±

HEAC_1±

HEAC_2±

SPDIF_IN

E1_TX±/E1_RX±

E2_TX±/E2_RX±

ANALOG FRONT END

YC

12-CHANNEL

INPUT

MATRIX

SYNC1

SYNC2

AND CLOCK GENERATION

2

C

AVLINK

CONTROLLER

CEC CONTROLLER

5V DETECT AND HPD

CONTROLLER

REPEATER

CONTROLLER

PLL

EQUALIZER SAMPLER

EQUALIZER SAMPLER

EQUALIZER SAMPLER

EQUALIZER SAMPLER

HDMI ETHERNET CHANNEL

AUDIO RETURN CHANNEL

CLAMP

CLAMP

CLAMP

CLAMP

LLC GENERATION

SYNC PROCESSING

TRI-LEVEL

SLICER

CONTROL INTERFACEI

EDID/

&

HDCP

EEPROM

HDCP

BLOCK

ADC0

ADC1

ADC2

ADC3

FASTSWITCHING

BLOCK + HDMI DECODE

12

12

12

12

HS/CS,VS/FIELD

CONTROL

AND DATA

DEEP COLOR

CONVERSION

4:2:2 TO 4:4:4

CONVERSION

+MUX

PROCESSOR

CONTROL

FILTER

PACKET

(A)

(B)

(C)

(D)

MUX

(A)

(B)

(C)

PACKET/

INFOFRAME

MEMORY

Figure 2. Detailed Functional Block Diagram

STANDARD DEFINITION PROCESSOR (SDP)

3D COMB

2D COMB

COMPONENT PROCESSOR

AND CGMS DETECTION

PROGRAMMABLE

DECODER

READBACK

TBC

VERTICAL

PEAKING

HORIZONTAL

PEAKING

CTI and LTI

DIGITAL PROCESSING BLOCK

SYNC SOURCE

AND POLARITY

DETECT

MACROVISION

DELAY

VSI

2

I

C

VIDEO DATA PROCESSOR

FINE CLAMP

ANCILLARY

DATA

FORMATTER

DIGITAL

CALIBRATION

DDR/SDR-SDRAM INTERFACE

STANDARD

AUTODECTION

MACROVISION

DETECTION

INTERLACE

TO PROGRESSIVE

CONVERSION

SYNC EXTRACT

(ESDP)

STANDARD

IDENTIFICATION

GAIN

CONTROL

FAST I

2

C

ACTIVE PEAK

AND HSYNC DEPTH

NOISE AND

INTERFACE

DECIMATION

FILTERS

COLOR SPACE

CONVERSION

FASTBLANK

OVERLAY

CONTROL

AV

CODE

INSERTION

CP CSC AND

DECIMATION

FILTERS

OFFSET

ADDER

INTERRUPT

CONTROLLER

AUDIO

PROCESSOR

12

P0 TO P11

12

P12 TO P23

12

P24 TO P35

VIDEO OUTPUT FORMATTER

LLC

HS/CS

VS/FIELD

DE

SYNC_OUT

TTX_SDA / TTX_SCL

INT1

INT2

AP0

AP1

AP2

AP3

AP4

AP5

SCLK

MCLK

AUDIO OUTPUT FORMATTER

Rev. PrC| Page 4 of 35

Page 4

AVR 2650 harman/kardon

124

ADV7844 PRELIMINARY

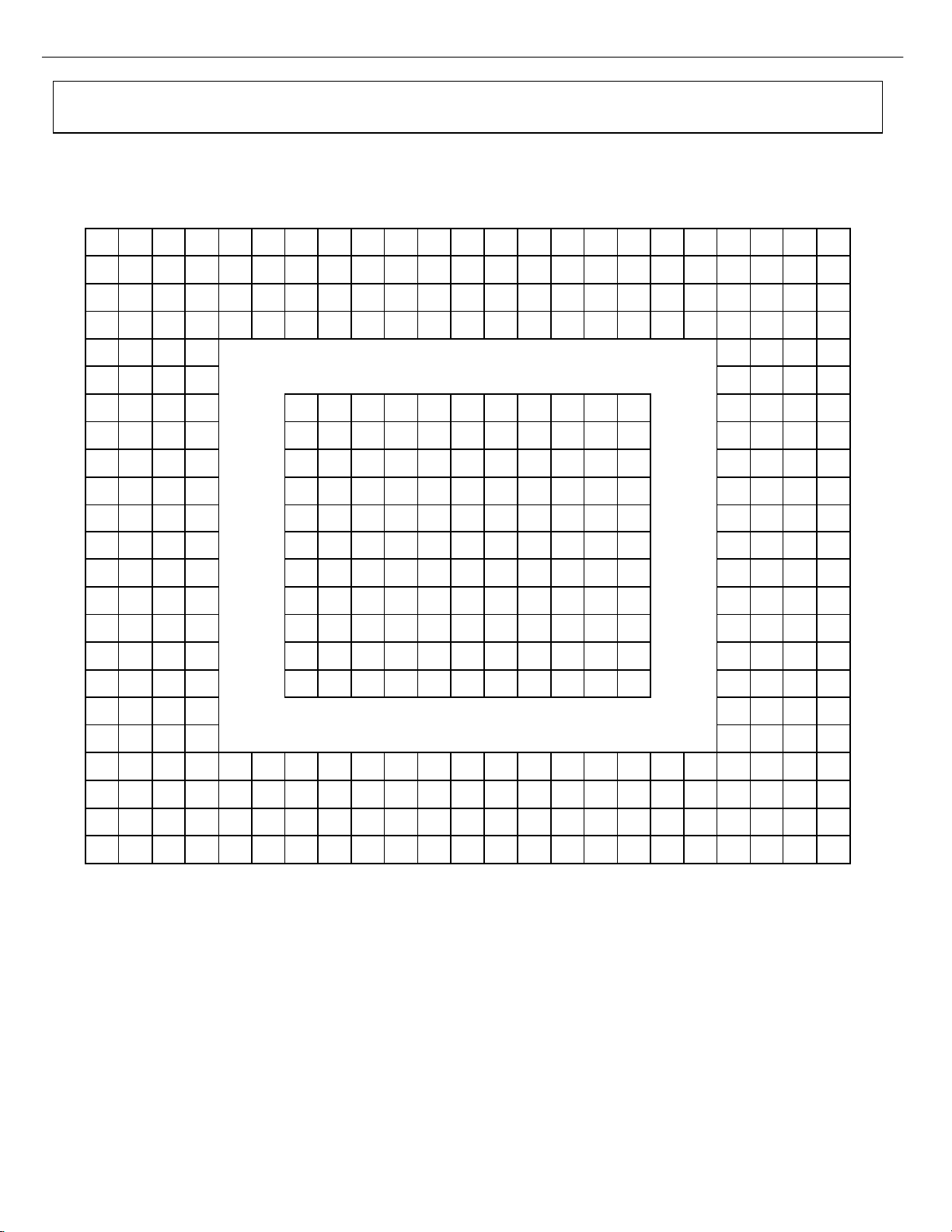

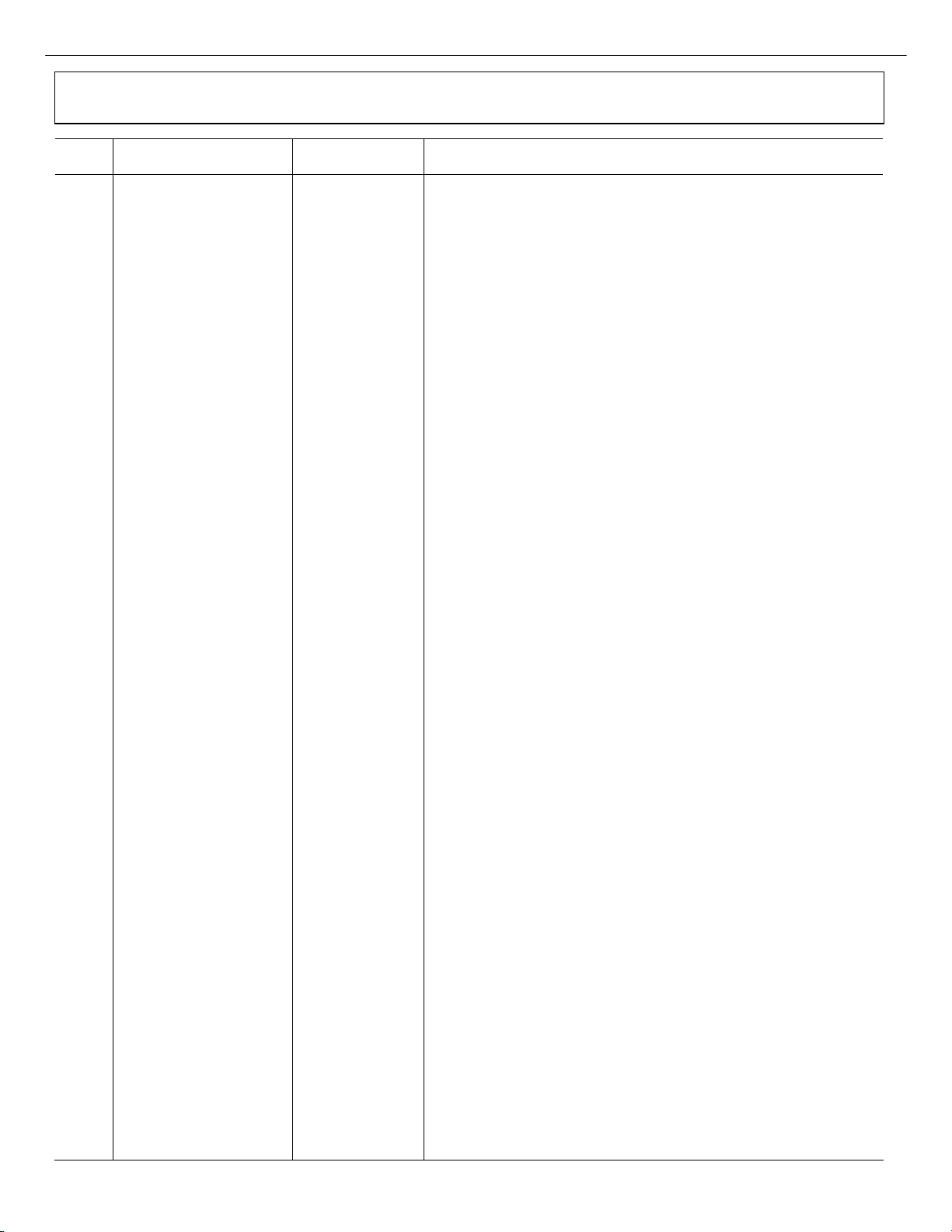

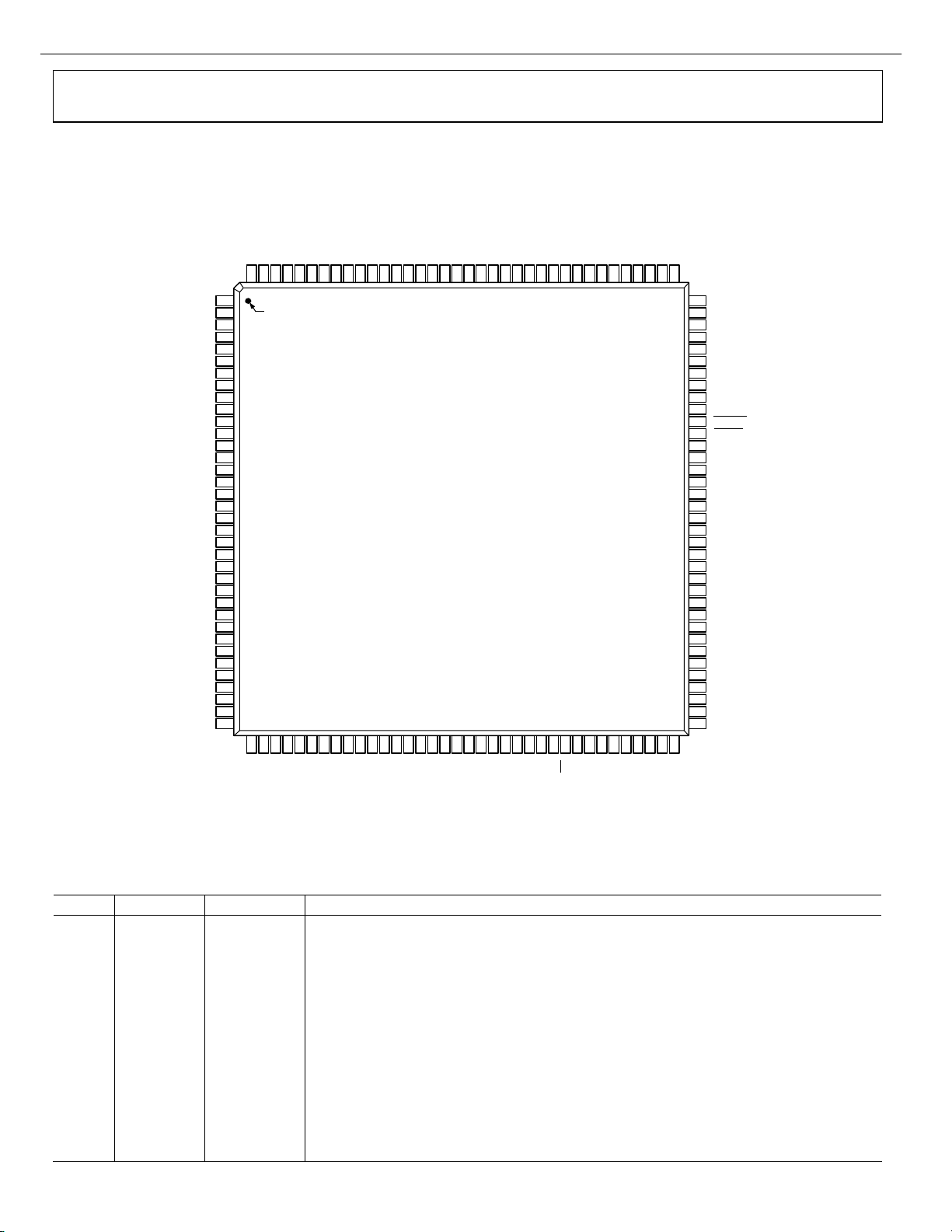

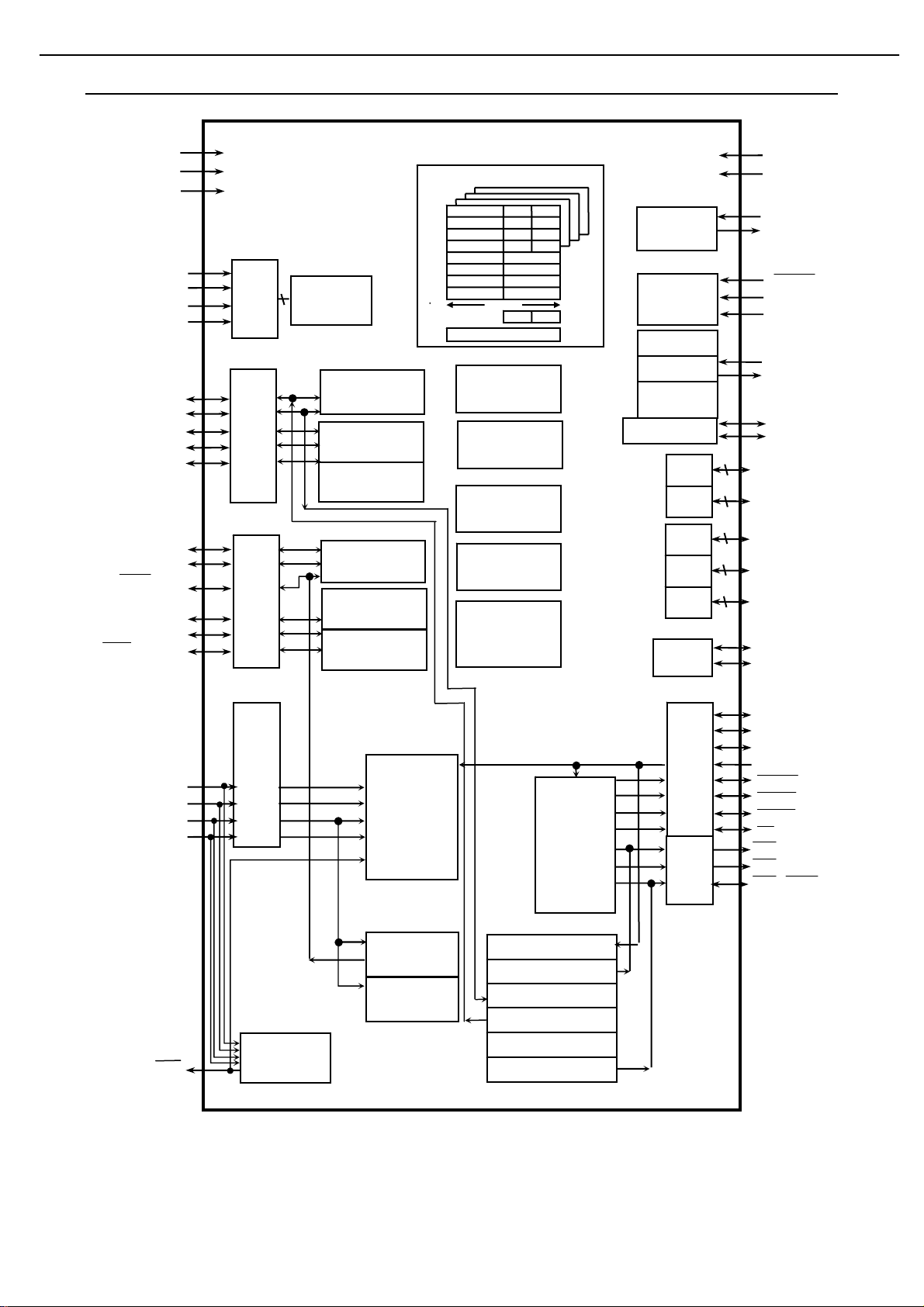

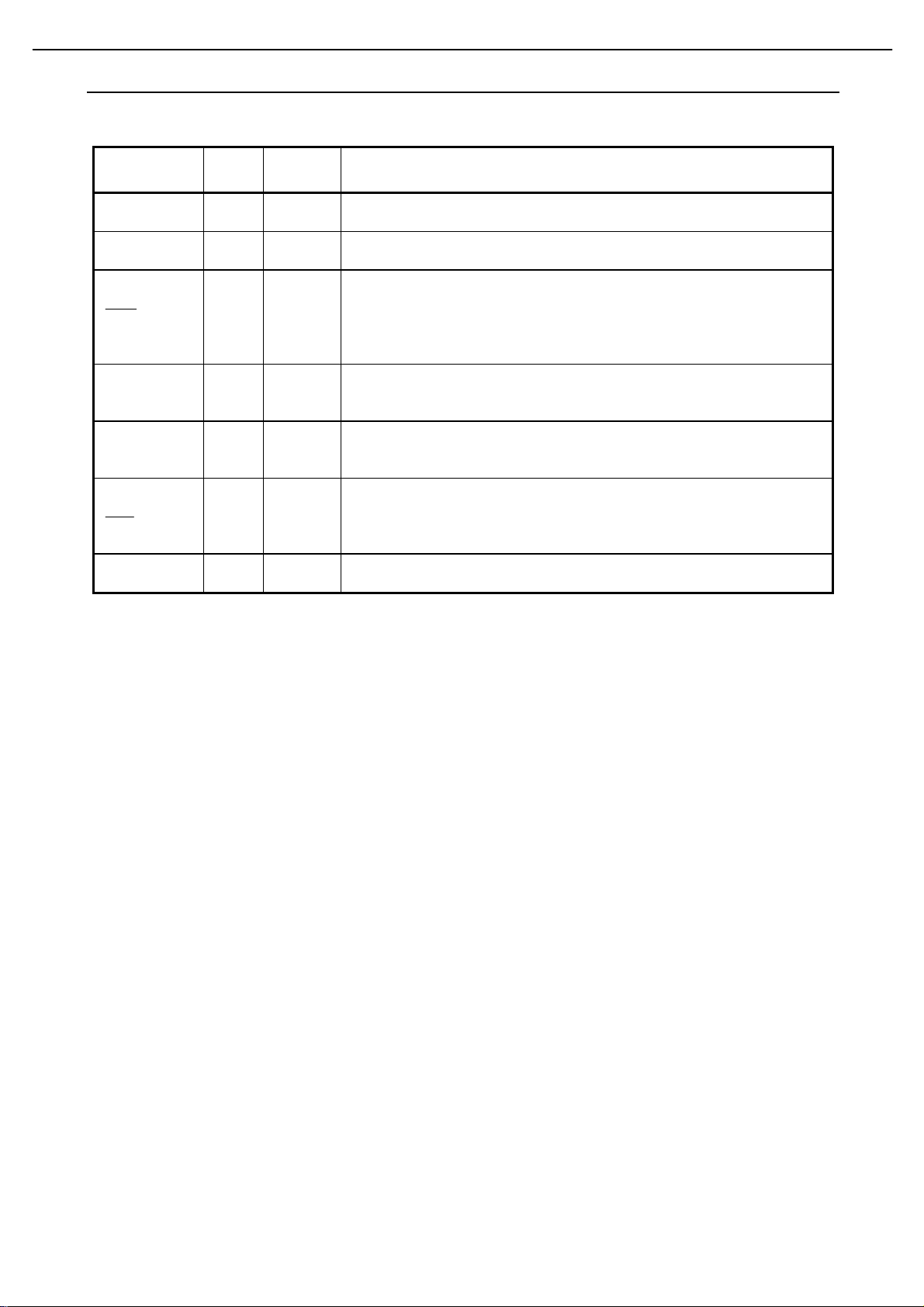

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1 2 3 4 5 6 7 8 9 1011121314151617181920212223

GND VS/FIELD E2_TX+ E2_RX+ TVDD RXD_2- RXD_1- RXD_0- RXD_C- HEAC_2- TVDD RXC_2- RXC_1- RXC_0- RXC_C- TVDD RXB_2- RXB_1- RXB_0- RXB_C- HEAC_1- GND

A

HS/CS FIELD/DE E2_TX- E2_RX- TVDD RXD_2+ RXD_1+ RXD_0+ RXD_C+ HEAC_2+ TVDD RXC_2+ RXC_1+ RXC_0+ RXC_C+ TVDD RXB_2+ RXB_1+ RXB_0+ RXB_C+ HEAC_1+ GND

B

P0 P1 E1_TX+ E1_RX+ TVDD PWRDN1 PWRDN2 HPA_D RXD_5V RXC_5V TVDD GND GND GND GND GND GND TVDD TVDD TVDD TVDD TVDD TVDD

C

P2 P3 E1_TX- E1_RX- TVDD

D

DVDDIO DVDDIO GND GND

E

P5 P4 EP_MISO EP_MOSI

F

SYNC_OUT

CEC HPA_C RXB_5V HPA_B TVDD RXA_5V HPA_A

DDCD_SDA DDCD_SCL DDCC_SDA DDCC _SCL

NC

NC

DDCB_SDA DDCB_SCL

RTERM

DDCA_SDA

DDCA_SCL

TVDD RXA_2+ RXA_2-

CVDD RXA_1+ RXA_1-

CVDD RXA_0+ RXA_0-

G

H

DDVCADS_AGVCVDDCVDDCVDDDNGDNGDNGDNGDNGDNGDNGDNGLCS_XTTADS_XTT8P9P

J

K

L

M

N

P

HS_IN2/TRI7

R

DNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDDV1TNI4TSET12P02P

VS_IN2/TRI8

T

U

NC NC

SYNC4 AIN10

A

B

C

D

E

F

-C_AXR+C_AXRDDVCLCS_AGVCVDDCVDDCVDDDNGDNG2TSET1TSETDNGDNGDNGDNGKCS_PESC_PE6P7P

G

H

DNGDNG3TSETDDVPDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNG0PAKLCM01P11P

J

PLATXNLATXDNGDDVPDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDDVKLCS5PA21P31P

K

DNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDDVDNGDNGOIDDVDOIDDVD

L

PFERNFERDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDDV3PA4PA41P51P

M

DDVADDVADDVADDVADNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDDV1PA2PA61P71P

N

21NIA11NIADDVADDVADNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDDVADSLCS91P81P

P

R

DNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDNGDDV2TNI5TSET32P22P

T

8NIA9NIA3IRT4IRTDNGDNGDNGDDVDDVDDVDDVDDVDDVDDVDDVOIDDVDOIDDVDOIDDVDOIDDVD

U

LLC P24 RESET AVLINK TRI1 TRI2 SYNC3 AIN7

V

P25 P26 SPDIF_IN AVDD AVDD AVDD AVDD

W

P27 P28 GND GND GND

Y

P29 P30 GND GND GND

AA

P31 P32 P34 GND DVDDIO

AB

GND P33 P35 GND DVDDIO

AC

NC

VDD_SDRAM

SDRAM_A11 SDRA M_A6 SDRAM _A2 SDRAM_CS

VDD_SDRAM

SDRAM_A9 SDRAM _A5 SDRAM _A1

NC

NC

SDRAM_A8 SDRAM _A4 SDRAM _A0

SDRAM_A7 SDRAM _A3 SDRAM_A10

SDRAM_LDQS

SDRAM_RAS SDRA M_ DQ 7

SDRAM_CAS VDD_SDRAM SDRAM_DQ4 SDRAM_DQ0 SDRAM_DQ13 SDRAM_DQ9 SDRAM_CKN VDD_SDRAM

SDRAM_BA1

SDRAM_BA0

SDRAM_WE

SDRAM_DQ6 SDRAM_DQ2 SDRAM_DQ15 SDRAM_DQ11 SDRAM_CKE VDD_SDRAM

GND

SDRAM_DQ5 SDRAM_DQ1 SDRAM_DQ12 SDRAM_DQ8

GND

VDD_ SDR AM SDR AM_D Q3 SDRAM_VREF SDRAM_DQ14 SDRAM_DQ10

SDRAM_CK

SDRAM_UDQS

GND AOUT NC AIN5 AIN6

VDD_SDRAM

GND NC NC SYNC2 AIN4

GND SYNC1

VDD_SDRAM

GNDAIN1AIN2AIN3GND

HS_IN1/TRI5

1 2 3 4 5 6 7 8 9 1011121314151617181920212223

Figure 7. Pin Configuration

VS_IN1/TRI6

GND

V

W

Y

AA

AB

AC

Rev. PrBC | Page 12 of 35

Page 5

AVR 2650 harman/kardon

125

PRELIMINARY ADV7844

Table 6. Function Descriptions

Pin

No.

A1 GND Ground Ground

A2 VS/FIELD Digital video

A3 E2_TX+ Digital output Digital Output Channel 2 True of Ethernet Interface

A4 E2_RX+ Digital input Digital Input Channel 2 True of Ethernet Interface

A5 TVDD Power Terminator Supply Voltage (3.3 V).

A6 RXD_2- HDMI input Digital Input Channel 2 Complement of Port D in the HDMI Interface.

A7 RXD_1- HDMI input Digital Input Channel 1 Complement of Port D in the HDMI Interface.

A8 RXD_0- HDMI input Digital Input Channel 0 Complement of Port D in the HDMI Interface.

A9 RXD_C- HDMI input Digital Input Clock Complement of Port D in the HDMI Interface.

A10 HEAC_2- HDMI input/output HDMI Ethernet and Audio Return Channel (HEAC) Complement Channel 2 in

A11 TVDD Power Terminator Supply Voltage (3.3 V).

A12 RXC_2- HDMI input Digital Input Channel 2 Complement of Port C in the HDMI Interface.

A13 RXC_1- HDMI input Digital Input Channel 1 Complement of Port C in the HDMI Interface.

A14 RXC_0- HDMI input Digital Input Channel 0 Complement of Port C in the HDMI Interface.

A15 RXC_C- HDMI input Digital Input Clock Complement of Port C in the HDMI Interface.

A16 NC No connect No Connect.

A17 TVDD Power Terminator Supply Voltage (3.3 V).

A18 RXB_2- HDMI input Digital Input Channel 2 Complement of Port B in the HDMI Interface.

A19 RXB_1- HDMI input Digital Input Channel 1 Complement of Port B in the HDMI Interface.

A20 RXB_0- HDMI input Digital Input Channel 0 Complement of Port B in the HDMI Interface.

A21 RXB_C- HDMI input Digital Input Clock Complement of Port B in the HDMI Interface.

A22 HEAC_1- HDMI input/output HDMI Ethernet and Audio Return Channel (HEAC) Complement Channel 1 in

A23 GND Ground Ground

B1 HS/CS Digital video

B2 FIELD/DE Miscellaneous

B3 E2_TX- Digital output Digital Output Channel 2 Complimentary of Ethernet Interface

B4 E2_RX- Digital input Digital Input Channel 2 Complimentary of Ethernet Interface

B5 TVDD Power Terminator Supply Voltage (3.3 V).

B6 RXD_2+ HDMI input Digital Input Channel 2 True of Port D in the HDMI Interface.

B7 RXD_1+ HDMI input Digital Input Channel 1 True of Port D in the HDMI Interface.

B8 RXD_0+ HDMI input Digital Input Channel 0 True of Port D in the HDMI Interface.

B9 RXD_C+ HDMI input Digital Input Clock True of Port D in the HDMI Interface.

B10 HEAC_2+ HDMI input/output HDMI Ethernet and Audio Return Channel (HEAC) True Channel 2 in HDMI

B11 TVDD Power Terminator Supply Voltage (3.3 V).

B12 RXC_2+ HDMI input Digital Input Channel 2 True Of Port C in the HDMI Interface.

B13 RXC_1+ HDMI input Digital Input Channel 1 True Of Port C in the HDMI Interface.

B14 RXC_0+ HDMI input Digital Input Channel 0 True Of Port C in the HDMI Interface.

B15 RXC_C+ HDMI input Digital Input Clock True Of Port C in the HDMI Interface.

B16 NC No Connect No Connect.

B17 TVDD Power Terminator Supply Voltage (3.3 V).

B18 RXB_2+ HDMI input Digital Input Channel 2 True of Port B in the HDMI Interface.

B19 RXB_1+ HDMI input Digital Input Channel 1 True of Port B in the HDMI Interface.

B20 RXB_0+ HDMI input Digital Input Channel 0 True of Port B in the HDMI Interface.

B21 RXB_C+ HDMI input Digital Input Clock True of Port B in the HDMI Interface.

Mnemonic Type Description

VS is a vertical synchronization output signal. FIELD is a field

output

output

digital

synchronization output signal in all interlaced video modes. VS or FIELD can

be configured for this pin.

HDMI Interface

HDMI Interface

HS is a horizontal synchronization output signal. CS (composite

synchronization) signal is a single signal containing both horizontal and

vertical synchronization pulses.

DE (data enable) is a signal that indicates active pixel data. FIELD is a field

synchronization output signal in all interlaced video modes. DE or FIELD can

be configured for this pin.

Interface

Rev. PrC| Page 13 of 35

Page 6

AVR 2650 harman/kardon

126

ADV7844 PRELIMINARY

Pin

No. Mnemonic Type Description

B22 HEAC_1+ HDMI input/output HDMI Ethernet and Audio Return Channel (HEAC ) True Channel 1 in HDMI

Interface

B23 GND Ground Ground

C1 P0 Digital video

output

C2 P1 Digital video

output

C3 E1_TX+ Digital output Digital Output Channel 1 True of Ethernet Interface

C4 E1_RX+ Digital input Digital Input Channel 1 True of Ethernet Interface

C5 TVDD Power Terminator Supply Voltage (3.3 V).

C6

C7

C8 HPA_D Miscellaneous

C9 RXD_5V HDMI input 5 V Detect Pin for Port D in the HDMI Interface.

C10 RXC_5V HDMI input 5 V Detect Pin for Port C in the HDMI Interface.

C11 TVDD Power Terminator Supply Voltage (3.3 V).

C12 GND Ground Ground

C13 GND Ground Ground

C14 GND Ground Ground

C15 GND Ground Ground

C16 GND Ground Ground

C17 GND Ground Ground

C18 TVDD Power Terminator Supply Voltage (3.3 V).

C19 TVDD Power Terminator Supply Voltage (3.3 V).

C20 TVDD Power Terminator Supply Voltage (3.3 V).

C21 TVDD Power Terminator Supply Voltage (3.3 V).

C22 TVDD Power Terminator Supply Voltage (3.3 V).

C23 TVDD Power Terminator Supply Voltage (3.3 V).

D1 P2 Digital video

D2 P3 Digital video

D3 E1_TX- Digital output Digital Output Channel 1 Complimentary of Ethernet Interface

D4 E1_RX- Digital input Digital Input Channel 1 Complimentary of Ethernet Interface

D5 TVDD Power Terminator Supply Voltage (3.3 V).

D6 SYNC_OUT Miscellaneous

D7 CEC Digital

D8 HPA_C Miscellaneous

D9 RXB_5V HDMI input 5 V Detect Pin for Port B in the HDMI Interface.

D10 HPA_B Miscellaneous

D11 TVDD Power Terminator Supply Voltage (3.3 V).

D12 RXA_5V HDMI input 5 V Detect Pin for Port A in the HDMI Interface.

D13 HPA_A Miscellaneous

D14 DDCD_SDA HDMI input HDCP Slave Serial Data Port D. DDCD_SDA is a 3.3 V input that is 5 V tolerant.

D15 DDCD_SCL HDMI input HDCP Slave Serial Clock Port D. DDCD_SCL is a 3.3 V input that is 5 V

D16 DDCC_SDA HDMI input HDCP Slave Serial Data Port C. DDCC_SDA is a 3.3 V input that is 5 V tolerant.

D17 DDCC_SCL HDMI input HDCP Slave Serial Clock Port C. DDCC_SCL is a 3.3 V input that is 5 V tolerant.

D18 RTERM Miscellaneous Sets Internal Termination Resistance. A 500 Ω resistor between this pin and

PWRDN1

PWRDN2

Miscellaneous

digital

Test pin This pin should be connected to the ground.

digital

output

output

digital

input/output

digital

digital

digital

Video Pixel Output Port.

Video Pixel Output Port.

Controls the Power-Up of the ADV7844. Should be connected to a digital 3.3

V I/O supply to power up the ADV7844.

Hot Plug Assert signal output for HDMI port D.

Video Pixel Output Port.

Video Pixel Output Port.

Sliced synchronization output.

Consumer Electronic Control Channel.

Hot Plug Assert signal output for HDMI port C.

Hot Plug Assert signal output for HDMI port B.

Hot Plug Assert signal output for HDMI port A.

tolerant.

Rev. PrBC | Page 14 of 35

Page 7

AVR 2650 harman/kardon

127

PRELIMINARY ADV7844

Pin

No. Mnemonic Type Description

analog GND should be used.

D19 DDCB_SDA HDMI input HDCP Slave Serial Data Port B. DDCB_SDA is a 3.3 V input that is 5 V tolerant.

D20 DDCB_SCL HDMI input HDCP Slave Serial Clock Port B. DDCB_SCL is a 3.3 V input that is 5 V tolerant.

D21 TVDD Power Terminator Supply Voltage (3.3 V).

D22 RXA_2+ HDMI input Digital Input Channel 2 True of Port A in the HDMI Interface.

D23 RXA_2- HDMI input Digital Input Channel 2 Complement of Port A in the HDMI Interface.

E1 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

E2 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

E3 GND Ground Ground

E4 GND Ground Ground

E20 DDCA_SDA HDMI input HDCP Slave Serial Data Port A. DDCA_SDA is a 3.3 V input that is 5 V tolerant.

E21 CVDD Power Comparator Supply Voltage (1.8 V).

E22 RXA_1+ HDMI input Digital Input Channel 1 True of Port A in the HDMI Interface.

E23 RXA_1- HDMI input Digital Input Channel 1 Complement of Port A in the HDMI Interface.

F1 P5 Digital video

output

F2 P4 Digital video

output

F3 EP_MISO Digital output SPI Master In/Slave Out for External EDID Interface.

F4 EP_MOSI Digital input SPI Master Out/Slave In for External EDID Interface.

F20 DDCA_SCL HDMI input HDCP Slave Serial Clock Port A. DDCA_SCL is a 3.3 V input that is 5 V

F21 CVDD Power Comparator Supply Voltage (1.8 V).

F22 RXA_0+ HDMI input Digital Input Channel 0 True of Port A in the HDMI Interface.

F23 RXA_0- HDMI input Digital Input Channel 0 Complement of Port A in the HDMI Interface.

G1 P7 Digital video

output

G2 P6 Digital video

output

G3

G4 EP_SCK Digital output SPI Clock for External EDID Interface.

G7 GND Ground Ground

G8 GND Ground Ground

G9 GND Ground Ground

G10 GND Ground Ground

G11 TEST1 Test Do Not Connect.

G12 TEST2 Test Do Not Connect.

G13 GND Ground Ground

G14 GND Ground Ground

G15 CVDD Power Comparator Supply Voltage (1.8 V).

G16 CVDD Power Comparator Supply Voltage (1.8 V).

G17 CVDD Power Comparator Supply Voltage (1.8 V).

G20 VGA_SCL Miscellaneous

G21 CVDD Power Comparator Supply Voltage (1.8 V).

G22 RXA_C+ HDMI input Digital Input Clock True of Port A in the HDMI Interface.

G23 RXA_C- HDMI input Digital Input Clock Complement of Port A in the HDMI Interface.

H1 P9 Digital video

H2 P8 Digital video

H3 TTX_SDA Miscellaneous

H4 TTX_SCL Miscellaneous

EP_CS

Digital output SPI Chip Select for External EDID Interface.

digital

output

output

digital

digital

Video Pixel Output Port.

Video Pixel Output Port.

tolerant.

Video Pixel Output Port.

Video Pixel Output Port.

DDC Port Serial Clock Input for VGA

Video Pixel Output Port.

Video Pixel Output Port.

I2C Port Serial Data Input/Output Pin. SDA is the data line for the teletext

port.

I2C Port Serial Clock Input. SCL is the clock line for the teletext port.

Rev. PrC| Page 15 of 35

Page 8

AVR 2650 harman/kardon

128

ADV7844 PRELIMINARY

Pin

No. Mnemonic Type Description

H7 GND Ground Ground

H8 GND Ground Ground

H9 GND Ground Ground

H10 GND Ground Ground

H11 GND Ground Ground

H12 GND Ground Ground

H13 GND Ground Ground

H14 GND Ground Ground

H15 CVDD Power Comparator Supply Voltage (1.8 V).

H16 CVDD Power Comparator Supply Voltage (1.8 V).

H17 CVDD Power Comparator Supply Voltage (1.8 V).

H20 VGA_SDA Miscellaneous

digital

H21 CVDD Power Comparator Supply Voltage (1.8 V).

H22 NC No Connect No Connect

H23 NC No Connect No Connect

J1 P11 Digital video

output

J2 P10 Digital video

output

J3 MCLK Miscellaneous Audio Master Clock Output.

J4 AP0 Miscellaneous Audio Output Pin. Pins AP0-AP5 can be configured to output SPDIF Digital

J7 GND Ground Ground

J8 GND Ground Ground

J9 GND Ground Ground

J10 GND Ground Ground

J11 GND Ground Ground

J12 GND Ground Ground

J13 GND Ground Ground

J14 GND Ground Ground

J15 GND Ground Ground

J16 GND Ground Ground

J17 GND Ground Ground

J20 PVDD Power PLL Supply Voltage (1.8 V).

J21 TEST3 Test Do Not Connect.

J22 GND Ground Ground

J23 GND Ground Ground

K1 P13 Digital video

output

K2 P12 Digital video

output

K3 AP5 Miscellaneous Audio Output Pin. Pins AP0-AP5 can be configured to output SPDIF Digital

K4 SCLK Miscellaneous

digital

K7 VDD Power Digital Core Supply Voltage (1.8 V).

K8 GND Ground Ground

K9 GND Ground Ground

K10 GND Ground Ground

K11 GND Ground Ground

K12 GND Ground Ground

DDC Port Data Clock Input for VGA

Video Pixel Output Port.

Video Pixel Output Port.

Audio Output (SPDIF), High Bit Rate (HBR), Direct Stream Digital (DSD),

Direct Stream Transfer (DST) or I2S.

Video Pixel Output Port.

Video Pixel Output Port.

Audio Output (SPDIF), High Bit Rate (HBR), Direct Stream Digital (DSD),

Direct Stream Transfer (DST) or I2S.

Audio Serial Clock Output.

Rev. PrBC | Page 16 of 35

Page 9

AVR 2650 harman/kardon

129

PRELIMINARY ADV7844

Pin

No. Mnemonic Type Description

K13 GND Ground Ground

K14 GND Ground Ground

K15 GND Ground Ground

K16 GND Ground Ground

K17 GND Ground Ground

K20 PVDD Power PLL Supply Voltage (1.8 V).

K21 GND Ground Ground

K22 XTALN Miscellaneous

analog

K23 XTALP Miscellaneous

analog

L1 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

L2 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

L3 GND Ground Ground

L4 GND Ground Ground

L7 VDD Power Digital Core Supply Voltage (1.8 V).

L8 GND Ground Ground

L9 GND Ground Ground

L10 GND Ground Ground

L11 GND Ground Ground

L12 GND Ground Ground

L13 GND Ground Ground

L14 GND Ground Ground

L15 GND Ground Ground

L16 GND Ground Ground

L17 GND Ground Ground

L20 GND Ground Ground

L21 GND Ground Ground

L22 GND Ground Ground

L23 GND Ground Ground

M1 P15 Digital video

output

M2 P14 Digital video

output

M3 AP4 Miscellaneous Audio Output Pin. Pins AP0-AP5 can be configured to output SPDIF Digital

M4 AP3 Miscellaneous Audio Output Pin. Pins AP0-AP5 can be configured to output SPDIF Digital

M7 VDD Power Digital Core Supply Voltage (1.8 V).

M8 GND Ground Ground

M9 GND Ground Ground

M10 GND Ground Ground

M11 GND Ground Ground

M12 GND Ground Ground

M13 GND Ground Ground

M14 GND Ground Ground

M15 GND Ground Ground

M16 GND Ground Ground

M17 GND Ground Ground

M20 GND Ground Ground

M21 GND Ground Ground

M22 REFN Miscellaneous Internal Voltage Reference Output.

Input Pin for 28.63636 MHz Crystal.

Crystal Input. Input pin for 28.63636 MHz Crystal or an External 1.8 V,

28.63636 MHz Clock Oscillator Source to Clock the ADV7844.

Video Pixel Output Port.

Video Pixel Output Port.

Audio Output (SPDIF), High Bit Rate (HBR), Direct Stream Digital (DSD),

Direct Stream Transfer (DST) or I2S.

Audio Output (SPDIF), High Bit Rate (HBR), Direct Stream Digital (DSD),

Direct Stream Transfer (DST) or I2S.

Rev. PrC| Page 17 of 35

Page 10

AVR 2650 harman/kardon

130

ADV7844 PRELIMINARY

Pin

No.

M23 REFP Miscellaneous

N1 P17 Digital video

N2 P16 Digital video

N3 AP2 Miscellaneous Audio Output Pin. Pins AP0-AP5 can be configured to output SPDIF Digital

N4 AP1 Miscellaneous Audio Output Pin. Pins AP0-AP5 can be configured to output SPDIF Digital

N7 VDD Power Digital Core Supply Voltage (1.8 V).

N8 GND Ground Ground

N9 GND Ground Ground

N10 GND Ground Ground

N11 GND Ground Ground

N12 GND Ground Ground

N13 GND Ground Ground

N14 GND Ground Ground

N15 GND Ground Ground

N16 GND Ground Ground

N17 GND Ground Ground

N20 AVDD Power Analog Supply Voltage (1.8 V).

N21 AVDD Power Analog Supply Voltage (1.8 V).

N22 AVDD Power Analog Supply Voltage (1.8 V).

N23 AVDD Power Analog Supply Voltage (1.8 V).

P1 P18 Digital video

P2 P19 Digital video

P3 SCL Miscellaneous

P4 SDA Miscellaneous

P7 VDD Power Digital Core Supply Voltage (1.8 V).

P8 GND Ground Ground

P9 GND Ground Ground

P10 GND Ground Ground

P11 GND Ground Ground

P12 GND Ground Ground

P13 GND Ground Ground

P14 GND Ground Ground

P15 GND Ground Ground

P16 GND Ground Ground

P17 GND Ground Ground

P20 AVDD Power Analog Supply Voltage (1.8 V).

P21 AVDD Power Analog Supply Voltage (1.8 V).

P22 AIN11 Analog video input Analog Video Input Channel.

P23 AIN12 Analog video input Analog Video Input Channel.

R1 P20 Digital video

R2 P21 Digital video

R3 TEST4 Test Do Not Connect.

Mnemonic Type Description

analog

Internal Voltage Reference Output.

analog

Video Pixel Output Port.

output

Video Pixel Output Port.

output

Audio Output (SPDIF), High Bit Rate (HBR), Direct Stream Digital (DSD),

Direct Stream Transfer (DST) or I2S.

Audio Output (SPDIF), High Bit Rate (HBR), Direct Stream Digital (DSD),

Direct Stream Transfer (DST) or I2S.

Video Pixel Output Port.

output

Video Pixel Output Port.

output

I2C Port Serial Clock Input. SCL is the clock line for the control port.

digital

I2C Port Serial Data Input/Output Pin. SDA is the data line for the control

digital

output

output

port.

Video Pixel Output Port.

Video Pixel Output Port.

Rev. PrBC | Page 18 of 35

Page 11

AVR 2650 harman/kardon

131

PRELIMINARY ADV7844

Pin

No. Mnemonic Type Description

R4 INT1 Miscellaneous

digital

R7 VDD Power Digital Core Supply Voltage (1.8 V).

R8 GND Ground Ground

R9 GND Ground Ground

R10 GND Ground Ground

R11 GND Ground Ground

R12 GND Ground Ground

R13 GND Ground Ground

R14 GND Ground Ground

R15 GND Ground Ground

R16 GND Ground Ground

R17 GND Ground Ground

R20 HS_IN2/TRI7 Miscellaneous

analog

R21 VS_IN2/TRI8 Miscellaneous

analog

R22 SYNC4 Miscellaneous

analog

R23 AIN10 Analog video input Analog Video Input Channel.

T1 P22 Digital video

output

T2 P23 Digital video

output

T3 TEST5 Test Do Not Connect.

T4 INT2 Miscellaneous

digital

T7 VDD Power Digital Core Supply Voltage (1.8 V).

T8 GND Ground Ground

T9 GND Ground Ground

T10 GND Ground Ground

T11 GND Ground Ground

T12 GND Ground Ground

T13 GND Ground Ground

T14 GND Ground Ground

T15 GND Ground Ground

T16 GND Ground Ground

T17 GND Ground Ground

T20 GND Ground Ground

T21 GND Ground Ground

T22 GND Ground Ground

T23 GND Ground Ground

U1 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

U2 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

U3 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

U4 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

U7 VDD Power Digital Core Supply Voltage (1.8 V).

U8 VDD Power Digital Core Supply Voltage (1.8 V).

U9 VDD Power Digital Core Supply Voltage (1.8 V).

U10 VDD Power Digital Core Supply Voltage (1.8 V).

Interrupt. This pin can be active low or active high. When status bits change,

this pin is triggered. The events that trigger an interrupt are under user

control.

HS on Graphics Port 2. The HS input signal is used for 5-wire timing mode.

This pin can also be used as a trilevel/bilevel input on the SCART or Dterminal connector. Result available via I2C.

VS on Graphics Port 2. The VS input signal is used for 5-wire timing mode.

This pin can also be used as a trilevel/bilevel input on the SCART or Dterminal connector. Result available via I

This is a synchronization on green or luma input (SOG/SOY) used in

embedded synchronization mode. User configurable.

Video Pixel Output Port.

Video Pixel Output Port.

Interrupt. This pin can be active low or active high. When status bits change,

this pin is triggered. The events that trigger an interrupt are under user

control.

2

C.

Rev. PrC| Page 19 of 35

Page 12

AVR 2650 harman/kardon

132

ADV7844 PRELIMINARY

Pin

No.

U11 VDD Power Digital Core Supply Voltage (1.8 V).

U12 VDD Power Digital Core Supply Voltage (1.8 V).

U13 VDD Power Digital Core Supply Voltage (1.8 V).

U14 VDD Power Digital Core Supply Voltage (1.8 V).

U15 GND Ground Ground

U16 GND Ground Ground

U17 GND Ground Ground

U20 TRI4 Miscellaneous

U21 TRI3 Miscellaneous

U22 AIN9 Analog video input Analog Video Input Channel.

U23 AIN8 Analog video input Analog Video Input Channel.

V1 LLC Digital video

V2 P24 Digital video

V3

V4 AVLINK Digital

V20 TRI1 Miscellaneous

V21 TRI2 Miscellaneous

V22 SYNC3 Miscellaneous

V23 AIN7 Analog video input Analog Video Input Channel.

W1 P25 Digital video

W2 P26 Digital video

W3 NC No connect No Connect.

W4 SPDIF_IN Miscellaneous

W20 AVDD Power Analog Supply Voltage (1.8 V).

W21 AVDD Power Analog Supply Voltage (1.8 V).

W22 AVDD Power Analog Supply Voltage (1.8 V).

W23 AVDD Power Analog Supply Voltage (1.8 V).

Y1 P27 Digital video

Y2 P28 Digital video

Y3 GND Ground Ground

Y4 GND Ground Ground

Y5 GND Ground Ground

Y6 VDD_SDRAM Power External Memory Interface Digital Input/Output Supply (DDR 2.5 V or SDR

Y7 SDRAM_A11 SDRAM interface Address Output. Interface to external RAM address lines.

Y8 SDRAM_A6 SDRAM interface Address Output. Interface to external RAM address lines.

Y9 SDRAM_A2 SDRAM interface Address Output. Interface to external RAM address lines.

Y10

Y11 SDRAM_LDQS SDRAM interface Lower Data Strobe Pin. Data strobe pins are used for the RAM interface. This

Y12 GND Ground Ground

Mnemonic Type Description

Trilevel/Bilevel Input on the SCART or D-Terminal Connector. Result available

RESET

SDRAM_CS

analog

analog

output

output

Miscellaneous

digital

input/output

analog

analog

analog

output

output

digital

output

output

SDRAM interface

via I2C.

Trilevel/Bilevel Input on the SCART or D-Terminal Connector. Result available

via I2C.

Line-Locked Output Clock for the Pixel Data (Range is 13.5 MHz to 170 MHz).

Video Pixel Output Port.

System Reset Input. Active low. A minimum low reset pulse width of 5 ms is

required to reset the ADV7844 circuitry.

Digital SCART Control Channel.

Trilevel/Bilevel Input on the SCART or D-Terminal Connector. Result available

via I2C.

Trilevel/Bilevel Input on the SCART or D-Terminal Connector. Result available

via I2C.

This is a synchronization on green or luma input (SOG/SOY) used in

embedded synchronization mode. User configurable.

Video Pixel Output Port.

Video Pixel Output Port.

Audio Clock Input Pin for SPDIF

Video Pixel Output Port.

Video Pixel Output Port.

3.3 V).

Chip Select.

RAM. One of four command signals to the external SDRAM.

is an output with read data and an input with write data. It is edge aligned

with write data and centered in read data. SDRAM_ LDQS corresponds to

the data on SDRAM_DQ0 to SDRAM_

Rev. PrBC | Page 20 of 35

SDRAM_CS

enables and disables the command decoder on the

Page 13

AVR 2650 harman/kardon

133

PRELIMINARY ADV7844

Pin

No.

Y13 SDRAM_DQ6 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

Y14 SDRAM_DQ2 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

Y15 SDRAM_DQ15 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

Y16 SDRAM_DQ11 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

Y17 SDRAM_CKE SDRAM interface Clock Enable. This pin acts as an enable to the clock signals of the external

Y18 VDD_SDRAM Power External Memory Interface Digital Input/Output Supply (DDR 2.5 V or SDR

Y19 GND Ground Ground

Y20 AOUT Analog monitor

Y21 NC No connect No Connect.

Y22 AIN5 Analog video input Analog Video Input Channel.

Y23 AIN6 Analog video input Analog Video Input Channel.

AA1 P29 Digital video

AA2 P30 Digital video

AA3 GND Ground Ground

AA4 GND Ground Ground

AA5 GND Ground Ground

AA6 VDD_SDRAM Power External Memory Interface Digital Input/Output Supply (DDR 2.5 V or SDR

AA7 SDRAM_A9 SDRAM interface Address Output. Interface to external RAM address lines.

AA8 SDRAM_A5 SDRAM interface Address Output. Interface to external RAM address lines.

AA9 SDRAM_A1 SDRAM interface Address Output. Interface to external RAM address lines.

AA10

AA11 SDRAM_DQ7 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AA12 GND Ground Ground

AA13 SDRAM_DQ5 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AA14 SDRAM_DQ1 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AA15 SDRAM_DQ12 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AA16 SDRAM_DQ8 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AA17 SDRAM_CK SDRAM interface Differential Clock Output. All address and control output signals to the RAM

AA18 VDD_SDRAM Power External Memory Interface Digital Input/Output Supply (DDR 2.5 V or SDR

AA19 GND Ground Ground

AA20 NC No connect No Connect.

AA21 NC No connect No Connect.

AA22 SYNC2 Miscellaneous

AA23 AIN4 Analog video input Analog Video Input Channel.

AB1 P31 Digital video

AB2 P32 Digital video

AB3 P34 Digital video

AB4 NC No connect No Connect.

AB5 GND Ground Ground

AB6 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

AB7 SDRAM_A8 SDRAM interface Address Output. Interface to external RAM address lines.

AB8 SDRAM_A4 SDRAM interface Address Output. Interface to external RAM address lines.

Mnemonic Type Description

RAM.

3.3 V).

Analog Monitor Output.

output

Video Pixel Output Port.

output

Video Pixel Output Port.

output

3.3 V).

SDRAM_RAS

SDRAM interface Row Address Select Command Signal. One of four command signals to the

external SDRAM.

should be sampled on the positive edge of SDRAM_CK and on the negative

analog

output

output

output

edge of

3.3 V).

This is a synchronization on green or luma input (SOG/SOY) used in

embedded synchronization mode. User configurable.

Video Pixel Output Port.

Video Pixel Output Port.

Video Pixel Output Port.

SDRAM_CK

.

Rev. PrC| Page 21 of 35

Page 14

AVR 2650 harman/kardon

134

ADV7844 PRELIMINARY

Pin

No.

AB9 SDRAM_A0 SDRAM interface Address Output. Interface to external RAM address lines.

AB10 SDRAM_BA1 SDRAM interface Bank Address Output. Interface to external RAM bank address lines.

AB11

AB12 VDD_SDRAM Power External Memory Interface Digital Input/Output Supply (DDR 2.5 V or SDR

AB13 SDRAM_DQ4 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AB14 SDRAM_DQ0 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AB15 SDRAM_DQ13 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AB16 SDRAM_DQ9 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AB17

AB18 VDD_SDRAM Power External Memory Interface Digital Input/Output Supply (DDR 2.5 V or SDR

AB19 GND Ground Ground

AB20 SYNC1 Miscellaneous

AB21 HS_IN1/TRI5 Miscellaneous

AB22 VS_IN1/TRI6 Miscellaneous

AB23 GND Ground Ground

AC1 GND Ground Ground

AC2 P33 Digital video

AC3 P35 Digital video

AC4 NC No connect No Connect.

AC5 GND Ground Ground

AC6 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

AC7 SDRAM_A7 SDRAM interface Address Output. Interface to external RAM address lines.

AC8 SDRAM_A3 SDRAM interface Address Output. Interface to external RAM address lines.

AC9 SDRAM_A10 SDRAM interface Address Output. Interface to external RAM address lines.

AC10 SDRAM_BA0 SDRAM interface Bank Address Output. Interface to external RAM bank address lines.

AC11

AC12 VDD_SDRAM Power External Memory Interface Digital Input/Output Supply (DDR 2.5 V or SDR

AC13 SDRAM_DQ3 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AC14 SDRAM_VREF SDRAM interface 1.25 V Reference for DDR SDRAM Interface or 1.65 V for SDR.

AC15 SDRAM_DQ14 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AC16 SDRAM_DQ10 SDRAM interface Data Bus. Interface to external RAM 16-bit data bus.

AC17 SDRAM_UDQS SDRAM interface Upper Data Strobe Pin. Data strobe pins for the RAM interface. This is an

AC18 VDD_SDRAM Power External Memory Interface Digital Input/Output Supply (DDR 2.5 V or SDR

AC19 GND Ground Ground

AC20 AIN1 Analog video input Analog Video Input Channel.

AC21 AIN2 Analog video input Analog Video Input Channel.

AC22 AIN3 Analog video input Analog Video Input Channel.

AC23 GND Ground Ground

Mnemonic Type Description

SDRAM_CAS

SDRAM_CK

SDRAM_WE

SDRAM interface Column Address Select Command Signal. One of four command signals to

the external SDRAM.

3.3 V).

SDRAM interface Differential Clock Output. All address and control output signals to the RAM

should be sampled on the positive edge of SDRAM_CK and on the negative

edge of

3.3 V).

This is a synchronization on green or luma input (SOG/SOY) used in

analog

analog

analog

output

output

SDRAM interface Write Enable Output Command Signal. One of four command signals to the

embedded synchronization mode. User configurable.

HS on Graphics Port 1. The HS input signal is used for 5-wire timing mode.

HS_IN1/TRI5 is a 3.3 V input that is 5 V tolerant.

Vertical Synchronization Input Signal. Used for 5-wire timing mode.

Video Pixel Output Port.

Video Pixel Output Port.

external SDRAM.

3.3 V).

output with read data and an input with write data. It is edge aligned with

write data and centered in read data. UDQS corresponds to the data on DQ8

to DQ16.

3.3 V).

SDRAM_CK

.

Rev. PrBC | Page 22 of 35

Page 15

AVR 2650 harman/kardon

135

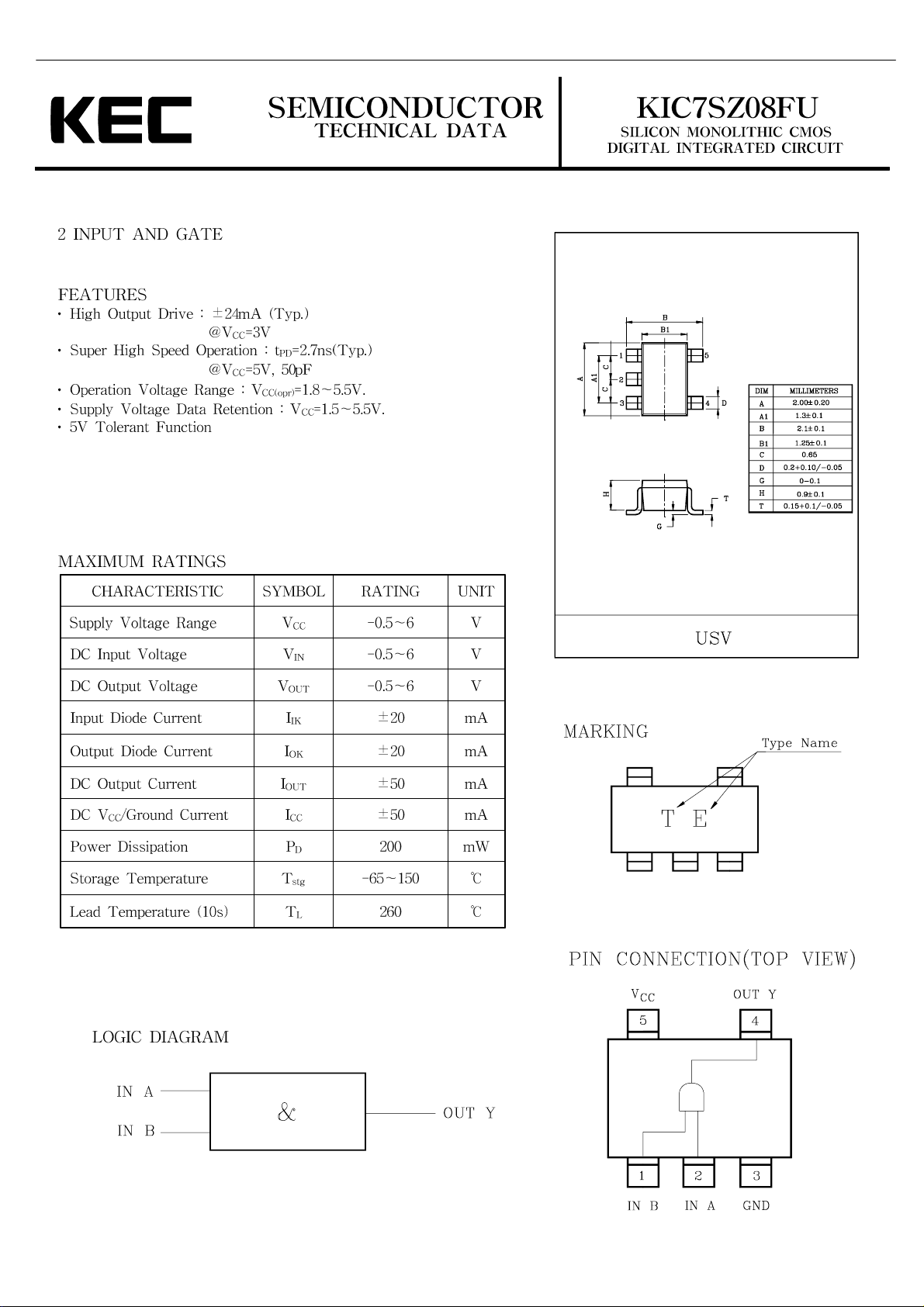

HDMI 1.4 Mux with

ADI Confidential

FEATURES

4-input, 1-output HDMI mux

HDMI 1.4a support: 3D TV formats, content type bits,

CEC 1.4-compatible

Xpressview fast switching on all HDMI input ports

High-bandwidth digital content protection (HDCP 1.4a)

HDCP repeater support

225 MHz HDMI Rx and Tx support 36-/30-/24-bit Deep Color

Ultralow jitter digital PLL (100% deskew)

Quad HDMI Rx input

Adaptive equalizer for cable lengths up to 30 meters

Internal extended display identification data (EDID) RAM

EDID replication (512 bytes per port)

EDID with HDMI cable 5 V power support

5 V detect inputs

Hot plug assertion control pins

Single HDMI Tx output: EDID data extraction and hot plug

detect (HPD) input

HDMI 1.4a audio pass-through support

2

I

S, DSD, and HBR, including Dolby TrueHD and

DTS-HD master audio

General

Interrupt controller with 3 interrupt outputs

Software libraries, driver, and application available

2-layer PCB design supported

144-lead, 20 mm × 20 mm LQFP package

APPLICATIONS

Port expansion for Analog Devices HDMI decoders

Audio video receivers (AVRs)

Home theater in a box (HTiB)

Sound bar with HDMI repeater support

Flat panel TVs

Other repeater applications

GENERAL DESCRIPTION

The ADV3014 is a high performance, four-input, one-output,

High-Definition Multimedia Interface (HDMI™) switch that

integrates HDMI 1.4a receiver and transmitter functions onto

one chip. It supports all HDCP repeater functions through fully

tested Analog Devices, Inc., repeater software libraries and drivers.

The ADV3014 incorporates Xpressview™ fast switching on all

Xpressview Fast Switching

ADV3014

FUNCTIONAL BLOCK DIAGRAM

SYNC

AND DDC

AND DDC

AND DDC

AND DDC

MEASUREMENT

PROCESSOR

Xpressview™ FAST

SWITCHING RECEIVER

PACKET

PROCESSOR

INFOFRAME/

PACKET MEMORY

Figure 1.

HDCP

ENGINE

ENCRYPTION

ADV3014

RX0±

RX1±

RX2±

AND TMDS

RXC±

HDMI ENCODER

INT1

INT2

INT_TX

INTERRUPT

CONTROLLER

09068-001

RXA_0±

RXA_1±

RXA_2±

RXA_C±

RXB_0±

RXB_1±

RXB_2±

RXB_C±

RXC_0±

RXC_1±

RXC_2±

RXC_C±

RXD_0±

RXD_1±

RXD_2±

RXD_C±

PWRDN

RESET

CEC

EQ

TMDS

EQ

TMDS

EQ

TMDS

EQ

TMDS

HDCP

DECRYPTION ENGI NE

HDCP KEYS

CEC CONTRO L L ER

GLOBAL CONTROLS

input HDMI ports. Using the Analog Devices hardware-based

HDCP engine that minimizes software overhead, Xpressview

technology allows fast switching between any HDMI input

ports in less than 1 second.

The ADV3014 supports all mandatory HDMI 1.4a 3D TV formats

in addition to all HD TV formats up to 1080p 36-bit Deep Color.

The ADV3014 also features an integrated HDMI 1.4 CEC controller, which supports capability discovery and control (CDC).

The HDMI receiver supports programmable/adaptive equalization that ensures robust operation of the interface at cable lengths

of up to 30 meters.

The ADV3014 offers integrated control of hot plug circuits,

sensing of 5 V input signals and on-board EDID controls with

EDID replication and power-down mode EDID.

The ADV3014 supports pass-through of all HDMI 1.4a audio

formats including I

2

S, DSD, and HBR formats such as Dolby®

TrueHD and DTS-HD® master audio.

Fabricated in an advanced CMOS process, the ADV3014 is

provided in a space-saving, 144-lead, 20 mm × 20 mm LQFP

surface-mount, Pb-free package. It is specified over the 0°C to

70°C temperature range.

Page 16

AVR 2650 harman/kardon

136

ADI Confidential ADV3014

DETAILED FUNCTIONAL BLOCK DIAGRAM

XTAL

XTAL1

RXA_C+/RXA_C–

RXB_C+/RXB_C–

RXC_C+/RXC_C–

RXD_C+/RXD_C–

RXA_0+/RXA_0–

RXA_1+/RXA_1–

RXA_2+/RXA_2–

RXB_0+/RXB_0–

RXB_1+/RXB_1–

RXB_2+/RXB_2–

RXC_0+/RXC_0–

RXC_1+/RXC_1–

RXC_2+/RXC_2–

RXD_0+/RXD_0–

RXD_1+/RXD_1–

RXD_2+/RXD_2–

CEC

5V_DETA

5V_DETB

5V_DETC

5V_DETD

HP_CTRLA

HP_CTRLB

HP_CTRLC

HP_CTRLD

EP_MISO

EP_MOSI

EP_CS

EP_SCK

DDCA_SDA

DDCA_SCL

DDCB_SDA

DDCB_SCL

DDCC_SDA

DDCC_SCL

DDCD_SDA

DDCD_SCL

EQUALIZER

EQUALIZER

EQUALIZER

EQUALIZER

CONTROLLER

CONTROLLER

SPI MASTER/

RX

PLL

SAMPLER

SAMPLER

SAMPLER

SAMPLER

CEC

5V DETECT

RX HPD

SLAVE

RX EDID/

REPEATER

CONTROLLER

VIDEO/AUDIO

CLOCK

GENERATION

XPRESSVIEW™

FAST SWITCHING

RECEIVER

PROCESSOR

+

BACKGROUND

MEASUREMENT

HDCP

DECRYPTION

ENGINE

HDCP KEYS

EDID

RAM

VIDEO DATA

DE

VS

HS

AUDIO DATA

MEASUREMENT

SYNC

PACKET

PROCESSOR

INFOFRAME

PACKET

MEMORY

HDCP

ENCRYPTION

TX

PLL

CH0

CH1

HDMI

ENGINE

CH2

ENCODER

BUFFER

EDID/HDCP

TXC+/TXC–

TX0+/TX0–

TX1+/TX1–

TX2+/TX2–

SERIALIZER

TMDS DRIV ERS

HP_TX

TX HPD

CONTROLLER

TXDDC_SDA

TXDDC_SCL

TX

EDID/HDCP

CONTROLLER

INT1

INT2

INT_TX

INTERRUPT

CONTROLLER

PWRDN

RESET

SCL

SDATA

ALSB

CS

GLOBAL

CONTROLS

2

I

C

CONTROLLER

ADV3014

09068-001

Figure 2. Detailed Functional Block Diagram

Rev. Sp0 | Page 3 of 16

Page 17

A

A

AVR 2650 harman/kardon

137

ADV3014 ADI Confidential

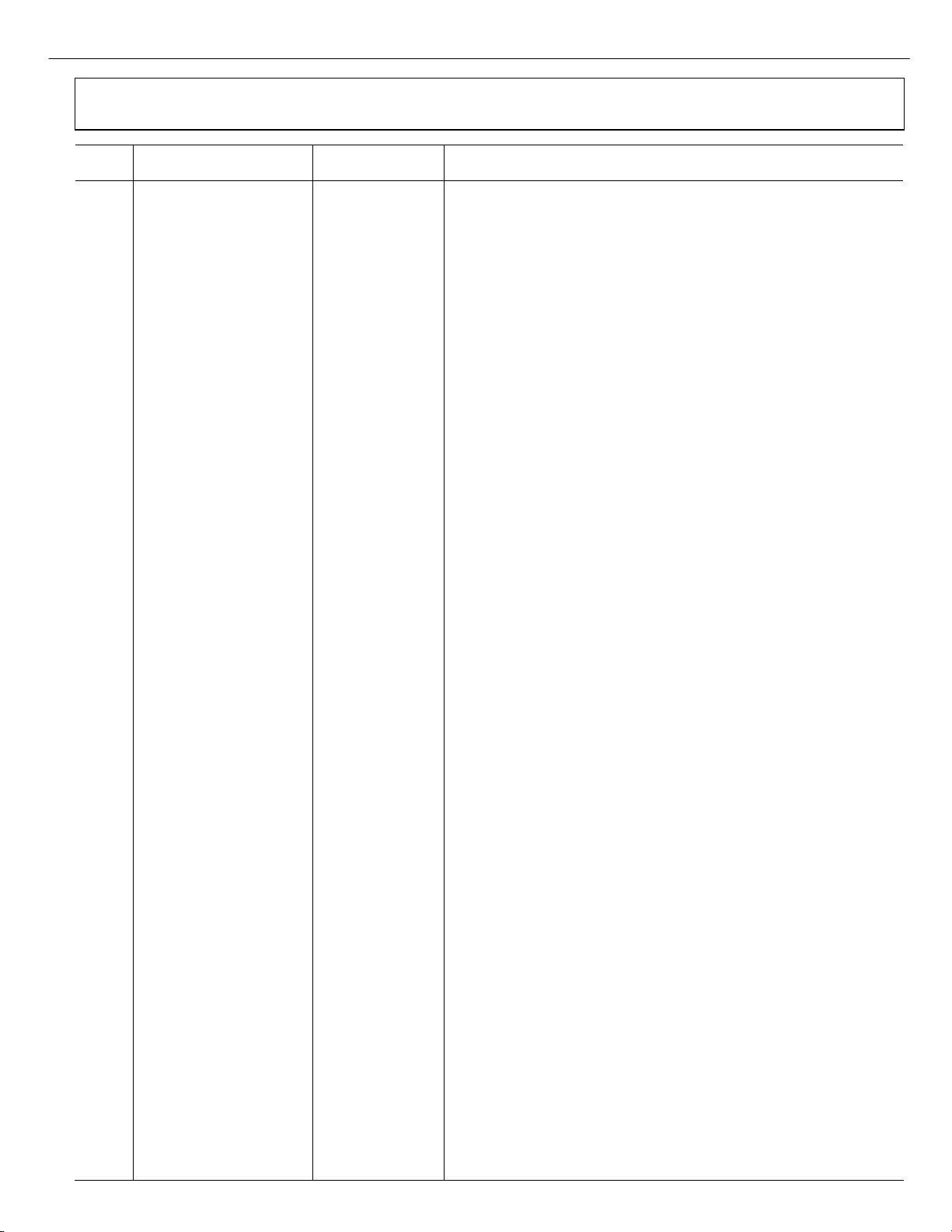

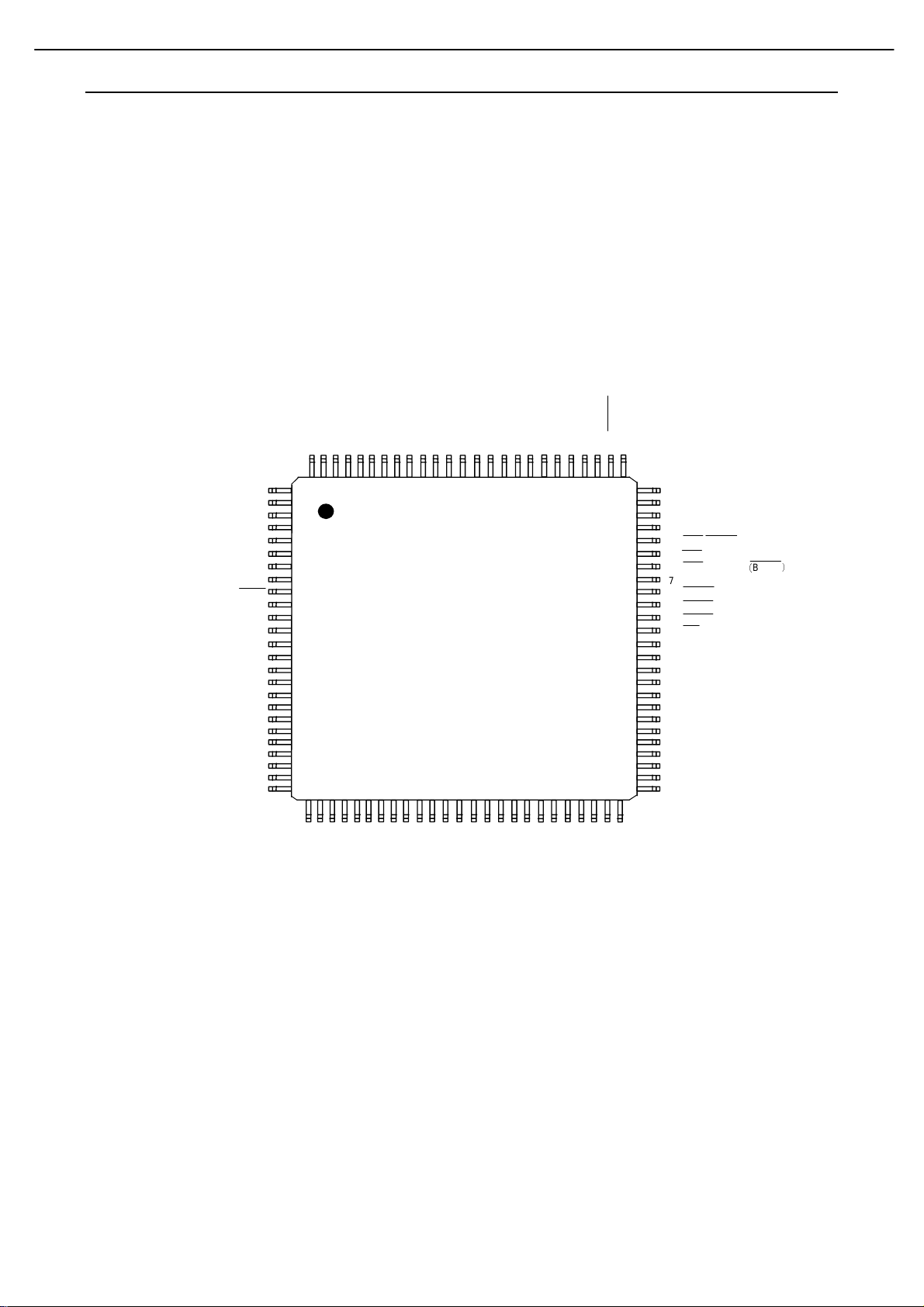

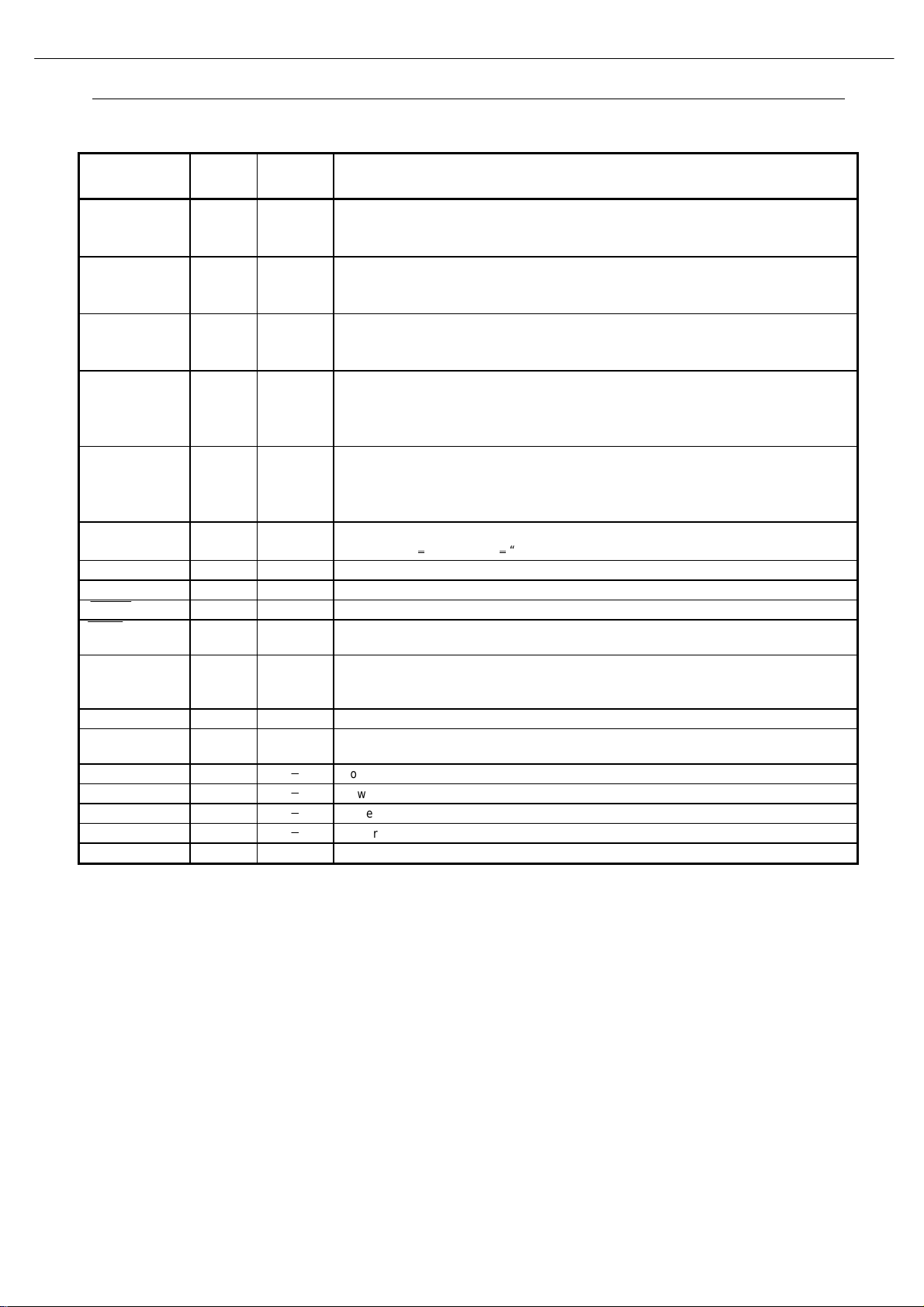

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

5V_DETC

HP_CTRLC

RXB_2+

RXB_2–

TVDD

RXB_1+

RXB_1–

CGND

RXB_0+

RXB_0–

TVDD

RXB_C+

RXB_C–

CGND

CVDD

DDCB_SCL

DDCB_SDA

DVDD

DGND

5V_DETB

HP_CTRLB

RXA_2+

RXA_2–

TVDD

RXA_1+

RXA_1–

CGND

RXA_0+

RXA_0–

TVDD

RXA_C+

RXA_C–

CGND

CVDD

DDCC_SDA

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

CVDD

CGND

TVDD

CGND

TVDD

DGND

DVDD

CVDD

CGND

TVDD

CGND

TVDD

CVDD

CGND

1

PIN 1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

404142434445464748495051525354555657585960616263646566676869707172

TXC–

TXAVDD

TXC+

TXGND

TEST0

HP_TX

TXPGND

TXPLVDD

TXPLGND

XDDC_SD

EXT_SWING

TXDDC_SCL

TX0–

TXGND

ADV3014

TOP VIEW

(Not to S cale)

TX1–

TX0+

TX1+

TXGND

TXAVDD

DGND

DVDD

CS

ALSB

EP_SCK

TEST1

EP_CS

EP_MOSI

EP_MISO

CEC

TX2–

TX2+

TXGND

DDCC_SCL

RXC_C–

RXC_C+

RXC_0–

RXC_0+

RXC_1–

RXC_1+

RXC_2–

RXC_2+

HP_CTRLD

5V_DETD

DDCD_SD

DDCD_SCL

RXD_C–

RXD_C+

RXD_0–

RXD_0+

RXD_1–

RXD_1+

RXD_2–

RXD_2+

TXPVDD

Figure 4. Pin Configuration

DDCA_SCL

109

110

111

112

108

DDCA_SDA

107

RTERM

106

5V_DETA

105

HP_CTRLA

104

PGND

103

PVDD

102

XTAL1

101

XTAL

100

PVDD

99

PGND

98

PWRDN

97

RESET

96

TEST16

95

TEST15

94

TEST14

93

DVDD

92

DGND

91

TEST13

90

TEST12

89

TEST11

88

TEST10

87

TEST9

86

DVDDIO

85

DGNDIO

84

INT_TX

83

INT2

82

INT1

81

DVDD

80

DGND

79

SCL

78

SDATA

77

TEST8

76

TEST7

75

TEST6

74

TEST5

73

DVDDIO

TEST2

TEST3

TEST4

DGNDIO

9068-002

Table 5: Pin Function Descriptions

Pin No. Mnemonic Type Description

1 DDCC_SCL Digital input HDCP Slave Serial Clock Port C. DDCC_SCL is a 3.3 V input that is 5 V tolerant.

2 CVDD Power Receiver Comparator Supply Voltage (1.8 V).

3 CGND Ground TVDD and CVDD Ground.

4 RXC_C− HDMI input Digital Input Clock Complement of Port C in the HDMI Interface.

5 RXC_C+ HDMI input Digital Input Clock True of Port C in the HDMI Interface.

6 TVDD Power Receiver Terminator Supply Voltage (3.3 V).

7 RXC_0− HDMI input Digital Input Channel 0 Complement of Port C in the HDMI Interface.

8 RXC_0+ HDMI input Digital Input Channel 0 True of Port C in the HDMI Interface.

9 CGND Ground TVDD and CVDD Ground.

10 RXC_1− HDMI input Digital Input Channel 1 Complement of Port C in the HDMI Interface.

11 RXC_1+ HDMI input Digital Input Channel 1 True of Port C in the HDMI Interface.

12 TVDD Power Receiver Terminator Supply Voltage (3.3 V).

13 RXC_2− HDMI input Digital Input Channel 2 Complement of Port C in the HDMI Interface.

Rev. Sp0 | Page 8 of 16

Page 18

AVR 2650 harman/kardon

138

ADI Confidential ADV3014

Pin No. Mnemonic Type Description

14 RXC_2+ HDMI input Digital Input Channel 2 True of Port C in the HDMI Interface.

15 HP_CTRLD Digital output Hot Plug Control Output for Port D. This pin is 5 V tolerant.

16 5V_DETD HDMI input 5 V Detect Pin for Port D in the HDMI Interface. This pin is 5 V tolerant.

17 DGND Ground DVDD Ground.

18 DVDD Power Digital Supply Voltage (1.8 V).

19 DDCD_SDA Digital I/O HDCP Slave Serial Data Port D. DDCD_SDA is a 3.3 V input that is 5 V tolerant.

20 DDCD_SCL Digital Input HDCP Slave Serial Clock Port D. DDCD_SCL is a 3.3 V input that is 5 V tolerant.

21 CVDD Power Comparator Supply Voltage (1.8 V).

22 CGND Ground TVDD and CVDD Ground.

23 RXD_C− HDMI input Digital Input Clock Complement of Port D in the HDMI Interface.

24 RXD_C+ HDMI input Digital Input Clock True of Port D in the HDMI Interface.

25 TVDD Power Terminator Supply Voltage (3.3 V).

26 RXD_0- HDMI input Digital Input Channel 0 Complement of Port D in the HDMI Interface.

27 RXD_0+ HDMI input Digital Input Channel 0 True of Port D in the HDMI Interface.

28 CGND Ground TVDD and CVDD Ground.

29 RXD_1− HDMI input Digital Input Channel 1 Complement of Port D in the HDMI Interface.

30 RXD_1+ HDMI input Digital Input Channel 1 True of Port D in the HDMI Interface.

31 TVDD Power Terminator Supply Voltage (3.3 V).

32 RXD_2− HDMI input Digital Input Channel 2 Complement of Port D in the HDMI Interface.

33 RXD_2+ HDMI input Digital Input Channel 2 True of Port D in the HDMI Interface.

34 CVDD Power Comparator Supply Voltage (1.8 V).

35 CGND Ground TVDD and CVDD Ground.

36 TXPVDD Power

37 TXPLVDD Power 1.8 V power supply

38 TXPGND Ground TXPVDD Ground.

39 TXPLGND Ground TXPLVDD Ground

40 EXT_SWING Analog input

41 HP_TX Analog input

42 TEST0 Test pin Connect to ground.

43 TXDDC_SDA Digital I/O

44 TXDDC_SCL Digital output

45 TXAVDD Power 1.8 V Power Supply for TMDS Outputs.

46 TXGND Ground TXAVDD Ground.

47 TXC− HDMI output

48 TXC+ HDMI output

49 TXGND Ground TXAVDD Ground.

50 TX0− HDMI output

51 TX0+ HDMI output

52 TXGND Ground TXAVDD Ground.

53 TX1− HDMI output

54 TX1+ HDMI output

55 TXAVDD Power 1.8 V Power Supply for TMDS Outputs.

56 TX2− HDMI output

1.8 V PLL Power Supply. These pins provide power to the digital portion of the clock PLL. The

designer should provide quiet, noise-free power to these pins.

Sets Internal Reference Currents. Place an 887Ω resistor (1% tolerance) between this pin and

ground.

Hot Plug Detect Signal. This pin indicates to the interface whether the receiver is connected.

This pin is 5 V tolerant.

Serial Port Data I/O to Receiver. This pin serves as the master to the DDC bus. This pin is 5 V

tolerant.

Serial Port Data Clock to Receiver. This pin serves as the master clock for the DDC bus.

This pin is 5 V tolerant.

Differential Clock Output. Differential clock output at the TMDS clock rate; supports

TMDS logic level.

Differential Clock Output. Differential clock output at the TMDS clock rate; supports

TMDS logic level.

Differential Output Channel 0 Complement. Differential output of the red data at 10×

the pixel clock rate; supports TMDS logic level.

Differential Output Channel 0 True. Differential output of the red data at 10× the pixel clock

rate; supports TMDS logic level.

Differential Output Channel 1 Complement. Differential output of the red data at 10×

the pixel clock rate; supports TMDS logic level.

Differential Output Channel 1 True. Differential output of the red data at 10× the pixel

clock rate; supports TMDS logic level.

Differential Output Channel 2 Complement. Differential output of the red data at 10×

the pixel clock rate; supports TMDS logic level.

Rev. Sp0 | Page 9 of 16

Page 19

AVR 2650 harman/kardon

139

ADV3014 ADI Confidential

Pin No. Mnemonic Type Description

57 TX2+ HDMI output

58 TXGND Ground TXAVDD Ground.

59 CEC Digital I/O Consumer Electronics Control Channel. This pin is 5 V tolerant.

60 DGND Ground DVDD Ground.

61 DVDD Power Digital Supply Voltage (1.8 V).

62 ALSB Digital input This pin is used to set the I2C address of the Rx IO and the Tx main maps.

Digital input

Digital input

Digital input

Miscellaneous

analog

63

64 EP_SCK Digital output SPI Clock Interface for the EDID.

65 EP_CS Digital output SPI Chip Selected Interface for the EDID.

66 EP_MOSI Digital output SPI Master Out/Slave In for the EDID.

67 EP_MISO Digital input SPI Master In/Slave Out for the EDID.

68 TEST1 Test pin Connect to ground.

69 TEST2 Test pin Connect to ground.

70 TEST3 Test pin Connect to ground.

71 TEST4 Test pin Connect to ground.

72 DGNDIO Ground DVDDIO Ground.

73 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

74 TEST5 Test pin Connect to ground.

75 TEST6 Test pin Connect to ground.

76 TEST7 Test pin Connect to ground.

77 TEST8 Test pin Connect to ground.

78 SDATA Digital I/O I2C Port Serial Data Input/Output Pin. SDATA is the data line for the control port.

79 SCL Digital input I2C Port Serial Clock Input. SCL is the clock line for the control port.

80 DGND Ground DVDD Ground.

81 DVDD Power Digital Supply Voltage (1.8 V).

82 INT1 Digital output

83 INT2 Digital output

84 INT_TX Digital output Interrupt; Open Drain. A 2 kΩ pull-up resistor to the microcontroller I/O supply is recommended.

85 DGNDIO Ground DVDDIO Ground.

86 DVDDIO Power Digital I/O Supply Voltage (3.3 V).

87 TEST9 Test pin Leave floating.

88 TEST10 Test pin Leave floating.

89 TEST11 Test pin Leave floating.

90 TEST12 Test pin Leave floating.

91 TEST13 Test pin Leave floating.

92 DGND Ground DVDD Ground.

93 DVDD Power Digital Supply Voltage (1.8 V).

94 TEST14 Test pin Leave floating.

95 TEST15 Test pin Leave floating.

96 TEST16 Test pin Leave floating.

97

98

99 PGND Ground PVDD Ground.

100 PVDD Power PLL Supply Voltage (1.8 V).

101 XTAL

CS

RESET

PWRDN

Differential Output Channel 2 True. Differential output of the red data at 10× the pixel

clock rate; supports TMDS logic level.

Chip Select Pin. This pin must be set low or left floating for the chip to process I2C messages

that are destined for the ADV3014. The ADV3014 ignores I2C messages that it receives if

this pin is high.

Interrupt Pin. This pin can be active low or active high. When status bits change, this pin is

triggered. The events that trigger an interrupt are under user control.

Interrupt Pin. This pin can be active low or active high. When status bits change, this pin is

triggered. The events that trigger an interrupt are under user control.

System Reset Input. Active low. A minimum low reset pulse width of 5 ms is required to reset

the ADV3014 circuitry.

Active-Low Power-Down Pin. If used, this pin should be pulled high to power up the

ADV3014. This pin can also be used as an in-system power detect where an internal EDID can

be powered from a 5 V signal of the HDMI port when it is connected to active equipment. This

pin is 5 V tolerant.

Input Pin for 28.63636 MHz Crystal or an External 1.8 V 28.63636 MHz Clock Oscillator Source to

Clock the ADV3014.

Rev. Sp0 | Page 10 of 16

Page 20

AVR 2650 harman/kardon

140

ADI Confidential ADV3014

Pin No. Mnemonic Type Description

102 XTAL1

103 PVDD Power PLL Supply Voltage (1.8 V).

104 PGND Ground PVDD Ground.

105 HP_CTRLA Digital output Hot Plug Control Output for Port A. This pin is 5 V tolerant.

106 5V_DETA Digital input 5 V Detect Pin for Port A in the HDMI Interface. This pin is 5 V tolerant.

107 RTERM

108 DDCA_SDA Digital I/O HDCP Slave Serial Data Port A. DDCA_SDA is a 3.3 V input/output that is 5 V tolerant.

109 DDCA_SCL Digital input HDCP Slave Serial Clock Port A. DDCA_SCL is a 3.3 V input that is 5 V tolerant.

110 CVDD Power Receiver Comparator Supply Voltage (1.8 V).

111 CGND Ground TVDD and CVDD Ground.

112 RXA_C− HDMI input Digital Input Clock Complement of Port A in the HDMI Interface.

113 RXA_C+ HDMI input Digital Input Clock True of Port A in the HDMI Interface.

114 TVDD Power Receiver Terminator Supply Voltage (3.3 V).

115 RXA_0− HDMI input Digital Input Channel 0 Complement of Port A in the HDMI Interface.

116 RXA_0+ HDMI input Digital Input Channel 0 True of Port A in the HDMI Interface.

117 CGND Ground TVDD and CVDD Ground.

118 RXA_1− HDMI input Digital Input Channel 1 Complement of Port A in the HDMI Interface.

119 RXA_1+ HDMI input Digital Input Channel 1 True of Port A in the HDMI Interface.

120 TVDD Power Receiver Terminator Supply Voltage (3.3 V).

121 RXA_2− HDMI input Digital Input Channel 2 Complement of Port A in the HDMI Interface.

122 RXA_2+ HDMI input Digital Input Channel 2 True of Port A in the HDMI Interface.

123 HP_CTRLB Digital output Hot Plug Control Output for Port B. This pin is 5 V tolerant.

124 5V_DETB Digital input 5 V Detect Pin for Port B in the HDMI Interface. This pin is 5 V tolerant.

125 DGND Ground DVDD Ground.

126 DVDD Power Digital Supply Voltage (1.8 V).

127 DDCB_SDA Digital I/O HDCP Slave Serial Data Port B. DDCB_SDA is a 3.3 V input/output that is 5 V tolerant.

128 DDCB_SCL Digital input HDCP Slave Serial Clock Port B. DDCB_SCL is a 3.3 V input that is 5 V tolerant.

129 CVDD Power Receiver Comparator Supply Voltage (1.8 V).

130 CGND Ground TVDD and CVDD Ground.

131 RXB_C− HDMI input Digital Input Clock Complement of Port B in the HDMI Interface.

132 RXB_C+ HDMI input Digital Input Clock True of Port B in the HDMI Interface.

133 TVDD Power Receiver Terminator Supply Voltage (3.3 V).

134 RXB_0− HDMI input Digital Input Channel 0 Complement of Port B in the HDMI Interface.

135 RXB_0+ HDMI input Digital Input Channel 0 True of Port B in the HDMI Interface.

136 CGND Ground TVDD and CVDD Ground.

137 RXB_1− HDMI input Digital Input Channel 1 Complement of Port B in the HDMI Interface.

138 RXB_1+ HDMI input Digital Input Channel 1 True of Port B in the HDMI Interface.

139 TVDD Power Receiver Terminator Supply Voltage (3.3 V).

140 RXB_2− HDMI input Digital Input Channel 2 Complement of Port B in the HDMI Interface.

141 RXB_2+ HDMI input Digital Input Channel 2 True of Port B in the HDMI Interface.

142 HP_CTRLC Digital output Hot Plug Control Output for Port C. This pin is 5 V tolerant.

143 5V_DETC Digital input 5 V Detect Pin for Port C in the HDMI Interface. This pin is 5 V tolerant.

144 DDCC_SDA Digital I/O HDCP Slave Serial Data Port C. DDCC_SDA is a 3.3 V input/output that is 5 V tolerant.

Miscellaneous

analog

Miscellaneous

analog

Crystal Output Pin. This pin should be left floating if a clock oscillator is used.

This pin sets the internal termination resistance. A 500 Ω resistor between this pin and

ground should be used.

Rev. Sp0 | Page 11 of 16

Page 21

AVR 2650 harman/kardon

141

Page 22

AVR 2650 harman/kardon

142

TMP92CD28

CMOS 32-Bit Microcontrollers

TMP92CD28FG / TMP92CD28DFG

Outline and Device Characteristics

The TMP92CD28 is a high-speed advanced 32-bit Microcontroller developed for controlling

equipment which processes mass data.

The TMP92CD28 has a high-performance CPU (900/H1 CPU) and various built-in I/Os.

The TMP92CD28FG and TMP92CD28DFG are housed in a 100-pin flat package.

Device characteristics are as follows:

(1) CPU: 32-bit CPU (900/H1 CPU)

Compatible with 900/L1 instruction code

16 Mbytes of linear address space

General-purpose register and register banks

Micro DMA: 8 channels (250 ns/4 bytes at f

(2) Minimum instruction execution time: 50 ns (at f

(3) Internal memory

Internal RAM: 32-Kbytes

Internal ROM: 512-Kbytes

= 20 MHz, best case)

SYS

= 20 MHz)

SYS

Page 23

AVR 2650 harman/kardon

143

TMP92CD28

(4) External memory expansion

Expandable up to 16 Mbytes (Shared program/data area)

Can simultaneously support 8- or 16-bit width external data bus

Dynamic data bus sizing

Separate bus system

(5) Memory controller

Chip select output: 3 channels

(6) 8-bit timers: 6 channels

(7) 16-bit timers: 2 channels

(8) General-purpose serial interface: 2 channels

UART/synchronous mode: 2 channels (channel 0 , and 1)

IrDA ver.1.0 (115 kbps) mode selectable: 2 channels (channel 0 and 1)

(9) Serial bus interface: 2 channels

2

C bus mode

I

Clock synchronous mode (only channel 1)

(10) SPI controller : 1 channel

Supported up to SPI mode of SD card and MMC card

Built-in FIFO buffer of 32 bytes to each Input/Output

(11) High Speed serial interface : 1 channel

Built-in FIFO buffer of 32 bytes to each Input/Output

(12) USB Host Controller : 1chanel

Universal Serial Bus Specification Rev2.0

Open HCI for USB Release 1.0a

12Mbps – Full speed support. (Isochronous Transfer is not supported.)

(13) Watchdog timer

(14) Timer for real-time clock (RTC)

(15) Key-on wake up (only for HALT release):4 channels

(16) Program patch logic: 8 banks

(17) Interrupts: 47interrupts

9 CPU interrupts: Software interrupt instruction and illegal instruction

34 internal interrupts: Seven selectable priority levels

4 external interrupts (INT0 to INT3): Seven selectable priority levels

(INT0 to INT3 selectable edge or level interrupt)

(18) Input/output ports: 70pins

(19) St andby function

Three HALT modes: IDLE2 (Programmable), IDLE1, STOP

Power cut mode (Built-in power supply management circuits (PMC) for leak current

provision.)

(20) Clock controller

Built-in two blocks of clock doubler (PLL). PLL supplies 48 MHz for USB and 36 MHz for CPU

from 9MHz

Clock gear function: Select high-frequency clock fc to fc/16

Special timer for CLOCK (fs = 32.768 kHz)

Page 24

(

)

A

A

Y

A

A

A

A

/

(

)

(

)

AVR 2650 harman/kardon

144

TMP92CD28

DVCC3A[5]

DVCC3B[1]

DVSS[8]

(PG0)/KI0

(PG1)/KI1

(PG2)/KI2

(PG3)/KI3

(PN1)/SDA0/TA3OUT

(PN2)/SCL0/TA2IN/SI0

(PN3)HSCLK/SCK1

(PN4)SDA1/HSSO/SO1

(PN5)SCL1/HSSI/SI1

(PF0)TXD0

(PF1)RXD0

(PF2)SCLK0/ 0CTS /CLK

(PF5)SCLK1/

/TB0OUT0

(PF3)TXD1/SPDO

(PF4)RXD1/SPDI

1CTS /SPCLK

(PC0)INT0

(PC1)INT1

(PC2)INT2/TB1IN0/TB0IN0

(PC3)INT3

PWE

PortG

PortN

PortF

PortC

PMC

Key-on

Wake up

Serial Bus I/F

(Ch.0)

Serial Bus I/F

HSIO

Serial I/O

(Ch.0)

Serial I/O

Ch.1

Ch.1

SPIC

Interrupt

Controller

16-BitTimer

(TMRB0)

16-Bit Timer

(TMRB1)

TLCS-900/H1

X

W

A

XB

C

XD

E

XH

W

IX

I

IZ

SP

32bit

SR

Watchdog

Timer

Real Time

Clock

32-KB RAM

CB

ED

LH

F

Regulator

Mode

Controller

PLL

H-OSC

Clock Gear

L-OSC

Port0

Port1

Port4

512-KB ROM

Program

patch logi

8-Banks

Port5

Port6

USB

Memory

Controller

(4-Blocks)

Port7

Port8

8-Bit Timer(TMRA0)

8-Bit Timer(TMRA1)

8-Bit Timer(TMRA2)

8-Bit Timer(TMRA3)

8-Bit Timer(TMRA4)

8-Bit Timer(TMRA5)

( ): Initial function after reset

DVCC1A[1]

DVCC1B[1]

RVIN [2]

RVOUT[2]

RESET

M0

M1

X

X2

XT2

XT1

D0 to D7(P00 to P07)

D8 to D15(P10 to P17)

0 to A7(P40 to P47)

8 to A15(P50 to P57)

16 to A23(P60 to P67)

D

D-

X1USB(P77)

USBPON(P76)

/USBOC(P75)

TA0IN/(P74)

SRLUB(P73)

SRLLB

(P72)

SRWR (P71)

RD

P70

0CS /TA1OUT(P80)

2CS (P82)

3CS / WAIT

TA5OUT(P83)

Figure 1.1 TMP92CD28 Block Diagram

Page 25

AVR 2650 harman/kardon

145

TMP92CD28

2. Pin Assignment and Functions

The assignment of input/output pins for the TMP92CD28, their names and functions are as

follows:

2.1 Pin Assignment Diagram

Figure 2.1.1 shows the pin assignment of the TMP92CD28FG.

/RESET

PC0/INT0

PC2/INT2/TB1IN0/TB0IN0

PC1/INT1

PC3/INT3

DVCC3B

XT1

XT2

PWE

DVSS

DVCC1B

RVOUT1

RVIN

RVIN

RVOUT2

DVCC1A

DVSS

P00/D0

P01/D1

P02/D2

P03/D3

P04/D4

P05/D5

P06/D6

P07/D7

1

5

10

15

20

25

DVSS

100

DVSS

A

PG0

PG2

PG1

PG3

95

PN3/HSCLK/SCK1

PN5/HSSI/SCL1/SI1

PN2/SCL0/TA2IN

PN1/SDA0/TA3OUT

90

PF5/SCLK1/CTS1/SPCLK

PN4/HSSO/SDA1/SO1

DVCC3

TMP92CD28FG

LQFP100

TOPVIEW

30

9

P11/D

P10/D8

P13/D11

P12/D10

DVCC3A

35

3

P40/A0

P41/A1

P17/D15

P15/D1

P14/D12

P16/D14

0

PF3/TXD1/SPDO

PF1/RXD

DVSS

PF4/RXD1/SPDI

P42/A2

PF0/TXD0/

PF2/SCLK0/CTS0/CLK/TB0OUT0

85

40

7

P45A5

P46/A6

P43/A3

P47/A

P44/A4

P77/X1USB

45

DVSS

DVCC3A

D+

P76/USBPON

AM0

P75/USBOC

D-

80

P50/A8

DVCC3A

75

70

65

60

55

9

P51/A

P53/A11

P52/A10

X1

DVSS

X2

AM1

P83/CS3/WAIT/TA5OUT

P82/CS2

P80/CS0/TA1OUT

P74/TA0IN

P73/SRLUB

P72/SRLLB

P71/SRWR

P70/RD

DVCC3A

DVSS

P67/A23

P66/A22

P65/A21

P64/A20

P63/A19

P62/A18

P61/A17

P60/A16

P57/A15

P56/A14

50

P55/A13

P54/A12

BOOT

Figure 2.1.1 Pin Assignment Diagram (100-pin LQFP)

Page 26

AVR 2650 harman/kardon

146

TMP92CD28

Figure 2.1.2 shows the pin assignment of the TMP92CD28DFG.

T

BOOT

AM0

P77/X1USB

DVSS

PF0/TXD0

PF2/SCLK0/CTS0/CLK/TB0OUT0

PF5/SCLK1/CTS1/SPCLK

PN4/HSSO/SDA1/SO1

PF1/RXD0

PF3/TXD1/SPDO

PF4/RXD1/SPDI

PN1/SDA0/TA3OUT

PN2/SCL0/TA2IN

PN3/HSCLK/SCK1

PN5/HSSI/SCL1/SI1

DVCC3A

PG3

PG2

PG1

D+

D-

85

90

95

100

B

X1

X2

AM1

P82/CS2

P76/USBPON

P75/USBOC

DVCC3A

80

P83/CS3/WAIT/TA5OU

DVSS

75

P72/SRLLB

P71/SRWR

P70/RD

DVCC3A

P74/TA0IN

P73/SRLU

P80/CS0/TA1OUT

70

DVSS

65

TMP92CD28DFG

QFP100

TOPVIEW

5

1

PG0

DVSS

/RESET

PC1/INT1

PC0/INT0

10

3

XT1

XT2

DVCC3B

PC3/INT

PC2/INT2/TB1IN0/TB0IN0

PWE

DVSS

15

2

RVIN

RVIN

DVCC1B

RVOUT1

RVOUT

0

P61/A17

P60/A16

P57/A15

P56/A14

P55/A13

P54/A12

P63/A19

P62/A18

P65/A21

P64/A2

P67/A23P66/A22

60

20

0

DVSS1

P01/D1

P00/D

DVCC1A

P02/D2

55

25

P03/D3

P05/D5

P06/D6

P04/D4

P53/A11

P52/A10

50

P51/A9

P50/A8

DVCC3A

DVSS

45

P47/A7

P46/A6

P45A5

P44/A4

P43/A3

P42/A2

P41/A1

P40/A0

P17/D15

P16/D14

P15/D13

P14/D12

P13/D11

P12/D10

P11/D9

40

35

30

DVSS

P10/D8

P07/D7

DVCC3A

Figure 2.1.2 Pin Assignment Diagram (100-pin QFP)

Page 27

AVR 2650 harman/kardon

147

TMP92CD28

2.2 Pin Names and Functions

The following table shows the names and functions of the input/output pins

Table 2.2.1 Pin Names and Functions (1/3)

Pin name

P00 to P07

D0 to D7

P10 to P17

D8 to D15

P40 to P47

A0 to A7

P50 to P57

A8 to A15

P60 to P67

A16 to A23

P70

RD

P71

SRWR

P72

SRLLB

P73

SRLUB

P74

TA0IN

P75

USBOC

P76

USBPON

P77

X1USB

P80

0CS

TA1OUT

(

BOOT Note)

P82

2CS

P83

3CS

TA5OUT

WAIT

PC0

INT0

PC1

INT1

PC2

INT2

TB0IN0

TB1IN0

PC3

INT3

Number

of Pin

8 I/O

8 I/O

8 I/O

8 I/O

8 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 Input

1 I/O

1 I/O

1 I/O

1 Output

1 Output

1 I/O

1 Input

1 Input

1 Input

1 Input

I/O

I/O

I/O

Output

Output

Output

Output

Output

Output

Output

Input

Input

Output

Input

Output

Output

Input

Output

Output

Output

Input

Input

Input

Input

Input

Input

Input

Function

Port 0: I/O port Input or output specifiable in units of bits

Data: Data bus 0 to 7

Port 1: I/O port Input or output specifiable in units of bits

Data: Data bus 8 to 15

Port 4: I/O port Input or output specifiable in units of bits

Address: Address bus 0 to 7

Port 5: I/O port Input or output specifiable in units of bits

Address: Address bus 8 to 15

Port 6: I/O port Input or output specifiable in units of bits

Address: Address bus 16 to 23

Port 70: I/O port (Schmitt input, with pull-up register)

Read: Outputs strobe signal for read external memory.