Page 1

harman/kardon

AVR247/230 Service Manual

Page 1 of 131

harman/kardon Service Manual

AVR247/230

5 x 50W 7.1 CHANNEL A/V RECEIVER

CONTENTS

ESD WARNING………………………..…..2 ELECTRICAL PARTS LIST…….…..…12

BASIC SPECIFICATIONS........................3 SEMICONDUCTOR PINOUTS…....….54

TROUBLESHOOTING GUIDE.................4 PCB DRAW

PROCESSOR RESET..............................4 BLOCK DIAGRAM.............................119

PACKAGE LIST AND PARTS…...............5 WIRING DIAGRAM……………..….…120

DISASSEMBLY.........................................6 AMP BIAS ADJUSTMENT...…...…....121

UNIT EXPLODED VIEW AND PARTS…11 SCHEMATIC DIAGRAMS...………....122

Released EU2008 harman/kardon, Inc. Rev 0, 05/2008

250 Crossways Park Dr.

Woodbury, New York, 11797

INGS…………………..…110

Page 2

harman/kardon

AVR247/230 Service Manual

Page 2 of 131

Some semiconductor (solid state) devices can be damaged easily by static electricity. Such components commonly are called

Electrostatically Sensitive (ES) Devices. Examples of typical ES devices are integrated circuits and some field effect transistors and

semiconductor "chip" components.

The following techniques should be used to help reduce the incidence of component damage caused by static electricity.

1. Immediately before handling any semiconductor component or semiconductor-equipped assembly, drain off any electrostatic charge on

your body by touching a known earth ground. Alternatively, obtain and wear a commercially available discharging wrist strap device,

which should be removed for potential shock reasons prior to applying power to the unit under test.

2. After removing an electrical assembly equipped with ES devices, place the assembly on a conductive surface such as aluminum foil, to

prevent electrostatic charge build-up or exposure of the assembly.

3. Use only a grounded-tip soldering iron to solder or unsolder ES devices.

4. Use only an anti-static solder removal device. Some solder removal devices not classified as "anti-static" can generate electrical charges

sufficient to damage ES devices.

5. Do not use freon-propelled chemicals. These can generate electrical change sufficient to damage ES devices.

6. Do not remove a replacement ES device from its protective package until immediately before you are ready to install it. (Most replacement

ES devices are packaged with leads electrically shorted together by conductive foam, aluminum foil or comparable conductive material.)

7. Immediately before removing the protective material from the leads of a replacement ES device, touch the protective material to the

chassis or circuit assembly into which the device will be installed.

CAUTION :

8. Minimize bodily motions when handling unpackaged replacement ES devices. (Otherwise harmless motion such as the brushing together

or your clothes fabric or the lifting of your foot from a carpeted floor can generate static electricity sufficient to damage an ES devices.

Be sure no power is applied to the chassis or circuit, and observe all other safety precautions.

Each precaution in this manual should be followed during servicing.

Components identified with the IEC symbol in the parts list are special significance to safety. When replacing a component identified with

, use only the replacement parts designated, or parts with the same ratings or resistance, wattage, or voltage that are designated in the

parts list in this manual. Leakage-current or resistance measurements must be made to determine that exposed parts are acceptably

insulated from the supply circuit before retuming the product to the customer.

Page 3

Technical Specifications

harman/kardon

AVR247/230 Service Manual

Page 3 of 131

Audio Section

Stereo Mode

Continuous Average Power (FTC)

65 Watts per channel, 20Hz–20kHz,

@ < 0.07% THD, both channels driven into 8 ohms

7 Channel Surround Modes

Power Per Individual Channel

Front L&R channels:

50 Watts per channel,

@ < 0.07% THD, 20Hz–20kHz into 8 ohms

Center channel:

50 Watts, @ < 0.07% THD, 20Hz–20kHz into 8 ohms

Surround (L & R Side, Back) channels:

50 Watts per channel,

@ < 0.07% THD, 20Hz–20kHz into 8 ohms

Input Sensitivity/Impedance

Linear (High Level) 200mV/47kohms

Signal-to-Noise Ratio (IHF-A) 100dB

Surround System Adjacent Channel Separation

Analog Decoding 40dB

(Pro Logic, etc.)

Dolby Digital (AC-3) 55dB

DTS 55dB

Frequency Response

@ 1W (+0dB, –3dB) 10Hz–130kHz

High Instantaneous

Current Capability (HCC) ±35 Amps

Transient Intermodulation

Distortion (TIM) Unmeasurable

Rise Time 16 µsec

Slew Rate 40V/µsec**

FM Tuner Section

Frequency Range 87.5–108MHz

Usable Sensitivity IHF 1.3 µV/13.2dBf

Signal-to-Noise Ratio Mono/Stereo: 70/68dB (DIN)

Distortion Mono/Stereo: 0.2/0.3%

Stereo Separation 40dB @ 1kHz

Selectivity ±400kHz: 70dB

Image Rejection 80dB

IF Rejection 90dB

AM Tuner Section

Frequency Range 522–1620kHz

Signal-to-Noise Ratio 45dB

Usable Sensitivity Loop: 500µV

Distortion 1kHz, 50% Mod: 0.8%

Selectivity ±10kHz: 30dB

Video Section

Video Format PAL/NTSC

Input Level/Impedance 1Vp-p/75 ohms

Output Level/Impedance 1Vp-p/75 ohms

Video Frequency Response

(Composite and S-Video) 10Hz–8MHz (-3dB)

Video Frequency

Response (Component) 10Hz–100MHz (-3dB)

™

HDMI

Audio and video processing

General

Power Requirement AC 220–240V/50Hz

Power Consumption 65W idle, 540W maximum

(7 channels driven)

Dimensions (Max)

Width 440mm

Height 165mm

Depth 382mm

Weight 13.6 kg

This product incorporates copyright protection technology that is protected by method

claims of certain U.S.patents and other intellectual property rights owned by Macrovision

Corporation and other rights owners. Use of this copyright protection technology must be

authorized by Macrovision Corporation, and is intended for home and other limited viewing

uses only unless otherwise authorized by Macrovision Corporation. Reverse engineering or

disassembly is prohibited.

Depth measurement includes knobs, buttons and terminal connections.

Height measurement includes feet and chassis.

All features and specifications are subject to change without notice.

Harman Kardon, The Bridge and Logic 7 are registered trademarks of

Harman International Industries, Incorporated.

is a trademark of Harman International Industries, Inc.

*Manufactured under license from Dolby Laboratories.

“Dolby,”“Pro Logic” and the Double-D symbol are

trademarks of Dolby Laboratories.

"DTS","DTS ES","Neo:6"and"96/24" are trademarks of DTS,Inc.

SA-CD is a trademark of Sony Electronics, Inc.

Blu-ray Disc is a trademark of the Blu-ray Disc Association.

Apple and iPod are registered trademarks of Apple Computer, Inc.

Cirrus is a registered trademark of Cirrus Logic Corp.

**Without input anti slewing and output isolation networks.

Faroudja and DCDi by Faroudja are trademarks of Genesis Microchip, Inc.

HD-DVD is a trademark of the DVD Format/Logo Licensing Corporation (DVD FLLC).

HDMI, the HDMI logo and High-Definition Multimedia Interface are trademarks or

registered trademarks of HDMI Licensing, LLC.

Page 4

Troubleshooting Guide

harman/kardon

AVR247/230 Service Manual

Page 4 of 131

SYMPTOM CAUSE SOLUTION

Unit does not function when Main • No AC Power • Make certain AC power cord is plugged

Power Switch

Display lights, but no sound • Intermittent input connections • Make certain that all input and speaker

or picture connections are secure

No sound from any speaker; • Amplifier is in protection mode • Check speaker-wire connections for shorts at receiver

light around Power switch

No sound from surround or • Incorrect surround mode • Select a mode other than Stereo

center speakers • Input is mono • There is no surround information from mono sources (except with

Unit does not respond to • Weak batteries in remote • Change remote batteries

remote commands • Wrong device selected • Press the AVR Selector

1

is pushed into a live outlet

• Check to see if outlet is switch controlled

• Mute is on • Press Mute button

• Volume control is down • Turn up volume control

2

is red due to possible short and speaker ends

• Amplifier is in protection mode • Contact your local Harman Kardon service depot

due to internal problems

Theater and Hall surround modes)

• Incorrect configuration • Check speaker mode configuration

• Stereo or Mono program material • Some surround modes may not create rear-channel information

from nonencoded programs

• Remote sensor Úis obscured • Make certain front-panel sensor is visible to remote or

connect remote sensor

5

Intermittent buzzing in tuner • Local interference • Move unit or antenna away from computers, fluorescent lights,

motors or other electrical appliances

Letters flash in the Channel Indicator • Digital audio feed paused • Resume play for DVD

Display $and Digital Audio stops • Check that Digital Signal is fed to the Digital Input selected

Processor Reset

In the rare case where the unit’s operation or the

displays seem abnormal, the cause may involve

the erratic operation of the system’s memory or

microprocessor.

To correct this problem, first unplug the unit from

the AC wall outlet and wait at least three

minutes. After the pause,reconnect the AC

power cord and check the unit’s operation.If the

system still malfunctions, a system reset may

clear the problem.

To clear the AVR’s entire system memory

including tuner presets, output level settings,

delay times and speaker configuration data, first

put the unit in Standby by pressing the System

Power Control button

the Tone Mode button

The unit will turn on automatically. Note that

once you have cleared the memory in this manner,

it is necessary to re-establish all system

configuration settings and tuner presets.

2

. Next press and hold

8

for three seconds.

NOTE: Resetting the processor will erase any

configuration settings you have made for

speakers,output levels, surround modes, digital

input assignments as well as the tuner presets.

After a reset the unit will be returned to the

factory presets, and all settings for these items

must be reentered.

If the system is still operating incorrectly,there

may have been an electronic discharge or severe

AC line interference that has corrupted the

memory or microprocessor.

If these steps do not solve the problem, consult

an authorized Harman Kardon service depot.

Page 5

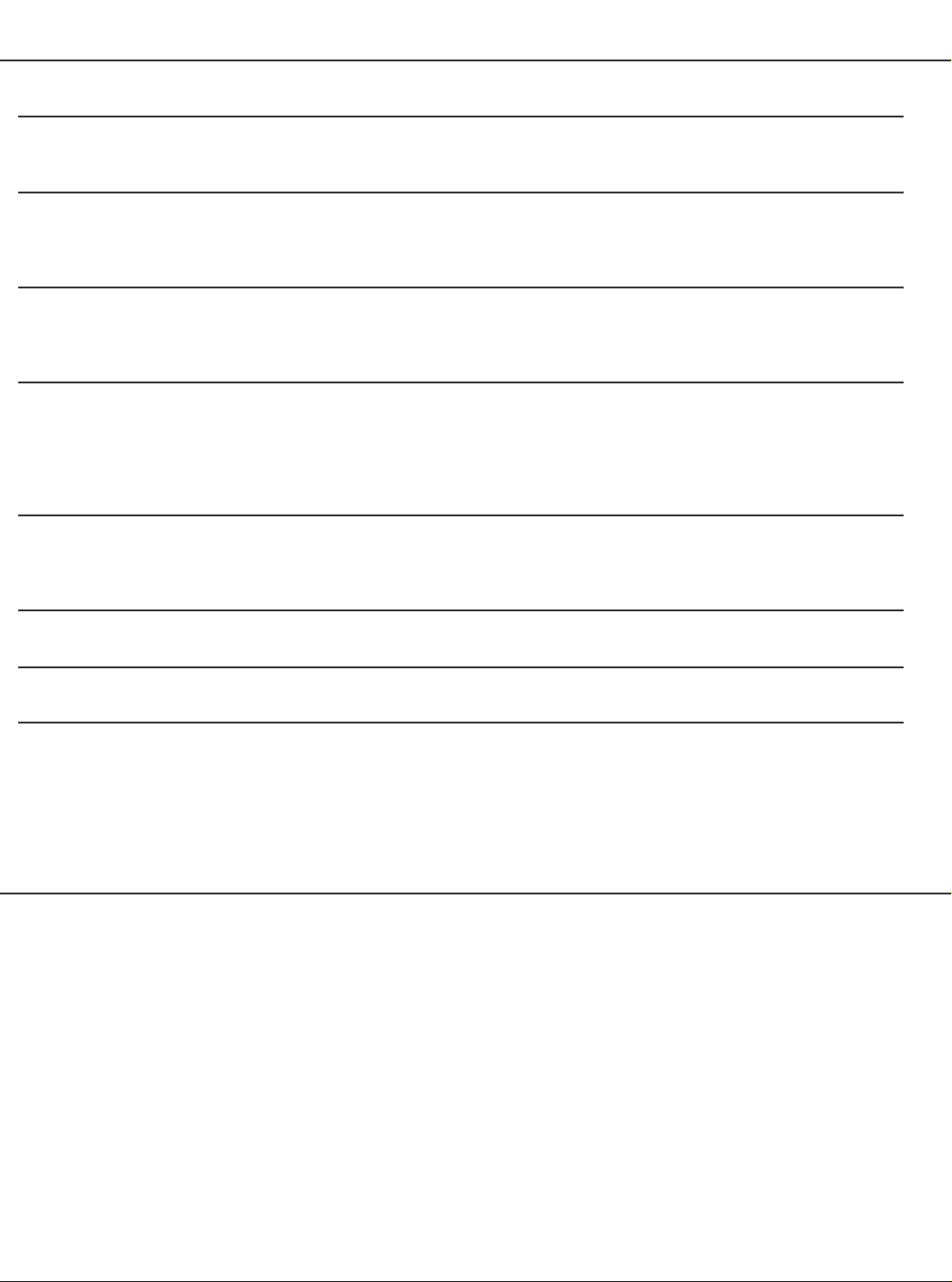

1. Instruction manual ass'y - Accessories

harman/kardon

AVR247/230 Service Manual

Page 5 of 131

2. Package Drawing

MICROPHONE ASS'Y

7

AVR247/230

1

5

9

POLY BAG

COVER ASS'Y

POLY BAG

2

AM LOOP ANTENNA ASS'Y

6

IMAGE BROCHURES

10

BOOKLET,INFORMATION

3

BATTERY ASS'Y

7

REMOCON ASS'Y

11

MANUAL INSTRUCTION

4

FM 1 POLE ANT

8

STAPLE

12

MANUAL SETUP GUIDE

2

SNOW PAD (L)

SET

4

ACCESSORY-1

1

SNOW PAD (R)

3

BOX ,OUT CARTON

5

13

STAPLE

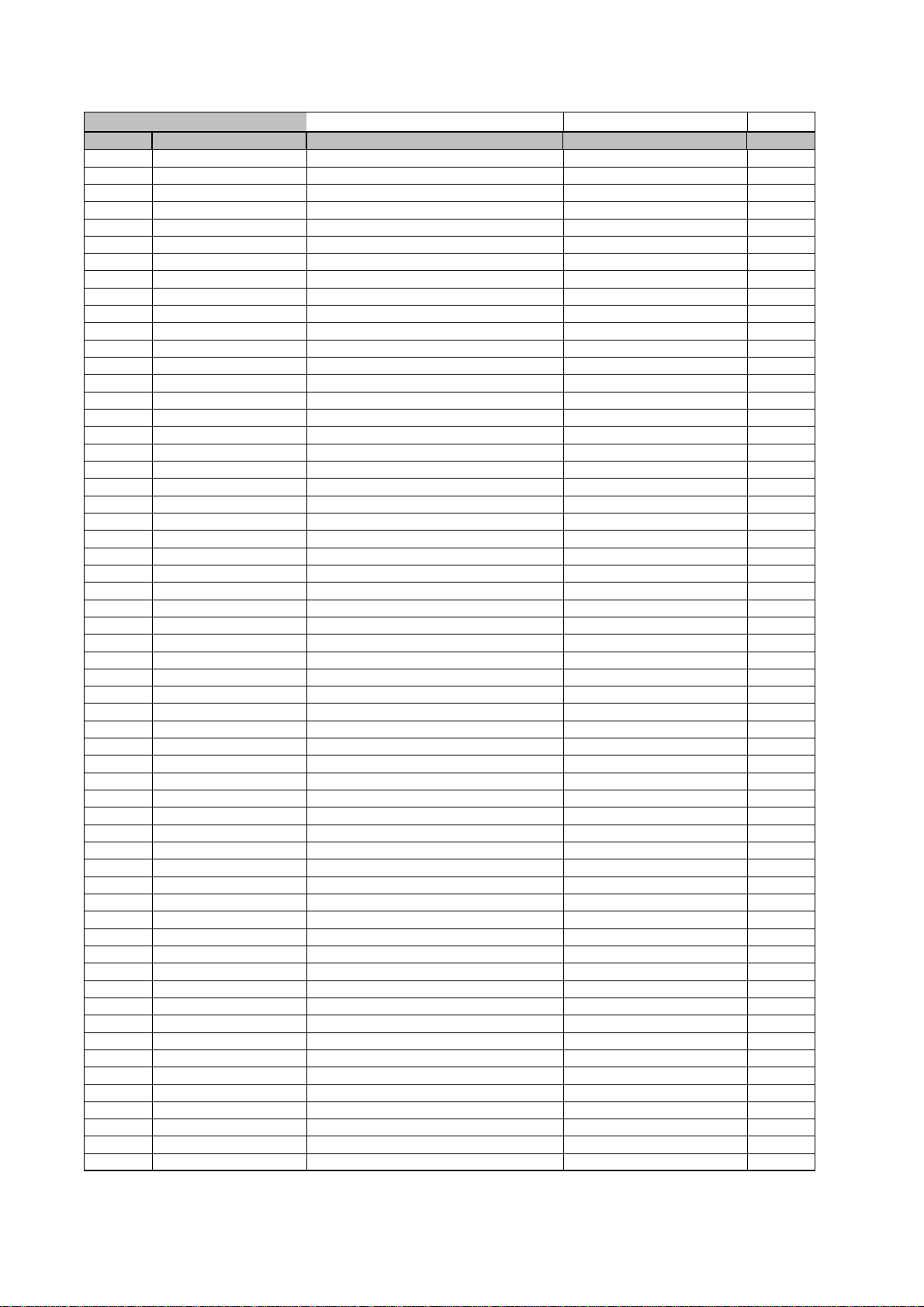

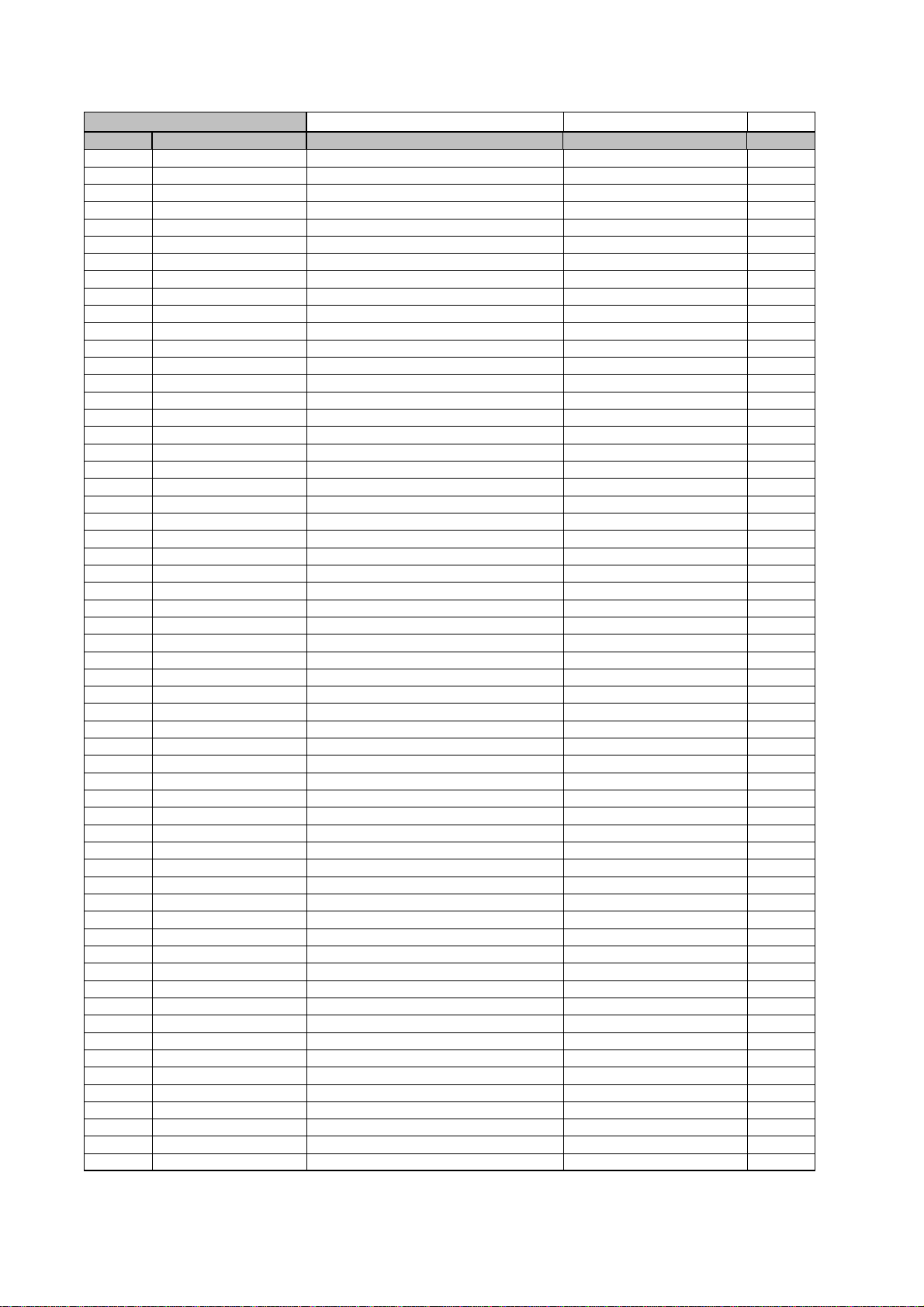

NO DESCRIPTION PARTS NO. Q,ty

1

2

3

4

FM 1 POL ANT CSA1A018Z 1

5

COVER ASS'Y CGRAVR130/230ZA

COVER A

1

COVER B

2

SHEET,FRONT COVER

3

4

PAD , COVER

BAG , POLY

5

6 IMAGE BROCHURES HQE1A273Z 1

7

REMOCON ASS'Y CARTAVR247/230 1

8 STAPLE CPL0905 3

A

MICROPHONE ASS'Y

CPB1061WPOLY BAG

CSA1A027ZAM LOOP ANTENNA ASS'Y 1

CABR03P3BATTERY 3

CGR1A331M7H43 1

CQE1A220Z

CPS1A676 1

CPB1A176Z 1

ACCESSORY-2

ACCESSORY-2ACCESSORY-1

NO DESCRIPTION PARTS NO. Q,ty

1

1

1

1CGR1A332M7H43

1

9

BOOKLET,INFORMATION

10

11

MANUAL ,SETUP GUIDE

12

13

STAPLE CPL0905 3

A MICROPHONE ASS'T CJXAVR340MICRO 1

CQE1A180Z 1

CQX1A1255ZMANUAL,INSTRUCTION

CQX1A1256Z

1CPB1061WPOLY BAG

1

1

ACCESSORY-1

1

21SNOW,PAD(L)

3

SET AVR247/230SET 1

4

BOX,OUT CARTON

5

ACCESSORY-26 CQXAVR247/230 1

MICROPHONE ASS'Y7 CJXAVR340MICRO 1

DESCRIPTIONNO

CQXAVR247/230

CPS6A564

CPS6A565SNOW,PAD(R)

CPG1A822U

6

Q,tyPARTS NO.

1

1

1

Page 6

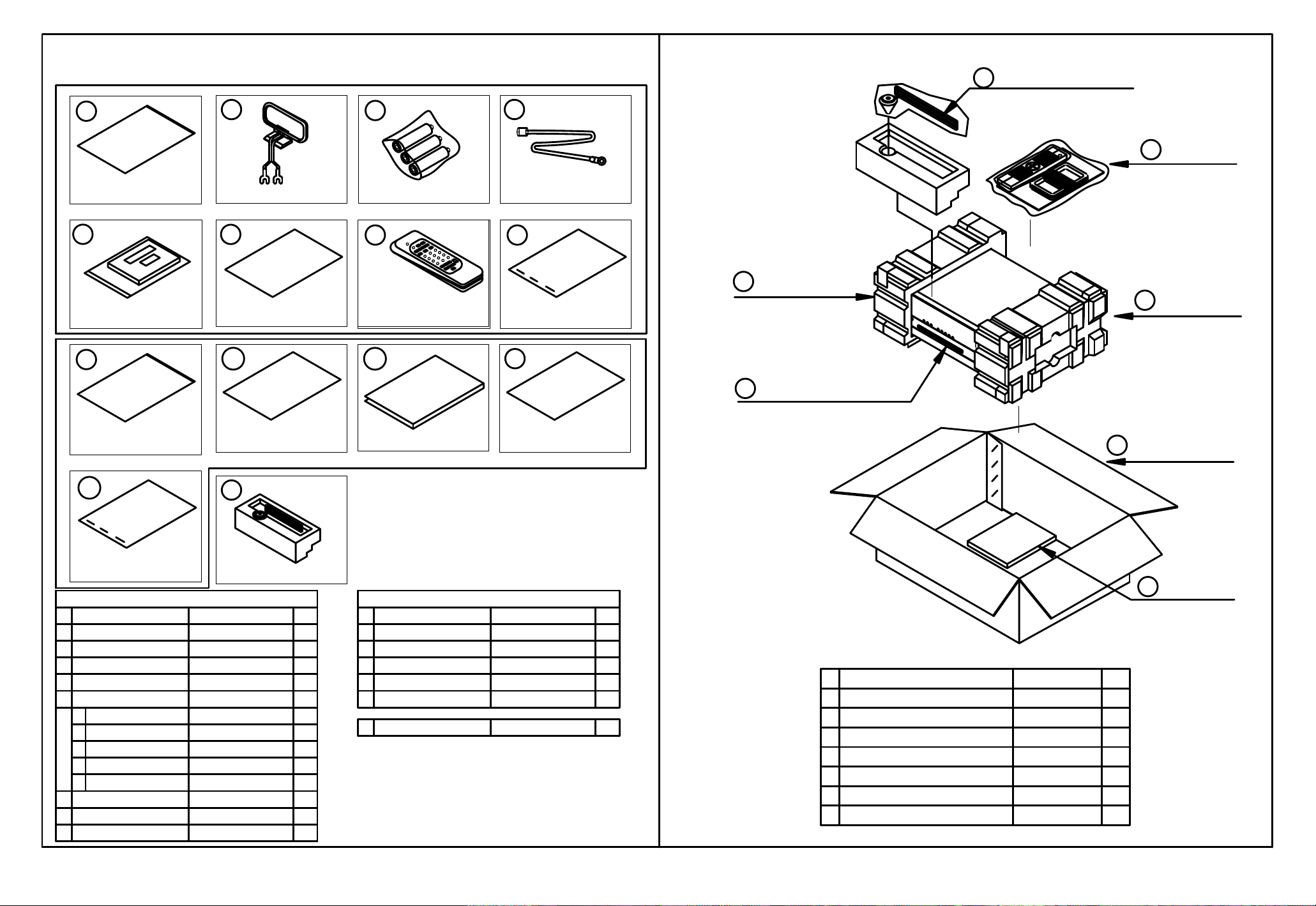

DISASSEMBLY

harman/kardon

AVR247/230 Service Manual

Page 6 of 131

AVR247/230

1. Removing the Top Cabinet

Remove the Screws

6

4

5

3. Removing the Rear Panel

13

1

~

10

9

11

7

8

12

13

3

1

2

Remove the Screws

10

11

12

13

14

15

16

25

26

9

7 6 5 4

8

27 29 30

33

1

~

21

22

23 24

28

31

18

17

1

3

2

32

33

19 20

9

8

4. Removing the Main PCB

1 7

Remove the Screws

~

2. Removing the Front Panel

Remove the Screws

7

6

5

1

4

2

3

1 9

~

1

5

2

6

3

4

7

Page 7

DISASSEMBLY PROCEDURES (AVR247)

harman/kardon

AVR247/230 Service Manual

Page 7 of 131

<1> TOP-CABINET(21) REMOVAL

1. Remove 13 screws(S1,S7) and then remove the Top-cabinet.

<2> FRONT PANEL ASS’Y REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Disconnect the card cable between conn

and connector(CN72) on the Input PCB(39-1).

3. Disconnect the lead wire(BN81-8P) on the Fip PCB(37-1) from connector(CN81) on the Trans PCB(40-4).

4. Disconnect the lead wire(BN22-6P) on the Phone PCB(

5. Disconnect the lead wire(BN18-5P) on the Phone PCB(

6. Disconnect the lead wire(BN10-4P) on the Volume PCB(37-6) from conn

7. Disconnect the lead wire(BN41-6P) on the Volume PCB(37-6) from conn

8. Disconnect the lead wire(BN90-2P) on the Main PCB(38

9. Remove 1 screw(S10) and then lead wire(JW82-1P,JW83-1P) on the Phone PCB(37-5).

10 .Remove 1screw(S10) and then lead wire(JW84-1P) on the Volume PCB(37-3).

11. Remove 10 scre ws(S1) and then remov e the Front Panel ASS’Y.

<3> Volume PCB(37-6) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Front Panel ASS’Y, referring to the previous step<2>.

3. Pull out the Volume Knob ASS’Y.

4. Disconnect connector(CN84) on the Volume PCB(37-6) from the lead

5. Disconnect the lead wire(BN92-5P)on the Volume PCB(

6. Remove 8 screws(S2,S14), and then remove the Volume PCB(37-6).

<4>PHONE PCB(37-5) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Front Panel ASS’Y, referring to the previous step<2>.

3. Disconnect connector(CN92) on the Phone PCB(37-5) from the lead wire(BN92-5P) on the Volume PCB(37-6).

4.. Disconnect connector(CN85)on the Phone PCB(37-5) from the lead wire(BN85-3P) on the Fip PCB(37-1).

5. Remove 2 screws(S2) and then remove the Phone PCB(37-5).

<5>POWER LED PCB(37-3) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Front Panel ASS’Y, referring to the previous step<2>.

3. Disconnect connector(CN88) on the Power Led PCB(37-3) from the lea

4. Remove 2 screws(S2) and then remove the Power led PCB(37-3).

<6>FIP PCB(37-1) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Front Panel ASS’Y, referring to the previous step<2>.

3. Disconnect the lead wire(BN84-5P) on the Fip PCB(3

4. Disconnect the lead wire(BN85-3P) on the Fip PCB(37

5. Disconnect the lead wire(BN88-4P) on the Fip PCB(37

ector(CN72-17p) on the Fip PCB(37-1)

37-5) from connector(CN22) on the Input PCB(39-1).

37-5) from connector(CN18) on the Input PCB(39-1).

ector(CN10) on the Input PCB(39-1).

ector(CN41) on the Video PCB(41).

-1) from connector(CN86) on the Moms PCB(37-4).

ire(BN84-5P) on the Fip PCB(37-1).

w

37-6) from connector(CN92) on the Phone PCB(37-5).

wire(BN88-4P) on the Fip PCB(37-1) .

d

-1) from connector(CN84) on the Volume PCB(37-6).

7

-1) from connector(CN85) on the Phone PCB(37-5).

-1) from connector(CN88) on the Power Led PCB(37-3).

Page 8

6. Disconnect the connector (CN89) on the Fip PCB(37-1) from lead wire(BN89-4P) on the Key PCB(37-2).

harman/kardon

AVR247/230 Service Manual

Page 8 of 131

7. Remove 3 screws(S2) and then remove the Guide PCB(37-8) & the Fip PCB(37-1).

<7>KEY PCB(37-2) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Front Panel ASS’Y, referring to the previous step<2>.

3. Remove the Fip PCB(37-1), referring to the previous step<6>.

4. Remove 10 screws(S2) and then remove the Key PCB(37-2).

<8>TUNER MODULE(44) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Disconnect the card cable between conne

ctor(CON1-1

3P) on the Tuner module(44)

and connector(CN13) on the Input PCB(39-1).

3. Remove 2 screws(S8) and then remove the Tuner Module(44).

<9>HUDSON PCB(42) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Disconnect connector(CN80) on the HUDSON PCB(42) from the lead

ire(BN80-3P) on the RS232 PCB(37-7).

w

3. Remove 3 screws(S15).

4. Disconnect the board to board connector between and connector(CN81-44P) on the HUDSON PCB(42)

and connector(BN81-44P) on VIDEO PCB(41) and then r

emove the HUDSON PCB(42).

<10>VIDEO PCB(41) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Hudson PCB(42), referring to

3. Disconnect the card cable between conn

the previ

ector(BN14-17p) on the Video PCB(41)

ous step<9>.

and connector(CN14) on the Input PCB(39-1).

4. Disconnect connector(CN43) on the Video PCB(41)

from the lead wire(BN43-3P) on the Regul

5. Disconnect connector(CN41) on the Video PCB(41) from

the lead wire(BN41-6P) on the Volume PCB(37-6).

ator PCB(A)(40-2).

6. Disconnect the card cable between connector(CN42) on the Video PCB(41)

and connector(BN44-7P) on the iPod PCB(39-2).

7. Disconnect the card cable between connector(BN15-15P) on the Video PCB(41)

and connector(CN15-15P) on the INPUT PCB(39-1).

8. Remove 6 screws(S8) and then remove the Video PCB(41).

<11>iPod PCB(39-2) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Hudson PCB(42), referring to

the previ

ous step<9>.

3. Remove the Video PCB(41), referring to the previous step<10>

4. Disconnect the card cable between connector(BN19-15P) on the the iPod PCB(39-2)

and connector(CN19) on the Input PCB(39-1).

5. Disconnect the card cable between conne

ctor(BN44-

7P) on the iPod PCB(39-2)

and connector(CN42) on the Video PCB(41).

6. Disconnect the card cable between connector(CN47-7P) on the iPod PCB(39-2)

and connector(CN47) on the RS232 PCB(37-7).

7. Disconnect the board to board connector betw

en and connector(CN23) on the XM PCB(39-4)

e

and connector(BN17-12P) on the iPod PCB(39-2).

Page 9

8. Remove 2 screws(S13) and then remove the iPod PCB(39-2).

harman/kardon

AVR247/230 Service Manual

Page 9 of 131

<12>XM PCB(39-4) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Hudson PCB(42), referring to the previ

ous step<9>.

3. Remove the Video PCB(41), referring to the previous step<10>

4. Disconnect the card cable between connector(BN21-7P) on XM PCB(39-4)

and connector(CN21) on the input PCB(39-1).

5. Disconnect the lead wire(BN85-2P) on the XM PCB(39-4) from connector(CN85) on the Regulator PCB(A)(40-2).

6. Disconnect the board to board connector betwe

en and connector(CN23) on the XM PCB(39-4)

and connector(BN17-12P) on the iPod PCB(39-2).

7. Remove 1 screws(S15) and then remove the XM PCB(39-4).

<13>RS232 PCB(37-7) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Hudson PCB(42), referring to

the previ

ous step<9>.

3. Remove the Video PCB(41), referring to the previous step<10>.

4. Disconnect the card cable between conne

ctor(CN47-

7P) on the iPod PCB(39-2)

and connector(CN47) on the RS232 PCB(37-7).

5.Remove 2 screws and then remove the RS232 PCB(37-7).

<14>INPUT PCB(39-1) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Tuner module(44), referring to the previous step<8>.

3. Remove the Hudson PCB(42), referring to the previ

ous step<9>.

4. Remove the Video PCB(41), referring to the previous step<10>.

5. Disconnect connector(CN20) on the the Input PCB(39-1)

from the lead wire(BN20-5P) on the Regul

6. Disconnect connector(CN22) on the Input PCB(39-1) from the lead w

7. Disconnect connector(CN18) on the Input PCB(39-1) from the lead w

8. Disconnect connector(CN10) on the Input PCB(39-1) from the lead w

9. Disconnect the card cable between connector(CN14) on the

ator PCB(B)(40-5).

ire(BN22-6P) on the Phone PCB(37-5).

ire(BN18-5P) on the Phone PCB(37-5)

ire(BN10-4P) on the Volume PCB(37-6).

Input PCB(39-1).

and connector(BN14-17P) on the Video PCB(41).

10. Disconnect the card cable between connector(CN19) on the Input PCB(39-1)

and connector(BN19-15P) on the I-Pod PCB(39-2).

11. Disconnect the card cab le between connector(CN21) on the input PCB(39-1)

and connector(BN21-7P) on XM PCB(43).

12. Disconnect the card cable between connector(CN12-21p) on the Input PCB(39-1)

and connector(CN12-21p)) on the main PCB(38-1)

13. Disconnect the card cable between connector(CN11-17p) on the Input PCB(39-1)

and connector(CN11) on the main PCB(38-1)

14. Disconnect the card cable between con

n

ector(CN72) on the Input PCB(39-1)

and connector(CN72-17p) on the Fip PCB(37-1)

15. Remove 11 screws(S8,S15) and then remove the Inp ut PCB(39-1).

<15>POWER TRANS(36) & POWER PCB ASS’Y(40) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Disconnect lead wire of the Power Trans(36) from connector (CN91-3P) on the Main PCB(38-1)

3. Disconnect connector(CN19-3P,CN20-4P) on TRANS PCB(40-3)

Page 10

from the lead wire(BN19-3P,BN20-4P) on the Main PCB(38-1).

harman/kardon

AVR247/230 Service Manual

Page 10 of 131

4. Disconnect the lead wire(BN96-8P) on the Power PCB(40-4)

from connector(CN96) on the Regulator PCB(B)(40-5).

5. Disconnect the lead wire(BN99-8P) on the Power PCB(40-4)

from connector(CN99) on the Regulator PCB(A)(40-2).

6. Disconnect connector(CN81) on the Trans PCB(40-4) from the lead

wire(BN81-8P) on the Fip PCB(37-1).

7. Remove 4 Trans screws(S9) and then remove the Power Trans(36)& Power PCB ASS’Y(40) REMOVAL .

<16>REMOTE PCB ASS’Y(40-7) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2.Disconnect connector(CN88) on the remote PCB(40-7) from

the lead wire(BN88-6P) on the Main PCB(38-1)

3. Remove 3screws(S13) and then remove the Remote PCB ASS’Y(40-7).

<17>MAIN PCB ASS’Y(38-1) REMOVAL

1. Remove the Top-cabinet, referring to the previous step<1>.

2. Remove the Tuner module(44), referring to the previous step<8>.

3. Remove the Hudson PCB(42), referring to

the previ

ous step<9>.

4. Remove the Video PCB(41), referring to the previous step<10>.

5. Remove the iPod PCB(39-2), referring to the previous step<11>.

6. Remove the XM PCB(39-4), referring to the previous step<12>.

7. Remove the RS232 PCB(37-7), referring to the previous step<13>.

8. Remove the Input PCB(39-1), referring to the previ

ous step<14>.

9. Remove the AC Cord(35) on the Main PCB(38-1)

10. Disconnect the lead wire(BN90-2P) on the Main PCB(38-1) from connector(CN86) on Moms PCB(37-4).

11. Disconnect conn ector (CN91-3P) on the Main PCB(38-

1) from lead wire of the Power Trans(36)

12. Disconnect the lead wire(BN89-2P) on the Main PCB(38-1)

from connector(CN89) on Regulator PCB(A)(40-2).

13. Disconnect the lead wire(BN19-3P,BN20-4P) on the Main PCB(38-1)

from connector(CN19-3P,CN20-4P) on TRANS PCB(40-4).

14. Disconnect the lead wire(BN88-6P) on the Main PCB(38

15. Disconnect the lead wire of the DC, FAN(49) from connector(CN

16. Remove 11screws(S13-1EA, S4-2EA, S6-2EA, S8-6EA) and then

-1) from connector(CN88) on remote PCB(40-7).

89-2P) on the Main PCB(38-1).

remove the Main PCB ASS’Y(38-1).

Page 11

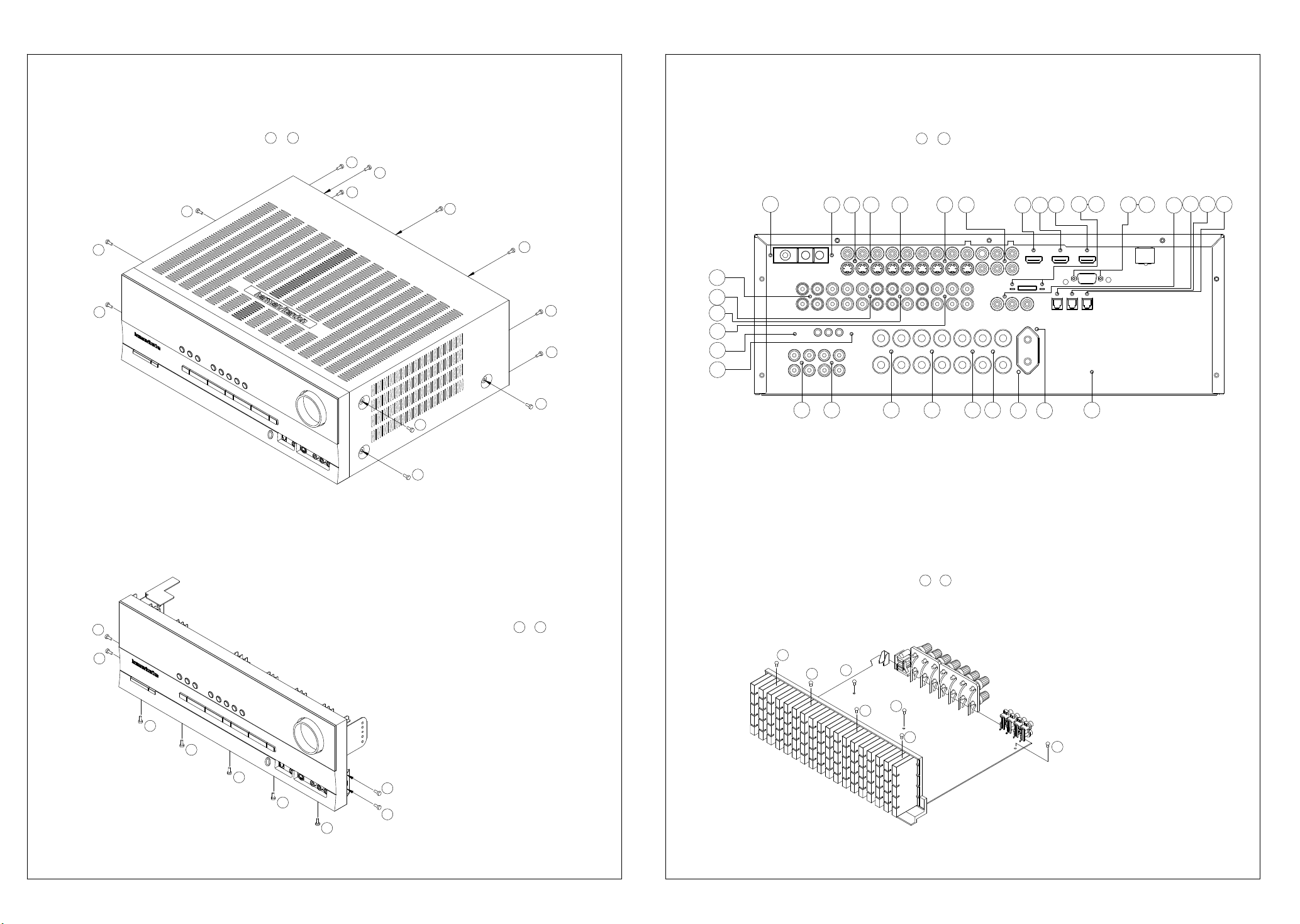

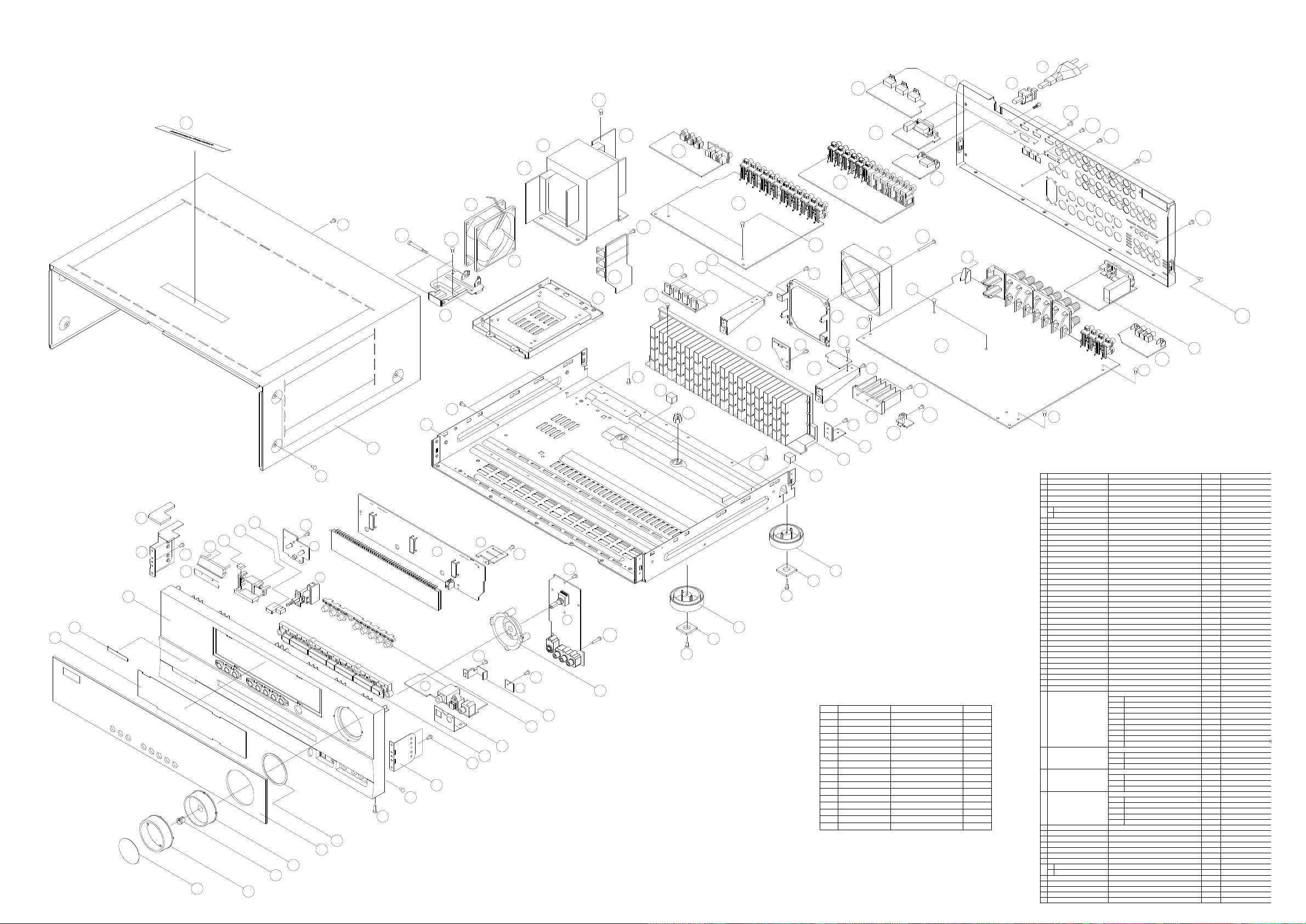

AVR247/230 EXPLODED VIEW

harman/kardon

AVR247/230 Service Manual

Page 11 of 131

35

42

33

S9

47

36

40-1

40-3

37-7

40-4

41

39-2

34

S15

S13

S13

S8

S5

40-2

23

39-1

24

38-2

S10

S13

S15

48

S16

32

S5

S6

x2

18

S4

39-5

S4

S5

38-1

43

40-7

S4

S4

S10

S12

30

51

S5

40-2

S14

S4

27

26

REMARK

DESCRIPTION

25

24

23

S4

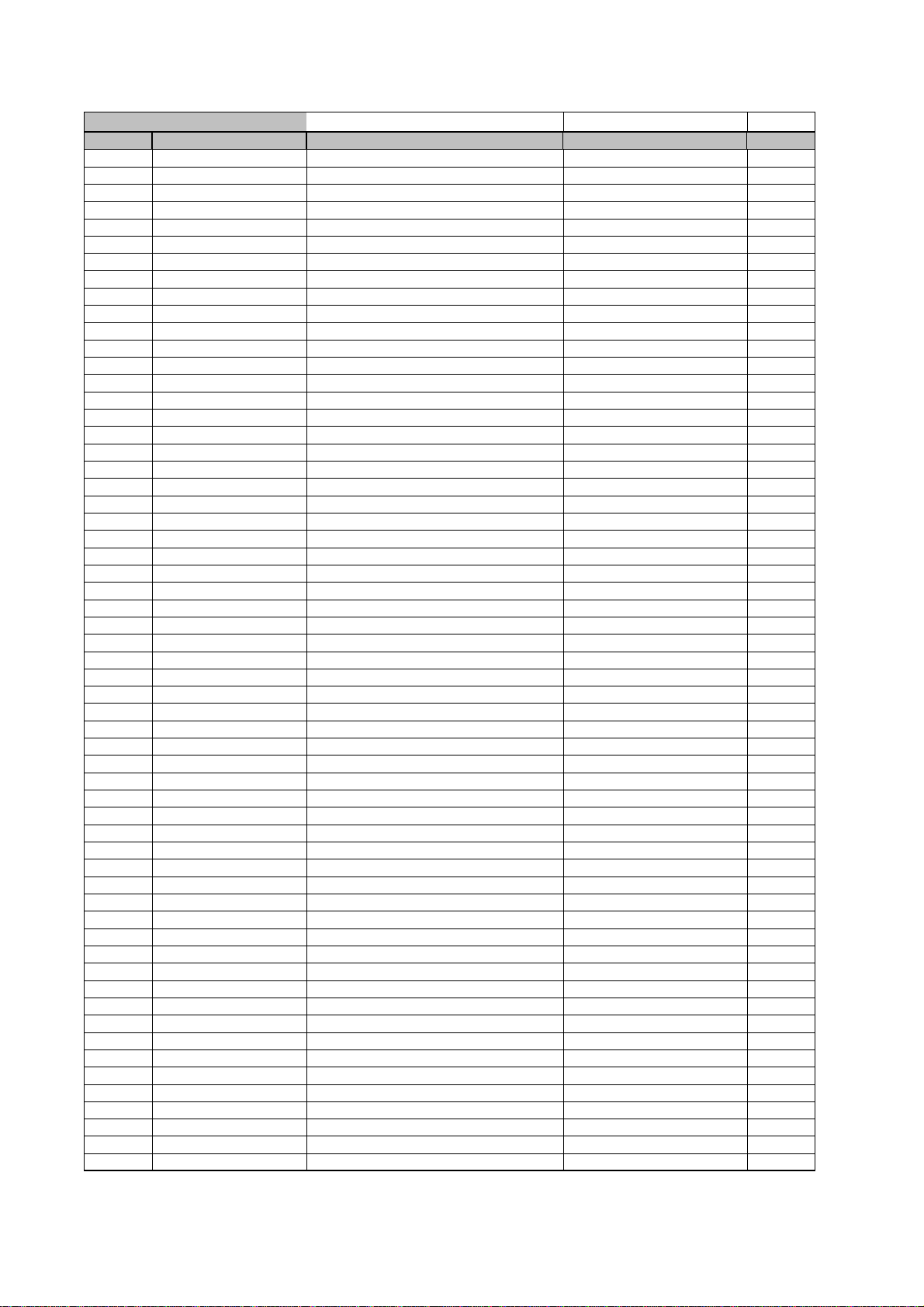

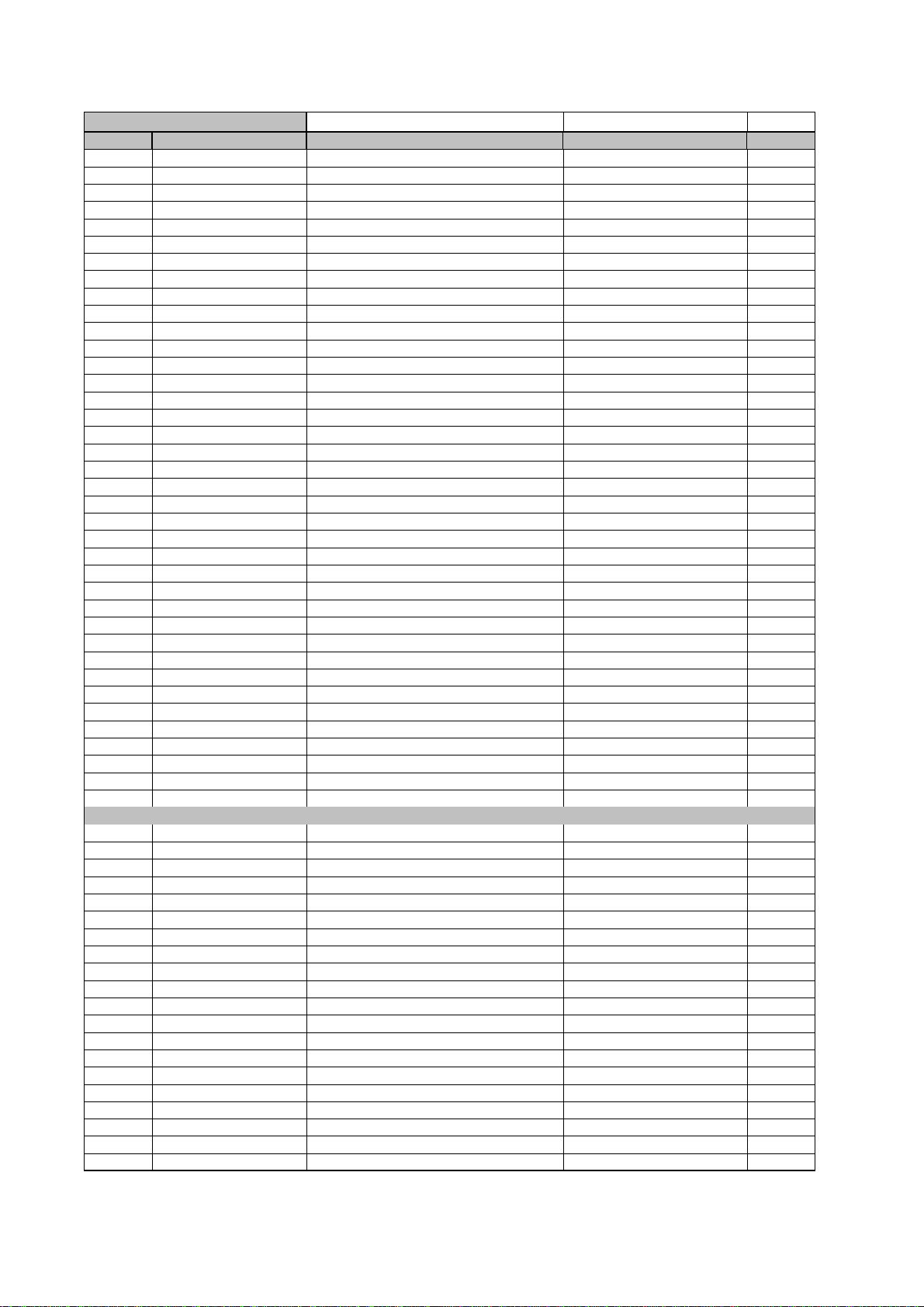

DESCRIPTION PARTS NO. Q,ty

NO

S1

SCREW

S2

S3

SCREW

S4

SCREW

S5

SCREW

S6

SCREW

S7

SCREW

S8

SCREW,TRANS

S9

SCREW

S10

SCREW

S11

SCREW

S12

SCREW

S13

SCREW,SPECIAL CHD1A012R 21

S14

SCREW,SPECIAL CHD1A012ZR 2

S15

SCREW,SPECIAL CHD3A012R 7

S16

SCREW,SPECIAL CHD4A012R 5

S17

CTB3+10GR

CTW3+8JR

CTB3+8JR

CTW3+12JR

CTB4+6FFC

CTB3+10GFZR

CHD1A023R

CTB3+6JR

CTB3+16GFZR

CTB3+10JRR

CTB3+8FFZR

13CTB3+8JFCSCREW

31

9

10

3

6

22

4

19

2

3

8

NO

ORNAMENT,VOLUME CGU1A318Z 1

1

CAP,VOLUME

2

HOLDER,VOLUME

3

INDICATOR,VOLUME

4

WINDOW ASS'Y

5

WINDOW,FIP CGU1A399Y

1

BADGE,MODEL

2

6

FILTER,FIP

7

BDAGE,HARMAN/KARDON

8

PANEL,FRONT

9

BRACKET,SIDE

10

KNOB,FUNCTION

11

KNOB,DISPLAY

12

KNOB,POWER

13

INDICATOR,POWER

14

KNOB,MOMS

15

BRACKET,PCB CMK2A010

16

PLATE,SHIELD

17

BRACKET , FAN CMD1A600 1

18

HOLDER,LED

19

BRACKET,FIP

20

CABINET,TOP

21

CHASSIS,BOTTOM

22

RUBBER,CUSHION

23

FOOT

24

SUPPORT,CUSHION

25

HEAT SINK

26

BRACKET,PCB

27

HOLDER,PCB

28

BRACKET,TRANS

29

BRACKET,PCB(H/T)

30

BRACKET,PCB CMD1A570 1

31

BRACKET,PCB

32

PANEL,REAR

33

BUSHING,AC CORD

34

CORD,POWER

35

TRANS,POWER

36

FRONT PAB ASS'Y

37

MAIN PCB ASS'Y COP11911O 1

38

INPUT PCB ASS'Y COP11913O 1

39

POWER PCB ASS'Y

40

VIDEO PCB ASS'Y

41

HUDSON PCB ASS'Y COP11915O 1

42

TUNER MODULE

43

44

RUBBER

45

46

BADGE ASS'Y

47

ORNAMENT,BADGE

1

BADGE,H/K(TOP)

2

FAN(80*80*25mm)

48

BEACKET,FAN(A) CMD1A615 1

49

SHEET,REFLECTION CMZ1A120 1

50

HEAT SINK CMY2A249 1

51

PARTS NO.

CGX1A338MBC63

CMH1A214

CGL1A222

CGUAVR247

CGB1A179Z

CMZ2A090SHEET,VOLUME 1

CMZ1A088

KGB1A158Z

CGW1A427RDNH43

CMD2A443

CBT1A1028MBYG27

CBT1A1027K128

CBT1A1026MMZG27

CGL1A258Z

CBC1A158MBZG27

CMC1A302

CMH1A215

CMD1A209

CKC5B145S46Z

CUA3A229

CHG1A329

CKL2A069H43

CHG1A104Z

CMY1A271

CMD1A417

CHE1A170

CMD2A487

CMD1A398

CMD1A387

CKF12A319Z

KHR1A028

CJA2B043ZA

CLT5W026ZE

COP11910O

FIP PCB

37-1

KEY PCB

37-2

POWER LED PCB

37-3

MOMS PCB

37-4

PHONE PCB

37-5

VOLUME PCB

37-6

RS232 PCB

37-7

GUIDE PCB(CARD CABLE)

37-8

MAIN PCB

38-1

GUIDE PCB(CARD CABLE) 1

38-2

INPUT PCB

39-1

ipod PCB 1

39-2

RDS PCB 1

39-5

COP11916O 1

VIDEO PCB 1

40-1

REGULATOR PAC(A) 7

40-2

TRANS PCB 1

40-3

TRANS PCB 1

40-4

REGULATOR PCB(B) 1

40-5

COP11918O 1

CNVM9014MS171L

CHG1A309

CHG1A160ZCUSHION 1

CGX1A375ZA

CGX1A375M7G32

KGB1A159Z

CFNCF12825MS

Q,ty

1

1

1

1

1

1

1

1

1

1

11

1

1

1

1

1

1

1

3

1

1

4

4

1

1

2

2

1

2

2

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1CMD1A555BRACKET,SIDE(L)

1

1

1

1

2

48

S1

S16

S9

47

29

40-5

S16

S17

S16

30

49

S5

46

S5

28

22

21

S7

45

44

14

S2

50

14-1

15

13

S2

37-3

37-1

37-4

37-8

S2

S2

9

8

7

S2

37-5

37-9

37-6

S11

S4

S2

19

16

12

17

11

S2

10

S1

S1

6

5

4

3

1

2

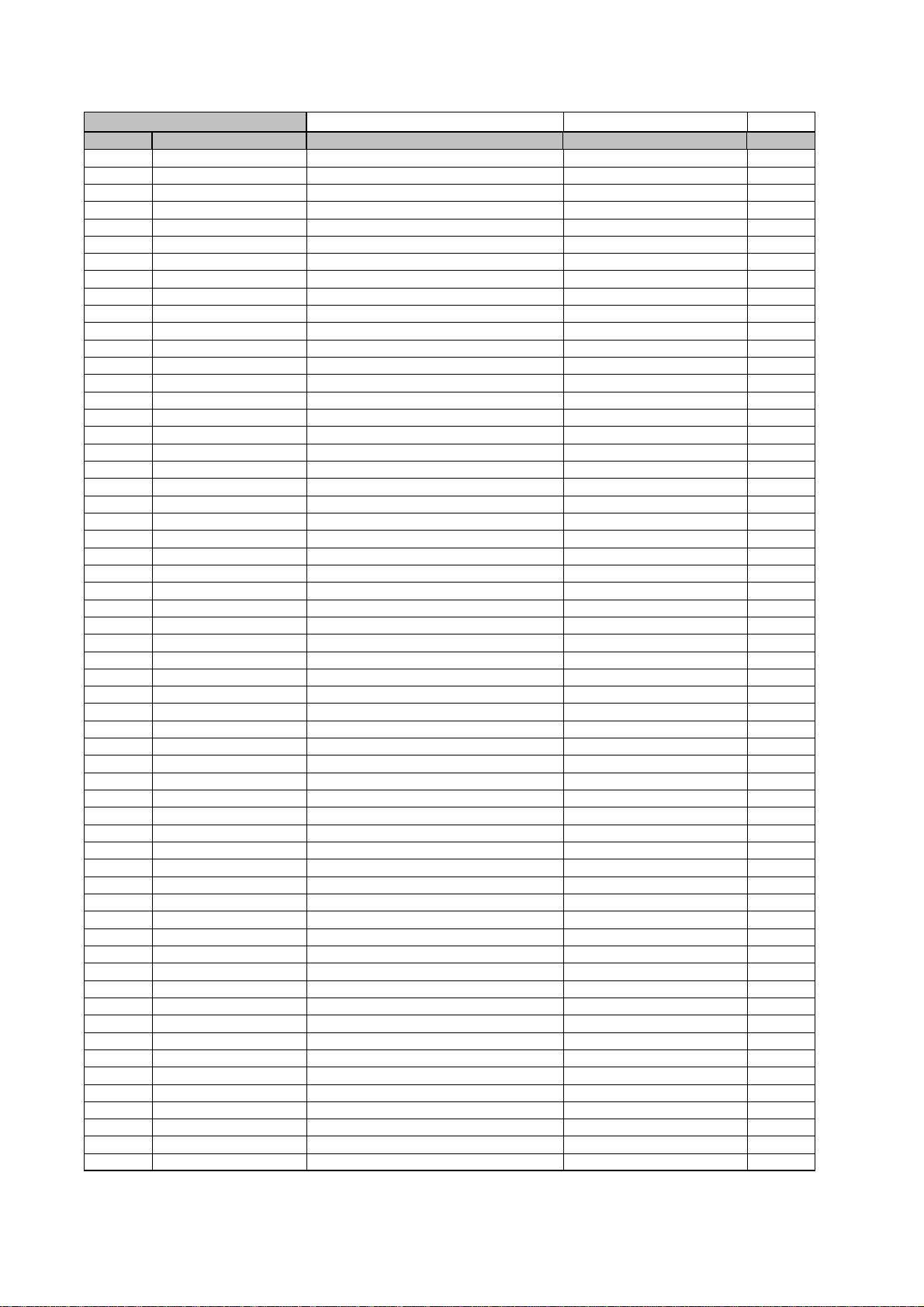

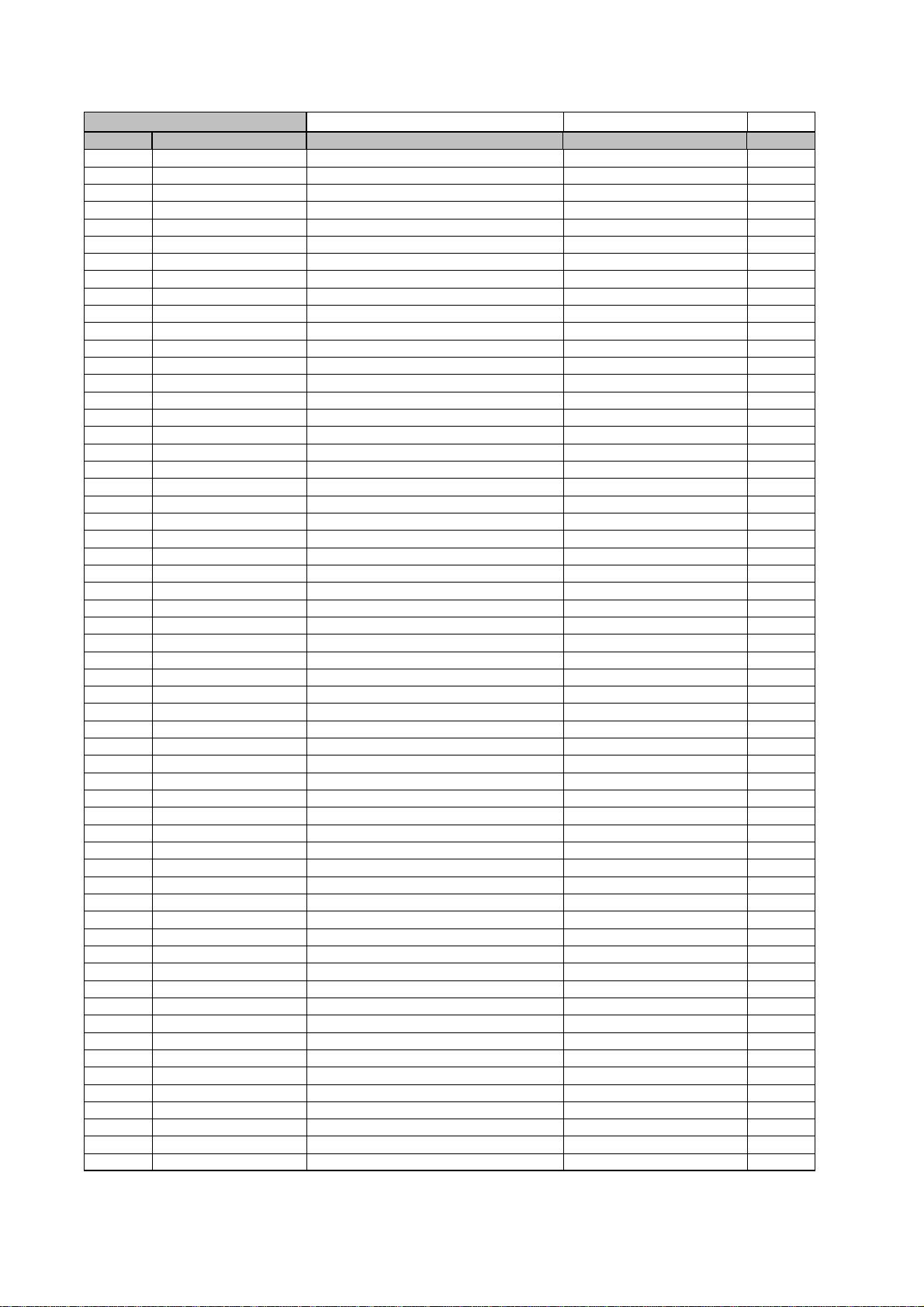

Page 12

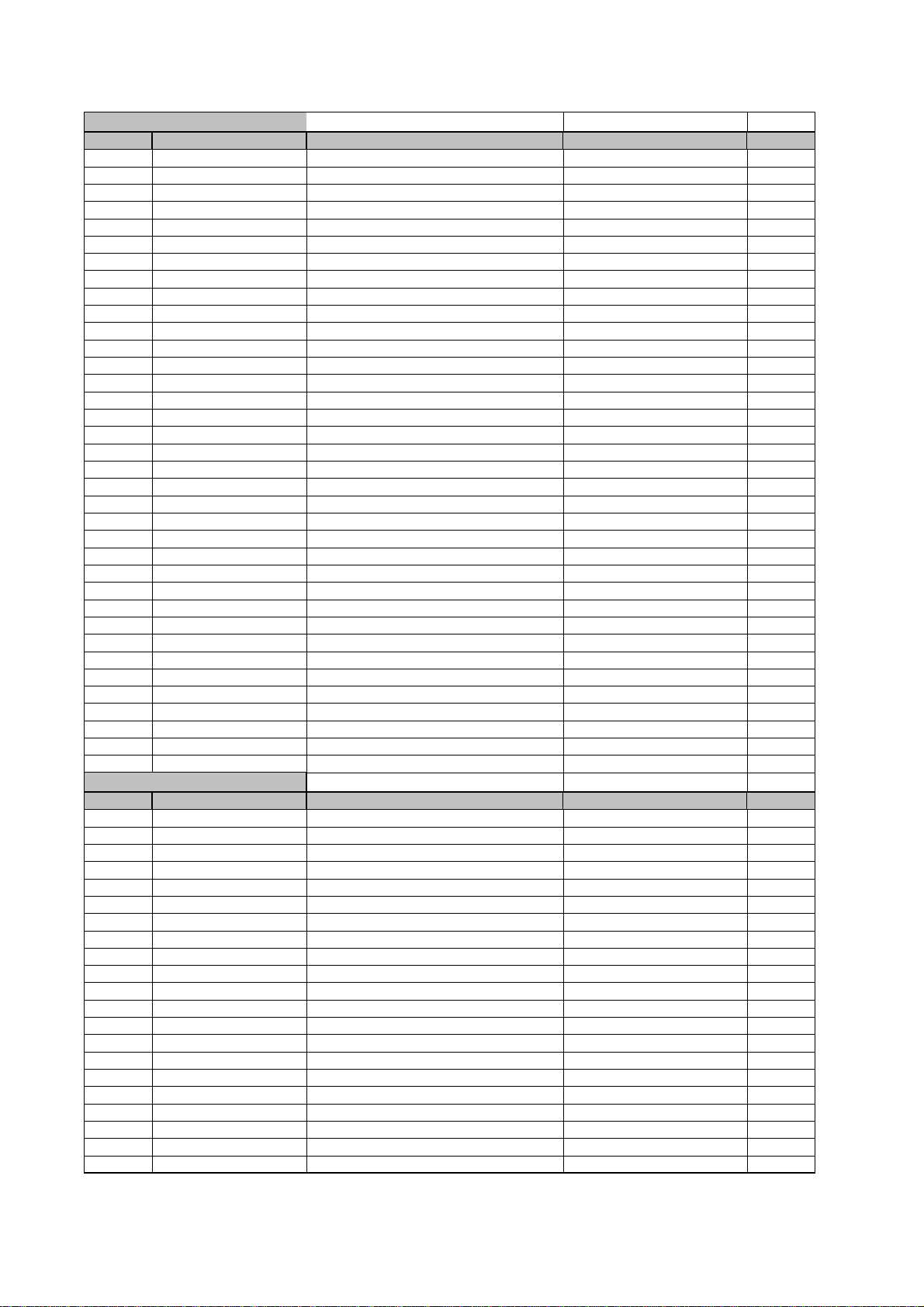

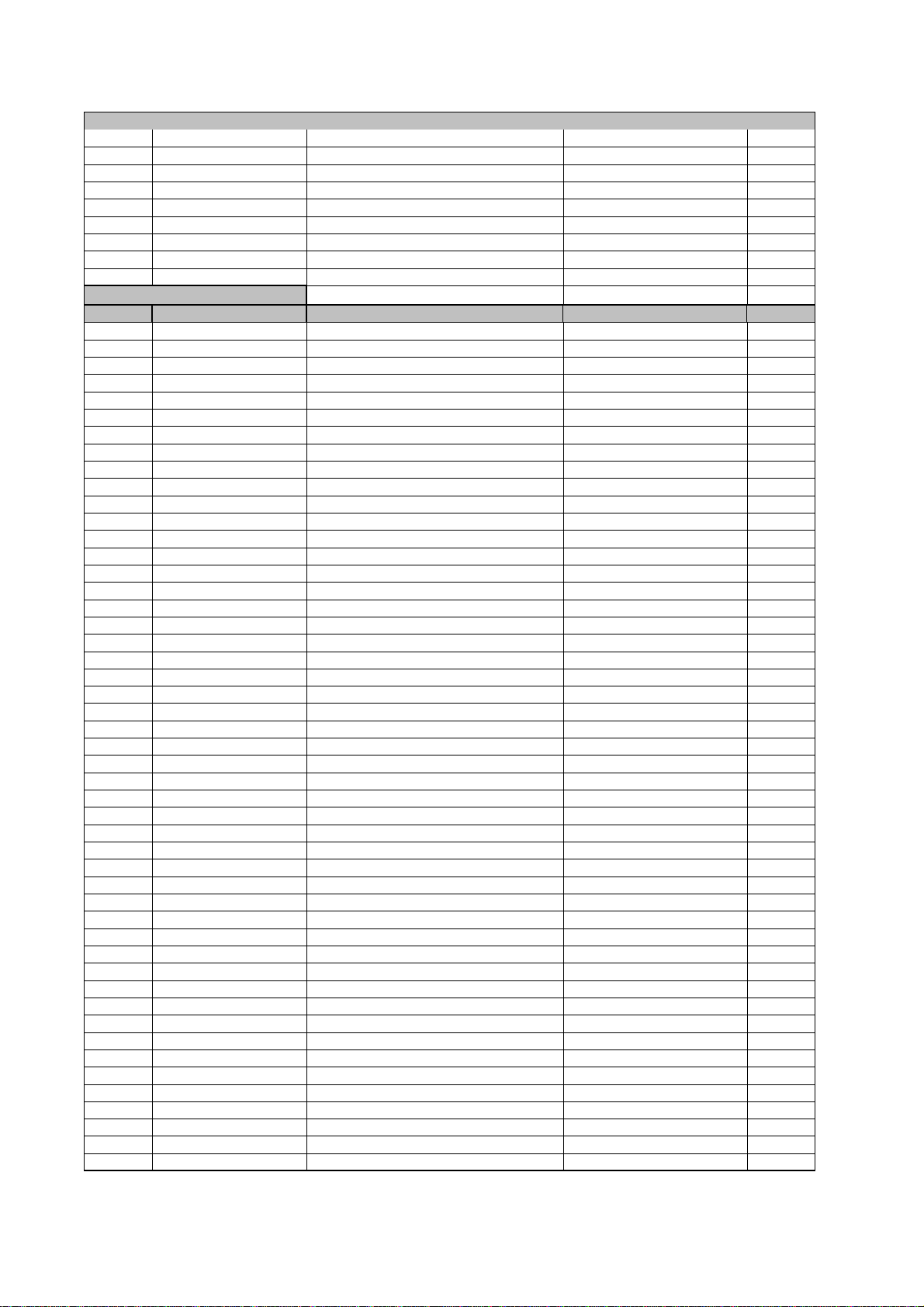

AVR247/230 Electrical Parts List

harman/kardon

AVR247/230 Service Manual

Page 12 of 131

Ref. # Part Number

CGL1A222 INDICATOR , VOLUME INDICATOR 1

CGUAVR247/230 WINDOW ASS'Y ASS'Y 1

CGB1A179Z BADGE, HARMAN(AVR247/230) BADGE 1

CGU1A399Y WINDOW , FIP FIP WINDOW 1

CGU1A318Z ORNAMENT , VOLUME ORANMENT 1

CGX1A338MBC63 CAP , VOLUME CAP 1

CGX1A375ZA BADGE ASS'Y ASS'Y 1

CHE36-3 CLAMPER , WIRE CLAMPER 1

CKC5B145S46Z CABINET , TOP TOP CABINEET 1

BKC5C145S46 CABINET , TOP TOP CABINEET 1

CLZ9Z028Z FERRITE CORE(21.2X6.4X12.7) FERRITE CORE 3

CMH1A214 HOLDER , VOLUME HOLDER 1

CMZ2A090 SHEET , VOLUME SHEET 1

CQB1A549Y LABEL , ATTENTION DVD48 LABEL 1

CQB1A551Z LABEL , BAR CODE LABEL 1

CQB1A622 LABEL , SERIAL NO LABEL 1

CQB1A797Z LABEL , HDMI LABEL 2

CTB3+8JFC SCREW SCREW 13

CTB4+6FFC SCREW SCREW 6

CHE154 CLAMPER , ARM CLAMPER 0,12

CJXAVR340MICRO MICRO PHONE ASS'Y ASS'Y 1

CPG1A822U BOX , OFFSET CARTON BOX 1

CPP1A081Z BAG,POLY SET BAG 1

CPS6A564 PAD , SNOW L SNOW PAD 1

CPS6A565 PAD , SNOW R SNOW PAD 1

CQB1A551Z LABEL , BAR CODE LABEL 2

CQB1A795Z LABEL , COUNTRY AVR245/230 LABEL 2

CQS1A001 RIBON , BAR CODE SONY(TR-4070) 0,12

CQXAVR247/230 INSTRUCTION MANUAL ASS'Y ASS'Y 1

CABR03P3 BATTERY (SIZE 'AAA') 3PCS IN 1 BATTERY 3

CARTAVR247/230 REMOCON TRANSMITTER ASS'Y ASS'Y 1

CGRAVR130/230ZA COVER ASS'Y ASS'Y 1

CGR1A331M7H43 COVER A COVER 1

CGR1A332M7H43 COVER B COVER 1

CPS1A676 PAD , COVER PAD 1

CQE1A220Z SHEET , FRONT COVER SHEET 1

CQE1A180Z BOOKLET , IMFORMATIONS BOOKLET 1

CQX1A1255Z MANUAL , INSTRUCTION AVR247/230 SHEET 1

CQX1A1256Z MANUAL , SET UP AVR147/230 MANUAL 1

CSA1A018Z FM 1 POLE ANT ANT 1

CSA1A027Z AM LOOP ANT ANT 1

HQE1A273Z HARMAN IMAGE BROCHURES BROCHURES 1

CRE1A037 LOCKER LOCKER 14

Description

Value Qty

FRONT PANEL ASSY

Ref. # Part Number

Description

Value Qty

CGWAVR247/230 FRONT PANEL ASS'Y ASS'Y 1

CBC1A158MBZG27 KNOB , MOMS KNOB 1

CBT1A1026MMZG27 KNOB , POWER KNOB 1

CBT1A1027K128 KNOB , DISPLAY KNOB 1

CBT1A1028MBYG27 KNOB , FUNCTION KNOB 1

CGL1A258Z INDICATOR , POWER INDICATOR 1

CGW1A427RDNH43 PANEL , FRONT AVR247/230 PANEL 1

CHG1A309 RUBBER RUBBER 1

CHR301 CLAMPER CLAMPER 20

CLZ9Z028Z FERRITE CORE(21.2X6.4X12.7) FERRITE CORE 4

CMC1A302 PLATE , SHIELD PLATE 1

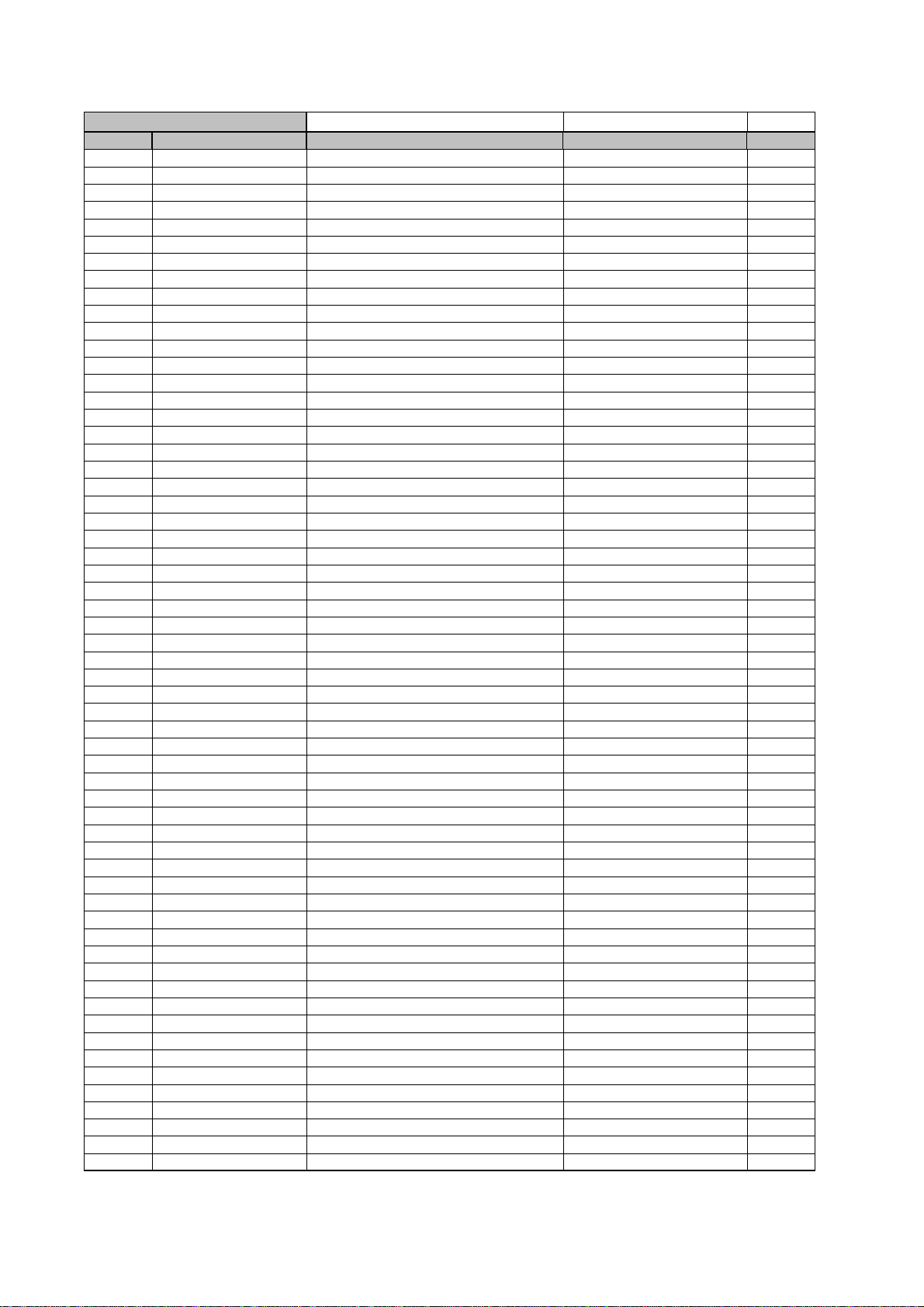

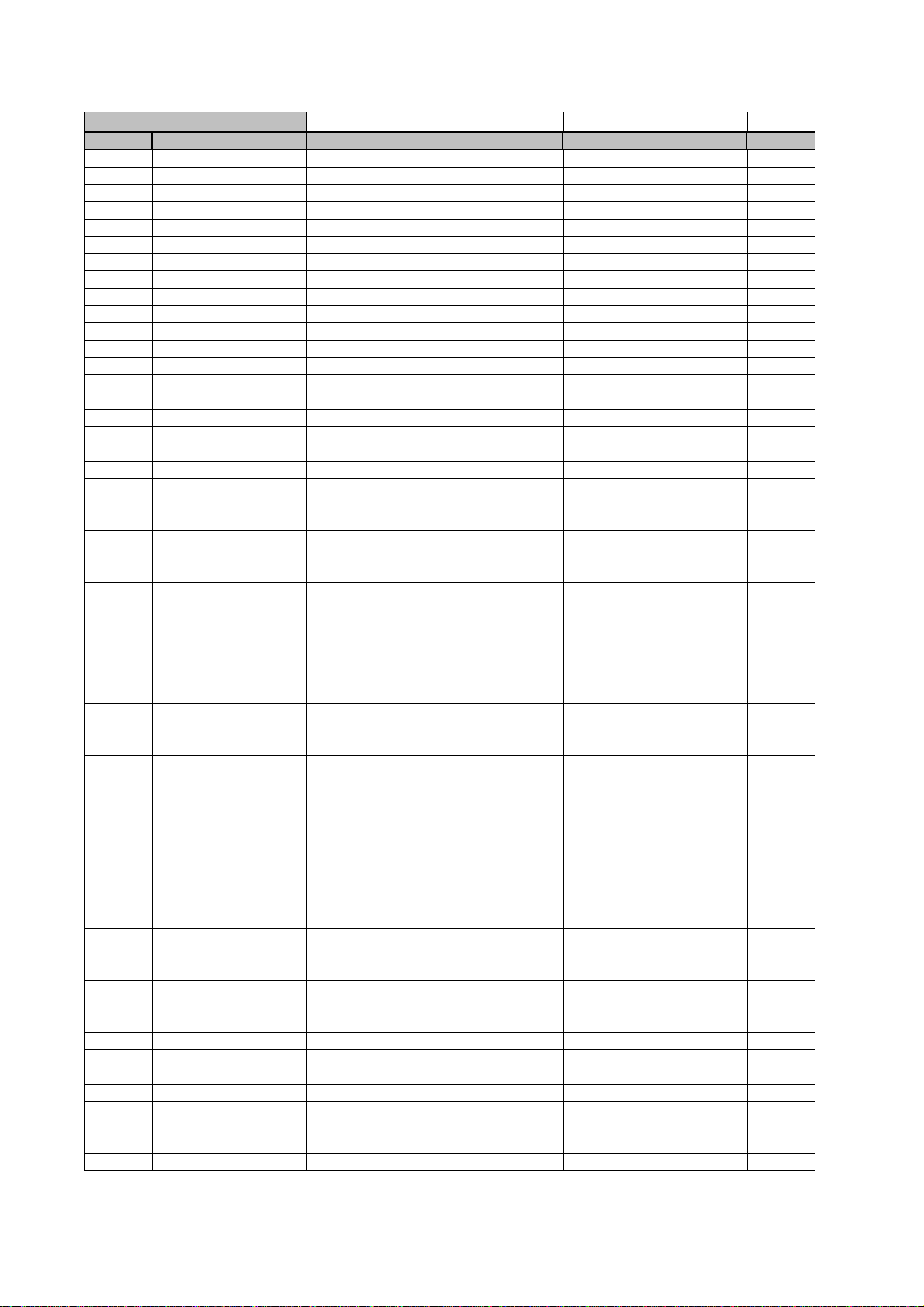

Page 13

FRONT PANEL ASSY

harman/kardon

AVR247/230 Service Manual

Page 13 of 131

Ref. # Part Number

CMD1A555 BRACKET , SIDE (L) BRACKET 1

CMD2A443 BRACKET , SIDE BRACKET 1

CMH2A215 HOLDER , LED AVR350 HOLDER 1

CMK2A010 BRACKET , PCB BRACKET 1

CMZ1A088 FILTER , FIP FIP FILTER 1

CMZ1A120 SHEET , REFLECTION SHEET 1

CTB3+10GR SCREW SCREW 31

CTB3+16GFZR SCREW SCREW 2

KGB1A158Z BADGE , HARMAN/KARDON(FRONT) BADGE 1

CB72 CWCAVR350CN72 CABLE , SHIELD CARD(17PIN, 240MM) CARD CABLE(SHILED) 1

Description

Value Qty

FRONT PCB ASSY

Ref. # Part Number

COP11910O AVR247/230 FRONT PCB ASS'Y ASS'Y 1

CMC3A111 PLATE , EARTH PLATE 1

CMD1A618 BRACKET , RESET BRACKET 1

C402 CCEA1HH100T CAP , ELECT 10UF 50V 1

C403 CCEA1HH100T CAP , ELECT 10UF 50V 1

C714 HCBS1H151KBT CAP , CERAMIC 150UF 50V K 1

C716 CCEA1AH331T CAP , ELECT 330UF 10V 1

C719 HCBS1H102KBT CAP , CERAMIC 1000PF 50V K 1

C720 HCBS1H102KBT CAP , CERAMIC 1000PF 50V K 1

C721 HCBS1H102KBT CAP , CERAMIC 1000PF 50V K 1

C723 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C728 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C729 HCBS1H473ZFT CAP , CERAMIC 0.047UF 50V Z 1

C731 CCEA1HH100T CAP , ELECT 10UF 50V 1

C735 CCEA1CKS100T CAP , ELECT 10UF 16V 1

C742 HCBS1H223ZFT CAP , CERAMIC 0.02UF 50V Z 1

C793 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C794 HCBS1C222MXT CAP , CERAMIC 2200PF 16V 1

C795 HCBS1H102KBT CAP , CERAMIC 1000PF 50V K 1

C796 HCBS1H102KBT CAP , CERAMIC 1000PF 50V K 1

C805 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C806 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C807 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C808 HCBS1H181KBT CAP , CERAMIC 180PF 50V 1

C809 CCEA1AH471T CAP , ELECT 470PF 10V 1

C812 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C817 HCBS1H100JCT CAP , CERAMIC 10PF 50V 1

C820 CCEA1HH100T CAP , ELECT 10UF 50V 1

C821 CCEA1EH470T CAP , ELECT 47UF 25V 1

C822 CCEA1EH470T CAP , ELECT 47UF 25V 1

C823 CCEA1HH100T CAP , ELECT 10UF 50V 1

C824 HCBS1H471KBT CAP , CERAMIC 470PF 50V 1

C825 HCBS1H151KBT CAP , CERAMIC 150PF 50V 1

C828 HCBS1H470JT CAP , CERAMIC 47PF 50V 1

C830 HCBS1H473ZFT CAP , CERAMIC 0.047F 50V 1

C841 CCEA1HH100T CAP , ELECT 10UF 50V 1

C842 CCEA1HH100T CAP , ELECT 10UF 50V 1

C843 CCEA1HH100T CAP , ELECT 10UF 50V 1

C850 HCBS1H471KBT CAP , CERAMIC 470PF 50V 1

C851 HCBS1H471KBT CAP , CERAMIC 470PF 50V 1

C852 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C855 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C856 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C857 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C862 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

Description

Value Qty

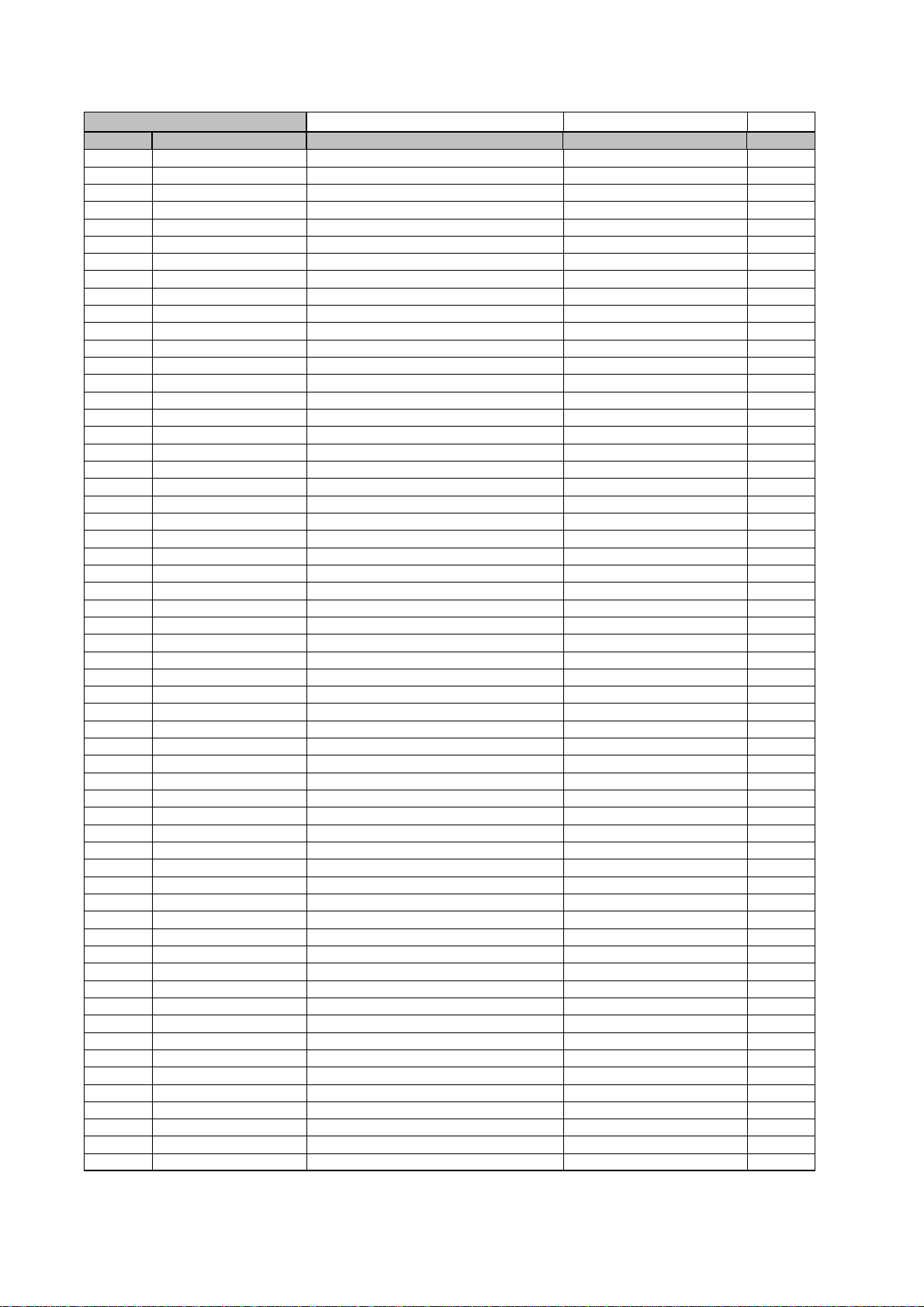

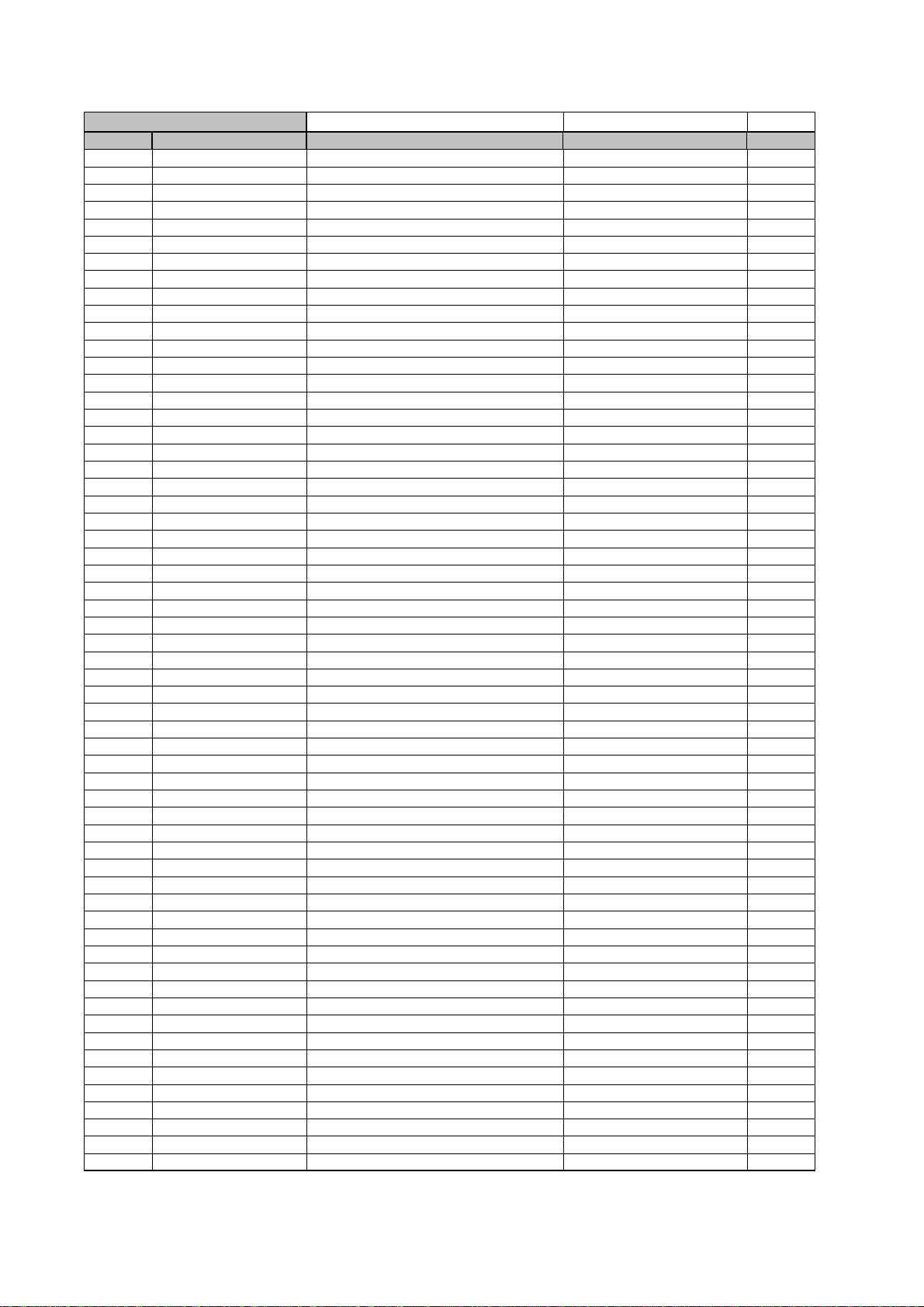

Page 14

FRONT PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 14 of 131

Ref. # Part Number

C863 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C866 CCEA1HKS100T CAP , ELECT 10UF 50V SMALL SIZE 1

C867 CCEA1HKS100T CAP , ELECT 10UF 50V SMALL SIZE 1

C868 CCEA1EKS470T CAP , ELECT 47UF 25V 1

C869 CCEA1EKS470T CAP , ELECT 47UF 25V 1

C870 HCBS1H681KBT CAP , CERAMIC 680PF 50V K 1

C871 HCBS1H681KBT CAP , CERAMIC 680PF 50V K 1

C872 CCEA1CH331T CAP , ELECT 330UF 16V 1

C873 CCEA1CH331T CAP , ELECT 330UF 16V 1

C874 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C882 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C889 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C891 HCBS1H223ZFT CAP , CERAMIC 0.023UF 50V Z 1

C892 HCBS1H223ZFT CAP , CERAMIC 0.023UF 50V Z 1

C893 HCBS1H223ZFT CAP , CERAMIC 0.023UF 50V Z 1

C894 CCEA1CKS100T CAP , ELECT 10UF 16V 1

C896 HCBS1H223ZFT CAP , CERAMIC 0.023UF 50V Z 1

C897 CCEA1AH471T CAP , ELECT 470UF 10V 1

C901 HCBS1H390JT CAP , CERAMIC 39PF 50V Z 1

C903 CCEA1HKS2R2T CAP , ELECT 2.2UF 50V 1

C905 CCEA1HKS2R2T CAP , ELECT 2.2UF 50V 1

C953 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C954 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C957 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

D455 CVD1SS133MT DIODE 1SS133 1

D730 CVD1SS133MT DIODE 1SS133 1

D774 CVD1SS133MT DIODE 1SS133 1

D778 HVD1N5819T DIODE , SCHOTTKY 1N5819 1

D784 CVD1SS133MT DIODE 1SS133 1

D785 CVD1SS133MT DIODE 1SS133 1

J906 CRD20TJ391T RES , CARBON 390OHM 1/5W 1

L702 HLQ02C100KT COIL , AXAIL 10uH 1

Q401 HVTKRC104MT T.R KRC104M 1

Q451 HVTKRC107MT T.R KRC107M 1

Q452 HVTKRA107MT T.R KRA107M 1

Q454 HVTKRC107MT T.R KRC107M 1

Q701 HVTKRC107MT T.R KRC107M 1

Q722 HVTKRA107MT T.R KRA107M 1

Q724 HVTKRC107MT T.R KRC107M 1

Q725 HVTKRC107MT T.R KRC107M 1

Q734 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q735 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q736 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q737 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q738 HVTKRC107MT T.R KRC107M 1

Q739 HVTKTA1271YT T.R KTA1271Y 1

R402 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R403 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R404 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R452 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R453 CRD20TJ362T RES , CARBON 3.6K OHM 1/5W J 1

R454 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R701 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R704 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R705 CRD20TJ820T RES , CARBON 82 OHM 1/5W J 1

R706 CRD20TJ820T RES , CARBON 82 OHM 1/5W J 1

R708 CRD20TJ820T RES , CARBON 82 OHM 1/5W J 1

R709 CRD20TJ470T RES , CARBON 47 OHM 1/5W J 1

R710 CRD20TJ470T RES , CARBON 47 OHM 1/5W J 1

Description

Value Qty

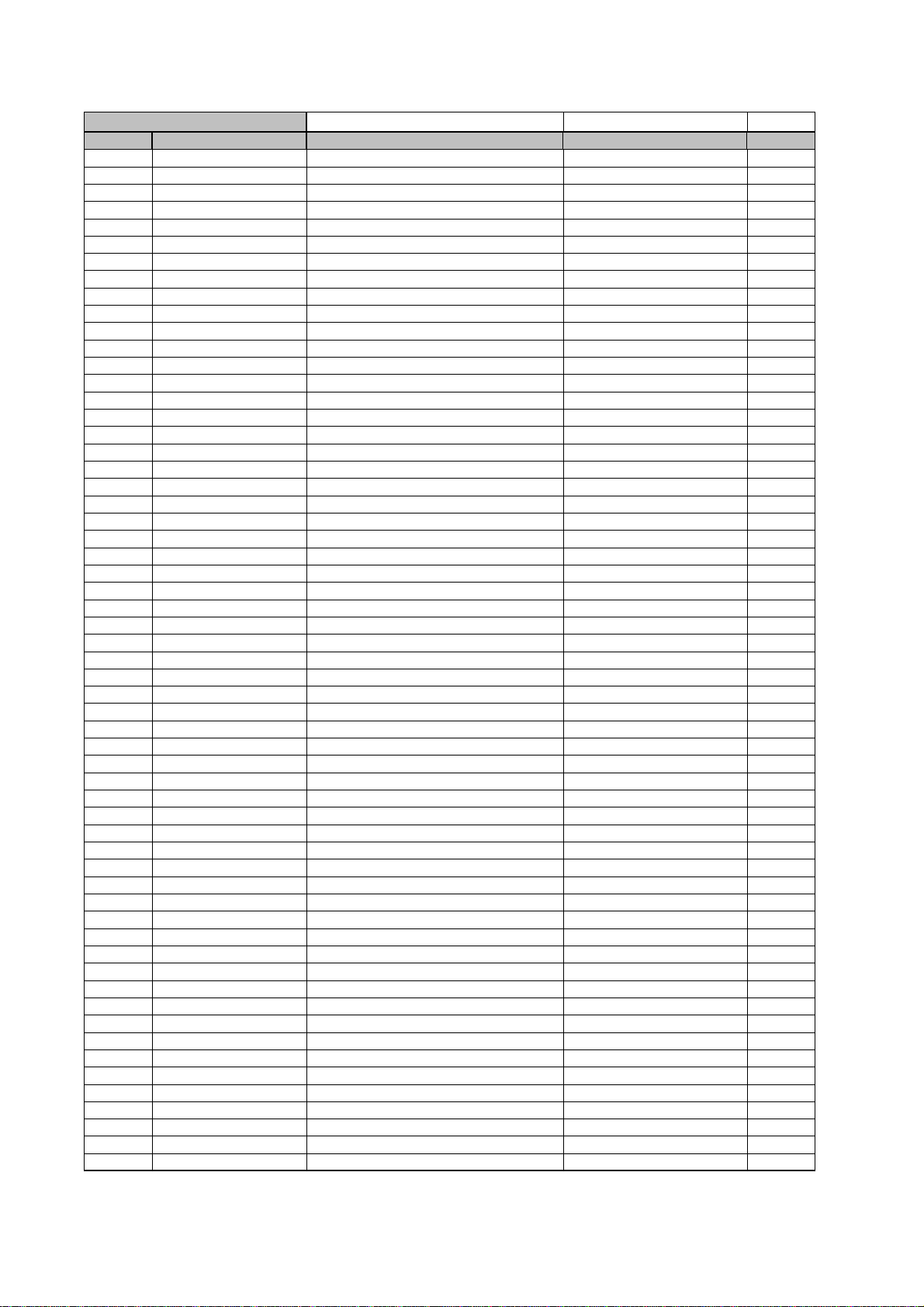

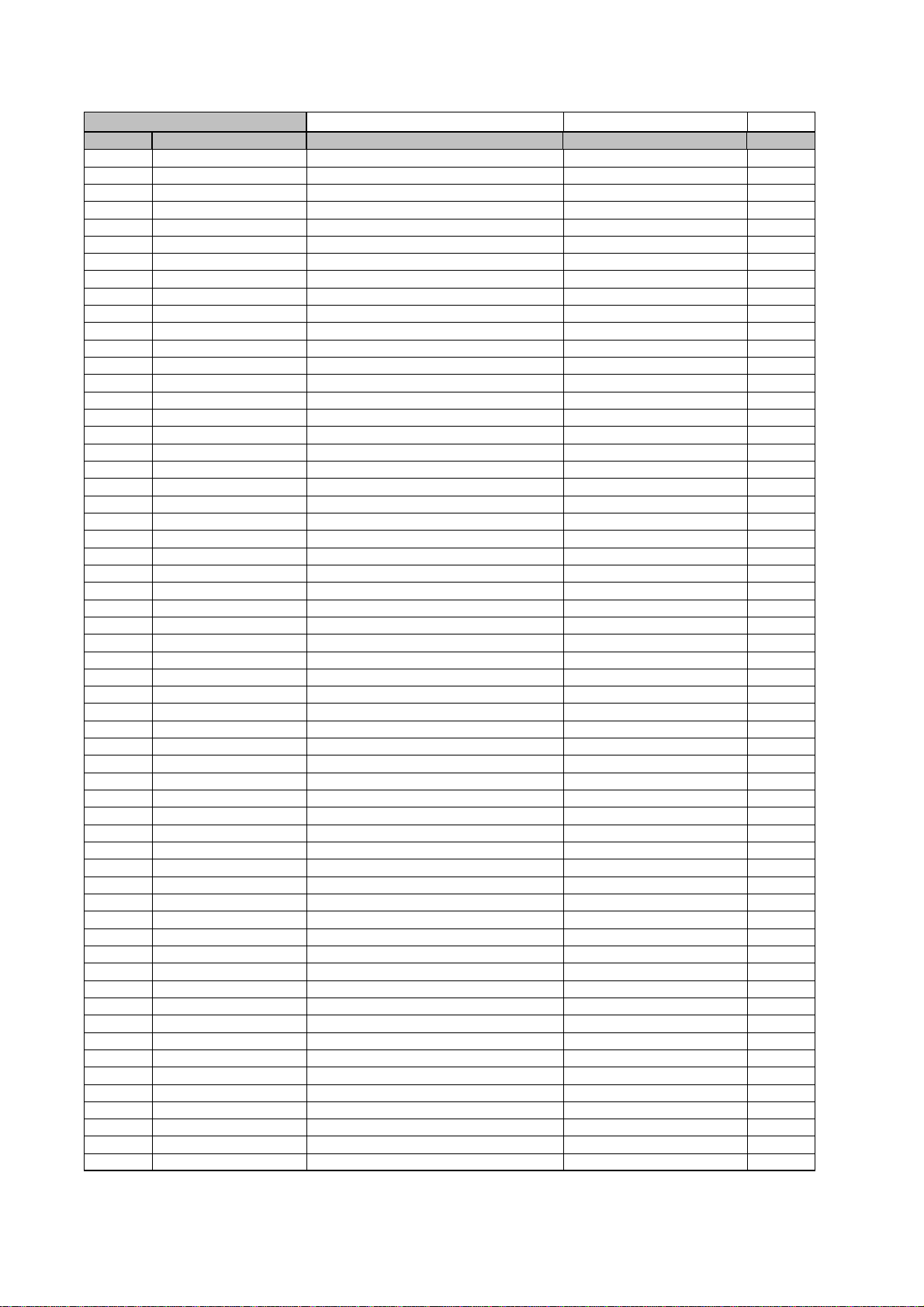

Page 15

FRONT PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 15 of 131

Ref. # Part Number

R711 CRD20TJ470T RES , CARBON 47 OHM 1/5W J 1

R718 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R737 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R747 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R753 CRD20TF1001T RES , CARBON 1K /1/5W /F 1

R754 CRD20TF1501T RES , CARBON 1.5K /1/5W /F 1

R755 CRD20TF1801T RES , CARBON 1.8K /1/5W /F 1

R756 CRD20TF2701T RES , CARBON 2.7K /1/5W/F 1

R757 CRD20TF3301T RES , CARBON 3.3K /1/5W/F 1

R758 CRD20TF5601T RES , CARBON(5.6K/F) 5.6K 1/5W F 1

R759 CRD20TF1001T RES , CARBON 1K /1/5W /F 1

R760 CRD20TF1501T RES , CARBON 1.5K /1/5W /F 1

R761 CRD20TF1801T RES , CARBON 1.8K /1/5W /F 1

R762 CRD20TF2701T RES , CARBON 2.7K /1/5W/F 1

R763 CRD20TF3301T RES , CARBON 3.3K /1/5W/F 1

R764 CRD20TF5601T RES , CARBON(5.6K/F) 5.6K/1/5W/F 1

R765 CRD20TF7501T RES , CARBON (7.5K/F) 7.5K/1/5W/F 1

R766 CRD20TF1001T RES , CARBON 1K /1/5W /F 1

R767 CRD20TF1501T RES , CARBON 1.5K /1/5W /F 1

R768 CRD20TF1801T RES , CARBON 1.8K /1/5W /F 1

R769 CRD20TF2701T RES , CARBON 2.7K /1/5W/F 1

R781 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R782 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R783 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R784 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R786 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R787 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R791 CRD20TJ822T RES , CARBON 8.2K OHM 1/5W J 1

R805 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R806 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R824 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R825 CRD20TJ681T RES , CARBON 680 OHM 1/5W J 1

R828 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R829 CRD20TJ681T RES , CARBON 680 OHM 1/5W J 1

R864 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R865 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R866 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R869 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R871 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R872 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R873 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R874 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R875 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R876 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R877 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R878 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R892 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R893 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R895 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R896 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R897 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R898 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R899 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R900 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R901 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R902 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R903 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R904 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R905 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

Description

Value Qty

Page 16

FRONT PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 16 of 131

Ref. # Part Number

R906 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R907 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R908 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R909 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R910 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R911 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R912 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R913 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R915 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R918 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R919 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R920 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R921 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R922 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R923 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R924 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R926 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R931 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R934 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R935 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R936 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R937 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R956 CRD20TJ1R0T RES , CARBON 1 OHM 1/5W J 1

S701 HST1A020ZT SW , TACT 1A020 1

S702 HST1A020ZT SW , TACT 1A020 1

S703 HST1A020ZT SW , TACT 1A020 1

S704 HST1A020ZT SW , TACT 1A020 1

S705 HST1A020ZT SW , TACT 1A020 1

S706 HST1A020ZT SW , TACT 1A020 1

S707 HST1A020ZT SW , TACT 1A020 1

S708 HST1A020ZT SW , TACT 1A020 1

S709 HST1A020ZT SW , TACT 1A020 1

S710 HST1A020ZT SW , TACT 1A020 1

S711 HST1A020ZT SW , TACT 1A020 1

S712 HST1A020ZT SW , TACT 1A020 1

S713 HST1A020ZT SW , TACT 1A020 1

S714 HST1A020ZT SW , TACT 1A020 1

S715 HST1A020ZT SW , TACT 1A020 1

S716 HST1A020ZT SW , TACT 1A020 1

S717 HST1A020ZT SW , TACT 1A020 1

S718 HST1A020ZT SW , TACT 1A020 1

S719 HST1A020ZT SW , TACT 1A020 1

S720 HST1A020ZT SW , TACT 1A020 1

BK71 CMD1A209 BRACKET , FLT BRACKET 1

BK72 CMD1A209 BRACKET , FLT BRACKET 1

BK73 CMD1A209 BRACKET , FLT BRACKET 1

BN10 CWZAVR247BN10 SHIELD WIRE ASS'Y(4P, 400mm) WIRE 1

BN18 CWZAVR125BN18 WIRE ASS'Y (SHIELD) WIRE 1

BN22 CWZAVR247BN22 SHIELD WIRE ASS'Y(6P, 550mm) WIRE 1

BN41 CWZAVR247BN41 SHIELD WIRE ASS'Y(6P, 600mm) WIRE 1

BN80 CWB2B903180EN WIRE ASS'Y WIRE 1

BN81 CWB2C908200BM WIRE ASS'Y WIRE 1

BN84 CWB2B905080EN WIRE ASS'Y WIRE 1

BN85 CWB2B903100EW WIRE ASS'Y WIRE 1

BN88 CWB2B904100EN WIRE ASS'Y WIRE 1

BN89 CWB2B904100EN WIRE ASS'Y WIRE 1

BN92 CWB2B905100EN WIRE ASS'Y WIRE 1

CN47 CJP07GA117ZY WAFER WAFER 1

CN72 CJP17GA193ZY WAFER, CARD CABLE (SMD) WAFER 1

Description

Value Qty

Page 17

FRONT PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 17 of 131

Ref. # Part Number

CN84 CJP05GB46ZY WAFER WAFER 1

CN85 CJP03GA19ZY WAFER , STRAIGHT, 3PIN WAFER 1

CN86 CJP02GA89ZM WAFER WAFER 1

CN88 CJP04GB46ZY WAFER WAFER 1

CN89 CJP04GB46ZY WAFER WAFER 1

CN92 CJP05GA19ZY WAFER, STRAIGHT, 5PIN WAFER 1

D701 CVD52CSBBCEAB2 L.E.D , BLUE L.E.D 1

D703 CVD52CSBBCEAB2 L.E.D , BLUE L.E.D 1

D705 CVD52CSBBCEAB2 L.E.D , BLUE L.E.D 1

D723 CVD50BOBBWGA L.E.D , 2 COLOR (ORG , BLUE) L.E.D 1

D727 CVD50BOBBWGA L.E.D , 2 COLOR (ORG , BLUE) L.E.D 1

ET03 CMD1A569 BRACKET , PCB BRACKET 1

FIP1 HFLHCA18ML03 F.I.P F.I.P 1

IC41 CVINJU7301M I.C , NJU7301M(TE1) JRC 1

IC73 HRVNJL34H380A SENSOR , REMOCON JRC 1

IC75 HVI74ACT04MTR I.C , HEX FAIRCHILD 1

IC76 HVI74HCU04AFNG I.C , INVERTER TOSHICA 1

IC86 HVINJM4556AL I.C , HEADPHONE JRC 1

IC87 HVINJM2068MDTE1 I.C , OP AMP JRC 1

IC97 HVIST202EBW IC , RS232C ST 1

JK81 CJJ4M043Y JACK , BOARD JACK 1

JK82 HJSTORX177L MODULE , OPTICAL(RX) OPT JACK(RX) 1

JK83 CJJ2E026Z JACK , HEADPHONE(SILVER PLATE) JACK 1

JK85 CJJ9M003Z JACK , S-VIDEO JACK 1

JK86 CJJ4S023Y JACK , BOARD JACK 1

JK97 CJJ9W001Z 9P D-SUB FEMALE(RS-232C) SEMCO JACK 1

JW82 CWE8202300RV WIRE ASS'Y WIRE 1

JW83 CWE8202150RV WIRE ASS'Y WIRE 1

JW84 CWE8202110RV WIRE ASS'Y WIRE 1

RL45 CSL4A014ZE RELAY (+12V) AXICOM 1

SW1 CSH1A008ZV SW , PUSH (MOMS) MOMS SW 1

SW95 KST1A010Z SW , TACT CN 1A010 1

SW96 HSH2B018Z SW , PUSH SWITCH 1

SW97 HSH2B018Z SW , PUSH SWITCH 1

VR74 CSR2A037Z ENCODER ENCODER 1

Description

Value Qty

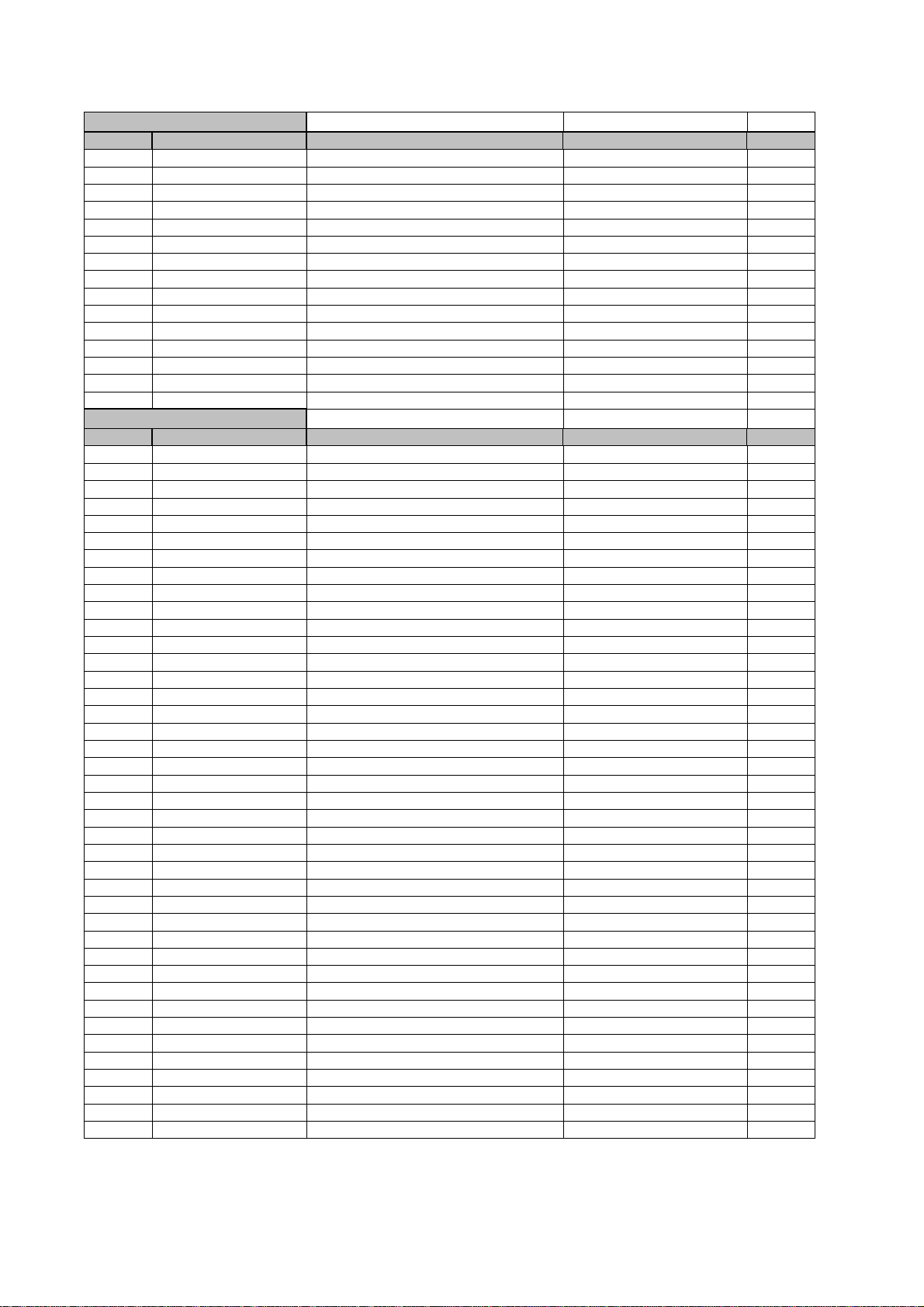

BOTTOM CHASSIS ASS'Y

Ref. # Part Number

CUAAVR247/230 BOTTOM CHASSIS ASS'Y ASS'Y 1

CHD1A012ZR SCREW , SPECIAL SCREW 2

CHD1A023R SCREW , SPECIAL SCREW 4

CHD4A012R SCREW , SPECIAL SCREW 5

CHE170 HOLDER , PCB HOLDER 2

CHE36-3 CLAMPER , WIRE CLAMPER 2

CHG1A104Z CUSHUON , RUBBER CUSHION 1

CHG1A160Z CUSHION , RUBBER CUSHION 1

CHG1A360 CUSHION , FOOT CUSHION 4

CHS1A032 TAPE , HEMELON TAPE 4

CJA2B043ZA CORD , POWER(EUR) POWER CORD 1

CKF12A319Z PANEL , REAR AVR247/230 REAR PANEL 1

CKL2A069H43 FOOT FOOT 4

CLZ9W003Z FERRITE , RING FERRITE RING 1

CMD2A487 BRACKET , TRANS BRACKET 1

CNVM9014MS171L MODULE , TUNER(EUR) TUNER 1

CQB1A173Y LABEL, FUSE CAUTION LABEL 1

CTB3+10GFZR SCREW SCREW 23

CTB3+6FFZR SCREW SCREW 8

CTB3+6JR SCREW SCREW 15

CTB3+8JR SCREW SCREW 10

Description

Value Qty

Page 18

BOTTOM CHASSIS ASS'Y

T

harman/kardon

AVR247/230 Service Manual

Page 18 of 131

Ref. # Part Number

CTW3+12JR SCREW SCREW 2

CTW3+8JR SCREW SCREW 9

CUA3A229 CHASSIS , BOTTOM AVR350/230 CHASSIS 1

KHR1A028 BUSHING , AC CORD BUSHING 1

CB11 CWC1B2A17A100B CABLE , CARD (1MM) 17PIN CARD CABLE 1

CB12 CWC1C4A21B110B CABLE , CARD CARD CABLE 1

CB13 CWC1C4A13B080B CABLE , CARD CARD CABLE 1

CB14 CWC6F2A17A120B CABLE , CARD(17PIN, 120MM, 1 MM PI

CB15 CWCAVR347BN15 CARD CABLE COPPER SHIELD ASS'Y CARD CABLE 1

CB19 CWC1B2A09A240B CABLE , CARD CARD CABLE 1

CB42 CWC1B2A07A120B CABLE, CARD (1mm PITCH, A-B TYPE) CARD CABLE 1

CB47 CWC1B2A07A060B CABLE , CARD CARD CABLE 1

F901 KBA2C6300TLEZ FUSE LITTEL FUSE 1

T901 CLT5W026ZE TRANS , POWER MAIN TRANS 1

Description

Value Qty

CARD CABLE 1

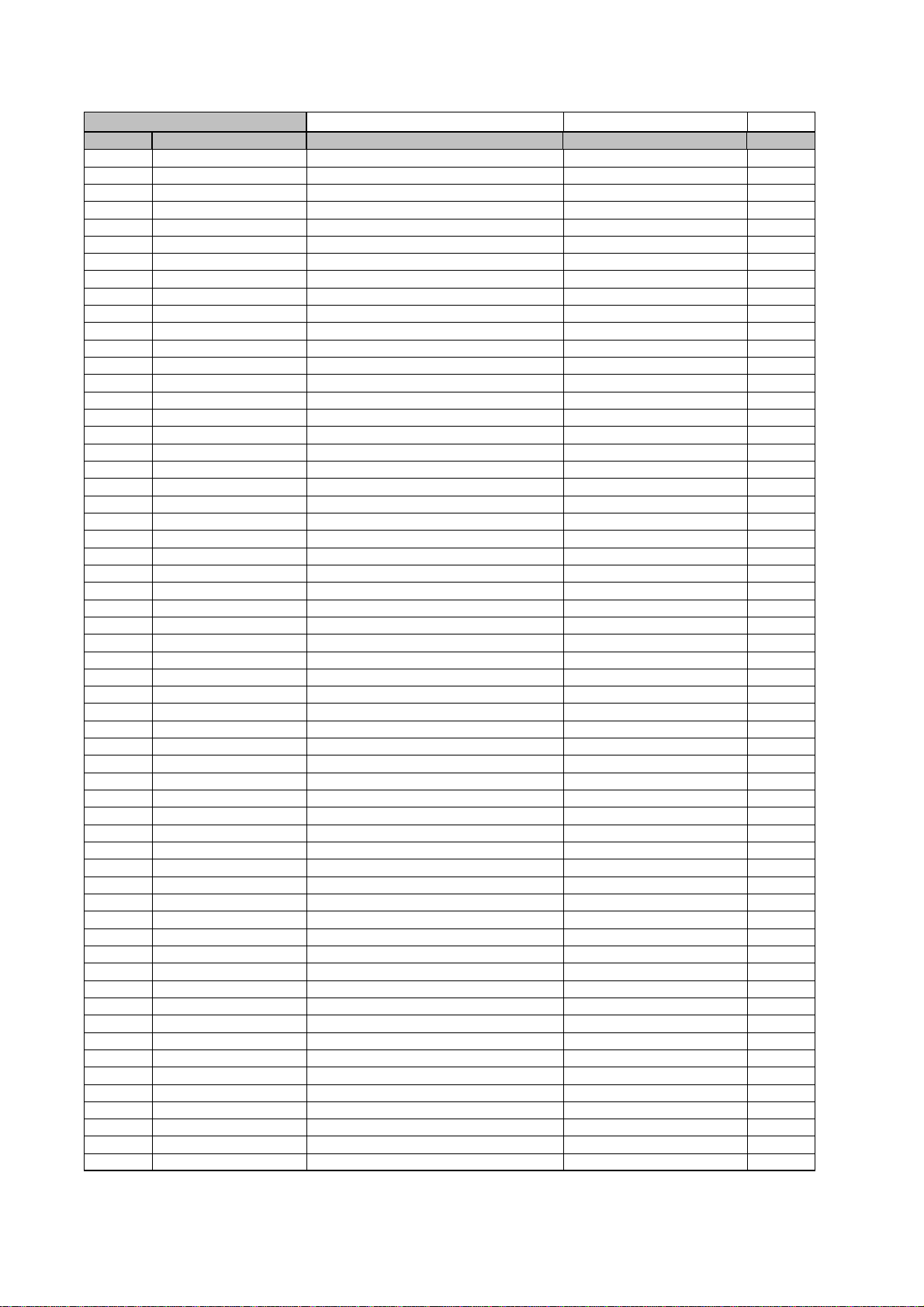

MAIN PCB ASSY

Ref. # Part Number

COP11911O AVR247/230 MAIN PCB ASS'Y ASS'Y 1

CHD3A012R SCREW , SPECIAL SCREW 3

CHS1A032 TAPE , HEMELON TAPE 1

CTW3+8JR SCREW SCREW 2

C8AGB288 BOND (MAX) BOND (MAX) 10,2

C501 CCEA1HH100T CAP , ELECT 10UF 50V 1

C502 CCEA1HH100T CAP , ELECT 10UF 50V 1

C503 CCEA1HH100T CAP , ELECT 10UF 50V 1

C504 CCEA1HH100T CAP , ELECT 10UF 50V 1

C505 CCEA1HH100T CAP , ELECT 10UF 50V 1

C506 CCKT1H331KB CAP , CERAMIC 330PF 50V 1

C507 HCBS1H331KBT CAP , CERAMIC 330PF 50V 1

C508 HCBS1H331KBT CAP , CERAMIC 330PF 50V 1

C509 CCKT1H331KB CAP , CERAMIC 330PF 50V 1

C510 HCBS1H331KBT CAP , CERAMIC 330PF 50V 1

C561 CCEA1CH101T CAP , ELECT 100UF 16V 1

C562 CCEA1CH101T CAP , ELECT 100UF 16V 1

C563 CCEA1CH101T CAP , ELECT 100UF 16V 1

C564 CCEA1CH101T CAP , ELECT 100UF 16V 1

C565 CCEA1CH101T CAP , ELECT 100UF 16V 1

C566 CCEA1CH101T CAP , ELECT 100UF 16V 1

C567 CCEA1CH101T CAP , ELECT 100UF 16V 1

C568 CCEA1CH101T CAP , ELECT 100UF 16V 1

C569 CCEA1CH101T CAP , ELECT 100UF 16V 1

C570 CCEA1CH101T CAP , ELECT 100UF 16V 1

C571 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C572 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C573 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C574 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C575 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C601 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C602 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C603 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C604 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C605 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C606 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C607 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C608 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C609 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C610 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

Description

Value Qty

Page 19

MAIN PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 19 of 131

Ref. # Part Number

C681 CCEA1HH100T CAP , ELECT 10UF 50V 1

C682 CCEA1HH100T CAP , ELECT 10UF 50V 1

C683 CCEA1HH100T CAP , ELECT 10UF 50V 1

C684 CCEA1HH100T CAP , ELECT 10UF 50V 1

C685 CCEA1HH100T CAP , ELECT 10UF 50V 1

C721 CCKT1H221KB CAP , CERAMIC 220PF 50V 1

C722 CCKT1H221KB CAP , CERAMIC 220PF 50V 1

C723 CCKT1H221KB CAP , CERAMIC 220PF 50V 1

C724 CCKT1H221KB CAP , CERAMIC 220PF 50V 1

C725 CCKT1H221KB CAP , CERAMIC 220PF 50V 1

C726 CCKT1H221KB CAP , CERAMIC 220PF 50V 1

C727 CCKT1H221KB CAP , CERAMIC 220PF 50V 1

C728 CCKT1H221KB CAP , CERAMIC 220PF 50V 1

C801 CCEA1HH100T CAP , ELECT 10UF 50V 1

C802 CCEA1HH100T CAP , ELECT 10UF 50V 1

C803 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C804 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C805 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C806 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C811 CCEA1CH101T CAP , ELECT 100UF 16V 1

C812 CCEA1CH101T CAP , ELECT 100UF 16V 1

C813 CCEA1CH101T CAP , ELECT 100UF 16V 1

C814 CCEA1CH101T CAP , ELECT 100UF 16V 1

C815 CCKT1H331KB CAP , CERAMIC 330PF 50V 1

C816 HCBS1H331KBT CAP , CERAMIC 330PF 50V 1

C817 CCEA1HH100T CAP , ELECT 10UF 50V 1

C818 CCEA1HH100T CAP , ELECT 10UF 50V 1

C819 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C820 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C900 HCQI1H473JZT CAP , MYLAR 0.047UF 50V 1

C901 HCQI1H473JZT CAP , MYLAR 0.047UF 50V 1

C905 CCFT1H223ZF CAP , CERAMIC 0.022UP 50V 1

C907 CCEA1CH101T CAP , ELECT 100UF 16V 1

C908 CCFT1H223ZF CAP , CERAMIC 0.022UP 50V 1

C910 HCQI1H473JZT CAP , MYLAR 0.047UF 50V 1

C911 CCEA1CH471T CAP , ELECT 470UF 16V 1

C912 CCEA1EH221T CAP , ELECT 220UF 16V 1

C913 CCFT1H104ZF CAP , SEMICONDUCTOR 0.1UF 50V ZF 1

C914 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C917 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C918 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C919 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C924 CCFT1H104ZF CAP , SEMICONDUCTOR 0.1UF 50V ZF 1

C925 CCFT1H104ZF CAP , SEMICONDUCTOR 0.1UF 50V ZF 1

C932 CCEA1CH101T CAP , ELECT 100UF 16V 1

C933 CCEA1CH221T CAP , ELECT 220UF 16V 1

C934 CCFT1H223ZF CAP , CERAMIC 0.022UP 50V 1

C939 CCEA1HH4R7T CAP , ELECT 4.7UF 50V 1

C940 CCEA1AH471T CAP , ELECT 470UF 10V 1

C948 CCFT1H104ZF CAP , SEMICONDUCTOR 0.1UF 50V ZF 1

C949 CCEA1HH220T CAP , ELECT 22UF 50V 1

C950 CCEA1AH471T CAP , ELECT 470UF 10V 1

C971 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C972 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C973 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C974 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C975 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C980 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C981 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

Description

Value Qty

Page 20

MAIN PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 20 of 131

Ref. # Part Number

C990 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C991 CCEA1HH1R0T CAP , ELECT 1UF 50V 1

C992 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C993 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C994 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C995 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C996 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C997 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C999 CCFT1H223ZF CAP , CERAMIC 0.022UF 50V ZF 1

D501 CVD1SS133MT DIODE 1SS133 1

D502 CVD1SS133MT DIODE 1SS133 1

D503 CVD1SS133MT DIODE 1SS133 1

D504 CVD1SS133MT DIODE 1SS133 1

D505 CVD1SS133MT DIODE 1SS133 1

D581 CVD1SS133MT DIODE 1SS133 1

D582 CVD1SS133MT DIODE 1SS133 1

D583 CVD1SS133MT DIODE 1SS133 1

D584 CVD1SS133MT DIODE 1SS133 1

D585 CVD1SS133MT DIODE 1SS133 1

D801 CVD1SS133MT DIODE 1SS133 1

D802 CVD1SS133MT DIODE 1SS133 1

D803 CVD1SS133MT DIODE 1SS133 1

D804 CVD1SS133MT DIODE 1SS133 1

D901 CVD1N4003SRT DIODE , RECT 1N4003 1

D902 CVD1SS133MT DIODE 1SS133 1

D911 CVD1SS133MT DIODE 1SS133 1

D912 CVD1SS133MT DIODE 1SS133 1

D914 CVD1SS133MT DIODE 1SS133 1

D917 CVD1SS133MT DIODE 1SS133 1

D953 CVD1SS133MT DIODE 1SS133 1

D954 CVD1N4003SRT DIODE , RECT 1N4003 1

D955 CVD1N4003SRT DIODE , RECT 1N4003 1

D956 CVD1N4003SRT DIODE , RECT 1N4003 1

D957 CVD1N4003SRT DIODE , RECT 1N4003 1

D961 CVD1N4003ST DIODE , RECT 1N4003 1

D962 CVD1N4003SRT DIODE , RECT 1N4003 1

D963 CVD1N4003ST DIODE , RECT 1N4003 1

D964 CVD1SS133MT DIODE 1SS133 1

D967 CVD1SS133MT DIODE 1SS133 1

D968 CVD1SS133MT DIODE 1SS133 1

D969 CVD1SS133MT DIODE 1SS133 1

D971 CVD1SS133MT DIODE 1SS133 1

D972 CVD1SS133MT DIODE 1SS133 1

D973 CVD1SS133MT DIODE 1SS133 1

D974 CVD1SS133MT DIODE 1SS133 1

D979 CVDZJ6.2BT DIODE , ZENER MTZJ6.2B 1

D980 CVD1SS133MT DIODE 1SS133 1

ET90 HJT1A025 PALTE , EARTH MET37-0002 1

ET91 HJT1A025 PALTE , EARTH MET37-0002 1

F901 KJCFC5S HOLDER , FUSE HOLDER 2

F902 KBA2D2500TLET FUSE SAVE FUSETECH 1

Q501 HVTKTA1268GRT T.R KTA1268GR 1

Q502 HVTKTA1268GRT T.R KTA1268GR 1

Q503 HVTKTA1268GRT T.R KTA1268GR 1

Q504 HVTKTA1268GRT T.R KTA1268GR 1

Q505 HVTKTA1268GRT T.R KTA1268GR 1

Q511 HVTKTC3200GRT T.R KTC3200GR 1

Q512 HVTKTC3200GRT T.R KTC3200GR 1

Q513 HVTKTC3200GRT T.R KTC3200GR 1

Description

Value Qty

Page 21

MAIN PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 21 of 131

Ref. # Part Number

Q514 HVTKTC3200GRT T.R KTC3200GR 1

Q515 HVTKTC3200GRT T.R KTC3200GR 1

Q516 HVTKTC3200GRT T.R KTC3200GR 1

Q517 HVTKTC3200GRT T.R KTC3200GR 1

Q518 HVTKTC3200GRT T.R KTC3200GR 1

Q519 HVTKTC3200GRT T.R KTC3200GR 1

Q520 HVTKTC3200GRT T.R KTC3200GR 1

Q541 HVTKTC3198YT T.R KTC3198Y 1

Q542 HVTKTC3198YT T.R KTC3198Y 1

Q543 HVTKTC3198YT T.R KTC3198Y 1

Q544 HVTKTC3198YT T.R KTC3198Y 1

Q545 HVTKTC3198YT T.R KTC3198Y 1

Q556 HVTKTC3200GRT T.R KTC3200GR 1

Q557 HVTKTC3200GRT T.R KTC3200GR 1

Q558 HVTKTC3200GRT T.R KTC3200GR 1

Q559 HVTKTC3200GRT T.R KTC3200GR 1

Q560 HVTKTC3200GRT T.R KTC3200GR 1

Q561 HVTKTC3200GRT T.R KTC3200GR 1

Q562 HVTKTC3200GRT T.R KTC3200GR 1

Q563 HVTKTC3200GRT T.R KTC3200GR 1

Q564 HVTKTC3200GRT T.R KTC3200GR 1

Q565 HVTKTC3200GRT T.R KTC3200GR 1

Q601 HVTKTA1268GRT T.R KTA1268GR 1

Q602 HVTKTA1268GRT T.R KTA1268GR 1

Q603 HVTKTA1268GRT T.R KTA1268GR 1

Q604 HVTKTA1268GRT T.R KTA1268GR 1

Q605 HVTKTA1268GRT T.R KTA1268GR 1

Q681 HVTKSC2785YT T.R KSC2785Y 1

Q682 HVTKSC2785YT T.R KSC2785Y 1

Q683 HVTKSC2785YT T.R KSC2785Y 1

Q684 HVTKSC2785YT T.R KSC2785Y 1

Q685 HVTKSC2785YT T.R KSC2785Y 1

Q801 HVTKSC2785YT T.R KSC2785Y 1

Q802 HVTKSC2785YT T.R KSC2785Y 1

Q812 HVTKTA1268GRT T.R KTA1268GR 1

Q813 HVTKTC3200GRT T.R KTC3200GR 1

Q814 HVTKTA1268GRT T.R KTA1268GR 1

Q815 HVTKTC3200GRT T.R KTC3200GR 1

Q816 HVTKTA1268GRT T.R KTA1268GR 1

Q817 HVTKTA1268GRT T.R KTA1268GR 1

Q818 HVTKTC3200GRT T.R KTC3200GR 1

Q819 HVTKTC3200GRT T.R KTC3200GR 1

Q820 HVTKTC3200GRT T.R KTC3200GR 1

Q821 HVTKTC3200GRT T.R KTC3200GR 1

Q822 HVTKTC3200GRT T.R KTC3200GR 1

Q823 HVTKTC3200GRT T.R KTC3200GR 1

Q824 HVTKTC3198YT T.R KTC3198Y 1

Q825 HVTKTC3198YT T.R KTC3198Y 1

Q901 HVTKSC2785YT T.R KSC2785Y 1

Q911 HVTKTA1271YT T.R KTA1271Y 1

Q912 HVTKTA1271YT T.R KTA1271Y 1

Q913 HVTKTA1271YT T.R KTA1271Y 1

Q914 HVTKTA1271YT T.R KTA1271Y 1

Q915 HVTKSC2785YT T.R KSC2785Y 1

Q916 HVTKSC2785YT T.R KSC2785Y 1

Q917 HVTKSC2785YT T.R KSC2785Y 1

Q918 HVTKSC2785YT T.R KSC2785Y 1

Q938 HVTKRA107MT T.R KRA107M 1

Q939 HVTKRA107MT T.R KRA107M 1

Description

Value Qty

Page 22

MAIN PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 22 of 131

Ref. # Part Number

Q942 HVTKSC2785YT T.R KSC2785Y 1

Q943 HVTKSC2785YT T.R KSC2785Y 1

Q951 HVTKRC107MT T.R KRC107M 1

Q952 HVTKRA107MT T.R KRA107M 1

Q960 HVTKRC107MT T.R KRC107M 1

Q961 HVTKTA1024YT T.R KTA1024YT 1

Q991 HVTKRC107MT T.R KRC107M 1

Q992 HVTKRA107MT T.R KRA107M 1

Q993 HVTKRA107MT T.R KRA107M 1

Q994 HVTKRC107MT T.R KRC107M 1

Q997 HVTKRA107MT T.R KRA107M 1

Q998 HVTKRC107MT T.R KRC107M 1

R501 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R502 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R503 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R504 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R505 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R506 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R507 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R508 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R509 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R510 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R511 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R512 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R513 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R514 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R515 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R516 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R517 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R518 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R519 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R520 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R521 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R522 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R523 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R524 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R525 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R531 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R532 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R533 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R534 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R535 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R536 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R537 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R538 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R539 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R540 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R541 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R542 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R543 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R544 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R545 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R556 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R557 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R558 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R559 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R560 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R561 CRD20TJ162T RES , CARBON 1.6K OHM 1/5W J 1

R562 CRD20TJ162T RES , CARBON 1.6K OHM 1/5W J 1

Description

Value Qty

Page 23

MAIN PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 23 of 131

Ref. # Part Number

R563 CRD20TJ162T RES , CARBON 1.6K OHM 1/5W J 1

R564 CRD20TJ162T RES , CARBON 1.6K OHM 1/5W J 1

R565 CRD20TJ162T RES , CARBON 1.6K OHM 1/5W J 1

R566 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R567 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R568 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R569 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R570 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R571 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R572 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R573 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R574 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R575 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R576 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R577 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R578 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R579 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R580 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R581 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R582 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R583 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R584 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R585 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R586 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R587 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R588 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R589 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R590 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R591 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R592 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R593 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R594 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R595 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R596 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R597 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R598 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R599 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R600 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R601 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R602 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R603 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R604 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R605 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R606 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R607 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R608 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R609 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R610 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R611 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R612 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R631 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R632 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R633 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R634 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R635 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R636 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R637 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R638 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R639 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

Description

Value Qty

Page 24

MAIN PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 24 of 131

Ref. # Part Number

R640 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R646 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R647 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R648 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R649 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R650 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R651 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R652 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R653 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R654 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R655 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R666 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R667 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R668 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R669 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R670 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R671 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R672 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R673 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R674 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R675 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R681 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R682 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R683 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R684 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R685 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R686 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R687 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R688 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R689 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R690 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R696 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R697 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R698 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R699 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R700 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R771 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R772 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R773 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R774 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R775 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R776 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R777 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R781 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R782 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R783 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R784 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R785 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R786 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R787 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R801 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R802 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R803 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R804 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R805 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R807 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R812 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R813 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R814 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

Description

Value Qty

Page 25

MAIN PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 25 of 131

Ref. # Part Number

R815 CRD25TJ470T RES , CARBON 47 OHM 1/4W 1

R817 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R818 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R819 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R820 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R821 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R822 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R823 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R824 CRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R830 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R831 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R832 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R833 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R834 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R835 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R836 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R837 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R838 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R839 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R840 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R841 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R842 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R843 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R844 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R845 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R848 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R849 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R850 CRD20TJ162T RES , CARBON 1.6K OHM 1/5W J 1

R851 CRD20TJ162T RES , CARBON 1.6K OHM 1/5W J 1

R852 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R853 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R854 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R855 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R856 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R857 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R858 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R859 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R860 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R861 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R862 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R863 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R870 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R871 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R872 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R873 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R900 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R901 CRD25TJ393T RES , CARBON 39K OHM 1/4W 1

R902 CRD25TJ393T RES , CARBON 39K OHM 1/4W 1

R903 CRD25TJ393T RES , CARBON 39K OHM 1/4W 1

R906 CRD25TJ393T RES , CARBON 39K OHM 1/4W 1

R907 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R908 CRD20TJ105T RES , CARBON 1M OHM 1/5W J 1

R909 CRD20TJ682T RES , CARBON 6.8K OHM 1/5W J 1

R910 CRD20TJ105T RES , CARBON 1M OHM 1/5W J 1

R911 CRD25TJ680T RES , CARBON 68 OHM 1/4W J 1

R912 CRD20TJ332T RES , CARBON 3.3K OHM 1/5W J 1

R917 CRD25TJ393T RES , CARBON 39K OHM 1/4W 1

R918 CRD25TJ393T RES , CARBON 39K OHM 1/4W 1

R919 CRD25TJ393T RES , CARBON 39K OHM 1/4W 1

Description

Value Qty

Page 26

MAIN PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 26 of 131

Ref. # Part Number

R920 CRD25TJ393T RES , CARBON 39K OHM 1/4W 1

R921 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R922 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R923 CRD20TJ220T RES , CARBON 22 OHM 1/5W J 1

R924 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R925 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R926 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R927 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R928 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R929 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R930 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R931 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R932 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R933 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R934 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R935 CRD20TJ154T RES , CARBON 150K OHM 1/5W J 1

R936 CRD20TJ184T RES , CARBON 180K OHM 1/5W J 1

R939 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R940 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R941 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R942 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R943 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R944 CRD25TJ223T RES , CARBON 22K OHM 1/4W J 1

R945 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R946 CRD25TJ223T RES , CARBON 22K OHM 1/4W J 1

R947 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R948 CRD25TJ222T RES , CARBON 2.2K OHM 1/4W J 1

R949 CRD20TJ822T RES , CARBON 8.2K OHM 1/5W J 1

R952 CRD25TJ223T RES , CARBON 22K OHM 1/4W J 1

R953 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R954 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R955 CRD20TJ203T RES , CARBON 20K OHM 1/5W J 1

R956 CRD20TJ394T RES , CARBON 390K OHM 1/5W J 1

R957 CRD20TJ153T RES , CARBON 15K OHM 1/5W J 1

R958 CRD20TJ563T RES , CARBON 56K OHM 1/5W J 1

R959 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R960 CRD20TJ332T RES , CARBON 3.3K OHM 1/5W J 1

R961 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R962 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R963 CRD20TJ105T RES , CARBON 1M OHM 1/5W J 1

R966 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R967 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R968 CRD20TJ105T RES , CARBON 1M OHM 1/5W J 1

R969 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R980 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R986 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R987 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R988 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R989 CRD20TJ302T RES , CARBON 3K OHM 1/5W J 1

R991 CRD20TJ822T RES , CARBON 8.2K OHM 1/5W J 1

R992 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R998 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

BN19 CWB3FE03250UP WIRE ASS'Y WIRE 1

BN20 CWB3FC04280UP WIRE ASS'Y WIRE 1

BN81 CWB1C902050EN WIRE ASS'Y WIRE 1

BN82 CWB1C902050EN WIRE ASS'Y WIRE 1

BN83 CWB1C902050EN WIRE ASS'Y WIRE 1

BN84 CWB1C902050EN WIRE ASS'Y WIRE 1

BN85 CWB1C902050EN WIRE ASS'Y WIRE 1

Description

Value Qty

Page 27

MAIN PCB ASSY

harman/kardon

AVR247/230 Service Manual

Page 27 of 131

Ref. # Part Number

BN86 CWB1C902050EN WIRE ASS'Y WIRE 1

BN87 CWB1C902050EN WIRE ASS'Y WIRE 1

BN88 CWB2B906070EN WIRE ASS'Y WIRE 1

BN89 CWB1C902250BM WIRE ASS'Y WIRE 1

BN90 CWB4F232550PU WIRE ASS'Y WIRE 1

BN98 HJP08GA130ZK WAFER WAFER 1

CN11 CJP17GA117ZY WAFER WAFER 1

CN12 CJP21GA115ZY WAFER , CARD CABLE WAFER 1

CN61 CJP02GA01ZY WAFER , STRAIGHT, 2PIN WAFER 1

CN62 CJP02GA01ZY WAFER , STRAIGHT, 2PIN WAFER 1

CN63 CJP02GA01ZY WAFER , STRAIGHT, 2PIN WAFER 1

CN64 CJP02GA01ZY WAFER , STRAIGHT, 2PIN WAFER 1

CN65 CJP02GA01ZY WAFER , STRAIGHT, 2PIN WAFER 1

CN66 CJP02GA01ZY WAFER , STRAIGHT, 2PIN WAFER 1

CN67 CJP02GA01ZY WAFER , STRAIGHT, 2PIN WAFER 1

CN89 CJP02GA01ZY WAFER , STRAIGHT, 2PIN WAFER 1

CN91 CJP02GA89ZY WAFER WAFER 1

CN92 CJP02KA060ZY WAFER WAFER 1

CN93 CJP02GA01ZY WAFER , STRAIGHT, 2PIN WAFER 1

C631 CCEA1JH101E CAP , ELECT 100UF 63V 1

C632 CCEA1JH101E CAP , ELECT 100UF 63V 1

C633 CCEA1JH101E CAP , ELECT 100UF 63V 1

C634 CCEA1JH101E CAP , ELECT 100UF 63V 1

C635 CCEA1JH101E CAP , ELECT 100UF 63V 1

C636 CCEA1JH101E CAP , ELECT 100UF 63V 1

C637 CCEA1JH101E CAP , ELECT 100UF 63V 1

C638 CCEA1JH101E CAP , ELECT 100UF 63V 1

C639 CCEA1JH101E CAP , ELECT 100UF 63V 1

C640 CCEA1JH101E CAP , ELECT 100UF 63V 1

C807 CCEA1JH101E CAP , ELECT 100UF 63V 1

C808 CCEA1JH101E CAP , ELECT 100UF 63V 1

C809 CCEA1JH101E CAP , ELECT 100UF 63V 1

C810 CCEA1JH101E CAP , ELECT 100UF 63V 1

C902 CCET50VKL4822NK CAP , ELECT 8200UF 50V 1

C904 KCKDKS472ME CAP , CERAMIC(X1/Y2/SC) 0.0047UF 2.5KV 1

C906 CCEA1EH102E CAP , ELECT 1000UF 25V 1

C909 CCET50VKL4822NK CAP , ELECT 8200UF 50V 1

C915 CCET50VKL4103NK CAP , ELECT 10000UF 50V 1

C916 CCET50VKL4103NK CAP , ELECT 10000UF 50V 1

ET01 CMD1A387 BRACKET , PCB BRACKET 1

IC94 HVIKIA7805API REGULATOR, +5V FAIRCHILD 1

IC97 HVIS-80842CNY-X I.C RESET SEIKO 1

JK91 CJJ5R006Z TERMINAL , SPEAKER TERMINAL 1

JK92 CJJ5Q012Z TERMINAL , SPEAKER TERMINAL 1

JK97 CJJ4P041W JACK IN/OUT JACK 1

JK98 CJJ4P042W JACK IN/OUT JACK 1