Texas Instruments UC3909QTR, UC3909Q, UC3909N, UC3909DWTR, UC3909DW Datasheet

...

UC2909

UC3909

DESCRIPTION

The UC3909 family of Switchmode Lead-Acid Battery Chargers accurately

controls lead acid battery charging with a highly efficient average current

mode control loop. This chip combines charge state logic with average current PWM control circuitry. Charge state logic commands current or voltage

control depending on the charge state. The chip includes undervoltage

lockout circuitry to insure sufficient supply voltage is present before output

switching starts. Additional circuit blocks include a differential current sense

amplifier, a 1.5% voltage reference, a –3.9mV/°C thermistor linearization

circuit, voltage and current error amplifiers, a PWM oscillator, a PWM comparator, a PWM latch, charge state decode bits, and a 100mA open collector output driver.

Switchmode Lead-Acid Battery Charger

FEATURES

• Accurate and Efficient Control of

Battery Charging

• Average Current Mode Control from

Trickle to Overcharge

• Resistor Programmable Charge

Currents

• Thermistor Interface Tracks Battery

Requirements Over Temperature

• Output Status Bits Report on Four

Internal Charge States

• Undervoltage Lockout Monitors VCC

and VREF

1/99

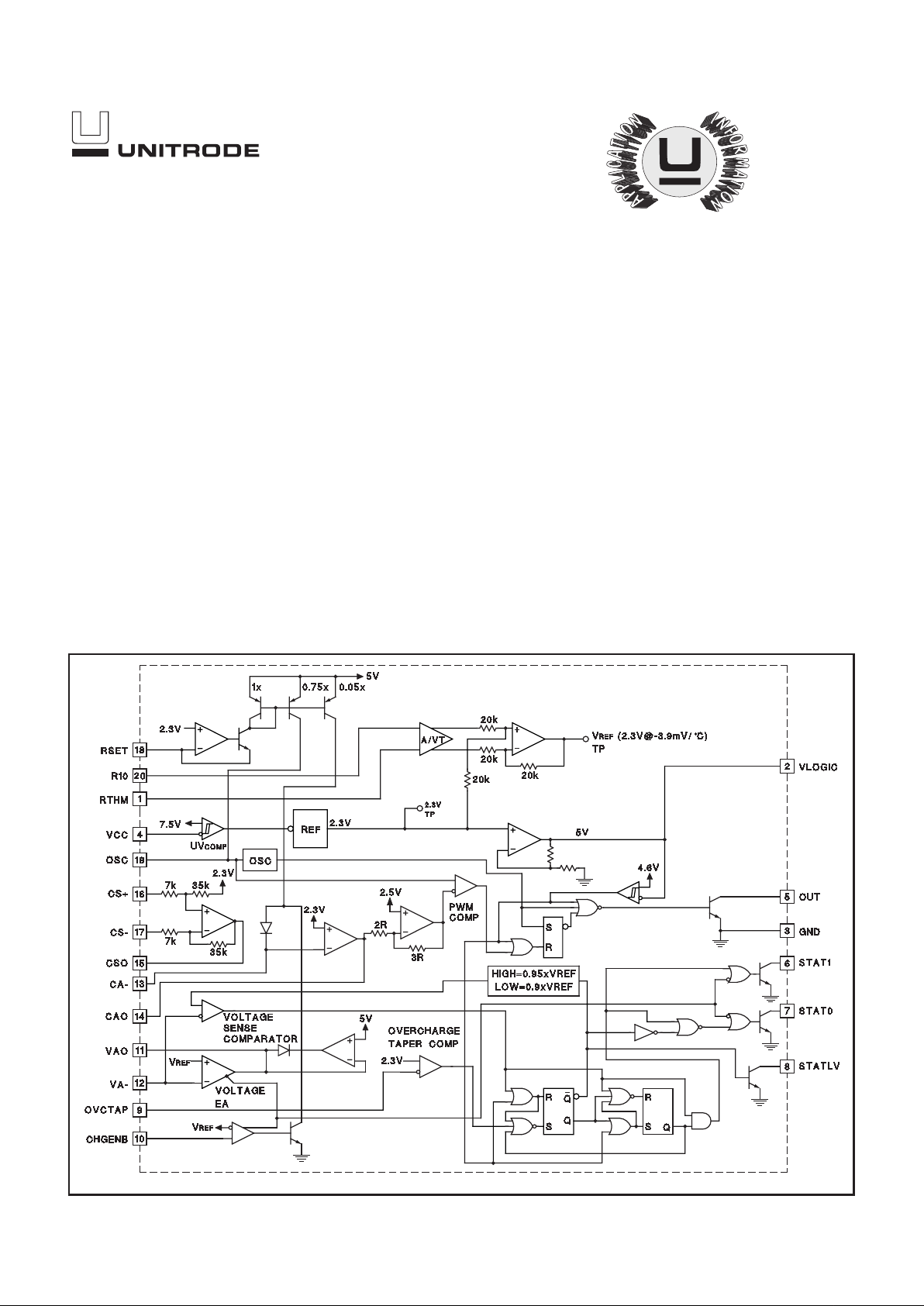

BLOCK DIAGRAM

UDG-95007-1

Pin numbers refer to J, N, DW packages.

2

UC2909

UC3909

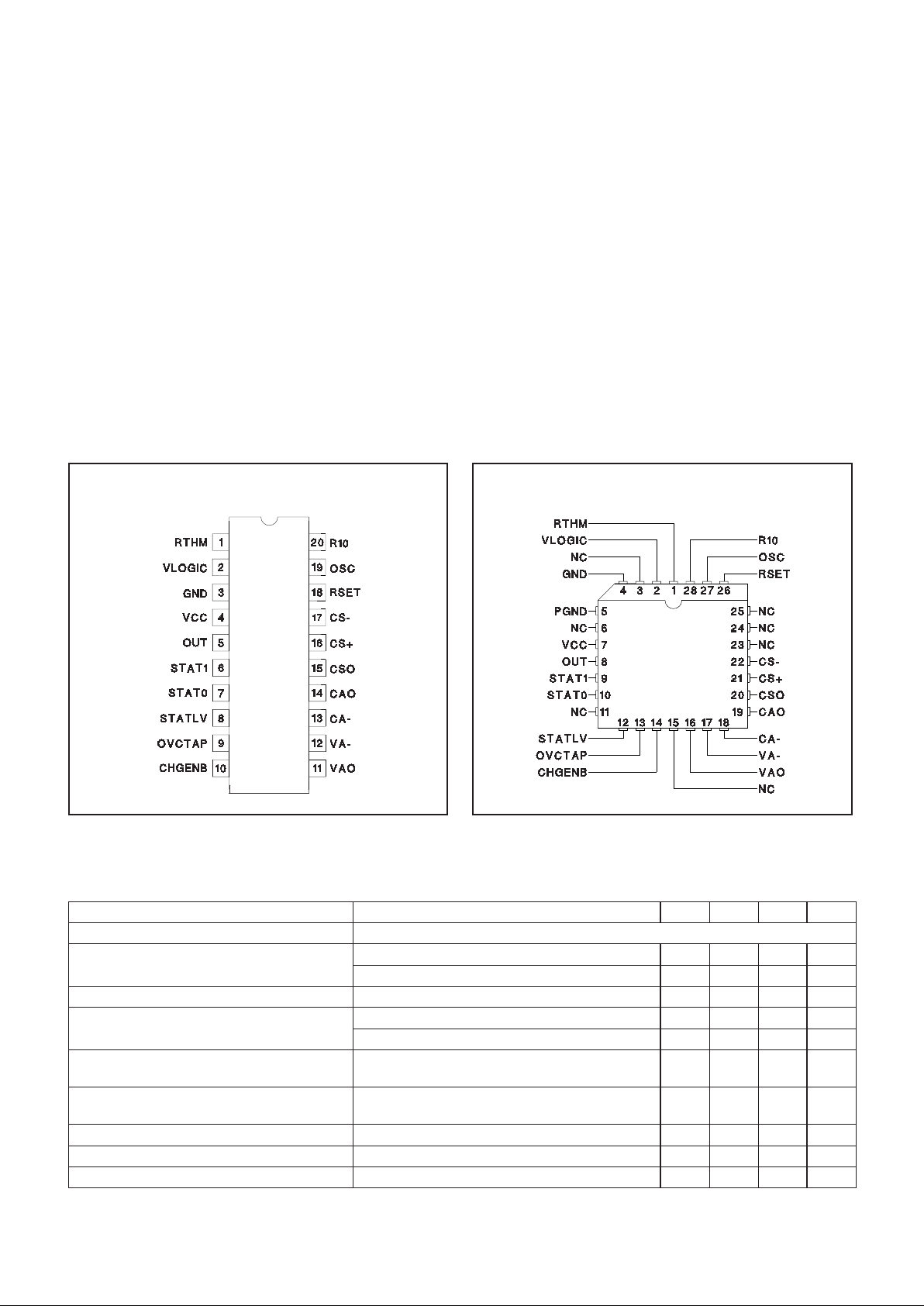

DIL-20, (Top View)

J or N, DW Packages

ABSOLUTE MAXIMUM RATINGS

Supply Voltage (VCC), OUT, STAT0, STAT1 . . . . . . . . . . . 40V

Output Current Sink . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.1A

CS+, CS-. . . . . . . . . . . . . . . . . . . . . . . . . . -0.4 to VCC (Note 1)

Remaining Pin Voltages. . . . . . . . . . . . . . . . . . . . . . -0.3V to 9V

Storage Temperature . . . . . . . . . . . . . . . . . . . -65°C to +150°C

Junction Temperature . . . . . . . . . . . . . . . . . . . -55°C to +150°C

Lead Temperature (Soldering, 10 sec.). . . . . . . . . . . . . +300°C

All currents are positive into, negative out of the specified terminal. Consult Packaging Section of Databook for thermal limitations and considerations of packages.

Note 1: Voltages more negative than -0.4V can be tolerated if

current is limited to 50mA.

CONNECTION DIAGRAMS

ELECTRICAL CHARACTERISTICS:

Unless otherwise stated these specifications apply for TA= –40°C to +85°C for

UC2909; °0C to +70°C for UC3909; CT= 330pF, R

SET

= 11.5k, R10 = 10k, R

THM

= 10k, VCC= 15V, Output no load, R

STAT0

=

R

STAT1

= 10k, CHGENB = OVCTAP = VLOGIC, TA= TJ.

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Current Sense AMP (CSA) Section

V

ID

= CS+ – CS–

DC Gain CS– = 0, CS+ = -50mV; CS+ = –250mV 4.90 5 5.10 V/V

CS+ = 0, CS– = 50mV; CS–- = 250mV 4.90 5 5.10 V/V

V

OFFSET(VCSO

– V

CAO

) CS+ = CS– = 2.3V, CAO = CA– 15 mV

CMRR VCM= –0.25 to VCC – 2, 8.8 < VCC < 14 50 dB

VCM= –0.25 to VCC, 14 < VCC < 35 50 dB

V

OL

VID= –550mV, –0.25V < VCM < VCC–2,

IO= 500µA

0.3 0.6 V

V

OH

VID= +700mV, –0.25V < VCM < VCC–2,

IO= –250µA

5.2 5.7 6.2 V

Output Source Current V

ID

= +700mV, CSO = 4V –1 –0.5 mA

Output Sink Current VID= –550mV, CSO = 1V 3 4.5 mA

3dB Bandwidth VID= 90mV, VCM= 0V 200 kHz

LCC-28, PLCC-28 (Top View)

L, Q Packages

3

UC2909

UC3909

ELECTRICAL CHARACTERISTICS: Unless otherwise stated these specifications apply for T

A

= –40°C to +85°C for

UC2909; °0C to +70°C for UC3909; CT= 330pF, R

SET

= 11.5k, R10 = 10k, R

THM

= 10k, VCC= 15V, Output no load, R

STAT0

=

R

STAT1

= 10k, CHGENB = OVCTAP = VLOGIC, TA= TJ.

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Current Error Amplifier (CEA) Section

I

B

8.8V < VCC < 35V, V

CHGENB

= V

LOGIC

0.1 0.8 µA

V

IO

(Note 2) 8.8V < VCC < 35V, CAO = CA– 10 mV

A

VO

1V < VAO < 4V 60 90 dB

GBW TJ= 25°C, F = 100kHz 1 1.5 MHz

V

OL

IO= 250µA 0.4 0.6 V

V

OH

IO= –5mA 4.5 5 V

Output Source Current CAO = 4V –25 –12 mA

Output Sink Current CAO = 1V 2 3 mA

ICA–, I

TRCK_CONTROL

V

CHGENB

= GND 8.5 10 11.5 µA

Voltage Amplifier (CEA) Section

I

B

Total Bias Current; Regulating Level 0.1 1 µA

VIO(Note 2) 8.8V < VCC < 35V, VCM = 2.3V, VAO = VA– 1.2 mV

A

VO

1V < CAO < 4V 60 90 dB

GBW TJ= 25°C, F = 100kHz 0.25 0.5 MHz

V

OL

IO= 500µA 0.4 0.6 V

V

OH

IO= –500µA 4.75 5 5.25 V

Output Source Current CAO = 4V –2 –1 mA

Output Sink Current CAO = 1V 2 2.5 mA

VAO Leakage: High Impedance State V

CHGENB

= GND, STAT0 = 0 & STAT1 = 0,

VAO = 2.3V

–1 1 µA

Pulse Width Modulator Section

Maximum Duty Cycle CAO = 0.6V 90 95 100 %

Modulator Gain CAO = 2.5V, 3.2V 63 71 80 %/V

OSC Peak 3V

OSC Valley 1V

Oscillator Section

Frequency 8.8V < VCC < 35V 198 220 242 kHz

Thermistor Derived Reference Section

V

ID

= V

RTHM

– V

R10

Initial Accuracy, VAO (RTHM = 10k) VID= 0, R10 = RTHM =10k (Note 3) 2.2655 2.3 2.3345 V

VID= 0, R10 = RTHM =10k, –40°C ≤TA< 0°C

(Note 3)

2.254 2.3 2.346 V

Line Regulation V

CC

= 8.8V to 35V 3 10 mV

VAO RTHM = 138k, R10 = 10k 2.458 2.495 2.532 V

RTHM = 138k, R10 = 10k, -40°C ≤ TA< 0°C 2.445 2.495 2.545 V

RTHM = 33.63k, R10 = 10k 2.362 2.398 2.434 V

RTHM = 33.63k, R10 = 10k, -40°C ≤ T

A

< 0°C 2.350 2.398 2.446 V

RTHM = 1.014k, R10 = 10k 2.035 2.066 2.097 V

RTHM = 1.014k, R10 = 10k, -40°C ≤ TA< 0°C 2.025 2.066 2.107 V

Charge Enable Comparator Section (CEC)

Threshold Voltage As a function of VA– 0.99 1 1.01 V/V

Input Bias Current CHGENB = 2.3V –0.5 –0.1 µA

Loading...

Loading...