Page 1

D. REPAIR PROCEDURE

C-2/D-230

D. REPAIR PROCEDURE

[1] TROUBLESHOOTING GUIDE ..................................................................................D-2

TAKING INOPERATIVE ..........................................................................................D-2

POWER LOSS INOPERATIVE ............................................................................... D-2

NO PICTURE .......................................................................................................... D-2

D-1 Ver. 1

Page 2

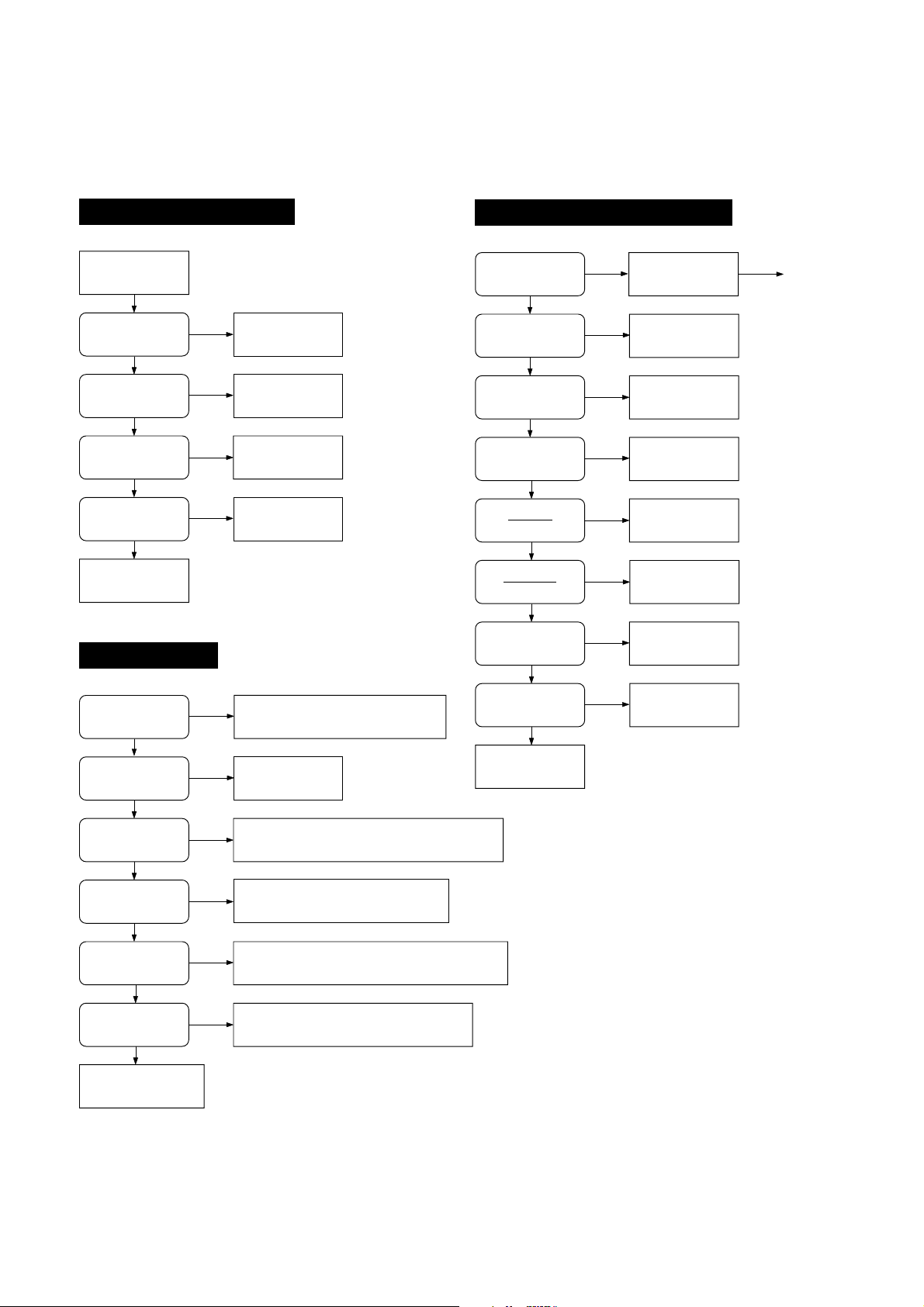

[1] TROUBLESHOOTING GUIDE

D. REPAIR PROCEDURE C-2/D-230

TAKING INOPERATIVE

PUSH SHUTTER

BUTTON

IC301-29, 30

(1st, 2nd)

PULSE INPUT

NO

YES

IC301-5, 6

(P ON, P(A) ON)

LOW

HIGH

IC301-62, 63, 64

HIGH

NO

YES

SERIAL

COMMUNICATION

NG

OK

CHECK CA2

NO PICTURE

CLK (72MHz)

INPUT TO

IC102-280 (CLK IN 1)

NO

CLK (36 MHz)

INPUT TO

IC101-132 (CLK IN 1)

OK

IC101-61 (ZAS)

OK

IC101-52

(ZBREQ)

OK

IC101-56

(ZBGRNT)

OK

IC101-118, 119

(IRL1, 2)

OK

CHECK SOLDERING OF

EACH CPU AND

MEMORY PIN

YES

NG

NG

NG

NG

NG

POWER LOSS INOPERTIVE

CHECK

SHUTTER BUTTON,

WIRE, R3008, R3009

CHECK

IC301, CA1

CHECK

IC301, CA1

CHECK IC301,

R3010, CA2

MAIN CLOCK FOR SYSTEM OPERATION

NO OPERATION IF ABSENT

CHECK X1101 OSCILLATOR AND IC111

BASIC CPU BLOCK

CHECK IC102-278,

R1033

ALWAYS APPEARS WHEN CPU, ETC. IS ACCESSED

CHECK IF CPU IS READKING PROGRAM, AND

CHECK ADDRESS AND DATA BUS OF IC121

REQUEST FOR USE OF DATA BUS FROM

ASIC TO CPU NO DMA TRANSMISSION

IF ABSENT

RECEIVES ZBREQ SIGNAL AND GIVES PERMISSION

TO ASIC FOR USE OF DATA BUS

NO DMA TRANSMISSION IF ABSENT

INCORRECT HANDSHAKING BETWEEN 8-BIT

CPU AND RS-232C

CHECK EACH INTERFACE

IC301-45 (CAM ON/

OFF) PULSE INPUT

IC302-7 (UNREG)

BARRIER SW

OPEN

YES

HIGH

IC301-24

(VDD)

HIGH

IC301-36

(RESET)

HIGH

IC301-43

(BAT OFF)

HIGH

IC301-40

OSCILLATION

YES

IC301-37

OSCILLATION

YES

CHECK IC301

CLOSE

NO

LOW

LOW

LOW

CHECK IC302, R3006

LOW

NO

NO

R3017, C3010, C3057

BARRIER SW ON

CHECK BARRIER

SW, WIRE, R3034

CHECK CA1

CHECK IC302

CHECK R3007

CHECK X3001

CHECK X3002,

NORMAL

D-2 Ver. 1

Loading...

Loading...