Page 1

Programme’s After Market Services

NHP–4 Series Transceivers

Chapter 4

System Module

Issue 1 04/99

Page 2

NHP–4

System Module

Technical Documentation

Contents

Baseband Block 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Baseband Block Connections 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal Signals and Connections 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Description 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Management 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU BLOCK 4–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DSP Block 4–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital ASIC Clock 4–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CDRFI 4–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Audio Block 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PAMS

Page No

RF Block Introduction 4–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter 4–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Description 4–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Description 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Description 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Synthesizer 4–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The VCTCXO Clock (G100) 4–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The Fujitsu Dual PLL Frequency Synthesizer IC (N101) 4–38. . . . . . . . . . . .

The 2 GHz UHF Channel Selector (LO_PRX, LO_PTX) 4–39. . . . . . . . . . . .

The 416.2 MHz TX VHF LO (LO_TIF) 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . .

The 256.2 MHz RX VHF LO (LO_RIF)/ 4–40. . . . . . . . . . . . . . . . . . . . . . . . . . .

Motorola MC145162D PLL IC (CLOCKS, N102) 4–40. . . . . . . . . . . . . . . . . . .

Parts List GR2 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page 4–2

Issue 1 04/99

Page 3

PAMS

NHP–4

Technical Documentation

List Of Figures

Figure 1 Baseband – Interconnections 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 2 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 3 Memory Map 4–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 4 DSP memory configuration w/ 64k external SRAM 4–19. . . . . . . . . .

RF/BB Block Diagram 4–A1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Supply 4–A2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU 4–A3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU Memory 4–A4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DSP 4–A5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DSP Memory 4–A6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF Block 4–A7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Module

Page No

Receiver 4–A8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter 4–A9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Synthesiser 4–A10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input / Output 4–A11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Clocks 4–A12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power 4–A13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Component Layout – Top 4–A14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Component Layout – Bottom 4–A15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Issue 1 04/99

Page 4–3

Page 4

NHP–4

System Module

PAMS

Technical Documentation

This page intentionally left blank

Page 4–4

Issue 1 04/99

Page 5

PAMS

NHP–4

Technical Documentation

Baseband Block

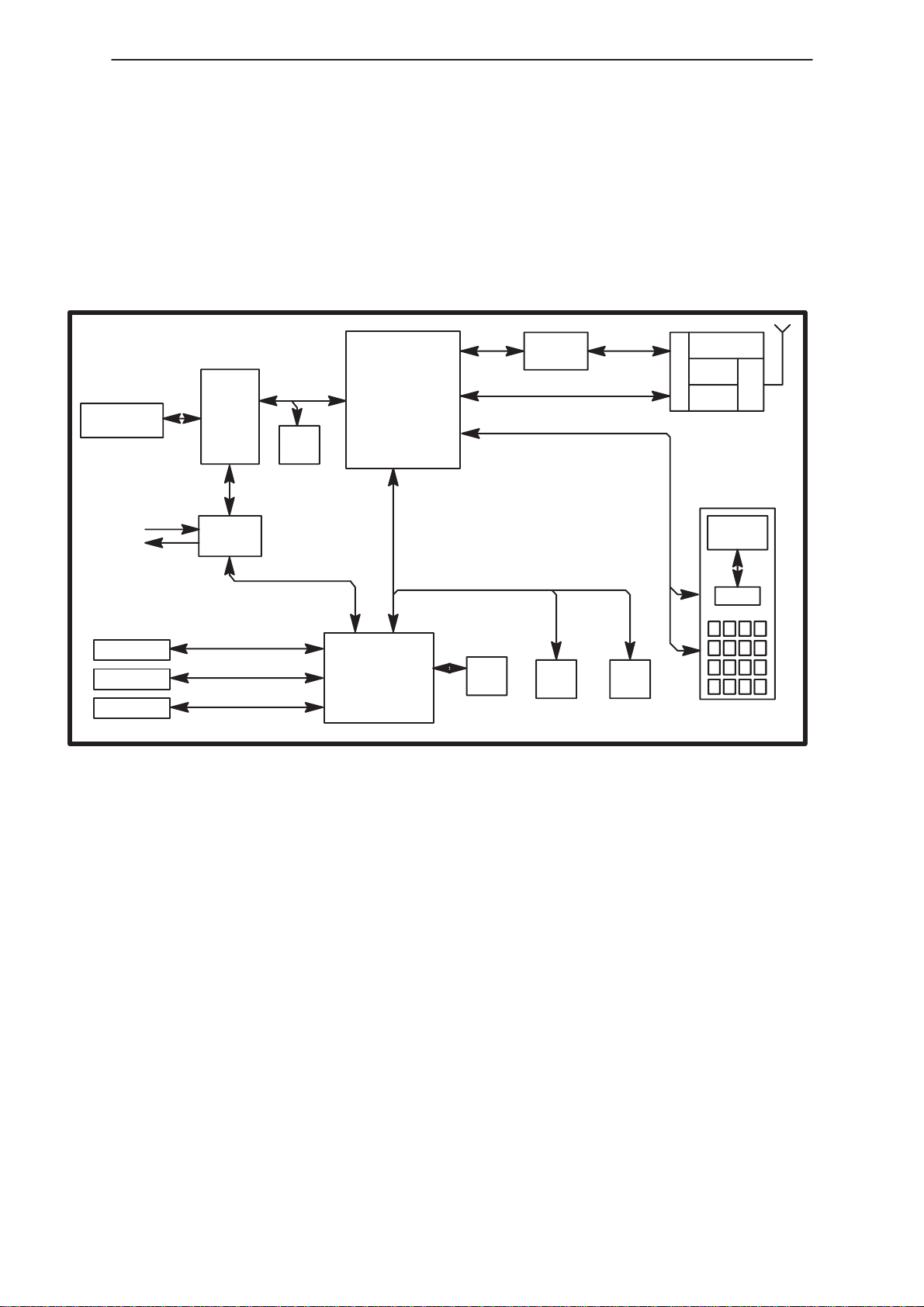

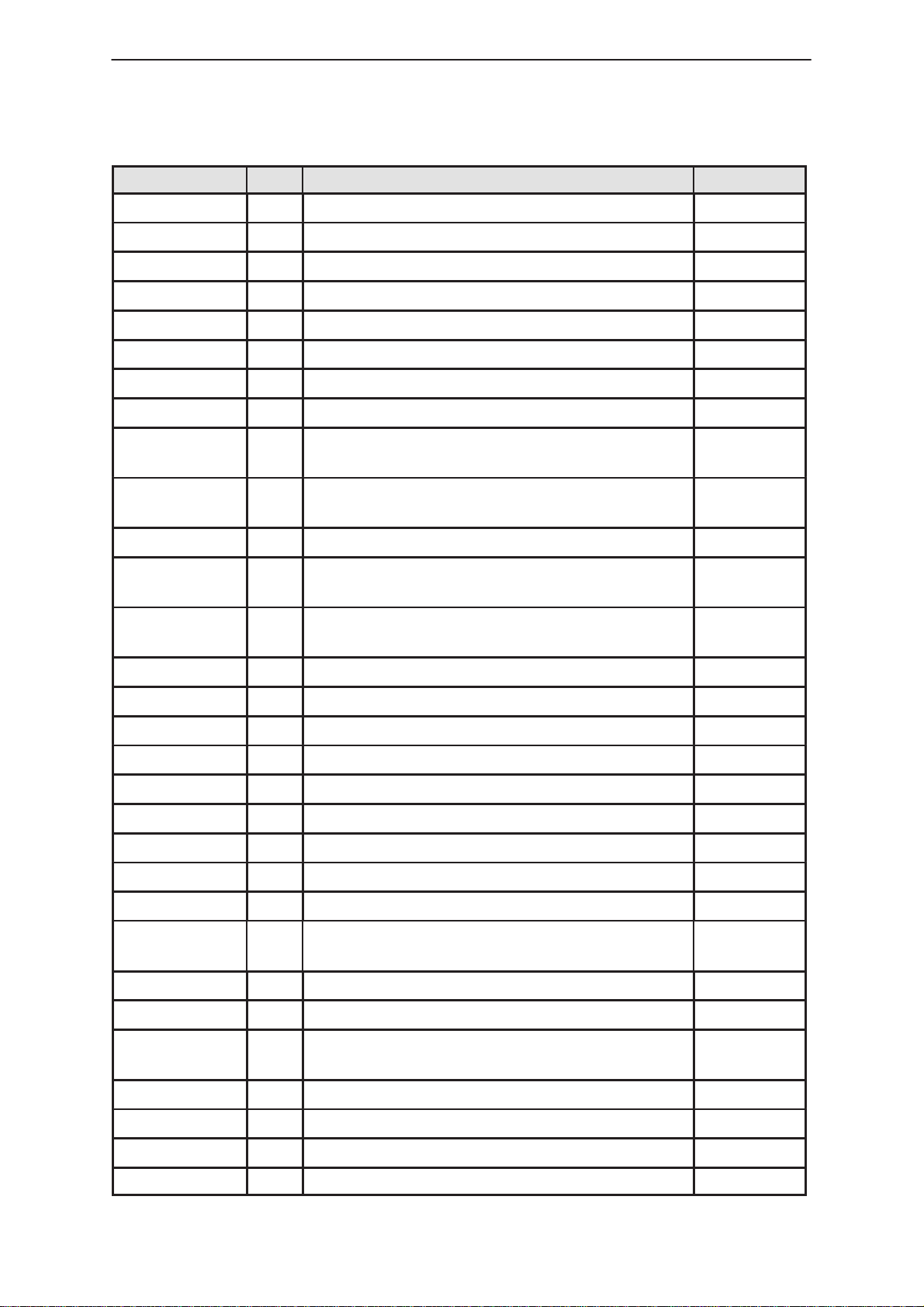

Baseband architecture refers to all those technology elements in the phone

design which do not include the RF functions. This document describes in

overview, the HD891 baseband architecture. Primarily the focus of this

document will be to highlight those aspects of the baseband architecture which

are unique to the CDMA project.

DSP

DBUS Interface

Multipath Analyzer

Message Injection

IS 125

MIC

EAR

sio

sio

ext

mem

sio

sio

PCM

CODEC

io

A15:0,

D7:0

64K x

16

SRAM

ASIC

CDRFI

System Module

RF

SYN

C

O

N

T

REC

R

O

L

XMIT/MOD

DUP

UIF–module

LCD

io

Switche

r

Charge

FLASH

r

LOAD

MBUS

Interfac

e

Charger Control

sio

sio

io

sio

sio

ext mem

MCU

Figure 1 Baseband – Interconnections

Baseband Block Connections

Below is a list of the functional blocks of the baseband architecture:

– Microcontroller Unit (MCU)

– MCU External Memory –

Electrically Eraseable Programmable Read Only Memory (EEPROM)

Static Random Access Memory (SRAM)

Flash Memory

A19:0,D7:0

sio

16k x 8

Serial

2

PROM

E

1M x 8 32K x 8

FLASH SRAM

LCD Driver

Issue 1 04/99

– Digital Signal Processor (DSP)

– DSP External Memory –

Static Random Access Memory (SRAM)

– CDSB ASIC

– CDMA RF to BB Interface (CDRFI)

– Audio Coder/Decoder (CODEC)

Page 4–5

Page 6

NHP–4

System Module

Technical Documentation

Internal Signals and Connections

Power Block

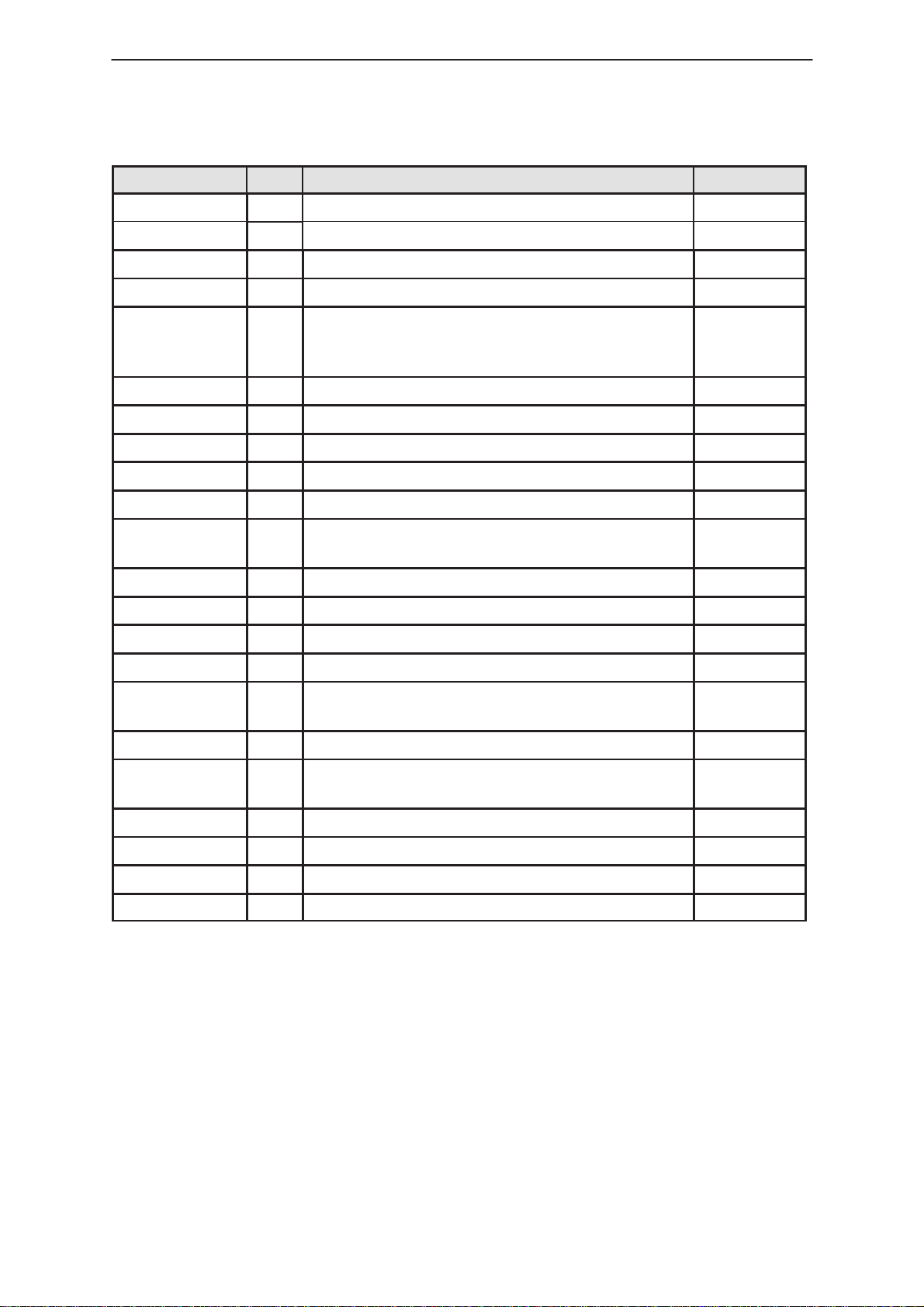

Table 1. Power Block Connections

Signal Name T ype Notes T o/From

XPWRON IN Power on switch UIF

WATCHDOG IN Watchdog reset pulse MCU

VBATTERY IN Battery voltage Sys. conn.

CHAR+ IN Charger Voltage Sys. conn.

CHAR– IN Charger Return GND

CHAR_PWM IN PWM for controlling battery charging MCU

XPWR_RESET OUT Master reset, Power–on Reset ASIC

3VA OUT Analog 3.15V supply CODEC

PAMS

3VD OUT 3.15V power supply for baseband

5VD OUT 4.8V supply for MBUS and XEAR Differential Circuit

(Switched)

VAHS OUT 4.8V supply for XEAR Differential Circuit (Switched),

and power for the Headset Accessory

LCD_PWR OUT 4.8V supply with series diode and resistor for LCD

(LCD can’t use 4.8V)

BATT_ADC OUT Battery voltage input to ADC MCU

CHAR_ADC OUT Charger voltage input to ADC MCU

CHAR_INT OUT Signal to indicate a Charger has been connected to

Phone.

UIF

Opamp

(N708) and

System Connector

UIF

ASIC

MCU Block

Table 2. MCU Block Connections

Signal Name T ype Notes T o/From

MCU_CLK IN 15.36 MHz Clk into MCU ASIC

XSYS_RESET IN MCU Reset from ASIC ASIC

MCUAD(19:0) OUT MCU 20 bit Address Bus Mem, ASIC

MCUDA(7:0) I/O MCU 8 bit Data Bus Mem, ASIC

XMCU_AS OUT MCU Address Strobe ASIC

XMCU_RD OUT MCU Read used as Output Enable Mem, ASIC

XMCU_WR OUT MCU Write used as Read/Write select Mem, ASIC

MCU_NMI IN MCU Non Maskable Interupt ASIC

MCU_INT0 IN MCU Maskable Interupt 1 ASIC

CODEC_DI OUT

CODEC_CLK OUT

Page 4–6

Audio codec control data MCU

Clock for audio codec control data transfer MCU

Issue 1 04/99

Page 7

PAMS

NHP–4

Technical Documentation

Table 2. MCU Block Connections (continued)

XCODEC_CS OUT

CODEC_DO IN

Audio codec chip select MCU

Audio codec control data MCU

System Module

To/FromNotesTypeSignal Name

CALL_LED OUT UIF CALL_LED enable UIF

BACK_LIGHT OUT UIF BACK_LIGHT enable UIF

PHFS_TXD2 OUT Hands Free speaker Mute Control and Trans-

Sys. conn.

mitted data from Flash during Flash Programming.

HOOK_RXD2 OUT Recieved data during Flash Programming. Sys. conn.

VIB_CONT OUT Vibrator Control for quit alarm Sys. conn.

MBUS_OUT OUT MBUS data output Sys. conn.

VAHS_EN OUT Headset voltage enable Sys. conn.

CHAR_PWM OUT Control PWM for charging batteries. PWR

WATCHDOG OUT Watchdog signal used to reset watchdog cir-

PWR

cuit

TEMP1_EN OUT Control signal to pick RFTEMP1 for A/D read MCU

TEMP2_EN OUT Control signal to pick RFTEMP2 for A/D read MCU

BATT_ADC IN A/D input for battery voltage level PWR

CHAR_ADC IN A/D input for monitoring of charging voltage PWR

HOOK_RXD2 IN A/D input – Hook indicator (Phone on or off

Sys. conn.

Hook)

BTEMP IN A/D input for monitoring Battery temp. Sys. conn.

RFTEMP IN A/D input for monitoring RFTEMP 1 and 2

RF

temp.

BTYPE IN A/D input for monitoring Battery type. Sys.conn.

RSSI IN A/D input for monitoring RSSI. RF

JCONN IN A/D input for monitoring Accessory type. Sys. conn.

MBUS_DET IN MBUS data input. Sys. conn

Issue 1 04/99

Page 4–7

Page 8

NHP–4

System Module

Technical Documentation

PAMS

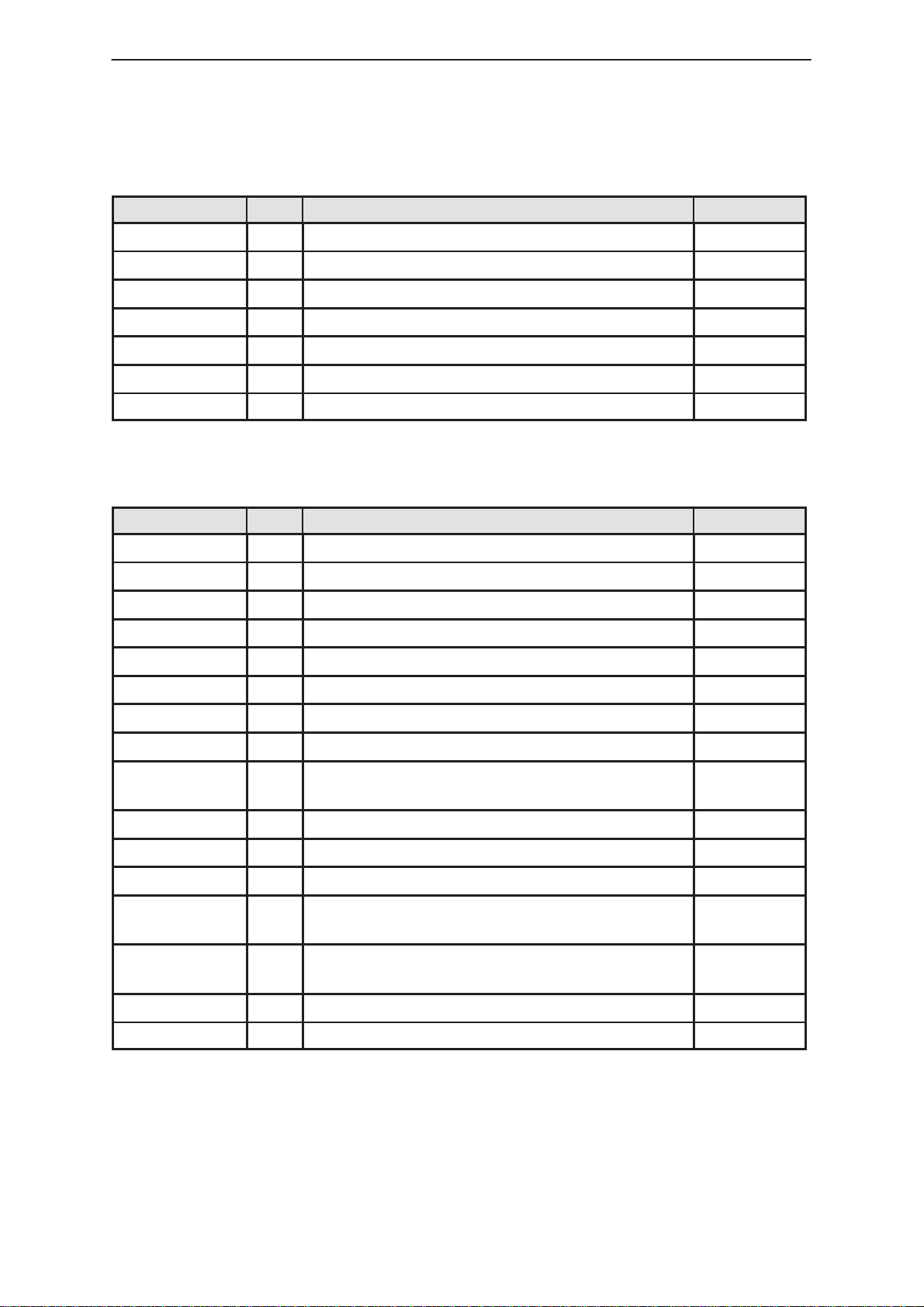

MCU Memory Block

Table 3. MCU Memory Block Connections

Signal Name T ype Notes T o/From

MCUAD(19:0) IN MCU 20 bit Address Bus MCU

MCUDA(7:0) I/O MCU 8 bit Data Bus MCU

XMCU_RD IN MCU Read used as Output Enable MCU

XMCU_WR IN MCU Write used as Read/Write select MCU

XFLASH_CS IN Flash Chip Select ASIC

XSRAM_CS IN SRAM Chip Select ASIC

VF IN 12 volt line for Flash programming Sys. conn.

DSP Block

Table 4. DSP Block Connections

Signal Name T ype Notes T o/From

DSP_CLK IN 15.36 MHz Clk into DSP ASIC

XSYS_RESET IN DSP Reset from ASIC ASIC

DSP_INT0 IN DSP Maskable Interupt 0 ASIC

DSP_INT1 IN DSP Maskable Interupt 1 ASIC

DSPAD(15:0) OUT DSP 16 bit Address Bus Mem, ASIC

DSPDA(15:0) I/O DSP 16 bit Data Bus Mem, ASIC

DSP_RXW OUT DSP Read / Write Select Mem, ASIC

IO_STRB OUT DSP Master Strobe for Memory Access Mem, ASIC

Codec_FS IN Frame Sync for aligning Codec audio data

ASIC

8KHz

Codec_MCLK IN CLK for moving Codec audio data ASIC

PCMOUT IN Audio Data from Codec CODEC

PCMIN OUT Audio Data to Codec CODEC

DSP_SYNC I/O Frame Sync for aligning data in and out of

DSP. Used by MP, MI, IS125 and Data Acc.

DSP_MCLK I/O CLK for moving data in and out of DSP. Used

by MP, MI, IS125 and Data Acc.

ASIC,

Sys. conn.

ASIC,

Sys. conn.

DBUS_IN IN Data to DSP. Sys. conn.

DBUS_OUT OUT Data from DSP. Sys. conn.

Page 4–8

Issue 1 04/99

Page 9

PAMS

NHP–4

Technical Documentation

System Module

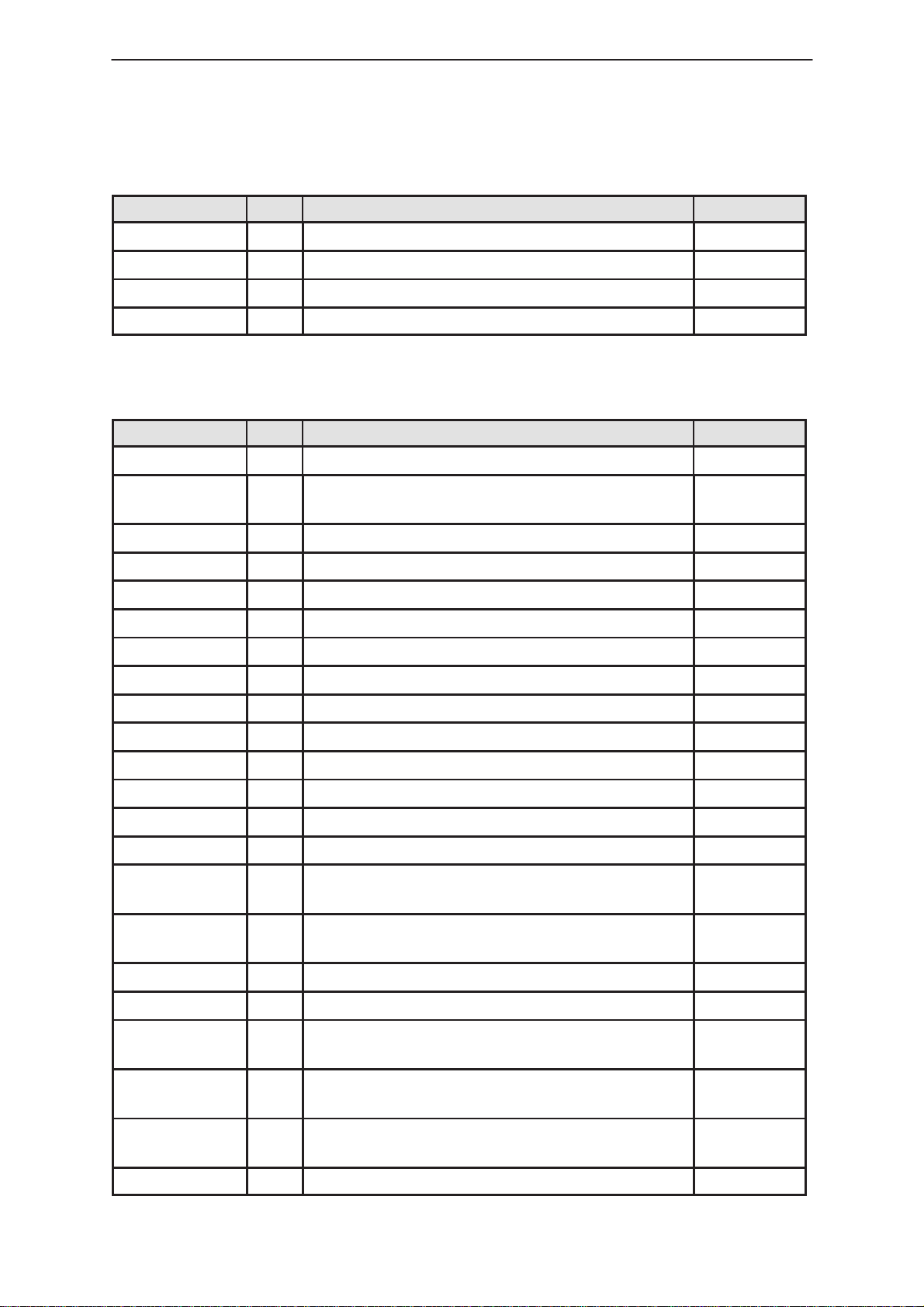

DSP memory Block

Table 5. DSP Memory Block Connections

Signal Name T ype Notes T o/From

DSPAD(15:0) IN DSP 16 bit Address Bus DSP

DSPDA(15:0) I/O DSP 16 bit Data Bus DSP

DSP_RXW IN DSP Read / Write Select DSP

XDSP_CS IN DSP SRAM Chip Select for Memory Access

CDSB ASIC Block

Table 6. CDSB ASIC Block Connections

Signal Name T ype Notes T o/From

XPWR_RESET

IN Master reset from 3V switching power supply PWR

XSYS_RESET OUT System Reset to MCU, DSP, CDRFI MCU, DSP,

CDRFI

OSC_OUT OUT 32KHz Clk output ASIC

OSC_IN IN 32KHz Clk input ASIC

OSC_EN IN Osc. enable ASIC

OSC_SEL IN Select clock or Backup ASIC

CDRFI_SI OUT CDRFI Serial Data In CDRFI

CDRFI_SO IN CDRFI Serial Data Out CDRFI

CDRFI_SEN OUT CDRFI Serial data ENABLE CDRFI

CDRFI_SCLK OUT CDRFI Serial data CLocK CDRFI

CDRFI_9.8M OUT CDRFI 9.8 MHz clock CDRFI

15.36M_IN IN 15.36MHz Clk IN CDRFI

9.83M_IN IN 9.83MHz Clk IN CDRFI

TXD(7:0) I/O CDRFI TX Data bits 0–7 CDRFI

CDRFI_RWSELOUT CDRFI Read/Write SELect CDRFI

CDRFI_IQSEL OUT CDRFI Tx IQ SELECT bit in digital mode, ad-

CDRFI

dress select bit in analog mode.

RXQ(4:0) IN CDRFI RX Quadrature–phase data bits 0–4 CDRFI

RXI(4:0) IN CDRFI RX In–phase data bits 0–4 CDRFI

DAFOUT IN CDRFI DAF INput –NOT

USED HD891–

IFclk IN Namps Support –NOT

USED HD891–

Noxw IN Namps Support –NOT

USED HD891–

GATE OUT CDRFI CDRFI

Issue 1 04/99

Page 4–9

Page 10

NHP–4

System Module

Table 6. CDSB ASIC Block Connections (continued)

Technical Documentation

To/FromNotesTypeSignal Name

DSP_CLK OUT 15.36 MHz Clk to DSP DSP

DSP_INT0 OUT DSP Maskable Interupt 0 DSP

DSP_INT1 OUT DSP Maskable Interupt 1 DSP

DSPAD(15:0) IN DSP 16 bit Address Bus (15,14,8–0) DSP

DSPDA(7:0) I/O DSP 8 bit Data Bus DSP

DSP_RXW IN DSP Read / Write Select DSP

IO_STRB IN DSP Master Strobe for Memory Access DSP

XDSP_IS IN DSP Data Strobe DSP

PAMS

DSP_SYNC OUT Frame Sync for aligning data in and out of

Sys. conn.

DSP. Used by MP, MI, IS125 and Data Acc.

DSP_MCLK OUT CLK for moving data in and out of DSP. Used

Sys. conn.

by MP, MI, IS125 and Data Acc.

DBUS_IN IN Signal used as an interupt for DBUS activity Sys. conn.

Codec_FS OUT Frame Sync for aligning Codec audio data

8KHz

DSP,

CODEC

Codec_MCLK OUT CLK for moving audio Codec data DSP,

CODEC

MCU_CLK OUT 15.36 MHz Clk to MCU MCU

MCUAD(19:0) IN MCU 20 bit Address Bus (19–16,5–0) MCU

MCUDA(7:0) I/O MCU 8 bit Data Bus MCU

XMCU_AS IN MCU Address Strobe MCU

XMCU_RD IN MCU Read used as Output Enable MCU

XMCU_WR IN MCU Write used as Read/Write select MCU

MCU_NMI OUT MCU Non Maskable Interupt MCU

MCU_INT0 OUT MCU Maskable Interupt 1 MCU

MBUS_DET IN MBUS data input. Sys. conn

CHAR_INT IN Signal to indicate a Charger has been con-

PWR

nected to Phone.

XFLASH_CS OUT Flash Chip Select MCU Mem.

XSRAM_CS OUT SRAM Chip Select MCU Mem.

XROM_CS OUT EEPROM Chip Select –NOT

MCU Mem.

USED HD891–

LCD_COL I/O LCD and COL/RO lines to UIF UIF

CDATTEN OUT SW AGC to RF RF

RF_LIMADJ IN RF

RF_SCLK OUT Serial Data Clk RF

Page 4–10

Issue 1 04/99

Page 11

PAMS

NHP–4

Technical Documentation

Table 6. CDSB ASIC Block Connections (continued)

System Module

RF_SDAT A OUT Serial Data RF

RF_RX_LE OUT Latch Enable for Serial Data RF

RF_TXB OUT Tx Power Bias

RF

8bit PDM – 3.84Mhz

RF_TXREF OUT REF Level for TXIP comparator

RF

8bit PDM – 1.92Mhz

RF_AFC OUT VCTCXO control voltage

RF

8bit PDM – 3.840Mhz

RF_AGCREF OUT AUXAGC RF

RF_TXGAIN OUT Offsets TX gain to RX gain –NOT

RF

USED HD891– 7bit PDM – 4.9152Mhz

RF_TXSLP OUT Correction of TX gain slope –NOT

RF

USED HD891– 7bit PDM – 1.92Mhz

To/FromNotesTypeSignal Name

RF_RXSLP OUT Correction of RX gain slope –NOT

RF

USED HD891– 7bit PDM – 1.92Mhz

RF_TXC OUT Limit maximum TX gain NOT

RF

USED HD891

8bit PDM – 4.9152Mhz

RF_PDM1 OUT PDM NOT

USED HD891

RF_PDM2 OUT PDM NOT

USED HD891

RF_TXPUNC OUT Enables the PA RF

RF_VCO_EN OUT Same as RF RESET to CDCONT RF

RF_RFE0 OUT RF Control Line RFEN0 RF

RF_RFE1 OUT RF Control Line RFEN1 RF

RF_RFE2 OUT RF Control Line RFEN2 RF

RF_RFE3 OUT RF Control Line FAST RF

RF_RFE4 OUT RF Control Line RX_FIL_CAL RF

RF_RFE5 OUT RF Control Line SEL0 RF

RF_RFE6 OUT RF Control Line SEL1 –NOT

RF

USED HD891–

RF_RFE7 OUT RF Control Line RX_CAL NC

Issue 1 04/99

Page 4–11

Page 12

NHP–4

System Module

Technical Documentation

CDRFI Block

Table 7. CDRFI Block Connections

Signal Name T ype Notes T o/From

XSYS_RESET IN XRESET When set = 0, reset registers

ASIC

to default values.

SDI IN Serial Data In ASIC

SDO OUT Serial Data Out ASIC

SENABLE IN Serial data ENABLE ASIC

SCLK IN Serial data CLocK ASIC

9.8M IN 9.8 MHz clock ASIC

VCLKIN IN VCLocK recovery INput RF

VCLKOUT OUT VCLocK recovery OUTput ASIC

CLKIN IN CLocK recovery INput RF

PAMS

CLKOUT OUT CLocK recovery OUTput ASIC

TXI+ OUT TX signal In–phase (+) RF

TXI– OUT TX signal In–phase (–) RF

TXQ+ OUT TX signal Quadrature–phase (+) RF

TXQ– OUT TX signal Quadrature–phase (–) RF

TXD(7:0) I/O TX Data bits 0–7 ASIC

R/WSEL IN Read/Write SELect ASIC

IQSELECT IN Tx IQ SELECT bit in digital mode,

ASIC

address select bit in analog mode.

RXQ IN RX signal Quadrature–phase RF

RXI IN RX signal In–phase RF

RXQ(5:0) OUT RX Quadrature–phase data bits 0–5 ASIC

RXI(5:0) OUT RX In–phase data bits 0–5 ASIC

TXAGC1 OUT TX AGC control RF

RXAGC1 OUT RX AGC control RF

ANATX OUT ANAlog mode TX signal –NOT USED

RF

HD891–

ANARX+DAF IN ANAlog mode RX + DAF signal –NOT USED

RF

HD891–

DAFOUT OUT DAF OUTput –NOT USED HD891– ASIC

GATE IN Controls TX output ASIC

VCO_EN IN Disables the Clock squaring circuits ASIC

TEST IN TEST input (if not used, must be on VSS)

Page 4–12

Issue 1 04/99

Page 13

PAMS

NHP–4

Technical Documentation

System Module

AUDIO Block

Table 8. Audio Block Connections

Signal Name T ype Notes T o/From

3VA

PCMIN

CODEC_FS

CODEC_MCLK

CODEC_DIN

CODEC_CLK

XCODEC_CS

XMIC_JCONN

MICN, MICP

PCMOUT

CODEC_DO

MIC_ENX

XEAR_HFJPWR

EARN, EARP

OUT

OUT

OUT

OUT

OUT

Analog supply voltage, Max 80 mA. PWR

IN

Received audio serial data DSP

IN

8kHz frame sync ASIC

IN

512kHz codec audio data clock ASIC

IN

Audio codec control data MCU

IN

IN

Clock for audio codec control data transfer

Audio codec chip select MCU

IN

External microphone Sys. conn.

IN

Differential microphone signal UIF conn

IN

Transmitted serial audio data input DSP

Audio codec control data output MCU

Microphone enable UIF

External received audio Sys. conn.

Internal received audio UIF

MCU

Functional Description

Below is a list of the functional blocks of the baseband architecture:

– Power Management

– Microcontroller Unit (MCU)

External Memory –

Electrically Eraseable Programmable Read Only Memory (EE-

PROM)

Static Random Access Memory (SRAM)

Flash Memory

MBUS

– Digital Signal Processor (DSP)

External Memory –

Static Random Access Memory (SRAM)

DBUS

Multipath Analyzyer

– Audio Coder/Decoder (CODEC)

– CDSB ASIC

Sleep Clock Oscillator (32 KHz)

– CDMA RF to BB Interface (CDRFI)

– RF Interface

Issue 1 04/99

Page 4–13

Page 14

NHP–4

System Module

Power Management

This section covers the power management system of the HD891

transceiver. The power management software is the same as HD881 with

some minor updates, however, the power supply section is completely

new. A highly efficient and low noise DC–DC converter is used for most of

the baseband power, and the PSL logic is replaced using a few

comparators. The charging circuit is also new.

PAMS

Technical Documentation

General

The HD891 power management section consists of charging, power–on,

watchdog, & reset circuits, and voltage regulators. The main 3V

baseband supply is generated by a buck mode dc–dc converter. Power

off quiescent current drain is 250uA while power on sleep mode current is

2mA.

Power Distribution

Power distribution to the rest of the phone is very simple. Baseband uses

the 3.15V 3VD output from the dc–dc converter. RF uses VBAT (from

VBATTERY) as a supply. UI and MBUS use the 4.8V supply (5VD). The

UI also uses VBATTERY for the LEDs and buzzer.

Figure 2

Page 4–14

Issue 1 04/99

Page 15

PAMS

NHP–4

Technical Documentation

Charging Switch/Regulator

The charging switch/regulator acts to connect the charger input to the

battery with minimal losses. To prevent overcharging the output voltage is

limited to 8.4V (+/–0.25V) when CHAR_PWM is high or 5.4V when

CHAR_PWM is low (startup). Maximum current is 1000mA. The input is

protected against transients by a varistor. Maximum dc input voltage

range is –5V to +16V.

Charging is controlled by the CHAR_PWM signal. When it is high,

charging is on. If the battery voltage is less than 5.4V charging is on

regardless of the CHAR_PWM state. Charging can only occur if the

charging voltage is greater than the battery voltage.

If there is no battery the charger will provide 8.5V working voltage to the

phone. The software should detect a no–battery condition and display a

warning in the UI. If desired, it may be possible to operate the phone in

standby, as long as the total phone current is less than 280mA.

Battery Monitor

System Module

A comparator continuously measures the battery voltage. When battery

voltage rises above 5.2V the phone will power on (watchdog reset). When

battery voltage falls below 5.0V the phone powers off. The 200mV

hysteresis prevents oscillation.

Charger Detection

When the charger input voltage rises above 5.0V and battery voltage is

above 5.2V the phone is powered on (watchdog reset). If battery voltage

is lower than 5.4V the charger automatically turns on to provide a

pre–charge. And then once the battery voltage reaches 5.2V the battery

monitor turns on the phone.

When a charger is connected and the phone is on, the CHAR_INT signal

will go high. It is possible that when the battery falls below 5.4V a false

CHAR_INT may occur even without a charger connected. This should not

be a problem because the software should have already powered down

the phone.

Watchdog

The watchdog timer is reset on power up or when the WATCHDOG input

is toggled. The minimum pulse width for either input is 10ms. Minimum

watchdog timeout is 9 seconds. If the MCU does not reset the timer by

toggling WATCHDOG (falling edge triggered) within the timeout period the

3VD output (& software) will power down.

Note: It is best to hold WATCHDOG low so a power down itself does not reset the timer!

Issue 1 04/99

Page 4–15

Page 16

NHP–4

System Module

DC–DC Converter, Regulators, Reset

Technical Documentation

PAMS

The main 3VD supply for baseband is regulated by a DC–DC converter. It

offers 90% efficiency in normal mode and 80% during sleep. The free–run

operating frequency is 250kHz, but locks to either 307kHz (CDMA) or

340kHz (AMPS) of the PWR_CLK input signal (Note: HD891 will operate

in CDMA mode only). The PLL lock time is 10ms. To put the DC–DC

converter into sleep mode the shutdown pin and PWR_CLK should be

held low.

The 5V supply to the LCD and MBUS is from a 4.8V LDO linear regulator.

Note: The LCD may be changed to a 3V version!

Table 9. Regulator Specifications

Output Voltage Current Noise

3VD 3.15V +/–0.10V 500mA 5mVpp 50mV n/a 100mV, 5ms

5VD 4.8V +/–0.2V 50mA 5mVpp 50mV 1ms 100mV, 5ms

1. Using a resistive load at 1/2 rated current.

2. From zero to rated current load.

1

Regulation

2

Risetime Transient

2

The XPWR_RESET line is released about 150ms after the 3VD output

has risen beyond 2.5V.

MCU BLOCK

The MCU block controls the user interface, link layer, upper layer protocols,

some physical layer tasks, and accessories not linked to data services. It also

executes service and diagnostics commands and manages the battery.

The block includes a Hitachi HD647534 processor ( 32K internal ROM, 2K

internal SRAM ) with access to a 1M x 8 FLASH, 32K x 8 SRAM, and 16K x 8

EEPROM. Clock and sleep control, system decode, software timers, and other

system support are incorporated into CDSB ASIC. MCU input clock will be

sourced by a 15.36 MHz clock from the ASIC. The period of an MCU state is

equal to the 15.36 MHz clock divided by two. A low power software standby

mode is invoked whenever processing lulls. The MCU communicates with

CDSB ASIC over a byte wide parallel data bus.

MCU memory pages 2 and 4 can be changed based on bits set in the CDSB

ASIC. Page 2 maybe set for EEPROM select or FLASH select. Default is

EEPROM. Page 4 maybe set for SRAM select or FLASH select. Default is

FLASH.

Page 4–16

Issue 1 04/99

Page 17

PAMS

NHP–4

Technical Documentation

External Memory

External memory accessed by the MCU:

1M x 8bit FLASH memory

– 150 ns maximum read access time

– contains the main program code for the MCU ; in the beginning

– Not all the FLASH is used, ONLY 40000 and up is available.

32k x 8bit SRAM memory

– 150 ns maximum read access time

16k x 8bit EEPROM memory (Serial)

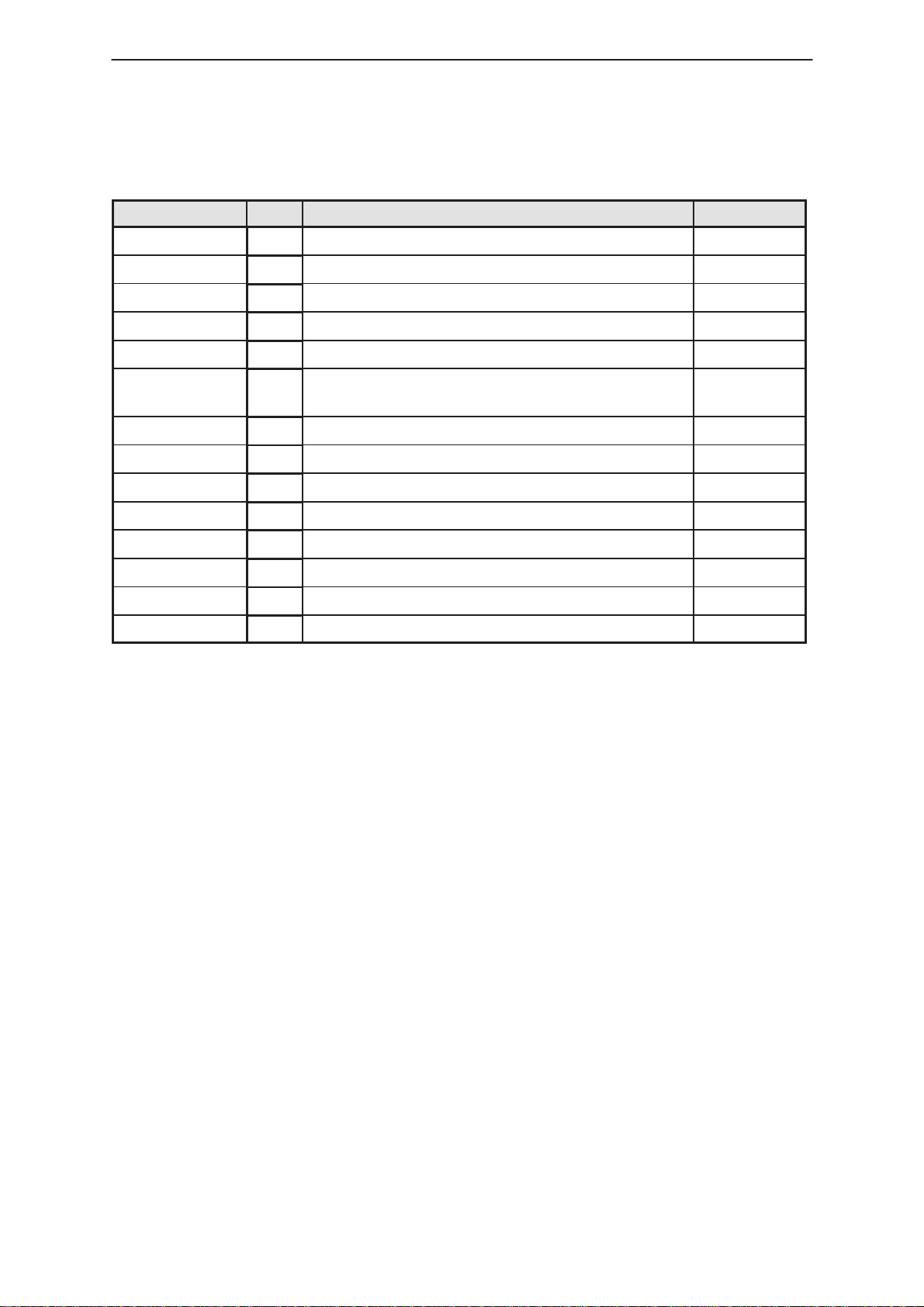

Memory Map

PAGE 0:

H0 0000

H0 0200

Vector tables

on chip

32K bytes

the DSP program code locates also in FLASH

PAGE 0:

H0 F680

on chip

RAM

2K bytes

ROM

H0 FE80

registers

384 bytes

System Module

PAGE 1:

ASIC

PAGE 2:

EEPROM/

FLASH

PAGE 3:

SRAM

PAGE 4:

FLASH/

SRAM

PAGE 5:

PAGE 6,7:

FLASH FLASH

PAGE 8,9,A,B: PAGE C,D,E,F:

Issue 1 04/99

FLASH FLASH

Figure 3 Memory Map

Page 4–17

Page 18

NHP–4

System Module

MBUS

MBUS interface will be implemented via serial port on the MCU. Protocol will be

DCT MBUS compatible.

DSP Block

The DSP block functions include speech processing, time critical physical layer

tasks, and multiplex sublayer tasks. The block consists of a TI LEAD processor

clocked by the 15.36 Mhz system clock. An internal upconverter and PLL

mechanism in the DSP will allow machine cycle rates up to 50 MHz. We will be

using a x 3 option, the ASIC will provide the 15.36 MHz clock to the DSP. This

will be advantageous in that a duty cycle closer to 50% could be guaranteed

without relying on the output of the VCTCXO which has the possibility of a much

wider variation. A low power sleep mode can invoked whenever processing

allows. A 64kx16 SRAM will be incorporated.

The DSP must communicate with the MCU and the CDSB ASIC. MCU

communication is directed through the CDSB ASIC to manage sleep and

interrupt timing. The mailbox function inside the ASIC provides the ”gateway” for

communications between the two processors. The digital ASIC interface is

memory mapped I/O consisting of byte wide parallel data, address lines, and

access control lines.

PAMS

Technical Documentation

The DBUS and the Multipath Analyzer/Message Injection are outputs/input of

the DSP. Only one of these comm. links may be used at a time.

The DSPU (Digital Signal Processing Unit) block is in charge of the channel and

speech coding according to the IS–96–B specifications for 8kbit VOCODERS,

and IS–3972 for 13kbit VOCODERS. The block consists of a TMS320C5xx

DSP and external RAMs. The DSP chip contains 28kword internal mask ROM

and 5k word internal and 32k word external RAM. The 64K word external RAM

is loaded with code stored in the MCU flash ROM.

The DSPU provides control and signal processing for CDMA modes of

operation.

– Control and general functions:

– communication with MCU / PC–Locals

– mode control of ASIC hardware

– RF control

– DBUS communication

– CDMA mode speech processing:

– Vocoder (Voice Coder) encoding and decoding

– acoustic echo cancellation

– CDMA mode control:

– PN (Pseudo Noise) signal acquisition and monitoring

– soft & hard handoffs

– ASIC Rake Receiver demodulator control

– received data rate determination

– Multiplex Sublayer (LM) routing of data to MCU or Voice Coder

– Loopback and Markov Service Options

Page 4–18

Issue 1 04/99

Page 19

PAMS

NHP–4

Technical Documentation

External Memory

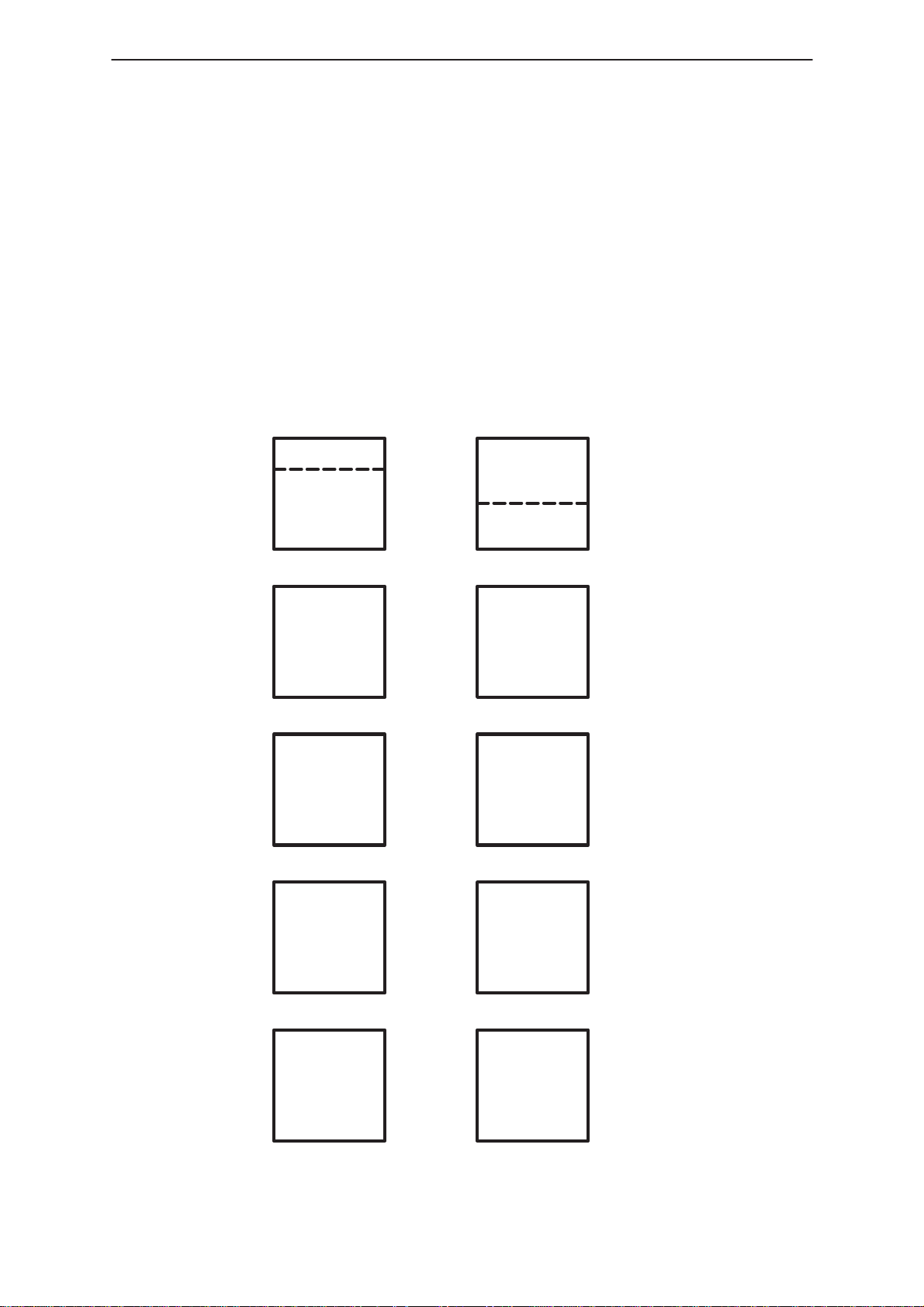

64k x 16 SRAM memory

Figure 4 shows the relative location and sizes of the memories used in the program and data spaces of the processor with 64k external SRAM.

Program

CDMA OVLY

(1k)

C_IP_RAM

XP_RAM

31k

(prog)

– 85 ns maximum read access time

0x0000

0x1000

0x1400

Data

ID_RAM

4k

rsvd cdma ovly

System Module

I/O

CDMA data

DBUS

0x9000

P_ROM

20k

0xE000 ASIC

D_ROM

8k

(prog/data)

0xFFFF 0xFFFF

Figure 4 DSP memory configuration w/ 64k external SRAM

XD_RAM

16k

(data only)

D_ROM

8k

(prog/data)

= Internal

0xC000

8k

DBUS interface will be implemented via serial port on the DSP. Protocol will be

TI DSP serial. Voltage levels will be 3 volt logic. When the DBUS is used with

the PCMCIA data tranfer card,the 3 volt logic will be converted to 5 volts by the

interface cable.

Issue 1 04/99

Page 4–19

Page 20

NHP–4

System Module

Multipath Analyzer

The Nokia Multipath Analyzer (MA) consists of several Microsoft Windows

application programs running on a PC with a PC DSP card that will receive

(only) real–time information from the DBUS. The Clock will be provided by the

PC DSP card. The DSP will send, selected by a test bitmask, through its built–in

serial port, test data to be processed by the MA’s PC DSP card. The formatted

output from the PC DSP card will then be displayed and controlled by the end

user through the Microsoft Windows display applications.

Message Injection

The Nokia Message Injection (MI) consists of a Microsoft Window application

program running on a PC with a PC DSP card that will transmit (only) real–time

commands thru the DBUS. The Frame Sync and Clock will be provided by the

PC DSP card. The PC DSP will send, selected by a test bitmask, through its

built–in serial port, commands to the phone DSP.

PAMS

Technical Documentation

Digital ASIC Clock

The CDSB ASIC includes two primary functions: System functionality and CDMA

baseband real time signal processing. Detailed descriptions of the functionality

and interfaces are included in the CDSB ASIC specification.

System functions that are incorporated in the CDSB ASIC include: clock and

sleep control, reset control, soft watchdog timer, interrupt management, MCU

decode, UIF keyboard interface, UIF display interface, MCU software OS timer,

MBUS detection and netfree timer, DBUS detection, RF controls, synthesizer

control, codec clock generation, slotted paging mode timers, and test functions.

CDMA functions include: demodulator searcher and rake receiver, symbol

combiner, power control, AFC, de–interleaver, Viterbi decoder, convolutional

encoder, interleaver, and FIR filter.

Sleep Clock Oscillator

A low power 32 KHz sleep clock oscillator is built into the ASIC.

RF Control PDM’s

All PDM output signals can be controlled by the DSP. The DSP writes a digital

2’s complement number into a register and the serial output from the PDM

generates a signal whose average value reflects the same digital number. Note

that the output reflects a 2’s complement format.

0 Mid Range Value

1 –> 127 Increasing negative value

255–> 128 Increasing positive value

equal number of ’1’ and ’0’ pulses.

maximum negative value has one ’1’ pulse.

maximum positive value has zero ’0’ pulses.

Page 4–20

Issue 1 04/99

Page 21

PAMS

NHP–4

Technical Documentation

The DSP can modify the RFIPDMSRC(4:0) register to allow the DSP algorithms

to control the cdAfc, cdTxb, cdTxc, cdTxGainAdj and cdAgcRef.

All PDM outputs can be inverted by modifying the RFPDMPOL(2:0) and

RFPDMPOL(4:0) registers.

CDRFI

CDRFI is a monolithic CMOS high speed CODEC designed for use in CDMA

(Code Division Multiple Access) Digital Cellular Telephone applications. It

provides A/D conversion of the in–phase and quadrature signals in receive path

and generation of the in–phase and quadrature signals in transmit path. The

CODEC interfaces with digital chip(s) via two parallel interface (separate

interfaces for AD and DA sig

nal converters) and one serial interface (for the control DA converters).

Features

– 64–pin TQFP package.

– 3.15V 5% power supply.

– Operating temperature –30 to +85 deg C.

– Internal signal ground generation (band gap).

System Module

–CDMA mode receive path (I,Q):

– 5 bit Analog to Digital signal converters.

– Digital offset correction.

– Single ended inputs.

– 9.8304 MHz sampling rate.

– CDMA mode transmit path (I,Q):

– 8 bit Digital to Analog signal converters.

– 4’th order reconstruction filters.

– Differential outputs.

– 4.9152 MHz sampling rate.

– Digital AGC control, transmit path:

– 10 bit Digital to Analog converter.

– Single ended output.

– 19.2 kHz sampling rate.

– Digital AGC control, receive path:

– 10 bit Digital to Analog converter.

– Single ended output.

– 19.2 kHz sampling rate.

*The coding for all converters is offset binary*

Issue 1 04/99

Page 4–21

Page 22

NHP–4

System Module

– Digital control:

– Clock recovery circuits (input signal level 200 mVrms sinewave, output

3volt–level):

Audio Block

The block consists of audio codec with some peripheral components. The

codec includes an internal microphone and earpiece amplifier and all the

necessary switches for routing. The controlling of the codec is done by the

MCU. PCM–data is transferred to/from the DSP.

PAMS

Technical Documentation

– 12 bit bus for signal ADC’s.

– 8 bit bus for signal DAC’s and

analog mode signal converters.

– Serial bus for AGC DAC’s.

– 9.8304 MHz squaring circuit.

–15.360 MHz squaring circuit.

An ST5090 PCM codec converts analog voice to digital samples that are

processed by the DSP. It also accepts DSP processed speech, converts it to

analog and transmits the output to the handset or hands free speaker. The

CODEC samples at 8 KHz and sends/receives linear coded data to/from the

DSP over a dedicated serial port. The master clock of the CODEC is

synchronized with the RF VCTCXO and is generated by the CDSB ASIC.

CODEC set up and DTMF tone generation are controlled by the MCU via a

second serial port.

The internal earpiece is driven differentially directly from the CODEC. This

configuation allows common mode noise on the two voice signals to be rejected.

However, the XEAR signal (used for accessories) is a single signal that is driven

by a differential OPAMP circuit out the bottom connector. The differential

speech signal from the CODEC is input to this circuit to reduce the common

mode noise.

Block Description

The audio codec communicates with the DSP through a SIO (signals: PCMIN,

CODEC_FS, CODEC_MCLK and PCMOUT) . MCU controls the audio codec

functionality through a separate SIO (signals: CODEC_DO, CODEC_DI,

CODEC_CLK and XCODEC_CS).

Receive Standby Mode

Page 4–22

The codec is in standby except when keybeeps are needed. LO–output is

floating in standby and it disables the microphone bias circuit on flex.

In Call Mode

The codec is enabled and serial audio data is transferred to/from the DSP.

Issue 1 04/99

Page 23

PAMS

NHP–4

Technical Documentation

RF Block Introduction

This document is divided into three major sections of the RF circuitry: the

transmitter, the receiver, and the synthesizer.

Transmitter

Functional Description

The 2170 uses CDMA spread spectrum modulation producing a channel

bandwidth of 1.23 MHz. For any transmit output level, the power is

spread over the entire channel bandwidth. The transmitter frequencies

are 1850 to 1910 MHz. There are 1200 channels in 50 kHz steps, where

each channel is 1.23 MHz wide, so several phones can operate in the

same frequency band, using the CDMA modulation to separate each

signal. The power control for the 2170 is performed in very tight 1 dB

increments, making the automatic gain control alignment a critical step in

the alignment procedures. In addition, the phone limits the PA output

power to 24 dBm.

System Module

This functional Description is comprised of three sections. The first,

section,

exiting the 2170 transmitter circuit, as well as the DC voltage supplies that

bias it.

of the transmitters control features. Finally, a circuit description is

included.

DC Power Control

The entire TX chain is turned on and off by the VR7 signal from the

baseband ASIC(D705). This signal controls 2 separate voltage

regulators, V3.6TX (N306), and V4.8TX (N305) which provide the bias

voltage and current for the entire transmitter chain, except for the PA

(N304). The PA draws it’s power indirectly from the battery connection,

through a discrete regulator circuit, consisting of a DC power transistor

(V300), which is switched on and off by V4.8TX.

During ‘non–full–rate’ operation, the TX_GATE signal from the baseband

ASIC (D705) is provided to the transmitter during a call to burst on and off

of the pre–driver (V305), driver (V303), and power amplifier (N304)

circuits that require higher current. The TX_GATE signal is simply a

control voltage used to switch on and off the higher current devices,

whether that current is drawn from the TX regulators or from the battery

directly. This is done to save current during pulsing operation of the

transmitter and to meet output power requirements when not transmitting,

even though VR7 is constantly a logic high.

DC Power Control, describes the various signals entering and

TX Gain Limiting and CDMA TX Gain Control describes the operation

Issue 1 04/99

Page 4–23

Page 24

NHP–4

System Module

The TX Gain is designed to overcome gain variation across the band as

well as device–to–device variations. Therefore, it is possible (using

manual control when transmit limiting is off) to produce an output power

that causes the phone to produce power much higher than necessary

resulting in excessive heat. If left on even for a few minutes without

current limiting the power supply, the unit can be damaged.

TX Gain Limiting

TX Limiting is a control feature for CDMA TX operation. In some

conditions the AGC loop of the phone may call upon the transmitter to

provide more output power than the phone is specified. The TX Limiting

circuit places a ceiling or limit on the output power of the CDMA

transmitter. Transmitting above the limit might put the PA (N304) out of

its linear range of operation, resulting in excessive spurious emissions,

and draining the charge on the battery much faster.

TX Limiting is performed by comparing two voltage signals, the

TX_LIM_ADJ (TXI_REF PDM from ASIC, D705) and the TX level voltage

(TXI) from the detector diode circuit (V307). This comparison is done with

an op–amp comparator (N303). The shifted output of the op–amp is the

TX_LIM voltage signal, which is routed to the CDSB ASIC (D705) pin 95.

When the CDMA TX output is not at the limit, the TX_LIM line is logic high,

approximately 3.15 V. In CDMA operation, the TXI_REF PDM stays fixed

at a tuned voltage level. This tuned level corresponds to the TX output

power limit of 24 dBm tuned during alignment. The tuned TXI_REF PDM

line will be approximately 2.0 V, however it will change slightly over

frequency due to the alignment of the phone. The detector voltage (from

V307) directly reflects the output power of the TX PA (N304). For

maximum CDMA output power, TXI is approximately 2.0 V. Failure of the

minimum CDMA output power from the transmitter will not affect the

limiting functionality.

PAMS

Technical Documentation

Page 4–24

When TXI equals TXI_REF at the internal comparator, the TX_LIM line

goes logic low to approximately 0.0 V. This signals the CDSB ASIC to

cease requesting additional gain of the TX PA, and to actually back off on

the gain by a small amount. The CDMA TX output power drops below the

limit value and, consequently, the TXI voltage no longer equals the

TXI_REF voltage at the comparator. The TX_LIM signal then goes to a

logic high. Should the AGC loop still require additional output power to

maintain the call, it will continue to increase the TX gain, and again the

limit will be reached. The TX_LIM line will toggle, and the cycle will

continue. Thus, a way to test CDMA TX Limiting Control is to probe the

TX_LIM line with an oscilloscope and maximize the gain of the transmitter.

When the TX output power reaches the limit the TX_LIM line will toggle

continuously, appearing as a square wave 3.2 Vpp (read at R840) with an

approximate frequency of 400 Hz.

Issue 1 04/99

Page 25

PAMS

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

NHP–4

Technical Documentation

CDMA TX Gain Control

A fundamental requirement for proper CDMA system operation is that

received signal power levels reaching the digital demodulators remain

constant. This is true for both the mobile unit and the base station. The

mobile unit must dynamically adjust the gain of its receiver to ensure that

the down converted baseband I & Q signal levels delivered to the CDSB

ASIC are always constant. The mobile must also dynamically adjust its

transmit output power so that the base station always receives the same

signal strength. The amount of gain needed at the mobile unit receiver is

used to determine how much gain to provide the mobile unit transmitter,

thus they are linked in a loop (called open loop operation).

This automatic gain control (AGC) is accomplished by a symphony of

operations between the CDSB ASIC(D705), the CDRFI(N703), and the

RX and TX AGC circuits. The gain of the CDMA transmitter is controlled

by two devices, the IF AGC IC (N308) and the AT–118 variable attenuator

(N300). To achieve a total required transmitter dynamic range of 74 dB

over frequency, temperature, and unit variations (max = 24 dBm, min =

–50 dBm), the IF AGC IC has an 85 dB AGC range, and the RF AT–118

attenuator has about 14 dB.

System Module

CDMA TX output power is controlled by the TX_IF_AGC (CDRFI, N703,

pin 5) in the baseband whose DC value can range anywhere from 0 to 3.1

V when measured on the signal TX_IF_AGC. This voltage range is then

divided and shifted down in slope to provide two DC control signals which

vary the gain of the IF AGC IC and the AT–118 variable attenuator. The

chart below shows the typical limits and the resulting attenuation of each

stage. As described in the table below, the IF AGC IC (N308) and the

AT–118 (N300) both provide two linear amplification/attenuation vs. control

signal characteristics which are simply added together to achieve the

entire dynamic range required for the transmitter.

ÁÁÁÁ

ÁÁÁÁ

Control Voltage

ÁÁÁÁ

Dynamic Range

IF AGC IC (N308)

ББББББ

ББББББ

0 to 2 V

ББББББ

85 dB

AT–118 (N300)

ББББББ

ББББББ

0 to 2 V

ББББББ

14 dB

Overall

ÁÁÁ

Range

(TX_IF_AGC

ÁÁÁ

PDM)

0 to 3.1 VDC

ÁÁÁ

(Avg.)

99 dB

The output power of the CDMA TX is determined by the CDSB ASIC

(D705). This value is a function of the received signal strength, a tuned

reference value (CloopRef) , and information provide by the CDMA

network the phone is operating within. These factors sum together to

equate to a digital value stored in a register called the TxCtr. This value is

multiplied by a slope correction value called the TX_SLOPE. The result of

this multiplication is stored in a register called the TxDAC. The TxDAC

value, still a digital word, goes through a digital to analog conversion by

the CDRFI IC (N703) to produce the TX_IF_AGC voltage.

Issue 1 04/99

Page 4–25

Page 26

NHP–4

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

System Module

The TX_IF_AGC voltage is then fed into an op–amp level shifter circuit

(N302) which outputs the two DC level–shifted output signals which

control the IF AGC IC (N308) and the RF AGC AT–118 attenuator (N300)

from 0 to 2 V, approx. The TX_AGC_ADJ signal from the CDSB ASIC

(N705, Pin 115) is simply used to provide a DC voltage level from which to

adjust the slope of the RF AGC attenuator (N300) over the voltage range

of the TX_IF_AGC input. The following chart shows typical DC control

voltage levels at each AGC stage for given CDMA RF signal output

powers.

PAMS

Technical Documentation

CDMA TX

Output RF

ÁÁÁ

Signal Level

ÁÁÁ

(dBm)

AGC_REF PDM

БББББ

БББББ

23

15

10

–5

–20

–35

The Service Software provides a manual control mechanism which

provides the ability to test this transmitter control functionality. This

mechanism is called CDMA TX Manual Gain Control and is discussed in

the Troubleshooting section of this manual.

Temperature Compensation

A thermistor (R307) is mounted directly on the opposite side of the board

from the RI21007 PA (N304). The thermistor measures the temperature

of that area of the board and sends the information to the microprocessor

via the RFTEMP1 line. The microprocessor compensates for changes in

the transmitters output power by adjusting the TXI_REF PDM. The output

power variation is due to temperature variations of the PA bias current,

detector voltage and the gains of the RF driver transistors (V303, V305).

(decimal

value)

–

300–350

350–400

450–500

600–650

750–800

TX_IF_AGC

Voltage

БББББ

Level (N703,

БББББ

Pin 5)

–

1.1

1.2

1.4

1.6

2.0

IF AGC IC Con-

trol

ÁÁÁÁ

Voltage (N308,

ÁÁÁÁ

Pin 16)

–

1.7

1.6

1.4

1.0

0.6

RF ATTN Con-

БББББ

БББББ

trol

Voltage (at

C109)

–

1.6V

1.3V

0.9V

0.3V

0.8mV

Page 4–26

Issue 1 04/99

Page 27

PAMS

NHP–4

Technical Documentation

Circuit Description

IQ Modulator (N307)

The I/Q inputs from the baseband contain spread spectrum data with a

frequency range of 0 to 615 kHz. These inputs to the modulator are

differential (positive and negative inputs), driven from the baseband by the

CDRFI (N703). Beginning at the transmitter schematic page, these

inputs, labeled TXI+/– and TXQ+/–, are matched to the modulator input

load requirements for pins 1–4 of the RF2703 I/Q modulator IC (N307).

Once fed into the IQ modulator, each signal stream (I and Q) is then

frequency converted up to the intermediate frequency of 208.1 MHz, and

output on pins 6 and 7. This is accomplished by using the LO_TIF signal

from the synthesizer section at 416.2 MHz, where the modulator IC

(N307) internally divides the frequency by 2 to the resulting 208.1 MHz,

and modulates the signal with the I and Q baseband signals streams.

Additionally, the IC internally sets the Q output signal phase shifted 90

with respect to the I signal. The resulting signal is the Offset Quadrature

Phase Shift Keyed (OQPSK) modulated IF signal.

System Module

The LO input of 416.2 MHz is provided at an input power range of approx.

–30 dBm to –20 dBm which provides a required 0.06 Vpp signal into the

modulator LO input impedance (N307, pin 13) of 500 Ohms. If the input

power of the LO from the synthesizer section is too low, then the resulting

output signals from I and Q (pins 6 and 7) will not be present at 208.1

MHz. Also, if the LO signal is not locked to 416.2 MHz, the output signals

from I and Q will appear to be ‘jumping’ around in frequency and/or slowly

drifting from the fixed IF of 208.1 MHz. If the input power of the LO is too

high, then carrier leakage may occur onto the modulated signal, causing a

peak to appear in the middle of the modulated 1.25 MHz bandwidth signal.

After the upconversion and combining, the output IF signal is sent to the

IF AGC IC to perform the required gain control before filtering.

TX AGC Level Shifter (N302)

The op–amp circuit containing the AGC level shifting provides the two

AGC control outputs (0 to 2 V each) derived from the one linear AGC

control voltage input signal, TX_IF_AGC from the CDRFI (N703). By

changing the op–amp level shifting, biased by V4.8TX (N305), the

TX_IF_AGC ranges from 0 to 3.1, thus shifting both control voltages into

the IF AGC IC (N308) for a range of 0 to 2.6 V, and the RF AGC variable

attenuator (V106) to a voltage range of 0 to 2 V. The additional DC

voltage level, TX_AGC_ADJ is simply set to a constant value by the ASIC,

however, it is used during alignment and testing for a preliminary test of

the functionality of the gain in the TX Chain.

Issue 1 04/99

Page 4–27

Page 28

NHP–4

System Module

IF AGC IC (N308)

The CDMA Automatic Gain Control Transmitter IC, or Q5505 (N308),

provides the gain control at the IF frequency, 208.1 MHz. The range of

gain is typically +39 dB to –65 dB which varies from unit to unit for a more

reasonable 85 dB total of dynamic range. The typical input signal

amplitude of –40 dBm is present at Pin 1 (CDMA+) input from the output

of the I/Q modulator. The complementary CDMA input (Pin 2) is simply

AC grounded since the input signal is not designed for differential inputs.

The RF gain is controlled by the DC value of the AGC shifted input at Pin

16, Vcontrol. As described in

typically 0 to 2.6 V, resulting in signal gain of approx. –65 dB to 39 dB.

The VCC (pins 13, 14, 15) for this IC is taken from V3.6TX (N306) and is

filtered by the ferrite bead, L300.

The differential outputs (Pins 9, 10) are matched from the load impedance

of 1 kOhm (R317) to the 50 Ohm input impedance of the next stage, a 2

dB 50 Ohm resistive attenuator (T–Pad, R318, R319, R320), by the T300

RF broadband balun filter. The broadband Balun filters the broadband

noise (DC to 128 MHz) so that it will not desense the receiver through the

rest of the gain of the TX chain. The circuit is also transformed from one

impedance to another, and from differential outputs to single–ended

output without losing any signal energy. The output of the 50 Ohm T–Pad

is then impedance matched through L301 and R322 and fed into the RF

mixer/upconverter IC (N301).

PAMS

Technical Documentation

TX AGC Level Shifter this signal ranges from

MRFIC1813R2 RF Upconverter IC (N301)

The RF upconverter IC (N301) simply subtracts the incoming fixed IF

frequency signal at 208.1 MHz from the LO_PTX UHF synthesized signal

at 2.0581 GHz to 2.1181 GHz to create the channel selected signal output

in 50 kHz steps at a final TX frequency output range of 1850 MHz to 1910

MHz. The input signal, at Pin 14, is mixed with the synthesizer LO signal

(Pin 5), and output to the final RF output signal (Pin 7). The critical mixing

design function at this stage not only creates the final output frequency,

but also every integer combination frequency from the IF and LO signal

inputs (including the LO feedthru itself). Thus, filtering the output of this

signal is required within the TX Band (1850 MHz to 1910 MHz) to prevent

any spurious output signals which are not allowed to be transmitted by the

product. The RF Upconverter IC will also provide typically 15 dB of signal

gain (termed ‘conversion gain’) for the final output signal as well.

The channel selection is controlled by the incoming LO signal, and is

programmed into the synthesizer by the baseband section. If the LO

signal appears to be off–frequency, drifting, or unlocked, refer to the

Synthesizer Troubleshooting Guide. The input power requirements are

approx. –15 dBm (50 Ohm reference) from the synthesizer section. Any

lower power level may cause the upconverter gain to decrease, and/or the

mixer not to be functional (no proper output frequency signal).

Page 4–28

Issue 1 04/99

Page 29

PAMS

NHP–4

Technical Documentation

The power supply of the IC (VDD, Pins 1, 8 and 12) is also filtered to

prevent any conducted spurious AC signals. This filtering is accomplished

by using ‘microstrip’ filters (Z135, Z136) printed on the circuit board, in

combination with all other AC bypass capacitors. The power supply for

this IC is provided by the V4.8TX (N305), which also helps isolate (filter)

the power supply signal from AC spurs.

Finally, the desired output (Pin 7) is impedance matched by an output

capacitor (C327) and another 1 dB resistive 50 Ohm RF attenuator

(T–pad, R314, R315, R316) and fed into the RF Saw Filter (Z302).

RF Filter (Z302)

This RF filter provides rejection in the RX band (1930 to 1990 MHz) to

attenuate any spurs present after the Upconverter IC (N301). Additionally,

harmonics and other spurious responses outside of the 60 MHz TX

Passband are attenuated. The insertion loss of this device in the TX band

is typically 3.7 dB.

System Module

AT–118 Variable Attenuator (V106)

The AT–118 (N300) is an attenuation stage in the RF path immediately

following the RF filter (Z302). Its purpose is to provide the remaining 14

dB of AGC required in the TX chain, and it helps suppress noise created

by the RF Upconverter IC. The RF AGC functionality is discussed in the

CDMA TX Gain Control section. The VC voltage to pin 5 of this device sets

the level of attenuation, and is typically varied from 0 to 2 V provided by

the TX AGC Level Shifter (Sec. ) over the entire AGC range (0 to 14 dB)

driven by the op–amp level shifter (N302). The IC is biased by Pin 3 , VS,

driven by the V3.6TX (N306) regulator.

The attenuator is followed by another 1 dB resistive T–pad (R311, R350,

R351), and then fed into the driver amplifiers.

1st and 2nd PA Driver Stages (V303, V305)

The first gain stage (V305) is a BJT amplifier in the common emitter

configuration. This stage typically provides 11dB of gain. The second

gain stage (V303) has the same configuration and typically provides 11dB

of gain. Both are actively biased using current driver circuits, V309 and

V308, which are switched on and off by the TX_GATE control signal

during pulsed operation. Overall, the bias current is provided by the

V4.8TX (N305) regulator, and is mostly controlled by the collector bias

resistor for each amplifier.

The first gain stage, V305, should be biased with approximately 4.2 V on

the collector and 0.7 V on the base. V309 dual PNP transistor circuit acts

as a switch, sourcing constant current to V305 when the TX_GATE

voltage goes high. Both transistors should have 4.2 V on each collector

(Pins 3, 6) when they are switched on. Also, both transistors use

microstrip inductors (Z705, Z129) on the collectors to help provide an RF

frequency choke, and to help match the output impedance.

Issue 1 04/99

Page 4–29

Page 30

NHP–4

System Module

The second gain stage, V303, should be biased the same with

approximately 4.2 V on the collector and 0.7 V on the base. The current

bias circuit of V308 acts the same as the circuit of V309 for the first stage,

except that the bias current is increased slightly by R344 to provide better

linearity performance due to the higher RF input power to the amplifier.

The first stage (V305) includes a two–element input matching circuit

consisting of a microstrip inductive element (Z704) printed on the circuit

board and a series input capacitor (C312). The second stage (V303)

simply uses one shunt input capacitor (C308).

RF Filter (Z301)

This RF filter is the same as that described in RF Filter (Z302) and helps

provide more attenuation of the out–of–band frequency components still

present in the signal before it is amplified by the PA (N304).

The output of the RF filter is fed into a 50 Ohm characteristic impedance

microstrip line (Z146) to keep a matched termination into the PA (N304).

PAMS

Technical Documentation

RI21007 Power Amplifier (N304)

The RI21007 (N304) Power Amplifier (PA) typically provides 25 dB of gain

and up to 30dBm output power. The most important aspect of the power

supply voltage is that a clean, stable supply voltage is supplied to the IC

so that the PA will not oscillate. As can be seen from the TX schematic

page, numerous bypass capacitors and RF chokes (inductors) of both

microstrip and ferrite beads are used in the PA’s bias circuitry, all from the

DC output of the voltage regulator transistor (V300) to the PA IC (N304).

These include the microstrip elements Z147, Z148, and Z152 and all of

the bypass capacitors to ground on Pins 1, 4, 5, 7, 9, 10, 14, and 16.

Inside the PA IC, the bias current drawn from VBAT is increased directly

with increasing output power to ensure linear performance. Thus, as the

TX gain is increased, the current will increase as well, causing the PA to

generate much more heat. The board will typically get extremely hot, to

the point of suffering possible permanent damage, if the board is left in an

offline high output power state for long periods of time. The VCC bias

voltage remains constant at 6.2 V, set by the voltage regulator circuit

(V300) described below.

The PA is switched on and off by the TX_GATE voltage FET driver switch

(V302) which will toggle Vref (Pins 10, 14). When Vref is low, the PA IC

wio;ll shutdown into standby mode, while the chip is still biased by VCC.

The PA output should NEVER be probed without using the proper

high–power attenuator tips provided with each passive/active probe

used. This can damage the probe.

Page 4–30

Issue 1 04/99

Page 31

PAMS

NHP–4

Technical Documentation

PA Bias Circuitry (V300)

The PA is provided with a constant voltage source at 6.2 V using the

FZT749 PNP power transistor (V300). This circuit is devised to provide a

constant base bias current, since the collector is set to a constant voltage

from the V301 current bias circuit. This circuit is enabled by the V4.8TX

(N305) regulator, where the base voltages of both NPN transistors (V301)

is set to approx. 2.3 V. This sets the emitter voltages to 2.3 – 0.7 = 1.6 V,

which in turn provides the bias current on the emitter resistors for both

transistors (V301). The voltage limiter circuit comprising of V300 and V301

serves to limit the supply voltage into the PA(N304) to 6.2 V.

Additionally, the large capacitor C300 is provided to keep the voltage bias

circuitry from becoming unstable and oscillating as the PA is burst on and

off by the TX_GATE control voltage. At worst case, the maximum battery

voltage occurs as the PA is at maximum gain, thus the power transistor,

V300, will dissipate quite a lot of power from the voltage drop and high

current. Depending on the battery capacity, however, the battery voltage

will typically drop as the PA current is increased. The power transistor and

the PA (N304) are mounted directly above/below each other to heat sink

on the PC board together to decrease the junction temperatures of each

device.

System Module

Detector (V114)

The PA’s RF output power is sampled by a capacitively coupled schottky

diode detector. The detector produces a DC voltage that is proportional to

the PA’s RF output power. The DC output voltage decreases as RF power

increases. The typical detector voltage will vary from 0 to 2.5 V, however

its maximum is set during the tuning and alignment process since it is

used to determine the TX limiting value.

Note it is unwise to probe the detector @ C343 to read the detector output signal. Doing so will load it down, providing inaccurate readings. It is better to probe at the input of

the op–amp comparator, pin 3. If the phone has passed alignment and test, the detector

voltage will not be any higher than the TX_LIM_ADJ average (DC) voltage, since this will

cause the TX_LIM signal to toggle high to control the TX AGC.

Isolator (Z300)

The Isolator isolates the PA from the Duplexor. The isolator provides a

stable 50 ohm load for the PA by absorbing any reflected power from the

Duplexor.

Duplexor (Z102)

The Duplexor isolates the transmit signal from the receiver path and

permits the phone to transmit and receive signals simultaneously (i.e. Full

Duplex operation). The Duplexor is a three terminal, dual frequency (RX

and TX) bandpass splitter/filter and provides the common antenna

connection to the TX and RX circuits. The transmit signal enters the

Duplexor at the “TX” port and exits from the “ANT” port. The Duplexor is

the largest device on the PCB and can be found on the RX schematic.

The TX Chain should not be troubleshot without a proper load on the

duplexor. Otherwise, false RF gain and/or power levels may be present.

Issue 1 04/99

Page 4–31

Page 32

NHP–4

System Module

Thermistor (R307)

The thermistor R141 changes resistance as a function of its temperature.

The voltage across this device comprises the RFTEMP1 signal to the

MCU (D700). It is placed near the power transistor (V300) and the power

amplifier (N304) for worst–case board temperature measurements.

PAMS

Technical Documentation

Page 4–32

Issue 1 04/99

Page 33

PAMS

NHP–4

Technical Documentation

Receiver

Functional Description

The 2170 uses a single–mode CDMA receiver, which will downconvert a

1.23 MHz wide signal down to the baseband modulated signal, 615 kHz in

bandwidth. The receiver uses a heterodyne deisgn technique where the

incoming signal is down converted from the PCS RX Band, 1930 MHz to

1990 MHz, to a fixed IF frequency at 128.1 MHz, filtered, then down

converted to it’s quadrature components at baseband. After filtering, the

baseband modulated I and Q signal components are then digitally

processed to recover the original data. The receiver output is 2 data

signals, I and Q, each 615 kHz wide, which are sent to the baseband

section.

The receiver contains Automatic Gain Control (AGC) circuitry which allows

the I and Q output signals to remain at the same levels, given a range of

input signal power at the antenna port from –25 dBm to –104 dBm. The

entire receiver is enabled by a logic high (+3.1 V) on the SYN_PWR_ON

signal from the baseband ASIC. The receiver power supply is provided by

2 main regulators on the power schematic page, V4.8RX (N1) and

V3.6RX (N5). After the synthesizer Local Oscillators settle to the right

frequency, the receiver will provide filtered I and Q output signals.

System Module

Antenna and Test Jig

The receiver chain begins at the antenna. The antenna is impedance

matched with 2 microstrip components, Z701 and Z506, printed on the

PCB, and 2 surface–mount components, L1 and C1. Since there is no RF

connector provided with the 2170 design, the unit must be placed in a

specified test jig for debugging. Without the ability to input a proper power

level RF signal with the test gig, little can be done to troubleshoot the

receiver. The test jig will bypass the antenna and inject an RF signal

directly into a matched impedance at the duplexor.

Duplexor (Z2)

The Duplexor, Z2 is a 3–port device (antenna, RX, and TX) which serves

to isolate the transmit signal from the receiver path, and vice versa. The

received signal proceeds from the antenna port through to the RX port

with minimum insertion loss (max. 4.3 dB). For the RX signal, the

duplexor will attenuate any interfering signals from outside the receive

band (1930–1990 MHz), and most importantly, it attenuates the

simultaneous transmit signal output from the PA (N304). The filtered

signal then proceeds through C11 into the RX Low–Noise Amplifier (LNA,

V1).

Issue 1 04/99

Page 4–33

Page 34

NHP–4

System Module

1st LNA (V1) and Active Bias (V3)

The first LNA, V1, provides approximately 14 dB of gain to the RX chain.

The current source to this device originates from the active bias circuitry

consisting two transistors (V3) providing constant current to V1. The

collector current to V1 is mainly controlled by R3 and R15, whereas the

base current is controlled by R7. Additionally, R12, and R13 set up the

voltage dividing ratio for the voltage bias for V3. The RF gain is provided

by the V1 transistor, where input and output matching component values

(such as L2, L6, and C7) are also critical to this device so that proper gain

is achieved without adding thermal noise to the signal. This section is one

of the most critical in the RX chain, since it dominates the receiver noise

figure. This stage amplify the RX–signal before the first RF SAW filter in

order to achieve an acceptable NF. If the LNA is malfunctioning, it is

probably due to a bad component which will be determined in the DC

Voltage Check section. The supply voltage for the LNA active bias circuit

is the V4.8RX signal provided by the N1 regulator, when ‘SYN_PWR_ON’

is high (3.1 V).

PAMS

Technical Documentation

RX SAW Filters (Z1, Z706) and 2nd LNA (N2)

The RX SAW Filters (Z1, Z706) and the 2nd LNA provide a clean desired

RX signal within the passband (from 1930 to 1990 MHz) to the input of the

mixer. The RX SAW Filters are provided on either side of the 2nd LNA

stage to further attenuate signals outside of the RX passband, especially

the TX–signal and the image. Both SAW Filters have a maximum

insertion loss of 5 dB, and will reject signals in the transmit band

(1850–1910 MHz) by at least 15 dB, and image frequency band

(2186–2246 MHz) by approx. 28 dB.

The 2nd LNA (N2) provides another 10 dB of gain to help overcome the

loss from the SAW filters. This LNA uses the V4.8RX power supply on Pin

7. Additionally, power supply filtering is accomplished by L4, C16, C18,

and C19. The LNA IC is impedance matched to 50 Ohms, thus no

matching components are necessary between the SAW filters.

Mixer (N6)

The mixer is a three port GaAs passive device. Of the five pins, two are

grounded. The remaining three constitute the RF, LO and IF ports. The

received signal (1930–1990 MHz) enters the mixer at pin 1, the RF port.

The received signal strength may be as low as –90 dBm, after

amplification. The LO_PRX signal is a high–side injection from the

synthesizer, at 2058.1 MHz to 2118.1 MHz. This LO signal is provided in

50 kHz steps to select the proper incoming channel frequency, producing

a conversion to the fixed IF frequency of 128.1 MHz (i.e. 2058.1 MHz

minus 1930 MHz = 128.1 MHz).

Page 4–34

Issue 1 04/99

Page 35

PAMS

Á

Á

Á

NHP–4

Technical Documentation

The LO_PRX signal originates from the UHF synthesizer and enters the

mixer at pin 3, the RF port, through a 3 component matching network (R8,

L5, C20). The LO_PRX signal is strong, minimum +4 dBm, and should be

present and locked shortly after the ‘SYN_PWR_ON’ signal is turned on.

If the locked signal is not present, then it is required to debug the

synthesizer. It should always be 128.1 MHz greater in frequency than the

received signal. These two incoming signals mix within the device and

produce the 128.1 MHz IF signal at the IF port, pin 2.

The mixer will produce every integer combination of the two incoming

frequencies at the RF and LO ports which require filtering at the desired IF

frequency of 128.1 MHz, accomplished by Z103. The insertion loss at the

mixer is approx. 8 dB.

IF AMP (V4) and IF SAW (Z103)

The IF Amplifier (V4) is configured much the same way as the 1st LNA

(V1). It is provided a constant current bias from V5, where the collector

current for V1 is mainly controlled by R24, R25, and R26, and the base

current is controlled by R14. Additionally, the voltage ratios for biasing the

constant current circuit (V5) are set by R16 and R27. The overall power

supply is provided by V4.8RX (from N1 regulator) as well. The input and

output impedance matching is provided by L14, C61, L9, and C33. The IF

Amp (V4) provides 15 dB of signal gain at 128.1 MHz. The resulting

output signal is sent to the IF SAW filter (Z103).

System Module

The IF SAW filter (Z103) is required to tightly filter out all of the remaining

frequency components outside the actual signal bandwidth (1.23 MHz) at

the fixed IF frequency (128.1 MHz). This prevents the receiver from

demodulating interference from adjacent channel signals which may be

much stronger than the desired channel signal. The filter input is

connected single ended and the output is differential coupled to the AGC

Amp. The input impedance is matched to the previous stage by L34, and

C59. The differential outputs from the SAW are used from Pins 5 and 6,

and the output is matched by components L10 and L7. The insertion loss

of the IF filter is approx. 13 dB. This is the final stage of filtering before

the desired signal is converted down to baseband. The output signals are

sent to the AGC IC (N9) for gain control.

AGC IC (N9)

The AGC IC (N9) will provide a constant signal level to the quadrature

demodulator (N8) given an entire range of input signal amplitudes from

the output of the IF SAW. The AGC IC will provide up to 90 dB of dynamic

range, from –45 dB of attenuation, to +45 dB of gain. The gain is

controlled by a DC voltage on Pin 16 (Vcontrol) which will range from 0.1

to 3.0 V. A level shifter/inverter circuit (N7) is provided to convert the DC

voltage signal on RX_IF_AGC from the voltage range of 2.5 V to 0.5 V as

described in the table below.

RX_IF_AGC DC V oltage

БББББББ

Issue 1 04/99

2.5 V

0.5 V

Vcontrol DC Voltage

ББББББББ

(N9, Pin 16)

0.1 V

3.0 V

RF Gain at 128.1 MHz

БББББББ

(N9)

–45 dB

+45 dB

Page 4–35

Page 36

NHP–4

System Module

The baseband section uses DSP to determine the amplitude of the

incoming I and Q baseband signals. The baseband then controls the

RX_IF_AGC voltage to produce the equivalent of –13 dBm (into 50 ohms)

at the RX_I and RX_Q signal outputs of the BBFIL (N10). Unlike

conventional RF power detection methods, the RSSI (Receive Signal

Strength Indicator) is then calculated using DSP from the resulting

RX_IF_AGC voltage and the RX_I and RX_Q signal levels.

The output of the AGC Amp is 2 open collectors. The supply voltage to

drive the output is connected through L12 and L13. An attenuator is

placed after the AGC Amp. (R29, R30 and R31). Additionally, the power

supply for the AGC IC (Pins 13, 14, 15) and output signal bias (Pins 9 and

10) are filtered by the ferrite bead, L11, and bypass capacitors, C39, C42,

and C41. The IC is supplied by the V3.6RX supply (N5). After the signal

level is adjusted, the constant amplitude RF signals at 128.1 MHz are then

passed to the I/Q demodulator.

Quadrature Demodulator (N8)

PAMS

Technical Documentation

The purpose of N8 is two–fold. The first is to convert the incoming RF

signal (128.1 MHz, 1.23 MHz bandwidth) down to baseband (DC to 615

kHz) by mixing with a LO signal from the synthesizer. The second is to

split the incoming signal into the quadrature components, each 90

degrees out–of–phase, thus performing the first step in demodulating the

incoming CDMA signal.

The LO_RIF signal provided by the synthesizer to Pin 13 is at 256.2 MHz,

and is divided down internally by the IC to 128.1 MHz, which then mixes

directly with the input signal to 0 Hz. However, since the carrier is

suppressed in the CDMA signal, the resulting I and Q single–ended (with

respect to ground) output signals are DC blocked by C51 and C52 from

the next stage, the BBFIL (N10). C47 provides an AC bypass for the

power supply at Pin 14, supplied by the V3.6RX regulator (N5). The

Quadrature demodulator provides typ. 23 dB of signal gain, but cannot

easily be measured due to the conversion of frequency.

Additionally, if the LO_RIF signal is unlocked or not present at 256.2 MHz,

then the receiver will fail tests, and troubleshooting is required in the

synthesizer.

BBFILCT (N10)

Page 4–36

The BBFILCT IC (N10) serves to filter and amplify the demodulated

baseband I & Q signals before delivering them to the CDRFI IC (N703) for

A/D conversion. The gain of this stage is 31 dB. The I & Q signals enter

this IC at pins 20 and 13 via C52 and C51 respectively. This IC is

calibrated dynamically to overcome variations due to temperature

changes. During normal operation, pin 3 of N10 will be pulsed about

every 10 seconds by the RX_FIL_CAL_3V signal. The BBFILCT DC

supply should be approximately 3.1 V at Pins 4, 8, and 15. The BBFIL is

turned on by the BBFIL_CNTRL signal baseband CDSB ASIC (D705)

which is controlled by the software timing in the ASIC.

Issue 1 04/99

Page 37

PAMS

NHP–4

Technical Documentation