MXIC MX23C8000MC-10, MX23C8000TC-12, MX23C8000TC-10, MX23C8000QC-20, MX23C8000QC-12 Datasheet

...

FEA TURES

MX23C8000

8M-BIT [1M x 8] CMOS MASK ROM

• 1M x 8 organization

• Single +5V power supply

• Fast access time : 100/120/150/200ns

• Totally static operation

• Completely TTL compatib le

GENERAL DESCRIPTION

The MX23C8000 is a 5V only, 8M-bit, Read Only

Memory. It is organized as 1M words by 8 bits, operates from a single +5V supply , has a static standby mode,

and has an access time of 100/120/150/200ns. It is

designed to be compatible with all microprocessors and

similar applications in which high performance, large bit

storage and simple interfacing are important design considerations.

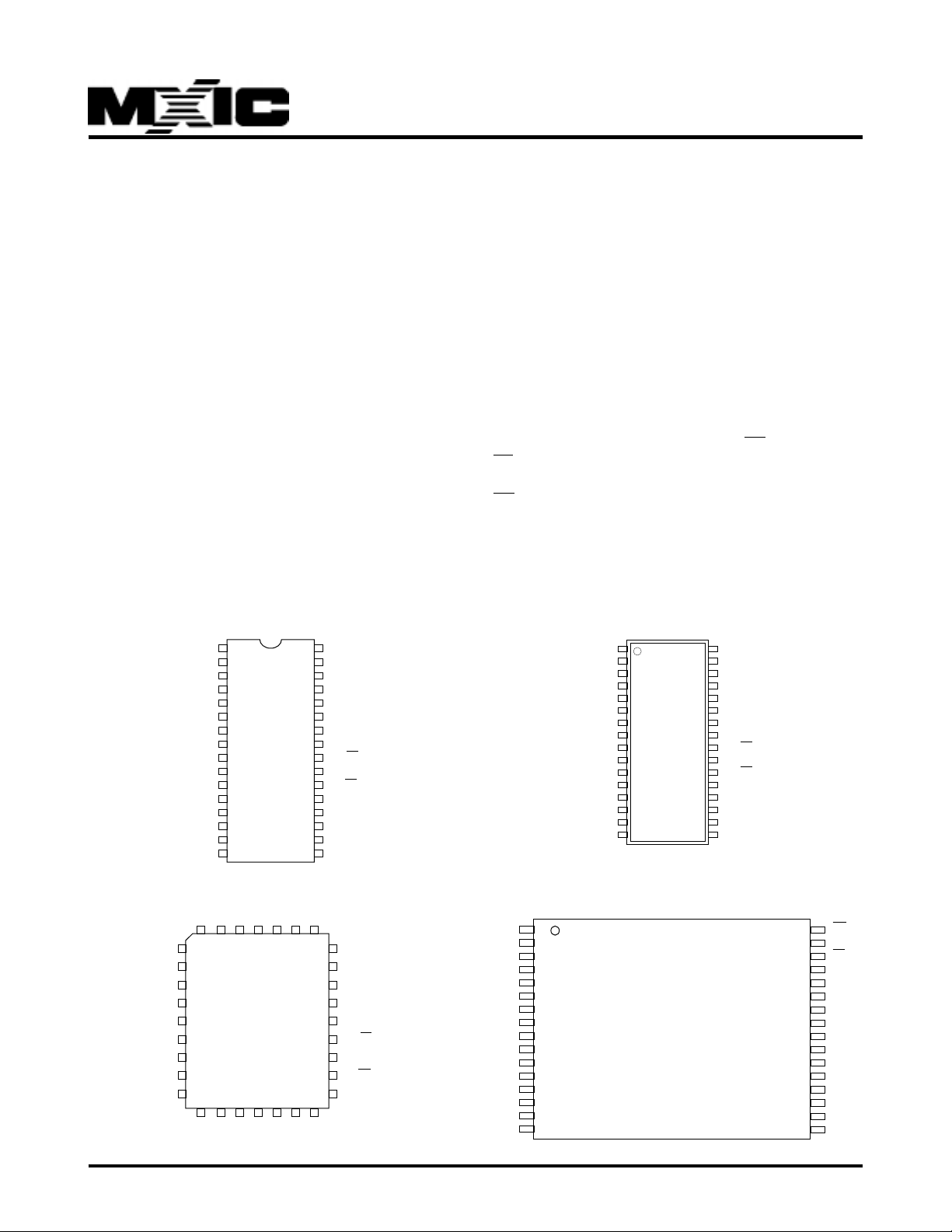

PIN CONFIGURATION

32 PDIP

A19

A16

A15

A12

VSS

A7

A6

A5

A4

A3

A2

A1

A0

Q0

Q1

Q2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

MX23C8000

VCC

32

A18

31

A17

30

A14

29

A13

28

A8

27

A9

26

A11

25

OE/OE

24

A10

23

CE/CE

22

Q7

21

Q6

20

Q5

19

Q4

18

Q3

17

• Operating current : 40mA

• Standby current : 100uA

• Package

- 32 pin plastic DIP

- 32 pin plastic SOP

- 32 pin plastic PLCC

- 32 pin plastic TSOP

MX23C8000 offers automatic pow er-down, with powerdown controlled by the chip enable (CE) input. When

CE goes high, the device automatically powers down

and remains in a low-power standby modes as long as

CE remains high.

MX23C8000 pin 24 may also be programmed either active HIGH or LOW in order to eliminate bus contention

in multiple-bus microprocessor systems.

32 SOP

A19

A16

A15

A12

VSS

A7

A6

A5

A4

A3

A2

A1

A0

Q0

Q1

Q2

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

MX23C8000

22

21

10

19

18

17

VCC

A18

A17

A14

A13

A8

A9

A11

OE/OE

A10

CE/CE

Q7

Q6

Q5

Q4

Q3

32 PLCC 32 TSOP

A12

A15

A16

A19

VCC

A18

4

5

A7

A6

A5

A4

9

A3

A2

A1

A0

DQ

MX23C8000

13

14 17 20

Q1

Q2

1

Q3Q4Q5

VSS

A17

32

30

A14

29

A13

A8

A9

A11

25

OE/OE

A10

CE/CE

Q7

21

Q6

VCC

A11

A13

A14

A17

A18

A19

A16

A15

A12

1

2

A9

3

A8

4

5

6

7

8

9

10

11

12

13

A7

14

A6

15

A5

16

A4

MX23C8000

P/N:PM0137 REV. 3.8, JUL. 16, 2001

1

32

OE/OE

31

A10

30

CE/CE

29

Q7

28

Q6

27

Q5

26

Q4

25

Q3

24

VSS

23

Q2

22

Q1

21

Q0

20

A0

19

A1

18

A2

17

A3

MX23C8000

PIN DESCRIPTION

Symbol Pin Function

A0~A19 Address Inputs

Q0~Q7 Data Outputs

CE/CE Chip Enable Input

OE/OE Output Enable Input

VCC Po wer Supply Pin (+5V)

VSS Ground Pin

ABSOLUTE MAXIMUM RATINGS*

RATING VALUE

Ambient Operating Temperature 0°C to 70°C

Storage T emperature -65°C to 125°C

Applied Input Voltage -0.5V to VCC+0.5

Applied Output Voltage -0.5V to VCC+0.5

VCC to Ground Potential -0.5V to 7.0V

Power Dissipation 1.0W

BLOCK DIAGRAM

CE/CE

OE/OE

A0~A19

ADDRESS

INPUTS

VCC

VSS

*Note:

Stress greater than those listed under ABSOLUTE MAXIMUM

RA TINGS ma y cause permanent damage to the device. This

is a stress rating only and functional operation of the device

at these or any other conditions above those indicated in the

operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended

period may affect reliability.

.

.

.

.

.

.

.

.

CONTROL

LOGIC

Y-DECODER

X-DECODER

.

.

.

.

.

.

.

.

OUTPUT

BUFFERS

Y-SELECT

8M BIT

ROM ARRAY

Q0~Q7

DC CHARACTERISTICS (Ta = 0°C ~ 70°C, VCC = 5.0V ± 10%)

Item Symbol MIN. MAX. Conditions

Output High Voltage VOH 2.4V - IOH = -1.0mA

Output Low Voltage VOL - 0.4V IOL = 2.1mA

Input High Voltage VIH 2.2V VCC+0.3V

Input Low Voltage VIL -0.3V 0.8V

Input Leakage Current ILI - 10uA VIN=0 to 5.5V

Output Leakage Current ILO - 10uA VOUT=0 to 5.5V

Power-Do wn Supply Current ICC3 - 100uA CE>VCC-0.2V

Standby Supply Current ICC2 - 1.0mA CE=VIH

Operating Supply Current ICC1 - 40mA Note 1

CAPACITANCE (Ta = 25°C, f=1.0MHz (Note 2))

Item Symbol MIN. MAX. UNIT Conditions

Input Capacitance CIN - 10 pF VIN=0V

Output Capacitance COUT - 10 pF VOUT=0V

P/N:PM0137

REV. 3.8, JUL. 16, 2001

2

MX23C8000

AC CHARACTERISTICS (Ta = -10°C ~ 70°C , VCC = 5.0V ± 10%)

23C8000-10 23C8000-12 23C8000-15 23C8000-20

PARAMETER SYMBOL MIN. MAX. MIN. MAX. MIN. MAX. MIN. MAX. CONDITIONS

Cycle Time tCYC 100ns - 120ns - 150ns - 200ns Address Access Time tAA - 100ns - 120ns - 150ns - 200ns

Output Hold Time After tOH 0ns - 0ns - 0ns - 0ns Address Change

Chip Enable Access Time tACE - 100ns - 120ns - 150ns - 200ns

Output Enable/Chip Select tAOE - 80ns - 80ns - 80ns - 100ns

Access Time

Output Low Z Delay tLZ 0ns - 0ns - 0ns - 0ns - Note 3

Output High Z Delay tHZ 20ns - 20ns - 20ns - 20ns Note 4

Note:

1. Measured with device selected at f=5MHz and output unloaded.

2. This parameter is periodically sampled and is not 100% teseted.

3. Output low-impedance delay (tLA) is measured from CE going low.

4. Output high-impedance delay (tHZ) is measured from CE going high.

AC T est Conditions

Input Pulse Levels 0.4V~2.4V

Input Rise and Fall Times 10ns

Input Timing Level 1.5V

Output Timing Le v el 0.8V and 2.0V

Output Load See Figure

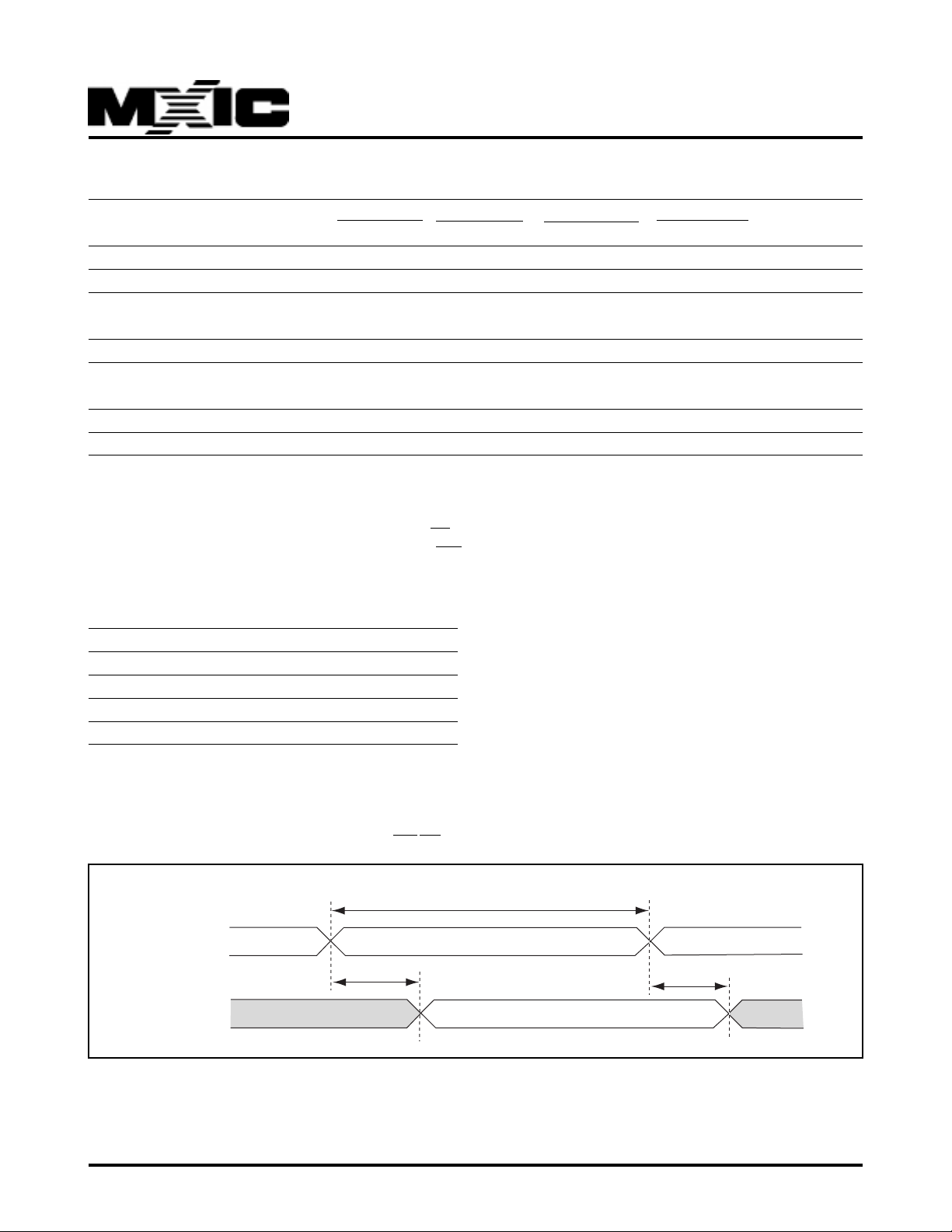

TIMING DIAGRAM

PROPAGA TION DELAY FROM ADDRESS (CE/OE=ACTIVE)

tCYC

ADDRESS

INPUTS

tAA

DATA OUT

VALID ADDRESS

tOH

VALID DATA

P/N:PM0137

REV. 3.8, JUL. 16, 2001

3

Loading...

Loading...