Page 1

®

Power for the Digital Revolution

®

.

AVR135

AVR135BK

AUDIO/VIDEO RECEIVER

SERVICE MANUAL

230V international version

Page 2

AVR 135 TECHNICAL SPECIFICATIONS

Audio Section

Stereo Mode

Continuous Average Power (FTC)

50 Watts per channel, 20Hz–20kHz,

@ <0.07% THD, both channels driven into 8 ohms

Six-Channel Surround Modes

Power per Individual Channel

Front L&R channels:

40 Watts per channel

@ <0.07% THD, 20Hz–20kHz into 8 ohms

Center channel:

40 Watts @ <0.07% THD, 20Hz–20kHz into 8 ohms

Surround (L & R Side, Back) channels:

40 Watts per channel

@ <0.07% THD, 20Hz–20kHz into 8 ohms

Input Sensitivity/Impedance

Linear (High-Level) 200mV/47k ohms

Signal-to-Noise Ratio (IHF-A) 100dB

Surround System Adjacent Channel Separation

Pro Logic I/II 40dB

Dolby Digital (AC-3) 55dB

DTS 55dB

Frequency Response

@ 1W (+0dB, –3dB) 10Hz –130kHz

High Instantaneous

Current Capability (HCC) ±25 Amps

Transient Intermodulation

Distortion (TIM) Unmeasurable

Slew Rate 40V/μsec

FM Tuner Section

Frequency Range 87.5–108.0MHz

Usable Sensitivity IHF 1.3μV/13.2dBf

Signal-to-Noise Ratio Mono/Stereo 70/68dB

Distortion Mono/Stereo 0.2/0.3%

Stereo Separation 40dB @ 1kHz

Selectivity ±400kHz, 70dB

Image Rejection 80dB

IF Rejection 90dB

AM Tuner Section

Frequency Range 520–1720kHz

Signal-to-Noise Ratio 45dB

Usable Sensitivity Loop 500μV

Distortion 1kHz, 50% Mod 0.8%

Selectivity ±10kHz, 30dB

Video Section

Television Format NTSC

Input Level/Impedance 1Vp-p/75 ohms

Output Level/Impedance 1Vp-p/75 ohms

Video Frequency Response

(Composite and S-Video) 10Hz–8MHz (–3dB)

Video Frequency Response

(Component Video) 10Hz–50MHz (–3dB)

General

Power Requirement AC 120V/60Hz

Power Consumption 65W idle, 540W maximum

(6 channels driven)

Dimensions (Product) (Shipping)

Width 17.3 inches (440mm) 21.5 inches (545mm)

Height 6.6 inches (168mm) 9.9 inches (251mm)

Depth 15 inches (382mm) 17.9 inches (455mm)

(Product) (Shipping)

Weight 24.4 lb (11.1kg) 29.3 lb (13.3kg)

Depth measurement includes knobs, buttons and terminal connections.

Height measurement includes feet and chassis.

All features and specifications are subject to change without notice.

Harman Kardon and Power for the Digital Revolution are registered trademarks of

Harman International Industries, Incorporated.

* Manufactured under license from Dolby Laboratories. “Dolby,” “Pro Logic” and the Double-D symbol

are trademarks of Dolby Laboratories.

DTS, DTS Surround, DTS-ES and DTS Neo:6 are registered trademarks of Digital Theater Systems, Inc.

VMAx is a registered trademark of Harman International Industries, Incorporated, and is an

implementation of Cooper Bauck Transaural Stereo under patent license.

Logic 7 is a registered trademark of Harman International Industries, Incorporated.

Cirrus is a registered trademark of Cirrus Logic, Inc.

46 TECHNICAL SPECIFICATIONS

Page 3

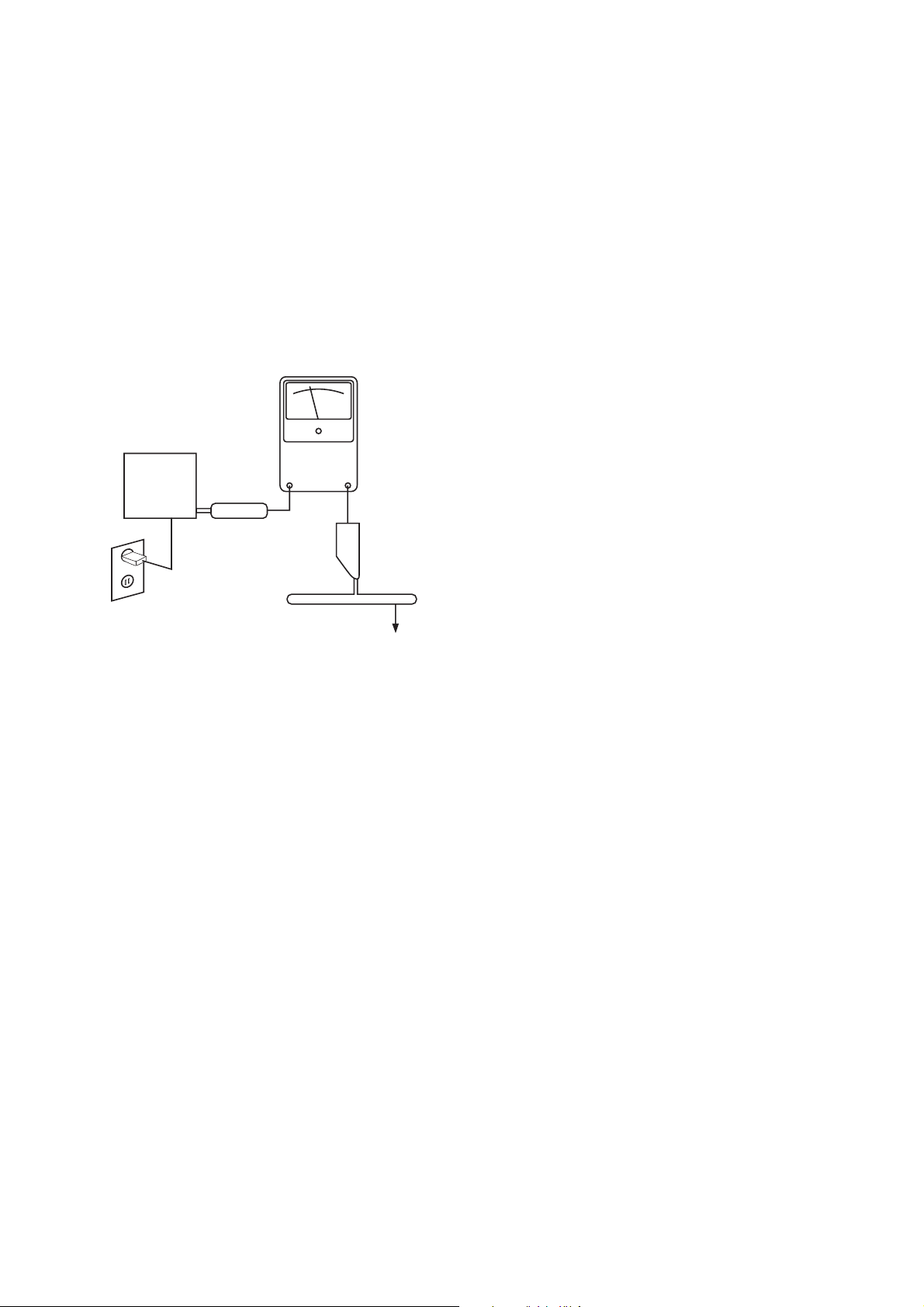

SAFETY PRECAUTIONS

The following check should be performed for the continued

protection of the customer and service technician.

LEAKAGE CURRENT CHECK

Measure leakage current to a known earth ground (water

pipe, conduit, etc.) by connecting a leakage current tester

between the earth ground and all exposed metal parts of the

appliance (input/output terminals, screwheads, metal

overlays, control shaft, etc.). Plug the AC line cord of the

appliance directly into a 250V AC 50Hz outlet and turn the

AC power switch on. Any current measured must not exceed

o.5mA.

Reading should

not be above

0.5mA

Earth

ground

Device

under

test

Test all

exposed metal

surfaces

Also test with

plug reversed

(Using AC adapter

plug as required)

Leakage

current

tester

AC Leakage Test

ANY MEASUREMENTS NOT WITHIN THE LIMITS

OUTLINED ABOVE ARE INDICATIVE OF A

POTENTIAL SHOCK HAZARD AND MUST BE

CORRECTED BEFORE RETURNING THE APPLIANCE

TO THE CUSTOMER.

Page 4

OPERATION

Surround Mode Chart

MODE FEATURES

Dolby Digital Available only with digital input sources encoded with Dolby Digital data. It provides up to five separate main audio channels and

a special dedicated Low-Frequency Effects channel.

Dolby Digital EX Available when the receiver is configured for 6.1/7.1-channel operation, Dolby Digital EX is the latest version of Dolby Digital. When used with

movies or other programs that have special encoding, Dolby Digital EX reproduces specially encoded soundtracks so that a full 6.1/7.1 sound field is

available. When the receiver is set for 6.1/7.1 operation and a Dolby Digital signal is present, the EX mode is automatically selected. Even if specific

EX encoding is not available to provide the additional channel, the special algorithms will derive a 6.1/7.1 output.

DTS 5.1 When the speaker configuration is set for 5.1-channel operation, the DTS 5.1 mode is available when DVD, audio-only music or laser discs encoded

with DTS data are played. DTS 5.1 provides up to five separate main audio channels and a special dedicated low-frequency channel.

DTS-ES 6.1 Matrix When the speaker configuration is set for 6.1/7.1 operation, playback of a DTS-encoded program source will automatically trigger the selection

DTS-ES 6.1 Discrete of one of the two DTS-ES modes. Newer discs with special DTS-ES discrete encoding will be decoded to provide six discrete, full-bandwidth

channels plus a separate low-frequency channel. All other DTS discs will be decoded using the DTS-ES Matrix mode, which creates a 6.1-channel

sound field from the original 5.1-channel soundtrack.

Dolby Pro Logic II Dolby Pro Logic II is the latest version of Dolby Laboratory’s benchmark surround technology that decodes full-range, discrete left, center right,

Movie right surround and left surround channels from either matrix surround-encoded programs and conventional stereo sources when an analog input

Music is in use. The Dolby Pro Logic II Movie mode is optimized for movie soundtracks, while the Pro Logic II Music mode should be used with

Pro Logic musical selections. The Pro Logic mode activates original Pro Logic processing for those who prefer that presentation.

Logic 7 Cinema Exclusive to Harman Kardon for A/V receivers, Logic 7 is an advanced mode that extracts the maximum surround information from either

Logic 7 Music surround-encoded programs or conventional stereo material. Depending on the number of speakers in use and the selection made in the

Logic 7 Enhance

DTS Neo:6 Cinema These two modes are available when any analog source is playing to create a six-channel surround presentation from conventional Matrix-encoded

DTS Neo:6 Music and traditional Stereo sources. Select the Cinema version of Neo:6 when a program with any type of analog Matrix surround encoding is present.

Dolby 3 Stereo Uses the information contained in a surround-encoded or two-channel stereo program to create center-channel information. In addition, the

Theater The Theater mode creates a sound field that resembles the acoustic feeling of a standard live-performance theater.

Hall 1, Hall 2 The two Hall modes create sound fields that resemble a small (Hall 1) and medium-sized (Hall 2) concert hall.

VMAx Near When only the two front-channel loudspeakers are used, Harman’s patented VMAx mode delivers a three-dimensional sound space with the illusion

VMAx Far of “phantom speakers” at the center and surround positions. The VMAx N, or “Near Field,” mode should be selected when your listening position is

5-Channel Stereo This mode takes advantage of multiple speakers to place a stereo signal at both the front and back of a room. Depending on whether the AVR

7-Channel Stereo has been configured for either 5.1 or 6.1/7.1 operation, one of these modes, but not both, is available at any time. Ideal for playing music in

Surround This mode turns off all surround processing and presents the pure left- and right-channel presentation of two-channel stereo programs.

Off (Stereo)

SURROUND SELECT menu, the “5.1” versions of Logic 7 modes are available when the 5.1 option is chosen, while the “7.1” versions of

Logic 7 produce a full sound field presentation, including back surround speakers when the “6.1/7.1” option is chosen. The Logic 7 C (or Cinema)

mode should be used with any source that contains Dolby Surround or similar matrix encoding. Logic 7 C delivers increased center-channel

intelligibility, and more accurate placement of sounds with fades and pans that are much smoother and more realistic than with other decoding

techniques. The Logic 7 M or Music mode should be used with analog or PCM stereo sources. Logic 7 M enhances the listening experience by

presenting a wider front soundstage and greater rear ambience. Both Logic 7 modes also direct low-frequency information to the subwoofer

(if installed and configured) to deliver maximum bass impact. The Logic 7 E (or Enhance) mode, available only when the 5.1 option is chosen,

is an extension of the Logic 7 mode that is primarily used with musical programs. Logic 7 adds additional bass enhancement that circulates low

frequencies in the 40Hz to 120Hz range to the front and surround speakers to deliver a less localized soundstage that appears broader and wider

than when the subwoofer is the sole source of bass energy.

Select the Music version of Neo:6 for optimal processing when a nonencoded, two-channel stereo program is being played.

information that is normally sent to the rear-channel surround speakers is carefully mixed in with the front-left and front-right channels for increased

realism. Use this mode when you have a center channel speaker but no surround speakers.

less than five feet from the speakers. The VMAx F, or “Far Field,” mode should be selected when your listening position is greater than five feet from

the speakers. The VMAx modes are also available using the

appear to push the sound field away from your ears, reducing the “inside the head” sensation often experienced when using headphones.

situations such as a party, it places the same signal at the front-left and surround-left, and front-right and surround-right speakers.

The center channel is fed a summed mono mix of the in-phase material of the left and right channels.

Headphones Output 4. When headphones are being used, the Far Field mode will

24 OPERATION

Page 5

TROUBLESHOOTING GUIDE

SYMPTOM CAUSE SOLUTION

Unit does not function when Main • No AC Power • Make certain AC power cord is plugged into

Power Switch is pushed a live outlet

• Check to see whether outlet is switch-controlled

Display lights, but no sound • Intermittent input connections • Make certain that all input and speaker connections

or picture are secure

•

Mute is on • Press Mute Button

• Volume control is down • Turn up volume control

Unit turns on, but front panel • Display brightness is turned off • Follow the instructions in the Display Brightness section

display does not light up on page 28 so that the display is set to VFD FULL

No sound from any speaker; • Amplifier is in protection mode • Check speaker wire connections for shorts at receiver and

light around power switch is red due to possible short speaker ends

• Amplifier is in protection mode • Contact your local Harman Kardon service center

due to internal problems

No sound from surround or • Incorrect surround mode • Select a mode other than Stereo

center speakers • Input is monaural • There is no surround information from mono sources

• Incorrect configuration • Check speaker mode configuration

• Stereo or Mono program material • The surround decoder may not create center- or rear-channel

information from nonencoded programs

41

Unit does not respond to • Weak batteries in remote • Change remote batteries

remote commands • Wrong device selected • Press the AVR selector

• Remote sensor is obscured • Make certain front panel sensor is visible to remote

or connect remote sensor

Intermittent buzzing in tuner • Local interference • Move unit or antenna away from computers, fluorescent

lights, motors or other electrical appliances

Letters flash in the channel indicator • Digital audio feed paused • Resume play for DVD

display and digital audio stops • Check that Digital Input is selected

In addition to the items shown above, additional information on troubleshooting possible problems with your AVR 135, or installation-related issues, may be found in the list of

"Frequently Asked Questions" which is located in the Product Support section of our Web site at www.harmankardon.com.

Processor Reset

In the rare case where the unit’s operation or the displays seem abnormal, the cause may involve the erratic

operation of the system’s memory or microprocessor.

To correct this problem, first unplug the unit from the

AC wall outlet and wait at least three minutes. After the

pause, reconnect the AC power cord and check the

unit’s operation. If the system still malfunctions, a system reset may clear the problem.

NOTE: Resetting the processor will erase any configuration settings you have made for speakers, output

levels, surround modes, digital input assignments as

well as the tuner presets. The unit will be returned to

the factory presets, and all settings for these items

must be reentered.

If the system is still operating incorrectly, there may

have been an electronic discharge or severe AC line

interference that has corrupted the memory or

microprocessor.

To clear the AVR 135’s entire system memory including tuner presets, output level settings, delay times and

speaker configuration data, press and hold the

Mode Button

will turn on automatically.

5 button for three seconds. The unit

Tone

If these steps do not solve the problem, consult an

authorized Harman Kardon service center.

TROUBLESHOOTING GUIDE 45

Page 6

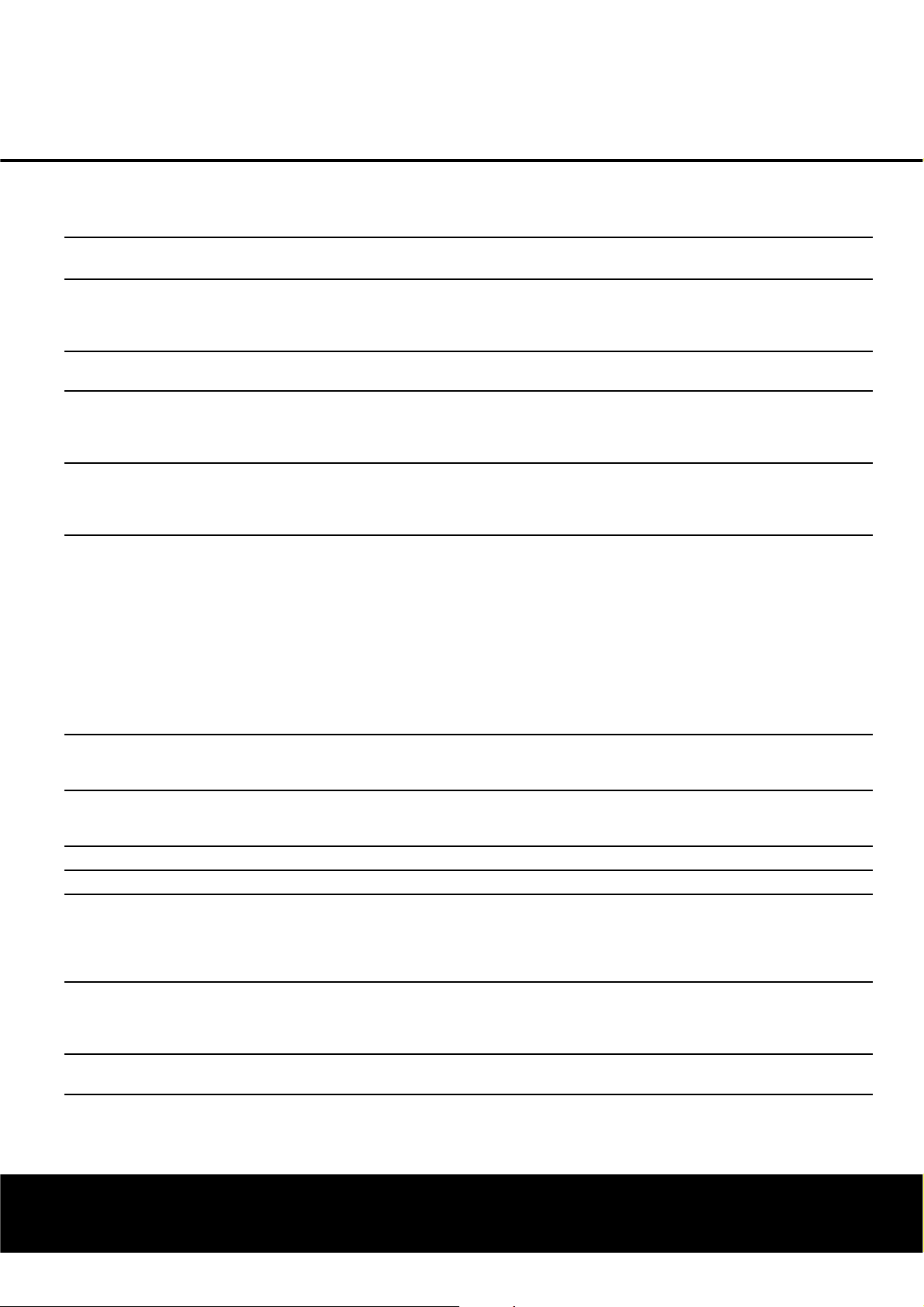

AMPLIFIER SECTION BIAS ADJUSTMENT

Measurement condition

. No input signal or volume position is minimum.

Standard value.

. Ideal current = 48mA ( ± 5%)

. Ideal DC Voltage = 25.92mV (

± 5%)

CUP11651Y (BIAS PCB)

...... ......

VR87

CN81

VR86

CN82

VR82

CN86

VR81

DC VOLTMETER..............Connect to CN81,CN82,CN83,CN84,CN85,CN86,CN87

NO. Channel Adjust for

1 Front Left 25.92mV (±5%)

2 Front Right 25.92mV (±5%)

3 Center

4 Surround Left

5 Surround Right

6

7

Surround Back Left

Surround Back Right

25.92mV (±5%)

25.92mV (±5%)

25.92mV (±5%)

25.92mV (±5%)

25.92mV (±5%)

Adjustment

VR81(235&335 ONLY)

CN87

VR83

VR84

VR85

VR86

VR87

VR82

Page 7

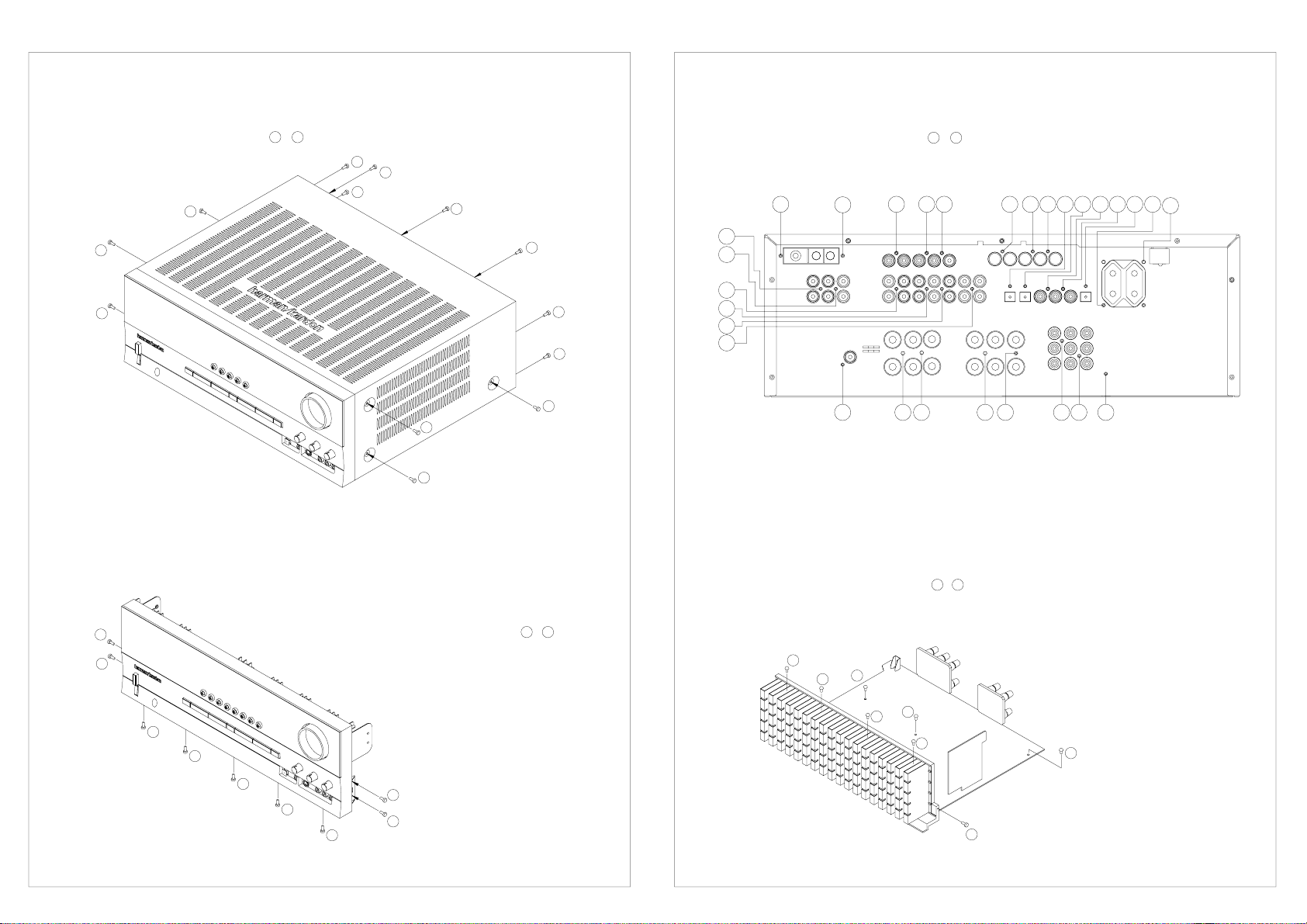

CHR@RRDLAKX

@UQ024.12/

0-QdlnuhmfsgdSnoB`ahmds

QdlnudsgdRbqdvr

5

3

4

0

2-QdlnuhmfsgdQd`qO`mdk

02

}

0/

8

00

6

7

01

02

2

0

1

QdlnudsgdRbqdvr

7

8

0/

00

01

02

03

6

11

12 14 15

15

0

}

354 2100405

13 16 17

06

18

1/07 08

10

3-QdlnuhmfsgdL`hmOBA

0 7

QdlnudsgdRbqdvr

}

1-QdlnuhmfsgdEqnmsO`mdk

8

7

6

5

4

3

QdlnudsgdRbqdvr

0

1

2

0 8

}

0

4

1

5

2

3

7

6

Page 8

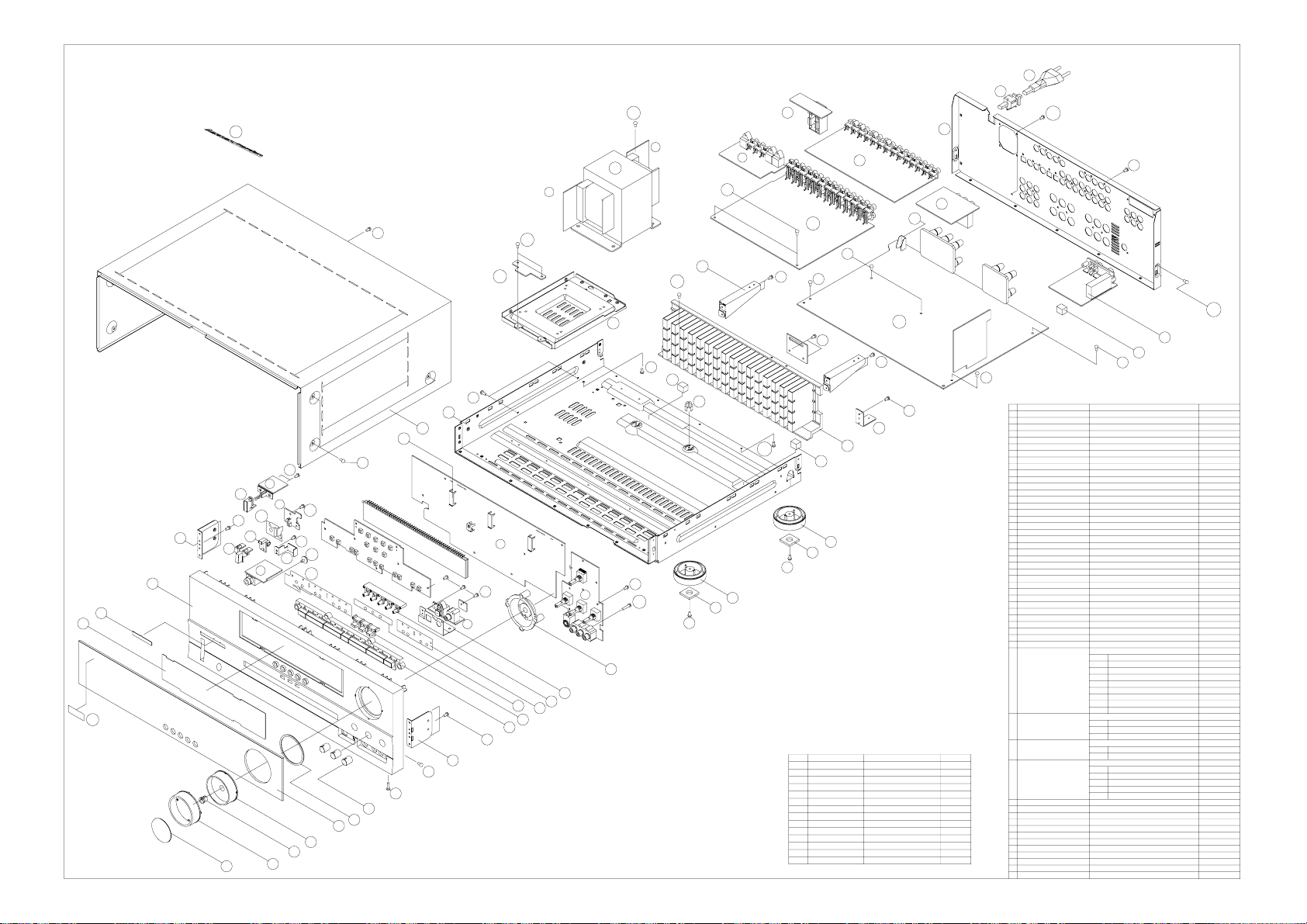

@UQ024.12/DWOKNCDUHDV

24

23

R8

36

3/,3

25

3/,4

R0

26,8

R3

R01

R00

2/

27,1

R02

22

3/,2

3/,0

R7

3/,1

28,0

R5

w1

R4

R3

21

R0/

R4

16

BSA2*0/F

BSVR2*0/F

BSV2*7I

BSA2*7I

BSV2*01I

BSA3*5EEB

BSA2*0/FEY

BGC0@/12

BSA2*5I

BGC0@/01Y

BGC3@/01

BSA2*7IEY

BSA2*05FEY

27,0

30

34

R3

R3

CDRBQHOSHNM

R4

06BSA2*7IEBRBQDV

26

0

8

0/

2

5

18

3

08

1

4

0

1

MN

B@O+UNKTLD

0

GNKCDQ+UNKTLD

1

HMCHB@SNQ+UNKTLD

2

VHMCNV+EHO

3

4

JMNA+QNS@QX

EHKSDQ+EHO

5

AC@FD+G@QL@M.J@QCNM

6

O@MDK+EQNMS

7

AQ@BJDS+RHCD

8

JMNA+ETMBSHNM

0/

JMNA+RDS

00

JMNA+CDK@X

01

JMNA+ONVDQ

02

HMCHB@SNQ+ONVDQ

03

JMNA+LNLR

04

AQ@BJDS+OBA

05

OK@SD+RGHDKC

06

07

GNKCDQ+KDC

08

AQ@BJDS+EHO

1/

B@AHMDS+SNO

10

BG@RRHR+ANSSNL

11

QTAADQ+BTRGHNM

12

ENNS

13

RTOONQS+BTRGHNM

14

GD@SRHMJ

15

AQ@BJDS+OBA

16

GNKCDQ+OBA

17

AQ@BJDS+SQ@MR

18

AQ@BJDS+OBA'G.S(

2/

RGDDS+UNKTLD

20

AQ@BJDS+OBA

21

O@MDK+QD@Q

22

ATRGHMF+@BBNQC

23

BNQC+ONVDQ

24

SQ@MR+ONVDQ

25

EQNMSO@A@RR&X

26

L@HMOBA@RR&X

27

HMOTSOBA@RR&X

28

UHCDNOBA@RR&X

3/

STMDQLNCTKD'DTQ(

30

A@CFD+LNCDK JFA0@035Y 0

31

HMRTK@SNQ+ETMBSHNM BLW0@037 1

32

HMRTK@SNQ+RDS BLW0@038 1

33

BTRGHNM+QTAADQ

34

BTRGHNM

35

A@CFD+SNO BFA0@041Y 0

36

37

38

O@QSRMNBFW0@227LAB11

BLG0@103

BFK0@111

BFT0@206Y

BAM0@063LAB11

BLY0@/77

JFA0@000W

BFV0@255QCYG32

BLC1@332

BAS0@8/4LAXB11

BAS0@8/3LAYB11

BAS0@708J017

BAS0@8/2LLYB11

BFK0@110

BAB0@036LAYB11

BLJ0@/0/

BLB0@1//

BLG0@104

BLC0@1/8

BJB3A034R35

BT@0@118

JGF0@/4/

BJK1@/58G32

BGF0@0/3

BLX0@137

BLC0@306

BGD0@06/

BLC0@376

BLC0@287

BLC0@276

BJE0/@143Y

JGQ0@/17

BI@1A/32Y@

BKS4U/26YD

BNO00634D

EHOOBA

26,0

JDXOBA

26,1

SNMDOBA

26,2

OGNMDOBA

26,3

LNLROBA

26,4

ONVDQKDCOBA

26,5

BNMMDBSNQOBA

26,6

CHFHS@KHMOTSOBA

26,7

CNVMKN@COBA

26,8

BNO00635D

L@HMOBA

27,0

@BNTSKDSROBA

27,1

HMOTSOBA

28,0

BNO00636D

UHCDNOBA

3/,0

CHFHS@KHMOTS.NTSOTSOBA

3/,2

SQ@MROBA

3/,3

SQ@MROBA

3/,4

BMUL8/03LR06/K

BGF0@046 0

BGF0@05/

P+sx

0

0

0

0

2

0

0

0

1

0

0

0

0

0

0

0

0

0

2

0

0

3

3

1

0

1

1

0

1BLC0@287

0

3

0

0

0

0

0

0

0

0

0

0

0

0

0

0

00

0

0

0

0BNO00637D

0

0

0

0

0

0

0

0

1BLW0@06/HMRTK@SNQ+ONVDQ

1BLW0@062HMRTK@SNQ+ETMBSHNM'K(

18

R3

R4

35

R4

11

10

1/

R1

26,4

04

26,5

37

R1

8

03

02

26,3

7

6

5

R1

R1

R2

05

38

R6

26,0

R1

26,7

26,2

R1

R03

17

R0/

15

14

13

12

R3

13

12

R3

08

06

01

33

32

31

8

R0

R0

4

20

3

2

1

07

0

00

0/

R1

CDRBQHOSHNM O@QSRMN- P+sx

MN

R0

RBQDV

R1

RBQDV

R2

RBQDV

R3

RBQDV

R4

RBQDV

R5

RBQDV

R6

RBQDV

R7

RBQDV+SQ@MR

R8

RBQDV

R0/

RBQDV+RODBH@K

R00

RBQDV+RODBH@K

R01

RBQDV

R02

RBQDV

R03

Page 9

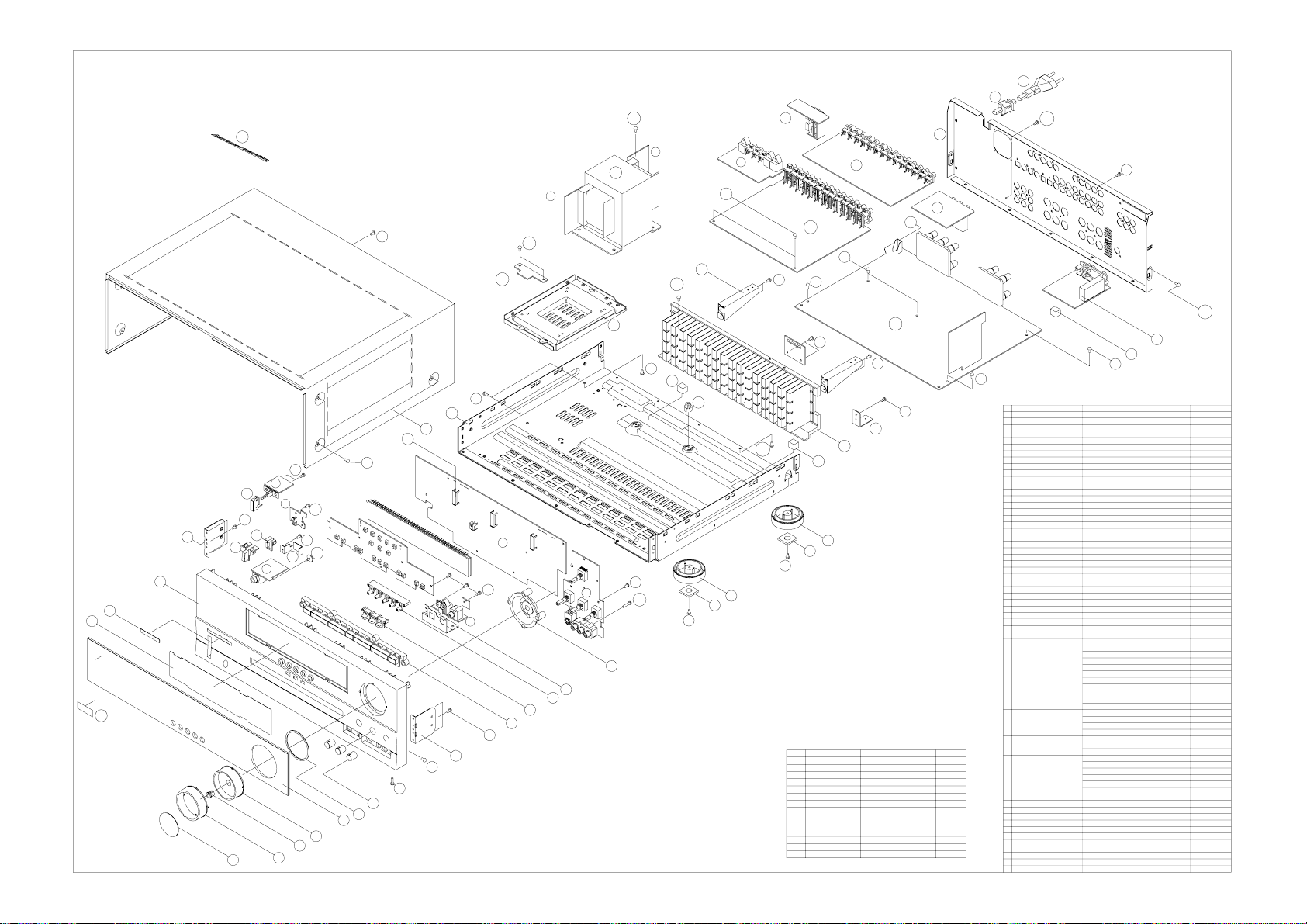

AVR135/230BK EXPLODE VIEW

24

23

R8

36

3/,3

25

3/,4

R0

26,8

R3

R01

R00

2/

27,1

R0

22

3/,2

3/,0

R7

3/,1

28,0

R5

w1

R4

R3

21

R0/

R4

16

BSA2*0/F

BSVR2*0/F

BSV2*7I

BSA2*7I

BSV2*01I

BSA3*5EEY

BSA2*0/FEY

BGC0@/12

BSA2*5I

BGC0@/01Y

BGC3@/01

BSA2*05FEY

27,0

30

34

R3

R3

CDRBQHOSHNM

R4

07BSA2*7IEYRBQDV

26

0

8

0/

2

5

18

3

08

1

4

1

MN

B@O+UNKTLD

0

GNKCDQ+UNKTLD

1

HMCHB@SNQ+UNKTLD

2

VHMCNV+EHO

3

4

JMNA+QNS@QX

EHKSDQ+EHO

5

AC@FD+G@QL@M.J@QCNM

6

O@MDK+EQNMS

7

AQ@BJDS+RHCD

8

JMNA+ETMBSHNM

0/

JMNA+RDS

00

JMNA+CDK@X

01

JMNA+ONVDQ

02

HMCHB@SNQ+ONVDQ

03

JMNA+LNLR

04

AQ@BJDS+OBA

05

OK@SD+RGHDKC

06

07

GNKCDQ+KDC

08

AQ@BJDS+EHO

1/

B@AHMDS+SNO

10

BG@RRHR+ANSSNL

11

QTAADQ+BTRGHNM

12

ENNS

13

RTOONQS+BTRGHNM

14

GD@SRHMJ

15

AQ@BJDS+OBA

16

GNKCDQ+OBA

17

AQ@BJDS+SQ@MR

18

AQ@BJDS+OBA'G.S(

2/

RGDDS+UNKTLD

20

AQ@BJDS+OBA

21

O@MDK+QD@Q

22

ATRGHMF+@BBNQC

23

BNQC+ONVDQ

24

SQ@MR+ONVDQ

25

EQNMSO@A@RR&X

26

L@HMOBA@RR&X

27

HMOTSOBA@RR&X

28

UHCDNOBA@RR&X

3/

STMDQLNCTKD'DTQ(

30

A@CFD+LNCDK JFA0@035Y 0

31

BTRGHNM+QTAADQ

34

BTRGHNM

35

A@CFD+SNO BFA0@041Y 0

36

O@QSRMNBFW0@227LAF16

BLG0@103

BFK0@111

BFT0@206Y

BAM0@063A2

BLY0@/77

JFA0@000W

BFV0@255Q3YG0/

BLC1@332

BAS0@8/4LAXF16

BAS0@8/3LAYF16

BAS0@708J017

BAS0@8/2LLXF16

BFK0@110

BAB0@036LAYF16

BLJ0@/0/

BLB0@1//

BLG0@104

BLC0@1/8

BJB3A034R0Y

BT@0@118

JGF0@/4/

BJK1@/58G32

BGF0@0/3

BLX0@137

BLC0@306

BGD0@06/

BLC0@376

BLC0@287

BLC0@276

BJE0/@143Y

JGQ0@/17

BI@1A/32Y@

BKS4U/26YD

BNO00634D

EHOOBA

26,0

JDXOBA

26,1

SNMDOBA

26,2

OGNMDOBA

26,3

LNLROBA

26,4

ONVDQKDCOBA

26,5

BNMMDBSNQOBA

26,6

CHFHS@KHMOTSOBA

26,7

CNVMKN@COBA

26,8

BNO00635D

L@HMOBA

27,0

@BNTSKDSROBA

27,1

HMOTSOBA

28,0

BNO00636D

UHCDNOBA

3/,0

CHFHS@KHMOTS.NTSOTSOBA

3/,2

SQ@MROBA

3/,3

SQ@MROBA

3/,4

BMUL8/03LR06/K

BGF0@046 0

BGF0@05/

P+sx

0

0

0

0

2

0

0

0

1

0

0

0

0

0

0

0

0

0

2

0

0

3

3

1

0

1

1

0

1BLC0@287

0

3

0

0

0

0

0

0

0

0

0

0

0

0

0

0

00

0

0

0

0BNO00637D

0

0

0

0

0

0

0

0

18

R3

R4

35

R4

11

10

1/

R1

26,4

04

26,5

R1

8

03

02

26,3

R1

R1

R2

05

7

6

5

R6

26,0

R1

26,7

26,2

R1

R03

17

R0/

15

14

13

12

R3

13

12

R3

08

06

01

31

8

R0

R0

4

20

3

2

1

07

0

00

0/

R1

CDRBQHOSHNM O@QSRMN- P+sx

MN

R0

RBQDV

R1

RBQDV

R2

RBQDV

R3

RBQDV

R4

RBQDV

R5

RBQDV

R6

RBQDV

R7

RBQDV+SQ@MR

R8

RBQDV

R0/

RBQDV+RODBH@K

R00

RBQDV+RODBH@K

R01

R02

RBQDV

R03

Page 10

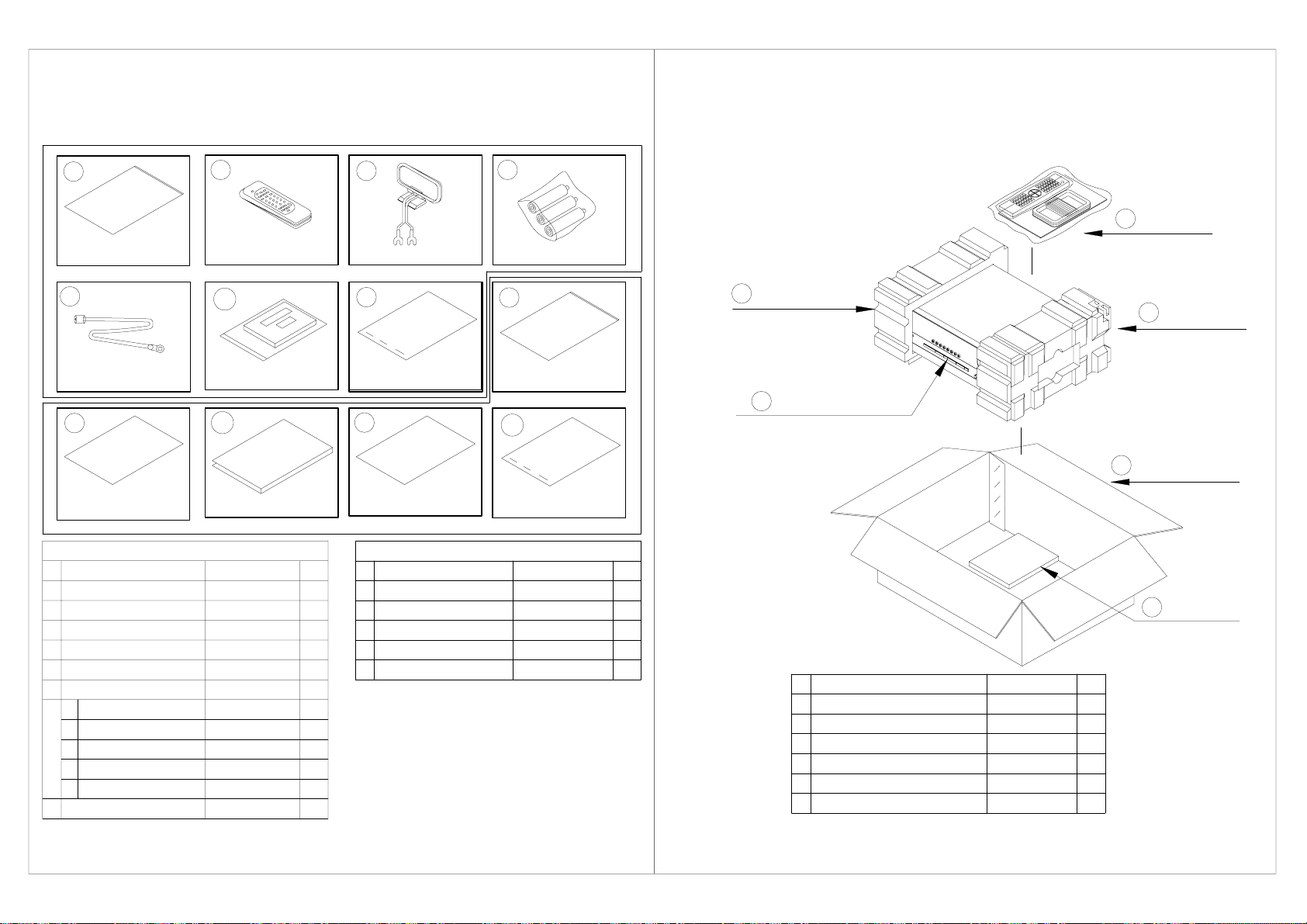

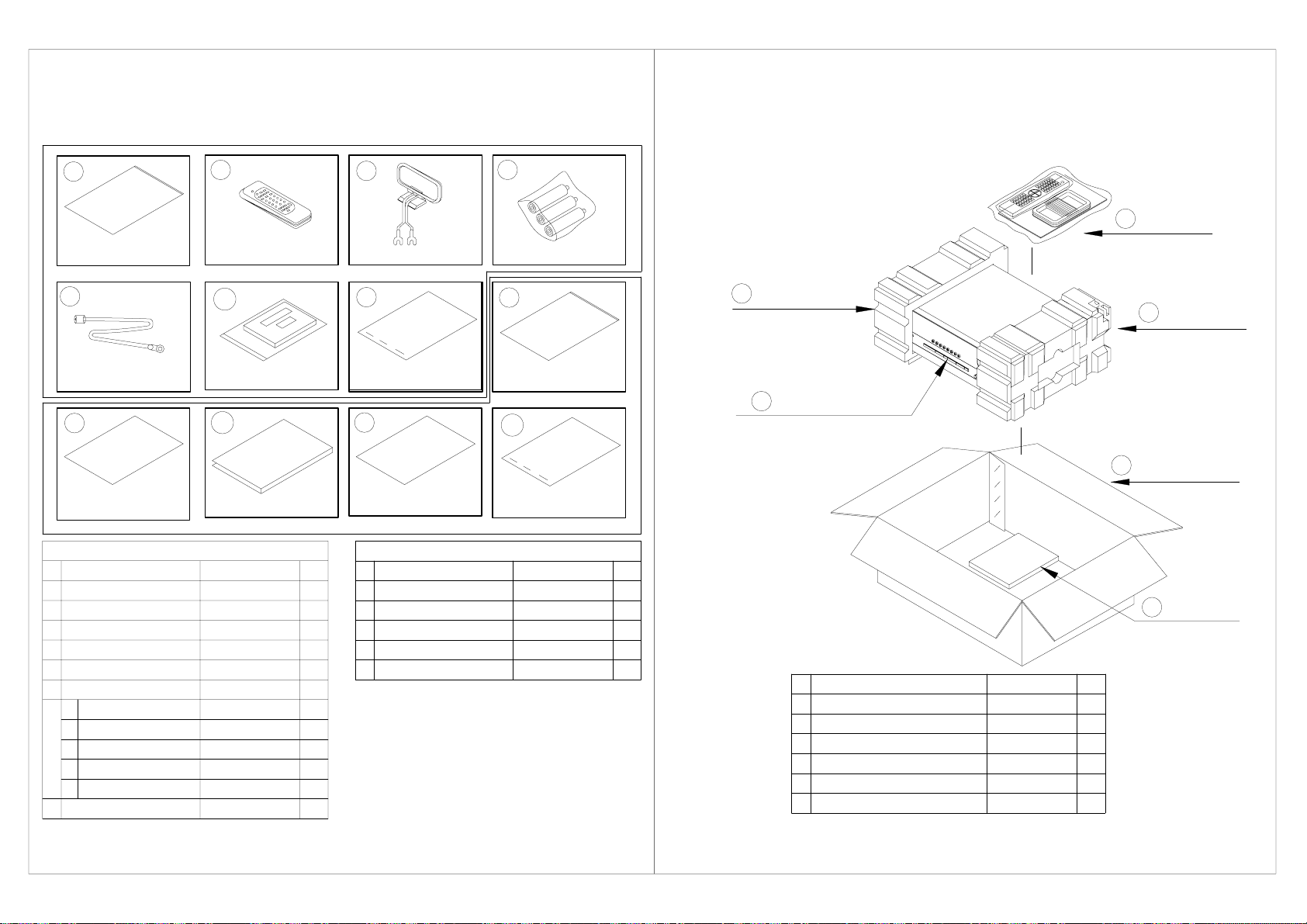

0-Hmrsqtbshnml`mt`k`rr&x,@bbdrrnqhdr 1-O`bj`fdCq`vhmf

BLACK

@UQ024.12/

0

ONKXA@F

4

EL0ONKD@MS

8

ANNJKDS+HMENQL@SHNM

MN CDRBQHOSHNM O@QSRMN- P+sx

0

1

QDLNBNMSQ@MRLHSSDQ@RR&X

2

3

EL0ONK@MS'TK( BR@0@/07Y 0

4

5

BNUDQ@RR&X

BNUDQ@

0

BNUDQA

1

RGDDS+EQNMSBNUDQ

2

O@C+BNUDQ

3

4

A@F+ONKX

6

RS@OKD JOK/8/4 2

1

QDLNBNM

SQ@MRLHSSDQ@RR&X

5

BNUDQ@RR&X

0/

L@MT@KHMRSQTBSHNM

BOA0/50XONKXA@F

HARTAVR135/230B

BR@0@/16Y@LKNNO@MSDMM@@RR&X 0

G@A@@@L0-4UGJA@SSDQX 2

CGRAVR130/230BZA

CGR1A331H10 1

CGR1A331H10 1

BPD0@11/Y

BOR0@565 0

BOA0@065Y 0

2

@LKNNO@MSDMM@@RR&X

6

RS@OKD

00

L@MT@KRDSTOFTHCD

3

7

01

RS@OKD

@BBDRRNQX,1@BBDRRNQX,0

MN CDRBQHOSHNM O@QSRMN- P+sx

0

0

0

0

0

7

ANNJKDS+HMENQL@SHNM

8

0/

00

L@MT@K+RDSTOFTHCD

01

RS@OKD JOK/8/4 2

BPD0@07/Y 0

BPW0@841YL@MT@K+HMRSQTBSHNM

BPW0@0/02Y

A@SSDQX@RR&X

ONKXA@F

@BBDRRNQX,0

0

1

RMNVO@C'K(

RDS

3

0BOA0/50XONKXA@F

0

0

CDRBQHOSHNMMN

@BBDRRNQX,0

0

1

RMNV+O@C'K(

RMNV+O@C'Q(20

RDS

3

ANW+NTSB@QSNM

4

61

@BBDRRNQX,1

CQXAVR135/230BK

BOR3@453

BOR3@454

AVR135/230BKSET

CPG1A775M

CQXAVR135/230BK

P+sxO@QSRMN-

0

0

0

0

RMNVO@C'Q(

2

ANW+NTSB@QSNM

4

@BBDRRNQX,1

5

Page 11

0-Hmrsqtbshnml`mt`k`rr&x,@bbdrrnqhdr 1-O`bj`fdCq`vhmf

@UQ024.12/

0

ONKXA@F

4

EL0ONKD@MS

8

ANNJKDS+HMENQL@SHNM

MN CDRBQHOSHNM O@QSRMN- P+sx

0

1

QDLNBNMSQ@MRLHSSDQ@RR&X

2

3

EL0ONK@MS'TK( BR@0@/07Y 0

4

5

BNUDQ@RR&X BFQ@UQ02/.12/Y@

BNUDQ@

0

BNUDQA

1

RGDDS+EQNMSBNUDQ

2

O@C+BNUDQ

3

4

A@F+ONKX

6

RS@OKD JOK/8/4 2

1

QDLNBNM

SQ@MRLHSSDQ@RR&X

5

BNUDQ@RR&X

0/

L@MT@KHMRSQTBSHNM

BOA0/50XONKXA@F

G@QS@UQ024.12/

BR@0@/16Y@LKNNO@MSDMM@@RR&X 0

G@A@@@L0-4UGJA@SSDQX 2

BFQ0@220L6G32 0

BPD0@11/Y

BOR0@565 0

BOA0@065Y 0

2

@LKNNO@MSDMM@@RR&X

6

RS@OKD

00

L@MT@KRDSTOFTHCD

3

7

01

RS@OKD

@BBDRRNQX,1@BBDRRNQX,0

MN CDRBQHOSHNM O@QSRMN- P+sx

0

0

0

0

0BFQ0@221L6G32

0

7

ANNJKDS+HMENQL@SHNM

8

0/

00

L@MT@K+RDSTOFTHCD

01

RS@OKD JOK/8/4 2

BPD0@07/Y 0

BPW0@841YL@MT@K+HMRSQTBSHNM

BPW0@0/02Y

A@SSDQX@RR&X

ONKXA@F

@BBDRRNQX,0

0

1

RMNVO@C'K(

RDS

3

0BOA0/50XONKXA@F

0

0

CDRBQHOSHNMMN

@BBDRRNQX,0

0

1

RMNV+O@C'K(

RMNV+O@C'Q(20

RDS

3

ANW+NTSB@QSNM

4

50

@BBDRRNQX,1 BPW@UQ024.12/

BPW@UQ024.12/

BOR3@453

BOR3@454

@UQ024.12/RDS

BOF0@664V

P+sxO@QSRMN-

0

0

0

0

RMNVO@C'Q(

2

ANW+NTSB@QSNM

4

@BBDRRNQX,1

5

Page 12

AVR135/230SET

Ref# Component Description 1 Description 2 Qty

CNVM9014MS170L TUNER MODULE(EUR) 1

T901 CLT5V037ZE TRANS , POWER 1

AV SURROUND RECEIVER

FRONT PCB

Ref# Component Description 1 Description 2 Qty

COP11745E FRONT PCB ASS'Y 1

C701 HCBS1H390JT CAP , CERAMIC 39PF 50V J 1

C702 HCBS1H390JT CAP , CERAMIC 39PF 50V J 1

C703 HCBS1H821KBT CAP , CERAMIC 820PF 50V K 1

C704 HCEA1VH100T CAP , ELECT 10UF 35V 1

C705 HCBS1H102KBT CAP , CERAMIC 1000PF 50V B 1

C706 HCBS1H561KBT CAP , CERAMIC 560PF 50V 1

C708 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C709 CCEA1CH101T CAP , ELECT 100UF 16V 1

C710 CCEA1HH2R2T CAP , ELECT 2.2UF 50V 1

C711 HCBS1H102KBT CAP , CERAMIC 1000PF 50V B 1

C712 HCEA1HH1R0T CAP , ELECT 1UF 50V 1

C713 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C714 HCBS1H151KBT CAP , CERAMIC 150PF 50V K 1

C716 HCEA1CH331T CAP , ELECT 330UF 16V 1

C719 HCBS1H181KBT CAP , CERAMIC 180PF 50V K 1

C720 HCBS1H181KBT CAP , CERAMIC 180PF 50V K 1

C721 HCBS1H181KBT CAP , CERAMIC 180PF 50V K 1

C723 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C724 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C725 CCKT1H473ZF CAP , CERAMIC 0.047UF 50V ZF 1

C726 HCEA1CH101T CAP , ELECT 100UF 16V 1

C728 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C729 CCKT1H473ZF CAP , CERAMIC 0.047UF 50V ZF 1

C730 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C731 HCEA1HH100T CAP , ELECT 10UF 50V 1

C735 CCEA1CH101T CAP , ELECT 100UF 16V 1

C736 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C737 HCBS1H180JCT CAP , CERAMIC 18PF 50V 1

C738 HCBS1H180JCT CAP , CERAMIC 18PF 50V 1

C739 CCEA1AH221T CAP , ELECT 220UF/10V 1

C740 CCEA1VH100T CAP , ELECT 10UF 35V 1

C770 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C771 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C773 HCEA1VH100T CAP , ELECT 10UF 35V 1

C774 HCEA1VH100T CAP , ELECT 10UF 35V 1

C775 HCBS1H151KBT CAP , CERAMIC 150PF 50V K 1

C776 HCBS1H151KBT CAP , CERAMIC 150PF 50V K 1

C777 HCEA1VH100T CAP , ELECT 10UF 35V 1

C778 HCEA1VH100T CAP , ELECT 10UF 35V 1

C779 HCEA1CKS470T CAP , ELECT 47UF 16V 1

C780 HCEA1CKS470T CAP , ELECT 47UF 16V 1

C781 HCEA1CKS100T CAP , ELECT 10UF 16V 1

C782 HCEA1CKS100T CAP , ELECT 10UF 16V 1

C785 HCBS1H470JT CAP , CERAMIC 47PF 50V J 1

C786 HCBS1H470JT CAP , CERAMIC 47PF 50V J 1

C787 HCEA1CKS100T CAP , ELECT 10UF 16V 1

C788 HCEA1CKS100T CAP , ELECT 10UF 16V 1

C789 HCEA1CKS100T CAP , ELECT 10UF 16V 1

C790 HCEA1CKS100T CAP , ELECT 10UF 16V 1

C791 HCEA1CKS470T CAP , ELECT 47UF 16V 1

C792 HCEA1CKS470T CAP , ELECT 47UF 16V 1

C793 KCFE1J183JBT CAP , FILM 0.018UF 63V J 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 13

FRONT PCB

Ref# Component Description 1 Description 2 Qty

C794 KCFE1J183JBT CAP , FILM 0.018UF 63V J 1

C795 KCFE1J823JBT CAP , FILM 0.082UF 63V J 1

C796 KCFE1J823JBT CAP , FILM 0.082UF 63V J 1

C797 KCFE1J332JBT CAP , FILM 0.0033UF 63V J 1

C798 KCFE1J332JBT CAP , FILM 0.0033UF 63V J 1

C799 KCFE1J183JBT CAP , FILM 0.018UF 63V J 1

C800 KCFE1J183JBT CAP , FILM 0.018UF 63V J 1

C805 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C806 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C807 CCFT1H104ZF CAP , SEMICONDUCTOR 0.1UF 50V ZF 1

C808 CCKT1H181KB CAP , CERAMIC 180PF 50V KB 1

C809 HCEA1AH471T CAP , ELECT 470UF 10V 1

C810 HCEA1CH101T CAP , ELECT 100UF 16V 1

C811 HCEA1CH101T CAP , ELECT 100UF 16V 1

C813 HCEA1HH4R7T CAP , ELECT 4.7UF 50V 1

C814 HCEA1HH4R7T CAP , ELECT 4.7UF 50V 1

C850 HCBS1H471KBT CAP , CERAMIC 470PF 50V 1

C851 HCBS1H471KBT CAP , CERAMIC 470PF 50V 1

C852 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C855 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C856 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C857 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C859 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C860 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C861 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C862 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C863 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C866 HCEA1CKS100T CAP , ELECT 10UF 16V 1

C867 HCEA1CKS100T CAP , ELECT 10UF 16V 1

C868 HCEA1CKS470T CAP , ELECT 47UF 16V 1

C869 HCEA1CKS470T CAP , ELECT 47UF 16V 1

C870 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C871 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C872 HCEA1CH331T CAP , ELECT 330UF 16V 1

C873 HCEA1CH331T CAP , ELECT 330UF 16V 1

C874 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C875 HCBS1H473ZFT CAP , CERAMIC 0.047UF 50V Z 1

C876 HCBS1H473ZFT CAP , CERAMIC 0.047UF 50V Z 1

C877 HCBS1H473ZFT CAP , CERAMIC 0.047UF 50V Z 1

C878 HCBS1H473ZFT CAP , CERAMIC 0.047UF 50V Z 1

C882 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C886 CCEA0JH102T CAP , ELECT 1000UF 6.3V 1

C887 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C888 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C889 HCBS1H220JCT CAP , CERAMIC 22PF 50V J 1

C890 HCBS1H220JCT CAP , CERAMIC 22PF 50V J 1

C891 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C892 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C893 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C894 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C895 HCEA1AH471T CAP , ELECT 470UF 10V 1

C896 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C897 HCEA1AH471T CAP , ELECT 470UF 10V 1

C898 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C899 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C900 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C901 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 14

FRONT PCB

Ref# Component Description 1 Description 2 Qty

C903 HCEA1HH2R2T CAP , ELECT 2.2UF 50V 1

C905 HCEA1HH2R2T CAP , ELECT 2.2UF 50V 1

D724 HVD1SS133MT DIODE 1SS133T-77 1

D728 HVD1SS133MT DIODE 1SS133T-77 1

D729 HVD1SS133MT DIODE 1SS133T-77 1

D730 HVD1SS133MT DIODE 1SS133T-77 1

D774 HVD1SS133MT DIODE 1SS133T-77 1

D778 KVD1N4003ST DIODE 1N4003 1

D779 HVD1SS133MT DIODE 1SS133T-77 1

D780 HVD1SS133MT DIODE 1SS133T-77 1

D781 HVD1SS133MT DIODE 1SS133T-77 1

D782 KVD1N4003ST DIODE 1N4003 1

D783 HVD1SS133MT DIODE 1SS133T-77 1

D784 HVD1SS133MT DIODE 1SS133T-77 1

D785 HVD1SS133MT DIODE 1SS133T-77 1

D786 HVDMTZJ5.6BT DIODE , ZENER 5.6V 1

D787 HVDMTZJ5.6BT DIODE , ZENER 5.6V 1

IC87 HVIRE5VL28CATZ IC , RESET RE5VL28CATZ 1

L702 HLQ02C100KT COIL , AXAIL 10UH 1

Q701 HVTKRC107MT T.R KRC107M 1

Q702 HVTKRC107MT T.R KRC107M 1

Q703 HVTKRC107MT T.R KRC107M 1

Q705 HVTKRC107MT T.R KRC107M 1

Q706 HVTKRC107MT T.R KRC107M 1

Q722 HVTKRA107MT T.R KRA107M 1

Q724 HVTKRC107MT T.R KRC107M 1

Q725 HVTKRC107MT T.R KRC107M 1

Q726 HVTKRC107MT T.R KRC107M 1

Q727 HVTKRC107MT T.R KRC107M 1

Q728 HVTKRC107MT T.R KRC107M 1

Q729 HVTKRC107MT T.R KRC107M 1

Q734 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q735 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q736 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q737 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q738 HVTKRC107MT T.R KRC107M 1

Q739 HVTKTA1271YT T.R KTA1271Y 1

Q743 HVTKRA107MT T.R KRA107M 1

R701 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R702 CRD20TJ1R0T RES , CARBON 1 OHM 1/5W J 1

R703 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R704 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R705 CRD20TJ820T RES , CARBON 82 OHM 1/5W J 1

R706 CRD20TJ820T RES , CARBON 82 OHM 1/5W J 1

R707 CRD20TJ820T RES , CARBON 82 OHM 1/5W J 1

R708 CRD20TJ820T RES , CARBON 82 OHM 1/5W J 1

R709 CRD20TJ470T RES , CARBON 47 OHM 1/5W J 1

R710 CRD20TJ470T RES , CARBON 47 OHM 1/5W J 1

R711 CRD20TJ470T RES , CARBON 47 OHM 1/5W J 1

R712 CRD20TJ470T RES , CARBON 47 OHM 1/5W J 1

R713 CRD20TJ332T RES , CARBON 3.3K OHM 1/5W J 1

R716 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R717 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R718 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R719 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R721 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R722 CRD20TJ1R0T RES , CARBON 1 OHM 1/5W J 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 15

FRONT PCB

Ref# Component Description 1 Description 2 Qty

R723 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R724 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R725 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R726 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R727 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R728 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R730 CRD20TJ112T RES,CABON 1.1K OHM 1/5W J 1

R731 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R732 CRD20TJ202T RES , CARBON 22K OHM 1/5W J 1

R733 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R734 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R735 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R736 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R737 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R744 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R745 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R746 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R747 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R749 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R750 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R751 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R753 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R754 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R755 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R756 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R757 CRD20TJ332T RES , CARBON 3.3K OHM 1/5W J 1

R758 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R759 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R760 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R761 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R762 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R763 CRD20TJ332T RES , CARBON 3.3K OHM 1/5W J 1

R764 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R765 CRD20TJ752T RES , CARBON 7.5K OHM 1/5W J 1

R766 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R767 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R768 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R769 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R771 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R772 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R773 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R780 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R781 CRD20TJ123T RES , CARBON 12K OHM 1/5W J 1

R805 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R806 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R810 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R811 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R813 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R814 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R824 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R825 CRD20TJ681T RES , CARBON 680 OHM 1/5W J 1

R826 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R827 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R829 CRD20TJ184T RES , CARBON 180K OHM 1/5W 1

R830 CRD20TJ184T RES , CARBON 180K OHM 1/5W 1

R831 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R832 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 16

FRONT PCB

Ref# Component Description 1 Description 2 Qty

R833 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R834 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R835 CRD20TJ184T RES , CARBON 180K OHM 1/5W 1

R836 CRD20TJ184T RES , CARBON 180K OHM 1/5W 1

R837 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R838 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R839 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R840 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R841 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R842 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R843 CRD20TJ105T RES , CARBON 1M OHM 1/5W J 1

R844 CRD20TJ105T RES , CARBON 1M OHM 1/5W J 1

R845 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R846 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R847 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R848 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R849 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R850 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R851 CRD20TJ392T RES , CARBON 3.9K OHM 1/5W J 1

R852 CRD20TJ392T RES , CARBON 3.9K OHM 1/5W J 1

R853 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R854 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R855 CRD20TJ681T RES , CARBON 680 OHM 1/5W J 1

R856 CRD20TJ681T RES , CARBON 680 OHM 1/5W J 1

R857 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R858 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R864 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R865 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R866 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R869 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R871 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R872 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R873 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R874 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R875 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R876 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R877 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R878 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R881 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R882 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R883 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R884 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R885 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R886 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R887 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R888 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R889 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R890 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R891 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R892 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R893 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R895 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R896 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R897 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R898 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R899 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R900 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 17

FRONT PCB

Ref# Component Description 1 Description 2 Qty

R901 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R902 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R903 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R904 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R905 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R906 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R907 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R908 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R909 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R910 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R911 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R912 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R913 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R914 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R915 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R918 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R919 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R923 CRD25TJ332T RES , CARBON 3.3K OHM 1/4W J 1

R924 CRD20TJ332T RES , CARBON 3.3K OHM 1/5W J 1

R925 CRD20TJ242T RES , CARBON 2.4K OHM 1/5W J 1

R926 CRD20TJ332T RES , CARBON 3.3K OHM 1/5W J 1

R927 CRD20TJ332T RES , CARBON 3.3K OHM 1/5W J 1

R928 CRD20TJ121T RES , CARBON 120 OHM 1/5W J 1

R929 CRD20TJ121T RES , CARBON 120 OHM 1/5W J 1

S701 HST1A020ZT SW , TACT 1

S702 HST1A020ZT SW , TACT 1

S703 HST1A020ZT SW , TACT 1

S704 HST1A020ZT SW , TACT 1

S705 HST1A020ZT SW , TACT 1

S706 HST1A020ZT SW , TACT 1

S707 HST1A020ZT SW , TACT 1

S708 HST1A020ZT SW , TACT 1

S709 HST1A020ZT SW , TACT 1

S710 HST1A020ZT SW , TACT 1

S711 HST1A020ZT SW , TACT 1

S712 HST1A020ZT SW , TACT 1

S713 HST1A020ZT SW , TACT 1

S714 HST1A020ZT SW , TACT 1

S715 HST1A020ZT SW , TACT 1

S716 HST1A020ZT SW , TACT 1

S717 HST1A020ZT SW , TACT 1

S718 HST1A020ZT SW , TACT 1

S719 HST1A020ZT SW , TACT 1

S720 HST1A020ZT SW , TACT 1

BAT1 HGP15BNH3A3H BATTERY , RECHARGEABLE GP15BNH3A3H 1

BK71 CMD1A209 BRACKET , FLT A4-92-1739 1

BK72 CMD1A209 BRACKET , FLT A4-92-1739 1

BK73 CMD1A387 BRACKET , PCB 1

BK74 CMD1A209 BRACKET , FLT A4-92-1739 1

BN10 CWZAVR230BN10 WIRE ASS'Y (SHIELD) 1

BN15 CWB2B906150EN WIRE ASS'Y 1

BN16 CWZAVR2550BN16 WIRE ASS'Y (SHIELD) 1

BN18 CWZAVR125BN18 WIRE ASS'Y (SHIELD) 1

BN41 CWZAVR130BN41 WIRE ASS'Y (SHIELD) 1

BN72 HJP32GA179ZJ CONN,FFC 1M/M 32P STR,SMD_JST 32FMNNBMTTNATF 1

BN80 CWB2B911420EW WIRE ASS'Y 1

BN81 CWB2B908250BM WIRE , ASS'Y 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 18

FRONT PCB

Ref# Component Description 1 Description 2 Qty

BN84 CWB2B905080EN WIRE ASS'Y 1

BN85 CWB2B902090EN WIRE ASS'Y 1

BN87 CWZAVR2550BN87 WIRE ASS'Y (SHIELD) 1

BN88 CWB2B904070EN WIRE ASS'Y 1

BN89 CWB2B905080EN WIRE ASS'Y 1

BN90 CWB2B902090EN WIRE ASS'Y 1

BN94 KJP13GB99ZM CONNECTOR MOLEX35237-1310 1

BN95 KJP08GB99ZM CONNECTOR , HOUSING MOLEX35237-0810 1

CN10 KJP04GB46ZM WAFER MOLEX 53015 1

CN11 KJP15GA98ZM WAFER MOLEX35336-1510 1

CN12 KJP15GA98ZM WAFER MOLEX35336-1510 1

CN15 CJP06GA19ZY WAFER, STRAIGHT, 6PIN 1

CN16 KJP08GB46ZM WAFER 1

CN82 KJP06HA37ZM WAFER MOLEX42140-2206 1

CN84 KJP05GA19ZM WAFER MOLEX53014-0510 1

CN85 KJP02GA19ZM WAFER 1

CN86 KJP02GA89ZM WAFER MOLEX35328-02 1

CN87 KJP06GA19ZM WAFER MOLEX53014-0610 1

CN89 KJP05GA19ZM WAFER MOLEX53014-0510 1

CN90 KJP02GA19ZM WAFER 1

C812 CCFT1H104ZF CAP , SEMICONDUCTOR 0.1UF 50V ZF 1

C817 CCCT1H100DC CAP , CERAMIC 10PF 50V DC 1

C853 KCKDKS472ME CAP , CERAMIC(X1/Y2/SC) 0.0047UF/2.5KV 1

D701 CVD52CSBBCEAB2 BLUE L.E.D 1

D703 CVD52CSBBCEAB2 BLUE L.E.D 1

D705 CVD52CSBBCEAB2 BLUE L.E.D 1

D723 CVD50BOBBWGA L.E.D , 2 COLOR (ORG , BLUE) TOL-50BOBBWGA 1

FIP1 HFLHCA18ML01 F.I.P 1

IC71 BVISAA6579TV1 I.C , RDS FILTER TW SAA6579T/V1 1

IC72 BVIMB90F482APFG IC , FLASH U-COM FUJITSU 1

IC73 HRVRPM6938H4 SENSOR , REMOTE RPM6938-H4 1

IC74 HVIANAM1385AT I.C , U-COM ANAM1385AT 1

IC75 HVI74ACT04MTR I.C , HEX 74ACT04M 1

IC76 HVITC74HCU04AFN IC , INVERTER TC74HCU04AFN 1

IC80 HVIHCF4053M013T I.C HCF4053M 1

IC81 HVINJM2068MDTE1 I.C , OP AMP NJM2068MD-TE1 1

IC82 HVINJM2068MDTE1 I.C , OP AMP NJM2068MD-TE1 1

IC83 HVI74ACT04MTR I.C , HEX 74ACT04M 1

IC84 HVI74ACT04MTR I.C , HEX 74ACT04M 1

IC85 HVIRH5VT18C I.C , RESET RICOH 1.8V 1

IC86 HVINJM4556AL I.C , HEADPHONE NJM4556AL 1

IC88 HVINJM2068MDTE1 I.C , OP AMP NJM2068MD-TE1 1

IC90 HVINJM2068MDTE1 I.C , OP AMP NJM2068MD-TE1 1

JK81 CJJ4M041Y JACK , BOARD (COAX) 1

JK82 HJSTORX179L MODULE , OPTICAL(RX) TORX179L 1

JK83 CJJ2E026Z JACK , HEADPHONE(SILVER PLATE) 1

JK85 CJJ9M003Z JACK , S-VIDEO 1

JK86 CJJ4S023Y JACK , BOARD 1

JW82 CWZAVR2550JW82 WIRE , ASS'Y 1

JW84 CWE8202110RV WIRE, ASS'Y 1

JW85 CWE8202070AA WIRE ASS'Y 1

SW01 CSH1A008ZV SW , PUSH (MOMS) 1

VR71 CVV2X05M104Z RES , VARIABLE(BALANCE) RK14128030214Y 1

VR72 CVV2X07C104Z RES , VARIABLE(TONE) RK14128030214C 1

VR73 CVV2X07C104Z RES , VARIABLE(TONE) RK14128030214C 1

VR74 HSR2A029Z VR , ENCODER 1

X701 HOX05000E160C CRYSTAL 5MHZ 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 19

FRONT PCB

Ref# Component Description 1 Description 2 Qty

X702 HOX04332E200C CRYSTAL 4.332MHZ 1

X703 HOX10000E220CS CRYSTAL 10MHZ 1

CB72 CWC1B2A32A250B CABLE , CARD 1

CGX1A338MBC22 CAP , VOLUME 1

CN88 KJP04GA19ZM WAFER 1

Bias PCB

Ref# Component Description 1 Description 2 Qty

CIP11651B BIAS T.R PCB AUTO ASS'Y 1

C852 HCEA1HH100T CAP , ELECT 10UF 50V 1

C853 HCEA1HH100T CAP , ELECT 10UF 50V 1

C854 HCEA1HH100T CAP , ELECT 10UF 50V 1

C855 HCEA1HH100T CAP , ELECT 10UF 50V 1

C856 HCEA1HH100T CAP , ELECT 10UF 50V 1

C857 HCEA1HH100T CAP , ELECT 10UF 50V 1

R875 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R876 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R877 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R878 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R879 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R880 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R883 CRD20TJ122T RES , CARBON 1.2K OHM 1/5W J 1

R884 CRD20TJ122T RES , CARBON 1.2K OHM 1/5W J 1

R885 CRD20TJ122T RES , CARBON 1.2K OHM 1/5W J 1

R886 CRD20TJ122T RES , CARBON 1.2K OHM 1/5W J 1

R887 CRD20TJ122T RES , CARBON 1.2K OHM 1/5W J 1

R888 CRD20TJ122T RES , CARBON 1.2K OHM 1/5W J 1

Q852 HVTKTD600KGR T.R , BIAS KTD600KGR 1

Q853 HVTKTD600KGR T.R , BIAS KTD600KGR 1

Q854 HVTKTD600KGR T.R , BIAS KTD600KGR 1

Q855 HVTKTD600KGR T.R , BIAS KTD600KGR 1

Q856 HVTKTD600KGR T.R , BIAS KTD600KGR 1

Q857 HVTKTD600KGR T.R , BIAS KTD600KGR 1

VR82 HVN1RA221B01T RES , SEMI FIXED(220 OHM) RH0615C100221 1

VR83 HVN1RA221B01T RES , SEMI FIXED(220 OHM) RH0615C100221 1

VR84 HVN1RA221B01T RES , SEMI FIXED(220 OHM) RH0615C100221 1

VR85 HVN1RA221B01T RES , SEMI FIXED(220 OHM) RH0615C100221 1

VR86 HVN1RA221B01T RES , SEMI FIXED(220 OHM) RH0615C100221 1

VR87 HVN1RA221B01T RES , SEMI FIXED(220 OHM) RH0615C100221 1

CN81 KJP02GB46ZM WAFER 1

CN82 KJP02GB46ZM WAFER 1

CN83 KJP02GB46ZM WAFER 1

CN84 KJP02GB46ZM WAFER 1

CN85 KJP02GB46ZM WAFER 1

CN86 KJP02GB46ZM WAFER 1

Regulator PCB

Ref# Component Description 1 Description 2 Qty

CN96 KJP08GA01ZM WAFER MOLEX 5267-08A 1

CN98 BJP08GB131ZK WAFER 1

R912 CRD20TJ153T RES , CARBON 15K OHM 1/5W J 1

R913 CRD20TJ153T RES , CARBON 15K OHM 1/5W J 1

R914 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

C928 CCEA1CH472E CAP , ELECT 4700UF 16V 1

C929 CCEA1EH332F CAP , ELECT 3300UF 25V 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 20

Regulator PCB

Ref# Component Description 1 Description 2 Qty

C930 CCEA1EH222E CAP. ELECT. 2200UF 25V 1

IC91 HVIL7815CP I.C, REGULATOR L7815CP 1

IC92 HVIL7915CP I.C, REGULATOR L7915CP 1

IC93 HVIL7805CP I.C, REGULATOR L7805CP 1

C922 HCEA1EH101T CAP , ELECT 100UF 25V 1

C923 HCEA1EH101T CAP , ELECT 100UF 25V 1

C924 HCEA1EH101T CAP , ELECT 100UF 25V 1

C925 CCKT1H223ZF CAP , CERAMIC 0.022UF 50V ZF 1

C926 CCKT1H223ZF CAP , CERAMIC 0.022UF 50V ZF 1

C927 CCKT1H223ZF CAP , CERAMIC 0.022UF 50V ZF 1

C931 HCEA1HH4R7T CAP , ELECT 4.7UF 50V 1

D903 KVD1N4003SRT DIODE TW 1N4003 1

D904 KVD1N4003ST DIODE 1N4003 1

D905 KVD1N4003ST DIODE 1N4003 1

D906 KVD1N4003ST DIODE 1N4003 1

D907 KVD1N4003ST DIODE 1N4003 1

D915 HVD1SS133MT DIODE 1SS133T-77 1

D916 HVD1SS133MT DIODE 1SS133T-77 1

MAIN PCB

Ref# Component Description 1 Description 2 Qty

COP11746E MAIN PCB ASS'Y 1

C501 HCEA1VH100T CAP , ELECT 10UF 35V 1

C502 HCEA1VH100T CAP , ELECT 10UF 35V 1

C503 HCEA1VH100T CAP , ELECT 10UF 35V 1

C504 HCEA1VH100T CAP , ELECT 10UF 35V 1

C505 HCEA1VH100T CAP , ELECT 10UF 35V 1

C506 CCKT1H331KB CAP , CERAMIC 330PF 50V KB 1

C507 CCKT1H331KB CAP , CERAMIC 330PF 50V KB 1

C508 CCKT1H331KB CAP , CERAMIC 330PF 50V KB 1

C509 CCKT1H331KB CAP , CERAMIC 330PF 50V KB 1

C510 CCKT1H331KB CAP , CERAMIC 330PF 50V KB 1

C561 HCEA1CH101T CAP , ELECT 100UF 16V 1

C562 HCEA1CH101T CAP , ELECT 100UF 16V 1

C563 HCEA1CH101T CAP , ELECT 100UF 16V 1

C564 HCEA1CH101T CAP , ELECT 100UF 16V 1

C565 HCEA1CH101T CAP , ELECT 100UF 16V 1

C566 HCEA1CH101T CAP , ELECT 100UF 16V 1

C567 HCEA1CH101T CAP , ELECT 100UF 16V 1

C568 HCEA1CH101T CAP , ELECT 100UF 16V 1

C569 HCEA1CH101T CAP , ELECT 100UF 16V 1

C570 HCEA1CH101T CAP , ELECT 100UF 16V 1

C571 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C572 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C573 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C574 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C575 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C601 CCCT1H120JC CAP , CERAMIC 12PF 50V JC 1

C602 CCCT1H120JC CAP , CERAMIC 12PF 50V JC 1

C603 CCCT1H120JC CAP , CERAMIC 12PF 50V JC 1

C604 CCCT1H120JC CAP , CERAMIC 12PF 50V JC 1

C605 CCCT1H120JC CAP , CERAMIC 12PF 50V JC 1

C606 CCCT1H330JC CAP , CERAMIC 33PF 50V JC 1

C607 CCCT1H330JC CAP , CERAMIC 33PF 50V JC 1

C608 CCCT1H330JC CAP , CERAMIC 33PF 50V JC 1

C609 CCCT1H330JC CAP , CERAMIC 33PF 50V JC 1

C610 CCCT1H330JC CAP , CERAMIC 33PF 50V JC 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 21

MAIN PCB

Ref# Component Description 1 Description 2 Qty

C681 HCEA1HH100T CAP , ELECT 10UF 50V 1

C682 HCEA1HH100T CAP , ELECT 10UF 50V 1

C683 HCEA1HH100T CAP , ELECT 10UF 50V 1

C684 HCEA1HH100T CAP , ELECT 10UF 50V 1

C685 HCEA1HH100T CAP , ELECT 10UF 50V 1

C726 CCKT1H221KB CAP , MYLAR 220PF 50V KB 1

C801 HCEA1HH100T CAP , ELECT 10UF 50V 1

C803 CCCT1H330JC CAP , CERAMIC 33PF 50V JC 1

C805 CCCT1H120JC CAP , CERAMIC 12PF 50V JC 1

C811 HCEA1CH101T CAP , ELECT 100UF 16V 1

C813 HCEA1CH101T CAP , ELECT 100UF 16V 1

C815 CCKT1H331KB CAP , CERAMIC 330PF 50V KB 1

C817 HCEA1VH100T CAP , ELECT 10UF 35V 1

C819 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C900 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C901 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C905 CCKT1H223ZF CAP , CERAMIC 0.022UF 50V ZF 1

C907 HCEA1CH101T CAP , ELECT 100UF 16V 1

C908 CCKT1H223ZF CAP , CERAMIC 0.022UF 50V ZF 1

C910 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C911 HCEA1CH471T CAP , ELECT 470UF 16V 1

C912 HCEA1CH221T CAP , ELECT 220UF 16V 1

C913 CCFT1H104ZF CAP , SEMICONDUCTOR 0.1UF 50V ZF 1

C917 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C918 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C919 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C939 HCEA1HH4R7T CAP , ELECT 4.7UF 50V 1

C940 HCEA1AH471T CAP , ELECT 470UF 10V 1

C971 HCQI1H562JZT CAP , MYLAR 5600PF 50V J 1

C973 HCQI1H562JZT CAP , MYLAR 5600PF 50V J 1

C974 HCQI1H562JZT CAP , MYLAR 5600PF 50V J 1

C975 HCQI1H562JZT CAP , MYLAR 5600PF 50V J 1

C980 HCQI1H562JZT CAP , MYLAR 5600PF 50V J 1

C981 HCQI1H562JZT CAP , MYLAR 5600PF 50V J 1

C990 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C991 HCEA1HH1R0T CAP , ELECT 1UF 50V 1

C992 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C993 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C995 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C996 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C997 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C999 CCKT1H223ZF CAP , CERAMIC 0.022UF 50V ZF 1

D501 HVD1SS133MT DIODE 1SS133T-77 1

D502 HVD1SS133MT DIODE 1SS133T-77 1

D503 HVD1SS133MT DIODE 1SS133T-77 1

D504 HVD1SS133MT DIODE 1SS133T-77 1

D505 HVD1SS133MT DIODE 1SS133T-77 1

D581 HVD1SS133MT DIODE 1SS133T-77 1

D582 HVD1SS133MT DIODE 1SS133T-77 1

D583 HVD1SS133MT DIODE 1SS133T-77 1

D584 HVD1SS133MT DIODE 1SS133T-77 1

D585 HVD1SS133MT DIODE 1SS133T-77 1

D801 HVD1SS133MT DIODE 1SS133T-77 1

D803 HVD1SS133MT DIODE 1SS133T-77 1

D901 KVD1N4003ST DIODE 1N4003 1

D902 HVD1SS133MT DIODE 1SS133T-77 1

D911 HVD1SS133MT DIODE 1SS133T-77 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 22

MAIN PCB

Ref# Component Description 1 Description 2 Qty

D912 HVD1SS133MT DIODE 1SS133T-77 1

D914 HVD1SS133MT DIODE 1SS133T-77 1

D917 HVD1SS133MT DIODE 1SS133T-77 1

D953 HVD1SS133MT DIODE 1SS133T-77 1

D954 KVD1N4003SRT DIODE TW 1N4003 1

D955 KVD1N4003SRT DIODE TW 1N4003 1

D961 KVD1N4003ST DIODE 1N4003 1

D962 KVD1N4003ST DIODE 1N4003 1

D963 KVD1N4003ST DIODE 1N4003 1

D977 HVD1SS133MT DIODE 1SS133T-77 1

D978 HVD1SS133MT DIODE 1SS133T-77 1

Q501 HVTKTA1268GRT T.R KTA1268GR 1

Q502 HVTKTA1268GRT T.R KTA1268GR 1

Q503 HVTKTA1268GRT T.R KTA1268GR 1

Q504 HVTKTA1268GRT T.R KTA1268GR 1

Q505 HVTKTA1268GRT T.R KTA1268GR 1

Q511 HVTKTC3200GRT T.R KTC3200GR 1

Q512 HVTKTC3200GRT T.R KTC3200GR 1

Q513 HVTKTC3200GRT T.R KTC3200GR 1

Q514 HVTKTC3200GRT T.R KTC3200GR 1

Q515 HVTKTC3200GRT T.R KTC3200GR 1

Q516 HVTKTC3200GRT T.R KTC3200GR 1

Q517 HVTKTC3200GRT T.R KTC3200GR 1

Q518 HVTKTC3200GRT T.R KTC3200GR 1

Q519 HVTKTC3200GRT T.R KTC3200GR 1

Q520 HVTKTC3200GRT T.R KTC3200GR 1

Q541 HVTKTC3198YT T.R KTC3198Y 1

Q542 HVTKTC3198YT T.R KTC3198Y 1

Q543 HVTKTC3198YT T.R KTC3198Y 1

Q544 HVTKTC3198YT T.R KTC3198Y 1

Q545 HVTKTC3198YT T.R KTC3198Y 1

Q556 HVTKTC3200GRT T.R KTC3200GR 1

Q557 HVTKTC3200GRT T.R KTC3200GR 1

Q558 HVTKTC3200GRT T.R KTC3200GR 1

Q559 HVTKTC3200GRT T.R KTC3200GR 1

Q560 HVTKTC3200GRT T.R KTC3200GR 1

Q561 HVTKTC3200GRT T.R KTC3200GR 1

Q562 HVTKTC3200GRT T.R KTC3200GR 1

Q563 HVTKTC3200GRT T.R KTC3200GR 1

Q564 HVTKTC3200GRT T.R KTC3200GR 1

Q565 HVTKTC3200GRT T.R KTC3200GR 1

Q601 HVTKTA1268GRT T.R KTA1268GR 1

Q602 HVTKTA1268GRT T.R KTA1268GR 1

Q603 HVTKTA1268GRT T.R KTA1268GR 1

Q604 HVTKTA1268GRT T.R KTA1268GR 1

Q605 HVTKTA1268GRT T.R KTA1268GR 1

Q681 KVTKSC2785YT T.R KSC2785Y 1

Q682 KVTKSC2785YT T.R KSC2785Y 1

Q683 KVTKSC2785YT T.R KSC2785Y 1

Q684 KVTKSC2785YT T.R KSC2785Y 1

Q685 KVTKSC2785YT T.R KSC2785Y 1

Q706 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q801 KVTKSC2785YT T.R KSC2785Y 1

Q812 HVTKTA1268GRT T.R KTA1268GR 1

Q813 HVTKTC3200GRT T.R KTC3200GR 1

Q816 HVTKTA1268GRT T.R KTA1268GR 1

Q818 HVTKTC3200GRT T.R KTC3200GR 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 23

MAIN PCB

Ref# Component Description 1 Description 2 Qty

Q819 HVTKTC3200GRT T.R KTC3200GR 1

Q820 HVTKTC3200GRT T.R KTC3200GR 1

Q824 HVTKTC3198YT T.R KTC3198Y 1

Q826 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q901 KVTKSC2785YT T.R KSC2785Y 1

Q938 HVTKRA107MT T.R KRA107M 1

Q939 HVTKRA107MT T.R KRA107M 1

Q942 KVTKSC2785YT T.R KSC2785Y 1

Q943 KVTKSC2785YT T.R KSC2785Y 1

Q951 HVTKRC107MT T.R KRC107M 1

Q952 HVTKRA107MT T.R KRA107M 1

Q960 HVTKRC107MT T.R KRC107M 1

Q961 HVTKTA1024YT T.R KTA1024Y 1

Q969 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q970 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q971 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q972 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q973 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q991 HVTKRC107MT T.R KRC107M 1

Q992 HVTKRA107MT T.R KRA107M 1

R501 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R502 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R503 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R504 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R505 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R506 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R507 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R508 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R509 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R510 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R511 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R512 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R513 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R514 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R515 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R516 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R517 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R518 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R519 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R520 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R521 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R522 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R523 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R524 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R525 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R531 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R532 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R533 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R534 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R535 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R536 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R537 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R538 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R539 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R540 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R541 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R542 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 24

MAIN PCB

Ref# Component Description 1 Description 2 Qty

R543 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R544 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R545 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R556 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R557 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R558 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R559 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R560 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R561 CRD20TJ202T RES , CARBON 2K OHM 1/5W J 1

R562 CRD20TJ202T RES , CARBON 2K OHM 1/5W J 1

R563 CRD20TJ202T RES , CARBON 2K OHM 1/5W J 1

R564 CRD20TJ202T RES , CARBON 2K OHM 1/5W J 1

R565 CRD20TJ202T RES , CARBON 2K OHM 1/5W J 1

R566 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R567 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R568 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R569 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R570 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R571 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R572 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R573 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R574 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R575 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R576 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R577 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R578 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R579 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R580 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R581 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R582 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R583 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R584 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R585 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R586 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R587 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R588 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R589 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R590 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R591 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R592 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R593 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R594 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R595 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R596 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R597 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R598 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R599 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R600 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R601 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R602 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R603 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R604 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R605 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R606 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R607 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R608 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R609 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 25

MAIN PCB

Ref# Component Description 1 Description 2 Qty

R610 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R611 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R631 KRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R632 KRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R633 KRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R634 KRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R635 KRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R636 KRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R637 KRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R638 KRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R639 KRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R640 KRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R646 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R647 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R648 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R649 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R650 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R651 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R652 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R653 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R654 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R655 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R666 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R667 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R668 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R669 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R670 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R671 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R672 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R673 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R674 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R675 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R676 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R677 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R678 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R679 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R680 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R681 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R682 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R683 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R684 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R685 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R686 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R687 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R688 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R689 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R690 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R696 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R697 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R698 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R699 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R700 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R706 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R716 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R726 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R771 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R772 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 26

MAIN PCB

Ref# Component Description 1 Description 2 Qty

R773 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R774 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R775 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R776 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R781 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R782 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R783 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R784 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R785 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R786 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R801 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R803 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R805 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R808 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R812 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R813 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R817 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R818 KRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R821 KRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R822 KRD25FJ180T RES , CARBON 18 OHM 1/4W 1

R830 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R831 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R834 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R835 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R836 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R837 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R842 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R843 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R848 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R850 CRD20TJ202T RES , CARBON 2K OHM 1/5W J 1

R852 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R853 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R856 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R857 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R860 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R862 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R864 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R866 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R868 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R870 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R872 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R900 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R901 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R902 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R903 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R906 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R910 CRD20TJ105T RES , CARBON 1M OHM 1/5W J 1

R911 CRD25TJ680T RES , CARBON 68 OHM 1/4W J 1

R917 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R918 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R919 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R920 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R932 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R939 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R940 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R941 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R942 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 27

MAIN PCB

Ref# Component Description 1 Description 2 Qty

R943 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R944 CRD25TJ223T RES , CARBON 22K OHM 1/4W J 1

R945 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R946 CRD25TJ223T RES , CARBON 22K OHM 1/4W J 1

R947 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R955 CRD20TJ393T RES , CARBON 39K OHM 1/5W J 1

R956 CRD20TJ394T RES , CARBON 390K OHM 1/5W J 1

R957 CRD20TJ153T RES , CARBON 15K OHM 1/5W J 1

R960 CRD20TJ392T RES , CARBON 39K OHM 1/5W J 1

R961 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R962 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R963 CRD20TJ105T RES , CARBON 1M OHM 1/5W J 1

R966 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R969 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R970 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R971 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R972 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R973 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R974 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R975 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R976 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R977 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R978 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R979 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R980 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R981 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R982 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R983 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R986 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R987 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R988 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R991 CRD20TJ822T RES , CARBON 8.2K OHM 1/5W J 1

R992 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R998 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

CMD1A387 BRACKET , PCB 1

CMYAVR135 HEAT SINK ASS'Y 1

CHD1A012 SCREW , TR 18

CHD3A012 SCREW , TR 3

CMD1A398 BRACKET , PCB 2

CMD1A417 BRACKET , PCB 2

CMY1A248 HEAT SINK 1

CTB3+8J SCREW 6

Q652 BVT2SB1560-OKM T.R , POWER 2SB1560 1

Q653 BVT2SB1560-OKM T.R , POWER 2SB1560 1

Q654 BVT2SB1560-OKM T.R , POWER 2SB1560 1

Q655 BVT2SB1560-OKM T.R , POWER 2SB1560 1

Q657 BVT2SD2390-OKM T.R , POWER 2SD2390 1

Q658 BVT2SD2390-OKM T.R , POWER 2SD2390 1

Q659 BVT2SD2390-OKM T.R , POWER 2SD2390 1

Q660 BVT2SD2390-OKM T.R , POWER 2SD2390 1

Q661 BVT2SB1560-OKM T.R , POWER 2SB1560 1

Q670 BVT2SD2390-OKM T.R , POWER 2SD2390 1

Q803 BVT2SD2390-OKM T.R , POWER 2SD2390 1

Q804 BVT2SB1560-OKM T.R , POWER 2SB1560 1

CTW3+8J SCREW 3

BN19 CWB3FE03250UP WIRE ASS'Y 1

BN20 CWB3FB43280UP WIRE ASS'Y 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 28

MAIN PCB

Ref# Component Description 1 Description 2 Qty

BN82 CWB1C902050EN WIRE ASS'Y 1

BN83 CWB1C902050EN WIRE ASS'Y 1

BN84 CWB1C902050EN WIRE ASS'Y 1

BN85 CWB1C902050EN WIRE ASS'Y 1

BN86 CWB1C902050EN WIRE ASS'Y 1

BN87 CWB1C902050EN WIRE ASS'Y 1

BN98 BJP08GA130ZK WAFER 1

BN99 CWB1C902050EN WIRE ASS'Y 1

CN61 KJP02GA01ZM WAFER MOLEX 5267-02A 1

CN62 KJP02GA01ZM WAFER MOLEX 5267-02A 1

CN63 KJP02GA01ZM WAFER MOLEX 5267-02A 1

CN64 KJP02GA01ZM WAFER MOLEX 5267-02A 1

CN65 KJP02GA01ZM WAFER MOLEX 5267-02A 1

CN66 KJP02GA01ZM WAFER MOLEX 5267-02A 1

CN80 KJP11GA19ZM WAFER MOLEX-53014 1

CN91 KJP03GA89ZM WAFER MOLEX35328-0310 1

CN94 KJP13GA98ZM WAFER MOLEX35336-1310 1

CN95 KJP08GA98ZM WAFER MOLEX35336-0810 1

CN99 CJP02GA19ZY WAFER, 2PIN CJP02GA19ZY 1

C631 CCEA1JH221E CAP , ELECT 220UF 63V 1

C632 CCEA1JH221E CAP , ELECT 220UF 63V 1

C633 CCEA1JH221E CAP , ELECT 220UF 63V 1

C634 CCEA1JH221E CAP , ELECT 220UF 63V 1

C635 CCEA1JH221E CAP , ELECT 220UF 63V 1

C636 CCEA1JH221E CAP , ELECT 220UF 63V 1

C637 CCEA1JH221E CAP , ELECT 220UF 63V 1

C638 CCEA1JH221E CAP , ELECT 220UF 63V 1

C639 CCEA1JH221E CAP , ELECT 220UF 63V 1

C640 CCEA1JH221E CAP , ELECT 220UF 63V 1

C807 CCEA1JH221E CAP , ELECT 220UF 63V 1

C808 CCEA1JH221E CAP , ELECT 220UF 63V 1

C902 CCET50VKL4822NK CAP , ELECT 8200UF/50V 1

C904 KCKDKS472ME CAP , CERAMIC(X1/Y2/SC) 0.0047UF/2.5KV 1

C906 HCEA1EH102E CAP , ELECT 1000UF 25V 1

C909 CCET50VKL4822NK CAP , ELECT 8200UF/50V 1

C915 CCET50VKL4822NK CAP , ELECT 8200UF/50V 1

C916 CCET50VKL4822NK CAP , ELECT 8200UF/50V 1

D971 HVD1SS133MT DIODE 1SS133T-77 1

ET01 CNE75 PLATE , EARTH 1

ET03 CNE75 PLATE , EARTH 1

IC94 HVIMC7805C I.C, REGULATOR KA7805-ABTU 1

JK90 CJJ4M040Z JACK , BOARD (SW) 1

JK91 CJJ5R006Z TERMINAL , SPEAKER 1

JK92 CJJ5R007Z TERMINAL , SPEAKER 1

JW90 CWEE212120VV WIRE ASS'Y 1

JW91 CWE8212180VV WIRE ASS'Y 1

JW99 CWE8202150AA WIRE ASS'Y 1

L501 CLEY0R5KAK COIL , SPEAKER 0.5UH K 1

L502 CLEY0R5KAK COIL , SPEAKER 0.5UH K 1

L503 CLEY0R5KAK COIL , SPEAKER 0.5UH K 1

L504 CLEY0R5KAK COIL , SPEAKER 0.5UH K 1

L505 CLEY0R5KAK COIL , SPEAKER 0.5UH K 1

L506 CLEY0R5KAK COIL , SPEAKER 0.5UH K 1

Q858 HVT2SA1360O T.R 2SA1360O 1

Q871 HVT2SA1360O T.R 2SA1360O 1

Q872 HVT2SA1360O T.R 2SA1360O 1

Q874 HVT2SA1360O T.R 2SA1360O 1

+DUPDQ&RQVXPHU*URXS,QWHUQDO %LOORI0DWHULDOV $95

Page 29

MAIN PCB

Ref# Component Description 1 Description 2 Qty

Q875 HVT2SA1360O T.R 2SA1360O 1

Q876 HVT2SA1360O T.R 2SA1360O 1

Q881 HVT2SC3423O T.R 2SC3423O 1

Q882 HVT2SC3423O T.R 2SC3423O 1

Q883 HVT2SC3423O T.R 2SC3423O 1

Q884 HVT2SC3423O T.R 2SC3423O 1

Q885 HVT2SC3423O T.R 2SC3423O 1