Page 1

For U.S.A., Canada, Europe

& Japan model

SERVICE MANUAL

MODEL DN-S3000

TABLE TOP SINGLE CD PLAYER

Ver. 1

●

For purposes of improvement, specifications and

design are subject to change without notice.

●

Please use this service manual with referring to the

operating instructions without fail.

●

Some illustrations using in this service manual are

slightly different from the actual set.

注 意

サービスをおこなう前に、このサービスマニュアルを

必ずお読みください。本機は、火災、感電、けがなど

に対する安全性を確保するために、さまざまな配慮を

おこなっており、また法的には「電気用品安全法」に

もとづき、所定の許可を得て製造されております。

従ってサービスをおこなう際は、これらの安全性が維

持されるよう、このサービスマニュアルに記載されて

いる注意事項を必ずお守りください。

●

本機の仕様は性能改良のため、予告なく変更すること

があります。

●

補修用性能部品の保有期間は、製造打切後8年です。

●

修理の際は、必ず取扱説明書を参照の上、作業を行っ

てください。

●

本文中に使用しているイラストは、説明の都合上現物

と多少異なる場合があります。

16-11, YUSHIMA 3-CHOME, BUNKYOU-KU, TOKYO 113-0034 JAPAN

X0180V.01 DE/CDM 0308

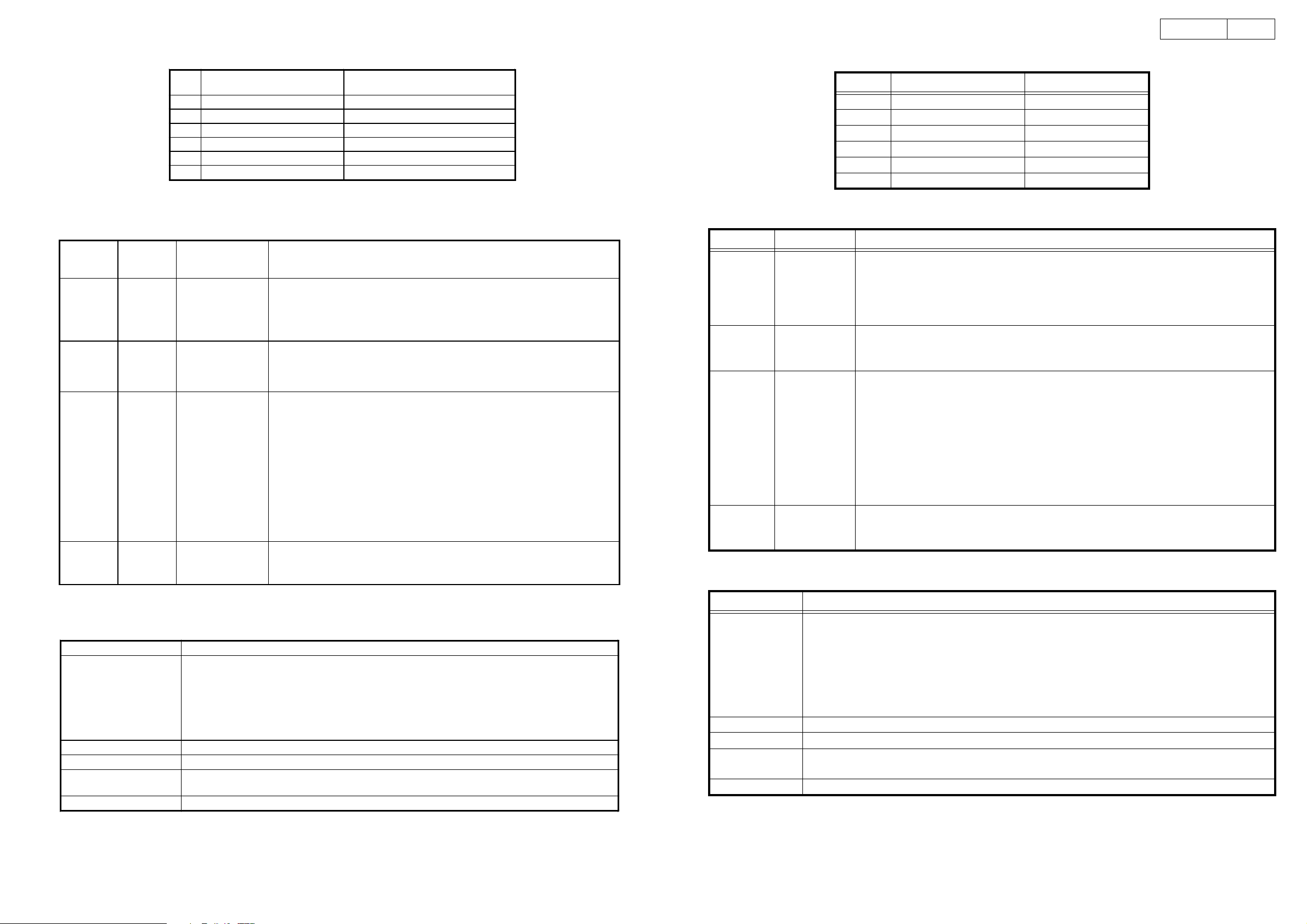

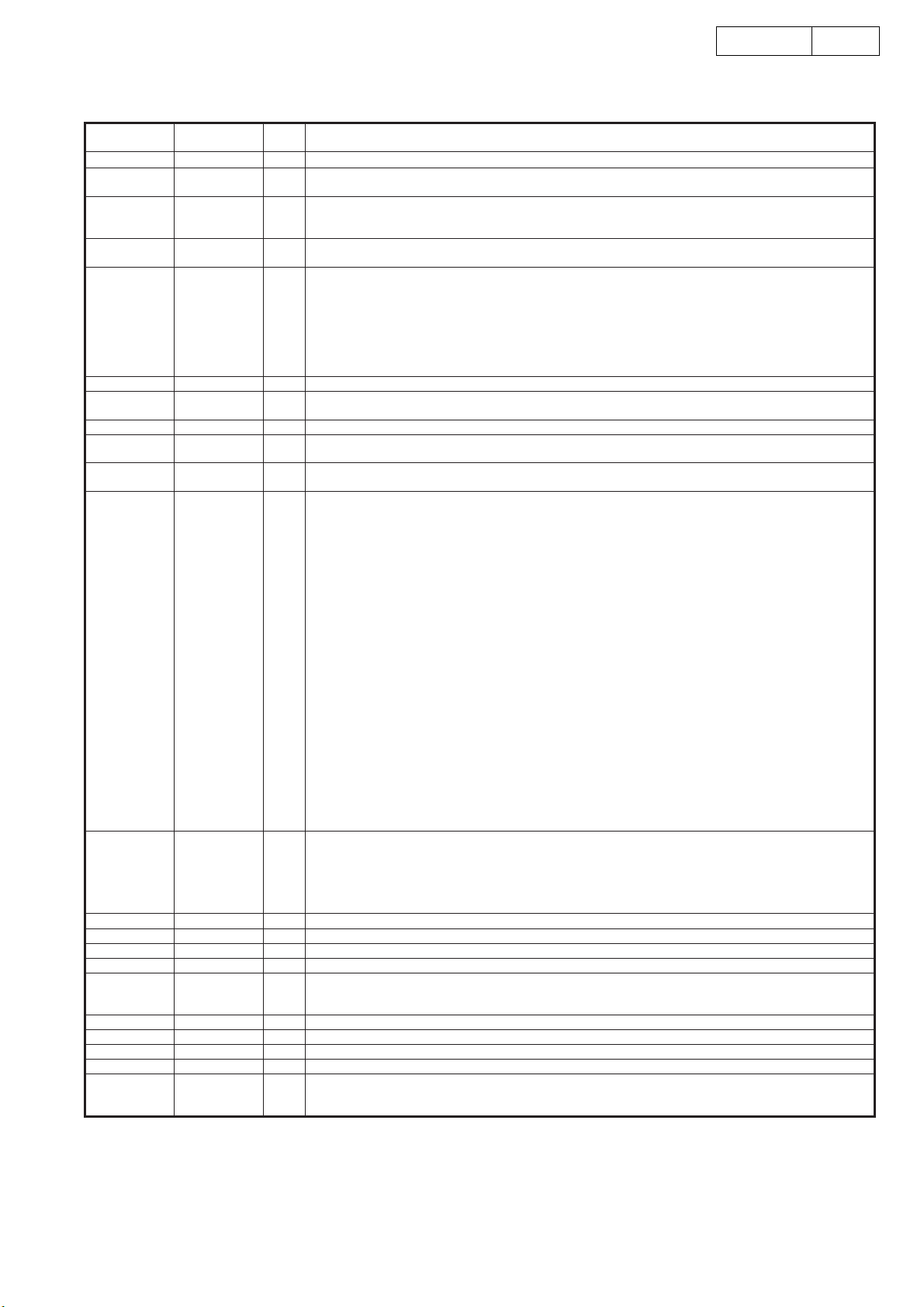

Page 2

SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

LEAKAGE CURRENT CHECK

Before returning the unit to the customer, make sure you make either (1) a leakage current check or (2) a line to chassis

resistance check. If the leakage current exceeds 0.5 milliamps, or if the resistance from chassis to either side of the

power cord is less than 460 kohms, the unit is defective.

LASER RADIATION

Do not stare into beam or view directly with optical instruments, class 3A laser product.

500V

2DN-S3000

(1)

(2)

1M

(1)

(2)

2

Page 3

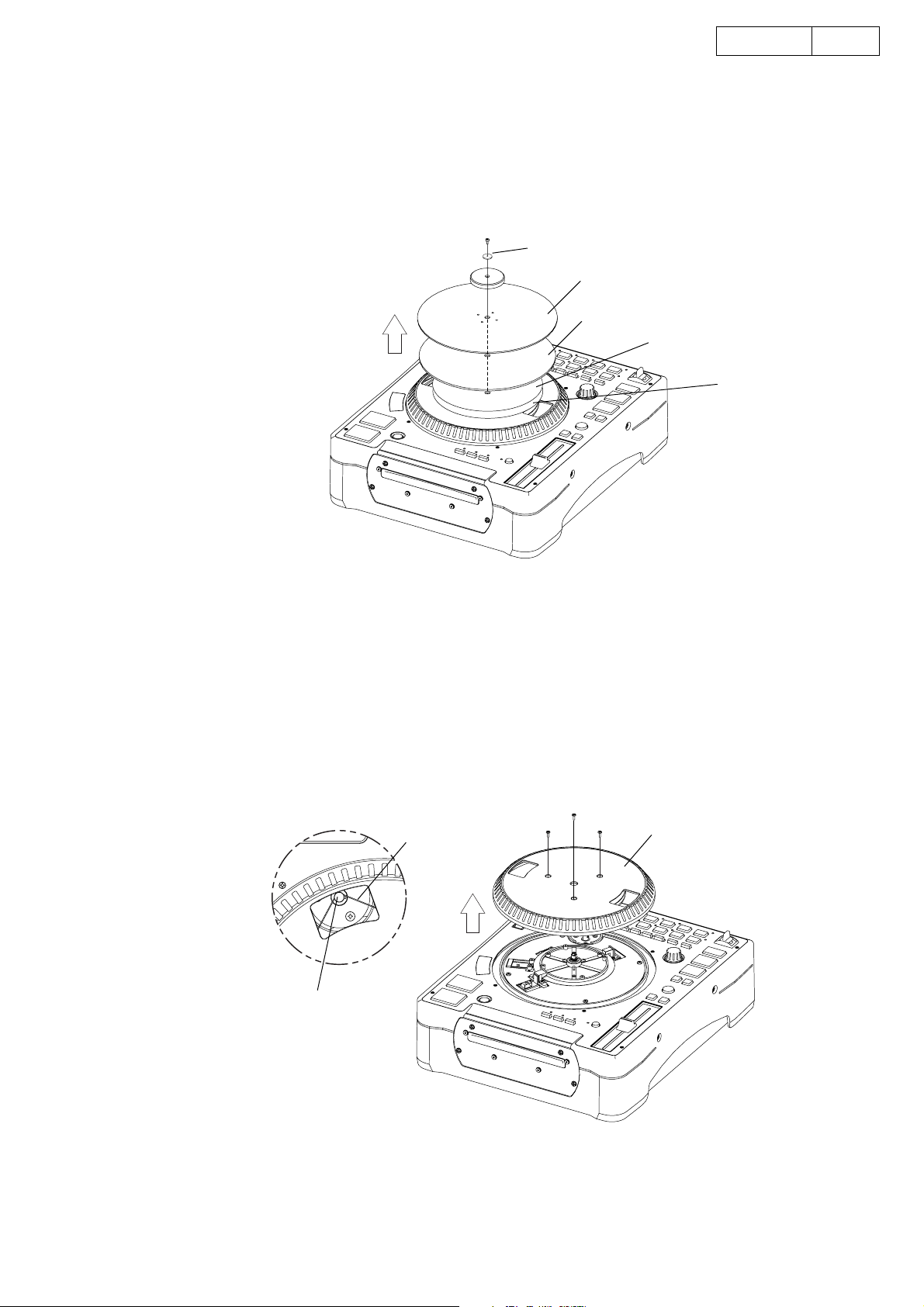

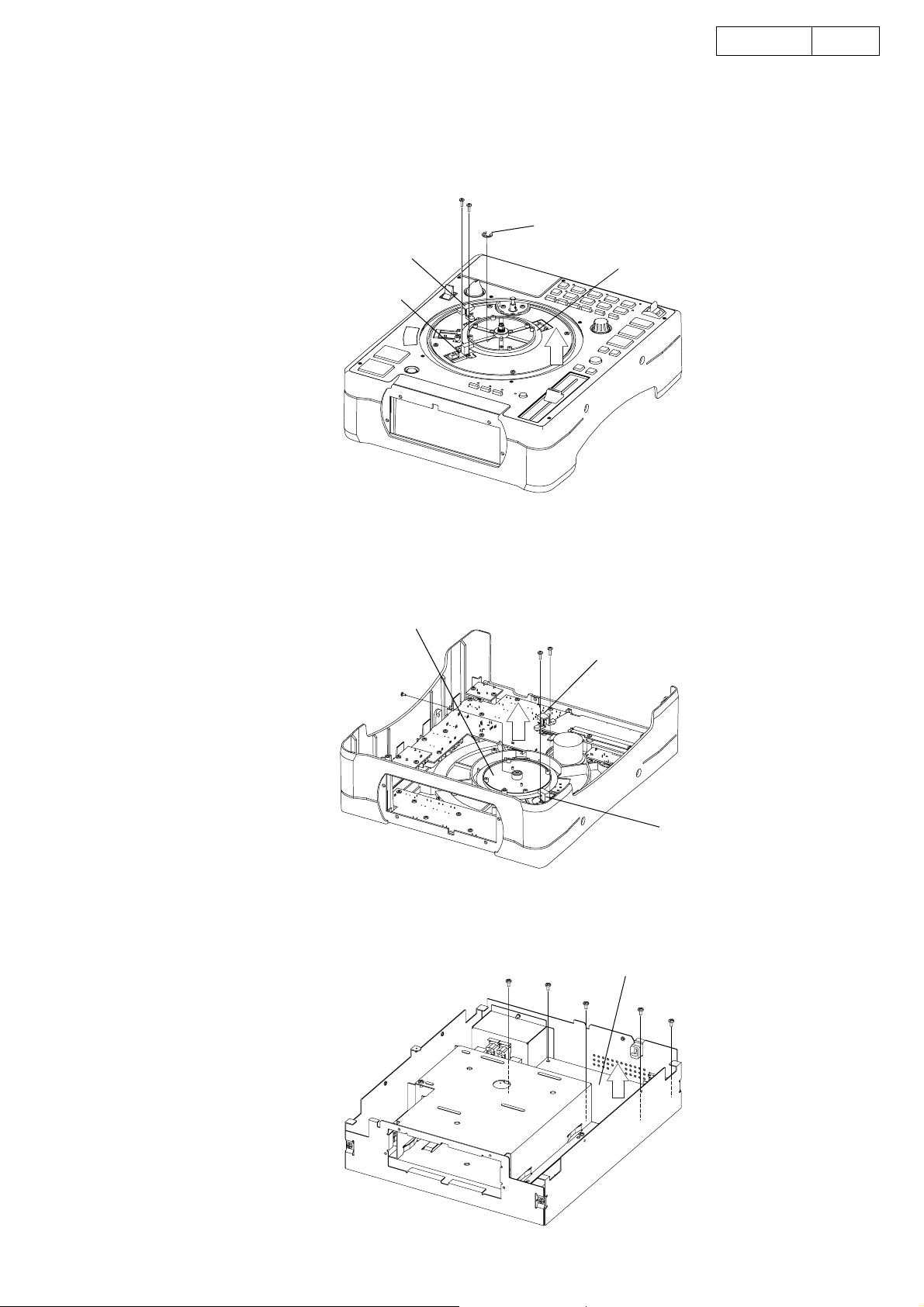

DISASSEMBLY

(Follow the procedure below in reverse order when reassembling.)

1. SLIP DISK, SLIP MAT

(1) Remove a screw and pull out Slip Disc and Slip Mat.

.

3DN-S3000

Washer

Slip Disc

Slip Mat

Slip Sheet

Anti-static Sheet

2. PLATTER

(1) Remove Belt from Motor Pully.

(2) Remove 3 screws and pull out Platter.

.

Motor Pully

Belt

Platter

3

Page 4

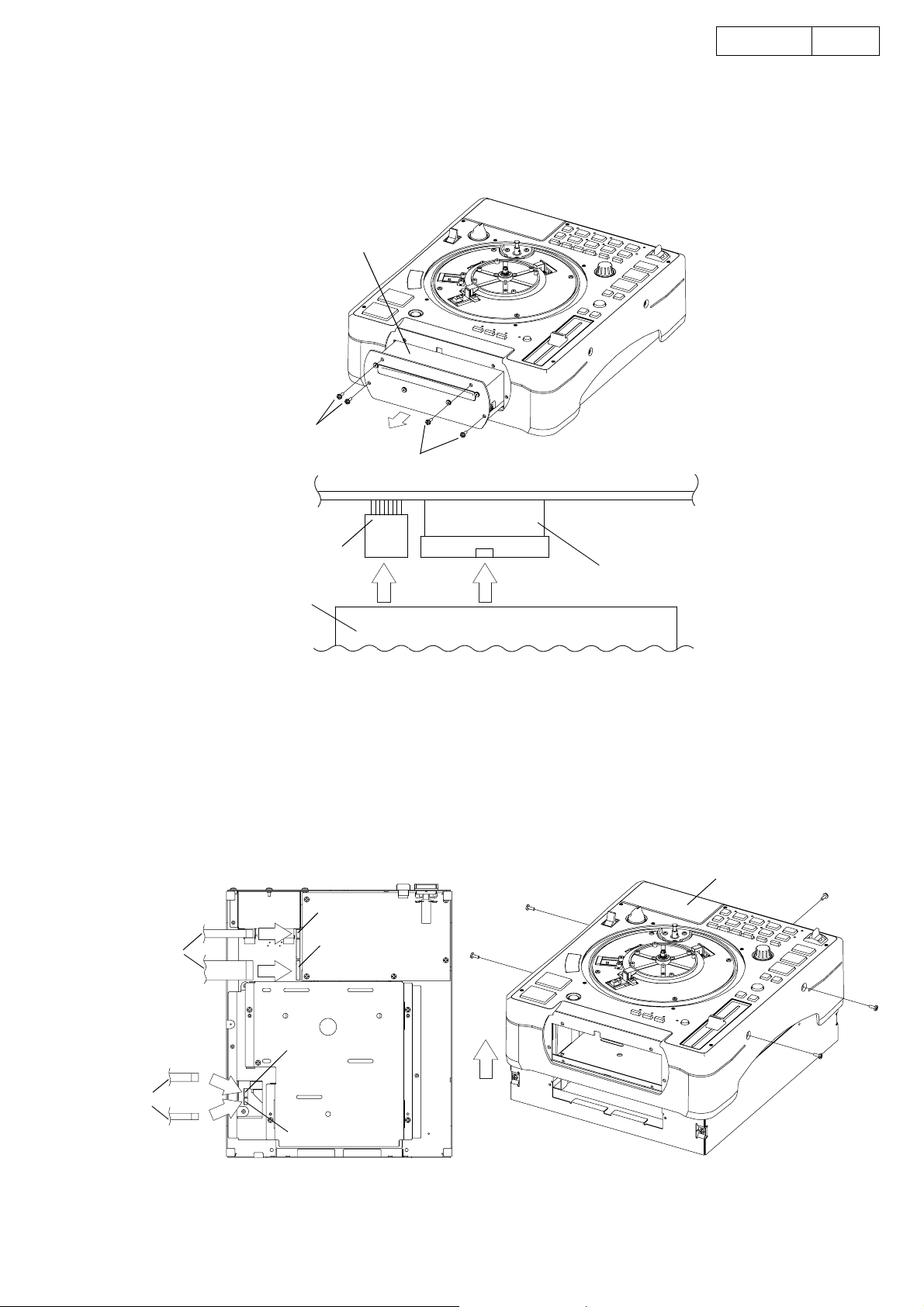

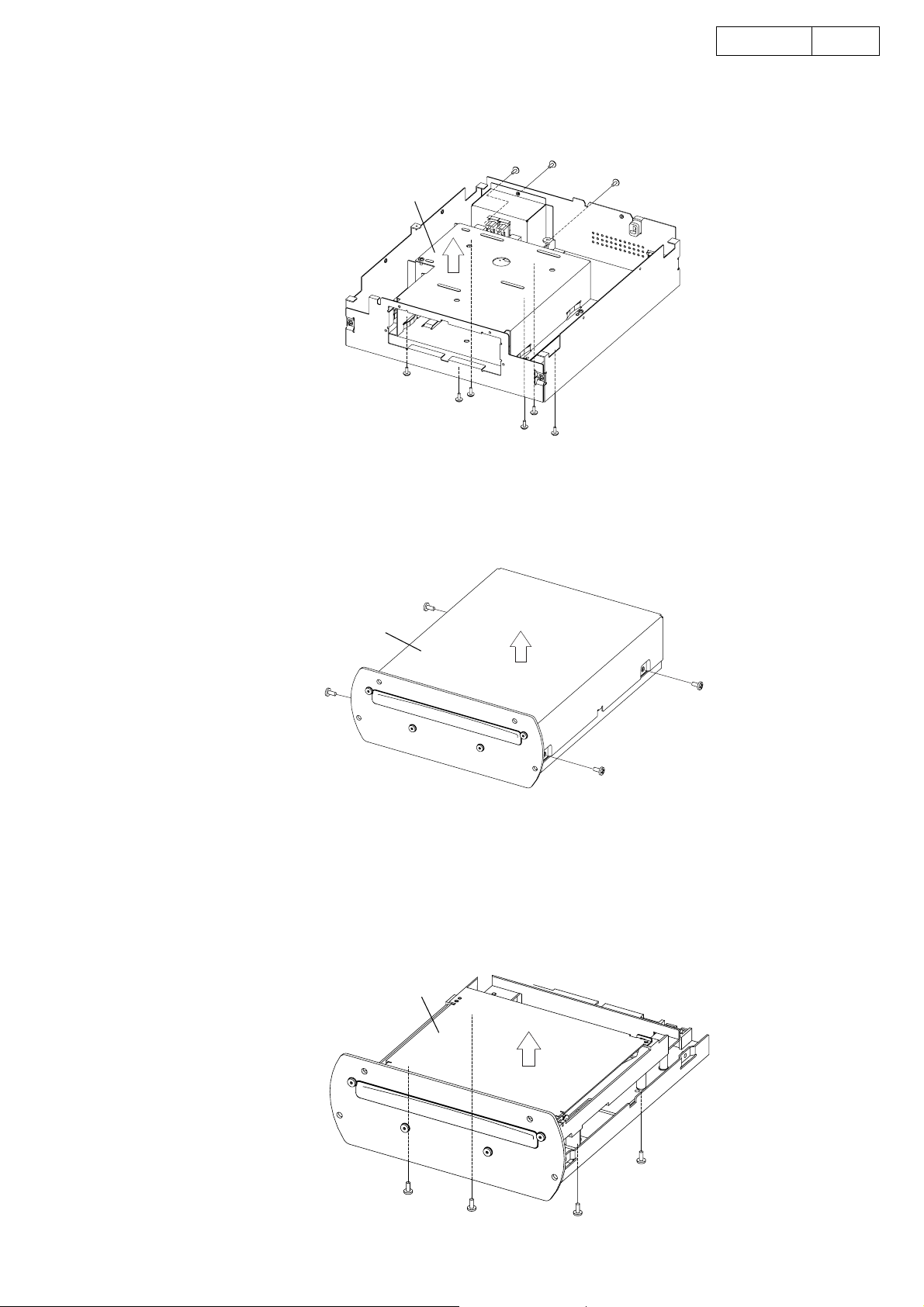

3. DRIVE UNIT

(1) Remove 4 screws and pull out Drive Unit.

(2) Disconnect Flat cable and Connector.

(3) Detach Drive Unit.

Drive Unit

71

4DN-S3000

71

Connector

Flat cable

Drive Unit

Note:

z Do not pull out aslant to prevent Flat cable damage.

z Do not fail to pull AC cord from wall outlet before disconnect the Flat cable and Connector.

If AC cord is remained plugged into wall outlet, power is kept supplied in the unit, which may cause danger.

4. COVER UNIT

(1) Remove 5 screws and pull out Cover Unit.

(2) Disconnect Connectors.

(3) Detach Cover unit.

CX042

Connector

CX101

Cover unit

CX041

Connector

CX031

Note:

z Do not fail to pull AC cord from wall outlet before disconnect Connectors.

If AC cord is remained plugged into wall outlet, power is kept supplied in the unit, which may cause danger.

4

Page 5

5. SENSOR AND SCALE UNITS OF PLATTER

(1) Remove 2 screws and pull out Sensor Cover and Sensor unit.

(2) Remove a E Ring.

(3) Pull out Scale unit.

5DN-S3000

E Ring

Sensor Cover

Sensor unit

6. SENSOR AND SCALE UNITS OF SLIP DISC

(1) Remove 2 screws and pull out Sensor Cover and Sensor unit.

(2) Remove a screw and pull out Scale unit.

Scale unit

Scale unit

Sensor Cover

7. POWER PWB

(1) Remove 5 screw and pull out Power PWB.

Sensor unit

Power PWB

5

Page 6

8. DSP PWB UNIT

(1) Remove 9 screws and pull out DSP PWB unit.

DSP PWB unit

9. DRIVE COVER

(1) Remove 4 screws and pull out Drive cover.

6DN-S3000

Drive cover

10. DRIVE

(1) Move Drive Rack in arrow direction through the Hole on the bottom chassis.

Loader frame comes out.

(2) Pull up Loader panel while pulling it towards front.

(3) Remove 4 screws and pull out Drive.

Drive

6

Page 7

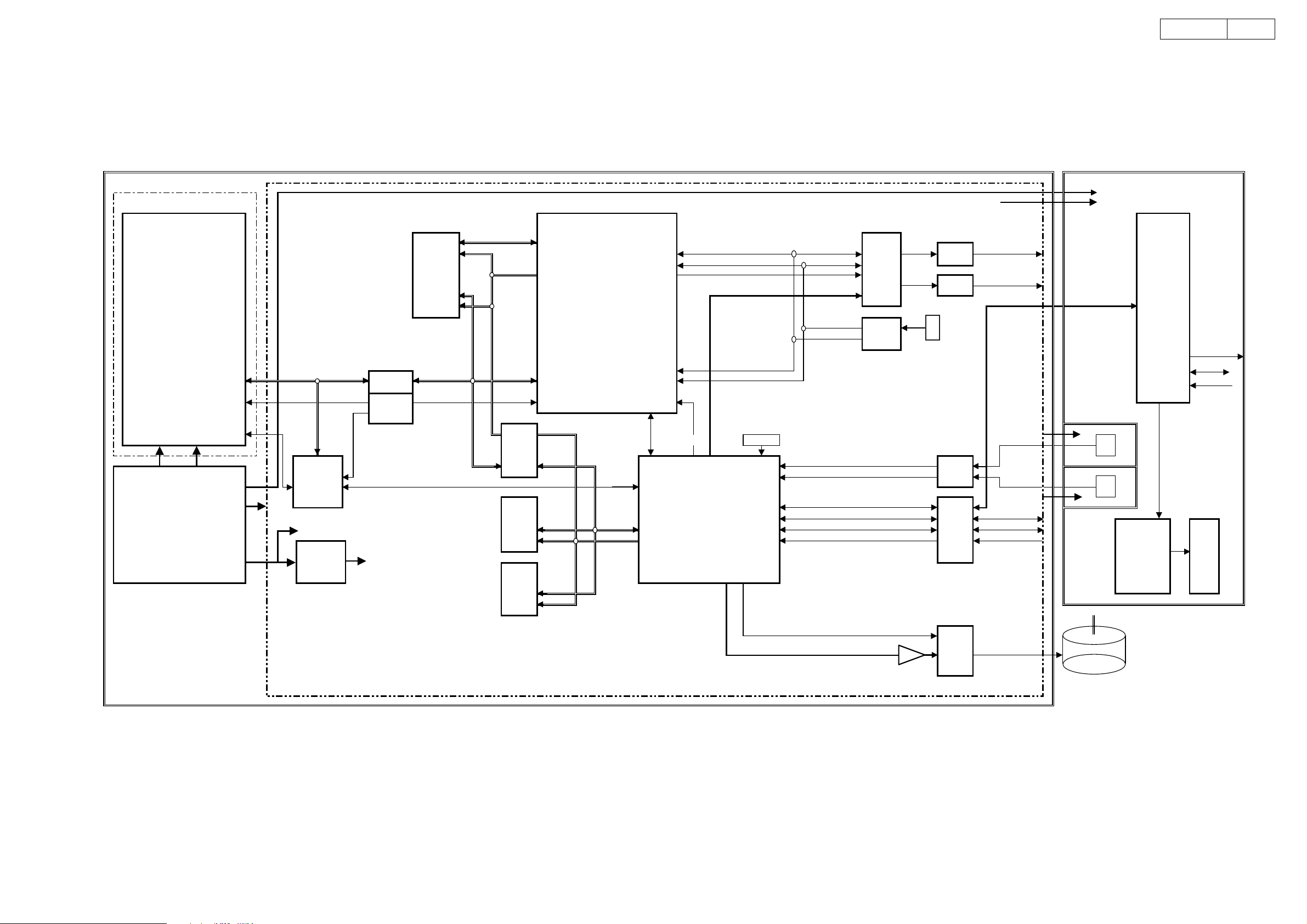

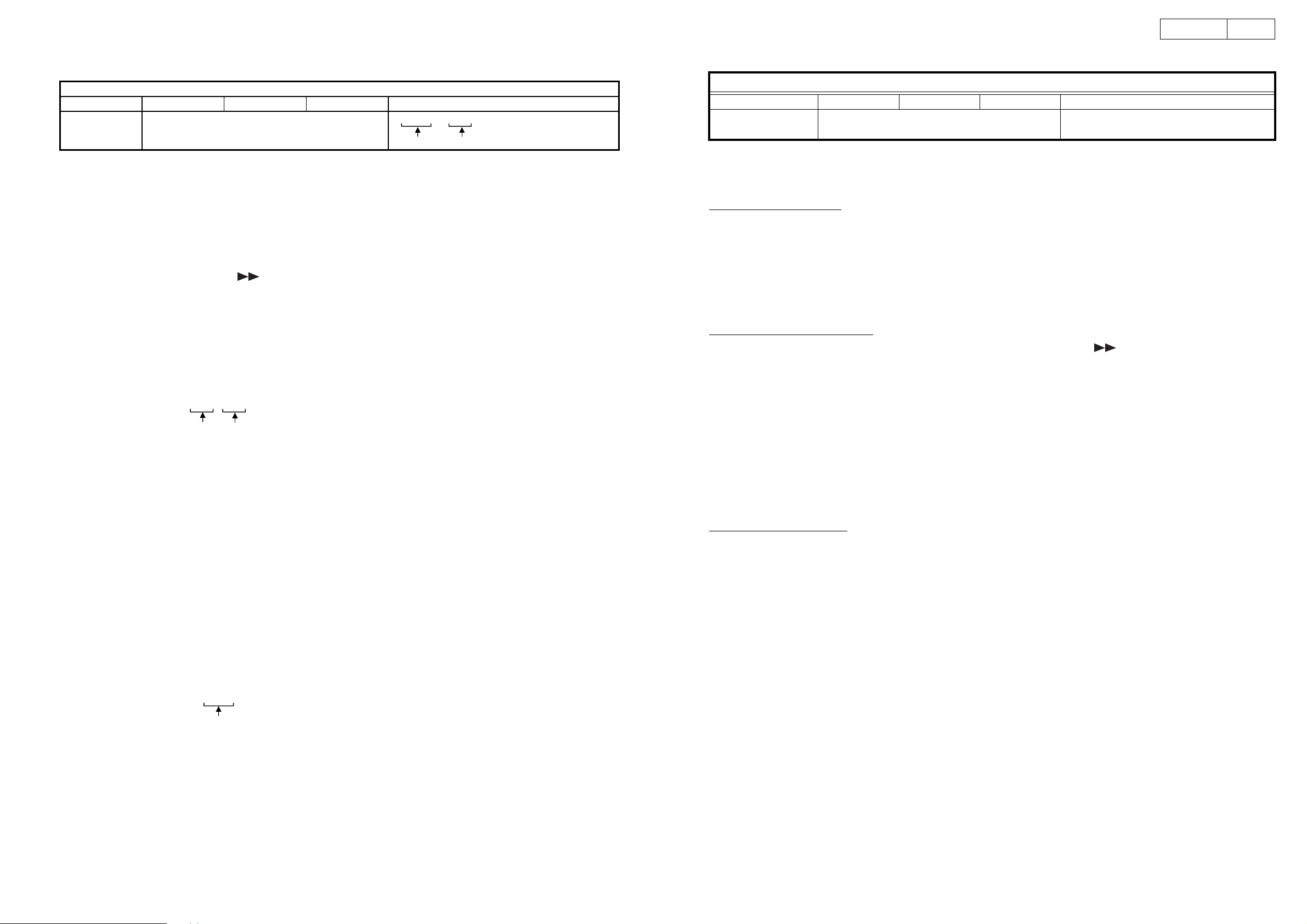

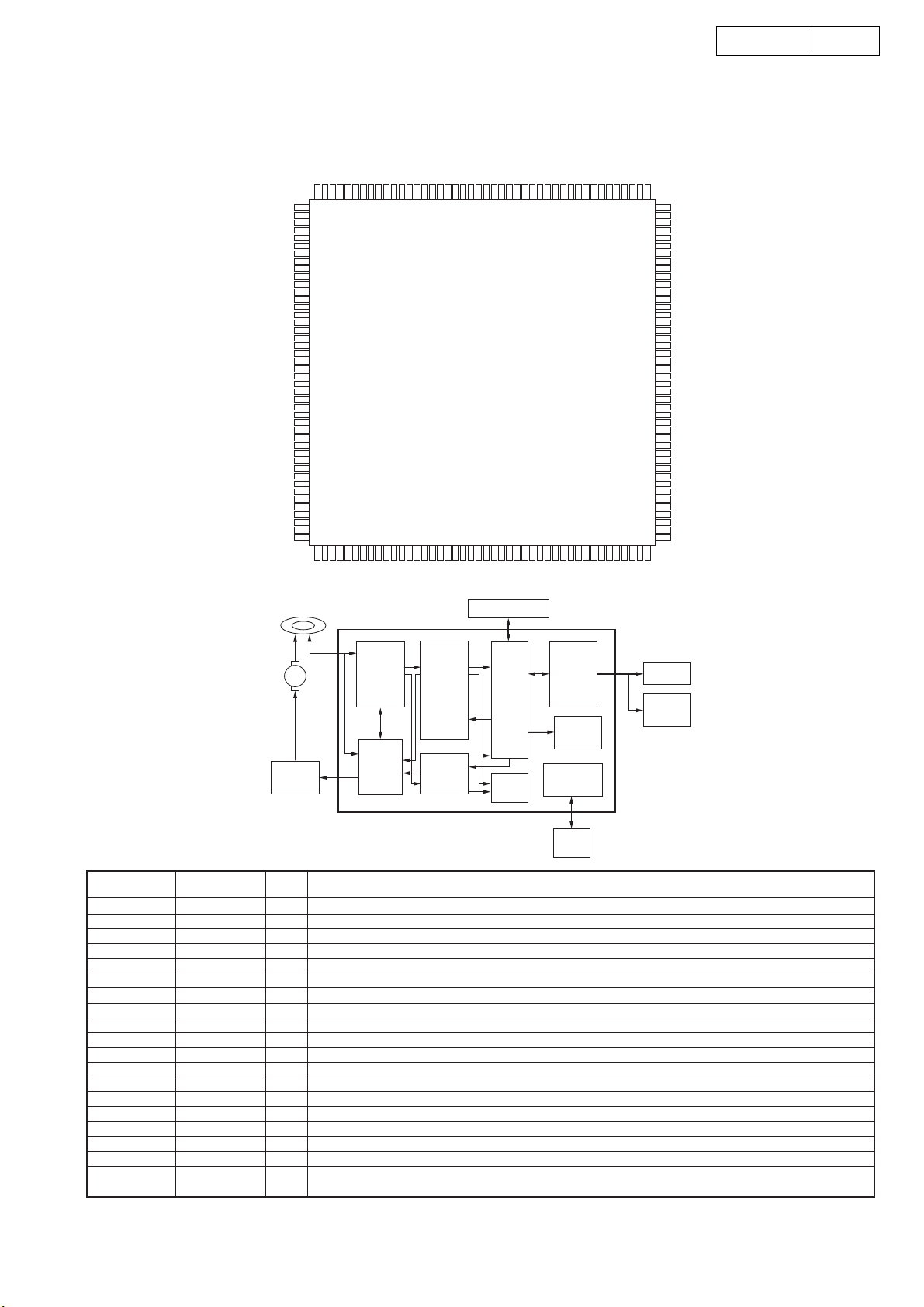

BLOCK DIAGRAM

DN-S3000

7DN-S3000

-HB,F1,F2

GND,+5

ROM

DRIVE

ATAPI

INTERFACE

9V 5.0V

SWITCHING

POWER SUPPLY

ATAPI

interface

-HB,F1,F2

±9.0V

5.0V

Interface

TMP86CM47U

5.0V

ATAP

CPU

Ragurater

128M

D16~31

SDRAM

RAM

32bit BUS

ADRESS

ADSP21065L

TXD0A

TXD0B

DSP

SHOCK PROOF

TXD1B CLOCK TMP86CM47U

BUS

select TXD1A

16Bit Bus TCK1

D0~D15

DMA

D0~15

CPU DSP 32.0M 32.0M 5v

BUS

interface

micon SERIAL 2

8M

FRASH

memory

3.3V

memo

4M

FRASH D/A

memory

RAM control

D0~D16

ADRESS

TFS0

TCK0

TFS1

FLAG

CONTROL

SYSTEM

CPU

MN102H730F

RAM10K

LRCK

BCLK

MAIN

D/A

DIT

AK4353

AMP

Trans

analog out

digital out

MAIN DOUT

256fs

DISC RV PULSE DISC

URN TABLE DIR TURN TABLE

SERIAL 1

UART

FW PULSE

UART

SERIAL 3

UART

DRIVER

PANEL

X'EFFECT IN

X'EFFECT OUT

3.3-5V FADER

adress

5v

DISC

SENSORSENSOR

TURN TABLE

ML9207

PANEL

µcom

ROM32k

RAM1k

LED out

Key scan

VR in

HB

FLTFLT Driver

CONTROL

motor

driver

Motor

7

Page 8

8DN-S3000

CONFIRMING THE SERVO

Required Measuring Implement

z Reference disc (TCD784 or CO-74176)

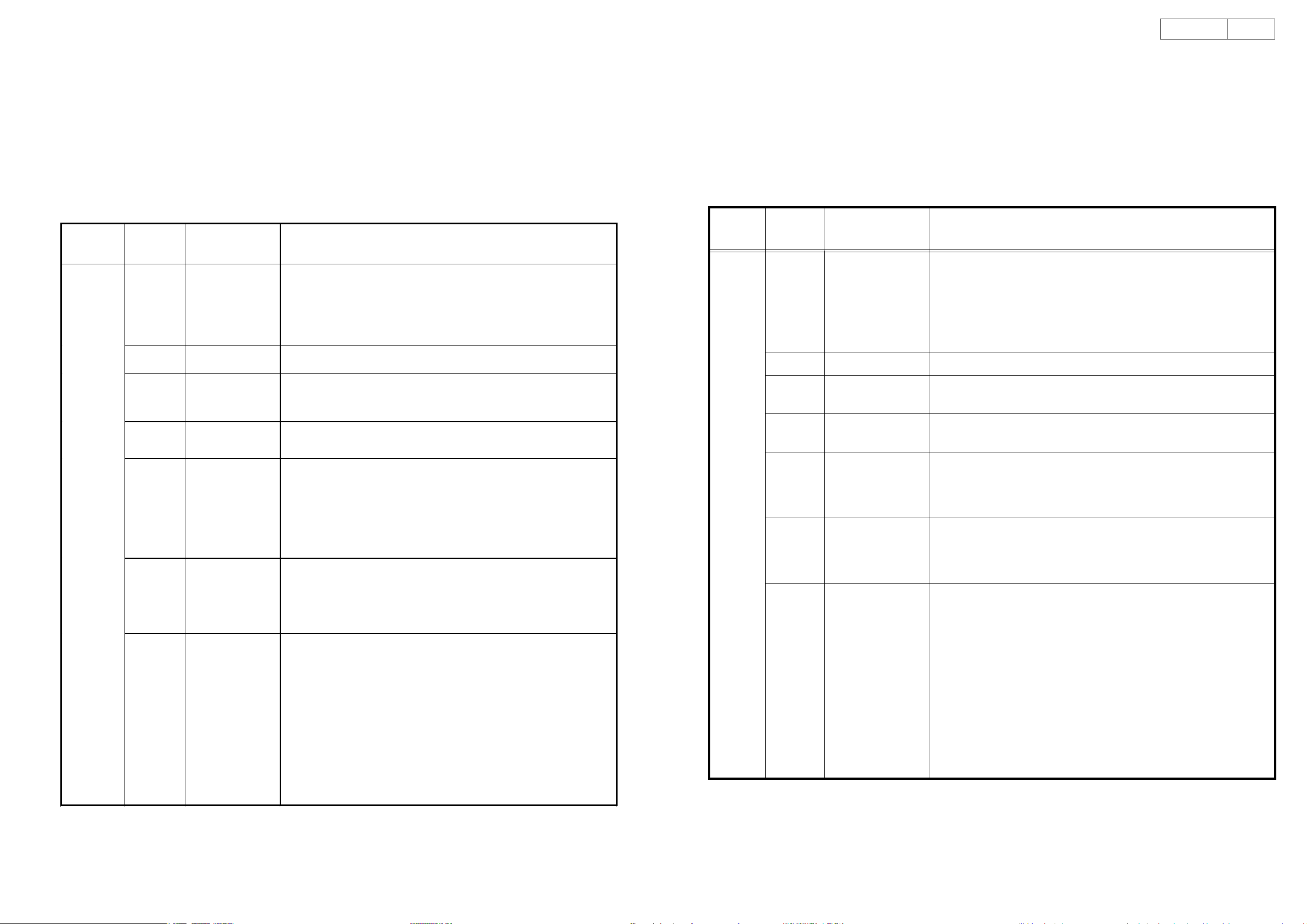

1. What is Service Program

Service program is a special program intended for confirming servo functions etc.

2. Contents of Service Program

Switch on the power while pushing the PITCH BEND + button and SCRATCH MODE button at the same time. After actuating

the servo program, select an aiming process number with the SELECT knob, A button, B button, SAMP button, or SAMP B

button. Press the SELECT knob to execute the selected process, the process number is then displayed on the track indicator

of the display. To exit from the service program, just switch off the power.

Process No.

(TRACK

Indication)

01

02

03

04

05

SELECT knob

06

07

Function

(Character-display)

com Version check

(Version No.)

OPEN/CLOSE

(Open Close)

Drive Diagnostic

(Drive_Diag)

Drive Data Read

(Data Read)

Error Code Check

(Error Data)

Total Running Time

(Total_Time)

Automatic

Servo Adjustment

call

Contents

Check Version with JOG dial.

1. System com version No.: “Sys_XXXX ”

2. DSP soft version No.: “Dsp_XXXX ”

3. ATAPI com version No.: “Atapi_XXXX ”

4. PANEL com version No.: “Panel_XXXX

5. ROM drive mecha. com version No.: “Drive_XXXX ”

Performs open/close each time when the SELECT knob is pushed.

ROM drive performs operation check when the SELECT knob is pushed, and

indicates the operational result. If the disc holder open, it starts the operation check

after closing. It indicates “Normal_End” if it ends normal. In case of error, ROM

drive error code is displayed in the character’s lower portion as “E

Starts continuous playback at its maximum reading speed from the beginning of

disc when the SELECT knob is pushed. It halts reading and stops if the knob is

pushed again.

Turn the PLATTER to display the logging error codes in the occurred order.

(“Error Data” is displayed.)

10 error logs are memorized at maximum.

Kinds of Error Code, displayed

Error Code Table (Appears only at Heat Run and Chucking Test function)

Pressing SELECT knob enters to data erase mode. (“Err Clear?” is displayed.)

If the SELECT knob is pushed again, the memorized error data are cleared.

Total time span of servo function that counted by the hour is displayed.

(“Total Time” is displayed.)

The display time is less than 65535 hours.

Note: No time is counted if powered down within 59 minutes.

Pressing SELECT knob enters to data erase mode. (“Time Clear?” is displayed.)

If the SELECT knob is pushed again, the memorized time data are cleared.

Starts automatic servo adjustment when the SELECT knob is pushed, and after

completing the adjustment, sort of the used disc is indicated. Data is selectable with

the PLATTER.

1. Disc check, CD/CD-RW

2. Focus gain data

3. Focus balance data

4. Focus offset data

5. Tracking gain data

6. Tracking balance data

7. Tracking offset data

8. PreAMP Tracking Sensor Gain

9. DSP Tracking Sensor Gain

10. PI offset

”

”.

****

サービスモード

サービスモードは、サーボ状態などを確認するための特別なプログラムです。

1. サービスプログラムの内容

PITCHBEND +ボタンと SCRATCHMODE ボタンを両方押しながら、電源を投入するとサービスモードになります。パラメータノブで各チェック項目

が、A ボタン ,B ボタン ,SAMP ボタン , または SAMPB ボタンで各テスト項目が選択できます。パラメータノブを押すか、PLAY/PAUSE ボタンを押すと各

項目のチェック、テストを開始し、その結果を表示します。

サービスモードをキャンセルするには、電源を切ってください。

*リファレンスディスク:TCD784、CO-74176

チェック項No.

( トラック番号 )

01 マイコンバージョンチェツク

02 CDEJECT パラメータノブを押すと CD の EJECT/LOAD が選択できます。

03 CD ドライブチェック

04 ドライブデータリード

05 エラーコードチェック

パラメータノブ

06 トータルランニングタイム

07 サーボ自動調整値

機能

キャラクター表示

VersionNo

(DriveDiag)

(DataRead)

(ErrorData)

(TotalTime)

読み出し

(ServoData)

内容

スクラッチディスクを回して、バージョンをチェックします。

1.システムマイコンバージョン No:"SysXXXX"

2.DSP ソフトバージョン No:"DspXXXX"

3.ATAPI マイコンバージョン No:"AtapiXXXX"

4.パネルマイコンバージョン No:"PanelXXXX"

5.CD ドライブマイコンバージョン No:"DriveXXXX"

パラメータノブを押すと CD ドライブの動作チェックを開始します。終了すると結果を表示し

ます。OK のときは NormalEnd が表示されます。

パラメータノブを押すと、データリードを開始し再生を開始します。再度、パラメータノブを押

すと、データリードを停止し、再生を停止します。

通常動作時、発生したエラーのエラーコードが表示されます。ディスクを回すと、最大 10 個

まで、記憶されたエラーデータが選択できます。( エラーコードはエラーコード表を参照下さい。)

・パラメータノブを押すと、エラーデータ消去モードになります。(ErrClear?が表示されます )

再度、パラメータノブを押すと、全てのエラーデータが消去されます。

スピンドルモータのトータル動作時間を表示します。1 時間単位で 65535 時間まで計測でき

ます。注意 )59 分以下で電源を切るとカウントされません。

・パラメータノブを押すと、トータル時間消去モードになります。(TimeClear?が表示されま

す ) 再度、パラメータノブを押すと、トータル時間が消去されます。

パラメータノブを押すとサーボ自動調整を開始します。調整が終了すると、調整データ表示

します。データはスクラッチディスクを回すことで選択できます。

1. ディスクチェック、CD/CD-RW

2. フォーカスゲインデータ

3. フォーカスバランスデータ

4. フォーカスオフセットデータ

5. トラッキングオフセットデータ

6. トラッキングバランスデータ

7. トラッキングオフセットデータ

8. プリアンプトラッキングセンサーゲイン

9.DSP トラッキングセンサーゲイン

10.PI オフセット

8

Page 9

3. TEST MODE

Process No.

(TRACK

Indication)

A button

B button

SAMP

button

SAMP B

button

-

-

-

-

Adjustment Item

Adjustment Value indication at

character portions.

1 Focus Gain 35 ~ 120

2 Focus Balance

3 Focus Offset

-20 ~ +20

-20 ~ +20

4 Tracking Gain 35 ~ 120

5 Tracking Balance

6 Tracking Offset

-20 ~ +20

-20 ~ +20

* Reference data.

Function

(Character-display)

Heat Run

(H/R1_Normal)

Chucking Test

(H/R2_Tray)

System check

(Sys._Check)

Starting with the PLAY/PAUSE button, it repeats open/close of the tray and

playback.

All tracks are played back if the track count is less than 20. Only the first and last

tracks are played back if the tracks are more than 21. When any errors, it stops

and indicates error code (see Error Code Table).

Starting with the PLAY/PAUSE button, it repeats open/close of the tray, servo on,

and TOC read.

The display shows the number of the tray operation. When any errors, it stops and

indicates error code (see Error Code Table).

It starts system check when the PLAY/PAUSE button is pushed, and indicates the

status by performing plain operational check in the system .

1. Communication judge between the system com and DSP

2. DSP SDRAM write/read operation check

3. Communication judge between the system com and ATAPI com

4. Communication judge between the ATAPI com and ROM drive

5. ROM drive operation check

After finishing the check, it indicates the result on the character display lower

portion.

When the 1. ~ 5. items are OK, their item numbers are indicated.

But if there is a NG item, its item number is not indicated.

Judges whether PLATTER can rotate at the specified rotating speed.

The message "Platter_OK" is displayed on the character display if the rotating

speed meets the specification. Otherwise, "Platter_NG" is displayed.

Contents

サーボ自動調整読み出し値

サーボ調整項目 調整 OK 範囲

1 フォーカスゲイン 35 〜 120

2 フォーカスバランス -20 〜 +20

3 フォーカスオフセット -20 〜 +20

4 トラッキングゲイン 35 〜 120

5 トラッキングバランス -20 〜 +20

6 トラッキングオフセット -20 〜 +20

2. テストモード

機能キャラクター表示 内容

A ボタン ヒートランテスト

H/R1Normal

A1 ボタンを押し、PLAY/PAUSE ボタンを押すとテストを開始します。

ディスクの出し入れと、再生を繰り返します。

20 トラック以下のディスクのときは、全てのトラックを再生します。

21 トラック以上のディスクのときは、ディスク先頭トラックと最終トラックのみ再生します。エラーが発生すると、エラーコード

を表示して停止します。

B ボタン チャッキングテスト

H/R2Tray

A2 ボタンを押し、PLAY/PAUSE ボタンを押すとテストを開始します。

ディスクの出し入れと、サーボ投入、TOC の読み込みを繰り返します。

エラーが発生すると、エラーコードを表示して停止します。

SAMP ボタン システムチェック

Sys.Check

A3 ボタンを押し、PLAY/PAUSE ボタンを押すとシステムチェックを開始し、チェック終了後、その結果を表示します。

1. システムマイコンと DSP の通信チェツクを行います。

2.DSP が SDRAM のリード / ライトチェツクを行います。

3. システムマイコンと ATAPI マイコンの通信チェツクを行います。

4.ATAPI マイコンと CD ドライブの通信チェツクを行います。

5.CD ドライブの動作チェックを行います。

全てのチェックが終了すると、キャラクター表示に結果を表示します。1 〜 5 項目のチェックが OK の時は、OK に

なった項目の番号が表示されます。NG の項目が合った場合、NG になった項目の番号が表示されま

せん。

SAMPB ボタン プラターチェック

PlateCheck

A4 ボタンを押し、PLAY/PAUSE ボタンを押すとプラターの回転チェックを開始し、チェック終了後、その結果を表示

します。プラターの回転をチェツクし OK のとき "PlatterOK" を表示します。NG のとき "PlatterNG" を表示

します。

3. エラーコードテーブル ( ヒートランテスト、及び、チャッキングテストのとき表示されます )

9DN-S3000

4. Error Code Table (Appears only at Heat Run and Chucking Test function)

Error Code Contents

Automatic Adjustment Error

E1 00

E1 01

E1 03

E1 04

E1 05

E1 06

E2 02 Servo down during automatic adjustment

E3 00 Unable to read TOC

E4 00

E4 01

E5 00 Slide error

Unable to detect disc

Unable to adjust tracking offset

Unable to adjust focus fine gain

Unable to actuate focus

Unable to actuate tracking

Unable to adjust tracking fine gain

Unable to close the disc holder in the regular time

Unable to open the disc holder in the regular time

エラーコード

内容

サーボ自動調整エラー

E100

E101

E103

E104

E105

E106

ディスクが検出できない。

トラッキングオフセットが調整できない。

フォーカスゲインが調整できない。

フォーカスサーボが入らない。

トラッキングサーボが入らない。

トラッキングゲインが調整できない。

E202 サーボ自動調整中サーボが外れた。

E300 TOC が規定時間内に読めない。

E400

E401

ディスクが規定時間内にローディングできない。

ディスクが規定時間内にイジェクトできない。

E500 スライドエラー

9

Page 10

Detailed error can be displayed by PLATTER when error occurs.

10DN-S3000

Error Indication

TR MIN SEC FRAM CHARACTER

Displays the track

No. in which error

occurred.

Displays the time at which error occurred. “H

Operation count Error code

* * * *E * * *

”

5. System µcom and DSP Version Upgrade

System µcom and DSP can be upgraded in the following manner.

Version Upgrade Method

(1) Record the version upgrade software on a CD-R or CD-RW disc, only as one file with the format ISO9660 Mode-1.

The file name of the supplied version upgrade software should be used as is and this disc needs to finalize.

(2) After loading the disc made in above step 1, turn off the power. Then, turn on the power while pressing the NEXT TRACK

button and FAST SEARCH FWD ( ) button. The version upgrade starts with reading data of the disc.

(3) When you start version upgrade operation, messages "Version_Up" and "System&DSP" are displayed on the character dis-

play.

Recovery positions are turned on one by one from the left end according as the upgrade operation proceeds. When this operation is completed, all recovery positions are turned on.

In case of some error or the power is turned off during the version upgrade, it may be impossible to operate at all thereafter.

Changing of IC502 on GU-3546 is necessary in this case, and software writing to IC502 should be done beforehand.

(4) When the upgrade is completed, the disk is ejected and operation returns to the normal mode.

(5) File name of the upgrade software indicates version numbers.

File name T3.

System com

* * * * * *

version

. BIN

DSP version

6. ROM Drive (FG-5000) µcom Version Upgrade

Drive (FG-5000) µcom can be upgraded in the following manner.

Version Upgrade Method

(1) Record the version upgrade software on a CD-R or CD-RW disc, only as one file with the format ISO9660 Mode-1.

The file name of the supplied version upgrade software should be used as is and this disc needs to finalize.

(2) After turning on the power, load the disc made in above step 1 into the mecha. you want to upgrade the version.

(3) "Drive" and "Version UP?" are indicated in the character display. Press the CD EJECT button and remove the disc when not

upgrade the version.

(4) Press the PLAY/PAUSE to start the version upgrade. "Now Loading" is indicated.

(5) When the version upgrade is finished, "Complete" is indicated and the disc EJECT.

(6) Turn off the power once and turn on again after take out the disc.

The version upgrade ends in 20~30 seconds normally. If the power turned off underway or the version upgrade ends

abnormally, the drive may become malfunction. In such a case, version upgrade with PC will be needed.

(7) File name of the upgrade software indicates version number.

File name FG5K

* * * *

. BIN

エラー表示

トラック 分 秒 フレーム キャラクター

エラーが発生した

トラック番号

エラーが発生した時間 (A タイム ) H ****動作回数

E ****エラーコード

4. マイコンアップデート

DN-S5000 は、ディスクから、システムマイコン、DSP、CD ドライブマイコンのアップデートを行うことができます。

(1) アップデートディスクの作成

システムマイコン、DSP、ドライブマイコンのアップデート用ディスクディスクを下記に従い作成下する。

① アップデート用のソフトを、CD-R、又は CD-RW ディスクに ISO9660,MODE1 のフォーマットで記録し、ファイナライズする。

・ 配布されたアップデートファイルを、CD ライティングソフトで DISCATONCE で書き込みしファイナライズする。

・ システムマイコン (DSP を含む ) とドライブマイコンの2個のアップデートソフトを 1 枚のディスクに記録出来ます。その他のソフトやデータを同一ディスク内

に記録しないこと。

・ ファイル名は、配布されたときのファイル名をそのまま使用すること。

(2) システムマイコン、DSP のアップデート

① (1) で作成したディスクをローディングし、電源を切り、NEXTTRACK と FASTSEARCHFWD( ) ボタンを押しながら電源を入れると、

ディスクのデータを読みとりアップデートを開始します。

② アップデートを開始すると、"VersionUp"、"System & DSP" が表示されます。

アップデートの進行に合わせ、再生位置表示が左から右へ順に点灯し、終了すると、全ての表示が点灯します。

注意 ) 大変希ではありますが、アップデート中に、アップデート未終了の異常状態が発生することがあります。アップデートを開始し3分

を経過しても終了しない場合も、異常が発生したと考えられますので、電源を切って、再度、(2) ①から同一の操作を行って

下さい。

発生した異常状況により、以後の全ての動作が出来なくなることがあります。その場合、GU-3546IC502 の交換が必要にな

ります。IC502 は、予め、ソフトウエアを書き込みする必要があります。(IC502 を発注の際は、最新のシステムマイコンバージョン No(GENNo)

で発注願います。)

③ アップデートが終了すると、ディスクがイジエクトされます。

(3) ドライブマイコンのアップデート

①システムマイコンのバージョンアップに引き続き、ドライブマイコンのバージョンアップを実施する場合は、再度、ディスクをローディングします。

・ドライブマイコンのみバージョンアップする場合、電源投入後、(1) で作製したディスクを最初にローディングします。

②ドライブ用のアップデートソフトが認識されると、表示にDriveVersionUP?が表示されます。

③ PLAY/PAUSE ボタンを押すと、アップデートを開始し、NowLoading が表示されます。

④アップデートが終了すると、Complete が表示され、ディスクがイジェクトされます。

⑤電源を切って終了です。

注意 ) 大変希ではありますが、アップデート中に異常が発生することがあります。

アップデートを開始し 3 分を経過しても終了しない場合も、異常が発生したと考えられますので、電源を切って、再投入して下さ

い。

但し、アップデート開始から終了までの間に機器の電源を切った場合、又は異常が発生した場合、ドライブが動作しなくなることが

あります。その場合、パソコンからのアップデートが必要になります。そのような場合は、QA に連絡願います。

Version number

10

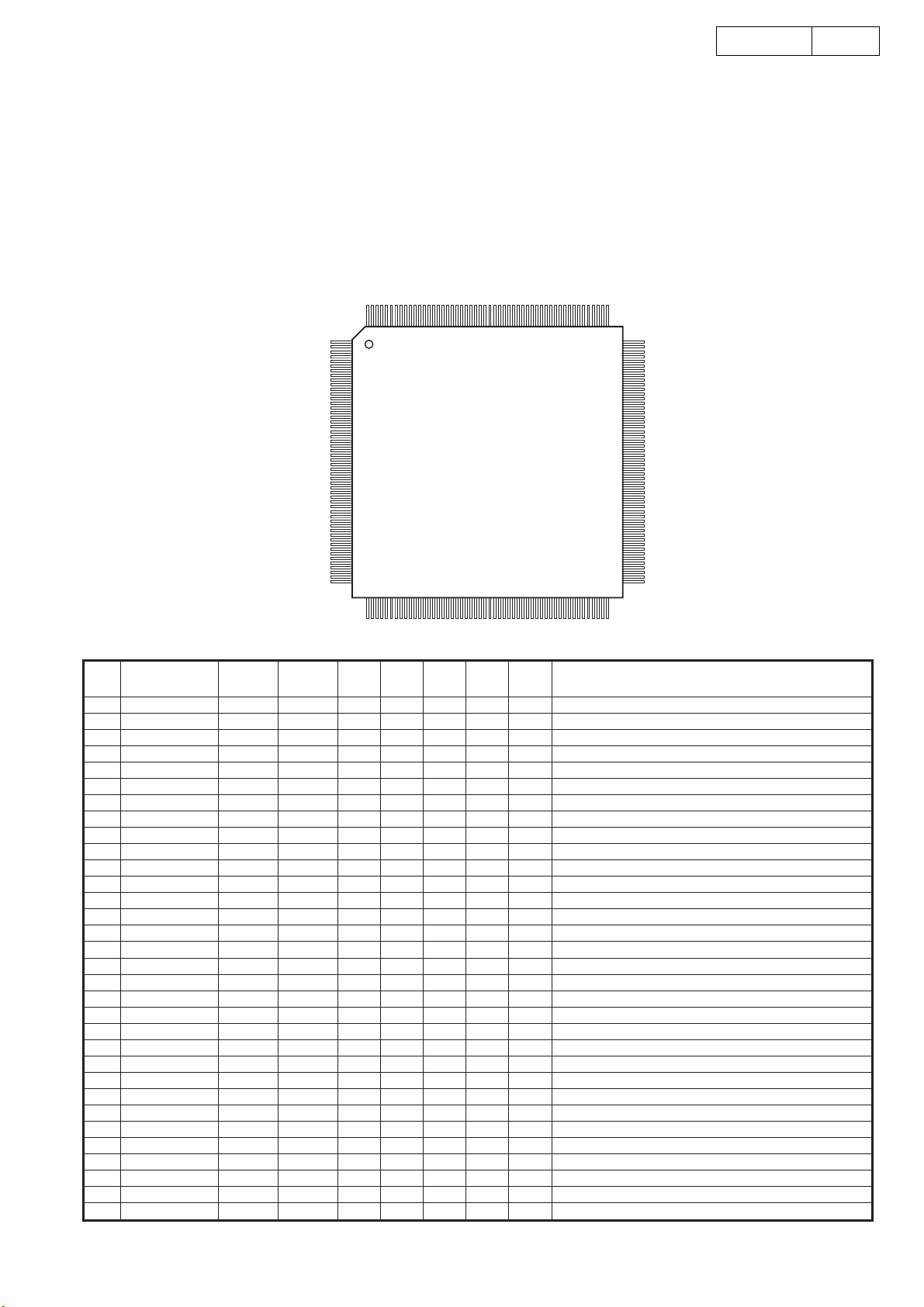

Page 11

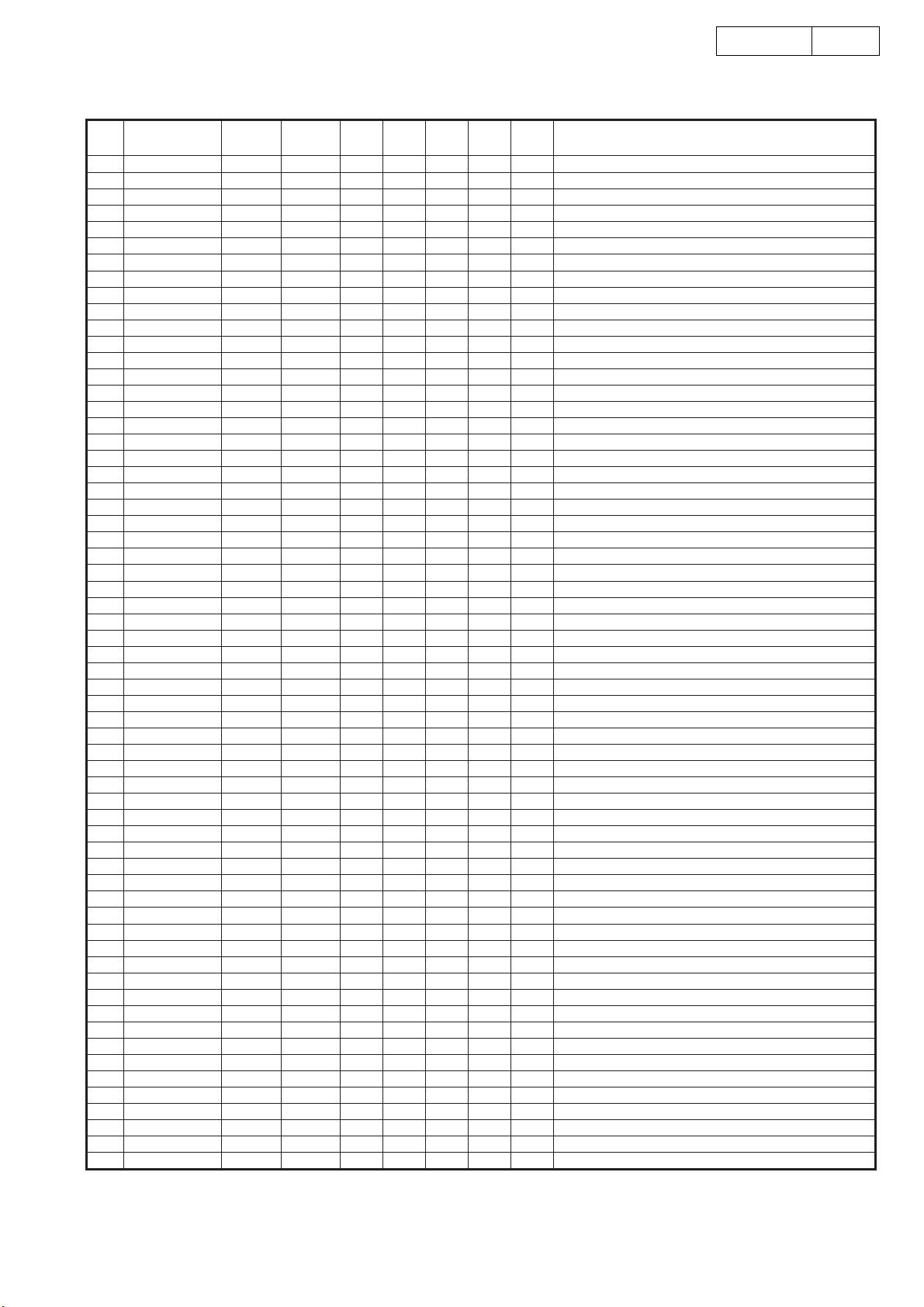

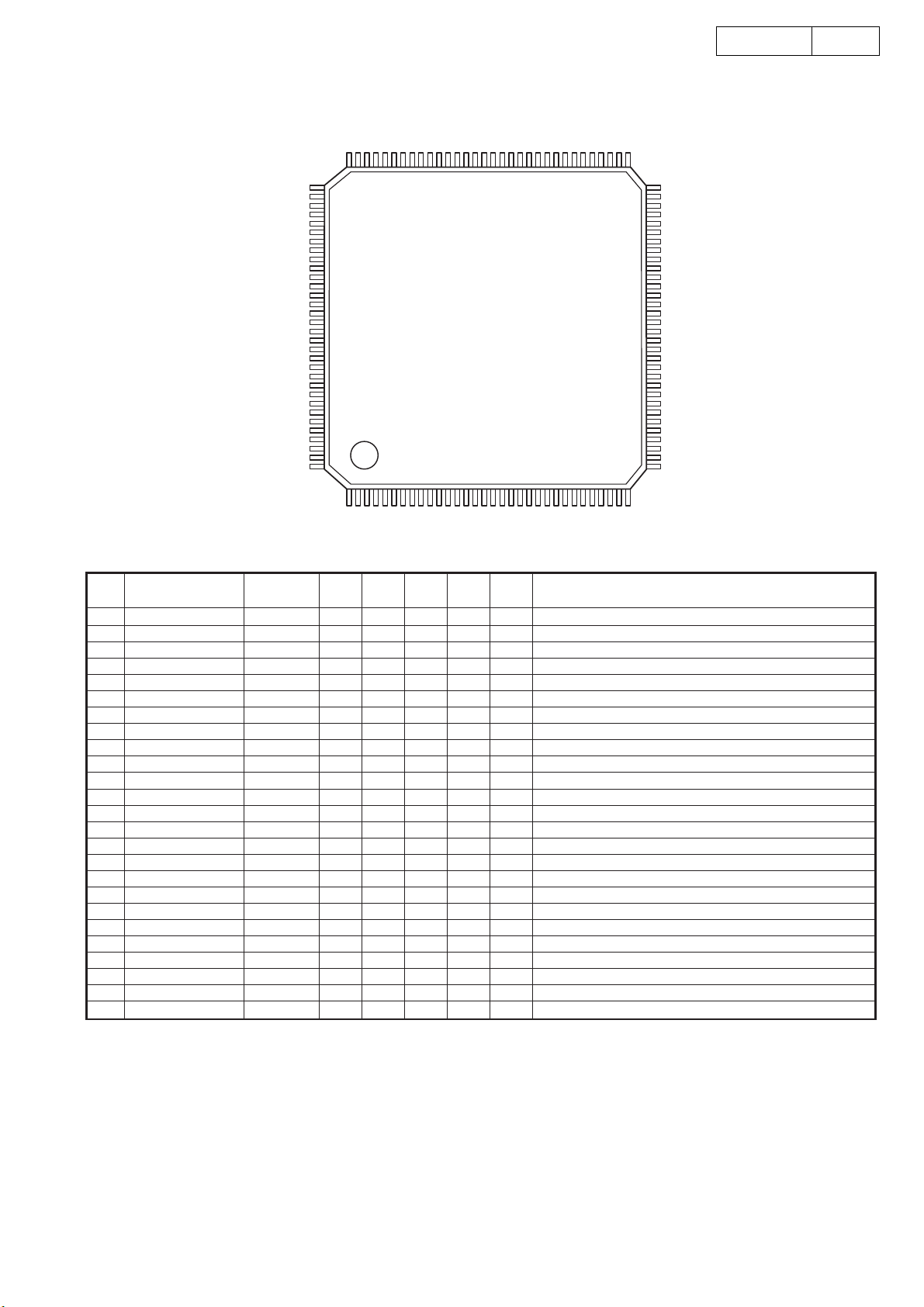

SEMICONDUCTORS /半導体一覧表

Only major semiconductors are shown, general semiconductors etc. are omitted to list.

主な半導体を記載しています。汎用の半導体は記載を省略しています。

1. IC’s

Note : Abbreviation ahead of IC No. indicates the name of P.W.B., etc.

注 ): ICNo. の前の記号は、基板の名称を表します。

DS : DSP P.W.B.

PA : PANEL P.W.B.

CD : CD-ROM P.W.B.

ADSP-21065L (DS: IC401)

208 157

11DN-S3000

156

105

52

1

TOP VIEW

53

104

ADSP-21065L Terminal Function

Pin

No.

1VDD VDD VDD —————Power (+3.3V)

2 RFS0 YLRCK YLRCK I — IPu — H

3GND GND GND —————GND

4 RCLK0 YBCK YBCK I — — — — Receive frame sync (BCK) signal (Serial port IN 0)

5 DR0A ADDATA ADDATA I — IPu — H Data receive A (serial port IN 0)

6 DR0B I — IPu — H Data receive B (serial port IN 0)

7 TFS0 YLRCK YLRCK I — IPu — H

8 TCLK0 YBCK YBCK I — — — — Send frame sync (BCK) signal (Serial port OUT 0)

9VDD VDD VDD —————Power (+3.3V)

10GND GND GND —————GND

11 DT0A MOUT1 MOUT2 O — IPu — H Data send A (Serial port OUT 0)

12 DTOB DOUT1 DOUT2 O — IPu — H Data send B (Serial port OUT 0)

13 RFS1 LRCK1 LRCK2 I — IPu — H

14GND GND GND —————GND

15 RCLK1 BCK1 BCK2 I — — L — Receive frame sync (BCK) signal (Serial port IN 1)

16 DR1A SAMP2 SAMP1 I — IPu — H Data receive A (serial por t IN 1)

17 DR1B I — IPu — H Data receive B (serial port IN 1)

18 TFS1 LRCK2 LRCK1 I/O — IPu — H

19 TCLK1 BCK2 BCK1 I/O ————Send frame sync (BCK) signal (Serial port OUT 1)

20

21VDD VDD VDD —————Power (+3.3V)

22 DT1A SOUT1 SOUT2 O — IPu — H Data send A (Serial port OUT 1)

23 DT1B SAMP1 SAMP2 O — IPu — H Data send B (Serial port OUT 1)

24 PWM_EVENT1 I/O — Pd — L PWM1 output

25GND GND GND —————GND

26 PWM_EVENT0 I/O — Pd — L PWM0 output

27 BR1_ I — Pu — H Multi-processing bus request 1

28 BR2_ I — Pu — H Multi-processing bus request 1

29VDD VDD VDD —————Power (+3.3V)

30 CLKIN I — — — — Clock input

31 XTAL_ O — — — — X’tal oscillator pin

32VDD VDD VDD —————Power (+3.3V)

Port Name

VDD VDD VDD —————Power (+3.3V)

Symbol

(IC301)

Symbol

(IC401)

I/O DET Ext Ini

Res

Receive frame sync (LRCK) signal (Serial port IN 0)

Send frame sync (LRCK) signal (Serial port OUT 0)

Receive frame sync (LRCK) signal (Serial port IN 1)

Send frame sync (LRCK) signal (Serial port OUT 1)

Function

11

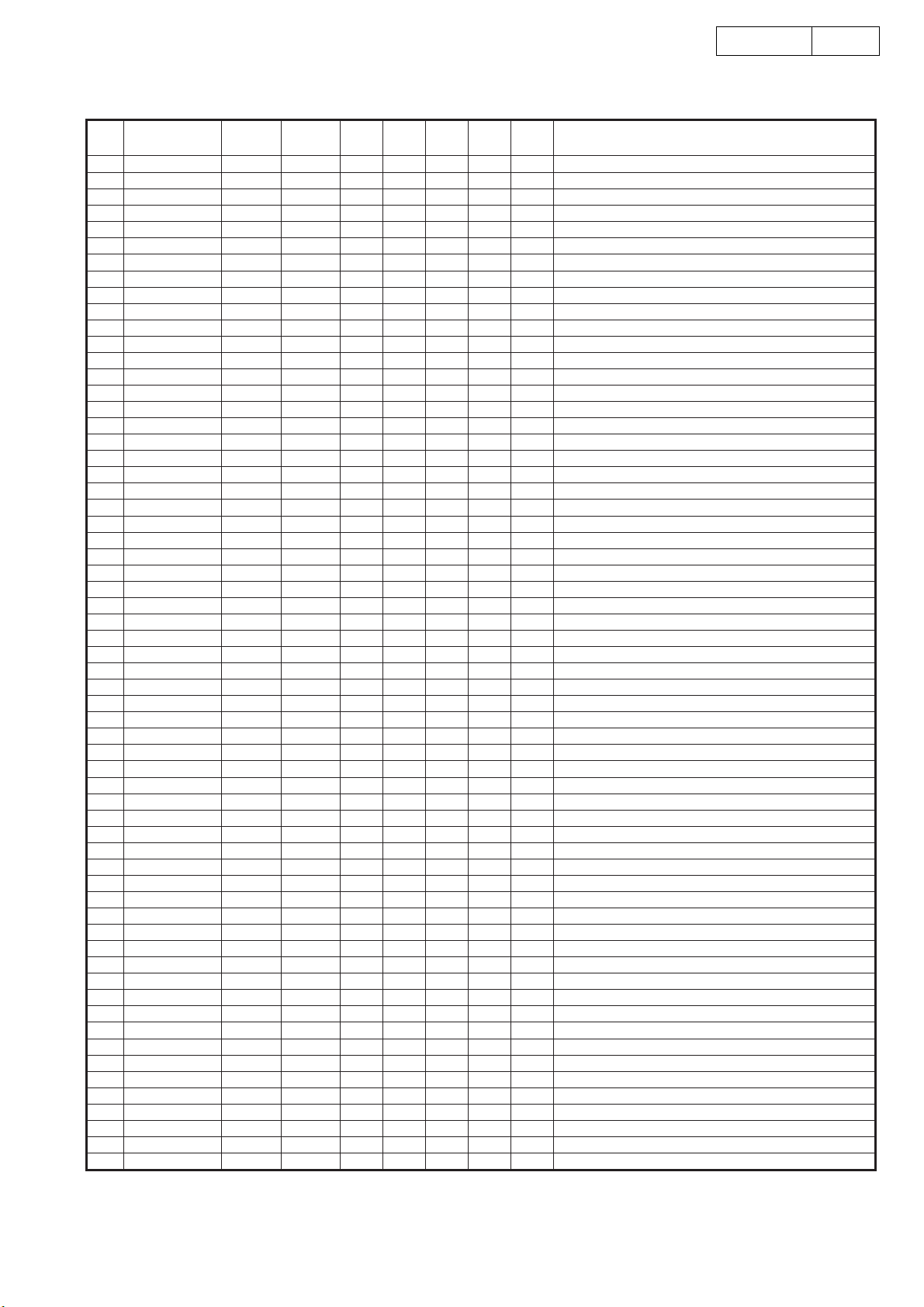

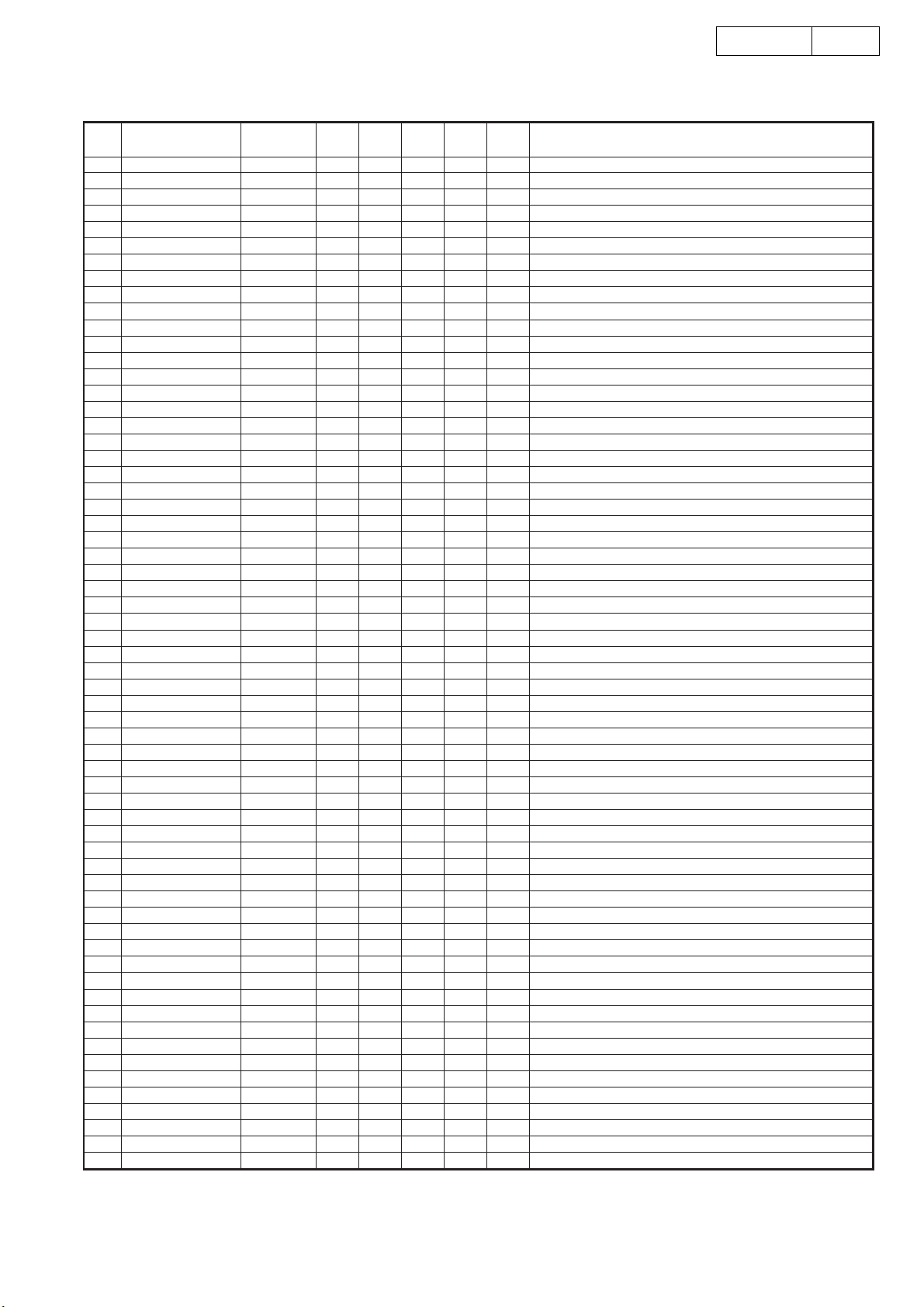

Page 12

12DN-S3000

Pin

No.

33GND GND GND —————GND

34 SDCLK1 O — Pd — L SDRAM clock enable 1

35GND GND GND —————GND

36VDD VDD VDD —————Power (+3.3V)

37 SDCLK0 I/O ————SDRAM clock enable 0

38 DMAR1_ I — Pu H H DMA request 1

39 DMAR2_ I — Pu H H DMA request 2

40 HBR_ I — Pu — H Host bus request (BOOT)

41GND GND GND —————GND

42 RAS_ I/O — Pu H H SDRAM row access strobe

43 CAS_ I/O — Pu H H SDRAM column access strobe

44 SDWE_ I/O — Pu H H SDRAM write enable

45VDD VDD VDD —————Power (+3.3V)

46 DQM O — — — — SDRAM data mask

47 SDCKE I/O — — H — SDRAM clock enable

48 SDA10 O — Pd L L SDRAM A10

49GND GND GND —————GND

50 DMAG1_ O — — H — DMA ground 1

51 DMAG2_ O — — H — DMA ground 2

52 HBG_ O — — H — Host bus ground (BOOT)

53 BMSTR O — — H — Bus master output (H out)

54VDD VDD VDD —————Power (+3.3V)

55 CS_ I — — L L Chip select (BOOT)

56 SBTS_ I — Pu H H Extend bus three state

57GND GND GND —————GND

58WR_ I/O————Memory write strobe

59RD_ I/O————Memory read strobe

60GND GND GND —————GND

61VDD VDD VDD —————Power (+3.3V)

62GND GND GND —————GND

63 REDY O — — — — Host bus ACK

64SW_ I/O————Sync type write select

65CPA_ I/O————Core priority access

66VDD VDD VDD —————Power (+3.3V)

67VDD VDD VDD —————Power (+3.3V)

68GND GND GND —————GND

69ACK I/O————Memory ACK

70 MS0_ I/O — Pu H H Memory select 0

71 MS1_ I/O ————Memory select 1

72GND GND GND —————GND

73GND GND GND —————GND

74 MS2_ I/O ————Memory select 2

75 MS3_ I/O ————Memory select 3

76 FLAG11

77VDD VDD VDD —————Power (+3.3V)

78 FLAG10

79 FLAG9 JOGB1 JOGB2 I — — — —

80 FLAG8 JOGA1 JOGA2 I — — — —

81 GND GND

82DATA0 I/O————Ext. bus data 0

83DATA1 I/O————Ext. bus data 1

84DATA2 I/O————Ext. bus data 2

85VDD VDD VDD —————Power (+3.3V)

86DATA3 I/O————Ext. bus data 3

87DATA4 I/O————Ext. bus data 4

88DATA5 I/O————Ext. bus data 5

89GND GND GND —————GND

90DATA6 I/O————Ext. bus data 6

91DATA7 I/O————Ext. bus data 7

92DATA8 I/O————Ext. bus data 8

93VDD VDD VDD —————Power (+3.3V)

94GND GND GND —————GND

Port Name

Symbol

(IC301)

DMABSY1

SAMPCOP

Symbol

(IC401)

DMABSY2

SAMPCOPY

GND —————GND

I/O DET Ext Ini

O — Pu — H General flag 11 (In DMA flag L: DMA)

I/O — Pu — H General flag 10 (In SAMPLER copy flag)

Res

General flag 9 (JOG turning direction detect signal B)

General flag 8 (JOG turning direction detect signal A)

Function

12

Page 13

13DN-S3000

Pin

No.

95VDD VDD VDD —————Power (+3.3V)

96DATA9 I/O————Ext. bus data 9

97DATA10 I/O————Ext. bus data 10

98DATA11 I/O————Ext. bus data 11

99GND GND GND —————GND

100DATA12 I/O————Ext. bus data 12

101DATA13 I/O————Ext. bus data 13

102NC —————NC

103NC —————NC

104DATA14 I/O————Ext. bus data 14

105VDD VDD VDD —————Power (+3.3V)

106GND GND GND —————GND

107DATA15 I/O————Ext. bus data 15

108DATA16 I/O————Ext. bus data 16

109DATA17 I/O————Ext. bus data 17

110VDD VDD VDD —————Power (+3.3V)

111DATA18 I/O————Ext. bus data 18

112DATA19 I/O————Ext. bus data 19

113DATA20 I/O————Ext. bus data 20

114GND GND GND —————GND

115NC —————NC

116DATA21 I/O————Ext. bus data 21

117DATA22 I/O————Ext. bus data 22

118DATA23 I/O————Ext. bus data 23

119GND GND GND —————GND

120VDD VDD VDD —————Power (+3.3V)

121DATA24 I/O————Ext. bus data 24

122DATA25 I/O————Ext. bus data 25

123DATA26 I/O————Ext. bus data 26

124VDD VDD VDD —————Power (+3.3V)

125GND GND GND —————GND

126DATA27 I/O————Ext. bus data 27

127DATA28 I/O————Ext. bus data 28

128DATA29 I/O————Ext. bus data 29

129GND GND GND —————GND

130VDD VDD VDD —————Power (+3.3V)

131VDD VDD VDD —————Power (+3.3V)

132DATA30 I/O————Ext. bus data 30

133DATA31 I/O————Ext. bus data 31

134 FLAG7 DFLG12 DFLG22 I/O — Pu — H General flag 7 (RESERVE)

135GND GND GND —————GND

136 FLAG6 DFLG11 DFLG21 I/O — Pu — H General flag 6 (RESERVE)

137 FLAG5 DTIMB1 DTIMB2 O — — — —

138 FLAG4 DTIMA1 DTIMA2 O — — — —

139GND GND GND —————GND

140VDD VDD VDD —————Power (+3.3V)

141VDD VDD VDD —————Power (+3.3V)

142NC —————NC

143 ID1 I — — L L Multi-processing ID1 (Single processor : 0)

144 ID0 I — — L L Multi-processing ID2 (Single processor : 0)

145 EMU_ EMU1_ EMU2_ O — — — — Emulation status

146

147 TRST_ TRST1_ TRST2_ I — IPu — H Test reset (JTAG)

148 TDI TDI1 TDI2 I — Pd — L Test data input (JTAG)

149 TMS TMS1 TMS2 I — IPu — H Test mode select (JTAG)

150GND GND GND —————GND

151 TCK TCK1 TCK2 I — Pu — H Test clock (JTAG)

152 BSEL I — — H H EPROM boot select (Boot by EPROM: 1)

153 BMS_ BMS1_ BMS2_ I — — H H Boot memory select (Host processor boot: 1)

154GND GND GND —————GND

155GND GND GND —————GND

156VDD VDD VDD —————Power (+3.3V)

Port Name

TD0 TD01 TD02 O — — — — Test data output (JTAG)

Symbol

(IC301)

Symbol

(IC401)

I/O DET Ext Ini

Res

General flag 5 (Pulse output for generating monitor play time)

General flag 4 (Pulse output for generating main play time)

Function

13

Page 14

14DN-S3000

Pin

No.

157 RESET_ DRES_ DRES_ I — — H L DSP reset signal

158VDD VDD VDD —————Power (+3.3V)

159GND GND GND —————GND

160 ADDR23 I/O ————Ext. bus address 23

161 ADDR22 I/O ————Ext. bus address 22

162 ADDR21 I/O ————Ext. bus address 21

163VDD VDD VDD —————Power (+3.3V)

164 ADDR20 I/O ————Ext. bus address 20

165 ADDR19 I/O ————Ext. bus address 19

166 ADDR18 I/O ————Ext. bus address 18

167GND GND GND —————GND

168GND GND GND —————GND

169 ADDR17 I/O ————Ext. bus address 17

170 ADDR16 I/O ————Ext. bus address 16

171 ADDR15 I/O ————Ext. bus address 15

172VDD VDD VDD —————Power (+3.3V)

173 ADDR14 I/O ————Ext. bus address 14

174 ADDR13 I/O ————Ext. bus address 13

175 ADDR12 I/O ————Ext. bus address 12

176VDD VDD VDD —————Power (+3.3V)

177GND GND GND —————GND

178 ADDR11 I/O ————Ext. bus address 11

179 ADDR10 I/O ————Ext. bus address 10 (SDRAM: Connects SDA10)

180 ADDR9 I/O ————Ext. bus address 9

181GND GND GND —————GND

182VDD VDD VDD —————Power (+3.3V)

183 ADDR8 I/O ————Ext. bus address 8

184 ADDR7 I/O ————Ext. bus address 7

185 ADDR6 I/O ————Ext. bus address 6

186GND GND GND —————GND

187GND GND GND —————GND

188 ADDR5 I/O ————Ext. bus address 5

189 ADDR4 I/O ————Ext. bus address 4

190 ADDR3 I/O ————Ext. bus address 3

191VDD VDD VDD —————Power (+3.3V)

192VDD VDD VDD —————Power (+3.3V)

193 ADDR2 I/O ————Ext. bus address 2

194 ADDR1 I/O ————Ext. bus address 1

195 ADDR0 I/O ————Ext. bus address 0

196GND GND GND —————GND

197 FLAG0 DR_/W1 DR_/W2 I/O ————General flag 0 (Command read write select)

198 FLAG1 DACK1_ DACK2_ I/O ————General flag 1

199 FLAG2 DBSY1 DBSY2 I/O ————General flag 2

200VDD VDD VDD —————Power (+3.3V)

201 FLAG3 DFLG10 DFLG20 I/O — Pu — H General flag 3 (RESERVE)

202NC ——————

203NC ——————

204GND GND GND —————GND

205 IRQ0_ DREQ1 DREQ2 I — Pu — H Interrupt request input 0 (SYS mcom interface)

206 IRQ1_ DREQ1_ DREQ2_ I — Pu — L Interrupt request input 1 (SYS mcom interface)

207 IRQ2_ JOGINT1 JOGINT2 I — — — —

208

Port Name

NC —————NC

Symbol

(IC301)

Symbol

(IC401)

I/O DET Ext Ini

Res

Interrupt request input 2 (JOG turning speed detect signal)

Function

14

Page 15

M5705Q (CD: IC501)

15DN-S3000

AVSS-DS

XSRFIN

XSIPIN

AVDD5-DS

XSDSSLV

XSRSLINT

XSAWRC

XSRFGC

XSEFGC

XSFOCUS

XSTRACK

XSSLEG

AVDD5-DA

XSMOTOR

AVSS-DA

XSRFRPLP

XSTELP

XSVREF2

XSRFRP

XSTEXI

AVSS-AD

XSTEI

XSFEI

XSAEI

AVDD5-AD

XSSBAD

XSDFCT

XSCSJ

XSCLK

XSDATA

XSLDC

XSFGIN

XSSPDON

XSFLAG(3)

XSFLAG(2)

XSFLAG(1)

XSFLAG(0)

XMP1_7

XMP1_6

XMP1_4

XSPDOFTR2

XSVR_PLL

174

173

XMP1_2

XGPIO(2)

XSFTROPI

XSFDO

172

171

XMP1_1

XMRSTJ

AVSS_PL

XSPLLFTR2

170

169

XGPO(1)

XGPO(0)

VDD5_PL

A

XSFDIREF

168

167

XCRSTJ

XMPSENJ

XSPDIREF

GND

166

165

VDD

XMALE

XTSLRF

XTPLCK

164

163

VDD

XMP1_0

VDD

162

XOSC1

XRA(3)

161

XOSC2

XRA(2)

160

GND

XRA(1)

159

XMD(0)

XRA(0)

158

XMD(1)

XRA(4)

157

XMD(2)

XRA(5)

156

XMD(3)

XRA(6)

155

XMD(4)

GND

154

XMD(5)

XRA(7)

153

XMD(6)

XRA(10)

XRA(11)

152

151

XMCSJ

XMD(7)

VDD

150

XMRDJ

XRA(8)

149

XMWRJ

XRA(9)

XROEJ

148

147

XMA(11)

XMINT1J

VDD

146

XMA(10)

XSAWRCVCO

XSVREFO

176

175

1

2

3

4

5

6

VDD

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

GND

28

29

30

31

32

33

34

35

36

37

38

39

40

41

GND

42

NC

43

44

45464748495051525354555657585960616263646566676869707172737475767778798081828384858687

XMP1_3

XMFSCSJ

4M DRAM

M5705

XRCASJ

XRRASJ

145

144

VDD

XMA(9)

XRSDCLK

XRWEJ

143

142

XMA(8)

XMA(7)

XRD(7)

141

XMA(6)

XRD(8)

140

XMA(5)

XRD(6)

139

XMA(4)

GND

138

XMA(3)

XRD(9)

137

XMA(2)

XRD(5)

136

XMA(1)

XRD(10)

XRD(4)

135

134

XMA(0)

XMA(12)

XRD(11)

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

88

GND

99

98

97

96

95

94

93

92

91

90

89

XRD(3)

XRD(12)

GND

XRD(2)

XRD(13)

XRD(1)

XRD(14)

XRD(0)

XRD(15)

XHD(7)

XHD(8)

XHD(6)

XHD(9)

XHD(5)

XHD(10)

XHD(4)

XHD(11)

VDD

XHD(3)

XHD(12)

XHD(2)

XHD(13)

GND

XHD(1)

XHD(14)

XHD(0)

XHD(15)

XHDRQ

XHIOWJ

XHIORJ

XHIORDY

XHDACKJ

XHINT

XHCS16J

XHA(1)

XHPDIAGJ

XHA(0)

XHA(2)

XHCS1J

XHCS3J

XHDASPJ

XMA(15)

XMA(14)

XMA(13)

ATAP I

M

Motor

Driver

Data

Separator

Digital

Servo

DVD-DSP

CD-DSP

RAM

Arbiter

Target

Search

&

MPEG

I/F

C3 ECC

EDC

MCU

ROM

M5705 Terminal Function

Pin Name

Type

2 XSRFIN I/A Analog RF signal input after passing through the equalizer

3 XSIPIN I/A Inverting input pin of data slicer

5 XSDSSLV O/A Slice level output pin

6 XSRSLINT I/A Reference current setting pin for analog data slicer

8 XSAWRC O/A Output for enlarge VCO range. Analog output from DAC buffer

9 XSRFGC O/A RF gain control output

10 XSEFGC O/A E,F gain control output

11

XSFOCUS O/A Output voltage level for focusing buffer IC

12 XSTRACK O/A Output voltage level for tracking buffer IC

13 XSSLEG O/A Output voltage level for sledge buffer IC

15 XSMOTOR O/A Output voltage level for spindle motor buffer IC

17 XSRFRPLP I/A High bandwidth low pass filter input for RFRP

18 XSTELP I/A High bandwidth low pass filter input for TE

19 XSVREF2 I/A 2.1V reference voltage input

20 XSRFRP I/A RF ripple/envelope signal input

21 XSTEXI I/A Tracking zero crossing input signal

23 XSTEI I/A Tracking error input signal

24 XSFEI I/A Focus error input signal

25

XSCEI I/A

1. Center error input signal

2. Photo Interrupt input

DescriptionPin No.

PC

MPEG

DEC.

15

Page 16

16DN-S3000

Pin Name

27 XSSBAD I/A Sub-beam addition signal input

166 XSPDIREF I/A

167 XSFDIREF I/A

169 XSPLLFTR2 I/A Data PLL loop filter pin#2

171 XSFDO O/A Output node of frequency detector charge pump circuit

172 XSFTROPI I/A Input node of loop filter OP circuit

173 XSVR_PLL I/A PLL reference voltage input

174 XSPDOFTR2 I/A Phase detector filter pin#1

175 XSVREFO O/A Reference voltage output

176 XSAWRCVCO I/A Auto Wide Range Control of VCO input pin. For enlarge VCO range in CAV mode

29 XSDFCT I Detect detection signal input

30 XSCSJ O Chip select signal for accessing control registers

31 XSCLK O Clock output for accessing control registers

32 XSDATA I/O Registers data input/output pin

33 XSLDC O Laser diode on/off control output for both CD/DVD

34 XSFGIN I Motor Hall sensor input

35 XSSPDON O Spindle motor on output

36, 37, 38, 39 XSFLAG[3:0] O These pins are used to monitor some status of servo control block

48, 51, 52 XGPIO[2:0] I/O

40 XMP1_7 I/O Internal microcontroller programmable I/O port 1.7.

41 XMP1_6 I/O Internal microcontroller programmable I/O port 1.6.

43 XMP1_5 I/O This pin is now changed to be NC.

44 XMP1_4 I/O Internal microcontroller programmable I/O port 1.4.

45 XMP1_3 I/O Internal microcontroller programmable I/O port 1.3.

47 XMP1_2 I/O Internal microcontroller programmable I/O port 1.2.

49 XMP1_1 I/O Internal microcontroller programmable I/O port 1.1.

57 XMP1_0 I/O

46 XMFSCSJ I/O Output chip select connected to external flash ROM chip enable pin

54 XMPSENJ I/O Output program store enable connected to external ROM PSENJ pin.

56 XMALE I/O This signal is used as address latch signal in address/data mux mode

70 XMCSJ I/O

71 XMRDJ I/O

72 XMWRJ I/O This signal is used as the Wire Strobe signal

73 XMINT1J I/O

74, 75, 77, 78,

79, 80, 81, 82,

83, 84, 85, 86,

87, 89, 90, 91

62, 63, 64, 65,

66, 67, 68, 69 bus for the 8-bit processor mode.

163 XTPLCK I/O PLCK test pin

164 XTSLRF I/O SLRF test pin

59 XOSC1 I Crystal input/System clock. The input frequency from outside crystal or oscillator is 33.8688MHz

60

53 XCRSTJ I

94 XHCS1J I This pin is used to select the command block task file registers

93 XHCS3J I This pin is used to select the control block task file registers

103 XHIORJ I Asserted by the host during a host I/O read operation

104 XHIOWJ I Asserted by the host during a host I/O write operation

105

101 XHDACKJ I

99 XHCS16J O

50 XHRSTJ I Host Reset. The reset of ATA bus

100 XHINT O

XMA[15:0] I/O These pins are used as address bus

XMD[7:0] I/O

XOSC2 O Crystal output

XHDRQ O

Type

Phase detector reference current generator. Connect a resistor between this pin and

ground to set reference current

Frequency detector reference current generator. Connect a resistor between this pin and

ground to set reference current

1. These pins are used as general purpose I/O bus

2. When use internal microcontroller, XGPIO[2] can be used as programmable I/O port 3.6.

Internal microcontroller programmable I/O port 1.0.

This pin is default used as the A16 (microcontroller address line 16)

1. This signal must be asserted for all microcontroller accesses to the register of this chip

2. When use internal microcontroller, this signal can be used as programmable I/O port 3.1

1. This signal is used as the Read Strobe signal

2. When use internal microcontroller, this signal can be used as programmable I/O port 3.0

1. This signal is an interrupt line to the microcontroller

2. When use internal microcontroller, this signal can be used as programmable I/O port 3.7

These pins are used as data bus for the 16-bit processor mode, or the address/data mux

Chip Reset. As asserted low input generates a component reset that stops all operations within

the chip and deasserts all output signals. All input/output signals are set to input.

DMA request. This pin is configured as the DMA request signal, and is used during DMA transfer

1.

between the host and the controller. This pin is tri-stated when DMA transfers are not enabled.

2.

MPEG acknowledge. This pin is used as the ACKJ signal when MPEG interface mode is selected.

1. DMA acknowledge. This pin is configured as DACKJ, and is used as the DMA acknowledge

signal during DMA data transfers.

2. MPEG request. This pin is used as the REQ signal when MPEG interface mode is selected

1. 16-bit data select. This signal indicates that a 16-bit data transfer is active on the host data

bus. This pin is open-drain tri-state output.

2. MPEG clock. This pin is used as the CLOCK signal when MPEG interface mode is selected.

1. Host interface request. This tri-state pin is the host interrupt request, and is asserted to

indicate to the host that the controller needs attention.

2. MPEG begin. This pin is used as the BEGIN signal when MPEG interface mode is selected

DescriptionPin No.

16

Page 17

17DN-S3000

Pin Name

97 XHPDIAGJ I/O This pin is used as the Passed Diagnostics signal, and may be an input or an open-drain output

92 XHDASPJ I/O

102 XHIORDY I/O

95, 96, 98 XHA[2:0] I

106, 107, 108, 2.

109, 111, 112, 3. VCD I/F. Bit3-0 are used as VCD I/F signal when VCD function is enabled. The relationship of

113, 114, 116, bit3-0 and VCD I/F is as follow

117, 118, 119, HD0—CD-DATA

120, 121, 122, HD1—CD-LRCK

123 HD2—CD-BCK

143 XRSDCLK O This signal is the clock output for SDRAM

147 XROEJ O

142 XRWEJ O This signal is asserted low when a buffer memory write operation is active

144 XRRASJ O

145 XRCASJ O

148, 149, 151,

152, 153, 155,

156, 157, 158,

159, 160, 161

124, 125, 126,

127, 128, 129,

131, 132, 134,

135, 136, 137,

138, 139, 140,

141

4 AVDD5_DS Analog Power +5V for Data Slicer part

14 AVDD5_D

26 AVDD5_AD Analog Power +5V for ADC part

168 AVDD5_PL Analog Power +5V for Data PLL part

7, 55, 58, 76,

115, 146,

150, 162

1 AVSS_DS Analog Ground for Data Slicer part

16 AVSS_DA Analog Ground for DAC part

22 AVSS_AD Analog Ground for ADC part

170 AVSS_PL Analog Ground for Data PLL part

28, 42, 61,

88, 110, 130,

138, 154, 165

XHD[15.0] I/O

XRA[11:0] O 1: Normal operation

XRD[15:0]

VDD Power +3.3V for digital core logic and pad

GND Digital Ground core logic and pad.

Type

This pin is used as the Drive Active/Slave Present signal, and is an input or an open-drain

output. This pin is used for Master/Slave drive communication and/or for driving an LED

1. I/O channel ready. This signal is driven low to extend host transfer cycles when the controller

is not ready to respond. This pin will be tri-stated when a read or write is not in progress.

2. MPEG error. This pin is used as the ERROR signal when MPEG interface mode is selected

Host address lines. The host address lines A[2:0] are used to access the various host control,

status, and data registers

1. Host data bus. This bus is used to transfer data and status between the host and the controller.

MPEG data bus 7-8. The HD[7:0] are used as the DATA [7:0] when MPEG interface mode is selected.

HD3—CD-C2PO

This signal is used as the memory output enable for external DRAM buffers. After RSTJ is

asserted, this signal will be low

This signal is used as Row address output to external DRAM buffer. After RSTJ is asserted, this

signal will be high

This signal is used as column address output to external DRAM. After RSTJ is asserted, this

signal will be high

1. RAM address lines. These are bits11-0 for addressing the buffer memory.

2. Hardware setting. The bits6-0 are used as hardware setting for some functions.

RA[9] : FLASH size is 64K/128K

1: FLASH size is 64K

0: FLASH size is 128K

RA[8] : External CPU is 8032/H8

1: 8032

0: H8

RA[7] : Microcontroller programmable I/O port 1 pin control

1: By internal microcontroller

0: By registers to decide input/output

RA[6] : System test pin output

0: System test pin output

RA[5] : For testing purpose, donít need to set

RA[4] : IDE master/slave

1: Slave

0: Master

RA[3] : For testing purpose, donít need to set

RA[2] : For testing purpose, donít need to set

RA[1-0] : MCU Mode selection

11: Normal Mode (internal uP, internal address latch)

10: Outside uP Mode (ICE Mode)

01: Test mode for internal uP testing

00: Internal uP mode with external address latch

I/O These signals are the 8-bit parallel data lines to/from the buffer memory.

A Analog Power +5V for DAC part

DescriptionPin No.

17

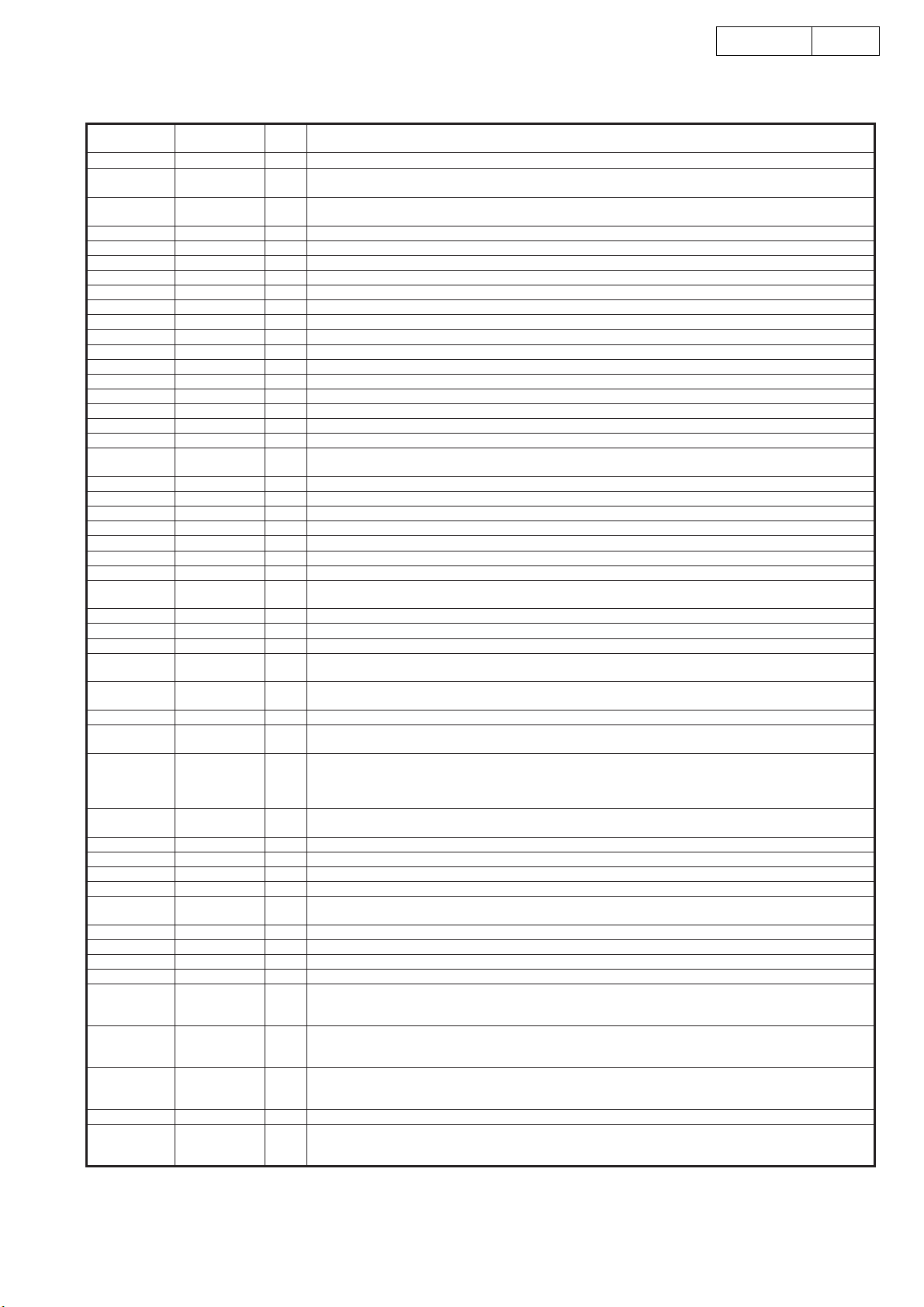

Page 18

MN102H730F (DS: IC501)

18DN-S3000

96 65

97 64

TOP VIEW

128 33

132

MN102H730F Terminal Function

Pin

No.

1 CS0_ CS0_ O — Pu — — Ext. memory chip select 0 (Flash ROM CS)

2 CS1_ CS1_ O — Pu — — Ext. memory chip select 1 (Flash ROM for memo)

3 D00 DQ0 I/O — — — — Ext. memory data in/output 0, DSP interface 0

4 D01 DQ1 I/O — — — — Ext. memory data in/output 1, DSP interface 1

5 D02 DQ2 I/O — — — — Ext. memory data in/output 2, DSP interface 2

6 D03 DQ3 I/O — — — — Ext. memory data in/output 3, DSP interface 3

7 VDD VDD — — — — —

8 VSS VSS — — — — — GND

9 D04 DQ4 I/O — — — — Ext. memory data in/output 4, DSP interface 4

10 D05 DQ5 I/O — — — — Ext. memory data in/output 5, DSP interface 5

11 D06 DQ6 I/O — — — — Ext. memory data in/output 6, DSP interface 6

12 D07 DQ7 I/O

13 D08 DQ8 — — —

14 D09 DQ9 — — —

15 D10 DQ10 — — —

16 PD0,DMAACK1_ RESERVE —

17 PD1,DMAREQ1_ RESERVE —

18 D11 DQ11 — — —

19 D12 DQ12 — — —

20 D13 DQ13 — — —

21 D14 DQ14 — — —

22 D15 DQ15 — — —

23 WORD WORD I — — Data bus width select (H: 16bit), GND fixed

24 VDD VDD — — — — — Power (+3.3V)

25 MODE MODE I — — L L Processor mode, GND fixed

Pin Name

Symbol

DET Ext Ini Res

I/O

Power (+3.3V)

— — — — Ext. memory data in/output 7, DSP interface 7

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

—

O

—

O

—

—

—

—

—

L—

L—

Ext. memory data in/output 8, DSP interface 8

Ext. memory data in/output 9, DSP interface 9

Ext. memory data in/output 10, DSP interface 10

Ext. memory data in/output 11, DSP interface 11

Ext. memory data in/output 12, DSP interface 12

Ext. memory data in/output 13, DSP interface 13

Ext. memory data in/output 14, DSP interface 14

Ext. memory data in/output 15, DSP interface 15

Function

18

Page 19

19DN-S3000

Pin

No.

26 PC3 MUTE O — Pu H H Mute signal (H: Mute)

27 XI XI I — — — — Oscillation input

28 XO XO O — — — — Oscillation output

29 VDD VDD — — — — — Power (+3.3V)

30 OSCI OSCI I — — — — Oscillation input, 32.0MHz

31 OSCO OSCO O — — — — Oscillation output

32 VSS VSS — — — — —

33 P57,BOSC TEST

34 PC5,NMI I — —

35 RST_ RST_ I —

36 PC0 YMCLK O —

37 P76 TEST O — Pu — P.W.B. check mode IN

38 P60,IRQ0 DTIMA I — Pu H H Main playback clock input

39 P61,IRQ1 DTIMB I — Pu H H Monitor playback clock input

40 P62,IRQ2,TM10IOA TABLE I — (Pu) H H Clock pulse input for platter

41 P63,IRQ3,TM10IOA CLK4M I — — Clock pulse input for platter

42 P64,IRQ4 ATANS_ I — (Pu) — H ATAPI µcom serial interface

43 P65,IRQ5,TM12IOA DISCPA I — (Pu) H H Clock pulse input for scratch disc

44 P66,IRQ6 DISCDIR I — (Pu) H H Direction pulse input for scratch disc

45 P67,IRQ7 DISCINT I — (Pu) H H

46 P70,TM13IOB DISCA I —

47 P71 YMDATA O — — H — AK4353 output data

48 PD2,DMAACK0_ NRES_ O — Pd L L AK4353 reset signal

49 PD3,TM3IO DISCPA_ I — — —

50

51 P77 RESERVE

52 P72,TM14IOB DISCPB I — — — — SCRATCH for DISC pulse B count input

53 P73 O — — L

54 P74

55 P75,TM12IOB CLK4M I — — — — Clock pulse input for disc

56 PA0,SBI0 RXD1 I — (Pu) — H Data receive from PANEL

57 PA1,SBO0 TXD1 O — Pu H H Data send to PANEL (PU µcom specify)

58 PA2,SBT0 MCMD_ O — Pu H H ATAPI µcom serial interface (PU µcom specify)

59 PA3,SBI1 X'RXDOUT I — (Pd) — H Data receive from X'EFFECT OUT

60 PA4,SBO1 X'TXDOUT O — Pu H H Data send to X'EFFECT OUT

6 1 PA5

62 PB0,SBI2 X’RXD IN I — (Pd) — H Data receive from X’EFFECT IN

63 PB1,SBO2 X’TXD IN O — Pu H H Data send to X’EFFECT IN

64 PB2 APRES_ O — Pd L L ATAPI µcom reset signal

65 PB3,SBI3 ATDATA I — (Pu) — H ATAPI µcom serial receive signal

66 PB4,SBO3 MDATA O — H

67 PB5,SBT3 MCLK O — —

68 VDD VDD — — — — — Power (+3.3V)

69 VSS VSS — — — — — GND

70 AVSS AVSS — — — — — Analog ref. GND for A/D conversion, GND

71 Vref Vref — — — — — Analog ref. V for A/D conversion, GND

72 P80 DFLG2 I/O — Pu — H DSP gener al flag 2

73 P81 DFLG1 I/O — Pu — H DSP gener al flag 1

74 P82 DR_/W1 O — — H — DSP interf ace send/receive select signal

75 P83 DACK_ I — Pu H H DSP interf ace ACK

76 P84 DBSY_ I — Pu

77 P85 DFLG0 I/O — Pu —

78 P86 DREQ_ O — Pu H H

79 P87 FPLAY1 I — Main fader start PLAY input

80 PD4 FCUE1

81 PD5 I — H

82 P90 I —

83 P91 RESERVE O — — L —

84 P92 PNLRST — LL

85 P93 APOWER O — Pd

86 Vref+ Vref+ — — — — — Analog ref. V for A/D conversion, +3.3V

87 AVDD AVDD — — — — — Power (+3.3V)

Pin Name

VDD VDD — — — — — P—ower (+3.3V)

Symbol

NMI

RESERVE

RESERVE

RESERVE

TESTIN1

TESTIN2

I/O

DET Ext Ini Res

GND

I — 32.0MHz output

O— —

O—

O—

I — (Pu) H H Main fader start CUE input

———

——

—

———

—L

—L

—L

—

(Pu)

Pu

Pu

—Pd

—

—

Connect to Power

—

µcom reset

H — Clock for AK4353 data

—

—

—

Start pulse input for scratch disc

SCRATCH for DISC pulse A count input

Clock invert pulse input for scratch disc

—

—

—

—

ATAPI µcom serial send signal

—

H ATAPI µcom serial send/receive clock

H H DSP interf ace busy signal

H DSP gener al flag 0

DSP interf ace request signal

HH

—

—

H

Panel µcom reset signal (L:Reset)

L

L Analog output voltage ON/OFF (L:OFF)

Function

19

Page 20

20DN-S3000

Pin

No.

88 P94 MCNT0 O — Pu L L Motor control signal 0

89 P95 MCNT1 O — Pu

90 P96,DAC2 MCNTDA O — L

91 P97,DAC3 RESERVE O — — H —

92 BREQ_ BREQ_ I — (Pu) H H Bus request signal

93 BRACK_ BRACK_ O — Pu H H Bus request accept signal

94 WEL_ WE_ O — Pu — H Ext. memory write enable (Lower 8bit)

95 P51 RESERVE O — — H —

96 RE_ RE_ O — Pu — H Ext. memory read enable

97 CS2_ CS2_ O — Pu — H Ext. memory chip select 2 (DSP1 interface)

98 VDD VDD — — — — — Power (+3.3V)

99 VSS VSS — — — — — GND

100 P54, BSTRE ML O — — H — AK4353 chip select

101 P55, WR_ RESERVE O — — H —

102 CS3_ CS3_ O — — — — Not used

103 A00 A00 O — — — — Ext. memory address bus 0

104 A01 A01 O — — — — Ext. memory address bus 1

105 A02 A02 O — — — — Ext. memory address bus 2

106 A03 A03 O — — — — Ext. memory address bus 3

107 A04 A04 O — — — — Ext. memory address bus 4

108 A05 A05 O — — — — Ext. memory address bus 5

109 A06 A06 O — — — — Ext. memory address bus 6

110 A07 A07 O — — — — Ext. memory address bus 7

111 A08 A08 O — — — — Ext. memory address bus 8

112 PD6 RESERVE O — — L —

113 PD7,TM7IO I —

114 A09 A09

115 A10 A10 O — — — — Ext. memory address bus 10

116 A11

117 A12 A12 O — — — — Ext. memory address bus 12

118 A13 A13 O — — — — Ext. memory address bus 13

119 VDD VDD — — — — — Power (+3.3V)

120 PC4 RESERVE O — — L —

121 A14 A14 O — — — — Ext. memory address bus 14

122 A15 A15 O — — — — Ext. memory address bus 15

123 A16 A16 O — — — — Ext. memory address bus 16

124 A17 A17 O — Pu — — Ext. memory address bus 17

125 A18 A18 O — Pu — — Ext. memory address bus 18

126 A19 A19 O — Pu — — Ext. memory address bus 19

127 A20 A20 O — Pu — — Ext. memory address bus 20

128 A21 A21 O — Pu — — Ext. memory address bus 21

Pin Name

Symbol

DISCPB_

A11 O — — — — Ext. memory address bus 11

DET Ext Ini Res

I/O

L L Motor control signal 1

Pu L

——

O — — — — Ext. memory address bus 9

Motor rotation speed control signal A/D 0

—

Function

20

Page 21

128M-SDRAM (DS: IC402)

21DN-S3000

V

DQ0

V

DD

DQ1

DQ2

V

SS

DQ3

DQ4

V

DD

DQ5

DQ6

SS

V

DQ7

NC

V

DQM0

WE#

CAS#

RAS#

CS#

A11

BA0

BA1

A10

A0

A1

A2

DQM2

V

NC

DQ16

V

SS

DQ17

DQ18

V

DD

DQ19

DQ20

SS

V

DQ21

DQ22

DD

V

DQ23

V

DD

1

2

3

Q

4

5

6

Q

7

8

9

Q

10

11

12

Q

13

14

15

DD

16

17

18

19

20

21

22

23

24

25

26

27

28

29

DD

30

31

32

Q

33

34

35

Q

36

37

38

Q

39

40

41

Q

42

43

DD

86

V

SS

85

DQ15

84

SS

Q

V

83

DQ14

82

DQ13

81

V

DD

DQ12

DQ11

V

SS

Q

DQ10

DQ9

V

DD

DQ8

NC

V

SS

DQM1

NC

NC

CLK

CKE

A9

A8

A7

A6

A5

A4

A3

DQM3

V

SS

NC

DQ31

DD

V

DQ30

DQ29

V

SS

Q

DQ28

DQ27

V

DD

DQ26

DQ25

SS

Q

V

DQ24

V

SS

Q

Q

Q

Q

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

Block Diagram

CKE

CLK

CS#

WE#

CAS#

RAS#

A0–A11,

BA0, BA1

14

DECODE

COMMAND

MODE REGISTER

ADDRESS

REGISTER

CONTROL

LOGIC

12

Note: The # symbol indicates signal is active LOW.

BANK0

REFRESH

12

COUNTER

12

8

ROW-

ADDRESS

MUX

2

2

12

BANK

CONTROL

LOGIC

COLUMNADDRESS

COUNTER/

LATCH

BANK0

ROW-

ADDRESS

LATCH

&

DECODER

4096

8

MEMORY

(4,096 x 256 x 32)

SENSE AMPLIFIERS

I/O GATING

DQM MASK LOGIC

READ DATA LATCH

WRITE DRIVERS

COLUMN

DECODER

BANK1

BANK0

ARRAY

8192

256

(x32)

BANK2

BANK3

4

DATA

OUTPUT

32

REGISTER

DATA

INPUT

32

REGISTER

4

32

DQM0–

DQM3

DQ0–

DQ31

21

Page 22

128M-SDRAM Terminal Function

Pin NO. Symbol Type Description

68 CLK I Clock

67 CKE I Clock Enable

20 CS# I Chip Select

17, 18, 19 WE#, CAS#, RAS# I Command Inputs

16, 71, 28, 59 DQM0-DQM3 I Input/Outout Mask

22, 23 BA0, BA1 I Bank Address Input(s)

21, 24-27, 60-66 A0-A11 I Address Inputs

2, 4, 5, 7, 8, 10, 11, 13, 31, 33, 34, 36, 37, 39,

40, 42, 45, 47, 48, 50, 51, 53, 54, 56, 74, 76,

77, 79, 80, 82, 83, 85

14, 30, 57, 69, 70, 73 NC - No Connect

3, 9, 35, 41, 49, 55, 75, 81 V

6, 12, 32, 38, 46, 52, 78, 84 V

1, 15, 29, 43 V

44, 58, 72, 86 V

DQ0-DQ31 I/O Data I/Os

DD

Q Supply DQ Power Supply

SS

Q Supply DQ Ground

DD

SS

Supply Power Supply: +3.3V ±0.3V

Supply Ground

22DN-S3000

22

Page 23

ML9207-01GP (PA: IC101)

23DN-S3000

AD3

AD4

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

10

11

12

13

14

15

16

17

18

19

20

AD2

AD1

DISP2

V

NC

FL2

V

P4

P3

P2

OSC1

RESET

CS

CP

DA

VDDP1

GND

OSC0

FL1

V

COM23

COM24

6162636465666768697071727374757677787980

1

2

3

4

5

6

7

8

9

TOP VIEW

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

COM22

COM21

COM20

COM19

COM18

COM17

COM16

COM15

COM14

COM13

COM12

COM11

COM10

COM9

COM8

COM7

COM6

COM5

COM4

COM3

4039383736353433323130292827262524232221

SEG31

SEG30

SEG29

SEG28

SEG27

SEG26

SEG25

SEG24

SEG23

SEG22

SEG20

SEG19

SEG21

ML9207-01GP Terminal Function

Pin No. Symbol I/O Function

3~37 SEG1~35 O FL display anode electrode drive output pin

39~62 COM1~24 O FL display grid electrode drive output pin

1, 2, 79, 80 AD1~4 O FL display anode electrode drive output pin

72~75 P1~4 O General port output pin

71 V

38, 78 V

64 GND

63, 76 V

70 DA I Serial data input pin (positive logic).

69 CP I Shift clock input pin

68 CS I Chip select input pin

67 RESET I Reset input pin, L: All functions are initialized

65 OSCO I

66 OSC1 O

77 NC

DD

DISP1~2

FL1~2

V

-GND: Power for logic

DD

V

—

: Power for FL display drive

DISP-VFL

Same power source should be used for V

Pin for self-oscillation, target oscillation frequency 4.0MHz

Not used

—

SEG32

and V

DD

SEG34

SEG33

DISP

DISP1

V

SEG35

COM2

COM1

23

Page 24

SP-3721A (CD: IC502)

A

CDRF

CDRDDC

ATOP

ATON

AIN

AIP

24DN-S3000

HOLD1

VNA

FNN

FNP

DIP

DIN

RX

BYP

SIGO

VPA

49505152535455565758596061626364

DVDRFP

DVDRFN

PD1

PD2

A2

B2

C2

D2

CP

CN

1

2

3

4

5

6

7

8

9

10

11

D

12

C

13

B

14

A

15

F

16

E

NC

VCI2

CDTE

TOP VIEW

VNB

DVDLD

DVDPD

CDPD

CDLD

VC

LDON#

VCI

VPB

VIIRR

VIP

32313029282726252423222120191817

VIB

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

FDCHG#

SDEN

SDAT

SCLK

LCP

LCN

CE

FE

TE

MEI

MEV

TPH

DFT

PI

MIN

MEVO

MLPF

SP3721A Terminal Function

PinName

Type

1, 2 DVDREP, DVDREN I RF Signal Inputs. Differential RF signal attenuator input pins

63 CDRF I RF Signal Inputs. Single-ended RF signal attenuator input pin

59, 60 AIP, AIN I AGC Amplifier Inputs. Differential AGC amplifier input pins

53, 54 DIP, DIN I

Analog inputs for RF Single Buffer. Differential analog inputs to the RF single-ended output buffer

and full wave rectifier

Low Impedance Enable. A TTL compatible input pin that activates the FDCHG switches. A low

32 FDCHG# I

level activates the switches and the falling edge of the internal FDCHG triggers the fast decay for

the MIRR bottom hold circuit. (open high)

49 HOLD1 I

Hold Control. A TLL compatible control pin which, when pulled high, disables the RF AGC charge

pump and holds the RF AGC amplifier gain at its present value. (open high)

11~14 D, C, B, A I Photo Detector Interface Inputs. Inputs from the main beam Photo detector matrix outputs

5~8 A2, B2, C2, D2 I

Photo Detector Interface Inputs. AC coupled inputs for the DPD from the main beam Photo

detector matrix outputs

15~16 F, E I CD tracking Error Inputs. Inputs from the CD photo detector error outputs.

3~4 PD1, PD2 I CD Photo detector Interface Inputs. Inputs from the CD photo detector error outputs

40 MEI I Mirror Envelope Inputs. The SIGO envelope input pin

35 MIN I

RF signal Input for Mirror. AC coupled inputs for the mirror detection circuit from the pull-in signal

(PI)

output.

21 DVDPD I APC Input. DVD APC input pin from the monitor photo diode

23 CDPD I APC Input. CD APC input pin from the monitor photo diode

25 LDON# I APC Output On/Off. APC output control pin. A low level activates the LD output. (open high)

61, 62 ATON/ATOP O Differential Attenuator Output. Attenuator outputs

51, 52 FNN, FNP O Differential Normal Output. Filter normal outputs

57 SIGO O Single Ended Normal Output. Single-ended RF output

64 CDRFDC O CD RF Signal Output. Single ended CD RF summing output

42 FE O Focusing Error Signal Output. Focus error output reference to VCI

41 TE O Tracking Error Signal Output. Tracking error output reference to VCI

DescriptionPinNo.

24

Page 25

25DN-S3000

Pin Name

43 CE O Center Error Signal Output. Center error output reference to VCI

34 NEVO O SIGO Bottom Envelope Output. Bottom envelope for mirror detection

37 DFT O

29 MIRR O Mirror Detect Output. Mirror Detect comparator output. Pseudo CMOS output

36 PI O

22 DVDLD O APC output. DVD APC output pin to control the laser power

24 CDLD O APC output. CD APC output pin to control the laser power

56 BYP I/O The RF AGC integration capacitor CBYP, is connected between BYP and VPA

9 CP I/O

10 CN I/O

45 LCP — Center Error LPF pin. An external capacitance is connected between this pin and the LCN pin

44 LCN — Center Error LPF pin. An external capacitance is connected between this pin and the LCP pin

30 MP — MIRR signal Peak hold pin. An external capacitance is connected to between this pin and VPB

31 MB — MIRR signal Bottom hold pin. An external capacitance is connected to between this pin and VPB

39 MEV — Sigo Bottom Envelope pin. An external capacitance is connected to between this pin and VPB

17 CDTE — CD Tracking. E-F Opamp output for feedback

38 TPH — PI Top Hold pin. An external capacitance is connected to between this pin and VPB

26 VC —

27

18 VCI2 — Reference Voltage input. DC bias voltage input for the servo input reference

55 RX —

33 MLPF — MIRR signal LPF pin. An external capacitance is connected between this pin and VPB

19 NC — No Connect

48 SDEN I

47 SDATA I/O

46 SCLK I

58 VPA Power. Power supply pin for the RF block and serial port

28 VPB Power. Power supply pin for the servo block

50 VNA Ground. Ground pin for the RF block and serial port

20 VNB Ground. Ground pin for the servo bolck

VCI — Reference Voltage input. DC bias voltage input for the servo input reference

Type

Defect Output. Pseudo CMOS output. When a defect is detected, the DFT output goes high. Also

the servo AGC output can be monitored at this pin, when CAR bits 7-4 are ‘0011’

Pull-in Signal Output. The summing signal output of A, B, C, D or PD1, PD2 for mirror detection.

Reference to VCI

Differential Phase tracking LPF pin. An external capacitance is connected between this pin and

the CN pin

Differential Phase tracking LPF pin. An external capacitance is connected between this pin and

the CP pin

Reference Voltage output. This pin provides the internal DC bias reference voltage (+2.5V lix).

Output Impedance is less than 50ohms

Reference Resistor Input. An external 8.2kohm, 1% resistor is connected from this pin to ground

to establish a precise PTAT (proportional to absolute temperature) reference current for the filter

Serial Data Enable. Serial Enable CMOS input. A high level input enable the serial port (Not to be

left open)

Serial Data. Serial data bi-directional CMOS pin. NRZ programming data for the internal registers

is applied to this input ( Not to be left open)

Serial Clock. Serial Clock CMOS input. The clock applied to this pin is synchronized with the data

applied to SDATA (Not to be left open)

DescriptionPin No.

25

Page 26

TMP86CM47U-4V14 (PA: IC102)

33

26DN-S3000

23

34

22

TOP VIEW

44

1

12

11

TMP86CM47U-4V14 Terminal Function

Pin No. Pin Name Symbol I/O DET Ext Ini Res Function

1 Vss Vss - - - - - GND (0V)

2 XIN XIN I - - - - Oscillation input 16.0MHz

3 XOUT XOUT O - - - - Oscillation output

4 TEST TEST I - - - - Fixed to L

5 Vdd Vdd - - - - - Power (+5.0V)

6 P21 PITCHLED O - Pu H H LED ON/OFF (L:ON)

7 P22 EJECTLED O - Pu H H LED ON/OFF (L:ON)

8 RESET_ RST_ I - - - - ucom RESET

9 P20 LED4 O - Pu H H LED ON/OFF (L:ON)

10 P00 TRSB I - Pu - H Track select encoder B input

11 P01 PM LED O - Pu H H LED ON/OFF (L:ON)

12 P02 RXD I - Pu - H Data receive from main unit

13 P03 TXD O - Pu H H Data send to main unit

14 P04 FLDA O - Pu H H ML9207 data signal

15 P05 FLCS_ O - Pu H H ML9207 latch signal

16 P06 FLCP_ O - Pu H H Clock signal for ML9207 data output

17 P07 NEXT LED O - Pu H H LED ON/OFF (L:ON)

18 P17 KIN5 I - Pu - H Key scan input 5

19 P16 KIN4 I - Pu - H Key scan input 4

20 P15 KIN3 I - Pu - H Key scan input 3

21 P14 KIN2 I - Pu - H Key scan input 2

22 P13 KIN1 I - Pu - H Key scan input 1

23 P12 KIN0 I - Pu - H Key scan input 0

24 P11 TRSA I Ed Pu - H Track select encoder A interrupt input

25 P10 FLRES_ O - Pd L L ML9207 reset signal

26 P30 PITCH I - - - - Pitch VR signal

27 P31 PITCHC I - - - - Pitch VR center value signal

28 P32 MAIN LED O - Pu H H LED ON/OFF (L:ON)

29 P33 SAMP LED O - Pu H H LED ON/OFF (L:ON)

30 P34 DISC LED O - Pu H H LED ON/OFF (L:ON)

31 P35 KINAD I - Pu Å| H Key A/D input

32 P36 PLAY I/O - Pu H H PLAY/PAUSE key scan (PLAY/PAUSE LED L:ON)

33 P37 CUE I/O - Pu H H CUE key scan (CUE LED L:ON)

34 VAREF VAREF I - - - - Power (+5.0V), Analog ref. V for A/D conversion

35 AVDD AVDD I - - - - Power (+5.0V), For A/D conversion circuit only

36 AVSS AVSS I - - - - GND (0V), Analog GND for A/D conversion

37 P40 KOUT0 O - Pu H H Key scan output 0/LED line select 0 (L: Select)

38 P41 KOUT1 O - Pu H H Key scan output 1/LED line select 1 (L: Select)

39 P42 KOUT2 I/O - Pu H H Key scan output 2/ (Other than scan, IN)

40 P43 KOUT3 I/O - Pu H H Key scan output 3/ (Other than scan, IN)

41 P44 LED0 O - - H - LED ON/OFF0 (L:ON)

42 P45 LED1 O - - H - LED ON/OFF1

43 P46 LED2 O - - H - LED ON/OFF2

44 P47 LED3 O - - H - LED ON/OFF3

*Pd or Pu detected in input port when power on, Pd=CD1, Pu=CD2

26

Page 27

TMP86CM47U-3RD2 (DS: IC151)

27DN-S3000

33

34

23

22

TOP VIEW

44

1

11

TMP86CM47U-3RD2 Terminal Function

Pin

No.

1 VSS VSS — — — — — GND (0V)

2 XIN XIN I — — — — Oscillation input 8.0MHz

3 XOUT XOUT O — — — — Oscillation output

4 TEST TEST I — — — — Fixed to L

5 VDD VDD — — — — — Power (+3.3V)

6 P21(LED) DVSEL O — Pu L H Not used

7 P22 BREQ1_ O — Pu H H System µcom bus request

8 RESET_ RST_ I — — — — µcom reset

9 P20 DRLCH O — Pu H H ATAPI data register latch signal, H: Latch

10 P00(INT0) MCMD_ I — — — — System µcom serial interface

11 P01 DMA O — Pu L H ATAPI DMA mode select (H: DMA)

12 P02 DMABSY1 I — Pu — H In DMA flag (L: DMA data transfer)

13 P03 ATANS O — Pu H H System µcom serial interface

14 P04(SO) ATDATA O — Pu H H System µcom serial data receive signal

15 P05(SI) MDATA I — — — — System µcom serial data send signal

16 P06(SCK_) MCLK I — — — — System µcom serial send/receive clock

17 P07(INT4/LED) BSYIN_ I — — — H TXD BUSY input

18 P17 BSYOUT_ O — Pu H H TXD BUSY output signal (L: BUSY)

19 P16 DRES_ O — Pd L L DSP reset (L: Reset)

20 P15 DMAR_/W I/O — Pu/Pd H L/H ATAPI DMA direction select (L: Read) *

21 P14 RD_ O — — H — ATAPI read strobe

22 P13 WR_ O — — H — ATAPI write strobe

23 P12(INT2) INTRQ I Lv — — — ATAPI interrupt request signal

24 P11(INT1) DMARQ I Lv Pd — — ATAPI DMA request signal (Pd with 5.6kW)

25 P10 IORDY I — Pu — H

26 P30 D0 I/O — Pd L L ATAPI data bus 0 (APRES_ATAPI reset)

27 P31 D1 I/O — — — — ATAPI data bus 1 (CS1 device register chip select 1)

28 P32 D2 I/O — — — — ATAPI data bus 2 (CS0 device register chip select 0)

29 P33 D3 I/O — — — — ATAPI data bus 3 (DA2 device register select 2)

30 P34 D4 I/O — — — — ATAPI data bus 4 (DA1 device register select 1)

31 P35 D5 I/O — — — — ATAPI data bus 5 (DA0 device register select 0)

32 P36 D6 I/O — — — — ATAPI data bus 6

33 P37 D7 I/O — — — — ATAPI data bus 7

34 VAREF VAREF I — — — —

35 AVDD AVDD I — — — — Power (+3.3V), Power for A/D conversion circuit only

36 AVSS AVSS I — — — — GND (0V), Analog GND for A/D conversion

37 P40 D8 I/O — — — — ATAPI data bus 8

38 P41 D9 I/O — — — — ATAPI data bus 9

39 P42 D10 I/O — — — — ATAPI data bus 10

40 P43 D11 I/O — — — — ATAPI data bus 11

41 P44 D12 I/O — — — — ATAPI data bus 12

42 P45 D13 I/O — — — — ATAPI data bus 13

43 P46 D14 I/O — — — — ATAPI data bus 14

44 P47 D15 I/O — — — — ATAPI data bus 15

* Pd or Pu detected in input port when power on, Pd=CD1, Pu=CD2

Pin Name Symbol DET Ext Ini Res

12

FunctionI/O

ATAPI data transfer cycle extend request signal (Pu with 1.0kW)

GND (0V), Analog ref. V for A/D conversion, A/D not used

27

Page 28

W29EE011P (CD: IC507)

A12

A15

A16NCVDDWENC

303132

1234

A7

5

A6

6

A5

7

A4

8

A3

A2

A1

A0

DQ0

TOP

9

VIEW

10

11

12

13

14 15 16 17 18 19 20

DQ1

DQ2

DQ3

GND

DQ4

DQ5

29

28

27

26

25

24

23

22

21

DQ6

A14

A13

A8

A9

A11

OE

A10

CE

DQ7

V

V

CE

OE

WE

A0

A16

DD

SS

.

.

.

.

.

.

.

CONTROL

DECODER

OUTPUT

BUFFER

CORE

ARRA

28DN-S3000

Terminal Function

DQ0

:

7

DQ

Y

Name Function

A0 - A16

DQ0 - DQ7

CE

OE

WE

VDD

GND

NC

Address Inputs

Data Inputs/Outputs

Chip Enable

Output Enable

Write Enable

Power Supply

Ground

No Connection

BD6670FM (CD: IC510)

EXOR

Hall comp

H1+

H2+

H3+

GSW

GND

CP1

CP2

1

H1-

2

Hall Amo

3

H2-

4

5

H3-

6

7

Gain

control

8

9

Charge

Pump

10

G

V

11

C

NF

12

SB

Matrix

13

Vcc

14

PWM

Comp

OSC

Q

D

CK

QB

TSD

Matrix

Current

Sense AMP

REVERSE

DETECT

U-Pre

Driver

L-P re

Driver

BD6670FM Terminal Function

Pin

Pin

No.

FG3

28

FG

27

V

H

Hall

26

bias

V

M

25

A1

24

NF1

R

23

A2

22

Driver

R

NF1

21

A3

20

R

NF2

19

PS

PS

18

Torque

AMP

CL

EC

17

ECR

16

V

15

M

Name

1 H1+ Hall input Amp 1 positive input

2 H1- Hall input Amp 1 negative input

3 H2+ Hall input Amp 2 positive input

4 H2- Hall input Amp 2 negative input

5 H3+ Hall input Amp 3 positive input

6 H3- Hall input Amp 3 negative input

7 GSW Gain switch pin

8 GND GND

9 CP1 Capacitor pin 1 for charge pump

10 CP2 Capacitor pin 2 for charge pump

11 VG Capacitor connection pin for charge pump

12 CNF Capacitor connection pin for phase compensation

13 SB Short Brake Pin

14 VCC Power supply for signal division

15 VM Power supply for driver

16 ECR Torque control standard voltage input terminal

17 EC Torque control voltage input terminal

18 PS Power Save in

19 RNF2 Resistor connection pin for current sense

20 A3 Output3 for motor

21 RNF1 Resistor connection pin for current sense

22 A2 Output2 for motor

23 RNF1 Resistor connection pin for current sense

24 A1 Output1 for motor

25 VM Power supply for driver

26 VH Hall bias pin

27 FG FG output pin

28 FG3 FG3 output pin

Function

28

Page 29

BA5954FP (CD: IC509)

BA5954FP Terminal Function

Pin

No.

1 VINFC Focus driver input

2 CFCerr1 Cap. connection pin for error amp filter

3 CFCerr2 Cap. connection pin for error amp filter

4 VINSL+ Op. amp input (+) for sled driver

5 VINSL- Op. amp input (-) for sled driver

6 VOSL Op. amp output for sled driver

7 VNFFC Focus driver feedback pin

8 Vcc Pre Vcc, power Vcc for sled driver

9 PVcc1 Power Vcc for loading driver

10 PGND Power GND

11 VOSL- Output (-) of sled driver

12 VOSL+ Output (+) of sled driver

13 VOFC- Output (-) of focus driver

14 VOFC+ Output (+) of focus driver

28

10k

STAND

BY

THERMAL

SHUT DOWN

20k

7.5k

10k

1272263254245236227

Pin

Name

7.5k

20k

7.5k

Function

DET.AMP.

x2

7.5k

x2

DET.AMP.

15

16

17

18

19

20

21

Pin

PGNDPreGND

LOADING

DRIVER

SLED

DRIVER

PGND

11

10

9

ACTUATOR

DRIVER

ACTUATOR

DRIVER

14

13

12

Function

PVcc2

10k 15k

10k

25k

Pin

No.

Vcc PVcc1

8

Name

15 VOTK+ Output (+) of tracking driver

16 VOTK- Output (-) of tracking driver

17 VOLD+ Output (+) of loading driver

18 VOLD- Output (-) of loading driver

19 PGND Power GND

20 VNFTK Tracking driver feedback pin

21 PVcc2 Power Vcc for actuator driver

22 PreGND Pre GND

23 VINLD Loading driver input

24 CTKerr2 Cap. connection pin for error amp filter

25 CTKerr1 Cap. connection pin for error amp filter

26 VINTK Tracking driver input

27 BIAS Bias input

28 STBY Standby pin

PVcc1

PVcc2

Vcc

29DN-S3000

AK4353VF (DS: IC709)

1MCKO

TX

DVDD

DVSS

MCKI

BICK

SDTI 7