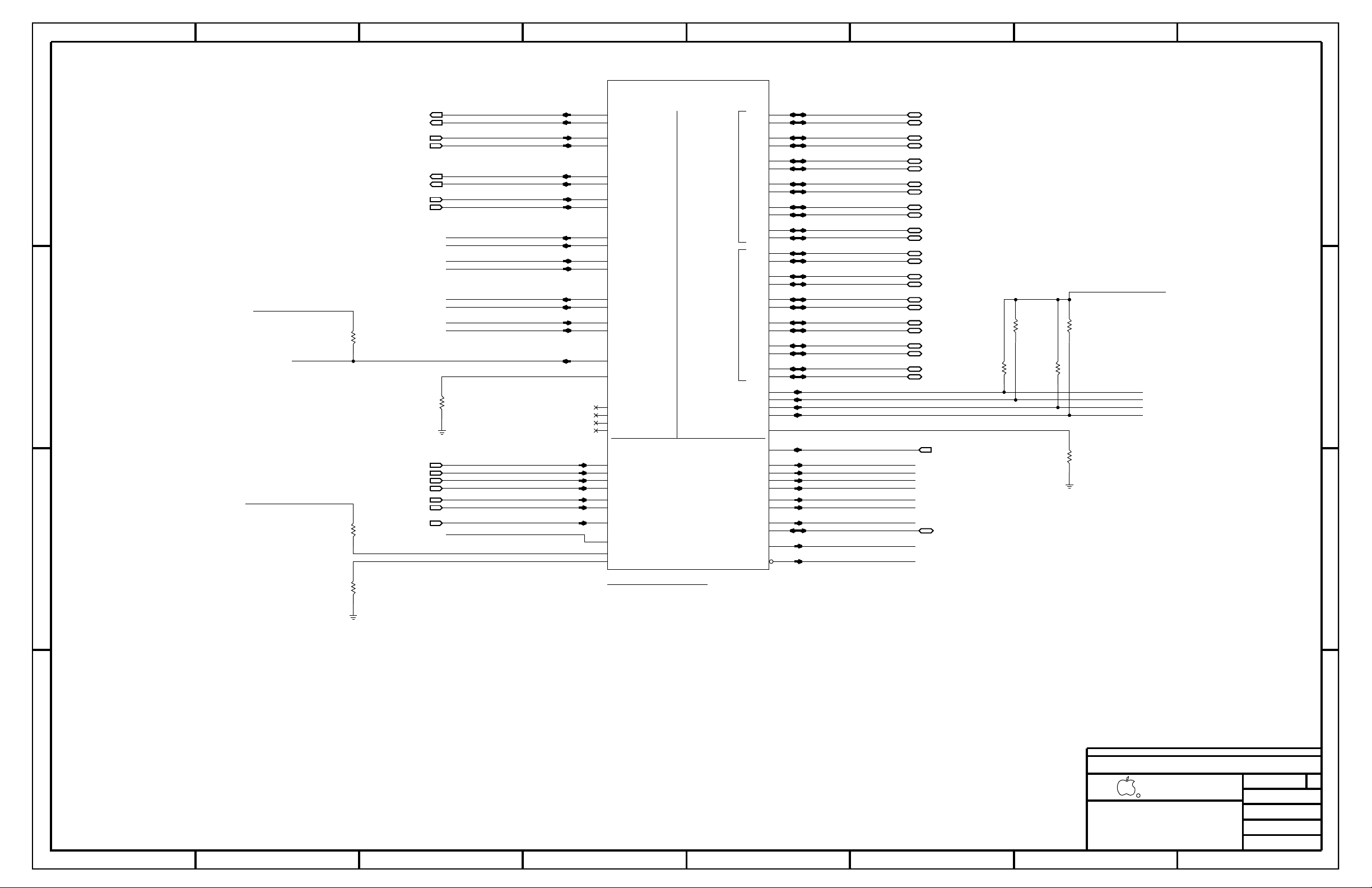

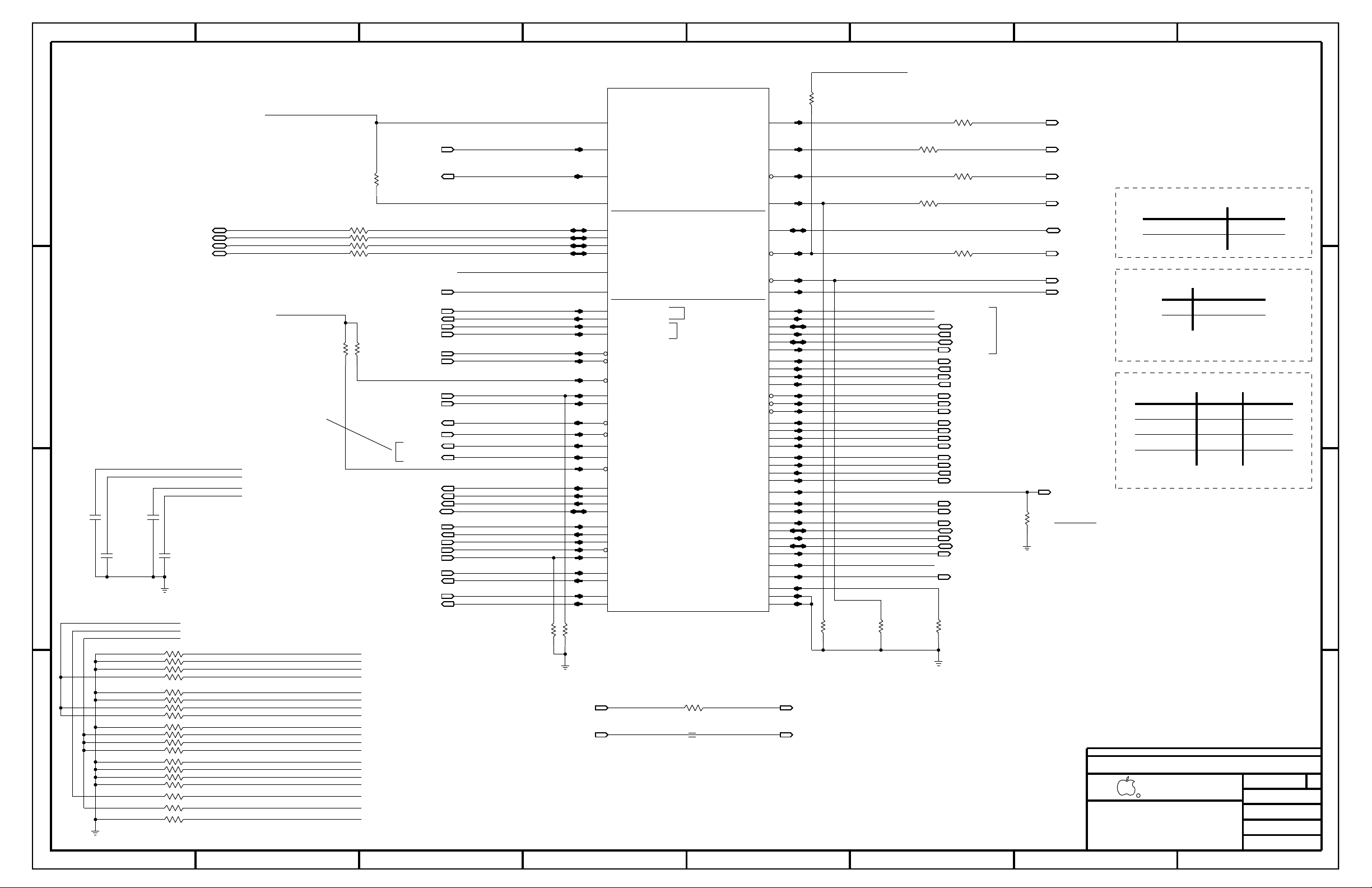

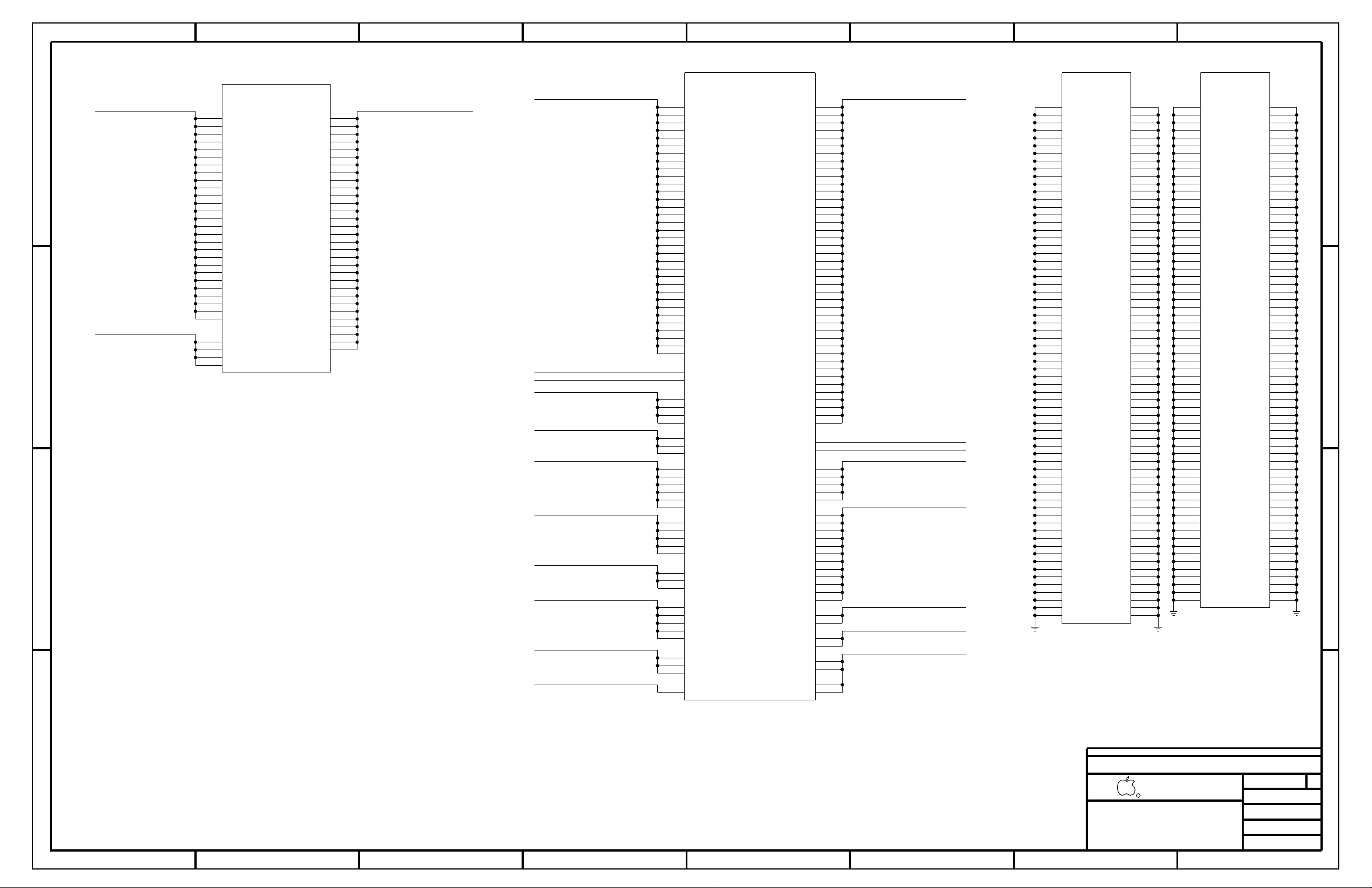

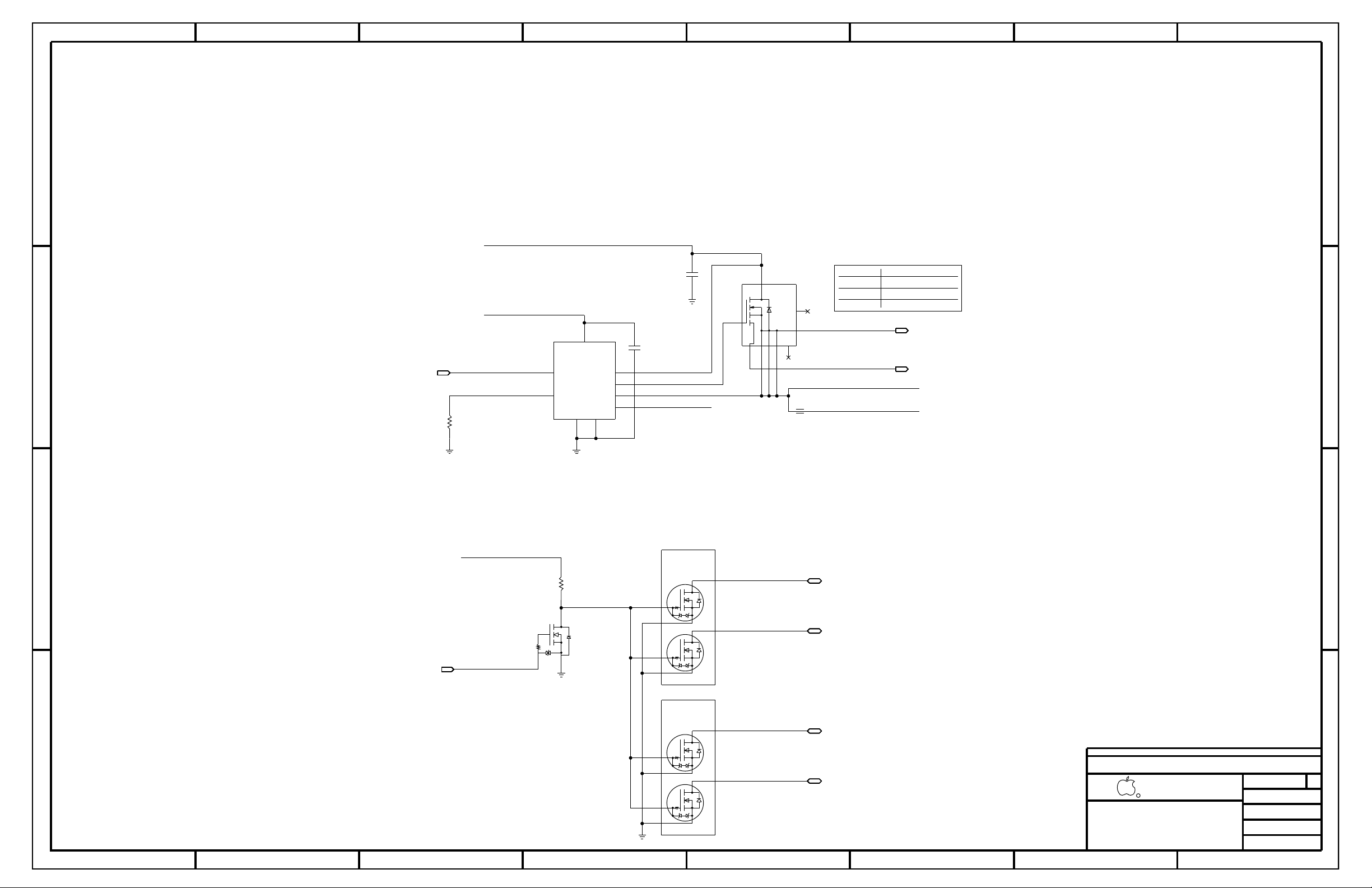

Apple macbook unibody a1342 Schematics

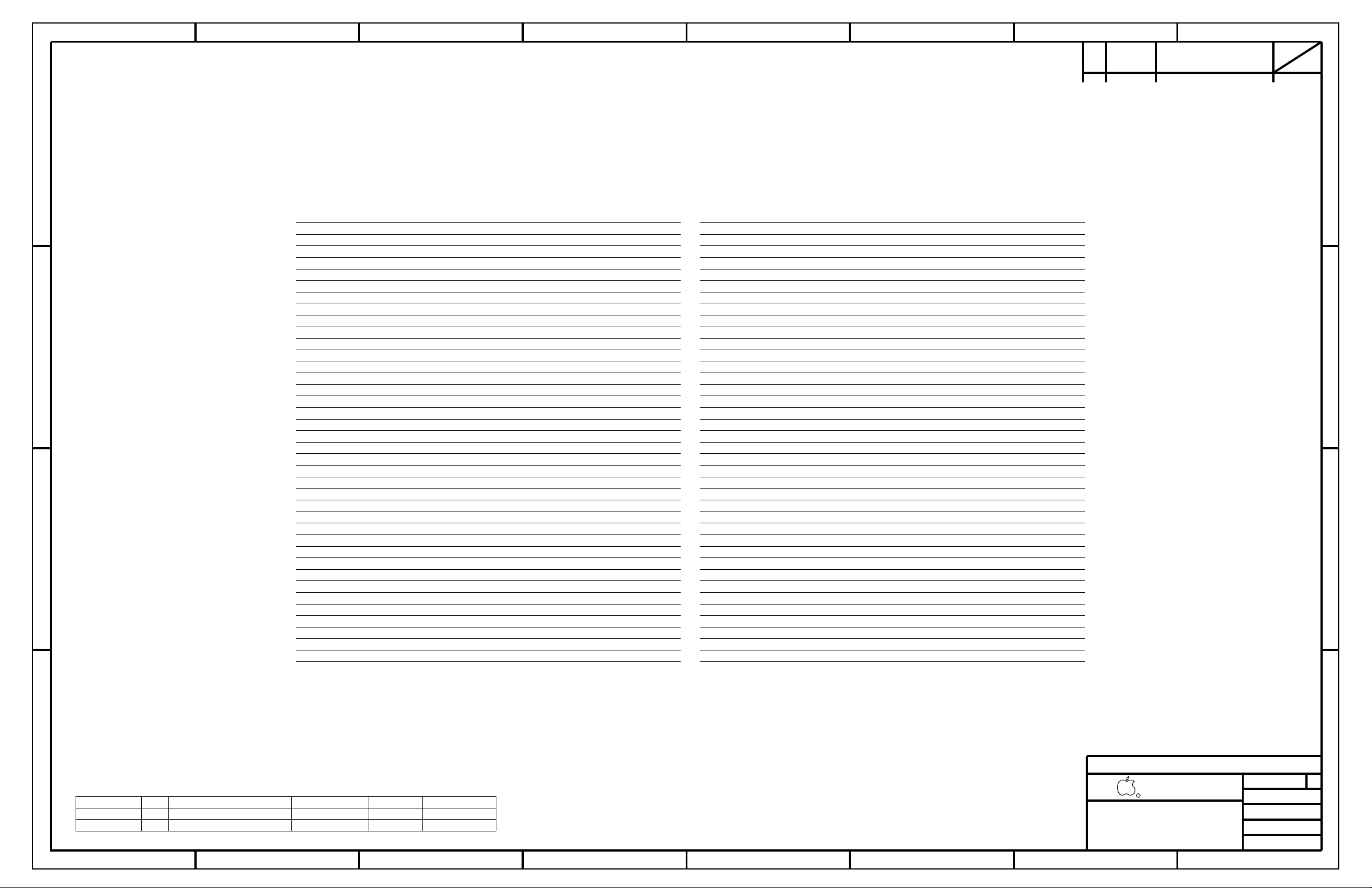

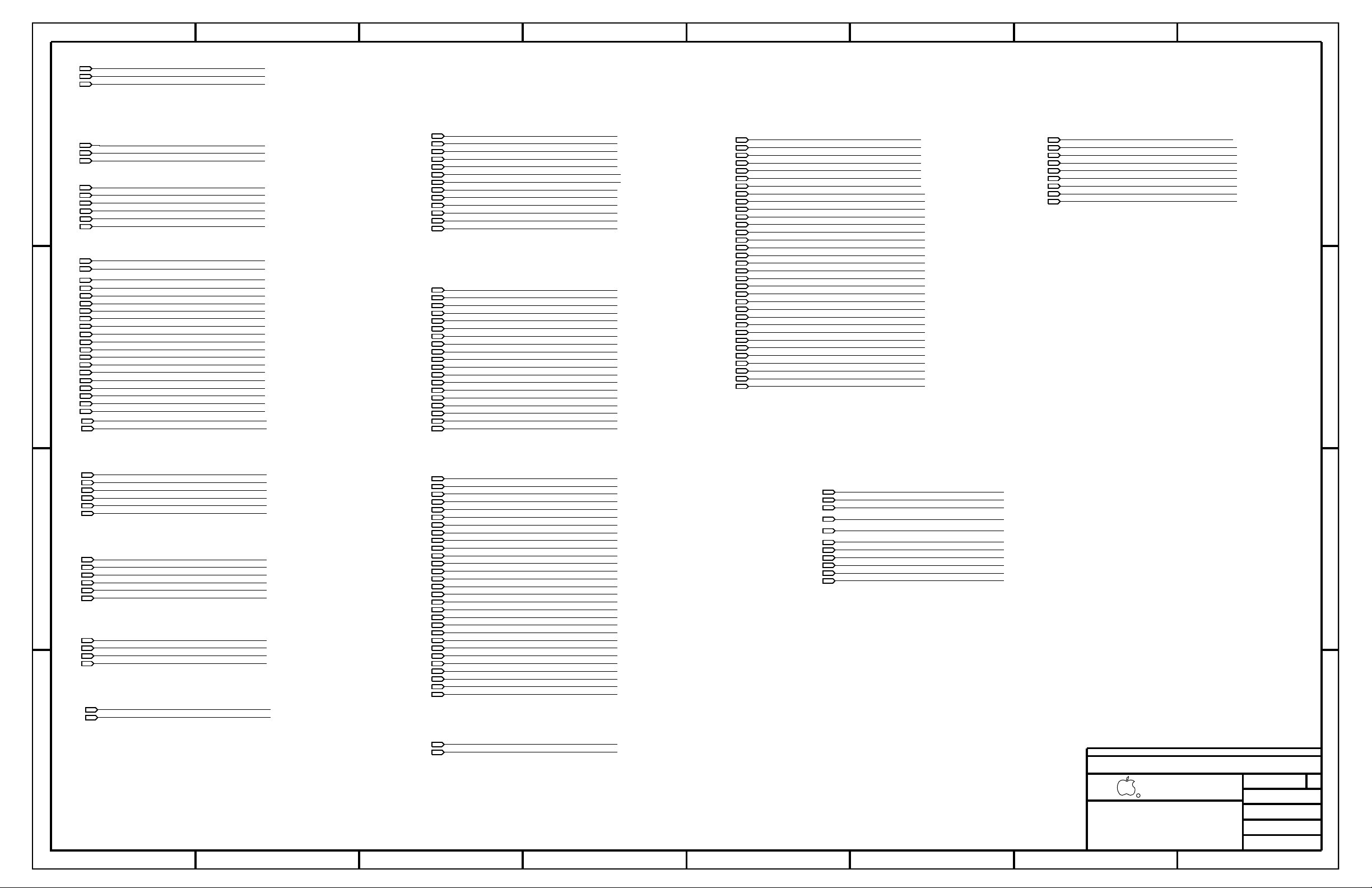

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

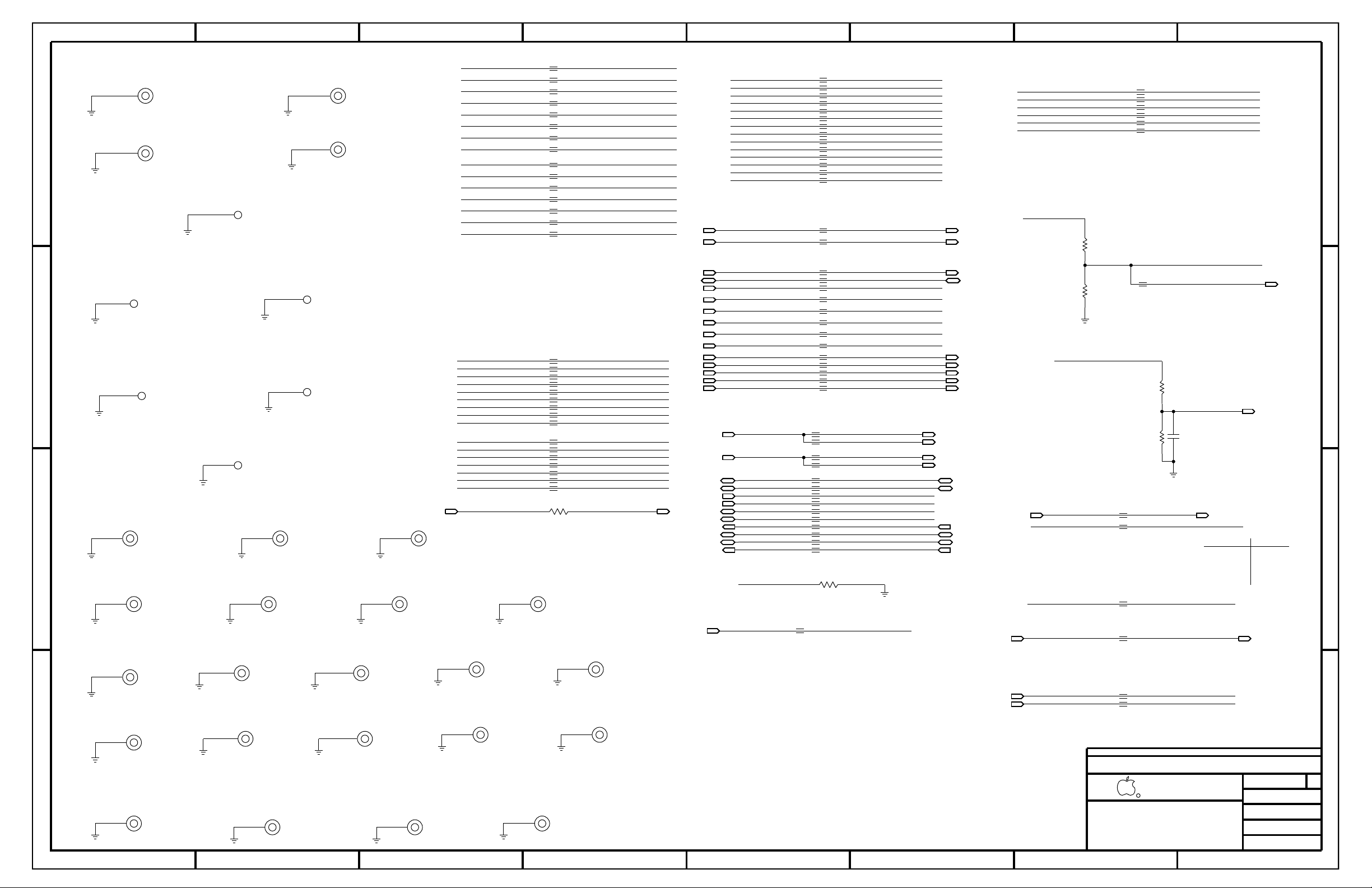

TABLE_TABLEOFCONTENTS_HEAD

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_HEAD

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

8

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

3

B

7

ECNREV

BRANCH

DRAWING NUMBER

REVISION

SIZE

D

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

DRAWING TITLE

THE POSESSOR AGREES TO THE FOLLOWING:

Apple Inc.

SHEET

R

DATE

D

A

C

THE INFORMATION CONTAINED HEREIN IS THE

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

C

3456

D

B

8 7 6 5 4 2 1

12

APPD

CK

DESCRIPTION OF REVISION

04/26/2010

Schematic / PCB #’s

SCRATCHO

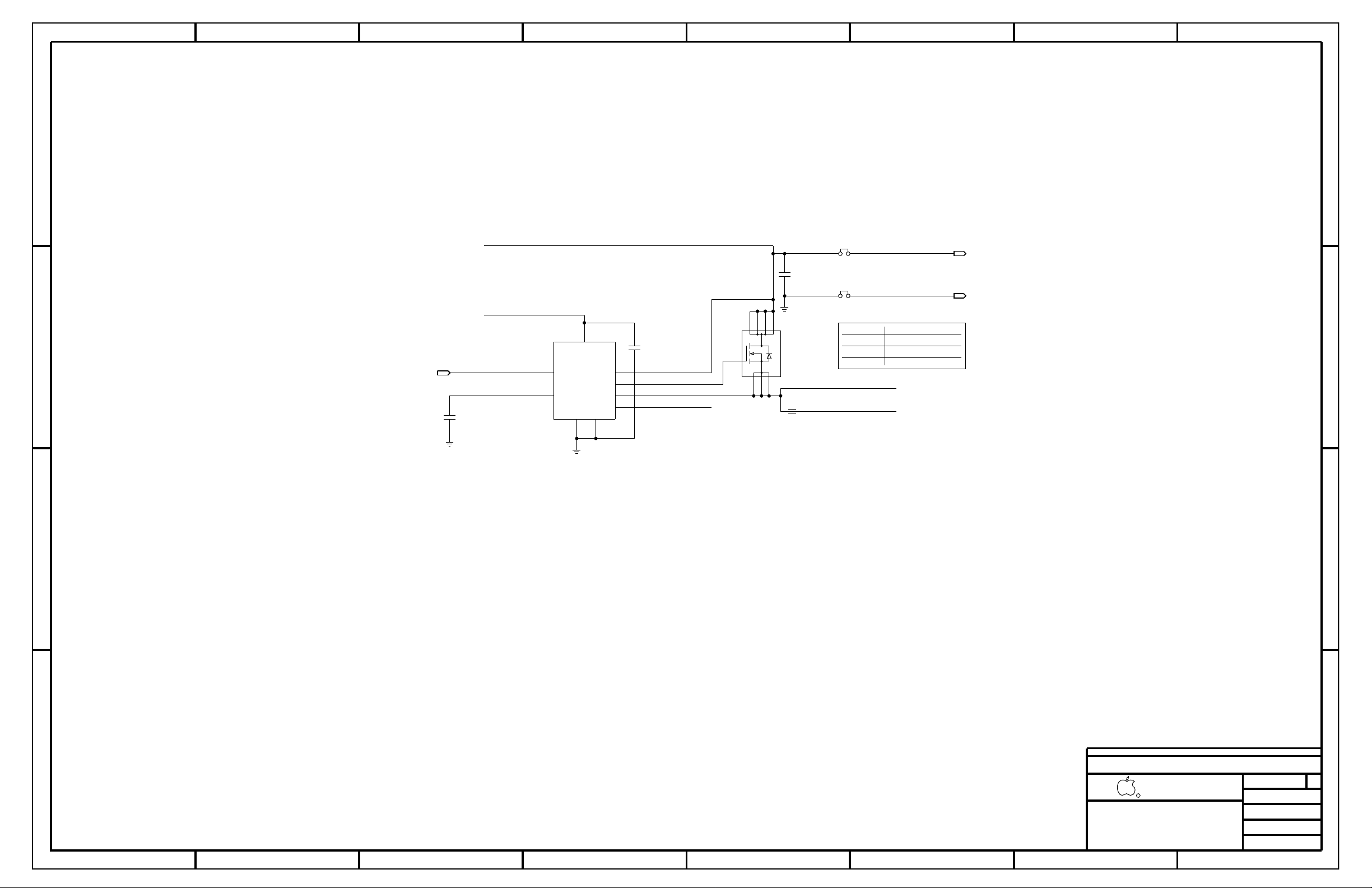

SCHEM MLB_LDO K87

1 OF 76

0000897412

C

051-8561

C.0.0

1 OF 109

PRODUCTION RELEASED

2010-04-26

52

38

MASTER

MASTER

K87 SMBus Connections

51

37

(T27_MLB)

(12/15/2009)

LPC+SPI Debug Connector

50

36

(T27_MLB)

(10/27/2009)

SMC Support

49

35

T27_MLB

02/16/2010

SMC

46

34

(K84_MLB)

(10/03/2009)

External USB Connectors

45

33

MASTER

MASTER

SATA Connectors

39

32

MASTER

MASTER

ETHERNET CONNECTOR

37

31

MASTER

MASTER

Ethernet PHY (RTL8211CL)

34

30

MASTER

MASTER

X16 WIRELESS CONNECTOR

33

29

T27_MLB

02/16/2010

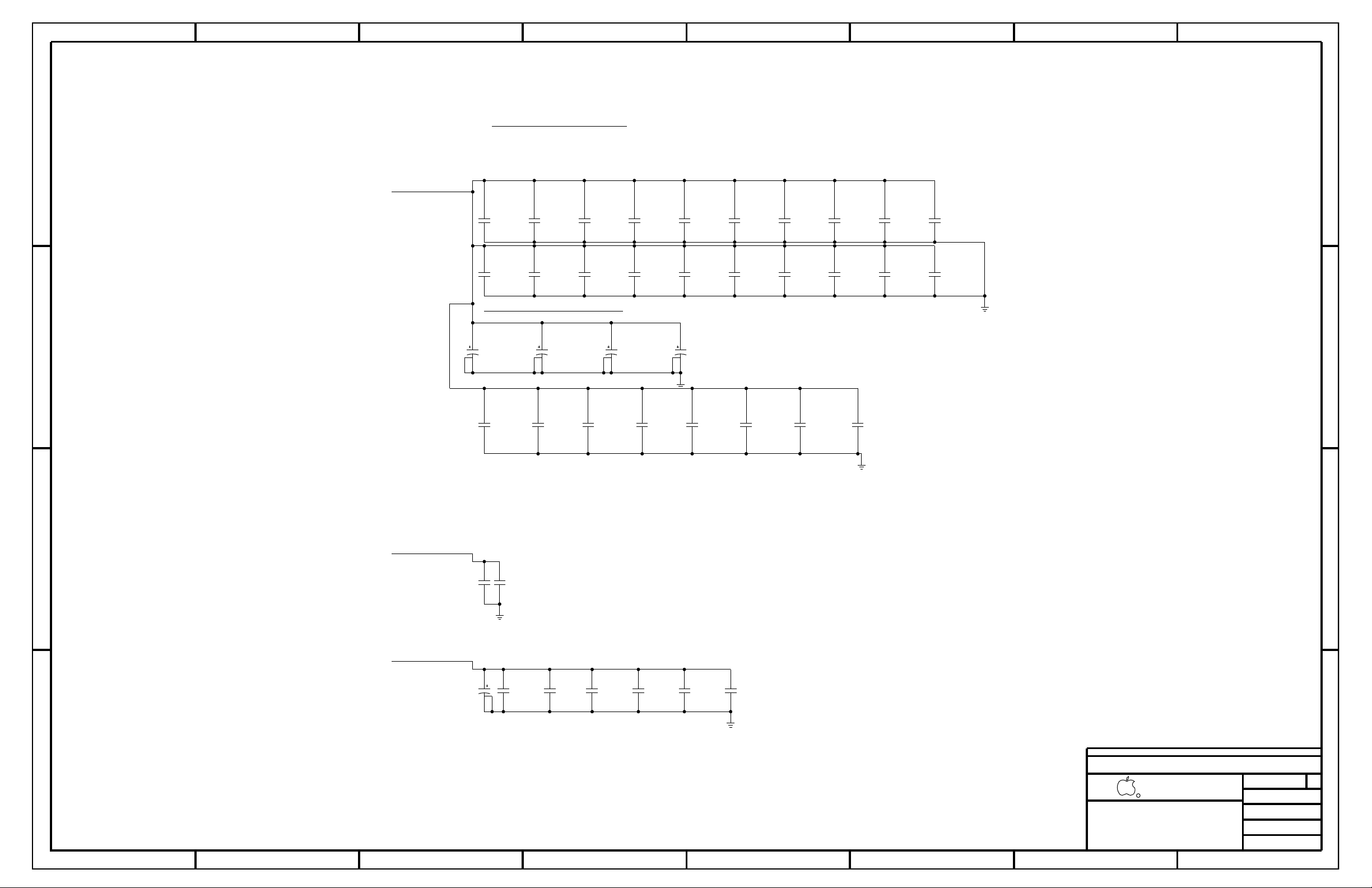

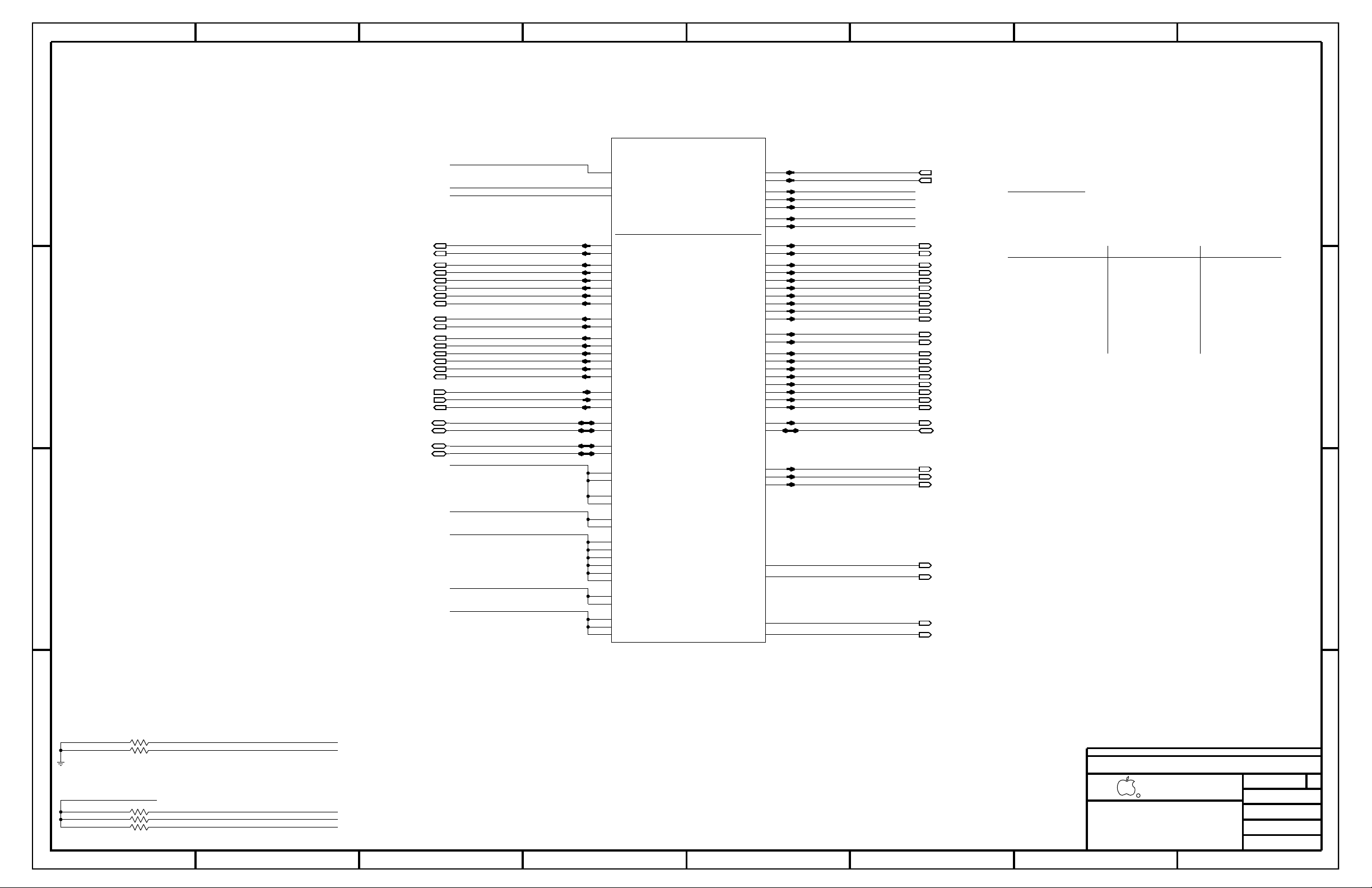

FSB/DDR3 Vref Margining

32

28

MASTER

MASTER

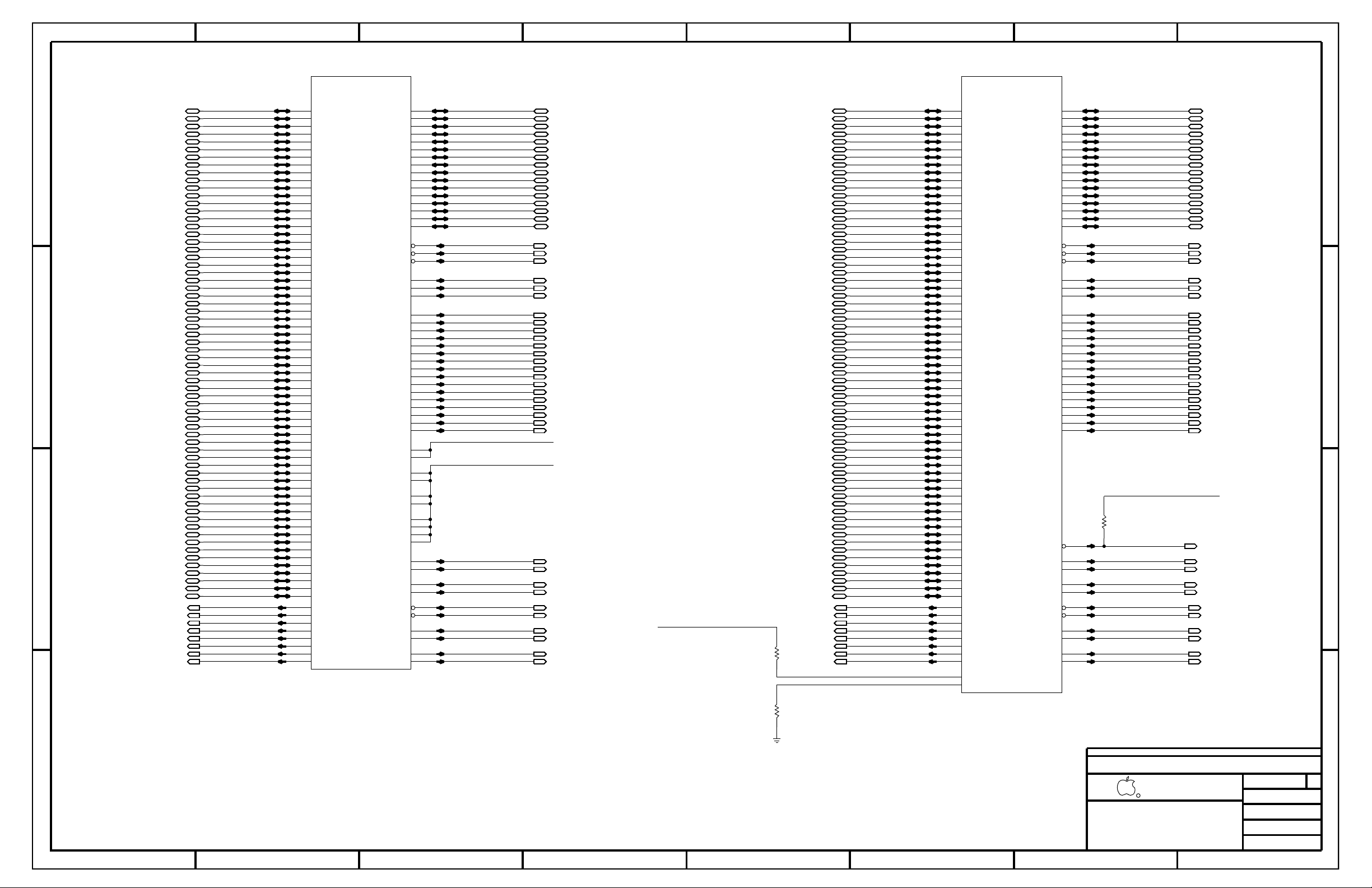

SO-DIMM Pinswaps

31

27

T27_MLB

02/16/2010

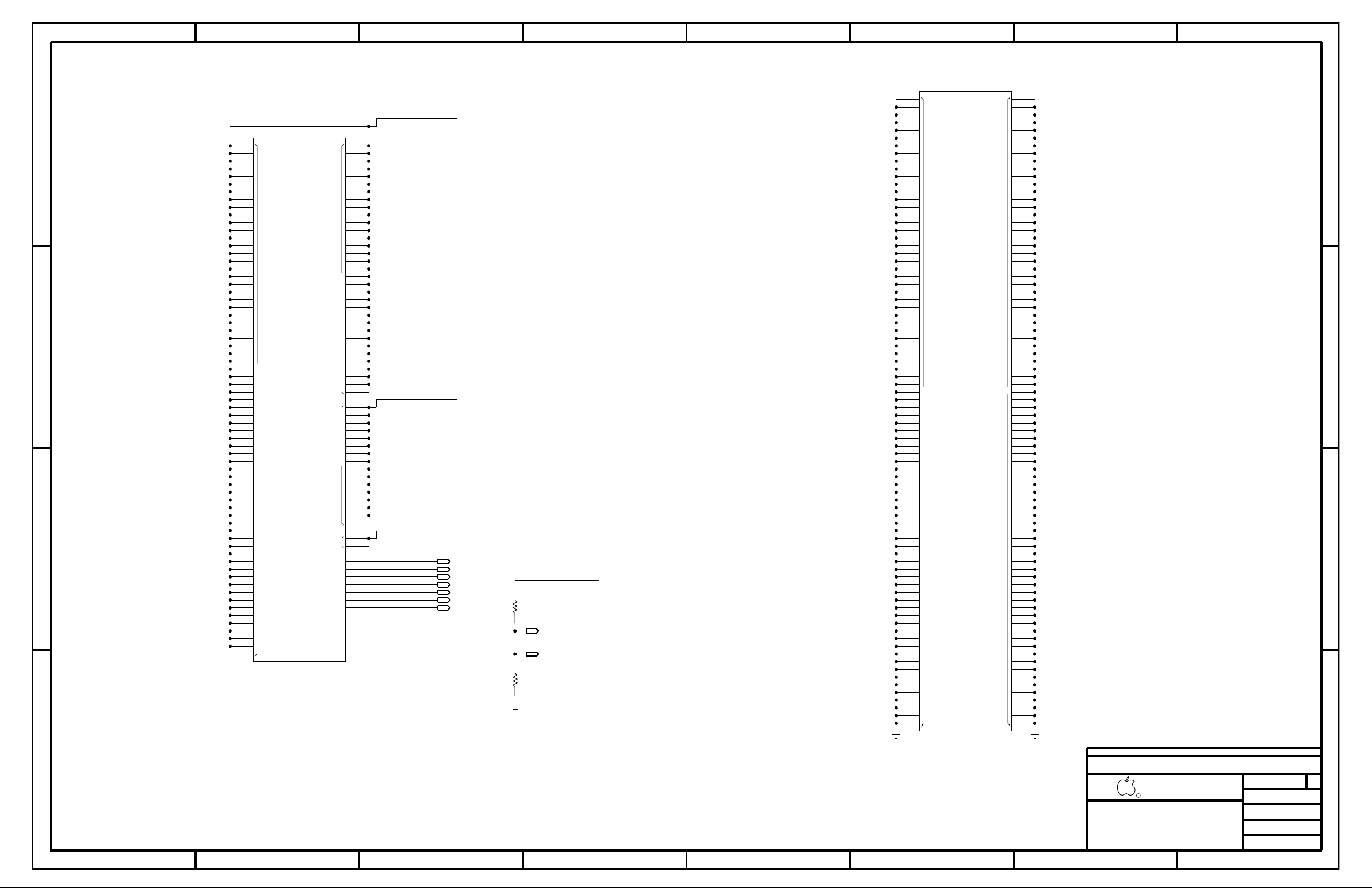

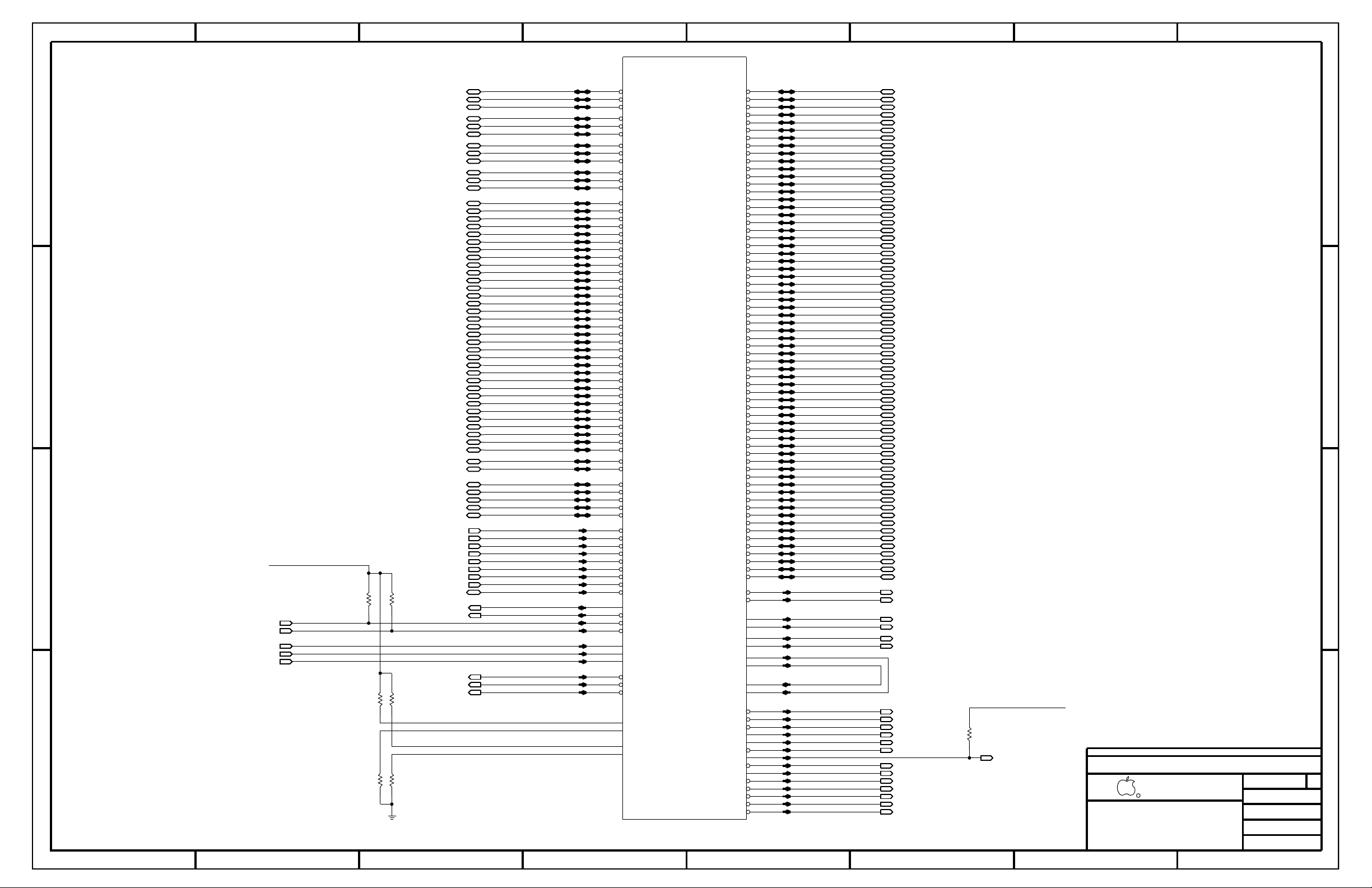

DDR3 SO-DIMM Connector B

29

26

T27_MLB

02/16/2010

DDR3 SO-DIMM Connector A

28

25

(T27_MLB)

(10/07/2009)

SB Misc

26

24

T27_MLB

02/16/2010

MCP Graphics Support

25

23

(T27_MLB)

(11/16/2009)

MCP Standard Decoupling

24

22

T27_MLB

12/15/2009

MCP89 GFX Core Rail Gating

23

21

K6_MLB

02/16/2010

MCP89 Memory Rail Gating

20

20

T27_MLB

02/16/2010

MCP Power & Ground

19

19

T27_MLB

02/16/2010

MCP HDA, LPC & MISC

18

18

T27_MLB

02/16/2010

MCP SATA, USB & Ethernet

17

17

T27_MLB

02/16/2010

MCP Graphics

16

16

T27_MLB

02/16/2010

MCP PCIe Interfaces

15

15

T27_MLB

02/16/2010

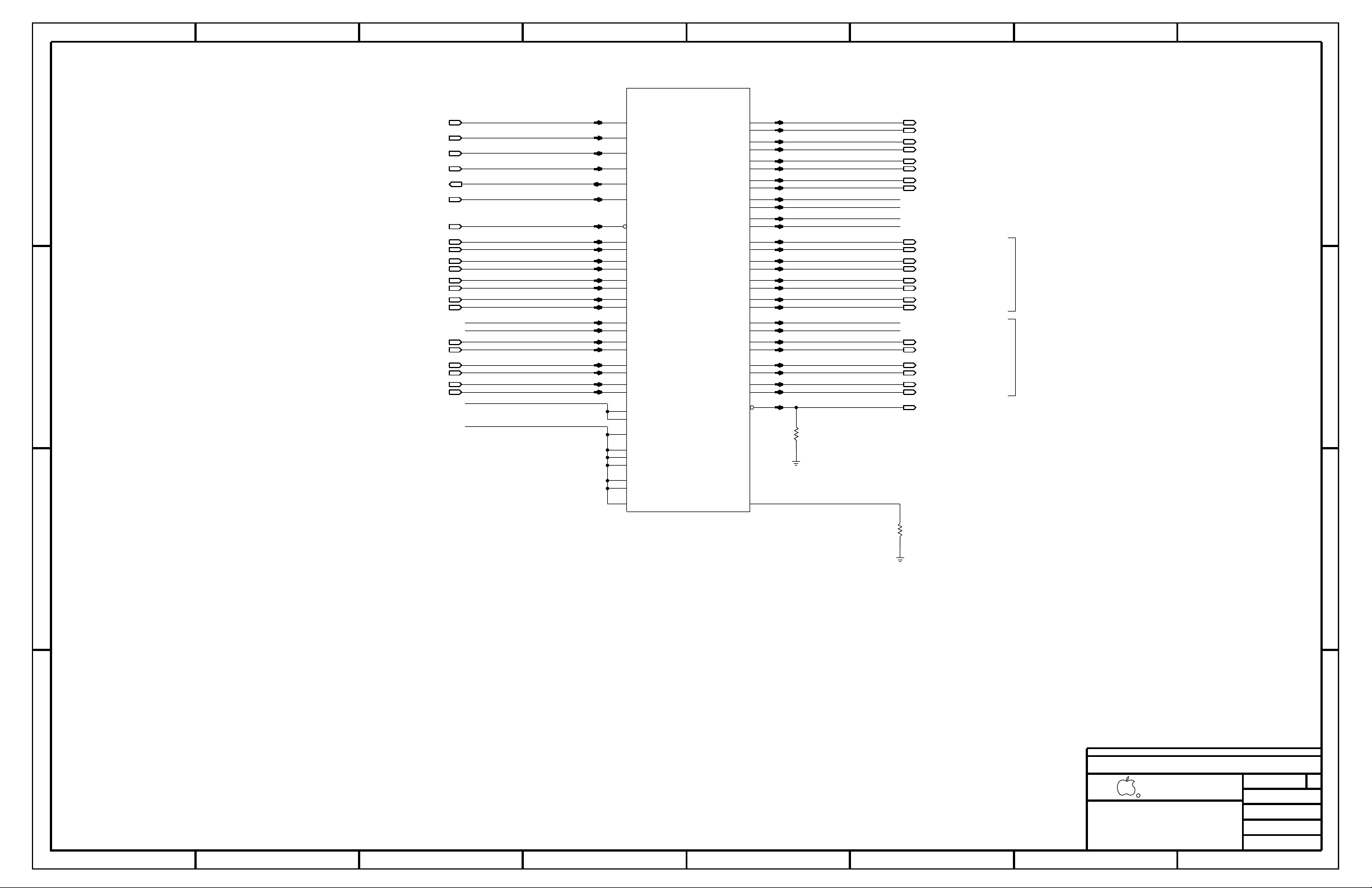

MCP Memory Interface

14

14

T27_MLB

02/16/2010

MCP CPU Interface

13

13

(K84_MLB)

(02/25/2009)

eXtended Debug Port(MiniXDP)

12

12

T27_MLB

02/16/2010

CPU Decoupling

11

11

T27_MLB

02/16/2010

CPU Power & Ground

10

10

T27_MLB

02/16/2010

CPU FSB

9

9

(K84_MLB)

(02/04/2009)

SIGNAL ALIAS

8

8

MASTER

MASTER

Power Aliases

7

7

MASTER

MASTER

FUNC TEST

6

6

MASTER

MASTER

Revision History

5

5

MASTER

MASTER

Revision History

4

4

(K84_MLB)

(01/19/2009)

BOM Configuration

3

3

MASTER

MASTER

Power Block Diagram

2

2

MASTER

MASTER

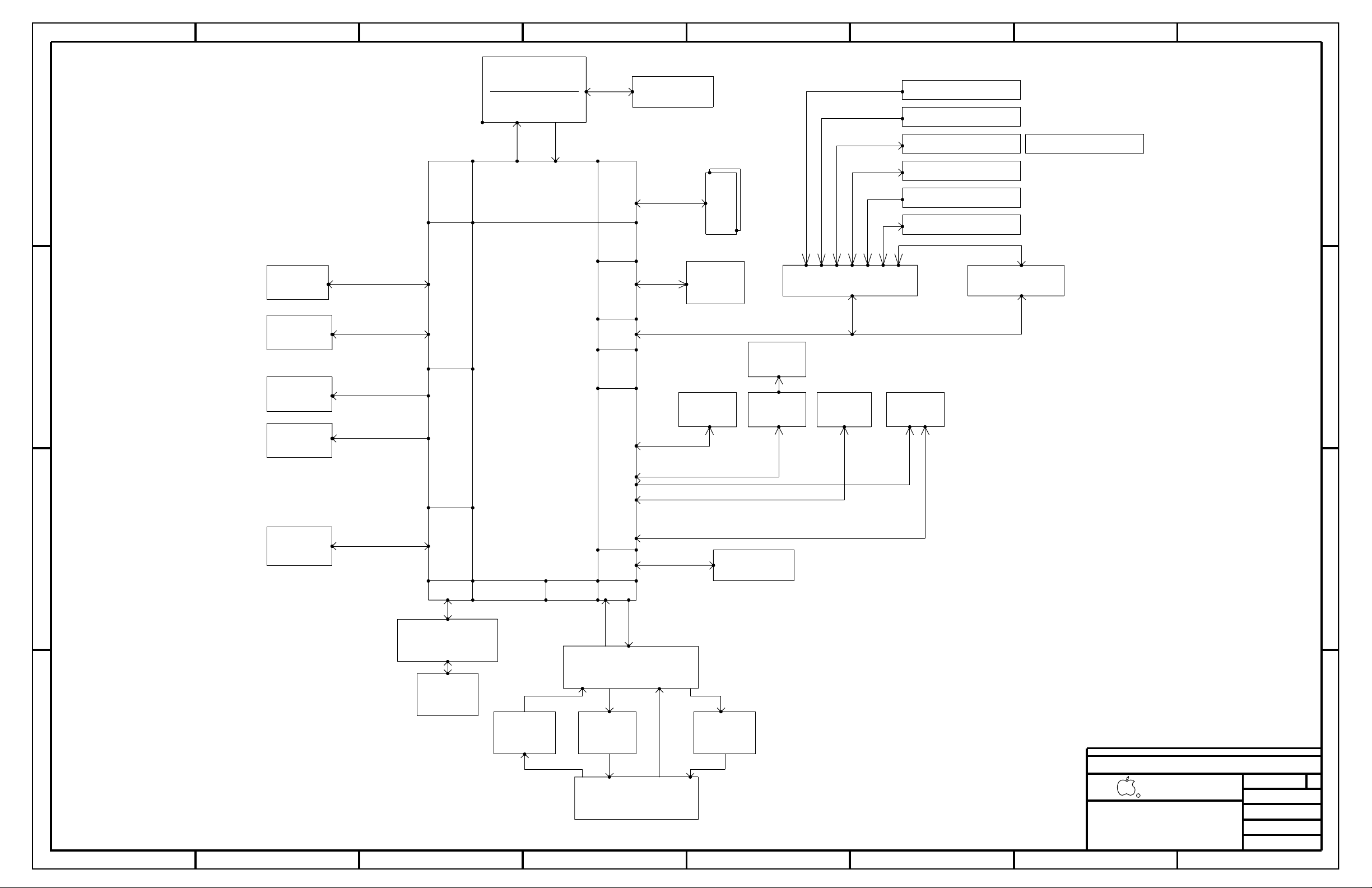

System Block Diagram

109

K87 RULE DEFINITIONS

MASTER

MASTER

76

108

K87 SPECIFIC CONSTRAINTS

MASTER

MASTER

75

106

SMC Constraints

02/16/2010

T27_MLB

74

104

Ethernet Constraints

MASTER

MASTER

73

103

MCP Constraints 2

02/16/2010

T27_MLB

72

102

MCP Constraints 1

02/16/2010

T27_MLB

71

101

Memory Constraints

02/16/2010

T27_MLB

70

100

CPU/FSB Constraints

02/16/2010

T27_MLB

69

98

LCD Backlight Support

(10/19/2009)

(K84_MLB)

68

97

LCD Backlight Driver (MC34845)

MASTER

MASTER

67

94

DisplayPort Connector

MASTER

MASTER

66

93

DISPLAYPORT SUPPORT

02/16/2010

K6_MLB

65

90

LVDS CONNECTOR

(10/19/2009)

(K84_MLB)

64

79

POWER FETS

MASTER

MASTER

63

78

Power Sequencing

(10/27/2009)

(T27_MLB)

62

77

Misc Power Supplies

MASTER

MASTER

61

76

CPU VTT(1.05V) SUPPLY

(02/04/2009)

(K84_MLB)

60

75

MCP VCore Regulator

(10/27/2009)

(K6_MLB)

59

74

IMVP6 CPU VCore Regulator

(11/18/2009)

(K84_MLB)

58

73

1.5V/0.75V DDR3 SUPPLY

(11/06/2009)

(K6_MLB)

57

72

5V/3.3V SUPPLY

(10/27/2009)

(K6_MLB)

56

70

PBus Supply & Battery Charger

(11/06/2009)

(K6_MLB)

55

69

DC-In & Battery Connectors

MASTER

MASTER

54

68

AUDIO: JACK TRANSLATORS

02/16/2010

AUDIO

53

67

AUDIO: JACK

02/16/2010

AUDIO

52

66

AUDI0: SPEAKER AMP

02/16/2010

AUDIO

51

65

AUDIO: HEADPHONE FILTER

02/16/2010

AUDIO

50

63

AUDIO: LINE INPUT FILTER

02/16/2010

AUDIO

49

62

AUDIO: CODEC/REGULATOR

02/16/2010

AUDIO

48

61

SPI ROM

02/16/2010

T27_MLB

47

60

DEBUG SENSORS AND ADC

MASTER

MASTER

46

59

SMS

MASTER

MASTER

45

58

WELLSPRING 2

MASTER

MASTER

44

57

WELLSPRING 1

02/16/2010

T27_MLB

43

56

Fan Connector

02/16/2010

T27_MLB

42

55

Thermal Sensors

MASTER

MASTER

41

54

Current Sensing

02/02/2010

T27_MLB

40

Sync

(.csa)

Date

Contents

Page

1

1 NA

NA

Table of Contents

53

Voltage Sensing

02/16/2010

T27_MLB

39

PCBF,MLB_LDO,K87820-2877

1

PCB

CRITICAL

Date

Page

Contents

(.csa)

Sync

1

SCHEM,MLB_LDO,K87

051-8561 CRITICAL

SCH

SCHEM,MLB_LDO,SCRATCHO,K87

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

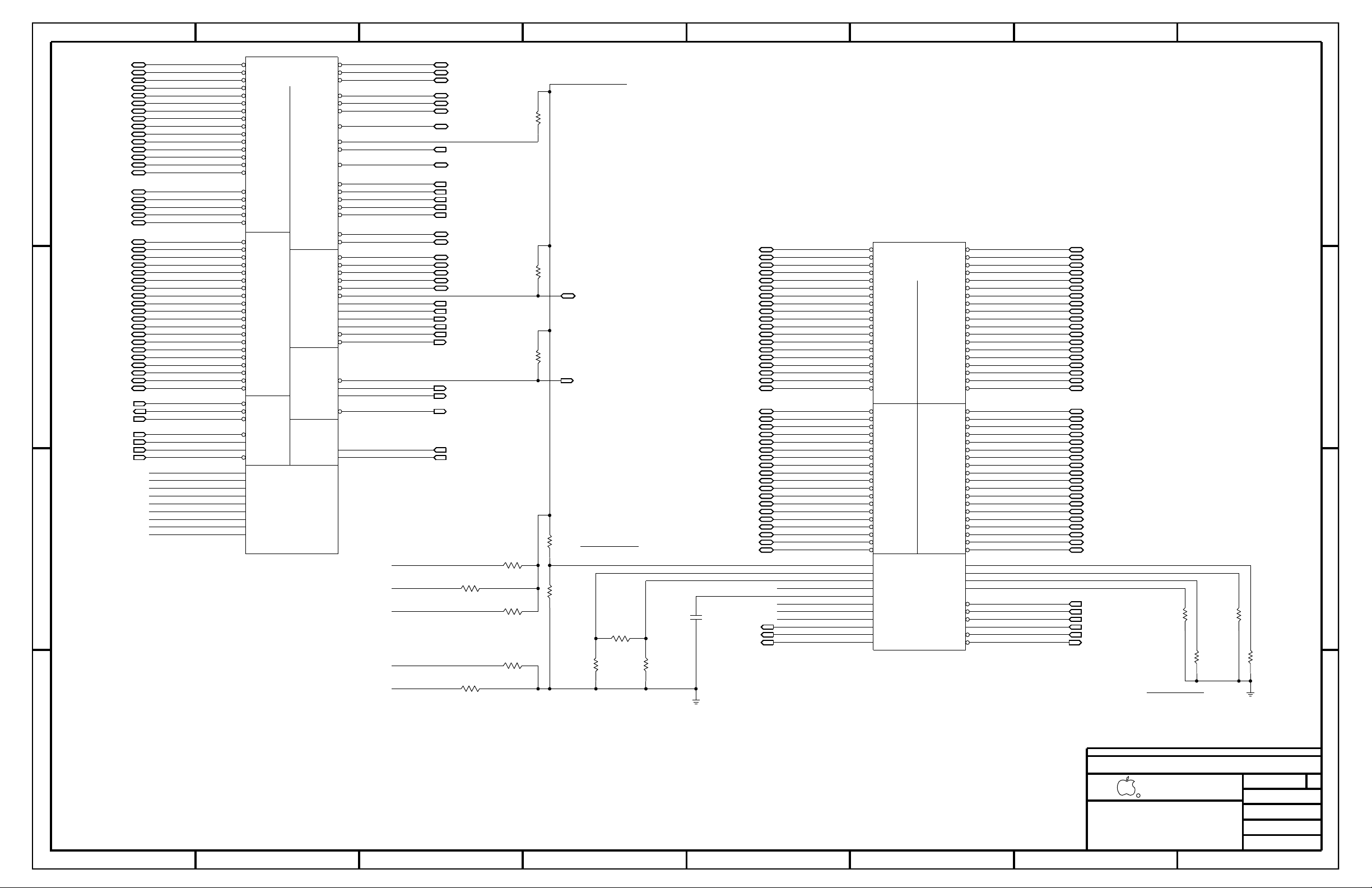

PG 18

HALL EFFECT CONN

INTEL CPU

K86K87

2.4GHZ 1.2GHZ

CULV

PENRYN

AMPS

GPIOs

PG 90

DISPLAY PORT

PG 94

SMB

PG 19

AUDIO

CODEC

PG 62

PG 63

LINE IN

FILTER FILTER

HEADPHONE

PG 65

CONNS

PG 67

J6701,J6702,J6703,J6704

AUDIO

U6201

SPEAKER

U6610, U6620, U6630

PG 66

CONN

PG 32

E-NET

U3700

J3900

PG 37

10/100/1000 E-NET

GIGABIT

PG 34

CONN

PCI

J5100

PG 51

PG 70-79

LPC+SPI CONN

POWER SUPPLY

U5535,U5515

SMS

PG 69

PG 59

PG 69,70

PG 55

PG 53,54

PG 56

DC/BATT

TEMP SENSORS

VOLTAGE AND CURRNET SENSING

POWER SENSE

FAN CONN

J6950

U5920

J6950,U7000

J5601

J3100

J2900

DIMM

PG 29,30

MINI XDP CONN

DDR3-1067/1333MHZ

J1300

PG 13

2 UDIMMs

PG 15

MEMORY

MAIN

FSB

1067/1333 MHz

Prt

Ser

Fan

ADC

J4600, J4610

PG 46

CAMERA

B,0BSB

SMC

PG 49

SMSLID

U4900

CONN

PG 58

SPI

PG 61

J5800

J9000U5701

PG 90PG 57

TRACKPAD/

KEYBOARD

BLUETOOTH

PG 34

U6100

MISC

PG 19

CTRL

PWR

PG 19

PG 18

LPC

J3401

11

10

98764 51 20

J1300

MINI XDP CONN

PG 13

HDA

PG 19

FSB INTERFACE

NVIDIA

U1400

U1000

PG 10

PG 14

PG 19

MCP

PG 18

SATA

DP OUT

HDMI OUT

20 LANES3

UP TO

PCI-E

PG 45

CONN

J4500

LVDS

J9000

SATA

ODD

AIR PORT

CONN

J3401

J9400

PG 17

MAC

RGMII

PG 16

LAN

PG 17

64-Bit

USB

CONN

TRACKPAD

BOOT ROM

SPI

PG 17

3

(UP TO 12 DEVICES)

CONN

EXTERNAL USB

DVI OUT

RGB OUT

TMDS OUT

1.05V/3GHZ.

PG 45

SATA

CONN

HD

J4501

1.05V/3GHZ.

LVDS OUT

RTL8251CA

SYNC_DATE=MASTER

SYNC_MASTER=MASTER

System Block Diagram

2 OF 109

C.0.0

051-8561

2 OF 76

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

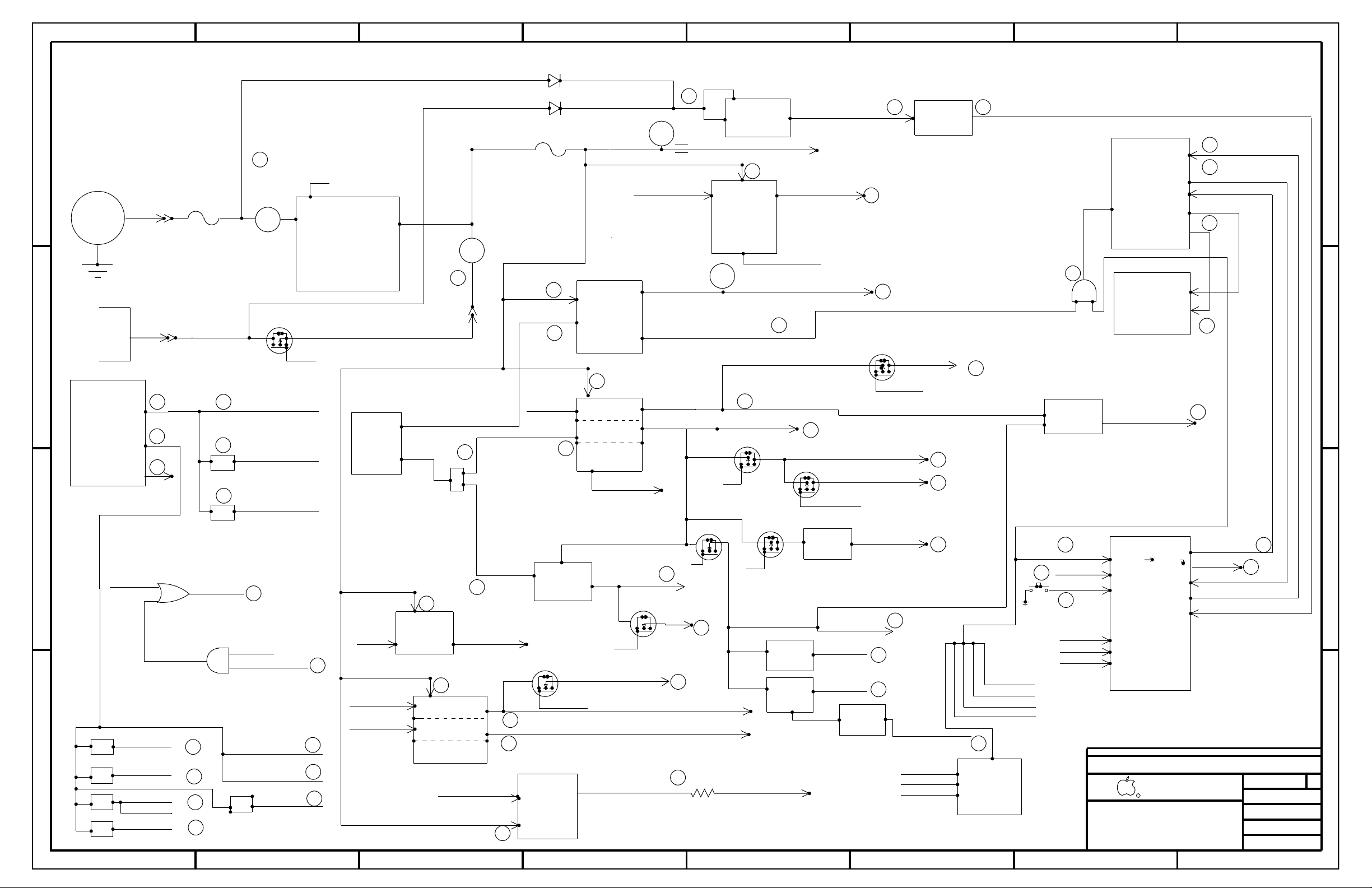

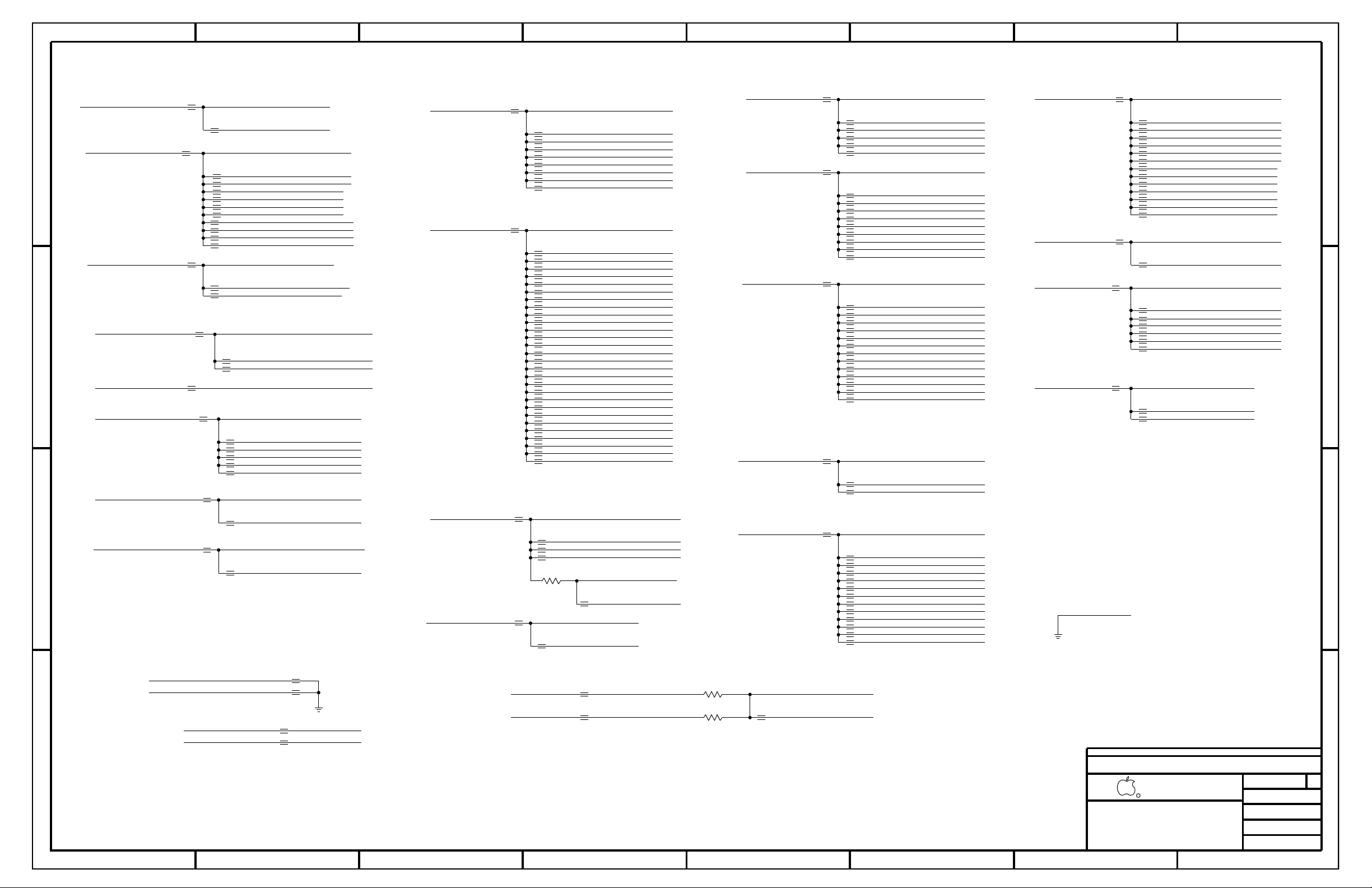

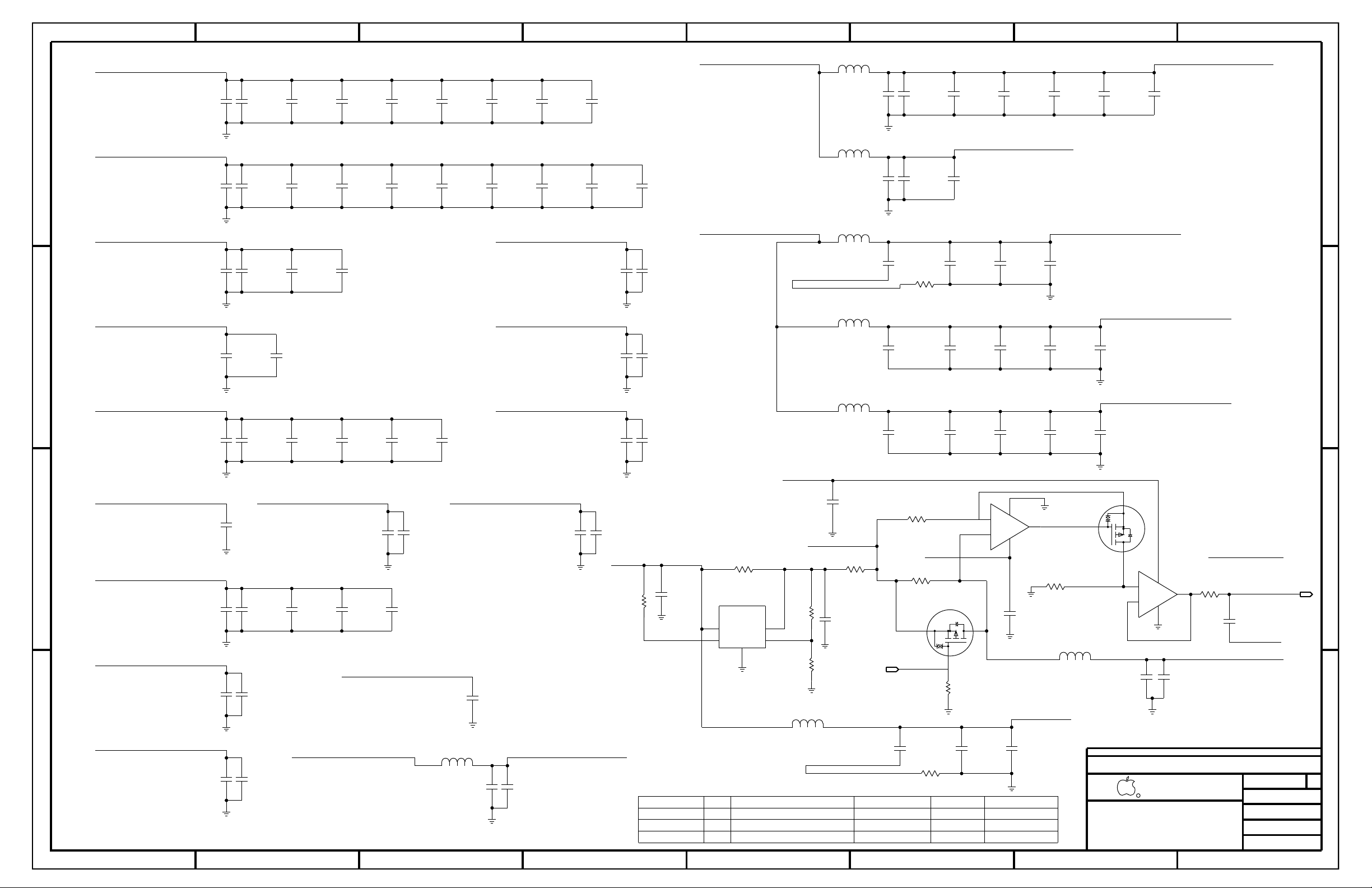

PP5V_S0_FET

Q7948

P3V3S0_EN

U7840

P5V3V3_PGOOD

PP0V9_ENET_FET

ISL8009B

VOUT

VIN

1.05V

TPS51125

PPBUS_G3H

SLP_S4_L(P94)

SLP_S4_L

SMC_BATT_ISENSE

U7100

PGOOD

(8A MAX CURRENT)

U2850

PP4V5_AUDIO_ANALOG

ALL_SYS_PWRGD

RSMRST_PWRGD

SMC_ONOFF_L

U7750

P5VS3_EN_L

PM_SLP_RMGT_L

09

PPVBAT_G3H_CONN

09-3

DELAY

MCP89

SMC_CPU_VSENSE

CPUVTTS0_PGOOD

TPS51117

SMC_CPU_ISENSE

27

02

Q5315

PBUS_G3H_VSENSE

CPUVTT

RN5VD30A-F

U5010

LT3470

CPU VCORE

SMC

ISL9563A

U7500

U7300

TPS51116

U9700

MC34845

0.75V

1.5V

S5

S3

ISL88042

U7870

PPMCPCORE_S0_REG

VOUT2

VIN

99ms DLY

SMC_RESET_L

PLT_RST*

RSMRST_OUT(P15)

PWRGOOD

Q7910

U6200

(25A MAX CURRENT)

1.5V

PP1V8_S0_REG

P0V9_ENET_EN

P0V9S5_EN

15-2

P3V3S0_EN

PM_SLP_S3_L

BKLT_EN

BKLT_EN

ENA

Q7890,Q7891

VIN

VOUT1

U6990

CHGR_EN

PBUS SUPPLY/

CPUVTTS0_EN

(S0)

6A FUSE

R7020

ENABLES

BATTERY CHARGER

02

IMVP_VR_ON_R

24

VOUT

PP1V05_S0

PGOOD

F7040

02

PPDCIN_G3H_OR_PBUS

(1.05V)

EN_PSV

U7600

VIN

VOUT

21

VIN

PM_SLP_RMGT_L

12

02

10

09-2

J6950

PM_SLP_S4_L

R7050

TPS62202

U7760

Q7920

AP_PWR_EN

(9 TO 12.6V)

U1400

PBUSVSENS_EN

EN

1.8V

PP1V5_S0_FET

1.05V

TPS74701

S0PGOOD_RST_L

PP1V05_S0_MCP_PLL_OR

P3V3S3_EN

VOUT

PPVOUT_SW_LCDBKLT

02

5V

(RT)

PGOOD1,2

VOUT

CURRENT)

12

11

PP1V05_S0_REG

NCP1529

Q7930

3.3V

VREG3

P5VS3_EN_L

P3V3S5_EN_L

Q7960

U7710

VOUT1

04

FDC638P

PP3V3_S0_FET

19

17

04

04

P60

U7740

PP1V05_S0

PP1V5_S0

PP3V3_S0

V2

V3

V1

RST*

20

MCPPLLDO_PGOOD

MCPCORES0_PGOOD

CPUVTTS0_PGOOD

MCPCORES0_EN

SMC_ADAPTER_EN

MCP_CORE

EN

VOUT

PPMCPCORE_S0_R

R7525

Q7890

PM_WLAN_EN_L

15

Q7930

17

PP3V3S0_EN

10

(S5)

EN2

EN1

VIN

U7201

06

28

MCP_PS_PWRGD

U1000

CPU

PWRGD

U1400

MCP89

CPU_RESET#

PWRBTN*

PLTRST*

RESET*

CPUPWRGD(GPIO49)

RSMRST*

FSB_CPURST_L

29

LPC_RESET_L

CPU_PWRGD

30

08-1

PM_RSMRST_L

PWR_BUTTON(P90)

RSMRST_IN(P13)

21

=DDRREG_EN

RC

=DDTVTT_EN

04-1

VIN

01

A

VR_ON

PPVBAT_G3H_CHGR_R

Q7055

U7000

ISL6259

SMC

25

3.425V G3HOT

DELAY

09-1

PWRGD(P12)

IMVP_VR_ON(P16)

18-2

15-1

PM_SLP_S3_L

IMVP_VR_ON_R

24

PM_PWRBTN_L

23

08

09

PP1V5R1V35_SW_MCP

PP1V5_S3_REG

(1A MAX CURRENT)

(12A MAX CURRENT)

13

VOUT2

15-1

15-6

P5VS0_EN

15-5

15-4

15-3

MCPCORES0_EN

DELAY

RC

DELAY

RC

DELAY

DELAY

RC

RC

P1V8S0_EN

CPUVTTS0_EN

P1V5S0_EN

DDRVTT_EN

3S2P

RC

DELAY

RC

(S0)

(S0)

02

VIN

02

ADAPTER

AC

IN

DCIN(16.5V)

F6905

01

A

VIN

(S5)

PP18V5_DCIN_CONN

PPVBAT_G3H_CHGR_REG

Q7085

Q7080

8A FUSE

ISL9504B

SLP_S5_L

SLP_S3_L

SLP_S3_L(P93)

SLP_S5_L(P95)

U4900

PPBUS_G3H

V

ENABLE

VOUT

PP3V42_G3H_REG

03

SMC PWRGD

04

RST*

P17(BTN_OUT)

SMC_DCIN_ISENSE

CHGR_BGATE

U4900

Q3450

P3V3ENET_EN_L

VOUT

MAX8840

EN

4.5V AUDIO

18

18

11

PP5V_S3_REG

(13A MAX CURRENT)

PP3V3_S5_REG

(5.5A MAX

SMC_PM_G2_EN

P16

22

PP0V75_S0_REG

(44A MAX CURRENT)

PPVCORE_S0_CPU

V

PP3V3_S3_FET

P3V3_S3_WLAN

16

P5VS0_EN

PP0V9_S5_REG

07

K86/K87 POWER SYSTEM ARCHITECTURE

VR_PWRGOOD_DELAY

P3V3S3_EN

PM_SLP_S3_L

14

DDRREG_EN

P5V3V3_PGOOD

31

PBUS_VSENSE

SYNC_MASTER=MASTER

SYNC_DATE=MASTER

Power Block Diagram

3 OF 109

C.0.0

051-8561

3 OF 76

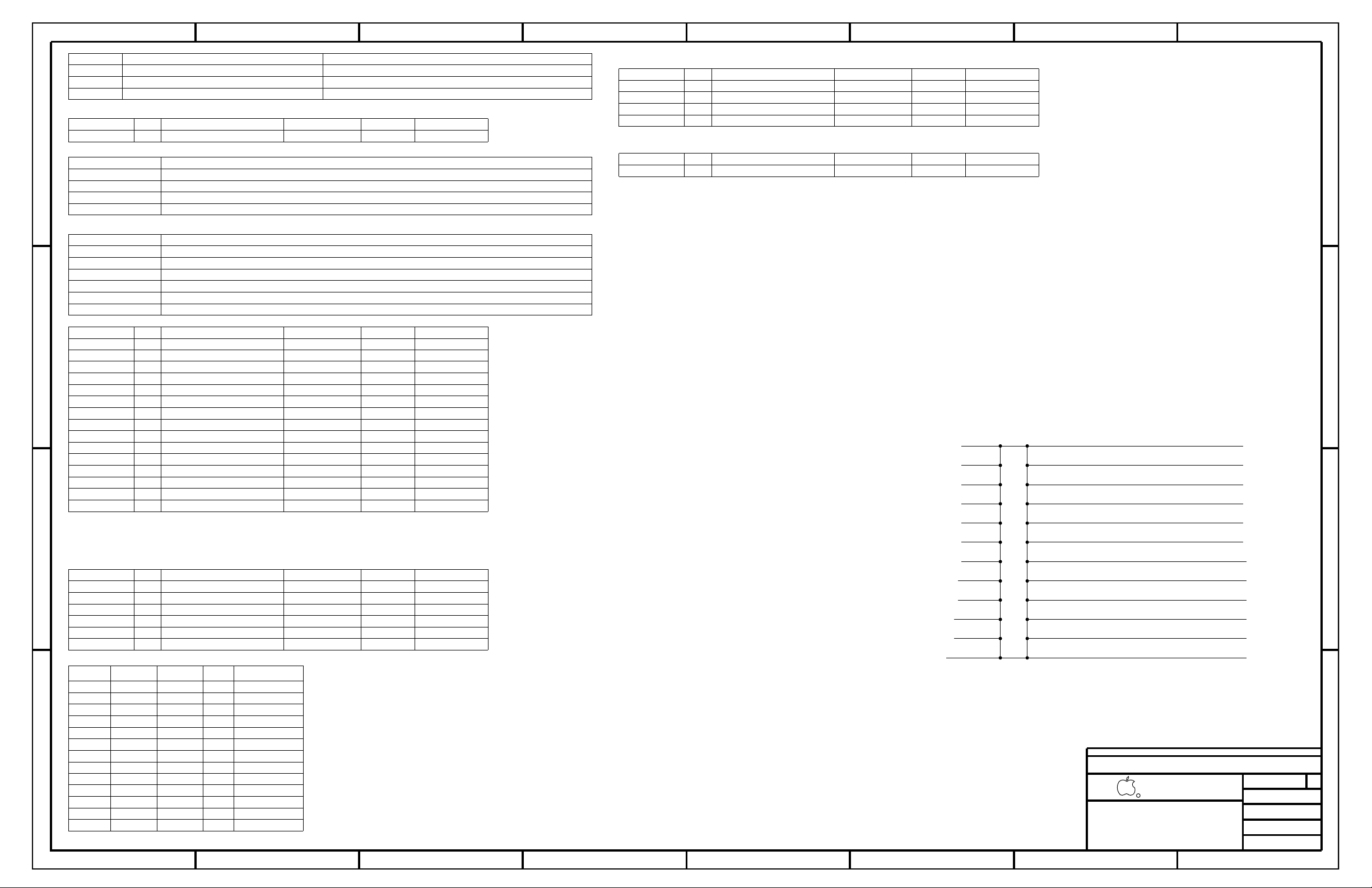

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

BOM OPTIONS

BOM NAME

BOM NUMBER

TABLE_BOMGROUP_HEAD

TABLE_ALT_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

TABLE_ALT_ITEM

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

Alternate Parts

514-0704 IS CLOUD GREY 4/LB3 PLASTIC W/PDNI PLATING VERSION OF 514-0692 PART FOR RJ45 CONNECTOR

BOM Groups (always-present)

BOM Groups (project phase-dependent)

SIGNAL(High Speed)

GROUND

SIGNAL(High Speed)

6

SIGNAL

GROUND

GROUND

POWER

5

BOTTOM

3

8

9

2

4

7

10

11

TOP

K86/K87 BOARD STACK-UP

SIGNAL

GROUND

SIGNAL(High Speed)

SIGNAL(High Speed)

Bar Code Labels / EEE #’s

Part Substitutions (differences with K6/K69)

Development BOM

BOM Variants

POWER

LOCKED BOOTROM APN IS 341S2488 (QL: old info?)

Module Parts

353S2718 IS NEW INTERSIL PART FOR FIXING B4 DONGLE ISSUE

514-0705 IS CLOUD GREY 4/LB3 PLASTIC W/PDNI PLATING VERSION OF 514-0689 PART FOR USB CONNECTORS

514-0706 IS CLOUD GREY 4/LB3 PLASTIC W/PDNI PLATING VERSION OF 514-0691 PART FOR MINI DP CONNECTOR

Programmable Parts

514-0718 IS CLOUD GREY 4/LB3 PLASTIC W/PDNI PLATING VERSION OF 514-0694 PART FOR AUDIO CONNECTOR

ZS0912,ZS0913,ZS0914,ZS0915,ZS0919

CRITICAL870-1939

5

POGO PIN,TALL,NOISE-IMPROVED,SILVER,K87

152S0685152S0796

ALL

CYNTEC AS ALTERNATE

ALL

DALE/VISHAY AS ALTERNATE

104S0018 104S0023

152S0778

DALE/VISHAY, MAGLAYERS AS ALTERNATE

ALL

ALL

DELTA AS ALTERNATE

ALL

152S0874

MAGLAYERS AS ALTERNATE

ALL

152S0847

MAGLAYERS AS ALTERNATE

114S0125

1

LED:K86_K87

R5714

RES,MTL FILM,1/16W,113 OHM,1,0402,SMD,LF

1

CRITICAL826-4393

LBL,P/N LABEL,PCB,28MM X 6 MM

[EEEE_DD19]

EEEE:DD19

826-4393

1

[EEEE_DD17]

EEEE:DD17

CRITICAL

LBL,P/N LABEL,PCB,28MM X 6 MM

LBL,P/N LABEL,PCB,28MM X 6 MM

CRITICAL

1

826-4393

[EEEE_DD16]

EEEE:DD16

DEVELOPMENT_BOM

1

085-1632 CRITICAL

DEVEL

K87 MLB_LDO DEVELOPMENT BOM

1

CDC,SLGYW,PRQ,1.2,10W,800,R0,1M,BGA

U1000

CRITICAL CPU:1.2GHZ

ZS0900,ZS0901,ZS0902,ZS0903

4

CRITICAL870-1940

POGO PIN,MED,NOISE-IMPROVED,SILVER,K87

CRITICAL

ZS0917,ZS0918,ZS0916

870-1938

3

POGO PIN,THIN,NOISE-IMPROVED,SILVER,K87

U4900

1

SUBASSY, IC, SMC, K87

CRITICAL341T0252

SMC:PROG_K87

CRITICAL

1

338S0563

U4900

SMC:BLANK

U4900

SUBASSY, IC, SMC, K86

CRITICAL341T0250

1

SMC:PROG_K86

335S0610

1

U6100

CRITICAL

BOOTROM:BLANK

U6100

CRITICAL341T0251

1

BOOTROM:PROG

IC,WELLSPRING CONTROLLER,K87

U5701

CRITICAL

1

WELLSPRING:PROG

337S2983

U5701

1

CRITICAL

WELLSPRING:BLANK

KEMET AS ALTERNATE

ALL

353S1832

ALL

NEW IMPROVED INTERSIL PART AS ALTERNATE

ALL

MURATA AS ALTERNATE

SCREW1,SCREW2,SCREW3,SCREW4

4

CRITICAL452-1708

SCR.M1.6X0.35X6.0,D4,HO.3,BLK,M97

MOLEX_DDR_CONN

CRITICAL516-0213

1

J2900

CONN,204P,SODIMM,P=0.6MM

CRITICAL

U1400

337S3866

1

MCP89M:A02

IC,MCP89M-A02,31X31MM,BGA1168

337S3680

PDC,LGDZ,PRQ,2.40,25W,1066,R0,3M,BGA

CRITICAL

U1000

CPU:2.4GHZ

1

DEBUG_ADC,LPCPLUS_CON,S0PGOOD_ISL,EFI_DEBUG,MCPPLL_LDO,EXT1V05,XDP_CON,LPCPLUS

870-1939

5

ZS0904,ZS0905,ZS0906,ZS0907,ZS0910

CRITICAL

POGO PIN,TALL,NOISE-IMPROVED,SILVER,K87

ZS0908,ZS0909,ZS0911

870-1940

3

CRITICAL

POGO PIN,MED,NOISE-IMPROVED,SILVER,K87

CONN,204P,SODIMM,SOCKET,DDR3,RAM,BGA

516S0790

MOLEX_DDR_CONN

J3100

CRITICAL

1

516-0201

FOX_DDR_CONN

CRITICAL

1

J2900

CONN,204P,SODIMM,P=0.6MM

J3100

CONN,204P,SODIMM,SOCKET,DDR3,RAM,BGA

FOX_DDR_CONN

1

CRITICAL

CRITICAL

1

U1400

MCP83M

IC,MCP83M-A02,31X31MM,BGA1168

U1400

337S3797 CRITICAL MCP89M:A01

IC,MCP89M-A01,31X31MM,BGA1168

1

K86_K87_COMMON

K86_K87_DEBUG:DEV

K86_K87_DEVELOPMENT_PVT

K86_K87_DEBUG:PRODPROJECT_PHASE:PROD

DEVELOPMENT_BOM

K86_SPECIFIC

K87_SPECIFIC

CPU:2.4GHZ,IMVP6:2PHASE,SMC:PROG_K87,MCP89M:A02

K86_K87_COMMON1

SYNC_MASTER=(K84_MLB)

BOM Configuration

SYNC_DATE=(01/19/2009)

CRITICAL

LBL,P/N LABEL,PCB,28MM X 6 MM

826-4393

1

EEEE:DD18

[EEEE_DD18]

085-1799

K86_K87_DEVELOPMENT_PVT

K87 MLB_LDO DEVELOPMENT BOM

K86_K87_COMMON,K87_SPECIFIC,MOLEX_DDR_CONN,EEEE:DD17

PCBA,MLB_LDO,MOLEX,K87

639-1116

639-1115

K86_K87_COMMON,K87_SPECIFIC,FOX_DDR_CONN,EEEE:DD16

PCBA,MLB_LDO,FOXCONN,K87

128S0093

152S0693

138S0602138S0603

353S2811

152S0516

128S0218

PROJECT_PHASE:DEV

LPCPLUS_CON,XDP_CON,VREFMRGN:YES,LPCPLUS

VREFMRGN:NO,BMON:PROD,BKLT:PROD,SENS_R:PROD,MCPHVDD:P2V5,LDO:FIXED,HTOL_SENSE:YES

VREFMRGN:YES,BMON:ENG,BKLT:ENG,SENS_R:ENG

K86_K87_COMMON1,PROJECT_PHASE:PROD,COMMON,ALTERNATE,BOOTROM:PROG,WELLSPRING:PROG,MCP_T_DIODE_SENSOR

DP_ESD,MIKEY,MCPPLL_R:REG,ENET1V05:INT,LED:K86_K87,S0PGOOD_BJT,ENET_ESD,VFRQ:SLPS3,SMC_DEBUG:YES,SPI:25MHZ,XDP,OLD_AUDIO_SWITCH

CPU:1.2GHZ,IMVP6:1PHASE,SMC:PROG_K86,MCP83M

337S3792

IC,FLASH,SPI,32MBIT,3.3V,86MHZ,8-SOP

IC,SMC,HS8/2117,9X9MM,TLP,HF

157S0055157S0058

152S0586

K86_K87_DEBUG:PROD

K86_K87_DEVELOPMENT_ONLY

337S3876

516S0706

341S2677

IC,PSOC+ W/ USB,56 PIN,MLF,CY8C24794

SUBASSY, IC, BOOT ROM, K86/K87

353S2988 353S2987

ALL

MIC5365 AS ALTERNATE

ALL

376S0634376S0908

TOSHIBA AS ALTERNATE

ALL

376S0634376S0907

ALL

FAIRCHILD AS ALTERNATE

376S0868376S0912

ONSEMI(NEW SPEC) AS ALTERNATE

4 OF 109

C.0.0

051-8561

4 OF 76

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

Changed C7428 from 0.47uF => 0.33uF (132S0101) per Intersil

T27: Changed USB_RBIAS from 931-ohms to 887-ohms per DG v1.3 (pg. 18). <radar:7459260 > Design Guide v1.3 updates

2010-04-1: A.9.0

Added ONsemi new spec part(376S0912) as an alternate to Q2300(376S0868).

2010-04-14: C.0.0

CSA 4: Added Toshiba(376S0908), Fairchild(376S0907) as an alternate to 376S0634.

2010-04-14: B.0.0

rdar://7822714

CSA 77: Deleted U7740 1.05V LDO circuit to free space for U2592 and current mirror circuit.

Reverted the changes and synced back to A.0.0

Per <rdar://7783507> K87: Add cap to DDC line to avoid DDC line glitch issue

CSA 93: Added C9303 3300pF cap on DP_CA_DET.

CSA 4: Added Alternate part for U2592 LDO. 353S2987(TI), 353S2988(Micrel) to 353S2986(Intersil).

Reverted the changes and synced back to A.2.0.

CSA 25,49,50: Changed Q2592 gate control pin to SMC_P24 from SMC_P10.

CSA 25: Added R2600 0ohm resistor to help layout change.

CSA 25: Changed R2600 refdes to R2550 to match with page#.

CSA 69: R6905 kept same 1ohm.

C6900 changed to 2.2uF. 138S0592.

CSA 4: Devel BOM# changed to 085-1799. And BOM OPTIONS to K86_K87_DEVELOPMENT_PVT.

2010-04-1: A.10.0

Added IMVP6:2PHASE to R7413 per Intersil

Cosmetic cleanup

csa 90: Deleted net properties for =PP5V_S3_CAMERA

csa 108: Added NET_PHYSICAL property to SATA_HDD_D2R_FILT_P and _N

csa 98: Deleted net properties for =PPBUS_S0_LCDBKLT

2009-12-09: 1.5.0

multiple: Added parentheses for SYNC_DATE property on all pages that have broken sync.

csa 4: Deleted entry in Module Parts table for R6612, R6617, R6630, R6633 since they were removed when we switched from piezo to dynamic speakers

csa 69: Changed J6955 symbol to K87 Hall effect assembly (339S0114)

csa 74: Changed 1PHASE BOM table to correctly call out 132S0080 (0.22uF) instead of 0.022uF

csa 54: Began syncing from T27 per <radar:7432091 > BATT_ISENSE filter change to address lower max sink current on ISL6259 BMON pin (K17 auto-shutdown issue)

2010-03-30: A.7.0

2010-03-31: A.8.0

CSA 25: Added R2591,R2594 for LDO:ADJ option. Changed U2592 to LDO:FIXED option.

LDO:FIXED, MCPHVDD:P2V5 added in bom table.

csa 72: Changed L7220 from 152S0693 to 152S0778 per <rdar://problem/7347216> K69 L7260 combo footprint

C5490 changed from CAP_402-0.022UF,10%,16V,CERM-X5R to CAP_402-0.022UF,20%,16V,CERM

csa 29,31: Began syncing from T27 per <radar:7424246 > BOM: K87 needs omit on J3100 and J2900 from T27

csa 18: T27: Swapped USB_EXTB and USB_EXTD for NVRN-612340 (pg. 18). <radar:7416825> Ensure USB_EXTB is on ports 8-11 (NVRN-612340)

LDO:FIXED, MCPHVDD:P2V5 added in bom table.

Changed J5100 BOMOPTION from LPCPLUS to LPCPLUS_CON to unstuff connector at DVT

R7416 added to BOM Table, 16.9K, (APN 114S0336)

*** Started syncing with K6

CSA 25: Changed U2594 power to 3V3_S0 from 3V42_G3H.

Per <rdar://7783507> K87: Add cap to DDC line to avoid DDC line glitch issue

CSA 4: Added MCPHVDD:P2V5, LDO:FIXED, HTOL_SENSE:YES to BOM Group K86_K87_DEBUG:PROD

Added =PP3V3_S0_OPA330 alias to power U2593

CSA 8: Added =PP3V42_G3H_OPA330 alias to power U2594

CSA 93: Added C9303 3300pF cap on DP_CA_DET.

2010-03-22: A.4.0

csa 37: Per <rdar://problem/7548726> K86/K87 Ethernet series R’s need to be 0 ohmed

C7413 = 100pF 5% (131S1027)

2010-03-22: A.2.0

CSA 50: Removed SMC alias to TP for SMC_NB_MISC_ISENSE to enable sense circuitry connection to SMC

Changed BOMOPTION names from LDO:YES and LDO:NO to MCPHVDD:P2V5 and MCPHVDD:P3V3

Added R2594 and R2591 with LDO:ADJ BOMOPTION

Added C2599, R2597, R2596, U2593, Q2592, R2599, C2594, U2594, R2598, C2598 with BOMOPTION HTOL_SENSE:YES

Added BOM TABLE with LDO:FIXED, LDO:ADJ, and HTOL_SENSE:NO stuffing options

Removed SMC_P10 alias to TP_SMC_P10

2010-01-15: 2.3.0

csa 51: (Per <rdar://problem/7540522> K86/K87: Production Debug Components)

Added LPCPLUS_CON to K87_DEVEL_ENG (does not change BOM for DVT)

Changed all instances of K87_DEBUG_xxxx to K87_DEBUG:xxxx

IMVP6:1PHASE BOM Table:

Changed description for 337S3876 to "IC,MCP83M-A02,31X31MM,BGA1168"

VREFMRGN:YES ==> VREFMRGN:NO

Changed 085-1093 to call out K87_DEVEL_PVT instead of K87_DEVEL_ENG

csa 4: Cosmetic: changed text sizes and alignment

2010-01-13: 2.2.0

Changed C4585, C4586 to 131S4713 (47pF, 5%)

Updated APN text note

Added the following functional test points under the J5100 LPC+SPI CONN FUNC_TEST group

Changed text note to say "HALL EFFECT ASSEMBLY"

Changed R3440 color to green, deleted WF text note about needing PU

Per <rdar://problem/7495072> K87: Call out LED:K86_K87 BOMOPTION in the K87_MISC BOM group

Removed table entry that says 376S0868 is an alternate for 376S0624

Created SMC:PROG_K86 pointing to 341T0250 (SUBASSY, IC, SMC, K86)

Deleted BOM table for Hall effect assembly

Syncing with K6 to pick up new symbols for Q2355 and Q2356

Switching from Engineering to Production BOM should only require changing PROJECT_PHASE:DEV to PROJECT_PHASE:PROD

Per <rdar://7542674 > K86/K87 Text note change

csa 45: Added PLACEMENT_NOTE for passive deemphasis circuit.

Changed K87_MCP BOM group to call out MCP89-A02

csa 34: Changed U3440 from AP002 part to AP016 (343S0511) per <radar:7459498> BOM: APN updates for FPF1009 and SAK parts

Changed BOOTROM:PROG to call out 341T0251 (SUBASSY, IC, BOOT ROM, K86/K87)

Keeping K86 and K87 pgs identical for CSA 74, modifying BOM table for IMVP 1 phase on K87’s schematic to reflect changes for K86.

CSA 25: U2590 added, APN 353S2971. R2592 of 10K and C2592 of 1UF, C2593 of 1UF added.

Nets MCP_PLL_LDO_EN and PP3V3_S0_LDO_R added.

2010-03-22: A.3.0

CSA 25: Copied from K6

2010-03-22: A.1.0

Summary of changes for MLB_LDO:

csa 74, csa 79:

Removed OMIT from R4585, R4586

2010-01-06: 1.11.0

2010-02-25: 2.19.0, 2.20.0

2010-03-04: B.0.0

CSA 74: Changed C7434 from 0.033uF to 0.047uF (APN 132S0189) per Liang

CSA 12: C1200, C1204, C1207, C1209, C1211, C1219, C1202, C1216 NOSTUFFED

Per <rdar://7488543> K87/K86 Task Measure each power supply in mlb.

CSA 69: C6970, C6971, C6972 of 1000pF (APN 131S0222) added

Per <rdar://7678515> K87:EMC:ESD: System hangs on air/contact discharge to MPM connector

CSA 4: MOLEX_DDR_CONN added to Module Parts, removed from Alternate table. Added second 639 and EEEE # to BOM table

2010-03-09: 0.8.0

** MLB_LDO branch

2010-02-26: 2.21.0

2010-02-25: 2.18.0

CSA 67: J6700 changed from APN 514-0718 to 514-0750

CSA 12: C1233, C1230, C1237, C1234 changed from NOSTUFF to STUFFED.

2010-02-15: 2.10.0

2010-02-18: 2.12.0

CSA 74: For K86 only: C7434 = 0.1uF added, R7417 changed to 8.25Kohm

2010-02-16: 2.11.0

2010-02-15: 2.9.0

2010-02-02: 2.8.0

*** Resynced with T27 and K6 (no differences)

*** Resynced Audio pages with the following changes:

csa 97: Changed R9710 from 7.32K 0402 1% to 7.68K (APN 114S0304) to support old K84 panel

csa 4: Added OLD_AUDIO_SWITCH BOM OPTION to K86_K87_COMMON1

csa 54: Broke sync with T27. Per <rdar://problem/7605797> K69/K86/K87 sensor IN1C unreliable

U5400 changed from OPA348 to OPA330. C5434 changed to NOSTUFF

CSA 74: R7417 changed to 5.90K, C7428 changed to 0.47uF, C7434 changed to 0.033uF

csa 4: Added BOM entry under Module Parts table to include CULV processor (337S3779) to minimize delta on this page between K86 and K87 per Diana

NOTE: All page numbers are .csa, not PDF. See page 1 for .csa -> PDF mapping.

csa 2: Updated CPU block text to include CPU description for both K86 and K87

Changed C9706 from 120pF to 220pF (131S2225)

Changed C9705 from 8.2nF to 33nF (132S0131)

-pg. 67, no stuffed R6712 and R6713

*** Resynced Audio pages with the following changes:

Added L4530, L4531 (APN 155S0137) to SIL connector pins

csa 97: Per <rdar://problem/7589365> K86/k87: Compensation settings change to provide more phase margin, reduce ripple

-pg. 62, changed R6211 to 22 Ohms

csa 37: Per <rdar://problem/7554342> K86/K87: Change L3720 to 152S1182

Changed L3720 to 152S1182 (IND,PWR,SHD,4.7UH,20%,0.91A,31X31X12MM) for lower ESR

LPC_SERIRQ

Added text note with part numbers for components of the assembly

csa 69: Per <rdar://problem/7494087> K87: remove OMIT from J6955 and delete BOM table

Changed K87_PROGPARTS BOM group to point to SMC:PROG_K87

- MCO: 056-3515

Created SMC:PROG_K87 pointing to 341T0252 (SUBASSY, IC, SMC, K87)

2009-12-16: 1.8.0

csa 25: T27: Removed R2575 & R2580 per DG v1.3 (pg. 25). per <radar:7459260 > Design Guide v1.3 updates

*** Started syncing the following pages:

T27: Added gain note for U5402 and SMC_BATT_ISENSE (pg. 54).

*** Other changes

Changed component color to Green

=PP3V3_S0_DPCONN’

csa 45: Added passive deemphasis to SATA HDD D2R lines:

2009-12-10: 1.6.0

=PP1V05_S0_MCP_AVDD_UF’

R7411 = 255 1% (114S0160)

=PPSPD_S0_MEM_B’

=PP5V_S0_HDD’

R7409 = 1.58k 1% (114S0236)

Added BOM table to insert the following APNs for IMVP6:1PHASE:

- UPDATED SCHEMATIC AND PCB PART NUMBER INFO

- ALL PAGES SYNC’ED FROM K84

2009-12-08: 1.3.0

INITIAL RELEASE 0.0.1-

2009-12-07: 1.2.0

2009-12-04: 1.1.0

=PP3V3_S0_PWRCTL’

=PP5V_S0_MCPREG’

csa 8: Deleted net properties for the following nets:

2009-12-08: 1.4.0

10/1/2009:

2009-12-03: Proto 0 release 1.0.0

csa 74: Component value changes per Leo (Intersil):

C7434 from 0.12uF => 0.022uF, 10% (132S0102)

Implemented different stuffing options for 1-phase vs 2-phase:

Added IMVP6:2PHASE to the following components:

R7417, C7428, R7409, R7411, C7406, R7414, C7414, C7413

C7428 = 0.22uF 10% (132S0102)

C7406 = 470pF 10% (132S4720)

R7414 = 97.6k 1% (114S0410)

csa 74: Changed C7434 from NOSTUFF to IMVP6:2PHASE per Intersil

T27: Changed RC balance on BATT_ISENSE, same time constant (pg. 54).

Alternates table on csa 4 already has 152S0778 as alternate to 152S0693

STILL NEED TO UPDATE VALUE OF C7428!

C7414 = 1000pF 10% (132S0045)

Updated table to add new values for 1phase (PWM freq., Max current, Load line)

Added C4585, C4586 (10pF, 5%, 131S0029) and NOSTUFFed

csa 57: Began syncing from T27 per <radar:7304029 > T27 schematic bom option for R5714 & R5030 to keep K87 in sync

Added R5714 (114S0125) to table with BOMOPTION LED:K86_K87

2009-12-17: 1.9.0

csa 4: Added BOM table to substitute in parts that have BOMOPTION xxx:K6_K69 (to allow sync with T27)

R7417 = 7.68k 1% (114S0304)

R7417 from 5.36k => 6.34k, 1% (114S0296)

csa 34: Deleted net properties for =PP3V3_S3_WLAN

csa 4: Per <rdar://problem/7473229> K86: Move to MCP83

This is for K86 ONLY. Adding entry to minimize delta on csa 4 between K87 and K86

Per <rdar://problem/7495116> K87: remove ON Semi alternate for Q2300 (376S0624)

Added LED:K86_K87 BOMOPTION to the K87_MISC BOM group

BOMOPTION is "MCP83M"

2009-12-22: 1.10.0

Updated DLY text note for U3440 to match T27

Changed R3454 to 100k, 1% (114S0411) to match T27 and K69

Added BOM table entry for MCP83M (337S3876)

- BOM: 639-0680

2010-01-07: 1.12.0

Changed BOMOPTION for R7872 from S0PGOOD_ISL to NOSTUFF

- Conn APN:518S0788"

csa 78: Per <rdar://problem/7495000> K87: Add NOSTUFF to R7872 to disconnect U7870 from ALL_SYS_PWRGD

- PCBF: 820-2801

"Assembly APN: 339S0114

Deleted OMIT BOMOPTION from J6955

LPCPLUS_GPIO

SMC_TMS

csa 23: *** BROKE SYNC WITH T27

csa 20; T27: Added CKPLUS_WAIVE properties to dismiss false errors (pg. 20). <radar:7368529> TASK: Waive false CheckPlus errors

2010-01-08: 2.0.0

Changed R4585, R4586 to 114S0065 (27.4 ohm, 1%)

csa 70: Per <rdar://problem/7519048> K86/K87: Change U7000 to 353S2929

Updated Q2355 and Q2356 with new schematic symbols

Changed K87_COMMON to call out K87_DEBUG_PVT instead of K87_DEBUG_ENG

Diff from the two changes above:

Per <rdar://problem/7540522> K86/K87: Production Debug Components

csa 4: Per <rdar://problem/7540383> K86: Update CPU part number to 337S3792

R7417 changed to 7.87K (APN 114S0305)

R5714 has BOMOPTION LED:K6_K69, and we need to substitute a different part on csa 4

csa 74: Cosmetic change: moved R7413, C7406 BOMOPTION label so they don’t look like wire name

csa 7: Per <rdar://problem/7517432> K86/K87 functional net property needed on signals in schematics

Need to resync with T27 once the change has been made there

Changed U7000 from 353S2392 to 353S2929

Deleted BOM table that stuffsdel the bypass option

2010-01-13: 2.1.0

Changed U1000 CPU:1.2GHZ BOMOPTION from 337S3779 to 337S3792

Toggled:

BKLT:ENG ==> BKLT:PROD

Removed:

csa 74: Per <rdar://7525313 > K86 CPU loadline, OCP update

Added IMVP6:2PHASE BOM option to R7416 for K87’s 13.7K

Per <rdar://problem/7544629> K86/K87: Update MCP83 description on csa 4

Should switch syncing back to T27 once it is updated there

Changed BOM group structure to match that in the radar (see PDF attached to radar)

Reverted back to ENG BOM, no longer PROD BOM (i.e. reverted much of 2.2.0 changes)

Per <rdar://problem/7495021> K86/K87: Replace "S" APNs with "T" APNs for programmed SMC and BR

csa 45: Per <rdar://problem/7524364> K86/K87: change SATA HDD D2R passive EQ values

BMON:ENG ==> BMON:PROD

SENS_R:ENG ==> SENS_R:PROD

DEBUG_ADC, S0PGOOD_ISL, EFI_DEBUG, MCPPLL_LDO, EXT1V05, MCP_T_DIODE_SENSOR, XDP_CON

Unchanged:

LPCPLUS, DEVEL_BOM, SMC_DEBUG:YES, XDP

Changed all instances of K87_DEVEL_xxxx to K87_DEVEL:xxxx

2010-01-18: 2.4.0

*** Resynced all synced pages and picked up the following (change notes from T27):

Revision History

=PP3V3_S0_CPUVTTISNS’

2010-01-28: 2.7.0

Changed BOMOPTIONs to be mutually exclusive (changed "_" to ":")

Added row to EEE table for E3T

2010-01-19: 2.5.0

- REPLACED K84 MCP AND CPU PAGES WITH K6 PAGES

Changed R9726 from 22k to 10k (114S0315) and removed NOSTUFF

*** Resynced with T27 and K6 (no differences)

csa 4: Per <rdar://problem/7571786> K86/K87: Add E3T EEE code for K86 to schematic

2010-01-22: 2.6.0

-pg. 66, added C6602

csa 45: Per <rdar://problem/7561001> K87:EMC: Radiated Emissions: Right Audio emissions fail

Added BOM table to stuff 0-ohms until we get go-ahead for filter

Added R4585, R4586 (51.1 ohm, 1%, 114S0093) and OMITted

csa 3: Updated text note to include "K86" in title

-pg. 67, added BOM options for U6700, R6712, and R6713 to support MAX14560 and MAX14504

Resync with T27 and K6. Clean up and rerelease schematic.

CSA 75: R7572 changed to 147K

Per <rdar://7644836> K87 power component update

CSA 69: J6955 BOMOPTION change to OMIT. Added BOM table with 607-6831 for J6955

2010-02-18: 2.17.0

Per <rdar://7686179> K86/K87 schematic: Change audio jack part number for new connector cap

CSA 97: U9700 changed to APN 353S2965

CSA 12: For K86 only: C1272 = 330uF added.

2010-02-18: 2.16.0

Per <rdar://7634730> K86/K87: add an RC on the LVDS_IG_BKL_PWM

Per <rdar://7685202> K86/K87 schematic: change U9700 to 353S2965 for Freescale backlight issue

Per <rdar://7488543> K86/K86 Task: Measure each Power supply in MLB

Per <rdar://7676934> K86/K87: Hall eff documentation change. Substitute 607-6831 for doc purposes

CSA 97: R9725 changed to 200ohm, C9799 of 47pF added. R9726.1 connection moved to LVDS_IG_BKLPWM

CSA 70: R7015 changed to 56.2K, C7015 changed to 1000pF, C7042 changed to 0.068uF

CSA 12: Added pads for 0603 caps (APN 138S0635). Compoonents C1230, C1231, C1232, C1233, C1234, C1235, C1236, C1237.

Per <rdar://7685811> K86/K87 schematic: add additional 639 for differentiation between Foxconn and Molex DIMM connectors

Per <rdar://7683852> K87 Proto1: 5 of 6 systems failing graphics noise (Underwater) acoustic spec by up to 3.1dB

Changed R3790-R3795 to 116S0004 (0-ohm, 0402) from 22-ohm

csa 23: Per <rdar://problem/7544657> K86/K87: Fix schematic symbol for Q2355, Q2356

Net change was to move LPCPLUS to the 639 (from the 085)

csa 4: Per <rdar://problem/7549122> K86/K87: Switch to new BOM group structure

Cleaned up text notes for 1phase, 2phase, and edp #s per radar request.

CSA 4: Added Alternate part for U2592 LDO. 353S2987(TI), 353S2988(Micrel) to 353S2986(Intersil).

2010-03-22: A.5.0

Removed NOSTUFF from C4585, C4586

Per <rdar://problem/7519025> K86/K87: update all instances of 376S0786 schematic symbols

Removed Intersil LDO(353S2986).

csa 4: Added BOM table entry for MCP89-A02 per <radar:7416858 > Task: Get part numbers for A02 rev.

*** Made the following changes to follow T27 on the following unsynced pages:

T27: Added CKPLUS_WAIVE properties to dismiss false errors (pg. 54).

T27: Added BOMOPTIONs and APNs for Foxconn and Molex SO-DIMM connectors (pp. 29, 31).

2009-12-11: 1.7.0

csa 69: Added OMIT to J6955, BOM table to stuff K84 Hall effect connector

Revision History

SYNC_DATE=MASTER

SYNC_MASTER=MASTER

5 OF 109

C.0.0

051-8561

5 OF 76

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

Revision History

NOTE: All page numbers are .csa, not PDF. See page 1 for .csa -> PDF mapping.

SYNC_DATE=MASTER

SYNC_MASTER=MASTER

Revision History

6 OF 109

C.0.0

051-8561

6 OF 76

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

Functional Test Points

FSB SIGNALS WITH NOTEST

(NEED TO ADD 1 GND TP)

(NEED 2 TP)

(NEED 4 TP)

(NEED 4 TP)

(NEED TO ADD 3 GND TP)

(NEED 2 TP)

DC POWER CONN FUNC_TEST

(NEED TO ADD 2 GND TP)

(NEED TO ADD 4 GND TP)

(NEED TO ADD 5 GND TP)

POWER NETS FUNC_TEST

(NEED 2 TP)

X16 WIRELESS CONN FUNC_TEST

(NEED 4 TP)

MIC FUNC_TEST

SPEAKER FUNC_TEST

J5100 LPC+SPI CONN FUNC_TEST

(NEED TO ADD 6 GND TP)

(NEED TO ADD 1 GND TP)

(NEED TO ADD 4 GND TP)

(NEED TO ADD 2 GND TP)

KEYBOARD CONN FUNC_TEST

(NEED 3 TP)

SATA ODD CONN FUNC_TEST

LVDS FUNC_TEST

IPD_FLEX_CONN FUNC_TEST

(NEED TO ADD 2 GND TP)

BATT POWER CONN FUNC_TEST

(NEED 2 TP)

FAN CONNECTORS FUNC_TEST

(NEED TO ADD 3 GND TP)

SATA HDD/SIL FUNC_TEST

HALL EFFECT CONNECTOR FUNC_TEST

(NEED TO ADD 4 GND TP)

TRUE

SPI_MISO

PP3V3_S0_LCD_DDC_F

TRUE

FSB_A_L<35..3>

NO_TEST=TRUE

PM_SLP_S4_L

TRUE

PP3V3_S3

TRUE

PP1V5R1V35_S3

TRUE

PP5V_SW_ODD

TRUE

TRUE

PP1V5_S0

TRUE

PP1V05_S0

TRUE

PPVCORE_S0_MCP

PP5V_S0

TRUE

TRUE

PP5V_S0

TRUE

PP1V8_S0

PPDDRVTT_S0

TRUE

PP0V9_S5

TRUE

TRUE

PP5V_S3_CAMERA_F

TRUE

SMC_PM_G2_EN

PM_SLP_S3_L

TRUE

PP4V5_AUDIO_ANALOG

TRUE

PP3V3_S5_AVREF_SMC

TRUE

TRUE

PP3V3_SW_LCD_PANEL_F

PPVOUT_S0_LCDBKLT

TRUE

PP5V_S0_HDD_FLT

TRUE

TRUE

CONN_PCIE_MINI_D2R_N

TRUE

PPVCORE_S0_CPU

FSB_HIT_L

NO_TEST=TRUE

FSB_DINV_L<3..0>

NO_TEST=TRUE

FSB_DSTB_L_N<3..0>

NO_TEST=TRUE

FSB_LOCK_L

NO_TEST=TRUE

FSB_HITM_L

NO_TEST=TRUE

WS_CONTROL_KBD

TRUE

TRUE

WS_LEFT_OPTION_KBD

TRUE

WS_LEFT_SHIFT_KBD

WS_KBD15_CAP

TRUE

TRUE

CONN_PCIE_MINI_R2D_N

WS_KBD14

TRUE

TRUE

WS_KBD13

WS_KBD5

TRUE

FSB_D_L<63..0>

NO_TEST=TRUE

FSB_ADS_L

NO_TEST=TRUE

TRUE

WS_KBD7

TRUE

WS_KBD8

TRUE

WS_KBD9

TRUE

WS_KBD10

PP3V3_S3

TRUE

USB_CAMERA_CONN_P

TRUE

TRUE

LVDS_IG_A_DATA_P<0>

TRUE

LVDS_IG_A_DATA_N<0>

TRUE

LVDS_IG_A_DATA_N<1>

TRUE

WS_KBD4

PSOC_SCLK

TRUE

TRUE

WS_KBD23

TRUE

SATA_HDD_R2D_N

TRUE

LVDS_IG_A_DATA_P<1>

TRUE

SATA_HDD_D2R_C_P

TRUE

PP3V42_G3H

TRUE

SMC_LID_R

TRUE

CONN_PCIE_MINI_R2D_P

TRUE

Z2_HOST_INTN

TRUE

PSOC_F_CS_L

TRUE

PP3V3_S3_BT_F

WS_KBD_ONOFF_L

TRUE

TRUE

PP3V42_G3H

WS_KBD1

TRUE

TRUE

ADAPTER_SENSE

TRUE

PP18V5_DCIN_FUSE

PICKB_L

TRUE

Z2_SCLK

TRUE

TRUE

PSOC_MOSI

PSOC_MISO

TRUE

TRUE

SPKRAMP_L_N_OUT

TRUE

Z2_MISO

TRUE

Z2_CS_L

TRUE

USB_CAMERA_CONN_N

NO_TEST=TRUE

FSB_REQ_L<4..0>

FSB_DSTB_L_P<3..0>

NO_TEST=TRUE

FSB_ADSTB_L<1..0>

NO_TEST=TRUE

Z2_DEBUG3

TRUE

Z2_CLKIN

TRUE

Z2_KEY_ACT_L

TRUE

TRUE

Z2_BOOST_EN

WS_KBD22

TRUE

TRUE

LED_RETURN_5

TRUE

PP5V_S0

TRUE

CONN_PCIE_MINI_D2R_P

TRUE

PCIE_CLK100M_MINI_CONN_P

PCIE_WAKE_L

TRUE

BI_MIC_P

TRUE

TRUE

PP3V3_S0

TRUE

PP3V3_S5

FAN_RT_TACH

TRUE

PP3V42_G3H

TRUE

TRUE

SPI_CLK

TRUE

PPVTT_S3_DDR_BUF

TRUE

PP1V05_S0_MCP_PLL_UF

TRUE

SPKRAMP_R_P_OUT

BI_MIC_N

TRUE

FAN_RT_PWM

TRUE

TRUE

PP3V42_G3H

TRUE

PP3V3_G3_RTC

PP0V9_ENET

TRUE

PPBUS_G3H

TRUE

TRUE

PP5V_S3

Z2_MOSI

TRUE

Z2_RESET

TRUE

TRUE

SMBUS_SMC_A_S3_SDA

WS_KBD2

TRUE

TRUE

WS_KBD3

TRUE

WS_KBD11

TRUE

WS_KBD12

TRUE

LED_RETURN_3

TRUE

LED_RETURN_2

TRUE

LVDS_IG_A_CLK_F_P

TRUE

LVDS_IG_A_CLK_F_N

LED_RETURN_1

TRUE

SMBUS_SMC_A_S3_SCL

TRUE

TRUE

PP3V3_SW_LCD_PANEL_F

TRUE

LVDS_IG_DDC_CLK

TRUE

LVDS_IG_DDC_DATA

TRUE

PPVOUT_S0_LCDBKLT

TRUE

SPKRAMP_SUB_P_OUT

TRUE

CONN_USB2_BT_N

AP_CLKREQ_Q_L

TRUE

AP_RESET_CONN_L

TRUE

TRUE

PP18V5_S3

TRUE

PP3V3_WLAN

PP3V3_ENET

TRUE

TRUE

SPI_MOSI

PP18V5_S3

TRUE

TRUE

SPI_CS0_L

SPIROM_USE_MLB

TRUE

TRUE

LPCPLUS_GPIO

TRUE

LPC_SERIRQ

TRUE

SMC_TMS

WS_KBD21

TRUE

TRUE

WS_KBD20

TRUE

WS_KBD19

TRUE

WS_KBD18

TRUE

WS_KBD17

WS_KBD16_NUM

TRUE

TRUE

WS_KBD6

TRUE

SMC_ODD_DETECT

TRUE

SATA_HDD_D2R_C_N

TRUE

SYS_LED_ANODE_R

TRUE

PPVBAT_G3H_CONN

TRUE

PP5V_S0_HDD_FLT

CONN_USB2_BT_P

TRUE

PP3V3_S3

TRUE

TRUE

BI_MIC_SHIELD

TRUE

PCIE_CLK100M_MINI_CONN_N

PP3V3_WLAN

TRUE

SPKRAMP_SUB_N_OUT

TRUE

SPKRAMP_L_P_OUT

TRUE

TRUE

SPKRAMP_R_N_OUT

TRUE

PP5V_SW_ODD

TRUE

PP5V_S3_CAMERA_F

TRUE

LED_RETURN_6

TRUE

LED_RETURN_4

TRUE

LVDS_IG_A_DATA_P<2>

LVDS_IG_A_DATA_N<2>

TRUE

TRUE

SMBUS_SMC_BSA_SDA

TRUE

SYS_DETECT_L

TRUE

SMBUS_SMC_BSA_SCL

TRUE

SATA_HDD_R2D_P

TRUE

SATA_ODD_D2R_C_P

SATA_ODD_D2R_C_N

TRUE

SATA_ODD_R2D_N

TRUE

TRUE

SATA_ODD_R2D_P

SYNC_DATE=MASTER

FUNC TEST

SYNC_MASTER=MASTER

I449

I448

I447

I446

I445

I444

I443

I442

I421

I418

I417

I413

I412

I411

I410

I409

I408

I407

I406

I405

I404

I403

I402

I401

I400

I399

I398

I397

I396

I395

I393

I392

I391

I390

I389

I388

I386

I385

I383

I382

I381

I380

I378

I377

I376

I374

I372

I371

I370

I369

I368

I366

I365

I364

I363

I362

I361

I360

I359

I358

I357

I355

I354

I353

I352

I351

I350

I349

I348

I347

I346

I345

I344

I343

I342

I341

I340

I339

I338

I337

I336

I335

I334

I333

I332

I331

I330

I329

I328

I327

I326

I322

I321

I320

I319

I318

I317

I315

I314

I313

I312

I308

I307

I305

I304

I303

I302

I301

I300

I299

I298

I297

I295

I294

I293

I292

I290

I289

I288

I287

I285

I283

I282

I281

I280

I279

I278

I276

I275

I274

I273

I271

I270

I269

I268

I267

I266

I265

I264

I262

I261

I260

I258

I257

I256

I255

I254

I253

I252

I251

I250

I249

I248

I247

I246

I245

I239

I238

I237

I231

I230

I229

I228

I227

I226

I16

I15

I12

7 OF 109

C.0.0

051-8561

7 OF 76

72 37 19

64

69 14 10

62 36 35 19

8 7

75

8

46 33

7

75 62

8

62

8

39

8

62

8 7

62

8 7

8

8

8

64

7

62 35

66 62 35 19

48

36 35

64

7

67 64 46

7

33

7

75 30

9

39

8

69 14 10

69 14 10

69 14 10

69 14 10

69 14 10

43

43

43

43

75 30

9

43

43

43

69 14 10

69 14 10

43

43

43

43

8 7

75 64

71 64

9

71 64

9

71 64

9

43

44 43

43

71 33

71 64

9

71 33

8 7

54

75 30

9

44 43

44 43

30

43

8 7

43

54

54

44 43

44 43

44 43

44 43

52 51

44 43

44 43

75 64

69 14 10

69 14 10

69 14 10

44 43

44 43

44 43

44

43

67 64

62

8 7

75 30

9

75 30

30 16

75 53 52

75 62

8

75 62

8

42

8 7

72 37

8

8

52 51

75 53 52

42

8 7

23 20 19

8

8

39

8

8

44 43

44 43

74 38

43

43

43

43

67 64

67 64

75 64

75 64

67 64

74 38

64

7

64

9

64

9

67 64 46

7

52 51

75 30

30

30

44

7

30

7

8

72 37

44

7

72 37

47 37 19

37 19

37 35 19

37 36 35

43

43

43

43

43

43

43

35 33

71 33

33

55 54

33

7

75 30

8 7

53 52

75 30

30

7

52 51

52 51

52 51

46 33

7

64

7

67 64

67 64

71 64

9

71 64

9

74 38

54

74 38

71 33

71 33

71 33

71 33

71 33

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

0 MA

LVDDR VRef/VTT (0.75V/0.675V) Rails

4250 MA

DIGITAL GROUND

(CONNECTS TO THE DECAPS)

(SINCE PE0[3:0] IS NOT USED ON K6)

(CONNECTS TO MCP BALLS)

(CONNECTS TO MCP BALLS)

(CPU VCORE PWR)

"S3" RAILS

"G3H" RAILS"S0,S0M" RAILS

UNUSED MCP PE0[3:0] AVDD/DVDD

(MCP VCORE AFTER SENSE RES)

(CONNECTS TO THE DECAPS)

FIX ME!! OUTPUT OF REGULATOR VALUES

105/241 MA

"S5" RAILS

"ENET" RAILS

MIN_NECK_WIDTH=0.20MM

MIN_LINE_WIDTH=0.50MM

GND

VOLTAGE=0V

=PP3V3_S3_PDCISENS

=PP3V3_S3_MCP_GPIO

=PPBUS_G3H

=PP3V42_G3H_OPA330

=PP3V42_G3H_BMON_ISNS

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2 MM

MIN_LINE_WIDTH=0.6 MM

PP3V42_G3H

VOLTAGE=3.42V

=PP3V42_G3H_HALL

=PPLVDDR_S3_MEM_A

MIN_NECK_WIDTH=0.17 mm

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6 mm

PP1V5R1V35_S3

VOLTAGE=1.5V

=PP1V05_S0_MCP_PLL_IFP

=PP1V05_S0_MCP_DP0_VDD

=PP3V3_S0_FAN_RT

=PPVCORE_S0_MCPGFXFET

=PP1V05_SW_MCP_FSB

MIN_NECK_WIDTH=0.2 MM

MIN_LINE_WIDTH=0.6 MM

PPVCORE_S0_MCP

VOLTAGE=1.05V

MAKE_BASE=TRUE

=PPVCORE_S0_MCP

PPVTT_S3_DDR_BUF

MIN_LINE_WIDTH=0.3 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=0.75V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.25 mm

MIN_LINE_WIDTH=1.5 mm

VOLTAGE=1.5V

PP1V5_S0

MAKE_BASE=TRUE

=PPCPUVTT_S0_REG

MIN_NECK_WIDTH=0.20 MM

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.30 MM

VOLTAGE=5V

PP5V_S0

=PP1V05_S0_CPU

=PP1V05_S0_MCP_FSB

=PPVIN_S3_DDRREG

=PPBUS_S5_CPUREGS_ISNS_R

PPBUS_G3H

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.25 mm

MIN_LINE_WIDTH=0.4 mm

VOLTAGE=12.6V

=PPVIN_S5_3V3S5

=PPBUS_S0_LCDBKLT

PPBUS_S5_IMVP_VTT_ISNS

MIN_LINE_WIDTH=0.6 mm

VOLTAGE=12.6V

MIN_NECK_WIDTH=0.3 MM

MAKE_BASE=TRUE

=PP3V3_S3_BT

=PPDCIN_S5_CHGR

=PP3V42_G3H_ONEWIRE

MIN_NECK_WIDTH=0.25 mm

PP3V3_S3

VOLTAGE=3.3V

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.5 mm

=PP5V_S0_LPCPLUS

=PP3V3_S5_REG

=PP3V3_S5_P3V3S3FET

=PP3V3_S5_MCPPWRGD

=PP3V3_S5_MCP

=PP3V3_S0_LCD_PANEL

=PP3V3_S0_FET

=PP3V3_S0_MCP_HVDD

=PP3V3_S0_P1V8S0

=PP3V3_S0_SMBUS_MCP_1

=PP3V3_S0_SMBUS_SMC_0_S0

=PP3V3_S0_SMBUS_SMC_B_S0

=PP3V3_S0_XDP

=PP3V3_S5_DP_PORT_PWR

=PP3V3_S5_P0V9S5

=PP3V3_S5_P3V3ENETFET

=PP3V3_S5_P3V3S0FET

=PP3V3_S5_VMON

=PP3V3_S3_SMBUS_SMC_MGMT

=PPVCORE_S0_CPU

=PPVTT_S3_DDR_BUF

=PP5V_S0_CPU_IMVP

=PP5V_S0_FAN_RT

=PP5VR3V3_S0_DPCADET

=PP5V_S0_CPUVTTS0

=PP3V3_S3_VREFMRGN

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=3.3V

PP3V3_ENET_PHY_VDDREG

=PP3V3_ENET_PHY_VDDREG

=PP3V3_S3_SMBUS_SMC_A_S3

=PP5V_S3_P5VS0FET

=PP3V3_ENET_PHY

=PP1V5_S0_FET

=PP1V5R1V35_S0_MCPDDRFET

=PP1V5R1V35_S3_MCP_MEM

=PPDDR_S3_REG

=PPLVDDR_S3_MEM_B

=PPVIN_S0_DDRREG_LDO

=PP1V05_S0_REG

PP1V05_S0_REG

VOLTAGE=1.05V

MIN_NECK_WIDTH=0.2mm

MIN_LINE_WIDTH=0.4MM

MAKE_BASE=TRUE

RTL8211_REGOUT

VOLTAGE=1.05V

MIN_NECK_WIDTH=0.2mm

MIN_LINE_WIDTH=0.4MM

MAKE_BASE=TRUE

=PP1V05_ENET_PHY

=PP0V9_ENET_FET

=PPDDRVTT_S0_MEM_B

MIN_LINE_WIDTH=0.6 mm

VOLTAGE=3.3V

MIN_NECK_WIDTH=0.2 mm

MAKE_BASE=TRUE

PP3V3_ENET

=PP3V3_ENET_MCP_RMGT

=PP3V3_ENET_MCP_PLL_MAC

=PP3V3_ENET_FET

=PP0V9_ENET_P0V9ENETFET

=PP1V05_S0_MCP_PLL_UF_R

=PP1V05_S0_MCP_M2CLK_DLL

=PPVCORE_S0_CPU_REG

=PP3V42_G3H_REG

PPDDRVTT_S0

MIN_NECK_WIDTH=0.2 mm

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.4 MM

VOLTAGE=0.75V

=PP3V3R1V8_S0_MCP_IFP_VDD

=PP5V_S3_REG

=PP3V3_S3_TPAD

MAKE_BASE=TRUE

PP1V05_S0_MCP_PE_AVDD

=PP1V05_S0_MCP_PE_DVDD1

=PP1V05_S0_MCP_PE_DVDD

=PP1V05_S0_MCP_PE_AVDD0

=PP1V05_S0_MCP_PE_DVDD0

=PP3V3_S3_FET

=PPVIN_S5_SMCVREF

=PP3V42_G3H_PWRCTL

=PP3V42_G3H_SMBUS_SMC_BSA

=PP3V3_S5_SMC

=PP3V42_G3H_SMCUSBMUX

=PP3V42_G3H_TPAD

=PP3V42_G3H_CHGR

=PP3V3_S5_LPCPLUS

=PP1V05_S0_MCP_PE_AVDD1

=PPVIN_S0_CPUVTTS0

=PPVIN_S5_CPU_IMVP

=PP1V05_S0_MCP_PLL_UF

=PPBUS_S5_CPUREGS_ISNS

=PP5V_S3_MCPDDRFET

=PP18V5_DCIN_CONN

PP1V8_S0

MIN_LINE_WIDTH=0.10MM

VOLTAGE=1.8V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.10MM

=PP3V3R1V5_S0_AUDIO

=PP1V8R1V5_S0_AUDIO

=PP1V5_S0_CPU

=PPDDRVTT_S0_MEM_A

=PPVTT_S0_DDR_LDO

=PP1V05_S0_MCP_PLL_OR

PP1V05_S0_MCP_PLL_UF

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=1.05V

MIN_LINE_WIDTH=0.6 mm

MAKE_BASE=TRUE

PP3V3_G3_RTC

=PP3V3_S3_SMS

=PP1V05_S0_MCP_SATA_DVDD

=PPMCPCORE_S0_REG

=RTL8211_REGOUT

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.4 mm

PP0V9_ENET

VOLTAGE=0.9V

=PP0V9_ENET_MCP_RMGT

=PP1V5_S0_MCP_PLL_VLDO

=PP1V8_S0_REG

=PP3V3R1V5_S0_MCP_HDA

VOLTAGE=1.05V

MIN_NECK_WIDTH=0.2mm

MIN_LINE_WIDTH=0.4MM

MAKE_BASE=TRUE

PP1V05_ENET

=PP3V3_S5_P0V9ENETFET

=PP5V_S3_AUDIO_AMP

=PP3V3_S3_WLAN

=PP5V_S0_MCPFSBFET

=PP5V_S0_FET

=PP3V3_S0_AUDIO

=PP3V3_S0_IMVP

=PP3V3_S0_LCD_DDC

MAKE_BASE=TRUE

VOLTAGE=5V

MIN_NECK_WIDTH=0.25 mm

MIN_LINE_WIDTH=0.5 mm

PP5V_S3

=PP5V_S3_EXTUSB

=PPVIN_S3_5VS3

VOLTAGE=18.5V

PP18V5_G3H

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.3 MM

MAKE_BASE=TRUE

=PPVIN_S0_MCPCORE

=PP3V3_S0_SMBUS_MCP_0

=PPSPD_S0_MEM_A

=PP3V3_S0_MCP_GPIO

=PP3V3_S0_MCP_PLL_UF

=PP5V_S3_ODD

=PP5V_S3_SYSLED

=PP5V_S3_DEBUG_ISNS

=PP5V_S3_AUDIO

=PP5V_S3_TPAD

=PP5V_S3_DEBUG_ADC_AVDD

MIN_NECK_WIDTH=0.2 MM

MIN_LINE_WIDTH=0.6 MM

MAKE_BASE=TRUE

VOLTAGE=1.05V

PP0V9_S5

=PP0V9_S5_MCP_VDD_AUXC

=PP5V_S3_CAMERA

=PP5V_S3_DEBUG_ADC_DVDD

=PP5V_S3_DDRREG

MAKE_BASE=TRUE

VOLTAGE=3.3V

MIN_NECK_WIDTH=0.20MM

PP3V3_S5

MIN_LINE_WIDTH=0.30MM

=PP3V3_S5_MCP_GPIO

=PP3V3_S5_ROM

=PP0V9_S5_REG

=PP3V3_S0_ODD

=PP3V3_S0_MCP

=PP3V3_S0_SMC

=PP3V3_S0_MCPTHMSNS

=PP5V_S0_HDD

=PP5V_S0_MCPREG

=PP1V05_S0_MCP_AVDD_UF

=PPSPD_S0_MEM_B

=PP3V3_S0_PWRCTL

=PP3V3_S0_DPCONN

=PP3V3_S0_CPUVTTISNS

=PP1V05_S0_MCP_PE_DVDD

PPVCORE_S0_CPU

MIN_NECK_WIDTH=0.3 MM

VOLTAGE=1.25V

MIN_LINE_WIDTH=0.6 MM

MAKE_BASE=TRUE

=PP3V3_S0_CPUTHMSNS

=PP3V3_S0_MCP_PLL_VLDO

=PP3V3_S0_MCPDDRISNS

=PP3V3_S0_DEBUGROM

MIN_NECK_WIDTH=0.20MM

MIN_LINE_WIDTH=0.30MM

MAKE_BASE=TRUE

PP3V3_S0

VOLTAGE=3.3V

=PP3V3_S0_MCPCOREISNS

=PP3V3_S0_OPA330

MAKE_BASE=TRUE

VOLTAGE=1.05V

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

PP1V05_S0

SYNC_DATE=MASTER

SYNC_MASTER=MASTER

Power Aliases

R0814

402

MF-LF

ENET1V05:INT

5%

0

1/16W

R0813

ENET1V05:EXT

1/16W05%

402

MF-LF

R0812

402

0

MF-LF

ENET1V05:INT

1/16W

5%

8 OF 109

C.0.0

051-8561

8 OF 76

1 2

1 2

1 2

19

55

40

7

54

26

75

7

24 17

24 17

42

22

23 20

39

7

23 20

7

75 62

7

60

62

7

13 12 11 10

23 20 14

57

40

39

7

56

68

30

55

54

7

37

56

63

25

23 20

64

63

23 20

61

38

38

38

13

66

61

63

63

62

38

12 11

57 29

58

42

66

60

29

31

38

63

31

9

63

21

15

63 57

27

57

61

31

63

27

7

23 20 18

9

23

63 62 61

9

63

61

23 15

58

54

7

24 17

56

44 43

23

20

23

8

20

20

63

36

62

38

36 35

34

43

62 55

37

20

60

58

23

40

21

54

7

48

48

12 11

26

57

61

7

23 20 19

7

45

23 20

59

31

7

23 20

61

61

23 19

63

51

30

22

63

53 52 48

58

64

7

34

56

59

38

26

19 18 17

23

33

36

46

52 50 48

44

46

7

23 20

64

46

57

75 62

7

19 18

47

61

33

23 20

36

41

33

59

23

27

62

66

40

23

8

39

7

41

61

40

37

75 62

7

40

23

62

7

OUT

IN

IN

IN

BI

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

BI

OUT

OUT

OUT

IN

IN

BI

BI

BI

BI

OUT

IN

IN

OUT

OUT

BI

BI

IN

BI

BI

BI

BI

OUT

IN

OUT

OUT

OUT

OUT

IN

IN

IN

OUT

IN

OUT

OUT

IN

IN

OUT

IN

OUT

IN

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

USB ALIASES

UNUSED USB PORTS

SMC ALIASES

LVDS ALIASES

ETHERNET ALIASES

1 1 1

BSEL<2..0>

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

0 0 0

133

200

333

100

(RSVD)

(166)

(400)

266

FSB MHZ

MCP89 MISC ALIASES

MLB MOUNTING (TO C. BRACKET) SCREW HOLES

MLB MOUNTING (TO TOPCASE) SCREW HOLES

LVDS CONNECTOR HOLE

EMI THINBC POGO PINS

EMI TALL POGO PINS

(870-1698 )

LEFT OF CPU

EMI IO MEDIUM POGO PINS

PCI-E ALIASES

ABOVE CPU

BELOW CPU

(870-1794 )

HEATSINK STANDOFFS

FAN STANDOFF

UNUSED GPU LANES

CPU FSB FREQUENCY STRAPS

CHARGER SIGNAL

MCP89 ETHERNET VREF

UNUSED ETHERNET LANE

UNUSED FIREWIRE LANE

DISPLAY PORT ALIASES

BELOW MCP

(870-1820 )

CPU VCORE ALIASES

=PEG_D2R_P<15:0>

MAKE_BASE=TRUE

PCIE_AP_D2R_N

MAKE_BASE=TRUE

PCIE_AP_D2R_P

MAKE_BASE=TRUE

PCIE_AP_R2D_C_N

PCIE_MINI_R2D_C_N

CONN_PCIE_MINI_D2R_P

CONN_PCIE_MINI_D2R_N

DP_IG_AUX_CH1_N

DP_IG_ML1_P<0..3>

DP_IG_ML0_N<0..3>

=MCP_IFPA_TXC_P

LCD_IG_PWR_EN

LCD_IG_BKLT_EN

=PP3V3_ENET_PHY

MAKE_BASE=TRUE

TP_USB_EXTD_N

TP_USB_EXTC_N

MAKE_BASE=TRUE

NC_LVDS_IG_B_DATA_P<0..3>

NO_TEST=TRUE

MAKE_BASE=TRUE

LVDS_IG_BKL_ON

NC_LVDS_IG_B_CLK_N

NO_TEST=TRUE

MAKE_BASE=TRUE

LVDS_IG_BKL_PWM

LVDS_IG_A_CLK_P

MAKE_BASE=TRUE

NC_LVDS_IG_A_DATA_P3

NO_TEST=TRUE

MAKE_BASE=TRUE

TP_ENET_CLK125M_TXCLK

TP_ENET_TXD<0..3>

ENET_CLK125M_TXCLK

MAKE_BASE=TRUE

ENET_TX_CTRL

MAKE_BASE=TRUE

TP_SMC_SYS_KBDLED

MAKE_BASE=TRUE

MAKE_BASE=TRUE

TP_CPU_PECI_MCP

=MCP_BSEL<0:2>

CPU_PECI_MCP

MAKE_BASE=TRUE

CPU_BSEL<0:2>

PCIE_ENET_R2D_C_N

PCIE_CLK100M_ENET_N

TP_PCIE_CLK100M_ENET_P

MAKE_BASE=TRUE

MAKE_BASE=TRUE

LVDS_IG_A_DATA_P<0..2>

LVDS_IG_A_DATA_N<0..2>

MAKE_BASE=TRUE

=MCP_IFPA_TXD_N<0..2>

=MCP_IFPA_TXD_P<0..2>

PCIE_AP_R2D_P

MAKE_BASE=TRUE

MAKE_BASE=TRUE

LVDS_IG_DDC_CLK

MAKE_BASE=TRUE

TP_FW_CLKREQ_L

PCIE_ENET_D2R_N

PCIE_ENET_D2R_P

ENET_ENERGY_DET

PCIE_CLK100M_FW_P

=PP3V3_ENET_FET

PCIE_ENET_R2D_C_P

TP_MCP_MEM_VDD_SEL_1V5

MAKE_BASE=TRUE

MCP_MEM_VDD_SEL_1V5

TP_ENET_CLKREQ_L

MAKE_BASE=TRUE

LVDS_IG_A_CLK_N

MAKE_BASE=TRUE

TP_ENET_MDC

TP_MCP_CLK25M_BUF0_R

TP_ENET_TX_CTRL

TP_ENET_RESET_L

ENET_RESET_L

MAKE_BASE=TRUE

MCP_CLK25M_BUF0_R

MAKE_BASE=TRUE

MAKE_BASE=TRUE

ENET_TXD<0..3>

TP_USB_MINI_P

MAKE_BASE=TRUE

TP_USB_T57_N

MAKE_BASE=TRUE

TP_USB_T57_P

MAKE_BASE=TRUE

MAKE_BASE=TRUE

TP_USB_WM_N

TP_USB_WM_P

MAKE_BASE=TRUE

USB_WM_N

USB_IR_N

TP_USB_IR_N

MAKE_BASE=TRUE

MAKE_BASE=TRUE

TP_DP_IG_ML1N<0..3>

MAKE_BASE=TRUE

NC_LVDS_IG_B_CLK_P

NO_TEST=TRUE

NC_LVDS_IG_B_DATA_N<0..3>

NO_TEST=TRUE

MAKE_BASE=TRUE

=MCP_IFPA_TXC_N

=MCP_IFPAB_DDC_DATA

USB_MINI_P

PCIE_CLK100M_AP_P

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PCIE_CLK100M_AP_N

CONN_PCIE_MINI_R2D_P

CONN_PCIE_MINI_R2D_N

=PEG_D2R_N<15:0>

MAKE_BASE=TRUE

TP_PCIE_FW_D2R_N

TP_PCIE_CLK100M_FW_N

MAKE_BASE=TRUE

MAKE_BASE=TRUE

TP_PCIE_CLK100M_FW_P

MAKE_BASE=TRUE

TP_FW_PME_L

FW_PWR_EN

PCIE_FW_D2R_N

LCD_IG_BKLT_PWM

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PEG_R2D_C_P<15:0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PEG_D2R_P<15:0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PEG_D2R_N<15:0>

MAKE_BASE=TRUE

PCIE_AP_R2D_N

DP_IG_ML_N<0..3>

DP_IG_HPD1

=MCP_IFPA_TXD_P<3>

NC_LVDS_IG_A_DATA_N3

NO_TEST=TRUE

MAKE_BASE=TRUE

USB_EXTC_N

TP_PCIE_CLKREQ_L

MAKE_BASE=TRUE

=PEG_R2D_C_P<15:0>

=PEG_R2D_C_N<15:0>

USB_EXTD_N

MAKE_BASE=TRUE

TP_USB_EXTD_P

USB_EXTD_P

USB_EXTC_P

TP_USB_SDCARD_P

MAKE_BASE=TRUE

USB_MINI_N

USB_T57_N

PCIE_CLK100M_MINI_P

PCIE_CLK100M_MINI_N

USB_T57_P

USB_SDCARD_N

MAKE_BASE=TRUE

TP_USB_SDCARD_N

USB_WM_P

USB_SDCARD_P

PEG_CLK100M_P

PEG_CLKREQ_L

PCIE_AP_R2D_C_P

MAKE_BASE=TRUE

MAKE_BASE=TRUE

TP_USB_IR_P

USB_IR_P

=MCP_IFPAB_DDC_CLK

MAKE_BASE=TRUE

TP_USB_EXTC_P

TP_USB_MINI_N

MAKE_BASE=TRUE

PCIE_MINI_R2D_C_P

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PEG_R2D_C_N<15:0>

PEG_CLK100M_N

MAKE_BASE=TRUE

TP_PEG_CLK100M_N

MAKE_BASE=TRUE

TP_PEG_CLK100M_P

MAKE_BASE=TRUE

ENET_MDC

MAKE_BASE=TRUE

LVDS_IG_DDC_DATA

DP_EXT_HPD

MAKE_BASE=TRUE

MAKE_BASE=TRUE

DP_EXT_CA_DET

DP_EXT_AUX_CH_C_N

MAKE_BASE=TRUE

MAKE_BASE=TRUE

TP_DP_IG_AUX_CH1N

DP_EXT_ML_P<0..3>

MAKE_BASE=TRUE

DP_IG_ML_P<0..3>

DP_EXT_AUX_CH_C_P

MAKE_BASE=TRUE

SMC_SYS_KBDLED

SMC_BC_ACOK

MAKE_BASE=TRUE

=PP3V3_ENET_MCP_RMGT

MCP_RGMII_VREF

=RTL8211_ENSWREG

=MCP_IFPB_TXD_N<0..3>

=MCP_IFPB_TXD_P<0..3>

=MCP_IFPB_TXC_P

LVDS_IG_PANEL_PWR

MAKE_BASE=TRUE

TP_PCIE_FW_R2D_C_N

TP_PCIE_FW_R2D_C_P

MAKE_BASE=TRUE

PCIE_FW_D2R_P

PCIE_FW_R2D_C_N

=MCP_IFPB_TXC_N

=MCP_IFPA_TXD_N<3>

MAKE_BASE=TRUE

TP_PCIE_FW_D2R_P

PCIE_FW_R2D_C_P

FW_PME_L

ENET_CLKREQ_L

TP_PCIE_ENET_D2R_P

MAKE_BASE=TRUE

PCIE_CLK100M_ENET_P

PCIE_CLK100M_FW_N

RTL8211_ENSWREG

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.4MM

MIN_NECK_WIDTH=0.2mm

DP_EXT_ML_N<0..3>

MAKE_BASE=TRUE

TP_PCIE_CLK100M_ENET_N

MAKE_BASE=TRUE

DP_IG_AUX_CH1_P

DP_IG_HPD0

DP_IG_ML1_N<0..3>

DP_AUX_CH_C_N

DP_AUX_CH_C_P

DP_CA_DET

TP_PCIE_ENET_R2D_C_N

MAKE_BASE=TRUE

TP_PCIE_ENET_R2D_C_P

MAKE_BASE=TRUE

TP_PCIE_ENET_D2R_N

MAKE_BASE=TRUE

MAKE_BASE=TRUE

DP_IG_AUX_CH_N

MAKE_BASE=TRUE

TP_DP_IG_ML1P<0..3>

TP_DP_IG_AUX_CH1P

MAKE_BASE=TRUE

DP_IG_ML0_P<0..3>

DP_IG_AUX_CH0_N

MAKE_BASE=TRUE

DP_IG_AUX_CH_P

DP_IG_AUX_CH0_P

TP_FW_PWR_EN

MAKE_BASE=TRUE

IMVP6_NTC

MAKE_BASE=TRUE

TP_IMVP6_NTC

TP_IMVP6_VR_TT

MAKE_BASE=TRUE

=CHGR_ACOK

IMVP6_VR_TT

FW_CLKREQ_L

SYNC_DATE=(02/04/2009)

SIGNAL ALIAS

SYNC_MASTER=(K84_MLB)

2.0DIA-MLB-THIN-BC-K84

ZS0920

SM

NOSTUFF

OMIT

2.0DIA-TALL-EMI-MLB-M97-M98

ZS0919

SM

ZS0918

SM

OMIT

2.0DIA-MLB-THIN-BC-K84

ZS0917

OMIT

SM

2.0DIA-MLB-THIN-BC-K84

ZS0912

2.0DIA-TALL-EMI-MLB-M97-M98

SM

OMIT

ZS0913

2.0DIA-TALL-EMI-MLB-M97-M98

SM

OMIT OMIT

ZS0914

2.0DIA-TALL-EMI-MLB-M97-M98

SM

ZS0915

SM

2.0DIA-TALL-EMI-MLB-M97-M98

OMIT

ZS0916

2.0DIA-MLB-THIN-BC-K84

SM

OMIT

Z0905

OMIT

3P2R2P7

Z0913

OMIT

3P2R2P7

ZS0911

2.0DIA-MED-EMI-MLB-K84

OMIT

SM

ZS0909

SM

2.0DIA-MED-EMI-MLB-K84

OMIT

ZS0908

2.0DIA-MED-EMI-MLB-K84

OMIT

SM

ZS0903

2.0DIA-MED-EMI-MLB-K84

OMIT

SM

ZS0902

SM

OMIT

2.0DIA-MED-EMI-MLB-K84

OMIT

ZS0901

SM

2.0DIA-MED-EMI-MLB-K84

ZS0900

2.0DIA-MED-EMI-MLB-K84

OMIT

SM

ZS0910

OMIT

SM

2.0DIA-TALL-EMI-MLB-M97-M98

Z0906

OMIT

3P2R2P7

Z0907

3P2R2P7

OMIT

ZS0907

SM

2.0DIA-TALL-EMI-MLB-M97-M98

OMIT

ZS0904

OMIT

2.0DIA-TALL-EMI-MLB-M97-M98

SM

OMIT

ZS0906

SM

2.0DIA-TALL-EMI-MLB-M97-M98

ZS0905

2.0DIA-TALL-EMI-MLB-M97-M98

SM

OMIT

Z0910

3P2R2P7

OMIT

R0940

5%

1/16W

402

100K

MF-LF

69 10 14

Z0903

STDOFF-4.5OD.98H-1.1-3.48-TH

Z0902

STDOFF-4.5OD.98H-1.1-3.48-TH

Z0904

STDOFF-4.5OD.98H-1.1-3.48-TH

Z0901

STDOFF-4.5OD.98H-1.1-3.48-TH

Z0911

OMIT

3P2R2P7

58

31

58

R0916

ENET1V05:EXT

402

MF-LF

1/16W

5%

0

R0915

0

5%

1/16W

MF-LF

ENET1V05:INT

402

18 63 62 61

8

R0970

MF-LF

1/16W

5%

100K

402

R0958

1.47K

1/16W

1%

MF-LF

402

C0958

0.1UF

CERM

20%

402

10V

R0957

1%

402

1/16W

1.47K

MF-LF

18

19

64

7

17

17