Page 1

8

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

7

6 5 4 3

2 1

REV ECN

DESCRIPTION OF REVISION

CK

APPD

DATE

6

0001395489

ENGINEERING RELEASED

2012-03-13

SCHEM,MLB,J30

03/12/12

D

C

B

Sync

Date

02/15/2011

02/15/2011

03/26/2009

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

09/27/2011

02/15/2011

06/13/2011

06/13/2011

06/13/2011

06/13/2011

06/13/2011

06/13/2011

02/15/2011

06/13/2011

02/15/2011

09/19/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

11/03/2011

06/13/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

06/15/2011

02/15/2011

02/15/2011

06/23/2011

02/15/2011

11/08/2011

07/08/2011

07/08/2011

02/15/2011

12/21/2011

Page

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

(.csa)

50

SMC Support

51

LPC+SPI Debug Connector

52

SMBus Connections

53

Power Sensors: Load Side

54

Power Sensors: High Side

55

Thermal Sensors

56

Fan

57

WELLSPRING 1

58

WELLSPRING 2

59

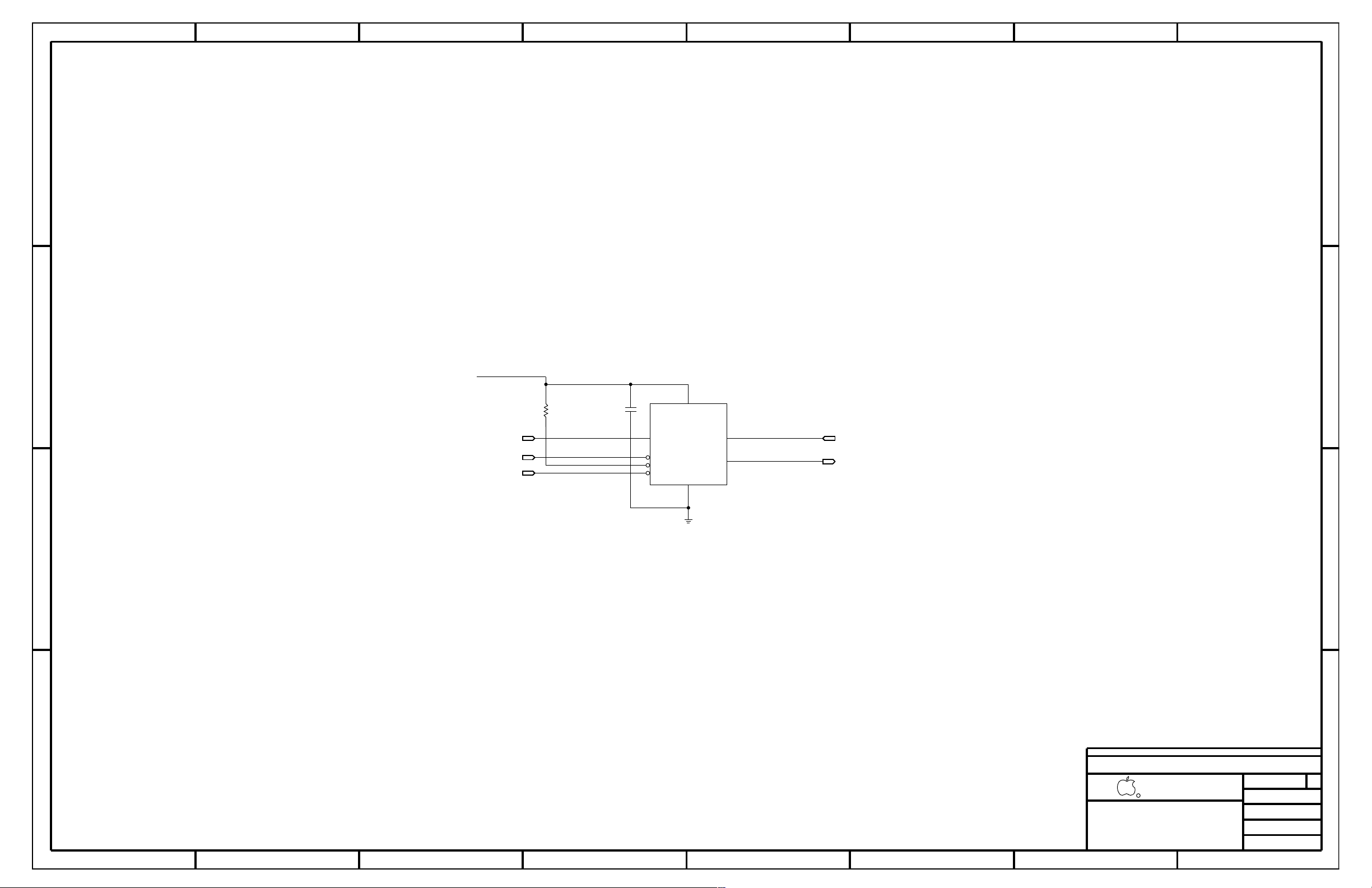

Digital Accelerometer

61

SPI ROM

62

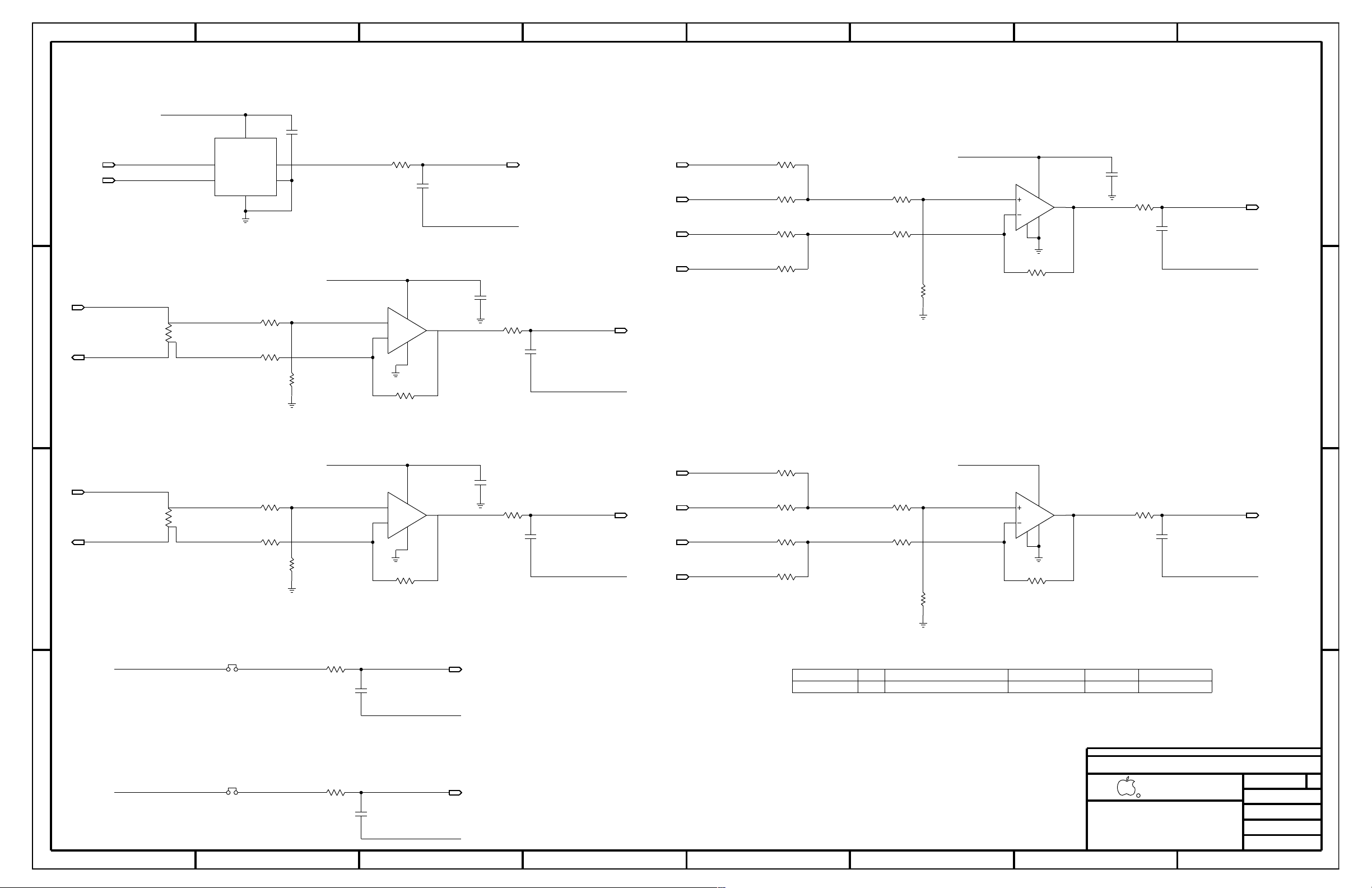

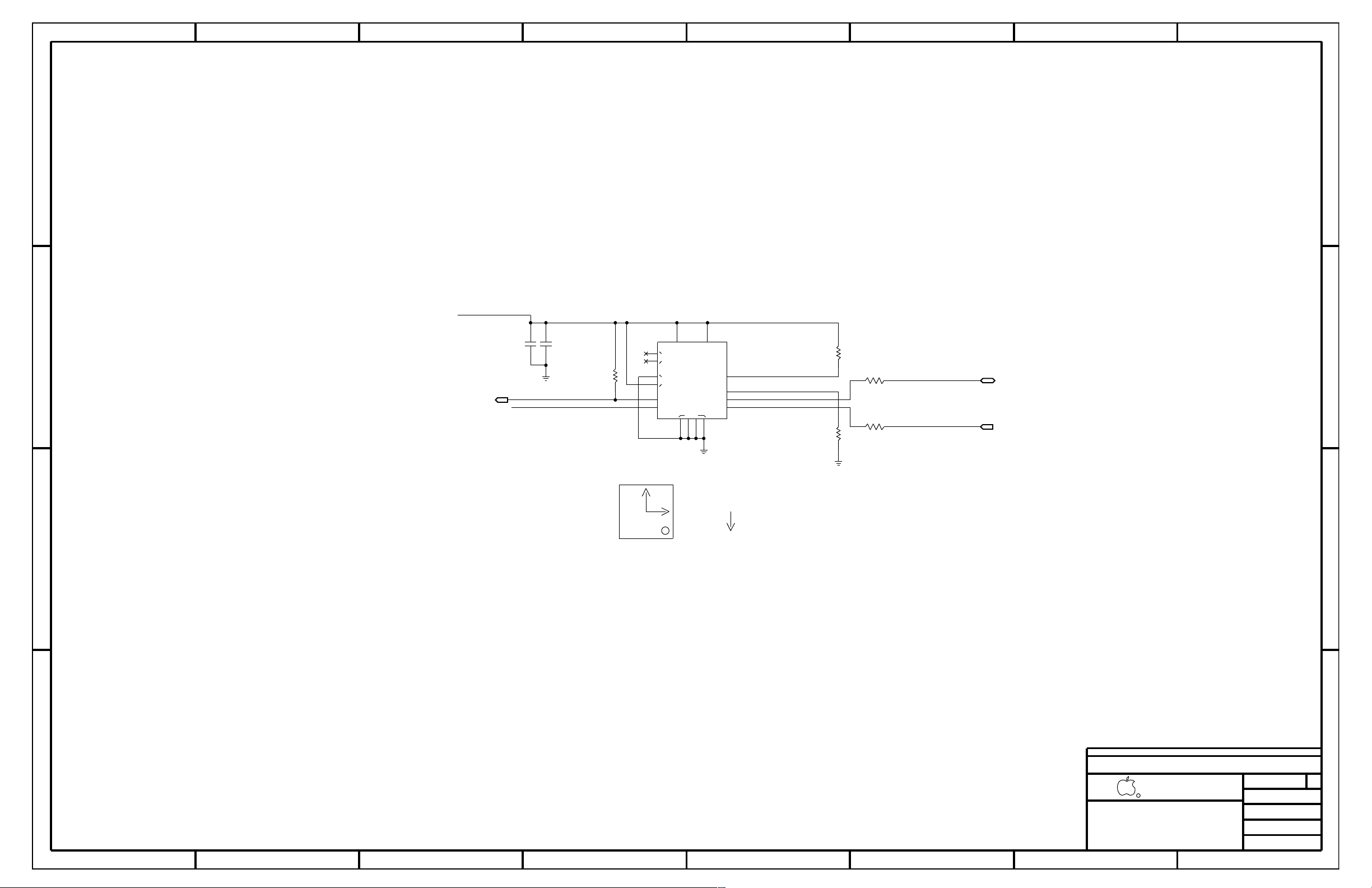

AUDIO: CODEC/REGULATOR

64

AUDIO: DETECT/MIC BIAS

65

AUDIO: HEADPHONE FILTER

66

AUDI0: SPEAKER AMP

67

AUDIO: JACK

68

AUDIO:Jack Translators

69

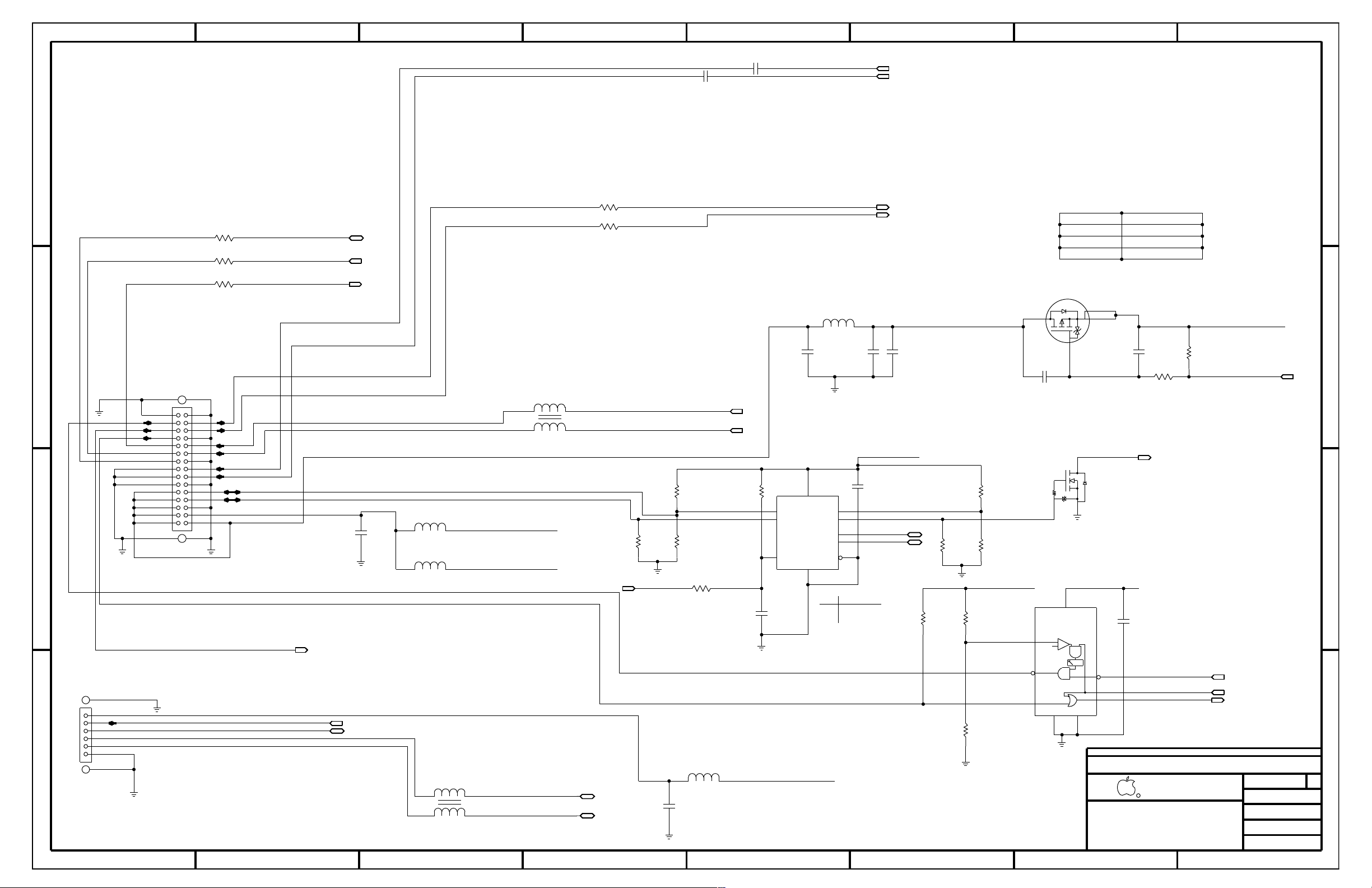

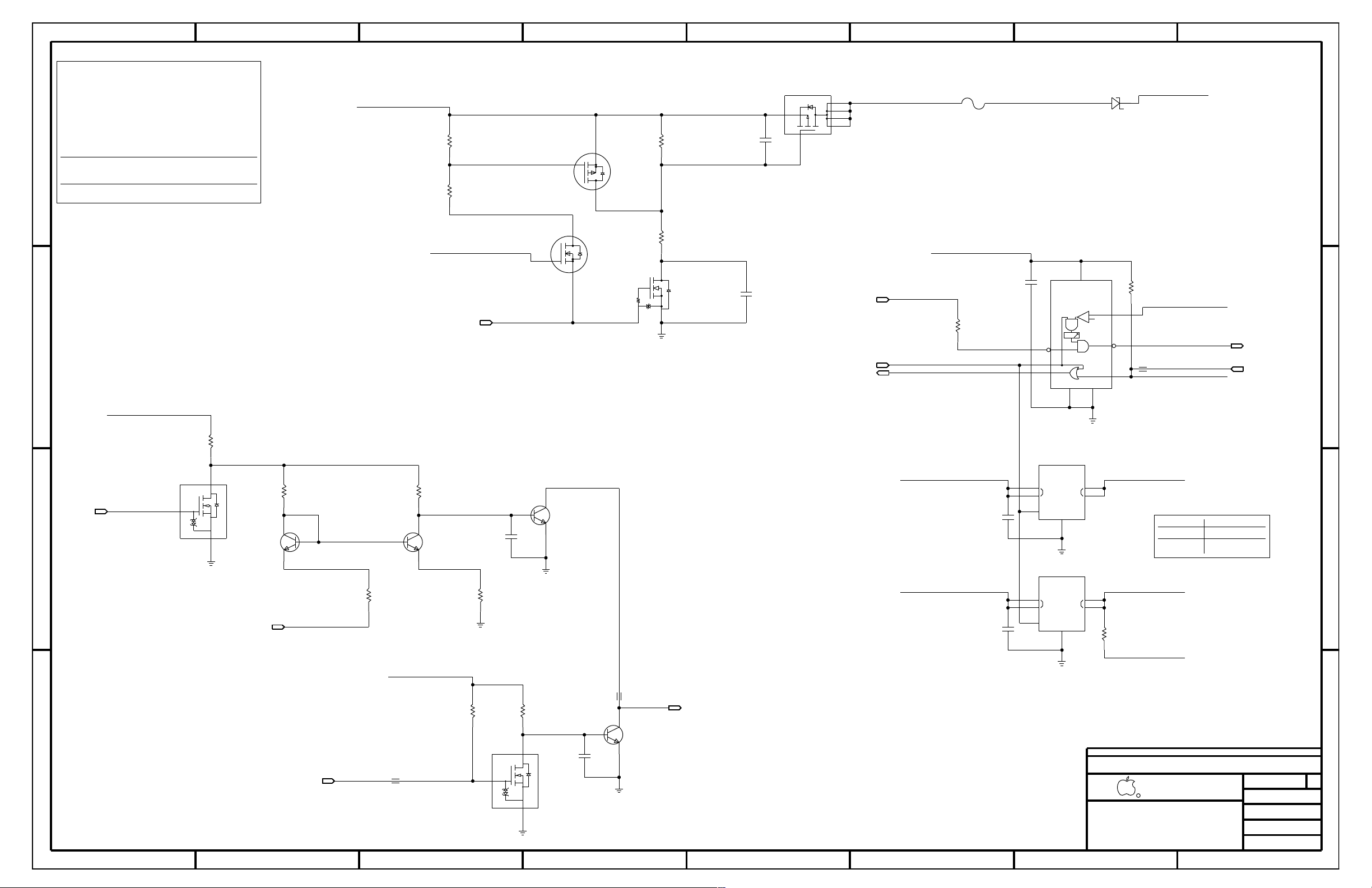

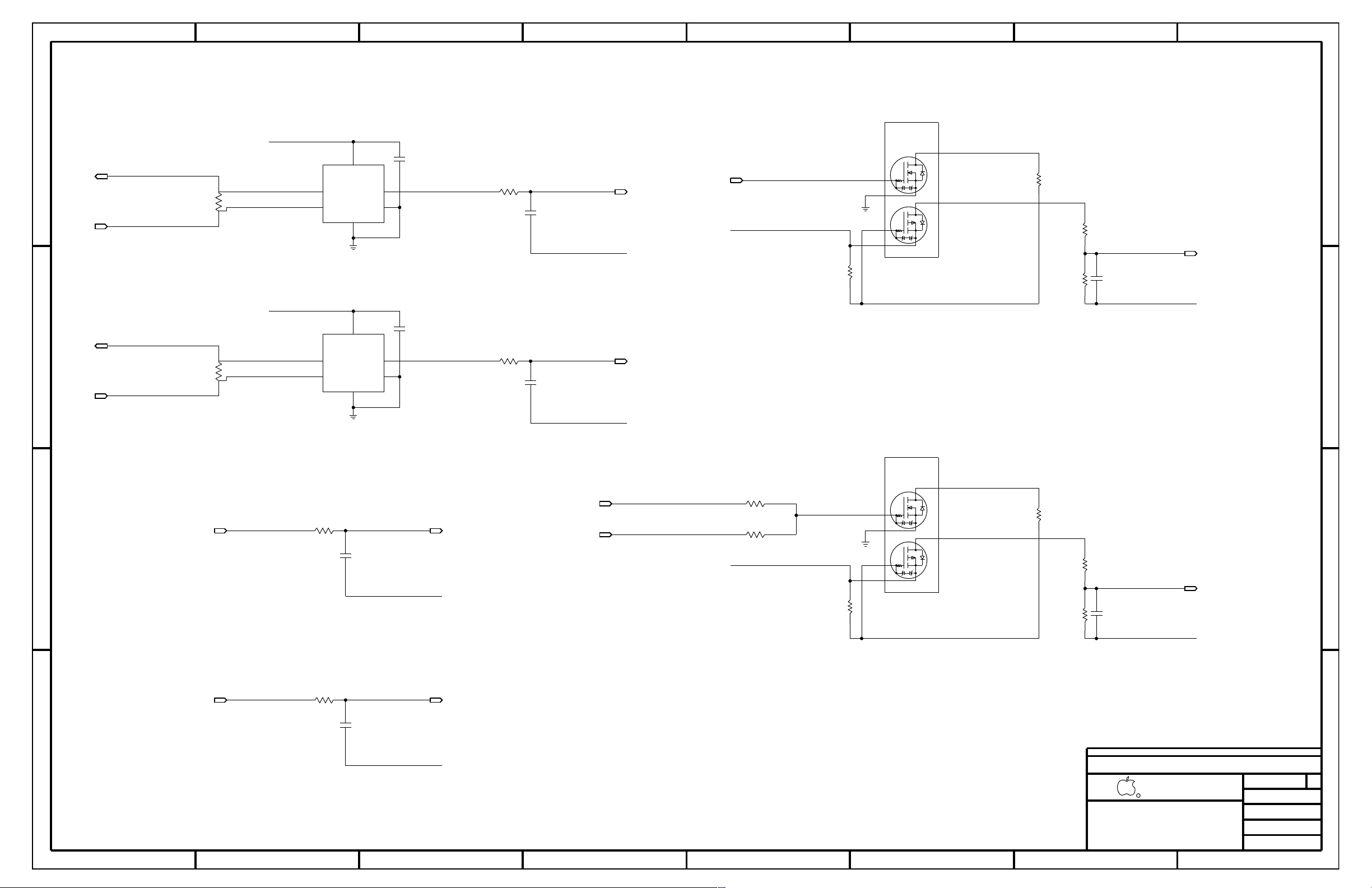

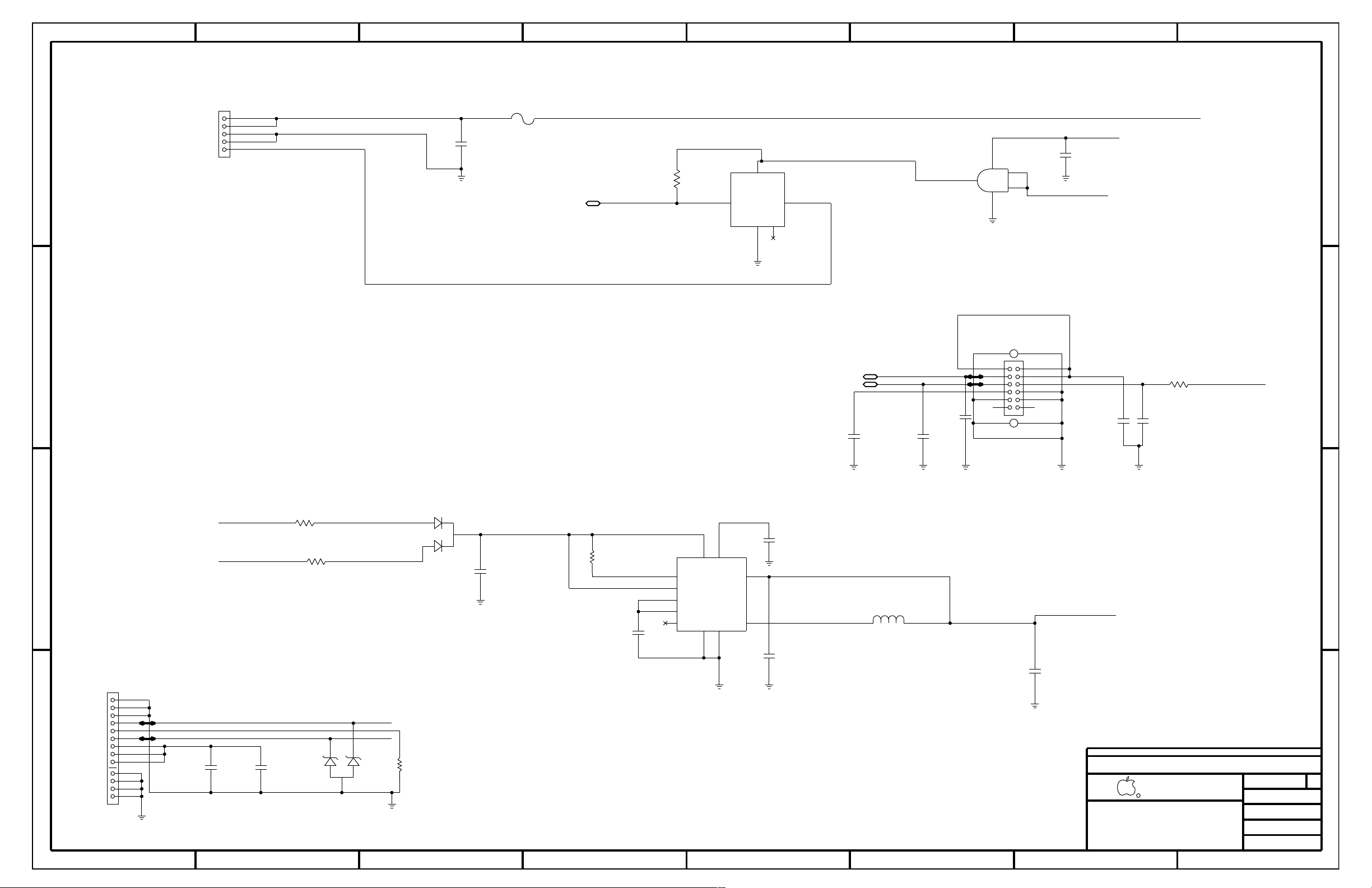

DC-In & Battery Connectors

70

PBus Supply & Battery Charger

71

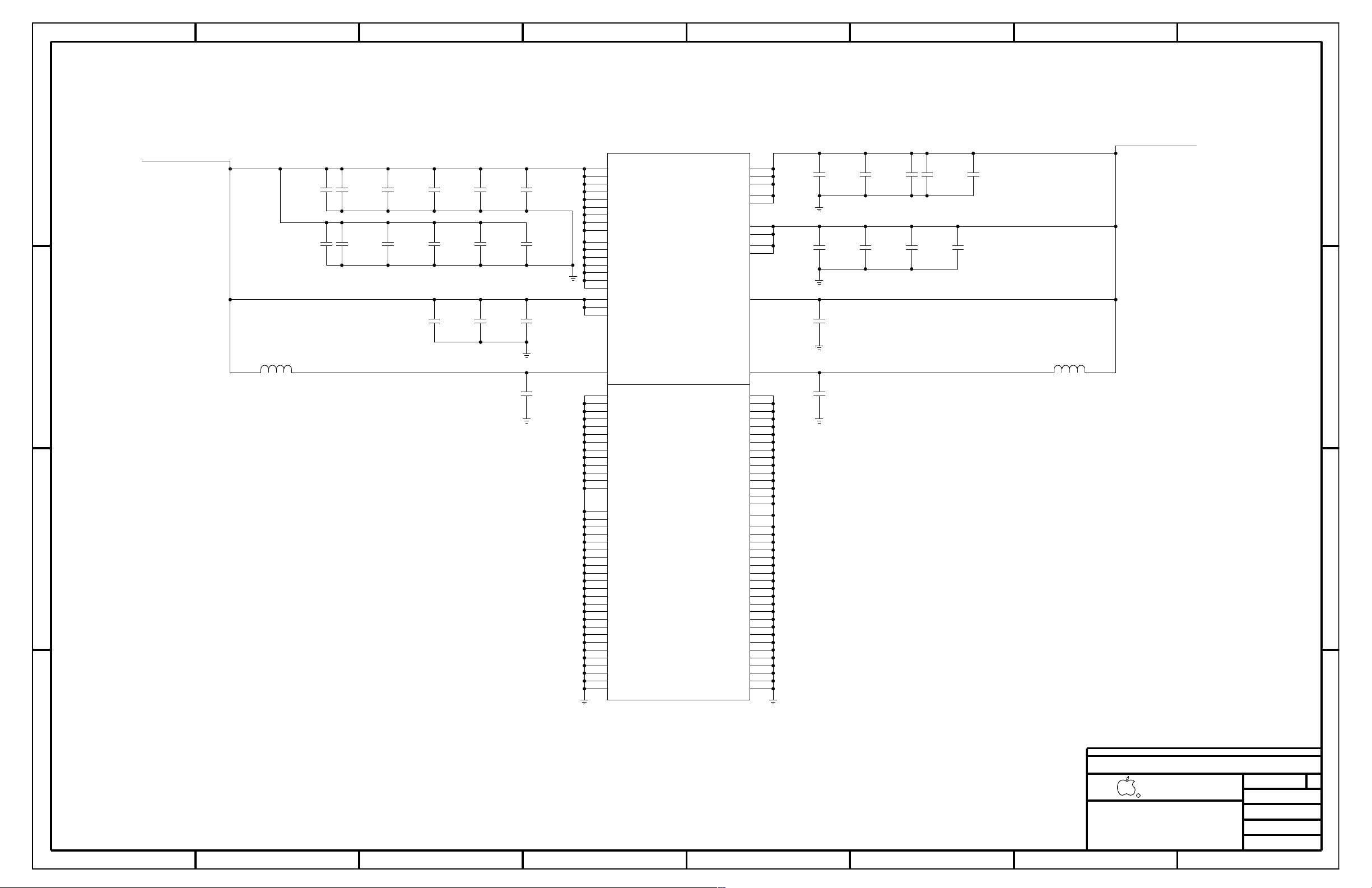

System Agent Supply

72

5V/3.3V SUPPLY

73

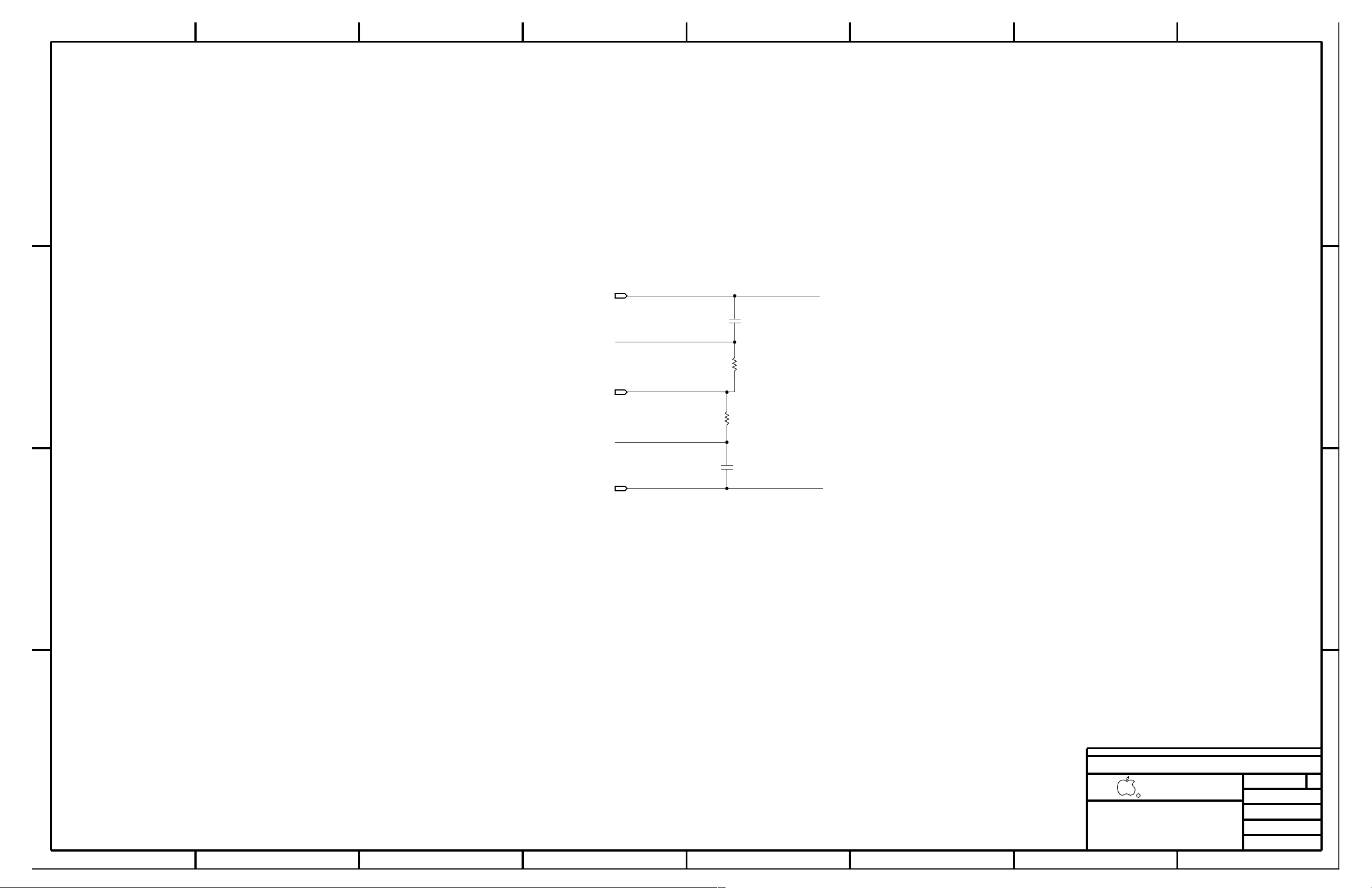

1.5V DDR3 Supply

74

CPU IMVP7 & AXG VCore Regulator

75

CPU IMVP7 & AXG VCore Output

76

CPUVCCIO (1.05V) Power Supply

77

Misc Power Supplies

78

Power FETs

79

Power Control 1/ENABLE

90

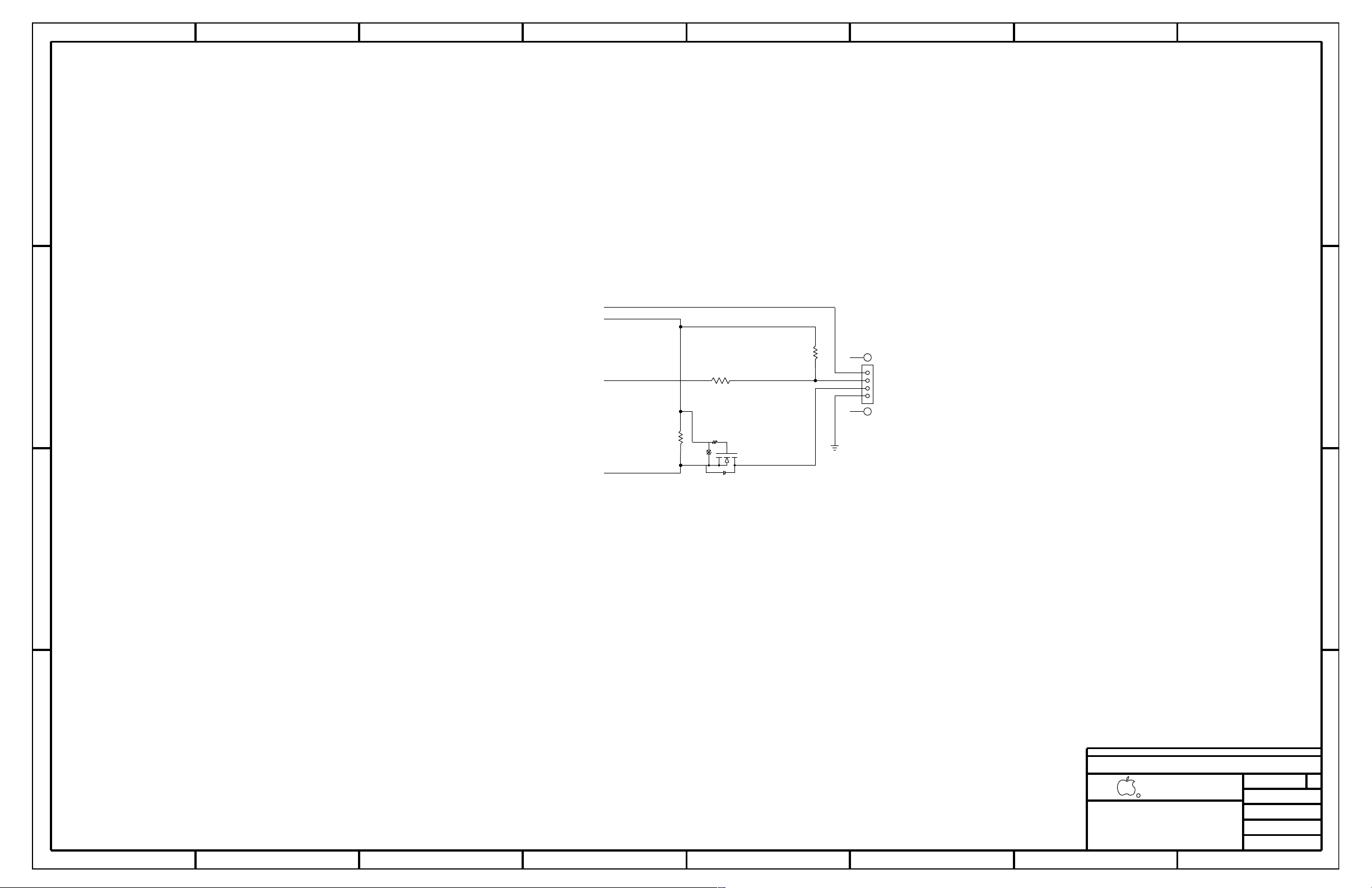

LVDS CONNECTOR

93

DisplayPort/T29 A MUXing

94

Thunderbolt Connector A

97

LCD Backlight Driver

100

CPU Constraints

101

Memory Constraints

102

PCH Constraints 1

103

PCH Constraints 2

104

Ethernet/FW Constraints

105

T29 Constraints

106

SMC Constraints

108

Project Specific Constraints

109

PCB Rule Definitions

Contents

Sync

YONAS_J30

J31_MLB

K90I_MLB

LINDA_J30

YONAS_J30

YONAS_J30

K90I_MLB

J31_MLB

JACK_J30

K90I_MLB

K90I_MLB

KAVITHA_J30

DIRK_J30

KAVITHA_J30

KAVITHA_J30

DIRK_J30

DIRK_J30

JACK_J30

JACK_J30

JACK_J30

JACK_J30

JACK_J30

JACK_J30

JACK_J30

JACK_J30

JACK_J30

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

J31_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

Date

01/02/2012

06/15/2011

02/15/2011

09/28/2011

11/03/2011

08/01/2011

02/15/2011

07/01/2011

09/28/2011

02/15/2011

02/15/2011

07/25/2011

02/16/2012

07/25/2011

07/25/2011

11/10/2011

02/20/2012

07/29/2011

09/27/2011

09/28/2011

08/22/2011

07/28/2011

08/03/2011

07/28/2011

09/28/2011

07/28/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

07/08/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

02/15/2011

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

(.csa)

1

1

2

3

4

5

6

7

8

9

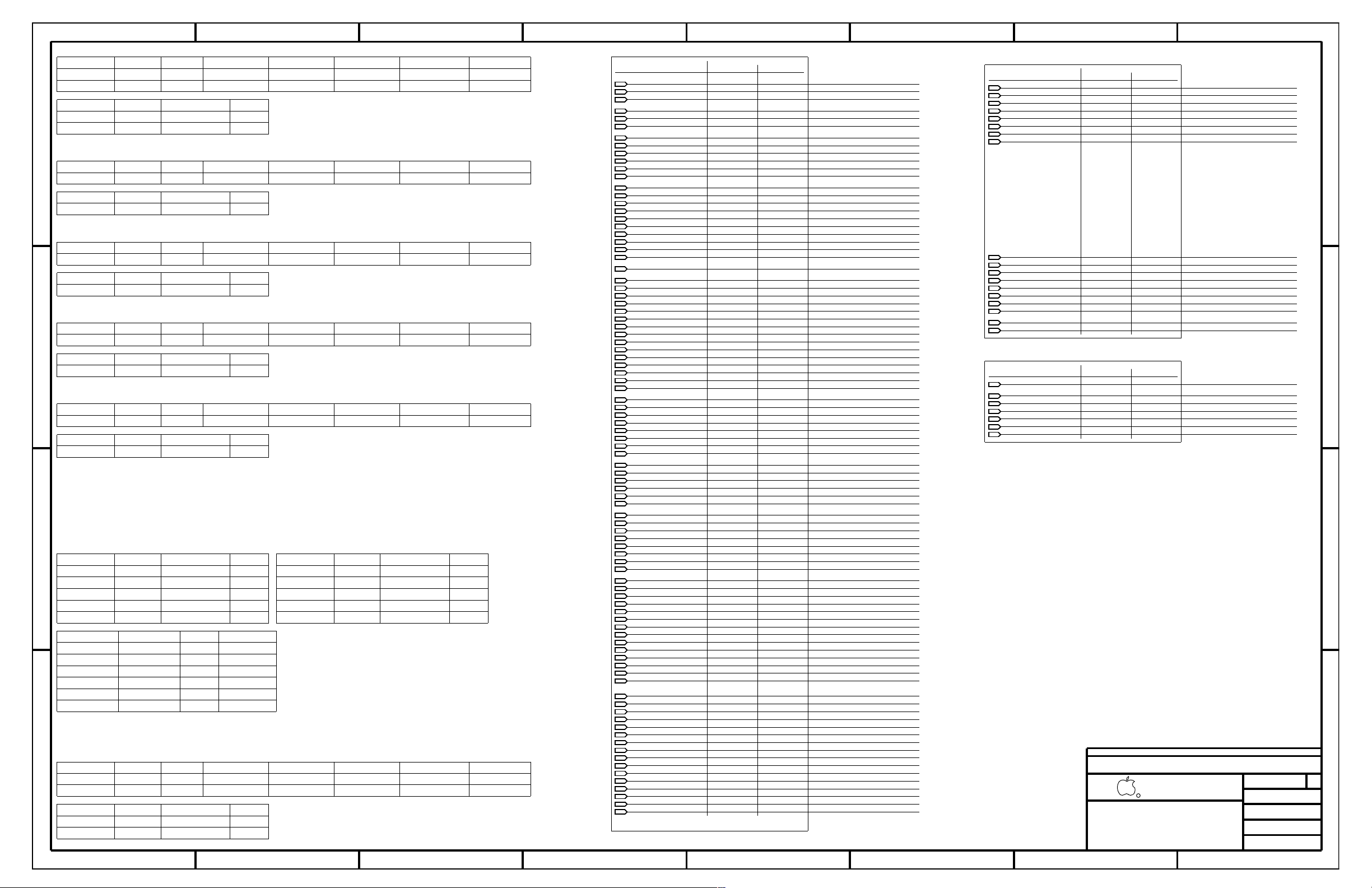

Table of Contents

2

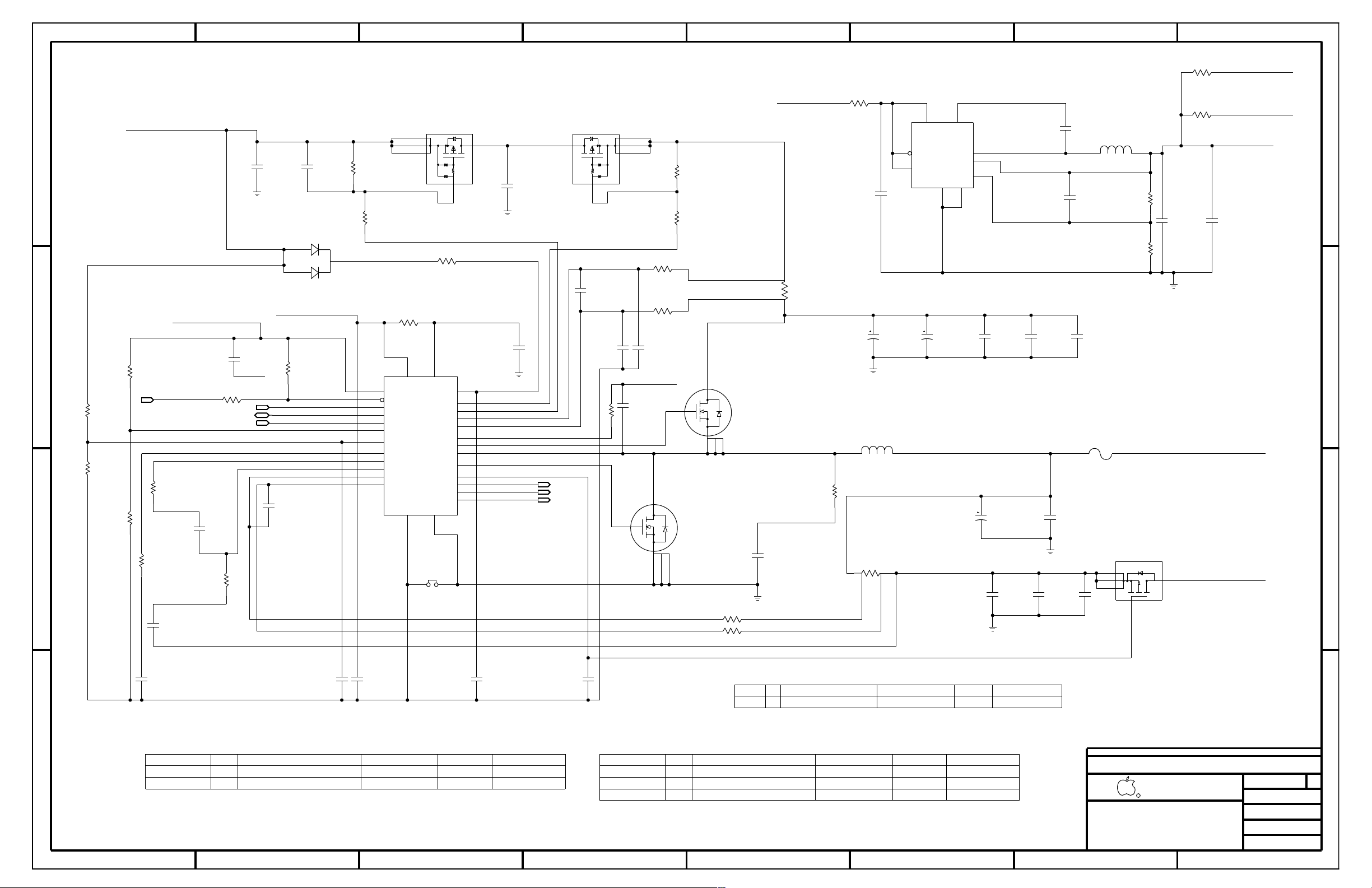

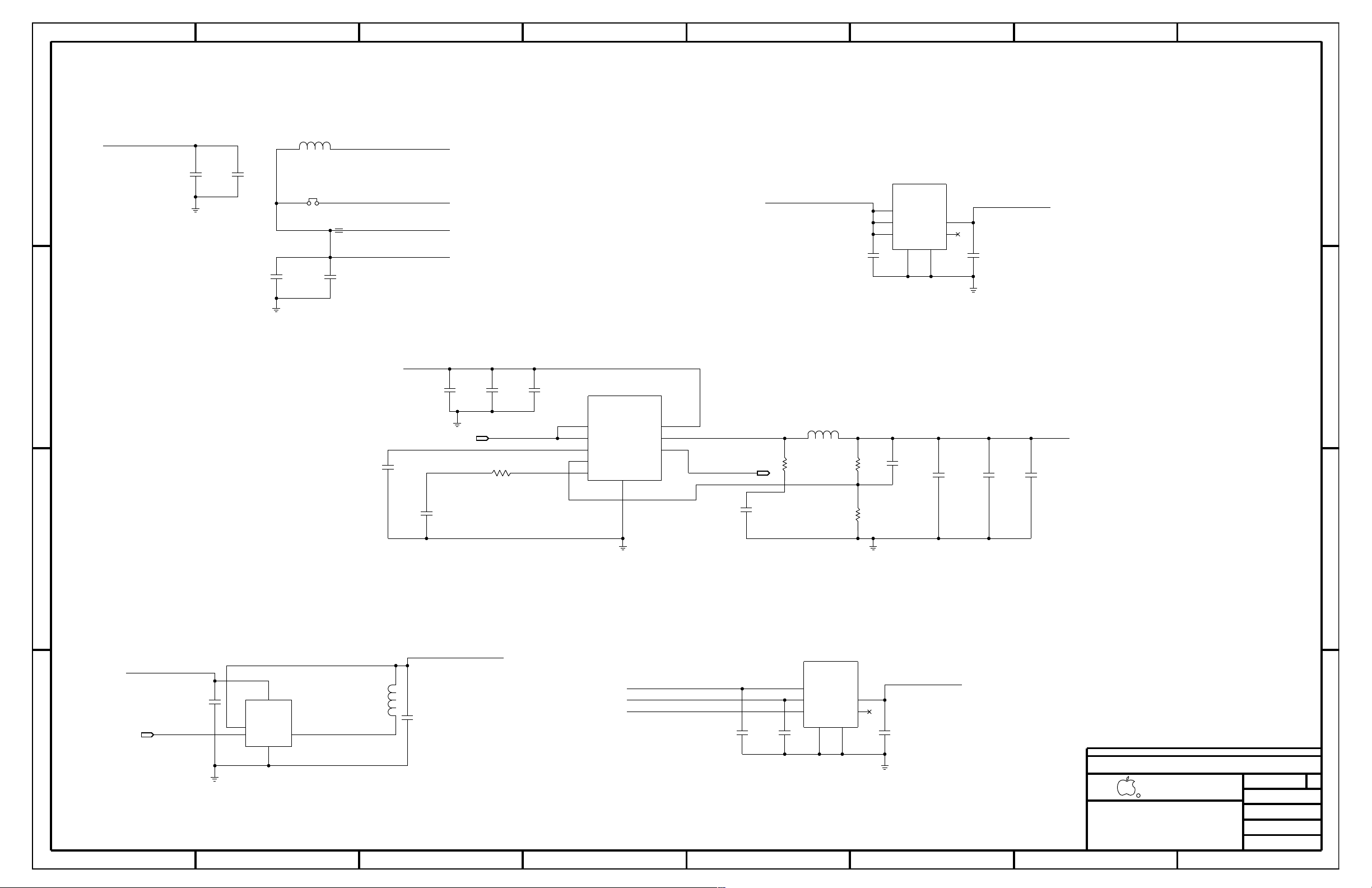

System Block Diagram

3

Revision History

4

Revision History

5

BOM Configuration

7

FUNC TEST

8

Power Aliases

9

Signal Aliases

10

CPU DMI/PEG/FDI/RSVD

11

CPU CLOCK/MISC/JTAG

12

CPU DDR3 INTERFACES

13

CPU POWER

14

CPU GROUNDS

16

CPU DECOUPLING-I

17

CPU DECOUPLING-II

18

PCH SATA/PCIe/CLK/LPC/SPI

19

PCH DMI/FDI/PM/Graphics

20

PCH PCI/USB/TP/RSVD

21

PCH GPIO/MISC/NCTF

22

PCH POWER

23

PCH GROUNDS

24

PCH DECOUPLING

25

CPU & PCH XDP

26

Chipset Support

27

USB HUB & MUX

28

CPU Memory S3 Support

29

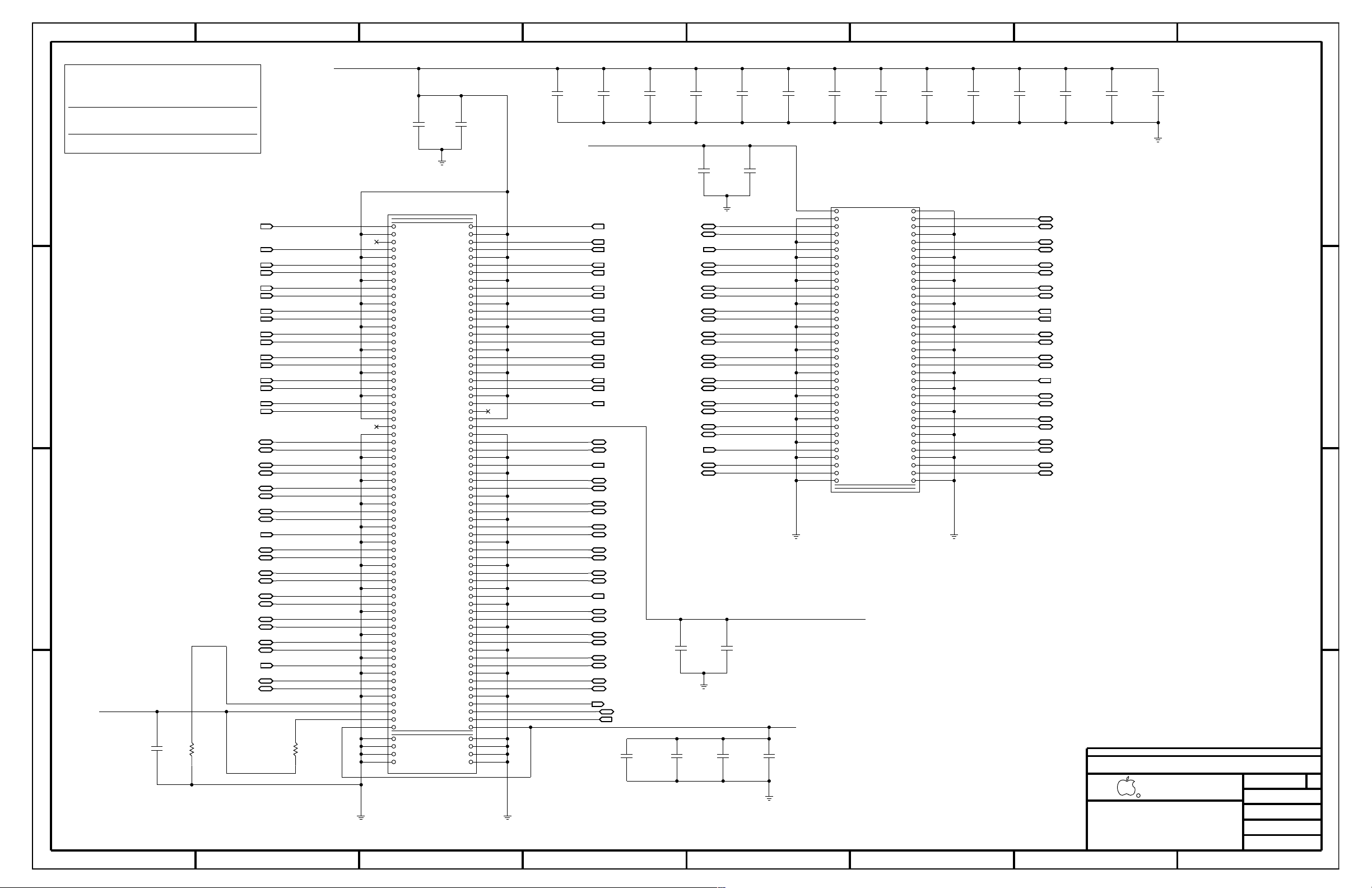

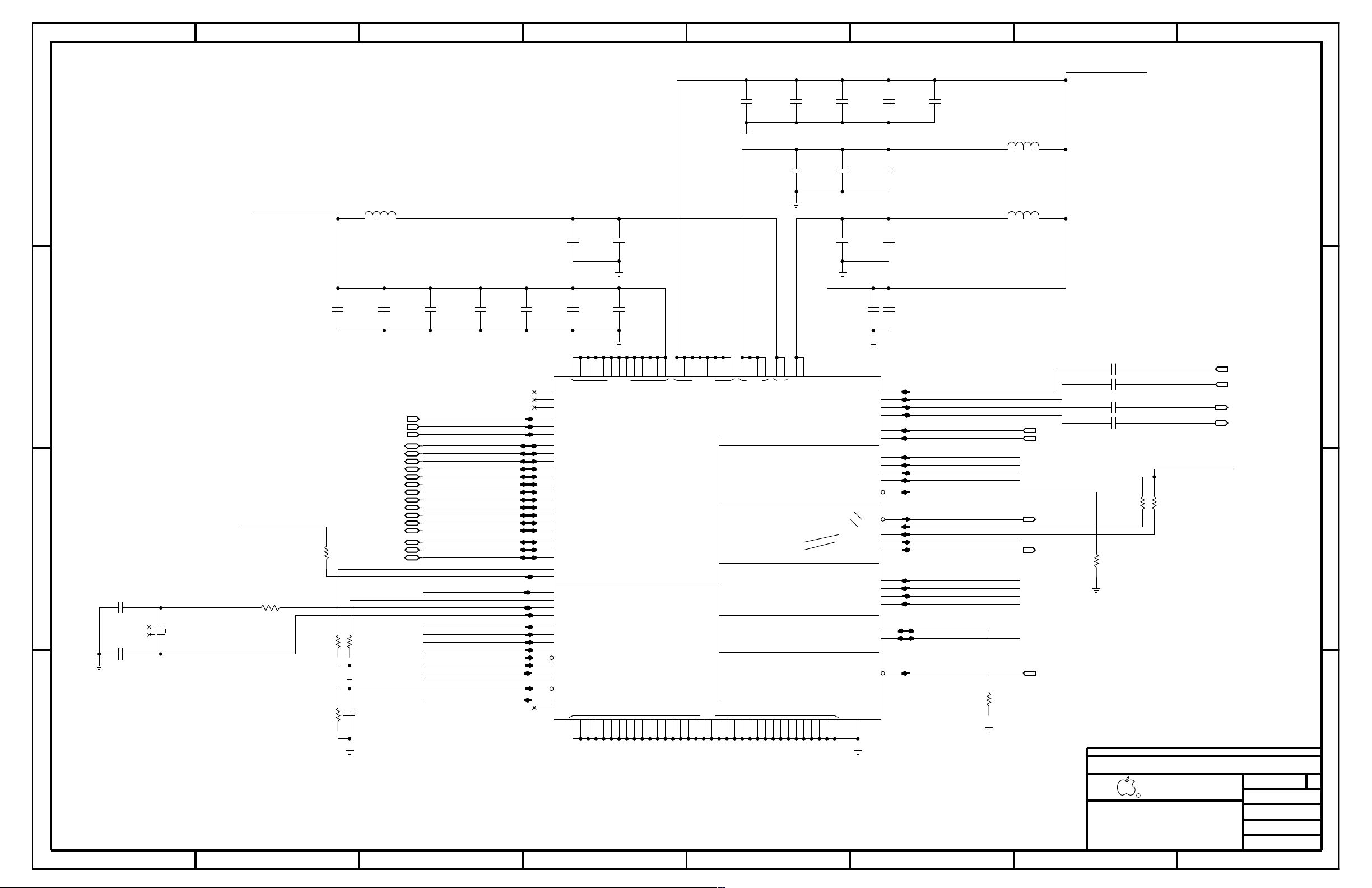

DDR3 SO-DIMM Connector A

30

DDR3 Byte/Bit Swaps

31

DDR3 SO-DIMM Connector B

33

SD Card Connector

34

DDR3/FRAMEBUF VREF MARGINING

35

X19/ALS/CAMERA CONNECTOR

36

T29 Host (1 of 2)

37

T29 Host (2 of 2)

38

T29 Power Support

39

ETHERNET PHY (CAESAR IV)

40

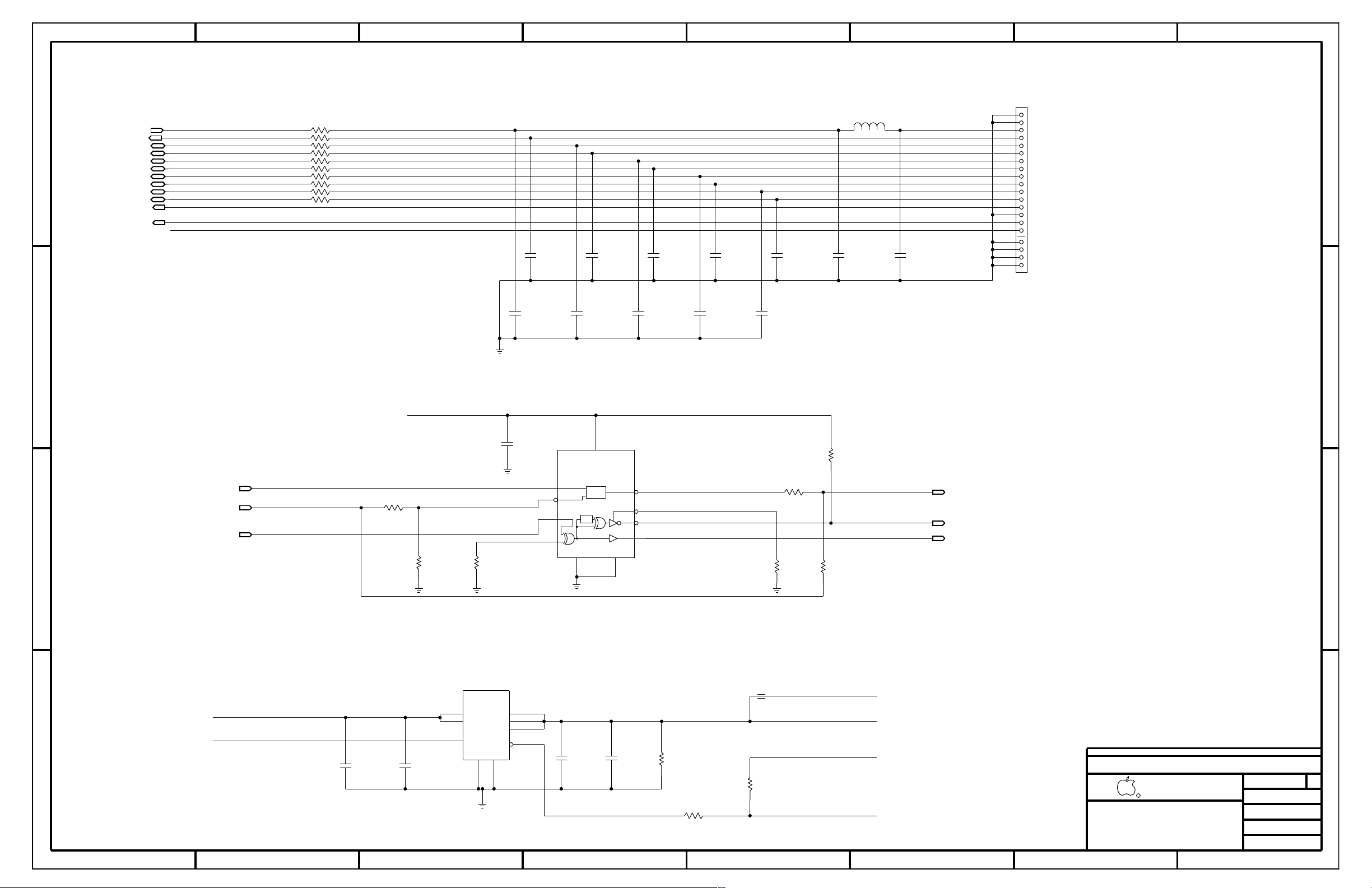

Ethernet Connector

41

FireWire LLC/PHY (FW643E)

42

FireWire Port & PHY Power

43

FireWire Connector

45

SATA/IR/SIL Connectors

46

External A USB3 Connector

47

External B USB3 Connector

48

Front Flex Support

49

SMC

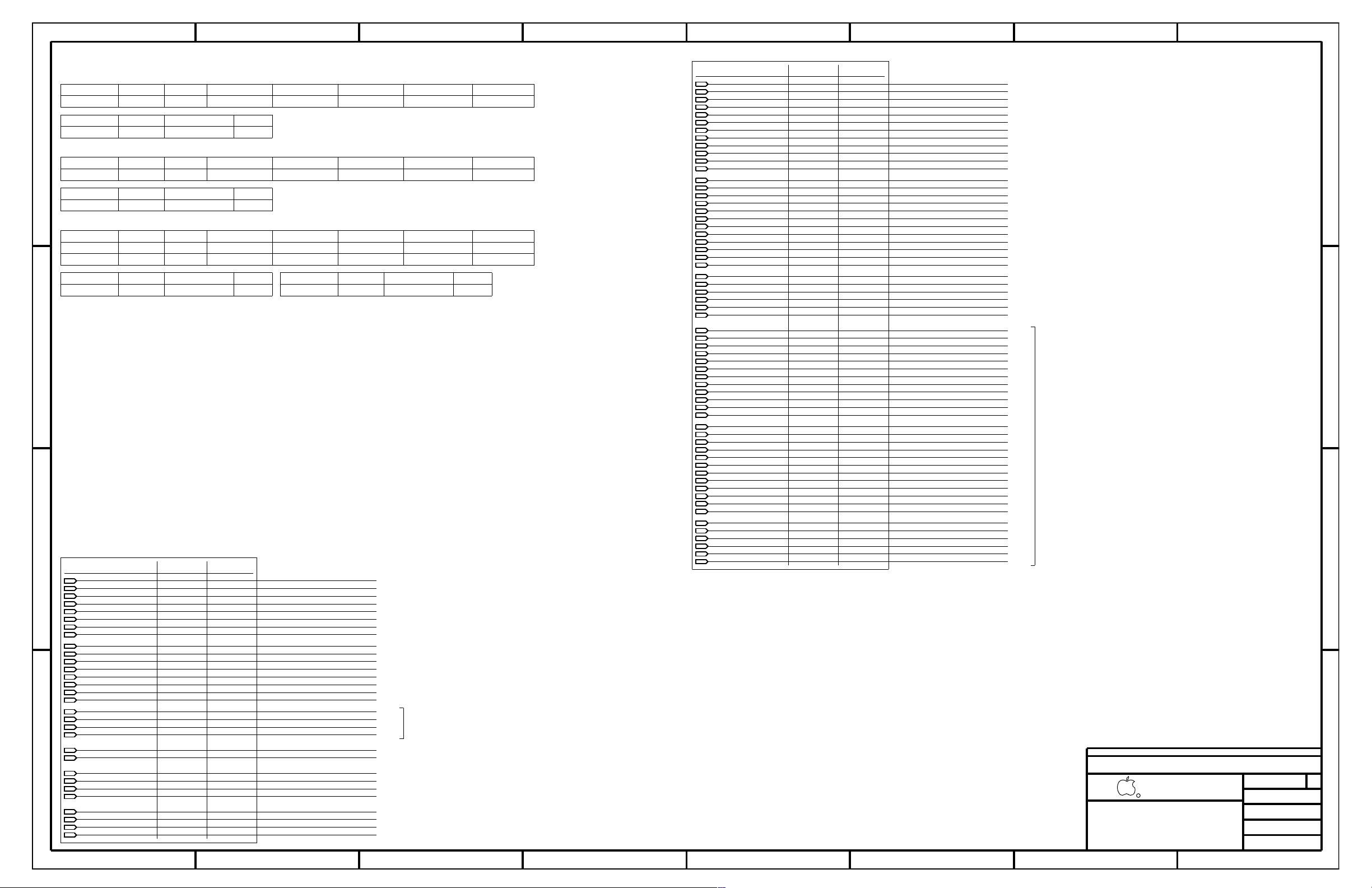

Contents

K90I_MLB

MASTER

K20A_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

MASTER

MASTER

MASTER

MASTER

MASTER

JACK_J30

MASTER

J31_MLB

J31_MLB

J31_MLB

J31_MLB

J31_MLB

J31_MLB

K90I_MLB

J31_MLB

K90I_MLB

LINDA_J30

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

YONAS_J30

J31_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

J31_MLB

K90I_MLB

K90I_MLB

K90I_MLB

K90I_MLB

YONAS_J30

J31_MLB

J31_MLB

K90I_MLB

YONAS_J30

D

C

B

Page

TABLE_TABLEOFCONTENTS_HEAD TABLE_TABLEOFCONTENTS_HEAD

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

A

Schematic / PCB #’s

PART NUMBER

051-9058

820-3115

DRAWING

TITLE=MLB

ABBREV=DRAWING

LAST_MODIFIED=Tue Mar 13 14:00:17 2012

QTY

1

1

DESCRIPTION

SCHEM,MLB,J30

PCBF,MLB,J30

REFERENCE DES

SCH

PCB

CRITICAL

CRITICAL

CRITICAL

BOM OPTION

SIZE

A

D

DRAWING TITLE

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

3

SCHEM,MLB,J30

Apple Inc.

R

DRAWING NUMBER

051-9058

REVISION

6.0.0

BRANCH

PAGE

1 OF 109

SHEET

1 OF 86

1245678

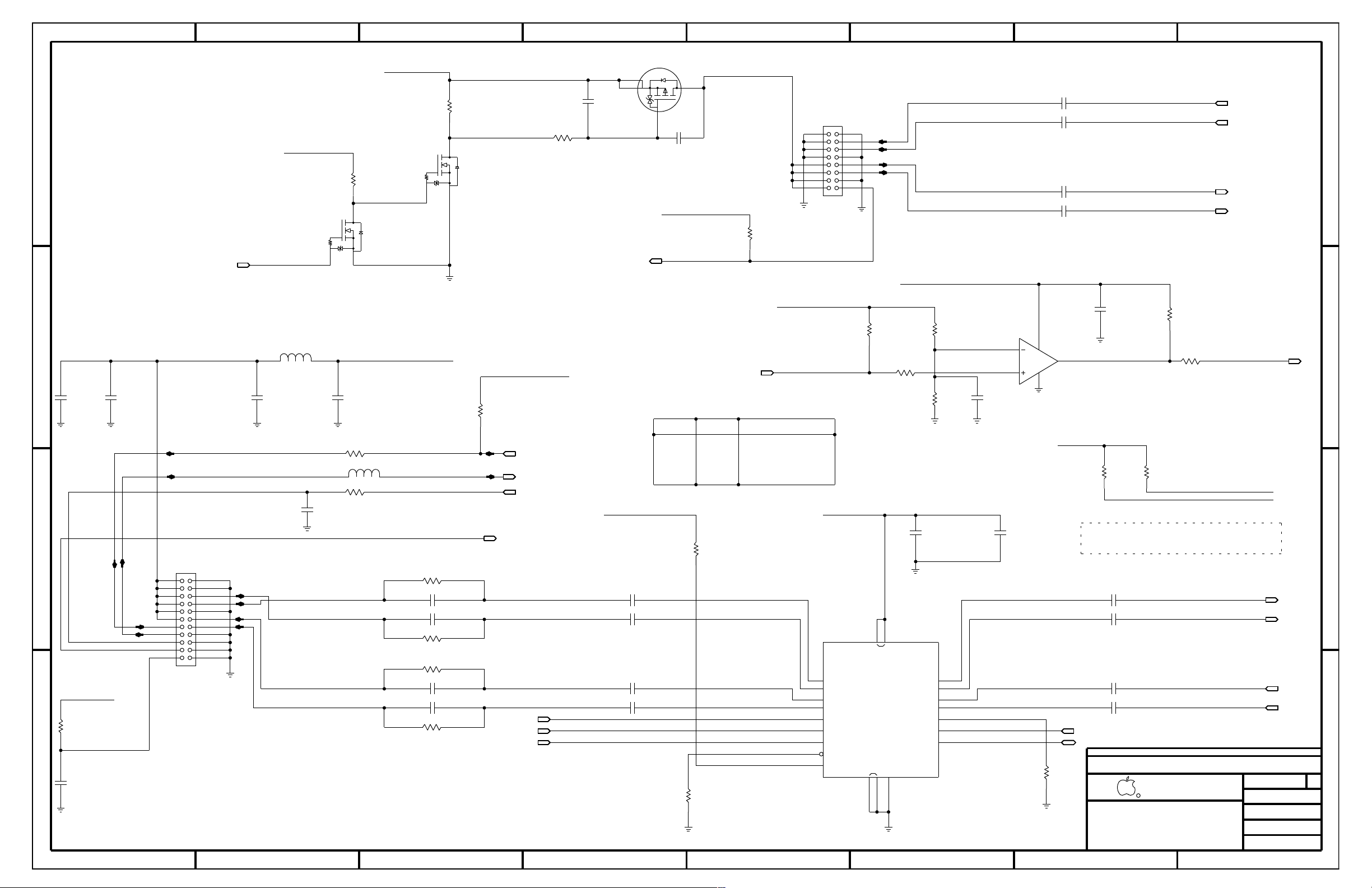

Page 2

8 7 6 5 4 3

12

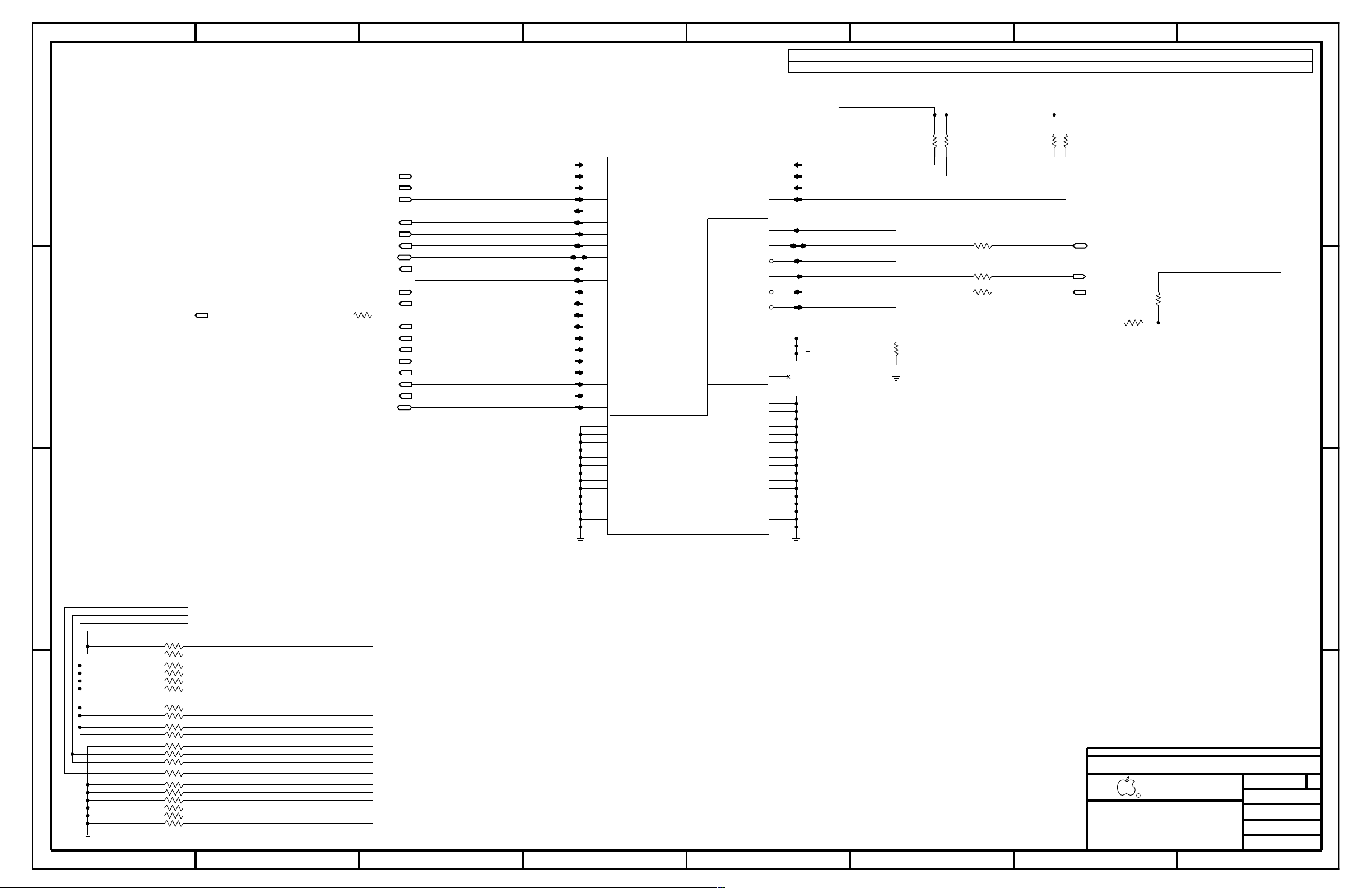

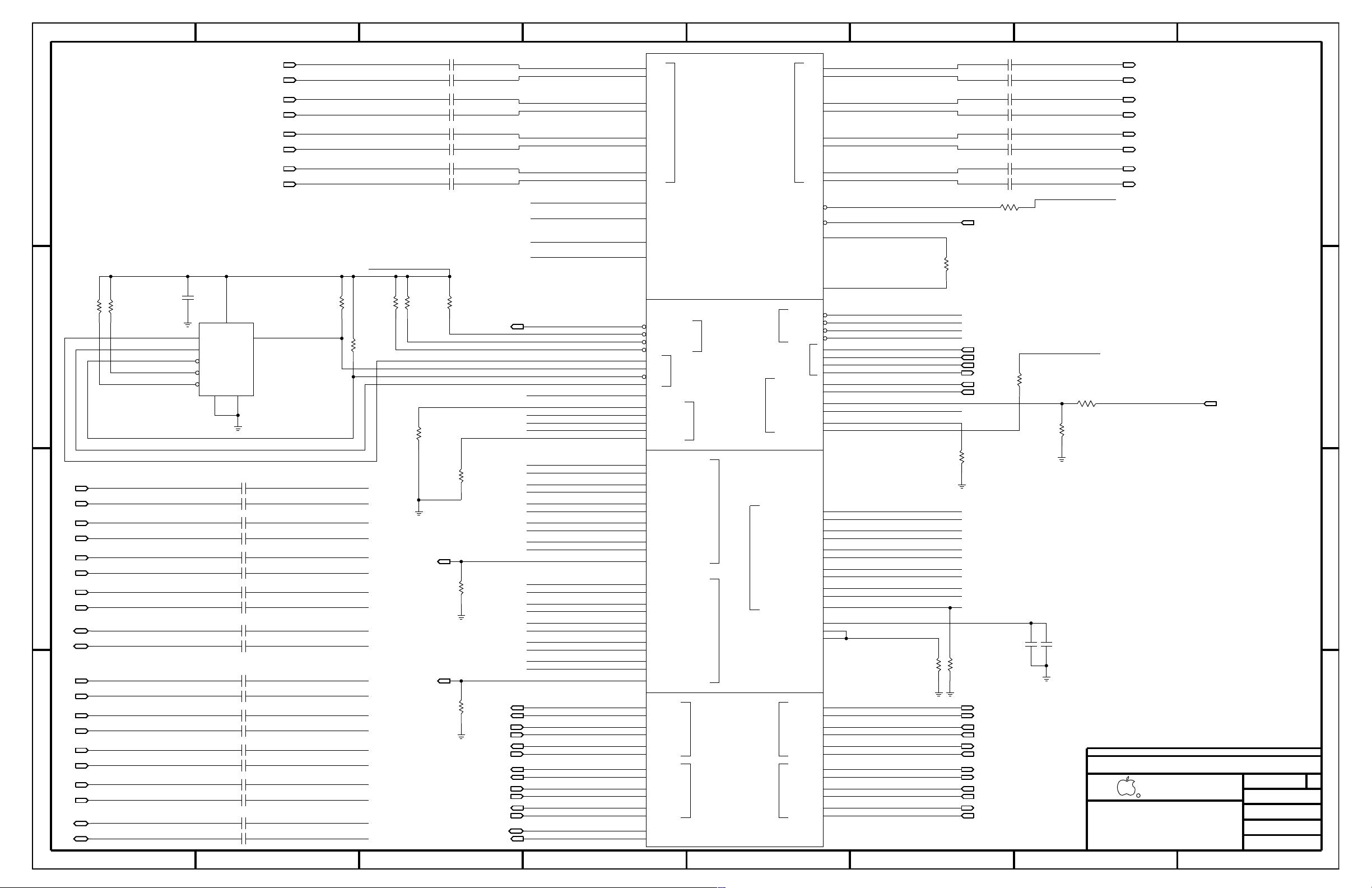

U1000

INTEL CPU

2.X GHz

IVY BRIDGE 2C-35W

PG 9-13

DDR3-1333/1600MHZ

D

GPIO

PG 19

U2600

SYSTEM

CLOCK

PG 24

J4501

SATA

CONN

HDD

PG 41

J4500

SATA

CONN

ODD

PG 41

U9390

MUX

PG 75

0

1

DP/TMDS

4 LANEs

U3600

CIO

PCIe x4

C

J9400

Display Port

/ T29

CONN

PG 76

1.05V/6GHZ.

1.05V/1.5GHZ.

T29 Host

PG 33,34

DP

J9000

LVDS

CONN

B

PG 74

BUFFER

PG 16

0

SATA

PG 16

1

eDP OUT

HDMI OUT

RGB OUT

DP OUT

DVI OUT

TMDS OUT

PG 17

LVDS OUT

PG 17

PG 18

PCI-E

PG 16

JTAG

PG 16

CLK

PCI

PEG

PG 16

FDI

PG 17

DMI

PG 17

INTEL

PANTHER POINT-MPCH

U1800

PG 16-21

PCI-E

(UP TO 8 LINES)

PG 16

2 3 1

PG 16

MISC

PG 19

SPI

PG 16

LPC

PG 16

PWR

CTRL

PG 17

USB

SMBUS

PG 16

HDA

PG 16

J2500

2 DIMMs

RTC

J3502

13

12

1011

8 9

6 70

543

21

(UP TO 14 DEVICES)

4

2 3

PG 18 PG 18

1

USB 3

XDP CONN

PG 23

J3100

PG 29

J2900

PG 27

DIMM

CAMERA

PG 32

DIMM’s

U6100

SPI

Boot ROM

PG 56

J3501

X19

Bluetooth

1 2 3

U2700

USB

HUB

PG 25

U4900

U5701

TP/KB

PSOC

From PCH

I2C

SMS ADC Ser

SMC

PG 45

J5800, J5713

J6900, J6950

DC/BATT

U5511

TEMP SENSOR

U5920

Sudden Motion Sensor

U5400,U5410,U5340,U5360,U5370,Q5480,Q5490

POWER SENSE

J5601

FAN CONN AND CONTROL

Fan

Prt

SPI

PG 63

PG 51

PG 55

PG 49, 50

PG 52

J5100

LPC+SPI Conn

Port80,serial

POWER SUPPLY

PG 63-73

PG 47

D

C

TRACKPAD/

PG 53PG 32

KEYBOARD

PG 54, 53

U4800

IR

Controller

PG 44 PG 41

U2760

USB

EHCI

MUX

XHCI

PG 25

J2550

J4501

IR

J4700

EXTERNAL B

USB 3

PG 43

J4600

EXTERNAL A

USB 3

PG 42

B

PCH XDP

CONN

PG 23

U6201

EXTMIC LINEIN HPOUT SPDIF MICIN LINEOUT

U4100

A

J3501

X19

AirPort

PG 32

FW643E

PG 38

J4310

FW800

CONN

PG 40

U3900

E-NET

BCM57765

PG 36

J4000

E-NET

CONN

PG 37

J3300

SD Card

CONN

PG 30

U6400

MIC BIAS

PG58

6 3

AUDIO

Codec

PG 57

J6700 J6701

AUDIO

CONNs

PG 61

U6610, U6620, U6630

SPEAKER

AMPs

PG 60

J6702

J6703

SYNC_MASTER=MASTER

PAGE TITLE

System Block Diagram

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=02/15/2011

DRAWING NUMBER

051-9058

REVISION

6.0.0

BRANCH

PAGE

2 OF 109

SHEET

2 OF 86

124578

SIZE

A

D

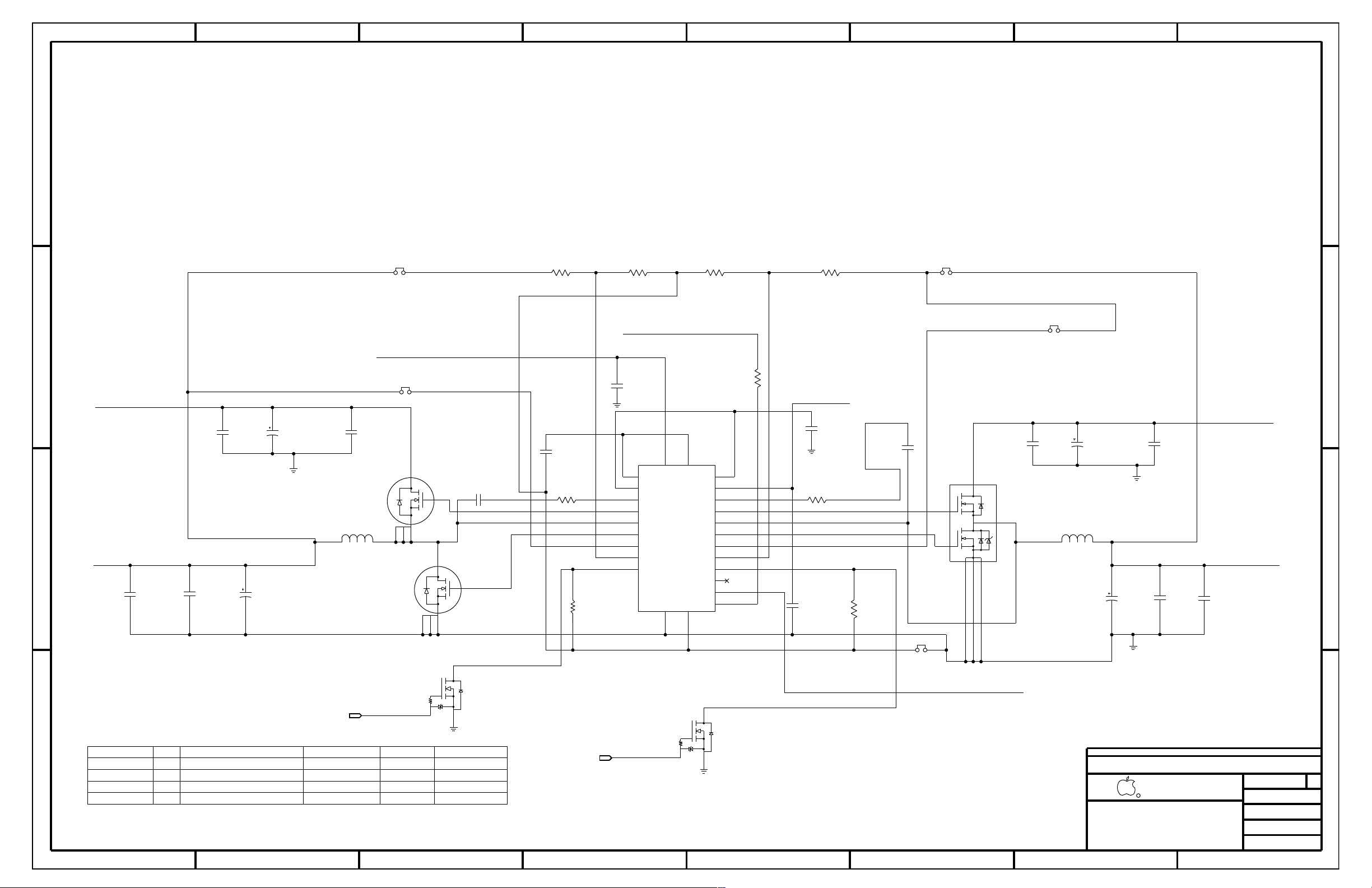

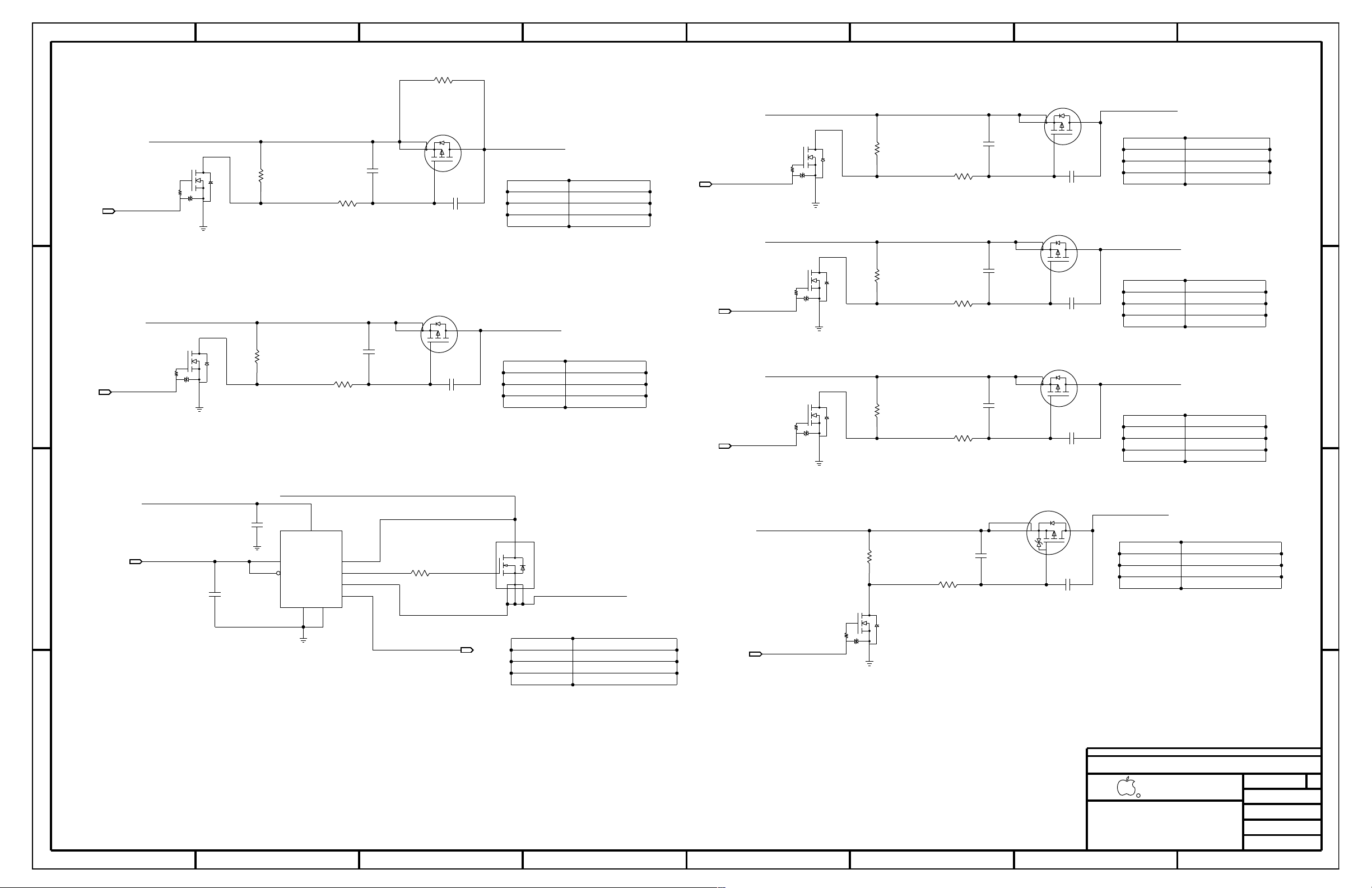

Page 3

8 7 6 5 4 3

12

R6905

Q5300

V

PP5V_S3_REG

PP3V3_S5_REG

D6990

R5400

A

22

PP3V3_S5

8

PP3V3_ENET

Q7922

PM_SLP_S3_L&&WOL_EN||SMC_ADAPTER_EN//WOL_EN

R7803

Q7800

P3V3S4_EN

Q7810

P3V3S3_EN

Q7820

P5V_3V3_SUS_EN

Q7830

PM_SLP_S3_L_R

2

15

PP5V_S0_CPUVCCIOS0

CPUVCCIOS0_EN

21

24

CPUIMVP_VR_ON

DDRREG_EN

DDRVTT_EN

PP5V_S0_FET

PVCCSA_EN

CPU_VCCSA_VID<1>

CPU_VCCSA_VID<0>

14

BCM57765

EN

U3900

CAESAR IV

(PAGE 36)

PP3V3_S4_FET

PP3V3_S3

PP3V3_SUS_FET

TPS720105

U7740

(PAGE 71)

14

VCC

EN

VR_ON

Q7860

P5VS0_EN

Q4590

ODD_PWR_EN_L

12

14

10-3

PP1V05_SUS_LDO

ENABLE

3.425V G3HOT

PM6640

U6990

(PAGE 63)

1.05V

ISL95870

U7600

(PAGE 70)

VIN

CPU VCORE

MAX15119GTM

U7400

(PAGE 68)

1.5V

S5

S3

0.75V

TPS51916

U7300

(PAGE 67)

VCC

EN

ISL95870A

VID0

VID1

(PAGE 65)

PP5V_S0_FET

PP5V_SW_ODD

PP1V2_ENET_PHY

VOUT

PGOOD

VOUT

VOUT

PGOOD

PGOODG

VLDOIN

VIN

VOUT1

VOUT2

PGOOD

VOUT

U7100

PGOOD

15

P1V8_S0_EN

17

P1V5S0_EN

9

19

PP3V3_FW_P3V3FWFET

PP3V42_G3H_REG

R7640

A

CPUVCCIOS0_PGOOD

CPUIMVP_PGOOD

CPUIMVP_AXG_PGOOD

PPDDR_S3_REG

PPVTT_S0_DDR_LDO

DDRREG_PGOOD

PP1V5S0FET_GATE

PPVCCSA_S0_REG

PVCCSA_PGOOD

PP5V_S0_VMON

PP1V5_S3RS0_VMON

PP1V05_S0_VMON

PP3V3_S0

16

MAX15053EWL

EN

U7760

(PAGE 71)

TPS62201

EN

U7770

(PAGE8 71)

TPS22924

EN

U4201

(PAGE 39)

PPCPUVCCIO_S0_REG

SMC_CPU_FSB_ISENSE

22-1

R5320

SMC_CPU_VSENSE

V

PPVCORE_S0_CPU_REG

R5330

SMC_GFX_VSENSE

V

PPVCORE_S0_AXG_REG

25-1

26-1

Q7801

PP1V5_S3RS0_FET

23

23-1

PP3V3_S0_VMON

VMON_Q2

ISL88042IRTEZ

VMON_Q3

VMON_Q4

(PAGE 73)

PP1V8_S0_REG

PP1V5_S0_REG

PP3V3_FW_FE5T

3

16

U7960

P1V05_S0_LDO_EN

SMC PWRGD

SN0903048

(PAGE 44)

22

18

EN

20

U5010

25

26

CPUIMVP_AXG_PGOOD

P1V8S0_PGOOD

P5V3V3_PGOOD

CPUVCCIOS0_PGOOD

PVCCSA_PGOOD

ALL_SYS_PWRGD

TPS720105

U7780

(PAGE 71)

PP1V05_S0_LDO

SMC_RESET_L

TPS22924

U4202

(PAGE 39)

EN

FW_PWR_EN

RSMRST_PWRGD

SMC_ONOFF_L

4

PP1V0_FW_FWPHY

COUGAR-POINT

(PCH)

SYS_RERST#

27

U2850

25

9

5

PM_SLP_S5_L

PM_SLP_S4_L

PM_SLP_S3_L

19

SYNC_MASTER=K20A_MLB

PAGE TITLE

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

U1800

PM_PCH_PWRGD

(PAGE 16~21)

SM_DRAMPWROK

CPU

U1000

UNCOREPWRGOOD

(PAGE 9~13)

SMC

PWRGD(P12)

RSMRST_IN(P13)

PWR_BUTTON(P90)

SLP_S5_L(P95)

SLP_S4_L(P94)

SLP_S3_L(P93)

U4900

(PAGE 43)

RSMRST_OUT(P15)

99ms DLY

IMVP_VR_ON(P16)

Revision History

Apple Inc.

R

PWRBTN#

RSMRST#

PLTRST#

PROCPWRGD

DRAMPWROK

RESET*

SYSRST(PA2)

P17(BTN_OUT)

RES*

PM_PWRBTN_L

PM_SYSRST_L

PM_RSMRST_L

PM_DSW_PWRGD

PLT_RERST_L

CPU_PWRGD

PM_MEM_PWRGD

30

PM_DSW_PWRGD

PM_RSMRST_L

CPUIMVP_VR_ON

PM_SYSRST_L

PM_PWRBTN_L

SMC_RESET_L

29

28

10

12

DRAWING NUMBER

REVISION

BRANCH

PAGE

SHEET

124578

26

6-1

4

SYNC_DATE=03/26/2009

051-9058

6.0.0

3 OF 109

3 OF 86

SIZE

D

C

B

A

D

J30 POWER SYSTEM ARCHITECTURE

PPDCIN_G3H

V

1

R7020

A

SMC_RESET_L

VIN

BATTERY CHARGER

Q7055

CHGR_BGATE

U7000

ISL6259HRTZ

PBUS SUPPLY/

(PAGE 63)

D

J6900

AC

ADAPTER

DCIN(16.5V)

F6905

6A FUSE

IN

J6950

PPVBATT_G3H_CONN

3S2P

(9 TO 12.6V)

Q5310

SMC_DCIN_ISENSE

R6990

VOUT

PPVBAT_G3H_CHGR_R

PPVBAT_G3H

R7050

SMC_BATT_ISENSE

PPDCIN_S5_P3V42G3H

F7040

1

A

PPBUS_G3H

C

SMC

U4900

P60

(PAGE 44)

SLP_S5#(E4)

COUGAR-POINT

(PCH)

B

A

U1800

(PAGE 16~21)

RC

DELAY

RC

DELAY

RC

DELAY

RC

DELAY

SLP_S4#(H4)

SLP_S3#(F4)

1V05_S0_LDO_EN

CPUVCCIOS0_EN

PVCCSA_EN

P1V5S0_EN

P1V8S0_EN

SMC_PM_G2_EN

SLP_SUS

PM_SLP_S3_L_R

21

21

22

19

17

6

R7916

PM_SLP_S5_L

R7917

RC

DELAY

RC

DELAY

R7978

P5VS0_EN

P3V3S0_EN

PBUSVSENS_EN

RC

DELAY

P3V3S4_EN

P5V_3V3_SUS_EN

P5VS3_EN

DDRREG_EN

P3V3S3_EN

PM_SLP_S4_L

PM_SLP_S3_L

PG73

P3V3S5_EN

PG73

PG 17

PG73

PG73

PG73

PG 17

PG 17

14-1

14-1

14-1

7

11

11

10-1

PG73

13-1

15

13-2

13

14

F9700

LCD_BKLT_EN

BKLT_PLT_RST_L

&&

PPBUS_SW_LCDBKLT_PWR

Q4260

FWP5ORT_PWR_EN

T29_A_HV_EN

www.qdzbwx.com

R5410

A

13

Q9706

VIN

LP8550

U9701

EN

(PAGE 76)

Q3880

PPBUS_S5_HS_OTHER_ISNS

P5VS3_EN_L

P3V3S5_EN_L

7

PP5V_S5_LDO

PPVOUT_SW_LCDBKLT

VOUT

F4260

LT3957

U3890

(PAGE 35)

PPBUS_FW_FET

VIN

VOUT

EN1

EN2

VREG5

P5V_3V3_SUS_EN

PP15V_T29_REG

VIN

5V

(L/H)

3.3V

(R/H)

TPS51125

U7200

(PAGE 66)

PGOOD

P5V3V3_PGOOD

Q7840

VOUT1

VOUT2

14-1

PP5V_SUS_FET

10-2

6 3

Page 4

PROTO:

8 7 6 5 4 3

12

D

C

D

C

SIZE

B

A

D

B

A

6 3

SYNC_MASTER=K90I_MLB SYNC_DATE=02/15/2011

PAGE TITLE

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

Revision History

Apple Inc.

R

DRAWING NUMBER

051-9058

REVISION

6.0.0

BRANCH

PAGE

4 OF 109

SHEET

4 OF 86

124578

Page 5

8 7 6 5 4 3

12

BOM Variants

BOM NUMBER

607-8895

085-3092

607-8721

607-8722

607-8723

D

607-9309

607-9310

607-9311

639-3752

639-3756

639-3753

639-3755

639-3751

639-3754

C

J30 BOM GROUPS

BOM GROUP

J30_COMMON

J30_COMMON1

J30_COMMON2

J30_PROGPARTS

J30_DEVEL:ENG BKLT:ENG,XDP_CONN,XDP_CPU:BPM,XDP_PCH,LPCPLUS_CONN:YES,LOADISNS:YES,DDRVREF_DAC,S0PGOOD_ISL

J30_DEVEL:PVT

J30_DEBUG:ENG

J30_DEBUG:PVT

J30_DEBUG:PROD

Module Parts

PART NUMBER

337S4113

B

337S4264

337S4265

337S4269

343S0534

338S0753

338S1072 CRITICAL

353S3055 CRITICAL

946-3827

516S0806

516-0246 CRITICAL

516S0805 CRITICAL SODIMM:MOLEX

516-0245 SODIMM:MOLEXCRITICAL

516S0805

516-0246

BOM NAME

CMN PTS,PCBA,MLB,J30

J30 MLB DEVELOPMENT BOM

POWER FETS PAIR,FAIRCHILD,DDR,J30

POWER FETS PAIR,FAIRCHILD,5V_S3,J30

POWER FETS PAIR,FAIRCHILD,PBUS_CHARGER,J30

POWER FETS PAIR,RENESAS,DDR,J30

POWER FETS PAIR,RENESAS,5V_S3,J30

POWER FETS PAIR,RENESAS,PBUS_CHARGER,J30

PCBA,MLB,MOL,2.9G,J30

PCBA,MLB,HYB,2.9G,J30

PCBA,MLB,FOX,2.5G,J30

PCBA,MLB,HYB,2.5G,J30

PCBA,MLB,MOL,2.5G,J30

PCBA,MLB,FOX,2.9G,J30

ALTERNATE,COMMON,J30_COMMON1,J30_COMMON2,J30_DEBUG:ENG,J30_PROGPARTS,T29BST:Y,TBTHV:P15V

BATT_3S,CPUMEM_S0,USBHUB2513B,HUB_3NONREM,T29:YES,SDRV_PD,SDRVI2C:MCU,AXG_PHASE1,BTPWR:S4,UV_GLUE_J30

BOOTROM_PROG,SMC_PROG,TPAD_PROG,ENET_PROG,T29ROM:PROG,T29MCU:PROG

DEVEL_BOM,BKLT:PROD,MOJO:YES,XDP,LPCPLUS_R:YES,VREFDQ:M1_M3,VREFCA:LDO,USBHUB2514B

BKLT:PROD,MOJO:YES,XDP,LPCPLUS_R:YES,LOADISNS:NO,VREFDQ:M1_M3,VREFCA:LDO,USBHUB2513B

QTY

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

DESCRIPTION

IC,IVB,2C,35W,1023BGA

IVB,S R0N0,PRQ,L1,2.5,35W,2+2,1.1,3M,BGA

IVB,S R0MU,PRQ,L1,2.9,35W,2+2,1.25,4M,BGA

PANTHERPOINT,C1,SLJ8C,PRQ,BD82HM77

IC,BCM57765B0,ENET&SD,8X8

IC,FW643E,1394B PHY/OHCI LINK/PCI-E,12

IC,T29,PRQ,S LJJY,FCBGA,15x15MM,C1

IC,PI3VEDP212,X2 DISPLAYPORT 2:1 MUX,QFN

J30 MLB DYMAX ADHESIVE 29993-SC 0.48G

CONN,204P,SODIMM,SOCKET,DDR3,RAM,BGA,FOXCONN

CONN,204P,SODIMM,DDR3,P=0.6MM,FOXCONN

CONN,204P,SODIMM,SOCKET,DDR3,RAM,BGA,MOLEX

CONN,204P,SODIMM,DDR3,P=0.6MM,MOLEX

CONN,204P,SODIMM,SOCKET,DDR3,RAM,BGA,MOLEX

CONN,204P,SODIMM,DDR3,P=0.6MM,FOXCONN

BOM OPTIONS

J30_COMMON,FET_PAIR

J30_DEVEL:ENG

DDR_POWER_FET:FAIR

5V_S3_POWER_FET:FAIR

CHARGER_POWER_FET:FAIR

DDR_POWER_FET:REN

5V_S3_POWER_FET:REN

CHARGER_POWER_FET:REN

J30_CMNPTS,CPU_2_9GHZ,SODIMM:MOLEX,EEEE_F1YK

J30_CMNPTS,CPU_2_9GHZ,SODIMM:HYBRID,EEEE_F1YH

J30_CMNPTS,CPU_2_5GHZ,SODIMM:FOXCONN,EEEE_F1YL

J30_CMNPTS,CPU_2_5GHZ,SODIMM:HYBRID,EEEE_F1YJ

J30_CMNPTS,CPU_2_5GHZ,SODIMM:MOLEX,EEEE_F1YM

J30_CMNPTS,CPU_2_9GHZ,SODIMM:FOXCONN,EEEE_F1YG

BOM OPTIONS

MIKEY,TPAD:Z2,RAMCFG_SLOT

LPCPLUS_CONN:YES,XDP_CONN

DEVEL_BOM,MOJO:YES,XDP,LPCPLUS_R:YES,VREFDQ:M1_M3,VREFCA:LDO_DAC

REFERENCE DES

U1000

U1000

U1000

U1800

U3900

U4100

U3600

U9390

UV_GLUE_J30

J3100

J2900

J3100

J2900

J3100

J2900

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

BOM OPTION

CPU_IVB_2C

CPU_2_5GHZ

CPU_2_9GHZ

UV_GLUE_J30

SODIMM:FOXCONN

SODIMM:FOXCONN

SODIMM:HYBRID

SODIMM:HYBRID

T29:YES

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

Bar Code Labels / EEEE #’s

PART NUMBER

826-4393

826-4393

826-4393

826-4393

826-4393

QTY

1

1

1

1

1

1

DESCRIPTION

LBL,P/N LABEL,PCB,28MM X 6 MM

LBL,P/N LABEL,PCB,28MM X 6 MM

LBL,P/N LABEL,PCB,28MM X 6 MM

LBL,P/N LABEL,PCB,28MM X 6 MM

LBL,P/N LABEL,PCB,28MM X 6 MM

LBL,P/N LABEL,PCB,28MM X 6 MM

REFERENCE DES

[EEEE:F1YG]

[EEEE:F1YH]

[EEEE:F1YJ]

[EEEE:F1YK]

[EEEE:F1YL]

[EEEE:F1YM]

Programmable Parts

PART NUMBER

335S0862

341S3096

335S0550

341S3430

337S3997 CRITICAL

341S3365 CRITICAL

338S1098

341S3300 CRITICAL

335S0807

335S0812

341S3558

341S2384

341S3522

QTY

1

1

1

1

1

1

1

1

1

1

1

1

1

DESCRIPTION

IC,FLASH,SERIAL,SPI,!MBIT,2V7,REV F

IC ENET,1!MBITFLAH,CIV REV01,K9x

IC,EEPROM,SERIAL,SPI,4Kx8,1.8V,MLP8,LF

IC,T29 EEPROM,LR,J30/J31

IC,MCU,32B,LPC1112A,16KB/2KB,HVQFN25

IC,PROGRMD,T29,PORT MCU,K90IA,K91A,K92A

IC,SMC12-A3,40MHZ/50DMIPS MCU,9x9,157BGA

IC,SMC,EXTERNAL,FSB,A3,J30

IC,SPI SRL 50MHZ FLASH,64MBT,8SOP,FUSE=1

64 MBIT SPI SRL DUAL I/O FLSH,SOIC8

IC,EFI,V00C7,J30/J31

IR,ENCORE II, CY7C63803-LQXC

IC,PSOC,TP/KB,J30/J31

Alternate Parts

PART NUMBER

138S0603

128S0303 128S0353 138S0648

138S0676 138S0691

152S0778

376S0855

376S0977 376S0859

376S0972

376S0777

376S0953

377S0107

371S0709

607-9310

607-9311

ALTERNATE FOR

PART NUMBER

138S0602

157S0084

152S0693

376S1032

376S1017

376S0845376S0937

376S0761

376S0958376S0957

376S0958

377S0126

371S0652

514-0671514-0788

607-8722

607-8723

BOM OPTION

REF DES

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

COMMENTS:

Murata alt to Samsung

Delta alt to TDK Magnetics157S0058

Panasonic alt to Sanyo

Murata alt to Samsung

Cyntec alt to Vishay

Diodes alt to Toshiba

Diodes alt to Toshiba

Rohm alt to Toshiba

Fairchild alt to Renesas

AON alt to Siliconix

Fairchild alt to Fairchild

Fairchild alt to Renesas

ONsemi alt to Semtech

NXP alt to Infineon

Acon(w liteon) alt to Acon

Renesas alternate to fairchild

Renesas alternate to fairchild

REFERENCE DES

U3990

U3990

U3690

U3690

U9330

U9330

U4900

U4900

U6100

U6100

U6100

U4800

U5701

TABLE_ALT_HEAD

PART NUMBER

TABLE_ALT_ITEM

152S1499

TABLE_ALT_ITEM

152S1493

TABLE_ALT_ITEM TABLE_ALT_ITEM

138S0652

TABLE_ALT_ITEM

TABLE_ALT_ITEM

152S1512

TABLE_ALT_ITEM

152S1019

TABLE_ALT_ITEM

376S1023 376S0960

TABLE_ALT_ITEM

353S3312

TABLE_ALT_ITEM

353S3238

TABLE_ALT_ITEM

353S3519

TABLE_ALT_ITEM

TABLE_ALT_ITEM

138S0681

TABLE_ALT_ITEM

138S0671

TABLE_ALT_ITEM

TABLE_ALT_ITEM

377S0124

TABLE_ALT_ITEM

341S3492

TABLE_ALT_ITEM

376S1053

376S1076

CRITICAL

CRITICAL826-4393

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

ALTERNATE FOR

PART NUMBER

152S0864

152S1300

138S0660138S0684

152S1295

152S1271

353S3055

353S1428

353S2179

155S0367155S0578

138S0638

138S0673

376S0796376S0903

377S0057

341S3096

376S0604

376S0634

BOM OPTION

EEEE_F1YG

EEEE_F1YH

EEEE_F1YJ

EEEE_F1YK

EEEE_F1YL

EEEE_F1YM

BOM OPTION

ENET_BLANK

ENET_PROG

T29ROM:BLANK

T29ROM:PROG

T29MCU:BLANK

T29MCU:PROG

SMC_BLANK

BOOTROM_BLANK

BOOTROM_BLANK

BOOTROM_PROG

TPAD_PROG

BOM OPTION

SMC_PROG

REF DES

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

ALL

COMMENTS:

Coilcraft alt to Murata

Coilcraft alt to Murata

Samsung/Murata alt to Taiyo

Murata alt to Taiyo

Cyntec alt to NEC

Cyntec alt to TOKO

Siliconix alt to Renesas

NXP alt to Pericom

Intersil alt to TI

Intersil alt to TI

Taiyo alt to Murata

Taiyo alt to Samsung

Taiyo alt to Murata

Fairchidl alt to Vishay

Amotech alt to Tdk

Numonix alt to Atmel (ENET ROM)

Diodes alt to fairchild

Diodes alt to onsemi

D

C

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

B

Sub BOM

A

PART NUMBER

607-8895

607-8721

607-8722

607-8723 CSET3 CRITICAL

QTY

1

1

1

1

1

DESCRIPTION

J30 MLB DEVELOPMENT

CMN PTS,PCBA,MLB,J30

POWER_FETS PAIR,FAIRCHILD,DDR,J30

POWER_FETS PAIR,FAIRCHILD,5V_S3,J30

POWER_FETS PAIR,FAIRCHILD,PBUS_CHARGER,J30

6 3

REFERENCE DES

DEVEL

CMNPTS

CSET2 CRITICAL

CRITICAL

CRITICAL085-3092

CRITICAL

CRITICAL

BOM OPTION

DEVEL_BOM

J30_CMNPTS

FET_PAIRCSET1

FET_PAIR

FET_PAIR

PAGE TITLE

BOM Configuration

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=02/15/2011SYNC_MASTER=K90I_MLB

DRAWING NUMBER

051-9058

REVISION

6.0.0

BRANCH

PAGE

5 OF 109

SHEET

5 OF 86

124578

SIZE

A

D

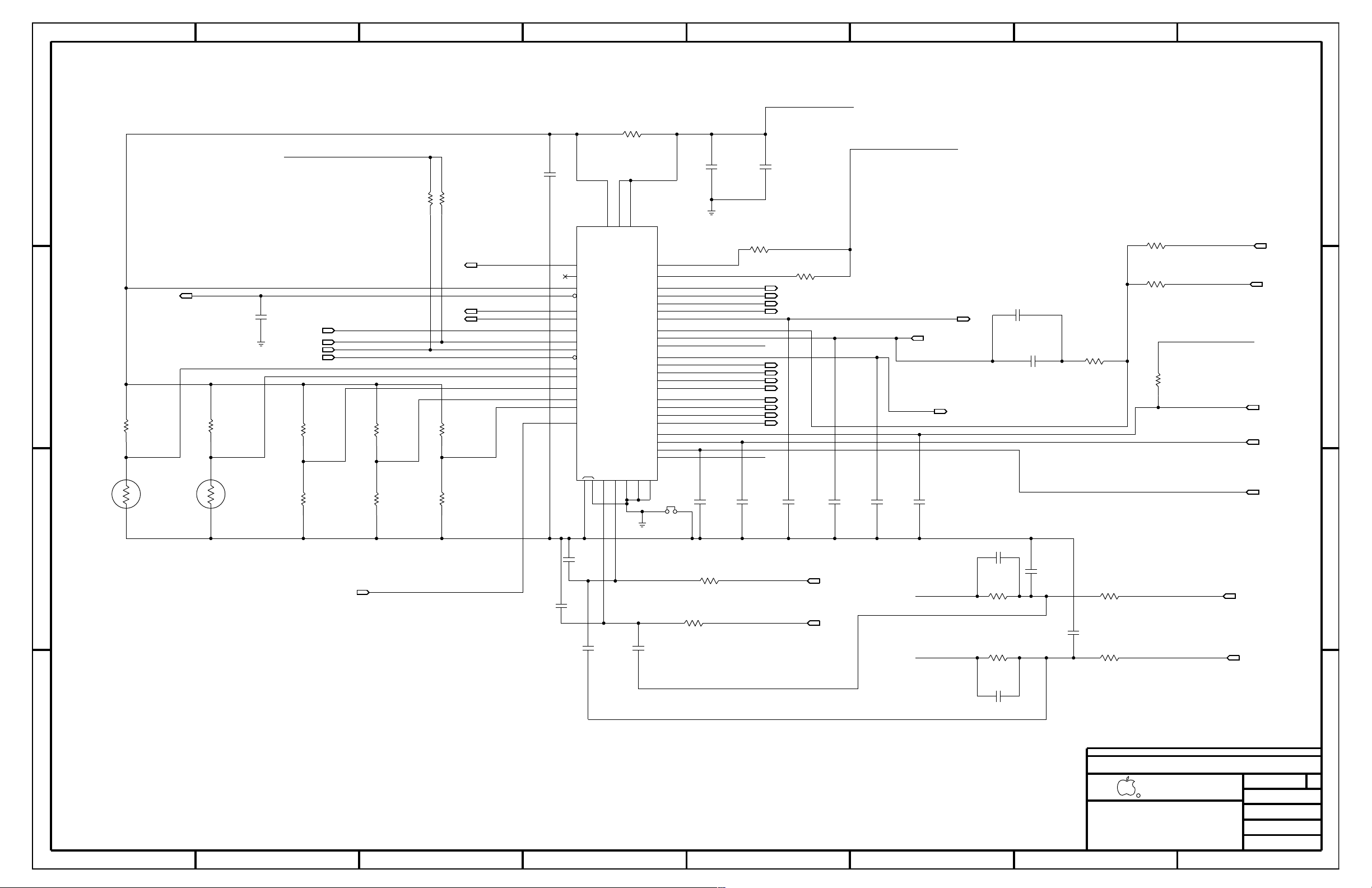

Page 6

8 7 6 5 4 3

12

NC_EDP_TXP<0..3>

Functional Test Points

NC NO_TESTs

Fan Connectors

I12

I15

I16

D

I554

I553

I555

TRUE

TRUE

TRUE

MIC FUNC_TEST

TRUE

TRUE

TRUE

PP5V_S0

FAN_RT_PWM

FAN_RT_TACH

(NEED TO ADD 1 GND TP)

BI_MIC_LO

BI_MIC_HI

BI_MIC_SHIELD

(NEED TO ADD 1 GND TP)

6 7

52

52

61 62

61 62

61 62

SPEAKER FUNC_TEST

I227

I226

I228

I230

I229

I231

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

SPKRAMP_L_N_OUT

SPKRAMP_L_P_OUT

SPKRAMP_R_N_OUT

SPKRAMP_R_P_OUT

SPKRAMP_SUB_N_OUT

SPKRAMP_SUB_P_OUT

60 61 85

60 61 85

60 61 85

60 61 85

60 61 85

60 61 85

LVDS FUNC_TEST

I259

I258

I260

I407

C

I262

I261

I256

I257

I255

I252

I253

I254

I250

I251

I313

I246

I247

I248

I249

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

PP3V3_LCDVDD_SW_F

PP3V3_S0_LCD_F

PPVOUT_SW_LCDBKLT

LVDS_DDC_CLK

LVDS_DDC_DATA

LVDS_IG_A_DATA_N<0>

LVDS_IG_A_DATA_P<0>

LVDS_IG_A_DATA_N<1>

LVDS_IG_A_DATA_P<1>

LVDS_IG_A_DATA_N<2>

LVDS_IG_A_DATA_P<2>

LVDS_CONN_A_CLK_F_N

LVDS_CONN_A_CLK_F_P

LED_RETURN_1

LED_RETURN_2

LED_RETURN_3

LED_RETURN_4

LED_RETURN_5

LED_RETURN_6

(NEED TO ADD 5 GND TP)

(NEED 2 TP)

(NEED 2 TP)

6

74

6

74

74 77

8

74

8

74

17 74 80

17 74 80

17 74 80

17 74 80

17 74 80

17 74 80

74 85

74 85

74 77

74 77

74 77

74 77

74 77

74 77

SATA ODD CONN

I264

I268

I269

I267

B

I265

I266

I628

I627

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

PP5V_SW_ODD

SMC_ODD_DETECT

SATA_ODD_D2R_C_P

SATA_ODD_D2R_C_N

SATA_ODD_R2D_P

SATA_ODD_R2D_N

SMC_SSD_TEMP_CTL_R

HDD_OOB_TEMP

(NEED TO ADD 3 GND TP)

(NEED 2 TP)

41 45

41 85

41 85

41 80

41 80

6

41

SATA HDD/IR/SIL

I319

I314

I315

I318

I317

I307

I309

I625

I311

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

PP5V_S0_HDD_FLT

SATA_HDD_R2D_P

SATA_HDD_R2D_N

SATA_HDD_D2R_C_P

SATA_HDD_D2R_C_N

SYS_LED_ANODE_R

IR_RX_OUT

SMC_SSD_THROTTLE_R

PP5V_S3_IR_R

(NEED TO ADD 3 GND TP)

(NEED 2 TP)

41 80

41 80

41 80

41 80

41

41 44

41

6

41

BATT POWER CONN

I322

I321

I320

A

I305

TRUE

TRUE

TRUE

TRUE

SMBUS_SMC_5_G3_SCL

SMBUS_SMC_5_G3_SDA

SYS_DETECT_L

PPVBAT_G3H_CONN

(NEED TO ADD 5 GND TP)

(NEED 5 TP)

6

45 48 84

6

45 48 84

63

63 64

BIL CONN

I326

I323

I324

I325

I308

TRUE

TRUE

TRUE

TRUE

TRUE

PP3V42_G3H

SMBUS_SMC_5_G3_SCL

SMBUS_SMC_5_G3_SDA

SMC_BIL_BUTTON_L

SMC_LID_R

(NEED TO ADD 2 GND TP)

6 7

6

45 48 84

6

45 48 84

45 46 63

63

I303

I301

I302

I300

I299

I298

I293

I288

I292

I295

I290

I271

I289

I595

I594

I593

I375

I374

I372

I370

I371

I369

I368

I361

I366

I365

I363

I364

I362

I360

I359

I357

I358

I377

I564

I626

I354

I355

I344

I345

I346

I347

I349

I348

I350

I352

I351

I353

I327

I328

I329

I343

I342

I341

I339

I340

I338

I336

I337

I333

I335

I334

I332

I330

I331

I356

I394

I408

I409

I410

I297

I294

X19 CONN

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

PP3V3_WLAN

PCIE_AP_D2R_PI_P

PCIE_AP_D2R_PI_N

PCIE_AP_R2D_P

PCIE_AP_R2D_N

PCIE_CLK100M_AP_CONN_P

PCIE_CLK100M_AP_CONN_N

PP3V3_S3RS4_BT_F

PCIE_WAKE_L

USB_BT_CONN_P

USB_BT_CONN_N

AP_CLKREQ_Q_L

AP_RESET_CONN_L

AP_TEMP_SMB_SDA_R

AP_TEMP_SMB_SCL_R

WIFI_EVENT_L_R

(NEED TO ADD 5 GND TP)

IPD_FLEX_CONN

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

PP3V3_S4

PP18V5_Z2

Z2_CS_L

Z2_DEBUG3

Z2_MOSI

Z2_MISO

Z2_SCLK

Z2_BOOST_EN

Z2_HOST_INTN

Z2_CLKIN

Z2_KEY_ACT_L

Z2_RESET

PSOC_MISO

PSOC_MOSI

PSOC_SCLK

SMBUS_SMC_2_S3_SCL

SMBUS_SMC_2_S3_SDA

PSOC_F_CS_L

PICKB_L

PP5V_S5_CUMULUS

(NEED TO ADD 2 GND TP)

KEYBOARD CONN

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

PP3V3_S4

PP3V42_G3H

WS_KBD1

WS_KBD2

WS_KBD3

WS_KBD4

WS_KBD5

WS_KBD6

WS_KBD7

WS_KBD8

WS_KBD9

WS_KBD10

WS_KBD11

WS_KBD12

WS_KBD13

WS_KBD14

WS_KBD15_CAP

WS_KBD16_NUM

WS_KBD17

WS_KBD18

WS_KBD19

WS_KBD20

WS_KBD21

WS_KBD22

WS_KBD23

WS_KBD_ONOFF_L

WS_LEFT_SHIFT_KBD

WS_LEFT_OPTION_KBD

WS_CONTROL_KBD

KBD BACKLIGHT CONN

TRUE

TRUE

KBDLED_ANODE

SMC_KDBLED_PRESENT_L

CAMERA/ALS CONN

TRUE

TRUE

TRUE

TRUE

TRUE

PP5V_S3_ALSCAMERA_F

SMBUS_SMC_2_S3_SCL

SMBUS_SMC_2_S3_SDA

USB_CAMERA_CONN_P

USB_CAMERA_CONN_N

(NEED 3 TP)

(NEED TO ADD 2 GND TP)

(NEED TO ADD 1 GND TP)

(NEED TO ADD 2 GND TP)

6

32 46

32 81

32 81

32 81

32 81

32 85

32 85

32

17 24 32

32 80

32 80

32

32

32

32

32

6 7

6

54

53 54

53 54

53 54

53 54

53 54

54

53 54

53 54

53 54

53 54

53 54

53 54

53 54

6

45 48 84

6

45 48 84

53 54

53 54

54

6 7

6 7

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

54

54

32

6

45 48 84

6

45 48 84

32 80

32 80

I287

I285

I414

I280

I281

I282

I283

I376

I278

I270

I416

I273

I274

I275

I417

I392

I391

I390

I388

I418

I386

I383

I419

I382

I565

I380

I598

I597

I596

I599

I600

I601

I602

I603

I604

I605

I606

I607

I608

I610

I611

I612

I614

I613

I617

I616

I618

I620

I619

I622

DEBUG VOLTAGE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

DC POWER CONN

I312

I304

TRUE

TRUE

PPVCORE_S0_CPU

PPVCORE_S0_AXG

PP1V2_S3_ENET_INTREG

PP1V05_S0

PP1V5_S3RS0

PP1V8_S0

PP3V3_S0

PP5V_S0

PP3V3_S3

PP5V_S3

PPVCCSA_S0_CPU

PP3V3_S5

PP3V42_G3H

PPBUS_G3H

PP3V3_ENET

PP3V3_WLAN

PP5V_SW_ODD

PP5V_S0_HDD_FLT

PP18V5_Z2

PP3V3_S0_LCD_F

PP3V3_LCDVDD_SW_F

PP4V5_AUDIO_ANALOG

PP1V5_S3

SMC_PM_G2_EN

PM_SLP_S4_L

PM_SLP_S3_L

(NEED TO ADD 6 GND TP)

(NEED 3 TP)

PP18V5_DCIN_FUSE

ADAPTER_SENSE

(NEED TO ADD 4 GND TP)

7

7

71

7

7

85

7

7

85

6 7

7

7

7

16

7

85

16

6 7

16

7

7

6

32 46

6

41

6

41

6

54

6

74

6

74

57 62

7

45 73

17 26 32 45 73

8

17 26 45 73

63

63

18

18

LPC+SPI DEBUG_CONN

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

LPC_AD<0>

LPC_AD<1>

LPC_AD<2>

LPC_AD<3>

LPC_CLK33M_LPCPLUS

LPC_FRAME_L

LPC_PWRDWN_L

LPC_SERIRQ

LPCPLUS_GPIO

LPCPLUS_RESET_L

PM_CLKRUN_L

PP3V42_G3H

PP5V_S0

SMC_RX_L

SMC_TCK

SMC_TDI

SMC_TDO

SMC_TMS

SMC_TX_L

SPI_ALT_CLK

SPI_ALT_CS_L

SPI_ALT_MISO

SPI_ALT_MOSI

SPIROM_USE_MLB

(NEED TO ADD 2 GND TP)

16 45 47 81

16 45 47 81

16 45 47 81

16 45 47 81

24 47 81

16 45 47 81

17 45 47

16 45 47

19 47

24 47

17 45 47

6 7

6 7

45 46 47

45 46 47

45 46 47

45 46 47

45 46 47

45 46 47

47

47

47

47

19 47 56

TP_SDVO_TVCLKINN

17

TP_SDVO_TVCLKINP

17

TP_SDVO_STALLN

17

TP_SDVO_STALLP

17

TP_SDVO_INTN

17

TP_SDVO_INTP

17

NO_TEST

TP_CRT_IG_BLUE

17

TP_CRT_IG_GREEN

17

TP_CRT_IG_RED

17

TP_CRT_IG_DDC_CLK

17

TP_CRT_IG_DDC_DATA

17

TP_CRT_IG_HSYNC

17

TP_CRT_IG_VSYNC

17

TP_LVDS_IG_CTRL_CLK

17

TP_LVDS_IG_CTRL_DATA

17

TP_PCH_LVDS_VBG

17

TP_HDA_SDIN2

TP_HDA_SDIN3

TP_PCI_PME_L

TP_PCI_CLK33M_OUT3

TP_CLINK_CLK

16

TP_CLINK_DATA

16

TP_CLINK_RESET_L

16

TP_PCIE_CLK100M_PEBN

16

TP_PCIE_CLK100M_PEBP

16

TP_FW643_SDA

38

TP_FW643_SM

38

TP_FW643_TCK

38

TP_FW643_TMS

38

TP_FW643_FW620_L

38

TP_FW643_VBUF

38

TP_FW643_OCR10_CTL

38

TP_FW643_AVREG

38

TP_FW643_TDI

38

TP_XDP_PCH_OBSFN_A<0..1>

23

TP_XDP_PCH_OBSFN_B<0..1>

23

TP_XDPPCH_HOOK2

23

TP_XDPPCH_HOOK3

23

TP_XDP_PCH_OBSFN_D<0..1>

23

TP_XDP_PCH_HOOK4

23

TP_XDP_PCH_HOOK5

23

TP_PCH_GPIO64_CLKOUTFLEX0

16

TP_PCH_GPIO65_CLKOUTFLEX1

16

TP_PCH_GPIO66_CLKOUTFLEX2

16

TP_PCH_GPIO67_CLKOUTFLEX3

16

I500

I499

I498

I497

I495

I496

I494

I493

I492

I491

I581

I580

I582

I583

I584

I585

I586

I588

I587

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

NO_TEST

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

NC NO_TESTs

NC_FW2_TPBP

NC_FW2_TPBN

NC_FW2_TPBIAS

NC_FW2_TPAP

NC_FW2_TPAN

NC_FW0_TPBP

NC_FW0_TPBN

NC_FW0_TPAP

XDP_PCH_AP_PWR_EN

XDP_PCH_USB_HUB_SOFT_RST_L

XDP_PCH_SDCONN_STATE_RST_L

XDP_PCH_ENET_PWR_EN

XDP_PCH_SDCONN_DET_L

XDP_PCH_S5_PWRGD

XDP_PCH_PWRBTN_L

XDP_PCH_ISOLATE_CPU_MEM_L

XDP_FW_CLKREQ_L

XDP_AP_CLKREQ_L

XDP_PCH_AUD_IPHS_SWITCH_EN

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

NC_LVDS_IG_CTRL_CLK

TRUE

MAKE_BASE=TRUE

NC_LVDS_IG_CTRL_DATA

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

NC_CRT_IG_BLUE

NC_CRT_IG_GREEN

NC_CRT_IG_RED

NC_CRT_IG_DDC_CLK

NC_CRT_IG_DDC_DATA

NC_CRT_IG_HSYNC

NC_CRT_IG_VSYNC

NC_PCH_LVDS_VBG

NC_HDA_SDIN1TP_HDA_SDIN1

NC_HDA_SDIN2

NC_HDA_SDIN3

NC_PCI_PME_L

NC_PCI_CLK33M_OUT3

NC_CLINK_CLK

NC_CLINK_DATA

NC_CLINK_RESET_L

NC_PCIE_CLK100M_PEBN

NC_PCIE_CLK100M_PEBP

NC_FW643_SDA

NC_FW643_SM

NC_FW643_TCK

NC_FW643_TMS

NC_FW643_FW620_L

NC_FW643_VBUF

NC_FW643_OCR10_CTL

NC_FW643_AVREG

NC_FW643_TDI

NC_TP_XDP_PCH_OBSFN_A<0..1>

NC_TP_XDP_PCH_OBSFN_B<0..1>

NC_TP_XDPPCH_HOOK2

NC_TP_XDPPCH_HOOK3

NC_TP_XDP_PCH_OBSFN_D<0..1>

NC_TP_XDP_PCH_HOOK4

NC_TP_XDP_PCH_HOOK5

NC_PCH_GPIO64_CLKOUTFLEX0

NC_PCH_GPIO65_CLKOUTFLEX1

NC_PCH_GPIO66_CLKOUTFLEX2

NC_PCH_GPIO67_CLKOUTFLEX3

40

40

40

40

40

40

40

40

23

23

NC_SDVO_TVCLKINN

NC_SDVO_TVCLKINP

NC_SDVO_STALLN

NC_SDVO_STALLP

NC_SDVO_INTN

NC_SDVO_INTP

MAKE_BASE=TRUE

NC_EDP_TXN<0..3>

MAKE_BASE=TRUE

NC_EDP_AUXP

MAKE_BASE=TRUE

NC_EDP_AUXN

MAKE_BASE=TRUE

NC_CPU_THERMDA

MAKE_BASE=TRUE

NC_CPU_THERMDC

MAKE_BASE=TRUE

NC_CPU_RSVD<30..45>

MAKE_BASE=TRUE

NC_CPU_RSVD<8..27>

MAKE_BASE=TRUE

NC_PEG_R2D_CP<0..7>

MAKE_BASE=TRUE

NC_PEG_R2D_CN<0..7>

MAKE_BASE=TRUE

NC_PEG_D2RP<0..7>

MAKE_BASE=TRUE

NC_PEG_D2RN<0..7>

MAKE_BASE=TRUE

NC_PEG_R2D_CP<8..11>

MAKE_BASE=TRUE

NC_PEG_R2D_CN<8..11>

MAKE_BASE=TRUE

NC_PEG_D2RP<8..11>

MAKE_BASE=TRUE

NC_PEG_D2RN<8..11>

MAKE_BASE=TRUE

TP_PCIE_CLK100M_PE4N

16

TP_PCIE_CLK100M_PE4P

16

TP_PCIE_CLK100M_PE5N

16

TP_PCIE_CLK100M_PE5P

16

TP_PCIE_CLK100M_PE6N

TP_PCIE_CLK100M_PE6P

TP_PCIE_CLK100M_PE7N

TP_PCIE_CLK100M_PE7P

TP_PSOC_P1_3

53

TP_SATA_C_D2RN

16

TP_SATA_C_D2RP

16

TP_SATA_C_R2D_CN

16

TP_SATA_C_R2D_CP

16

TP_SATA_D_D2RN

16

TP_SATA_D_D2RP

16

TP_SATA_D_R2D_CN

16

TP_SATA_D_R2D_CP

16

TP_SATA_E_D2RN

16

TP_SATA_E_D2RP

16

TP_SATA_E_R2D_CN

16

TP_SATA_E_R2D_CP

16

TP_SATA_F_D2RN

16

TP_SATA_F_D2RP

16

TP_SATA_F_R2D_CN

16

TP_SATA_F_R2D_CP

16

TP_TBT_MONDC0

33

TP_TBT_MONDC1

33

TP_TBT_MONOBSP

33

TP_TBT_MONOBSN

33

TP_DP_T29SRC_ML_CP<0..3>

33

TP_DP_T29SRC_ML_CN<0..3>

33

TP_DP_T29SRC_AUXCH_CP

33

TP_DP_T29SRC_AUXCH_CN

33

TP_T29_PCIE_RESET0_L

6

33

TP_T29_PCIE_RESET1_L

6

33

TP_T29_PCIE_RESET2_L

6

33

TP_T29_PCIE_RESET3_L

6

33

PCH_VSS_NCTF<1>

TRUE

I522

I521

I520

I519

I518

I517

PCH_VSS_NCTF<2>

TRUE

PCH_VSS_NCTF<5>

TRUE

PCH_VSS_NCTF<9>

TRUE

PCH_VSS_NCTF<11>

TRUE

PCH_VSS_NCTF<12>

TRUE

TP_LVDS_IG_B_CLKN

8

TP_LVDS_IG_B_CLKP

8

TP_LVDS_IG_BKL_PWM

SMC_BS_ALRT_L

SYNC_MASTER=K90I_MLB

PAGE TITLE

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

TRUE

Apple Inc.

R

6 3

TP_EDP_TX_P<0..3>

TP_EDP_TX_N<0..3>

TP_EDP_AUX_P

TP_EDP_AUX_N

TP_CPU_THERMDA

TP_CPU_THERMDC

TP_CPU_RSVD<30..45>

TP_CPU_RSVD<8..27>

=PEG_R2D_C_P<0..7>

=PEG_R2D_C_N<0..7>

=PEG_D2R_P<0..7>

=PEG_D2R_N<0..7>

=PEG_R2D_C_P<8..11>

=PEG_R2D_C_N<8..11>

=PEG_D2R_P<8..11>

=PEG_D2R_N<8..11>

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

I547

81

I546

81

I545

81

I544

I543

81

I542

81

I541

81

I540

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

FUNC TEST

NC_PCIE_CLK100M_PE4N

NC_PCIE_CLK100M_PE4P

NC_PCIE_CLK100M_PE5N

NC_PCIE_CLK100M_PE5P

NC_PCIE_CLK100M_PE6N

NC_PCIE_CLK100M_PE6P

NC_PCIE_CLK100M_PE7N

NC_PCIE_CLK100M_PE7P

NC_PSOC_P1_3

NC_SATA_C_D2RN

NC_SATA_C_D2RP

NC_SATA_C_R2D_CN

NC_SATA_C_R2D_CP

NC_SATA_D_D2RN

NC_SATA_D_D2RP

NC_SATA_D_R2D_CN

NC_SATA_D_R2D_CP

NC_SATA_E_D2RN

NC_SATA_E_D2RP

NC_SATA_E_R2D_CN

NC_SATA_E_R2D_CP

NC_SATA_F_D2RN

NC_SATA_F_D2RP

NC_SATA_F_R2D_CN

NC_SATA_F_R2D_CP

NC_TBT_MONDC0

NC_TBT_MONDC1

NC_TBT_MONOBSP

NC_TBT_MONOBSN

NC_DP_T29SRC_ML_CP<0..3>

NC_DP_T29SRC_ML_CN<0..3>

NC_DP_T29SRC_AUXCH_CP

NC_DP_T29SRC_AUXCH_CN

TP_T29_PCIE_RESET0_L

TP_T29_PCIE_RESET1_L

TP_T29_PCIE_RESET2_L

TP_T29_PCIE_RESET3_L

PCH_VSS_NCTF<15>

TRUE

PCH_VSS_NCTF<17>

TRUE

PCH_VSS_NCTF<19>

TRUE

PCH_VSS_NCTF<19>

TRUE

PCH_VSS_NCTF<21>

TRUE

PCH_VSS_NCTF<25>

TRUE

PCH_VSS_NCTF<27>

TRUE

PCH_VSS_NCTF<29>

TRUE

NC_LVDS_IG_B_CLKN

NC_LVDS_IG_B_CLKP

NC_LVDS_IG_BKL_PWM

NC_SMC_BS_ALRT_L

DRAWING NUMBER

051-9058

REVISION

6.0.0

BRANCH

PAGE

7 OF 109

SHEET

6 OF 86

124578

9

9

9

9

D

9

9

9

9

9

9

9

9

C

6

33

6

33

B

6

33

6

33

81

81

6

81

6

81

81

81

81

81

A

SIZE

D

Page 7

8 7 6 5 4 3

=PPBUS_G3H

63 64

PPVIN_SW_T29BST

35

VOLTAGE=12.8V

=PPVIN_S5_HS_COMPUTING_ISNS

50

D

=PPVIN_S5_HS_OTHER_ISNS

50

=PP18V5_DCIN_CONN

63

=PP3V42_G3H_REG

63

C

=PPVRTC_G3_OUT

24

=PP5V_S5_LDO

66

=PP5V_SUS_FET

72

B

=PP5V_S3_REG

66

=PP5V_S0_FET

72

A

=PP5V_S0_HDD_ISNS

49

"G3Hot" (Always-Present) Rails

PPBUS_G3H

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.25 mm

VOLTAGE=12.8V

MAKE_BASE=TRUE

=PPBUS_S0_LCDBKLT

=PPBUS_S5_FWPWRSW

=PPBUS_S0_VSENSE

=PPVIN_SW_T29BST

=PPVIN_S5_HS_COMPUTING_ISNS_R

=PPVIN_S5_HS_OTHER_ISNS_R

PPBUS_S5_HS_COMPUTING_ISNS

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.25 mm

VOLTAGE=12.8V

MAKE_BASE=TRUE

=PPVIN_S0_CPUIMVP

=PPVIN_S3_DDRREG

=PPVIN_S0_CPUVCCIOS0

=PPVIN_S0_VCCSAS0

=PPVIN_S0_CPUAXG

PPBUS_S5_HS_OTHER_ISNS

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=12.8V

MAKE_BASE=TRUE

=PPVIN_S5_5VS3

=PPVIN_S5_3V3S5

PPDCIN_G3H

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.25 MM

VOLTAGE=18.5V

MAKE_BASE=TRUE

=PPDCIN_S5_CHGR

=PPDCIN_S5_VSENSE

PP3V42_G3H

MIN_LINE_WIDTH=0.3 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=3.42V

MAKE_BASE=TRUE

=PP3V3_S5_LPCPLUS

=PP3V3_S5_SMC

=PP3V42_G3H_BATT

=PP3V42_G3H_CHGR

=PP3V42_G3H_ONEWIREPROT

=PP3V42_G3H_PWRCTL

=PP3V42_G3H_SMBUS_SMC_BSA

=PP3V42_G3H_SMCUSBMUX

=PP3V42_G3H_TPAD

=PPVIN_S5_SMCVREF

=PPVBAT_G3_SYSCLK

=PP3V42_G3H_AUDIO

PPVRTC_G3H

MIN_LINE_WIDTH=0.2 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=3V

MAKE_BASE=TRUE

=PPVRTC_G3_PCH

5V Rails

PP5V_S5

MIN_LINE_WIDTH=0.5 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=5V

MAKE_BASE=TRUE

=PP5V_S5_P1V5DDRFET

=PP5V_S5_TPAD

=PP5V_S5_P5VSUSFET

PP5V_SUS

MIN_LINE_WIDTH=0.50MM

MIN_NECK_WIDTH=0.20MM

VOLTAGE=3.3V

MAKE_BASE=TRUE

=PP5V_SUS_PCH

PP5V_S3

MIN_LINE_WIDTH=0.5 mm

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=5V

MAKE_BASE=TRUE

=PP5V_S3_ALSCAMERA

=PP5V_S3_AUDIO

=PP5V_S3_AUDIO_AMP

=PP5V_S3_DDRREG

=PP5V_S3_IR

=PP5V_S3_MEMRESET

=PP5V_S3_ODD

=PP5V_S3_P5VS0FET

=PP5V_S3_USB

=PP5V_S3_SYSLED

PP5V_S0

MIN_LINE_WIDTH=0.4 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=5V

MAKE_BASE=TRUE

=PP5V_S0_BKL

=PP5V_S0_CPUIMVP

=PP5V_S0_CPUVCCIOS0

=PP5V_S0_FAN_RT

=PP5V_S0_HDD_ISNS_R

=PP5V_S0_KBDLED

=PP5V_S0_LPCPLUS

=PP5V_S0_VCCSAS0

=PP5V_S0_PCH

=PP5V_S0_VMON

=PP5V_S0_ISNS

=PP5V_S0_AUDIO

PP5V_S0_HDD

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.4MM

VOLTAGE=5V

MAKE_BASE=TRUE

=PP5V_S0_HDD

=PP3V3_S5_REG

66

6

77

39

50

8

35

50 39

50

68 69

67

70

65

69

=PP3V3_SUS_FET

72

66

66

64

50

6

=PP3V3_S4_FET

72

47

45 46

63

64

63

73

48

42

53

46

24

58

16 17 20

72

54

72

22

6

32

57

60

67

41 44

26

41

72

42

46

6

77

68 69

70

52

49

54

47

65

22 24

73

49

41

=PP3V3_S3_FET

72

=PP3V3_S0_FET

72

3.3V Rails

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.2 MM

MIN_LINE_WIDTH=0.50MM

MIN_NECK_WIDTH=0.20MM

MIN_LINE_WIDTH=0.50MM

MIN_NECK_WIDTH=0.20MM

MIN_LINE_WIDTH=0.50MM

MIN_NECK_WIDTH=0.20MM

=PP3V3_S3_USB_HUB

=PP3V3_S0_KBDLED

=PP3V3_S0_VMON

PP3V3_S5

=PP3V3_S5_XDP

=PP3V3_S0_P3V3S0FET

=PP3V3_S3_P3V3S3FET

=PP3V3_S5_CPU_VCCDDR

=PP3V3_S4_P3V3S4FET

=PP3V3_S5_LCD

=PP3V3_S5_PCH

=PP3V3_S5_PCHPWRGD

=PP3V3_S5_SMCBATLOW

=PP3V3_S5_PCH_VCCDSW

=PP3V3_S5_SYSCLK

=PP3V3_S5_VMON

=PP3V3_S5_PWRCTL

=PP3V3_S5_P3V3SUSFET

=PP3V3_S4_TBTAPWRSW

=PP3V3_S5_PCH_GPIO

PP3V3_SUS

=PP3V3_SUS_PCH_VCCSUS_USB

=PP3V3_SUS_PCH_VCCSUS_GPIO

=PP3V3_SUS_PCH_VCCSUS

=PP3V3_SUS_PCH_GPIO

=PP3V3_SUS_PCH

=PP3V3_SUS_PWRCTL

=PP3V3_SUS_P1V05SUSLDO

=PP3V3_SUS_SMC

=PP3V3_SUS_ROM

=PP3V3_SUS_PCH_VCC_SPI

PP3V3_S4

=PP3V3_S4_TPAD

=PP3V3_S4_SMC

=PP3V3_S4_SD_HPD

=PP3V3_S4_BT

PP3V3_S3

=PP3V3_S3_BT

=PP3V3_S3_MEMRESET

=PP3V3_S3_SMBUS_SMC_A_S3

=PP3V3_S3_SMBUS_SMC_MGMT

=PP3V3_S3_SMS

=PP3V3_S3_USB_RESET

=PP3V3_S3_VREFMRGN

=PP3V3_S3_WLAN

=PP3V3_S3_SDBUF

=PP3V3_S3_P3V3ENETFET

=PP3V3_S3_PCH_GPIO

=PP3V3_S3_ISNS

=PP3V3_S3_USBMUX

PP3V3_S0

MIN_LINE_WIDTH=0.5 MM

MIN_NECK_WIDTH=0.20MM

=PP3V3_S0_HDD

=PP3V3_S0_AUDIO

=PP3V3_S0_BKL_VDDIO

=PP3V3_S0_ISNS

=PP3V3_S0_HS_COMPUTING_ISNS

=PP3V3_S0_CPUTHMSNS

=PP3V3_S0_LCD

=PP3V3_S0_DP_DDC

=PP3V3_S0_ENETPHY

=PP3V3_S0_FAN_RT

=PP3V3_S0_FWPWRCTL

=PP3V3_S0_FWLATEVG

=PP3V3_S0_P3V3T29FET

=PP3V3_S0_SDCARD

=PP3V3_S0_P1V8S0

=PP3V3_S0_ODD

=PP3V3_FW_P3V3FWFET

=PP3V3_S0_PCH

=PP3V3_S0_PCH_GPIO

=PP3V3_S0_PCH_VCC3_3_CLK

=PP3V3_S0_PCH_VCC3_3_GPIO

=PP3V3_S0_PCH_VCC3_3_HVCMOS

=PP3V3_S0_PCH_VCC3_3_PCI

=PP3V3_S0_PCH_VCC3_3_SATA

=PP3V3_S0_PCH_VCCADAC

=PP3V3_S0_PCH_VCCA_LVDS

=PP3V3_S0_PWRCTL

=PP3V3_S0_RSTBUF

=PP3V3_S0_SB_PM

=PP3V3_S0_SMBUS_PCH

=PP3V3_S0_SMBUS_SMC_0_S0

=PP3V3_S0_SMBUS_SMC_B_S0

=PP3V3_S0_SMC

=PPSPD_S0_MEM_A

=PPSPD_S0_MEM_B

=PP3V3_S0_P1V5S0

=PP3V3_S0_T29PWRCTL

=PP3V3_S0_HS_OTHER_ISNS

=PP3V3_S0_DPSDRVA

=PP3V3_S0_P1V05S0LDO

=PP3V3_S0_IMVPISNS

=PP3V3_S0_XDP

=PP3V3_S0_T29I2C

VOLTAGE=3.3V

MAKE_BASE=TRUE

VOLTAGE=3.3V

MAKE_BASE=TRUE

VOLTAGE=3.3V

MAKE_BASE=TRUE

VOLTAGE=3.3V

MAKE_BASE=TRUE

VOLTAGE=3.3V

MAKE_BASE=TRUE

6

85

23

72

72

26

72

74

17

24

46

20 22

24

73

73

72

76

19

20 22

20 22

20

16 17 18 19

22

73

71

46

56

20 22

6

53 54

46

30

32

6

32

26

48

48

55

25

25

31

32

24

73

18 24

49

25

6

85

41

57 61 62

77

49

50

51

74

8

36

52

39

39 40

35

30

71

41

39

16 22

16 17 18 19 30

22

20 22

20 22

20 22

20 22

22

20

73

24

24

48

48

48

41

54

73

27

29

71

35

50

75

71

49

23

48

=PP1V8_S0_REG

71

2A max supply

=PP1V5_S3_DDR_ISNS

49

=PPDDR_S3_REG

67

=PP1V5_S3RS0_FET

72

=PP1V5_S0_REG

71

=PPVTT_S3_DDR_BUF

31 67

=PPVTT_S0_DDR_LDO

67

=PPVCCSA_S0_REG

65

=PP1V05_SUS_LDO

71

=PPCPUVCCIO_S0_REG

70

? mA

=PP3V3_ENET_FET

73

1.8V/1.5V/1.2V/1.05V Rails

PP1V8_S0

MIN_LINE_WIDTH=0.5 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1.8V

MAKE_BASE=TRUE

=PP1V8_S0_CPU_VCCPLL

=PP1V8_S0_PCH_VCCTX_LVDS

=PP1V8_S0_PCH_VCC_DFTERM

=PP1V8_S0_P1V05S0LDO

=PP1V8R1V5_S0_PCH_VCCVRM

=PPVDDIO_S0_SBCLK

PP1V5_S3_DDR

MIN_LINE_WIDTH=0.8 MM

MIN_NECK_WIDTH=0.1 MM

VOLTAGE=1.5V

MAKE_BASE=TRUE

=PP1V5_S3_MEMRESET

=PP1V5_S3_MEM_A

=PP1V5_S3_MEM_B

=PPVIN_S0_DDRREG_LDO

=PPDDR_S3_MEMVREF

PP1V5_S3

MIN_LINE_WIDTH=0.8 MM

MIN_NECK_WIDTH=0.1 MM

VOLTAGE=1.5V

MAKE_BASE=TRUE

=PP1V5_S3_P1V5S3RS0_FET

=PP1V5_S3_DDR_ISNS_R

PP1V5_S3RS0

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1.5V

MAKE_BASE=TRUE

=PP1V5_S3_CPU_VCCDDR

PP1V5_S0

MIN_LINE_WIDTH=2 mm

MIN_NECK_WIDTH=0.17 mm

VOLTAGE=1.5V

MAKE_BASE=TRUE

=PP1V5_S0_RDRVR

=PP1V8R1V5_S0_AUDIO

=PP3V3R1V5_S0_AUDIO

=PP3V3R1V5_S0_PCH_VCCSUSHDA

=PP1V5_S0_VMON

PPVTTDDR_S3

MIN_LINE_WIDTH=0.3 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=0.75V

MAKE_BASE=TRUE

PP0V75_S0_DDRVTT

MIN_LINE_WIDTH=2 mm

MIN_NECK_WIDTH=0.17 mm

VOLTAGE=0.75V

MAKE_BASE=TRUE

=PP0V75_S0_MEM_VTT_A

=PP0V75_S0_MEM_VTT_B

=PPVTT_S0_VTTCLAMP

PPVCCSA_S0_CPU

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=0.9V

MAKE_BASE=TRUE

=PPVCCSA_S0_CPU

PP1V05_SUS

MIN_LINE_WIDTH=0.4 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1.05V

MAKE_BASE=TRUE

=PP1V05_SUS_PCH_JTAG

PP1V05_S0

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1V

MAKE_BASE=TRUE

=PP1V05_S0_CPU_VCCIO

=PPVCCIO_S0_CPUIMVP

=PPVCCIO_S0_XDP

=PPVCCIO_S0_SMC

=PP1V05_S0_FWPWRCTL

=PP1V05_FW_P1V0FWFET

=PP1V05_S0_VMON

XW0800

SM

XW0801

SM

21

21

ENET Rails

=PP1V05_S0_P1V05T29FET

PP1V05_S0_PCH

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1V

MAKE_BASE=TRUE

=PP1V05_S0_PCH_VCCIO_PLLPCIE

=PP1V05_S0_PCH

=PP1V05_S0_PCH_VCCIO

=PP1V05_S0_PCH_VCCIO_PCIE

=PP1V05_S0_PCH_VCCIO_SATA

=PP1V05_S0_PCH_VCCASW

=PP1V05_S0_PCH_VCCIO_USB

=PP1V05_S0_PCH_VCC_CORE

=PP1V05_S0_PCH_VCCIO_CLK

=PP1V05_S0_PCH_VCCDIFFCLK

=PP1V05_S0_PCH_VCCSSC

=PP1V05_S0_PCH_V_PROC_IO

=PP1V05_S0_PCH_VCCIO_PLLUSB

=PP1V05_S0_PCH_VCC_DMI

=PP1V05_S0_PCH_VCCIO_PLLFDI

=PP1V05_S0_PCH_VCCDMI_FDI

PP3V3_ENET

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=3.3V

MAKE_BASE=TRUE

=PP3V3_ENET_PHY

=PP3V3_ENET_SYSCLK

=PPVDDIO_ENET_CLK

6

14

22

19 20 22

71

20

24

26

27

29

67

31

6

72

49

6

85

10 12 15 26

41

57

57

20 22 24

73

27

29

26

6

12 15

23

6

9

10 12 14

68

23

46

39

39

73

35

20

16 22

20 22

17

16 20 22

20 22

20 22

20 22

20 22

16 20 22

20 22

20 22

20

20 22

20

20

6

24 36 71

24

24

=PPBUS_FW_FET

39

=PP3V3_FW_FET

=PP1V0_FW_FET_R

39

=PP15V_T29_REG

8

35

=PP3V3_T29_FET

35

=PP1V05_T29_FET

35

=PP1V05_S0_LDO

71

=PPVCORE_S0_CPU_REG

69

=PPVCORE_S0_AXG_REG

69

=PP1V5_S3_CPU_VCCDQ

12 15

=PP1V05_S0_CPU_VCCPQE

8

12 14

=PP1V8_S0_CPU_VCCPLL_R

12 14

"FW" (FireWire) Rails

PPVP_FW

MIN_LINE_WIDTH=0.4 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=12.8V

MAKE_BASE=TRUE

=PPVP_FW_PORT1

=PPVP_FW_PHY_CPS_FET

PP3V3_FW_FWPHY

MIN_LINE_WIDTH=0.4 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=3.3V

MAKE_BASE=TRUE

=PP3V3_FW_FWPHY

=PP3V3_S0_P1V05FWFET

PP1V0_FW_FWPHY

MIN_LINE_WIDTH=0.4 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1.0V

MAKE_BASE=TRUE

=PP1V0_FW_FWPHY

T29 Rails (off when no cable)

PP15V_T29

MIN_LINE_WIDTH=0.4 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=17.8V

MAKE_BASE=TRUE

=PPHV_SW_TBTAPWRSW

PP3V3_T29

MIN_LINE_WIDTH=0.4 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=3.3V

MAKE_BASE=TRUE

=PPVDDIO_T29_CLK

=PP3V3_T29_RTR

=PP3V3_T29_PCH_GPIO

PP1V05_T29

MIN_LINE_WIDTH=0.4 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1.05V

MAKE_BASE=TRUE

=PP1V05_T29_RTR

1V05 S0 LDO

PP1V05_S0_PCH_VCCADPLL

MIN_LINE_WIDTH=0.4 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1.05V

MAKE_BASE=TRUE

=PP1V05_S0_PCH_VCCADPLL

Chipset "VCore" Rails

SYNC_MASTER=K90I_MLB

PAGE TITLE

PPVCORE_S0_CPU

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.25 MM

VOLTAGE=1.25V

MAKE_BASE=TRUE

=PPVCORE_S0_CPU

=PPCPUVCORE_S0_VSENSE

PPVCORE_S0_AXG

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1.05V

MAKE_BASE=TRUE

=PPVCORE_S0_CPU_VCCAXG

=PPAXGVCORE_S0_VSENSE

PP1V5_S3_CPU_VCCDQ

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1.5V

MAKE_BASE=TRUE

PP1V05_S0_CPU_VCCPQE

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1.05V

MAKE_BASE=TRUE

PP1V8_S0_CPU_VCCPLL_R

MIN_LINE_WIDTH=0.6 MM

MIN_NECK_WIDTH=0.2 MM

VOLTAGE=1.8V

MAKE_BASE=TRUE

Power Aliases

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

6 3

12

40

40

38 39 40

38 39

76

24

33 34 35

16 19

35

34

22

SYNC_DATE=02/15/2011

DRAWING NUMBER

051-9058

REVISION

6.0.0

BRANCH

PAGE

8 OF 109

SHEET

7 OF 86

124578

D

C

6

9

12 14

49

B

6

9

12 15

49

A

SIZE

D

Page 8

8 7 6 5 4 3

CPU signals

HEATSINK STANDOFFS

STDOFF-4.5OD.98H-1.1-3.48-TH

D

STDOFF-4.5OD.98H-1.1-3.48-TH

Z0902

1

Z0904

1

BELOW CPU

Z0920

STDOFF-4.5OD.98H-1.1-3.48-TH

1

LEFT OF CPU

FAN STANDOFF

STDOFF-4.5OD.98H-1.1-3.48-TH

Z0905

1

MLB MOUNTING (TO C. BRACKET) SCREW HOLES

OMIT

Z0906

3R2P5

1

OMIT

Z0907

3R2P5

1

MEMVTT_EN

26

MAKE_BASE=TRUE

DP_EXTA_ML_C_P<3..0>

75 81

MAKE_BASE=TRUE

DP_EXTA_ML_C_N<3..0>

75 81

MAKE_BASE=TRUE

DP_EXTA_AUXCH_C_P

75 81

MAKE_BASE=TRUE

DP_EXTA_AUXCH_C_N

75 81

MAKE_BASE=TRUE

FW_PLUG_DET_L

MAKE_BASE=TRUE

FW643_WAKE_L

39

MAKE_BASE=TRUE

16

16

16

16

16 81

16 81

16 81

16 81

TP_SMC_EXCARD_PWR_EN

MAKE_BASE=TRUE

PCIE_EXCARD_D2R_N

PCIE_EXCARD_D2R_P

PCIE_EXCARD_R2D_C_N

PCIE_EXCARD_R2D_C_P

PCIE_CLK100M_EXCARD_N

PCIE_CLK100M_EXCARD_P

PCIE_PCH_D2R_N<5..8>

PCIE_PCH_D2R_P<5..8>

PCIE_PCH_R2D_C_N<5..8>

PCIE_PCH_R2D_C_P<5..8>

PEG_CLK100M_P

PEG_CLK100M_N

MLB MOUNTING (TO TOPCASE) SCREW HOLES

OMIT

Z0908

3R2P5

C

1

OMIT

Z0911

3R2P5

1

OMIT

Z0909

3R2P5

1

OMIT

Z0912

3R2P5

1

OMIT

Z0910

3R2P5

1

TP_PCH_CLKOUT_DPN

16

TP_PCH_CLKOUT_DPP

16

=DDRVTT_EN

TP_DP_IG_B_MLP<3..0>

TP_DP_IG_B_MLN<3..0>

DPA_IG_AUX_CH_P

DPA_IG_AUX_CH_N

FW_PME_L

=FW_PME_L

SMC_EXCARD_PWR_EN

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

26 67

17

17

17

17

NC_PCIE_EXCARD_D2RN

NC_PCIE_EXCARD_D2RP

NC_PCIE_EXCARD_R2D_CN

NC_PCIE_EXCARD_R2D_CP

NC_PCIE_CLK100M_EXCARDN

TRUE

MAKE_BASE=TRUE

NC_PCIE_CLK100M_EXCARDP

TRUE

MAKE_BASE=TRUE

NC_PCIE_PCH_D2RN<5..8>

NC_PCIE_PCH_D2RP<5..8>

NC_PCIE_PCH_R2D_CN<5..8>

NC_PCIE_PCH_R2D_CP<5..8>

NC_PEG_CLK100MP

NC_PEG_CLK100MN

TRUE

MAKE_BASE=TRUE

TRUE

MAKE_BASE=TRUE

NC_PCH_CLKOUT_DPN

NC_PCH_CLKOUT_DPP

19 39

38 39

17

17

=PEG_R2D_C_P<12..15>

9

=PEG_R2D_C_N<12..15>

9

=PEG_D2R_P<12..15>

9

=PEG_D2R_N<12..15>

9

TP_DP_IG_C_CTRL_CLK

TP_DP_IG_C_CTRL_DATA

TP_DP_IG_D_CTRL_CLK

TP_DP_IG_D_CTRL_DATA

PPBUS_SW_LCDBKLT_PWR

77

MAKE_BASE=TRUE

NC_CPU_VCCIO_SEL

MAKE_BASE=TRUE

DP_EXTA_DDC_CLK

75

MAKE_BASE=TRUE

DP_EXTA_DDC_DATA

MAKE_BASE=TRUE

DP_EXTA_HPD

75

MAKE_BASE=TRUE

7 8

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

=PP3V3_S0_DP_DDC

R0920

2.2K

5%

1/16W

MF-LF

402

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

1

R0908

100K

5%

1/16W

MF-LF

402

2

R0910

1/16W

MF-LF

PCIE_T29_R2D_C_P<3..0>

PCIE_T29_R2D_C_N<3..0>

PCIE_T29_D2R_P<3..0>

PCIE_T29_D2R_N<3..0>

1

2

1

R0921

2.2K

5%

1/16W

MF-LF

402

2

DPB_IG_DDC_CLK

DPB_IG_DDC_DATA

DP_IG_D_CTRL_CLK

DP_IG_D_CTRL_DATA

7 8

DPA_IG_DDC_CLK

DPA_IG_DDC_DATA

DPA_IG_HPD

0

21

5%

402

CPU_VCCIO_SEL

1

R0922

2.2K

1/16W

MF-LF

R0923

5%

402

2

=PP3V3_S0_DP_DDC

1

2.2K

1/16W

MF-LF

R0925

5%

402

2

R0924

PPBUS_SW_BKL

MIN_LINE_WIDTH=0.5 MM

MIN_NECK_WIDTH=0.375 MM

VOLTAGE=12.6V

MAKE_BASE=TRUE

=PPBUS_SW_BKL

2.2K

1/16W

MF-LF

2.2K

1/16W

MF-LF

33 81

33 81

33 81

33 81

1

5%

402

2

17

17

1

5%

402

2

17

17 75

17

77

12 78

DPB_IG_HPD

17

TP_DP_IG_C_MLP<3..0>

17

TP_DP_IG_C_MLN<3..0>

17

DPB_IG_AUX_CH_P

17

DPB_IG_AUX_CH_N

17

TP_DP_IG_D_HPD

17

TP_DP_IG_D_MLP<3..0>

17

TP_DP_IG_D_MLN<3..0>

17

TP_DP_IG_D_AUXP

17

TP_DP_IG_D_AUXN

17

NC_BCM57765_CE_L_MS_INS_L

MAKE_BASE=TRUE

TP_LVDS_IG_B_CLKP

6

MAKE_BASE=TRUE

TP_LVDS_IG_B_CLKN

6

MAKE_BASE=TRUE

NC_LVDS_IG_B_DATAP<0..3>

MAKE_BASE=TRUE

NC_LVDS_IG_B_DATAN<0..3>

MAKE_BASE=TRUE

NC_LVDS_IG_A_DATAP<3>

MAKE_BASE=TRUE

NC_LVDS_IG_A_DATAN<3>

MAKE_BASE=TRUE

LVDS_DDC_CLK

6

74

MAKE_BASE=TRUE

LVDS_DDC_DATA

6

74

MAKE_BASE=TRUE

LCD_BKLT_PWM

77

MAKE_BASE=TRUE

LCD_IG_PWR_EN

74

MAKE_BASE=TRUE

LCD_BKLT_EN

77

MAKE_BASE=TRUE

T29 DP Ports

NO_TEST=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

DP_T29SNK0_HPD

DP_T29SNK0_ML_C_P<3..0>

DP_T29SNK0_ML_C_N<3..0>

DP_T29SNK0_AUXCH_C_P

DP_T29SNK0_AUXCH_C_N

DP_T29SNK1_HPD