2.5 V to 5.5 V, 500 A, 2-Wire Interface

Quad Voltage Output, 8-/10-/12-Bit DACs

FEATURES

AD5305: 4 Buffered 8-Bit DACs in 10-Lead MSOP

A Version: ⴞ1 LSB INL, B Version: ⴞ0.625 LSB INL

AD5315: 4 Buffered 10-Bit DACs in 10-Lead MSOP

A Version: ⴞ4 LSB INL, B Version: ⴞ2.5 LSB INL

AD5325: 4 Buffered 12-Bit DACs in 10-Lead MSOP

A Version: ⴞ16 LSB INL, B Version: ⴞ10 LSB INL

Low Power Operation: 500 A @ 3 V, 600 A @ 5 V

2-Wire (I

2

C® Compatible) Serial Interface

2.5 V to 5.5 V Power Supply

Guaranteed Monotonic by Design over All Codes

Power-Down to 80 nA @ 3 V, 200 nA @ 5 V

Three Power-Down Modes

Double-Buffered Input Logic

Output Range: 0 V to V

REF

Power-On Reset to 0 V

Simultaneous Update of Outputs (LDAC Function)

Software Clear Facility

Data Readback Facility

On-Chip Rail-to-Rail Output Buffer Amplifiers

Temperature Range –40ⴗC to +105ⴗC

APPLICATIONS

Portable Battery-Powered Instruments

Digital Gain and Offset Adjustment

Programmable Voltage and Current Sources

Programmable Attenuators

Industrial Process Control

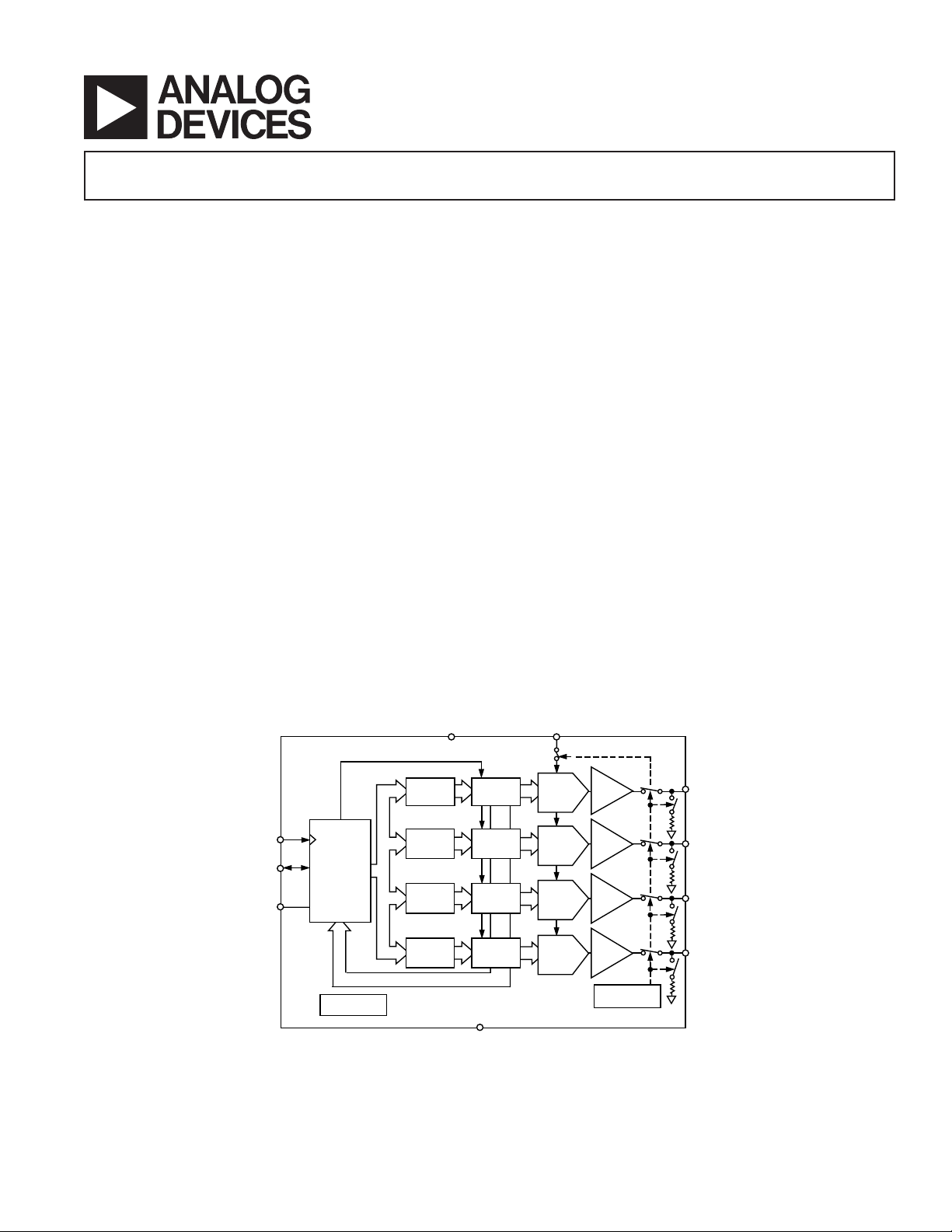

FUNCTIONAL BLOCK DIAGRAM

AD5305/AD5315/AD5325

*

GENERAL DESCRIPTION

The AD5305/AD5315/AD5325 are quad 8-, 10-, and 12-bit

buffered voltage output DACs in a 10-lead MSOP that operate

from a single 2.5 V to 5.5 V supply, consuming 500 µA at 3 V.

Their on-chip output amplifiers allow rail-to-rail output swing

with a slew rate of 0.7 V/µs. A 2-wire serial interface, which

operates at clock rates up to 400 kHz, is used. This interface is

SMBus compatible at V

< 3.6 V. Multiple devices can be

DD

placed on the same bus.

The references for the four DACs are derived from one reference

pin. The outputs of all DACs may be updated simultaneously

using the software LDAC function. The parts incorporate a

power-on reset circuit, which ensures that the DAC outputs power

up to 0 V and remain there until a valid write takes place to the

device. There is also a software clear function that resets all input

and DAC registers to 0 V. The parts contain a power-down

feature that reduces the current consumption of the devices to

200 nA @ 5 V (80 nA @ 3 V).

The low power consumption of these parts in normal operation

makes them ideally suited to portable battery-operated equipment.

The power consumption is 3 mW at 5 V, 1.5 mW at 3 V, reducing

to 1 µW in power-down mode.

V

DD

LDAC

INPUT

REGISTER

SCL

SDA

A0

*Protected by U.S.Patent No. 5,969,657and 5,684,481.

INTERFACE

LOGIC

POWER-ON

RESET

INPUT

REGISTER

INPUT

REGISTER

INPUT

REGISTER

AD5305/AD5315/AD5325

REV. F

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

REF IN

DAC

REGISTER

DAC

REGISTER

DAC

REGISTER

DAC

REGISTER

GND

STRING

DAC A

STRING

DAC B

STRING

DAC C

STRING

DAC D

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

BUFFER

POWER-DOWN

LOGIC

A

V

OUT

BBUFFER

V

OUT

V

CBUFFER

OUT

V

DBUFFER

OUT

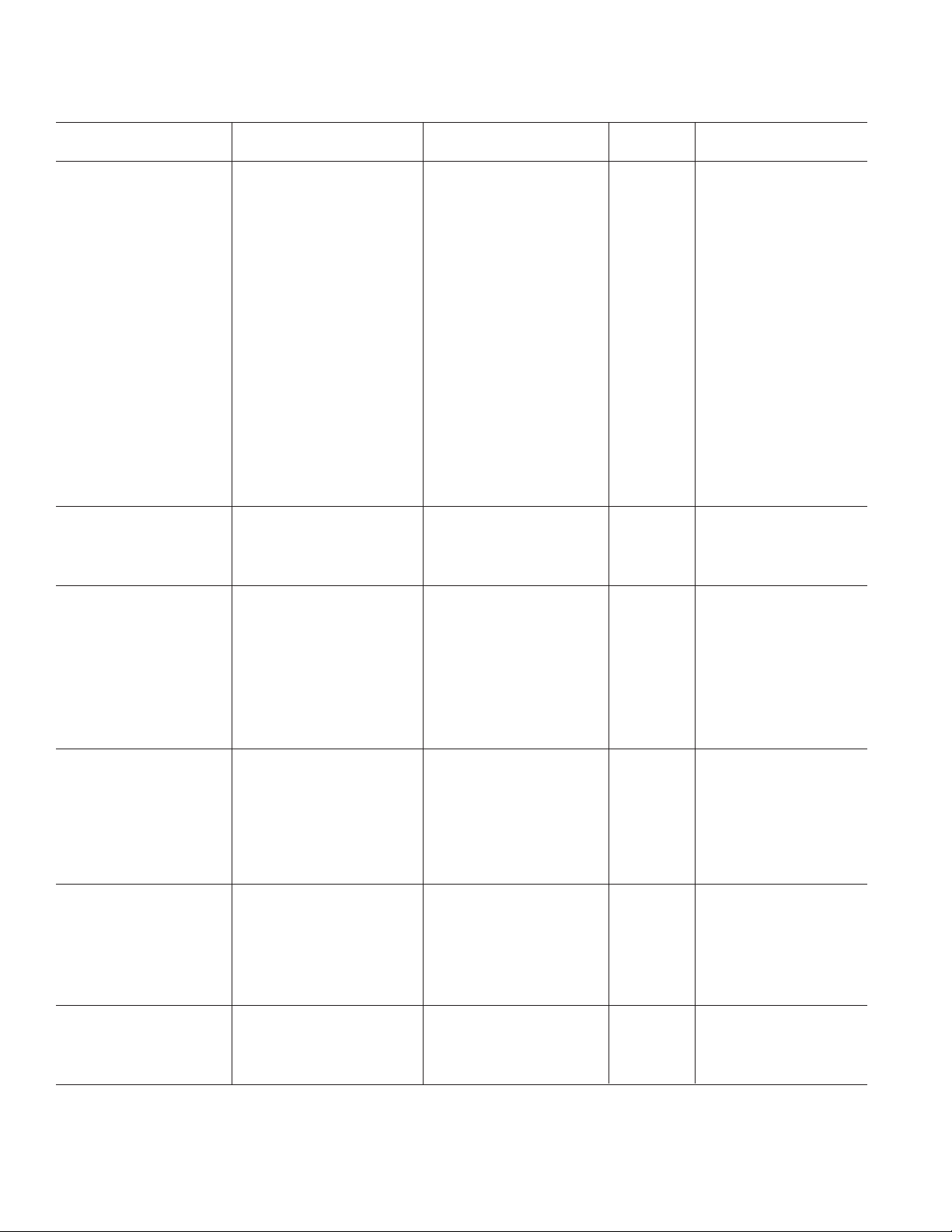

AD5305/AD5315/AD5325–SPECIFICATIONS

C

= 200 pF to GND; all specifications T

L

Parameter

1

DC PERFORMANCE

3, 4

A Version

Min Typ Max Min Typ Max Unit Conditions/Comments

MIN

to T

, unless otherwise noted.)

MAX

2

B Version

2

(VDD = 2.5 V to 5.5 V; V

= 2 V; RL = 2 k⍀ to GND;

REF

AD5305

Resolution 8 8 Bits

Relative Accuracy ±0.15 ±1 ±0.15 ±0.625 LSB

Differential Nonlinearity ±0.02 ±0.25 ±0.02 ±0.25 LSB Guaranteed Monotonic by Design

over All Codes

AD5315

Resolution 10 10 Bits

Relative Accuracy ±0.5 ±4 ±0.5 ±2.5 LSB

Differential Nonlinearity ±0.05 ±0.5 ±0.05 ±0.5 LSB Guaranteed Monotonic by Design

over All Codes

AD5325

Resolution 12 12 Bits

Relative Accuracy ±2 ±16 ±2 ±10 LSB

Differential Nonlinearity ±0.2 ±1 ±0.2 ±1 LSB Guaranteed Monotonic by Design

over All Codes

Offset Error ±0.4 ±3 ±0.4 ±3% of FSR

Gain Error ±0.15 ±1 ±0.15 ±1% of FSR

Lower Deadband 20 60 20 60 mV Lower deadband exists only if

Offset Error Drift

Gain Error Drift

Power Supply Rejection Ratio

DC Crosstalk

DAC REFERENCE INPUTS

V

Input Range 0.25 V

REF

V

Input Impedance 37 45 37 45 kΩ Normal Operation

REF

5

5

5

5

5

–12 –12 ppm of FSR/°C

–5 –5 ppm of FSR/°C

–60 –60 dB ⌬VDD = ± 10%

200 200 µVR

DD

0.25 V

DD

V

>10 >10 MΩ Power-Down Mode

offset error is negative.

= 2 kΩ to GND or V

L

DD

Reference Feedthrough –90 –90 dB Frequency = 10 kHz

OUTPUT CHARACTERISTICS

Minimum Output Voltage

Maximum Output Voltage

5

6

6

0.001 0.001 V This is a measure of the minimum

and maximum drive capability

VDD – 0.001 VDD – 0.001 V of the output amplifier.

DC Output Impedance 0.5 0.5 Ω

Short Circuit Current 25 25 mA VDD = 5 V

16 16 mA VDD = 3 V

Power-Up Time 2.5 2.5 µs Coming out of Power-Down Mode.

VDD = 5 V

55µs Coming out of Power-Down Mode.

VDD = 3 V

LOGIC INPUTS (A0)

5

Input Current ±1 ±1 µA

VIL, Input Low Voltage 0.8 0.8 V VDD = 5 V ± 10%

0.6 0.6 V VDD = 3 V ± 10%

0.5 0.5 V VDD = 2.5 V

VIH, Input High Voltage 2.4 2.4 V VDD = 5 V ± 10%

2.1 2.1 V VDD = 3 V ± 10%

2.0 2.0 V VDD = 2.5 V

Pin Capacitance 3 3 pF

LOGIC INPUTS (SCL, SDA)

VIH, Input High Voltage 0.7 V

VIL, Input Low Voltage –0.3 0.3 VDD–0.3 0.3 VDDVSMBus Compatible at VDD < 3.6 V

5

DD

VDD + 0.3 0.7 V

DD

VDD + 0.3 VSMBus Compatible at VDD < 3.6 V

IIN, Input Leakage Current ± 1 ±1 µA

V

, Input Hysteresis 0.05 V

HYST

CIN, Input Capacitance 8 8 pF

DD

0.05 V

DD

V

Glitch Rejection 50 50 ns Input filtering suppresses noise

spikes of less than 50 ns.

LOGIC OUTPUT (SDA)

VOL, Output Low Voltage 0.4 0.4 V I

Three-State Leakage Current ±1 ±1 µA

5

= 3 mA

0.6 0.6 V I

SINK

SINK

= 6 mA

Three-State Output Capacitance 8 8 pF

REV. F–2–

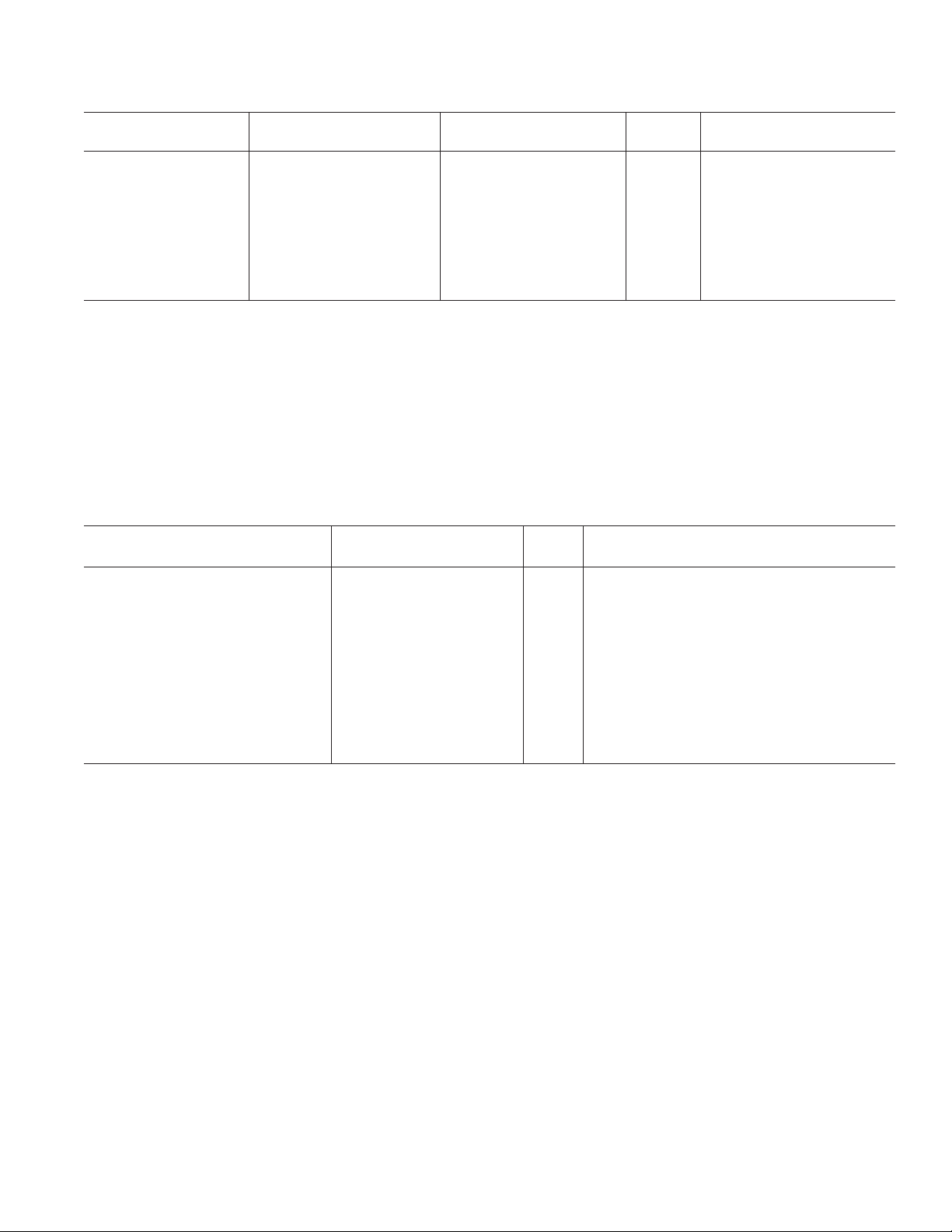

AD5305/AD5315/AD5325

Parameter

POWER REQUIREMENTS

V

IDD (Normal Mode)

IDD (Power-Down Mode) VIH = VDD and VIL = GND

NOTES

1

See the Terminology section.

2

Temperature range (A, B Version): –40°C to +105°C; typical at +25°C.

3

DC specifications tested with the outputs unloaded.

4

Linearity is tested using a reduced code range: AD5305 (Code 8 to 248); AD5315 (Code 28 to 995); AD5325 (Code 115 to 3981).

5

Guaranteed by design and characterization, not production tested.

6

For the amplifier output to reach its minimum voltage, offset error must be negative; to reach its maximum voltage, V

positive.

7

IDD specification is valid for all DAC codes. Interface inactive. All DACs active and excluding load currents.

Specifications subject to change without notice.

1

DD

VDD = 4.5 V to 5.5 V 600 900 600 900 µA

VDD = 2.5 V to 3.6 V 500 700 500 700 µA

VDD = 4.5 V to 5.5 V 0.2 1 0.2 1 µAI

VDD = 2.5 V to 3.6 V 0.08 1 0.08 1 µAI

7

AC CHARACTERISTICS

Parameter

2

A Version

Min Typ Max Min Typ Max Unit Conditions/Comments

2.5 5.5 2.5 5.5 V

(VDD = 2.5 V to 5.5 V; RL = 2 k⍀ to GND; CL = 200 pF to GND; all specifications T

1

otherwise noted.)

2

A, B Version

B Version

3

Min Typ Max Unit Conditions/Comments

Output Voltage Settling Time V

2

VIH = VDD and VIL = GND

= 4 µA (Max) During 0

DD

Readback on SDA

= 1.5 µA (Max) During 0

DD

Readback on SDA

= VDD and offset plus gain error must be

REF

to T

MAX

, unless

= VDD = 5 V

REF

MIN

AD5305 6 8 µs 1/4 Scale to 3/4 Scale Change (0x40 to 0xC0)

AD5315 7 9 µs 1/4 Scale to 3/4 Scale Change (0x100 to 0x300)

AD5325 8 10 µs 1/4 Scale to 3/4 Scale Change (0x400 to 0xC00)

Slew Rate 0.7 V/µs

Major-Code Transition Glitch Energy 12 nV-s 1 LSB Change around Major Carry

Digital Feedthrough 1 nV-s

Digital Crosstalk 1 nV-s

DAC-to-DAC Crosstalk 3 nV-s

Multiplying Bandwidth 200 kHz V

Total Harmonic Distortion –70 dB V

NOTES

1

Guaranteed by design and characterization, not production tested.

2

See the Terminology section.

3

Temperature range (A, B Version): –40°C to +105°C; typical at +25°C.

Specifications subject to change without notice.

= 2 V ± 0.1 V p-p

REF

= 2.5 V ± 0.1 V p-p, Frequency = 10 kHz

REF

REV. F

–3–

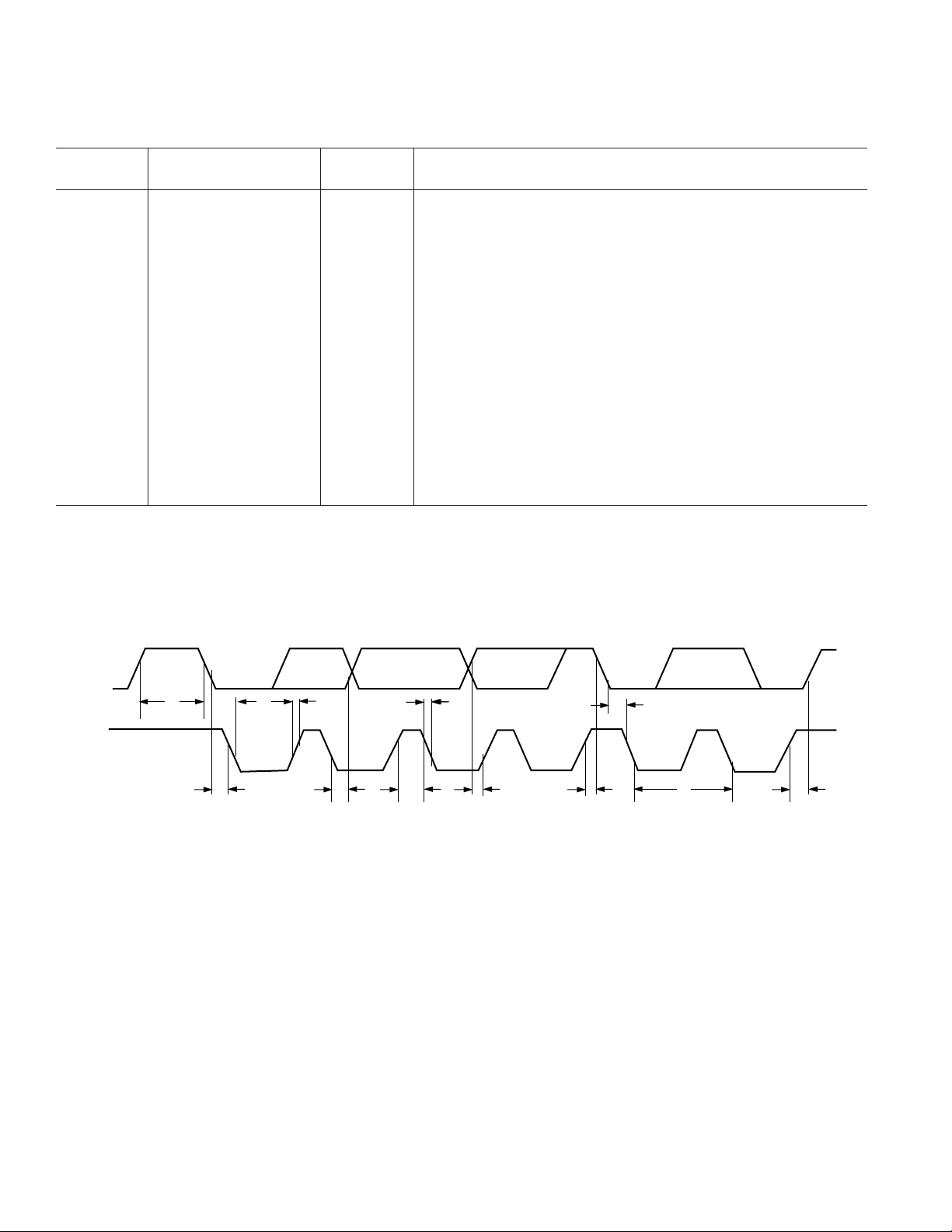

AD5305/AD5315/AD5325

, T

MAX

1, 2

(VDD = 2.5 V to 5.5 V; all specifications T

MIN

to T

, unless otherwise noted.)

MAX

TIMING CHARACTERISTICS

Limit at T

MIN

Parameter (A, B Version) Unit Conditions/Comments

f

SCL

t

1

t

2

t

3

t

4

t

5

3

t

6

t

7

t

8

t

9

t

10

t

11

C

B

NOTES

1

See Figure 1.

2

Guaranteed by design and characterization; not production tested.

3

A master device must provide a hold time of at least 300 ns for the SDA signal (referred to VIH min of the SCL signal) in order to bridge the undefined region of

SCL’s falling edge.

4

CB is the total capacitance of one bus line in pF. tR and tF measured between 0.3 VDD and 0.7 VDD.

Specifications subject to change without notice.

400 kHz max SCL Clock Frequency

2.5 µs min SCL Cycle Time

0.6 µs min t

1.3 µs min t

0.6 µs min t

100 ns min t

0.9 µs max t

0 µs min t

0.6 µs min t

0.6 µs min t

1.3 µs min t

, SCL High Time

HIGH

, SCL Low Time

LOW

, Start/Repeated Start Condition Hold Time

HD,STA

, Data Setup Time

SU,DAT

, Data Hold Time

HD,DAT

, Data Hold Time

HD,DAT

, Setup Time for Repeated Start

SU,STA

, Stop Condition Setup Time

SU,STO

, Bus Free Time between a STOP and a START Condition

BUF

300 ns max tR, Rise Time of SCL and SDA when Receiving

0 ns min t

, Rise Time of SCL and SDA when Receiving (CMOS Compatible)

R

250 ns max tF, Fall Time of SDA when Transmitting

0 ns min t

300 ns max t

20 + 0.1C

4

B

ns min tF, Fall Time of SCL and SDA when Transmitting

, Fall Time of SDA when Receiving (CMOS Compatible)

F

, Fall Time of SCL and SDA when Receiving

F

400 pF max Capacitive Load for Each Bus Line

SDA

SCL

t

9

t

4

START

CONDITION

t

3

t

10

t

6

t

t

11

2

t

5

Figure 1. 2-Wire Serial Interface Timing Diagram

t

7

REPEATED

START

CONDITION

t

4

t

1

t

8

STOP

CONDITION

REV. F–4–

AD5305/AD5315/AD5325

ABSOLUTE MAXIMUM RATINGS

(TA = 25°C, unless otherwise noted.)

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

SCL, SDA to GND . . . . . . . . . . . . . . . . –0.3 V to V

A0 to GND . . . . . . . . . . . . . . . . . . . . . . –0.3 V to V

Reference Input Voltage to GND . . . . . –0.3 V to V

A–D to GND . . . . . . . . . . . . . . . . –0.3 V to VDD + 0.3 V

V

OUT

Operating Temperature Range

Industrial (A, B Version) . . . . . . . . . . . . . . –40°C to +105°C

Storage Temperature Range . . . . . . . . . . . . . –65°C to +150°C

Junction Temperature (T

max) . . . . . . . . . . . . . . . . . . . 150°C

J

1, 2

+ 0.3 V

DD

+ 0.3 V

DD

+ 0.3 V

DD

MSOP

Power Dissipation . . . . . . . . . . . . . . . . . . .(T

max – TA)/

J

JA Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 206°C/W

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 44°C/W

JC

Reflow Soldering

Peak Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . 220°C

Time at Peak Temperature . . . . . . . . . . . . . 10 sec to 40 sec

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2

Transient currents of up to 100 mA will not cause SCR latch-up.

ORDERING GUIDE

Model Temperature Range Package Description Package Option Branding

AD5305ARM –40°C to +105°C 10-Lead MSOP RM-10 DEA

AD5305ARM-REEL7 –40°C to +105°C 10-Lead MSOP RM-10 DEA

AD5315ARM –40°C to +105°C 10-Lead MSOP RM-10 DFA

AD5315ARM-REEL7 –40°C to +105°C 10-Lead MSOP RM-10 DFA

AD5325ARM –40°C to +105°C 10-Lead MSOP RM-10 DGA

AD5325ARM-REEL7 –40°C to +105°C 10-Lead MSOP RM-10 DGA

AD5305BRM –40°C to +105°C 10-Lead MSOP RM-10 DEB

AD5305BRM-REEL –40°C to +105°C 10-Lead MSOP RM-10 DEB

AD5305BRM-REEL7 –40°C to +105°C 10-Lead MSOP RM-10 DEB

AD5315BRM –40°C to +105°C 10-Lead MSOP RM-10 DFB

AD5315BRM-REEL –40°C to +105°C 10-Lead MSOP RM-10 DFB

AD5315BRM-REEL7 –40°C to +105°C 10-Lead MSOP RM-10 DFB

AD5325BRM –40°C to +105°C 10-Lead MSOP RM-10 DGB

AD5325BRM-REEL –40°C to +105°C 10-Lead MSOP RM-10 DGB

AD5325BRM-REEL7 –40°C to +105°C 10-Lead MSOP RM-10 DGB

JA

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD5305/AD5315/AD5325 feature proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions

are recommended to avoid performance degradation or loss of functionality.

REV. F

–5–

AD5305/AD5315/AD5325

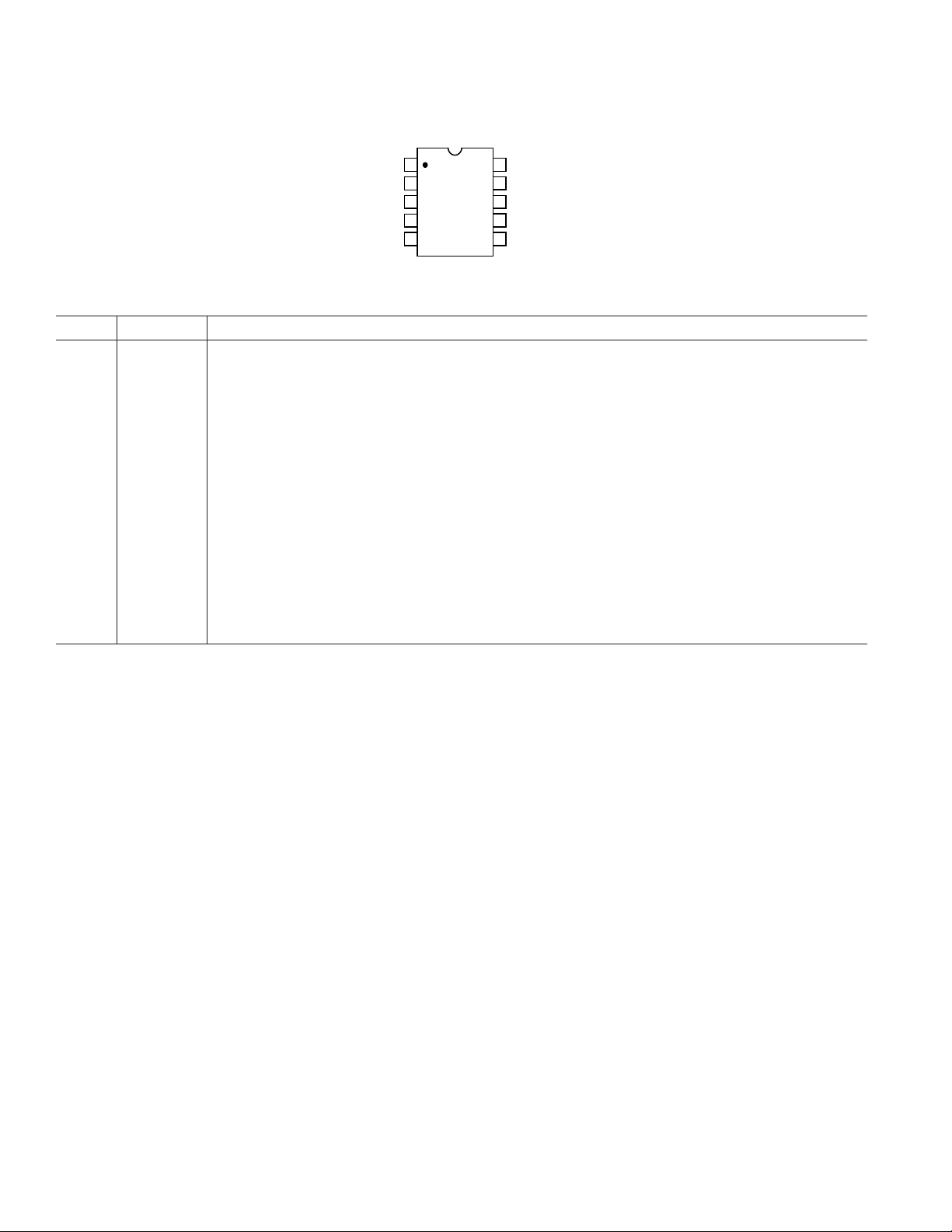

PIN CONFIGURATION

V

1

DD

A

B

C

AD5305/

2

AD5315/

3

AD5325

TOP VIEW

4

(Not to Scale)

5

V

OUT

V

OUT

V

OUT

REFIN

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Function

1V

DD

Power Supply Input. These parts can be operated from 2.5 V to 5.5 V and the supply should be

decoupled to GND.

2V

3V

4V

ABuffered Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.

OUT

BBuffered Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.

OUT

CBuffered Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.

OUT

5 REFIN Reference Input Pin for All Four DACs. It has an input range from 0.25 V to V

6V

DBuffered Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.

OUT

7GND Ground Reference Point for All Circuitry on the Part.

8 SDA Serial Data Line. This is used in conjunction with the SCL line to clock data into or out of the 16-bit

input shift register. It is a bidirectional open-drain data line that should be pulled to the supply with an

external pull-up resistor.

9 SCL Serial Clock Line. This is used in conjunction with the SDA line to clock data into or out of the 16-bit

input shift register. Clock rates of up to 400 kbit/s can be accommodated in the 2-wire interface.

10 A0 Address Input. Sets the least significant bit of the 7-bit slave address.

A0

10

SCL

9

SDA

8

GND

7

6

V

D

OUT

.

DD

TERMINOLOGY

Relative Accuracy

For the DAC, relative accuracy or integral nonlinearity (INL) is

a measure of the maximum deviation, in LSB, from a straight

line passing through the endpoints of the DAC transfer function.

Typical INL versus code plots can be seen in TPCs 1, 2, and 3.

Differential Nonlinearity

Differential nonlinearity (DNL) is the difference between the

measured change and the ideal 1 LSB change between any two

adjacent codes. A specified differential nonlinearity of ±1 LSB

maximum ensures monotonicity. This DAC is guaranteed

monotonic by design. Typical DNL versus code plots can be

seen in TPCs 4, 5, and 6.

Offset Error

This is a measure of the offset error of the DAC and the output

amplifier. It is expressed as a percentage of the full-scale range.

Gain Error

This is a measure of the span error of the DAC. It is the deviation in slope of the actual DAC transfer characteristic from the

ideal expressed as a percentage of the full-scale range.

Offset Error Drift

This is a measure of the change in offset error with changes in

temperature. It is expressed in (ppm of full-scale range)/°C.

Gain Error Drift

This is a measure of the change in gain error with changes in

temperature. It is expressed in (ppm of full-scale range)/°C.

Power Supply Rejection Ratio (PSRR)

This indicates how the output of the DAC is affected by changes

in the supply voltage. PSRR is the ratio of the change in V

a change in V

in dB. V

REF

for full-scale output of the DAC. It is measured

DD

is held at 2 V and VDD is varied ±10%.

OUT

to

DC Crosstalk

This is the dc change in the output level of one DAC at midscale

in response to a full-scale code change (all 0s to all 1s and vice

versa) and output change of another DAC. It is expressed in µV.

Reference Feedthrough

This is the ratio of the amplitude of the signal at the DAC output to the reference input when the DAC output is not being

updated. It is expressed in dB.

REV. F–6–

Loading...

Loading...