High Speed Active Load

a

FEATURES ⴞ50 mA Voltage Programmable Current Range Three Selectable Gain Ranges

1.7 ns Propagation Delay

Inhibit Mode Function

High Speed Differential Inputs for Maximum Flexibility

Ultrasmall 20-Lead PSOP Package with Built-In Heatsink

APPLICATIONS

Automatic Test Equipment

Semiconductor Test Systems

Board Test Systems

PRODUCT DESCRIPTION

The AD53041 is a complete, high speed, current switching load

designed for use in linear, digital or mixed signal test systems.

Combining a high speed monolithic process with a unique surface mount package, this product attains superb electrical performance while preserving optimum packaging densities in an

ultrasmall 20-lead, PSOP package with a built-in heatsink.

Featuring current programmability of up to ±50 mA, the

AD53041 is designed to force the device under test to source

or sink the programmed I

currents are determined by applying a corresponding voltage

(5 V = 50 mA, 16 mA, 5 mA) to the I

The voltage-to-current conversion is performed within the

AD53041, thus allowing the current levels to be set by a standard voltage out digital-to-analog converter.

The AD53041 transition from I

put voltage of the device under test slews above or below the

programmed threshold or commutation voltage. The commutation voltage is programmable from –2 V to +7 V, covering the

large spectrum of logic devices while able to support the large

current specifications (48 mA) typically associated with line

drivers. To test I/O devices, the active load can be switched into

a high impedance state (Inhibit Mode), electrically removing the

active load from the path through the Inhibit Mode feature. The

active load leakage current in Inhibit is typically 100 nA.

The Inhibit input circuitry is implemented using high speed

differential inputs with a common-mode voltage range of

–2 V to +3 V and a maximum differential voltage of 3 V. This

allows for direct interface to precision differential ECL timing or

the simplicity of switching active load from a single ended TTL

or CMOS logic source. With switching speeds from I

into Inhibit of less than 2.0 ns, the AD53041 can be electrically

removed from the signal path “on the fly.”

OH

and I

currents. IOH and I

OL

and I

OHPGM

to IOL occurs when the out-

OH

OLPGM

or I

OH

OL

pins.

OL

with Inhibit Mode

AD53041

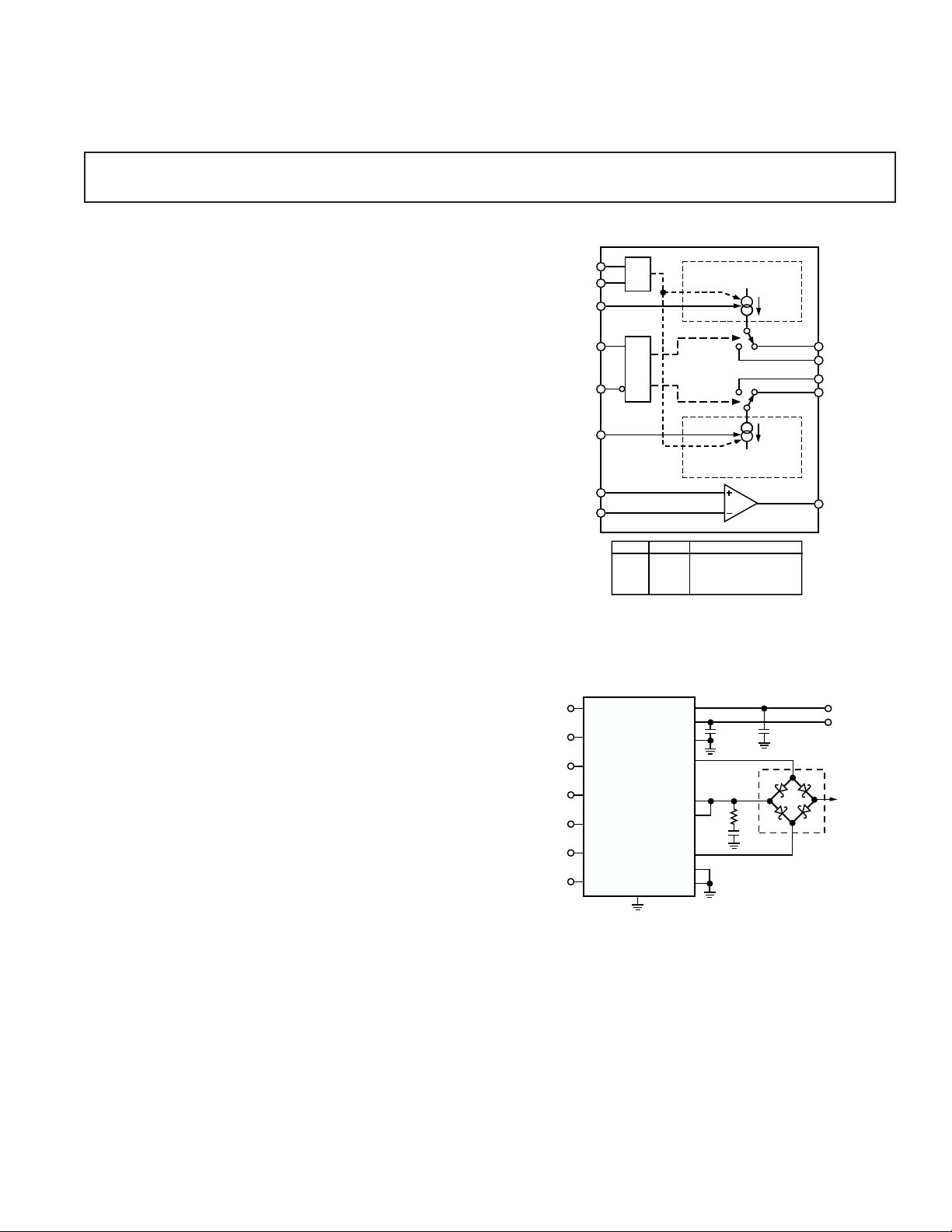

FUNCTIONAL BLOCK DIAGRAM

GAINA

GAINB

I

OLPGM

INH

INH

I

OHPGM

AD53041

V

COMIN

OUT_SENSE

GAINA GAINB FULL-SCALE CURRENT

0

0

1

1

The AD53041 is available in a 20-lead, PSOP package with a

built-in-heatsink and is specified to operate over the ambient

commercial temperature range from –25°C to +85°C.

INH

INH

I

OHPGM

V

COMIN

I

OLPGM

GAINA

GAINB

NOT SHOWN: THE AGND PINS ARE THE HIGH QUALITY GROUND

REFERENCE FOR THE VOLTAGE-TO-CURRENT CONVERTERS.

THE GND PINS PROVIDE RETURN PATHS FOR INTERNAL CURRENTS.

IS THE POSITIVE SUPPLY, VEE IS THE NEGATIVE SUPPLY.

V

CC

ALL GROUND PINS SHOULD BE CONNECTED TO THE SYSTEM

ANALOG GROUND PLANE.

AD53041

OUT_SENSE

GND

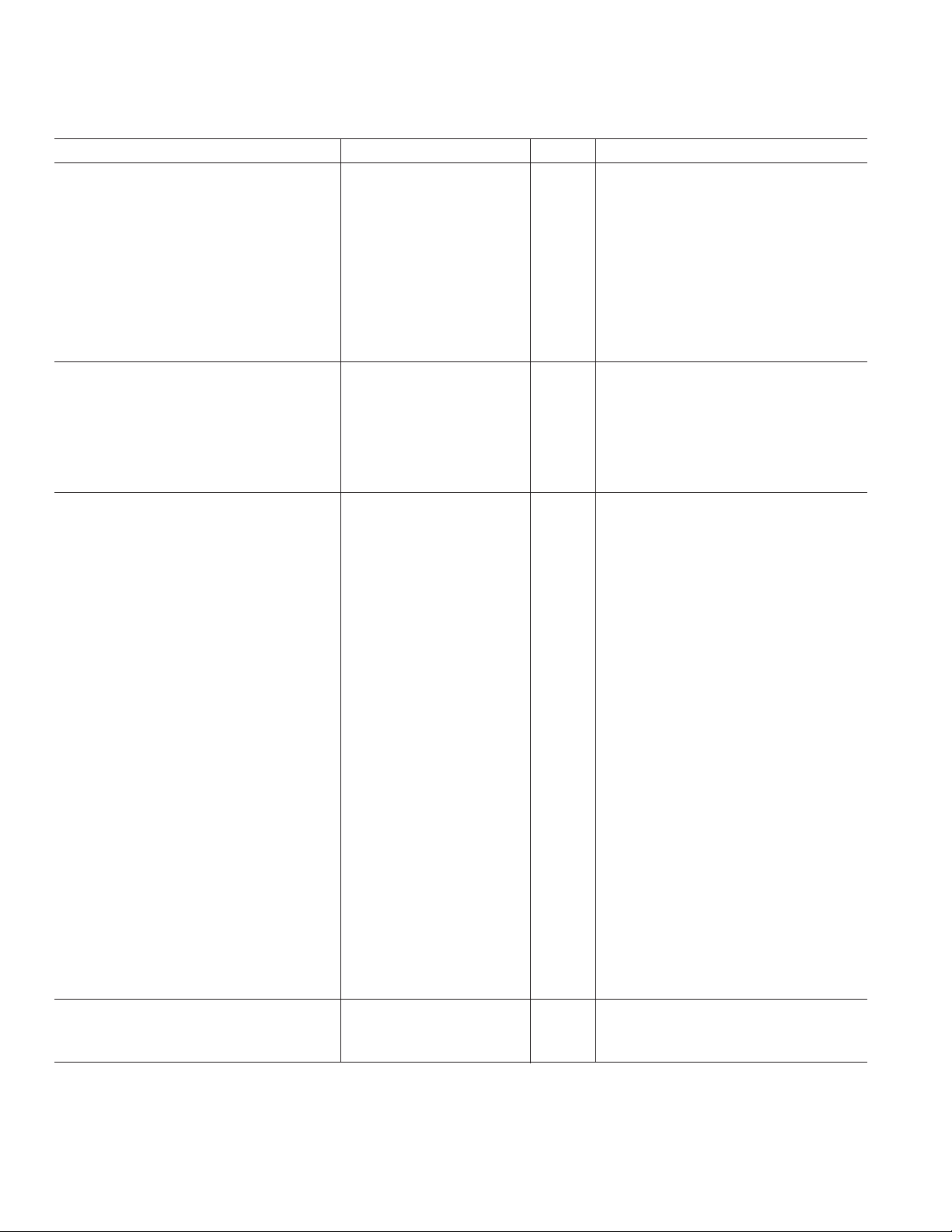

Figure 1. Typical Application Circuit

VOLTAGE-TO-CURRENT

VOLTAGE-TO-CURRENT

0

1

0

1

AGND

I

OLOUT

V

COMOUT

0.1F

I

OHOUT

I

OLRTN

I

OHRTN

CONVERTER

CONVERTER

V

COM

BUFFER

50mA

16mA

5mA

NOT VALID

0.1F 0.1F

1Ω

I

OLOUT

I

OLRTN

I

OHRTN

I

OHOUT

V

COMOUT

HSMS-2818

OR EQUIV.

V

CC

V

EE

TO DUT

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1998

AD53041–SPECIFICATIONS

–5.2 V ⴞ 3% unless otherwise specified. V

is bypassed to ground with a series RC consisting of a 1 ⍀ resistor and a 0.1 F capacitor,

COMOUT

(All specifications apply at TJ = +85ⴗC ⴞ 5ⴗC. +VS = +10.5 V ⴞ 3%, –VS =

and is also connected directly to OUT_SENSE. All temperature coefficients are characterized over TJ = 75ⴗC–95ⴗC.)

Parameter Min Typ Max Units Test Conditions

INPUT CHARACTERISTICS

INH, INH

Input Voltage –2 ECL 0 V

Bias Current –1 1 mA INH, INH = –2 V, 0 V

GAINA, GAINB

Input Voltage 0 TTL/CMOS 5 V

Bias Current 0 2 mA GAINA, GAINB = 5 V

V

I

I

COM

, I

OHPGM

I

, 0 to + Full Scale, Any Gain Range –0.1 5.2 V V(I

OH

I

, 0 to – Full Scale, Any Gain Range –0.1 5.2 V V(I

OL

, I

OHPGM

BUFFER

Voltage Range

OLPGM

Bias Current –300 300 µA V(I

OLPGM

OHOUT

) = –2 V, 7 V

OLOUT

OHPGM

) = –2 V, 7 V

) = +5 V, V(I

OLPGM

Voltage Range –2 7 V ±50 mA Output Current

Offset ±5mVV

Offset Drift 0.1 mV/°CV

Nonlinearity ±5mVV

Input Bias Current –50 50 µAV

Output Resistance <1 Ω V

= 0 V

COM

= 0 V

COM

= –2 V to 7 V

COM

= –2 V to 7 V

COM

= 0 V, I

COM

= ±50 mA

OUT

OUTPUT CHARACTERISTICS

Full-Scale Current Range See Functional Block Diagram

Range 0 50 mA

Range 1 16 mA

Range 2 5 mA

Offset Error V(I

Range 0 –1 1 mA V(I

OHPGM

OHOUT

) = V(I

) = ±2 V, V(I

OLPGM

) = 100 mV,

OLOUT

Range 1 –0.3 0.3 mA

Range 2 –0.3 0.3 mA

Offset Drift V(I

Range 0 1 µA/°CV(I

OHPGM

OHOUT

) = V(I

) = V(I

OLPGM

OLOUT

) = 100 mV,

) = 0 V

Range 1 1 µA/°C

Range 2 1 µA/°C

Gain Error

Range 0 <1 % FSR

Range 1 <5 % FSR

Range 2 <8 % FSR

Gain Drift

Range 0 1 µA/°C

Range 1 0.5 µA/°C

Range 2 0.3 µA/°C

Gain Ratio Drift

Range 1 to Range 0 0.01 %/°C

Range 2 to Range 0 0.01 %/°C

Nonlinearity ±0.05 % FSR Range 0

Common-Mode Error ±0.05 %FSR Range 0

PSRR ±0.1 %FSR/V Range 0, V(I

OHPGM

) = V(I

OLPGM

= 100 mV, Either Supply Over Operating

Range

) = 0 V

) = ±2 V

)

OUTPUT VOLTAGE RANGE

, I

I

OHOUT

I

OLOUT

, I

OLRTN

OHRTN

–2.5 7.5 V IOH = 50 mA

–2.5 7.5 V IOL = 50 mA

–2–

REV. A

Loading...

Loading...