Analog Devices AD53040 Datasheet

Ultrahigh Speed Pin Driver

a

FEATURES

500 MHz Driver Operation

Driver Inhibit Function

100 ps Edge Matching

Guaranteed Industry Specifications

50 ⍀ Output Impedance

>1.5 V/ns Slew Rate

Variable Output Voltages for ECL, TTL and CMOS

High Speed Differential Inputs for Maximum Flexibility

Ultrasmall 20-Lead SOP Package with Built-In Heat Sink

APPLICATIONS

Automatic Test Equipment

Semiconductor Test Systems

Board Test Systems

Instrumentation and Characterization Equipment

PRODUCT DESCRIPTION

The AD53040 is a complete high speed pin driver designed for

use in digital or mixed-signal test systems. Combining a high

speed monolithic process with a unique surface mount package,

this product attains superb electrical performance while preserving optimum packaging densities and long-term reliability in an

ultrasmall 20-lead, SOP package with built-in heat sink.

Featuring unity gain programmable output levels of –3 V to

+8 V, with output swing capability of less than 100 mV to 9 V,

the AD53040 is designed to stimulate ECL, TTL and CMOS

logic families. The 500 MHz data rate capacity and matched

output impedance allows for real-time stimulation of these

digital logic families. To test I/O devices, the pin driver can

be switched into a high impedance state (Inhibit Mode), electrically removing the driver from the path. The pin driver leakage

current inhibit is typically 100 nA and output charge transfer

entering inhibit is typically less than 20 pC.

with Inhibit Mode

AD53040

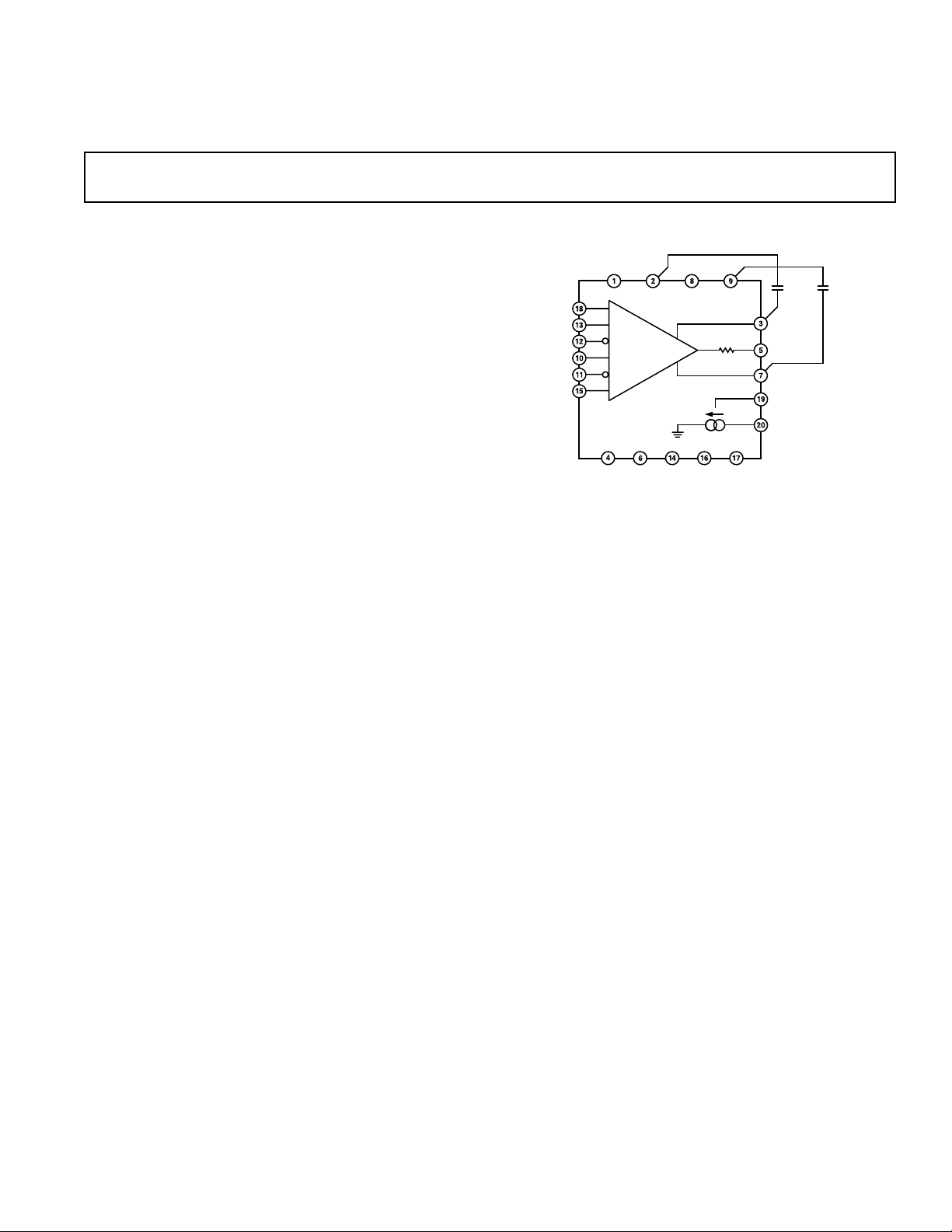

FUNCTIONAL BLOCK DIAGRAM

V

V

CCVEE

CC

V

H

DATA

DATA

INH

INH

V

L

DRIVER

AD53040

GND

GND GND GND GND

The AD53040 transition from HI/LO or to inhibit is controlled

through the data and inhibit inputs. The input circuitry uses

high speed differential inputs with a common-mode range of

±3 V. This allows for direct interface to precision differential

ECL timing or the simplicity of stimulating the pin driver from a

single ended TTL or CMOS logic source. The analog logic HI/LO

inputs are equally easy to interface. Typically requiring 10 µA of

bias current, the AD53040 can be directly coupled to the

output of a digital-to-analog converter.

The AD53040 is available in a 20-lead, SOP package with a

built-in heat sink and is specified to operate over the ambient

commercial temperature range of –25°C to +85°C.

50V

1.0mA/K

V

EE

39nF 39nF

V

HDCPL

V

OUT

V

LDCPL

TV

CC

THERM

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

AD53040–SPECIFICATIONS

(All specifications are at TJ = +85ⴗC ⴞ 5ⴗC, +VS = +12 V ⴞ 3%, –VS = –7 V ⴞ

3% unless otherwise noted. All temperature coefficients are measured at TJ = +75ⴗC–95ⴗC). (A 39 nF capacitor must be connected between

VCC and V

Parameter Min Typ Max Units Test Conditions

DIFFERENTIAL INPUT CHARACTERISTICS

Input Swing (Data to DATA, INH to INH) ECL 2 Volts

Max (DATA, DATA) to Min (INH, INH)

Max (INH, INH) to Min (Data, DATA) 2 Volts

Bias Current ±10 µAV

REFERENCE INPUTS

Bias Currents –50 +50 µAV

OUTPUT CHARACTERISTICS

Logic High Range –2 +8 Volts DATA = H, VH = –2 V to +8 V

Logic Low Range –3 +5 Volts DATA = L, V

Amplitude (V

Absolute Accuracy

V

V

V

V

Offset TC, V

Output Resistance 45 47 49 Ω DATA = H, V

Output Leakage –1.0 +1.0 µAV

Dynamic Current Limit 150 mA C

Static Current Limit ±65 mA Output to –3 V, V

PSRR, Drive Mode 35 dB VS = V

DYNAMIC PERFORMANCE, DRIVE

(VH and VL)

Propagation Delay Time 1.5 ns Measured at 50%, V

Propagation Delay TC 2 ps/°C Measured at 50%, V

Delay Matching, Edge to Edge 100 ps Measured at 50%, V

Rise and Fall Time

Rise and Fall Time TC

Overshoot, Undershoot and Preshoot ±(1% +50 mV) % of Step + mV a. V

Settling Time

and between VEE and V

HDCPL

and VL) 0.1 9 Volts VL = –0.05 V, VH = +0.05 V and

H

Offset –100 +100 mV DATA = H, VH = –2 V to +8 V, VL = –3 V

H

Gain + Linearity Error ±0.3 ±5% of V

H

Offset –100 +100 mV DATA = L, VL = –3 V to +5 V, VH = +6 V

L

Gain + Linearity Error ±0.3 ±5% of V

L

or V

H

L

1 V Swing 0.8 ns Measured 20%–80%, V

3 V Swing 1.7 ns Measured 10%–90%, V

5 V Swing 2.4 ns Measured 10%–90%, V

1 V Swing ±1 ps/°C Measured 20%–80%, V

3 V Swing ±2 ps/°C Measured 10%–90%, V

5 V Swing ±3 ps/°C Measured 10%–90%, V

to 15 mV 40 ns V

to 4 mV 8 µsV

Delay Change vs. Pulsewidth 50 ps V

LDCPL

.)

= –2 V, 0.0 V

IN

, VH = 5 V

L

V

= –3 V (VH = –2 V to +6 V)

L

V

= –1 V (VH = +6 V to +8 V)

L

V

= –2 V, VH = +7 V

L

+ mV DATA = H, VH = –2 V to +8 V, VL = –3 V

H

+ mV DATA = L, VL = –3 V to +5 V, VH = +6 V

0.5 mV/°CV

L

, VH = 0 V, +5 V and –3 V, 0 V

L

= 30 mA

I

OUT

= –3 V to +8 V

OUT

= 39 nF, VH = +7 V, VL = –2 V

BYP

DATA = H and Output to +8 V, V

V

= –3 V, DATA = L

L

V

= –400 mV

L

V

= –400 mV

L

V

= –400 mV

L

, VH = 0.0 V, 1.0 V

L

b. V

, VH = 0.0 V, 3.0 V

L

, VH = 0.0 V, 5.0 V

c. V

L

= 0 V, VH = 0.5 V

L

= 0 V, VH = 0.5 V

L

= 0 V, VH = 2 V,

L

= –3 V to +5 V, VH = +6 V

L

= +3 V, VL = 0 V,

H

= +8 V, VL = –1 V,

H

± 3%

S

= +400 mV,

H

= +400 mV,

H

= +400 mV,

H

L

L

L

L

L

L

= +6 V,

H

= 0 V, VH = 1 V

= 0 V, VH = 3 V

= 0 V, VH = 5 V

= 0 V, VH = 1 V

= 0 V, VH = 3 V

= 0 V, VH = 5 V

Pulsewidth = 2.5 ns/7.5 ns, 30 ns/100 ns

–2–

REV. B

AD53040

WARNING!

ESD SENSITIVE DEVICE

Parameter Min Typ Max Units Test Conditions

DYNAMIC PERFORMANCE, DRIVE

(VH and VL) (Continued)

Minimum Pulsewidth

3 V Swing 1.7 ns 4.0 ns Input, 10%/90% Output,

V

= 0 V, VH = 3 V

5 V Swing 2.6 ns 6.0 ns Input, 10%/90% Output,

Toggle Rate 500 MHz V

DYNAMIC PERFORMANCE, INHIBIT

Delay Time, Active to Inhibit 2 5 ns Measured at 50%, VH = +2 V,

Delay Time, Inhibit to Active 2 5 ns Measured at 50%, V

I/O Spike <200 mV, p-p V

Output Capacitance 5 pF Driver Inhibited

POWER SUPPLIES

Total Supply Range 19 V

Positive Supply +12 V

Negative Supply –7 V

Positive Supply Current 75 mA

Negative Supply Current 75 mA

Total Power Dissipation 1.15 1.43 W

Temperature Sensor Gain Factor 1.0 µA/K R

NOTES

Connecting or shorting the decoupling capacitors to ground will result in the destruction of the device.

Specifications subject to change without notice.

L

= 0 V, VH = 5 V

V

L

= –1.8 V, VH = –0.8 V,

L

V

> 600 mV p-p

OUT

V

= –2 V

L

V

= –2 V

L

= 0 V, VL = 0 V

H

= 10 K, V

LOAD

SOURCE

= +2 V,

H

= +12 V

ABSOLUTE MAXIMUM RATINGS

1

Power Supply Voltage

+V

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +13 V

S

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –8 V

–V

S

+V

to –VS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +20 V

S

Inputs

DATA, DATA, INH, INH . . . . . . . . . . . . . . . . +5 V, –3 V

DATA to DATA, INH to INH . . . . . . . . . . . . . . . . . . ±3 V

, VL to GND . . . . . . . . . . . . . . . . . . . . . . . . . +9 V, –4 V

V

H

to VL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +11 V, 0 V

V

H

Outputs

V

Short Circuit Duration . . . . . . . . . . . . . . . .Indefinite

OUT

V

Range in Inhibit Mode

OUT

V

V

. . . . . Do Not Connect Except for Capacitor to V

HDCPL

. . . . . Do Not Connect Except for Capacitor to V

LDCPL

THERM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +13 V, 0 V

Environmental

Operating Temperature (Junction) . . . . . . . . . . . . . .+175°C

Storage Temperature . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 sec)

3

. . . . . . . . . . +260°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Absolute maximum limits apply

individually, not in combination. Exposure to absolute maximum rating conditions

for extended periods may affect device reliability.

2

Output short circuit protection is guaranteed as long as proper heat sinking is

employed to ensure compliance with the operating temperature limits.

3

To ensure lead coplanarity (±0.002 inches) and solderability, handling with bare

hands should be avoided and the device should be stored in environments at 24°C

± 5°C (75°F ± 10°F) with relative humidity not to exceed 65%.

2

ORDERING GUIDE

CC

EE

Package Quantity Per Package

Model Description Shipping Container Option

AD53040KRP 20-Lead Power SOIC Tube, 38 Pieces RP-20

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD53040 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

Shipment Method,

REV. B

–3–

Loading...

Loading...