Yamaha DIO8 Service Manual

DIGITAL IO BOX

SERVICE MANUAL

011510

PA

200004**-350000

CONTENTS

REVISED PAGE LIST ··························································· 2-1

SPECIFICATIONS································································· 3-1

PANEL LAYOUT···································································· 3-2

DIMENSIONS········································································ 3-3

BLOCK DIAGRAM···································································· 4

DISASSEMBLY PROCEDURE················································· 5

LSI PIN DESCRIPTION···························································· 8

IC BLOCK DIAGRAM ····························································· 12

CIRCUIT BOARDS································································· 14

INSPECTION·········································································· 19

TEST PROGRAM··································································· 21

PARTS LIST

CIRCUIT DIAGRAM

HAMAMATSU, JAPAN

0.27K-

****

Printed in Japan '00.09

DIO8

REVISED PAGE LIST

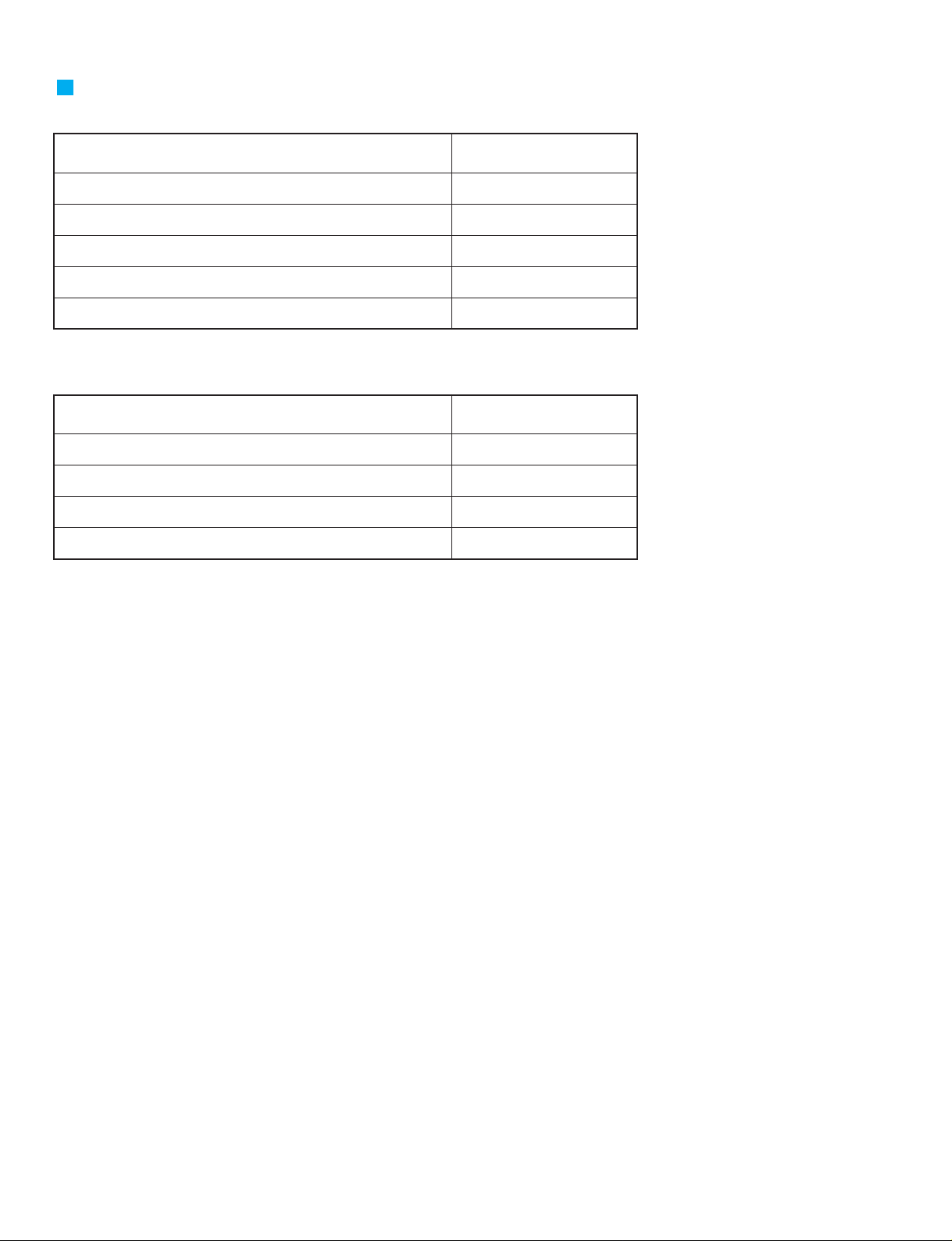

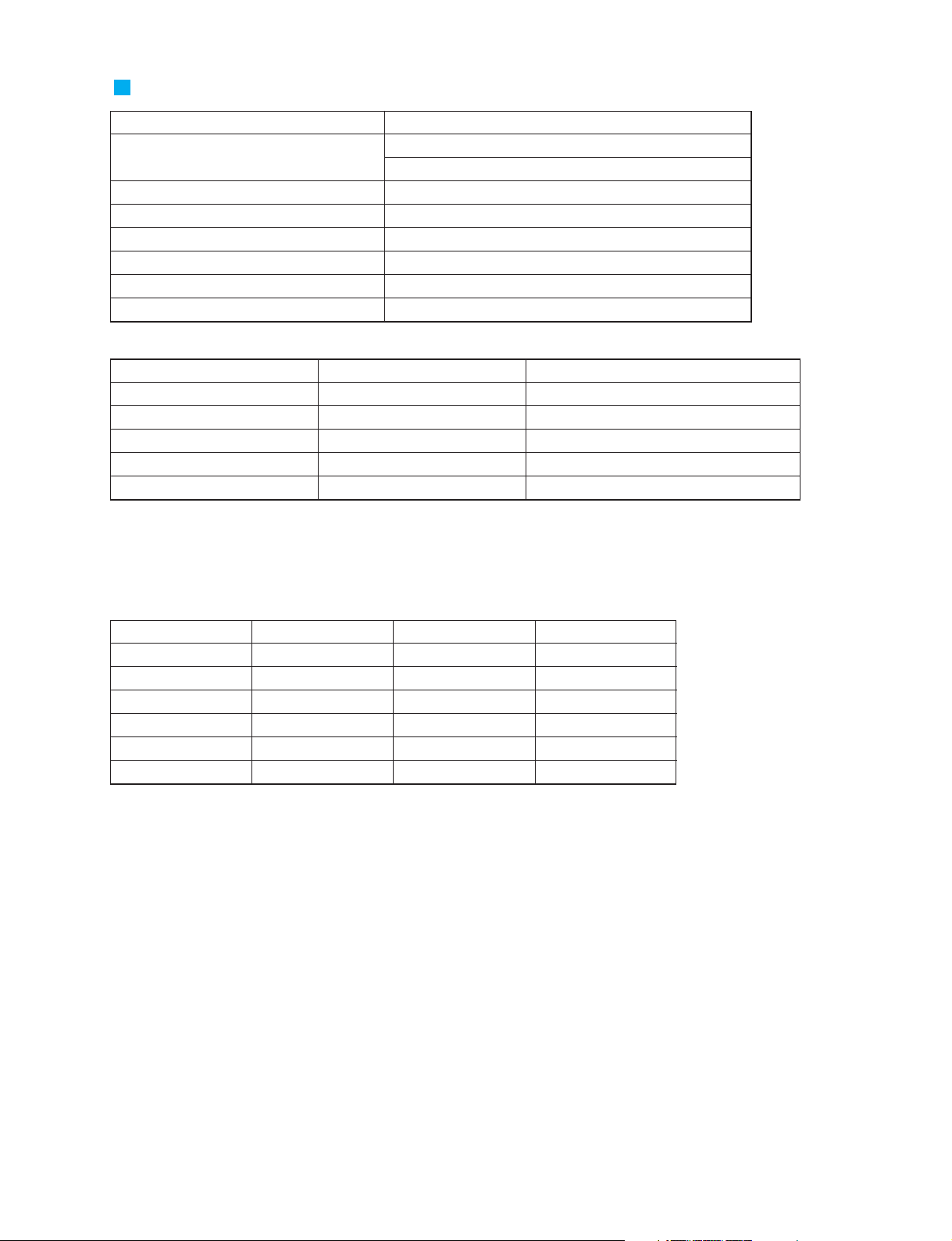

SPECIFICATIONS

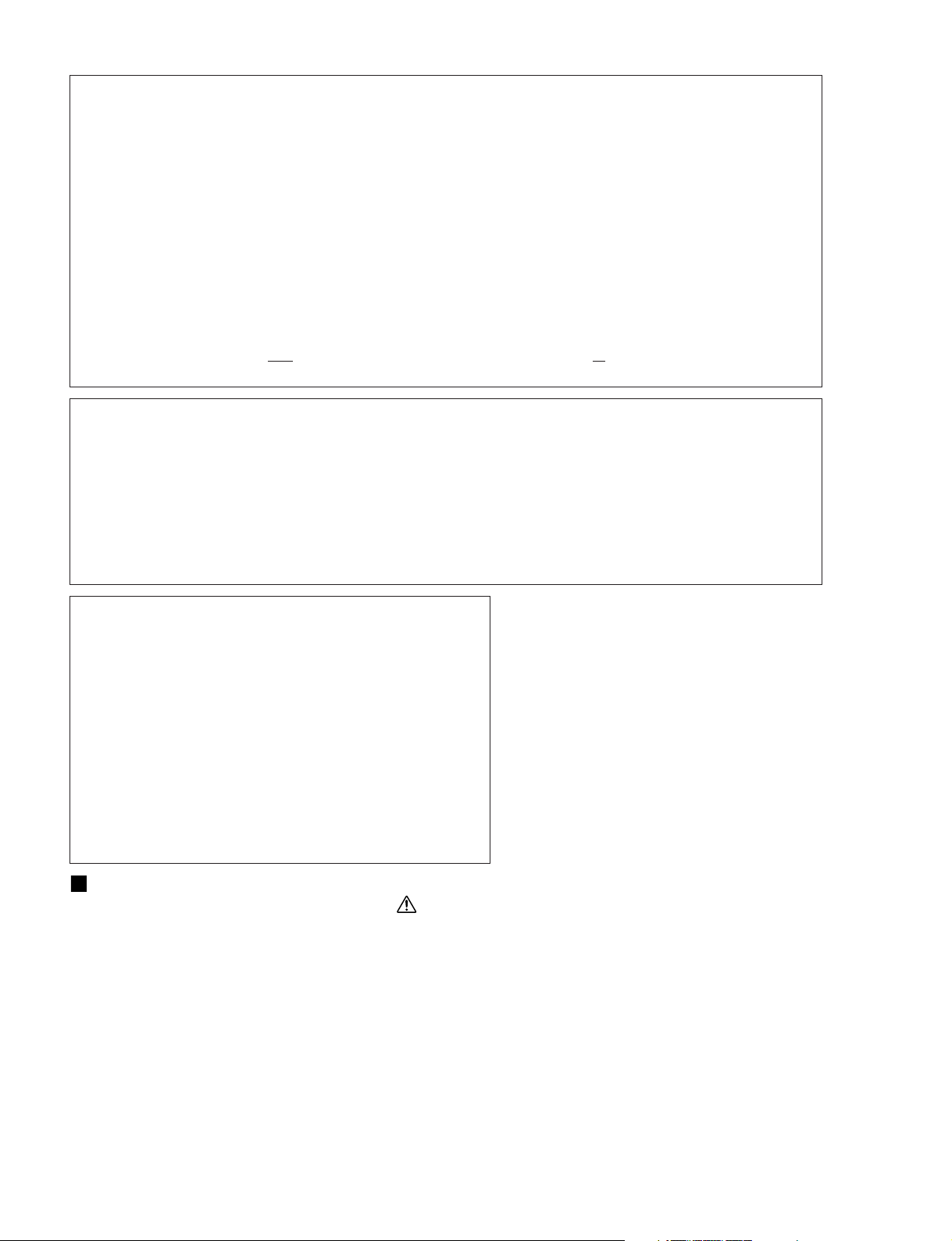

PANEL LAYOUT

DIMENSIONS

INSPECTION

TEST PROGRAM

<

PARTS LIST>

OVERALL ASSEMBLY

DC ASSEMBLY

FRONT PANEL ASSEMBLY

ELECTRICAL PARTS

ITEM

ITEM

PAGE

3-1

3-2

3-3

19~20

21~28

PAGE

3

5

6

7~11

2-1

DIO8

2-2

WARNING: CHEMICAL CONTENT NOTICE!

The solder used in the production of this product contains LEAD. In addition, other electrical/electronic and/or plastic (where

applicable) components may also contain traces of chemicals found by the California Health and Welfare Agency (and possibly

other entities) to cause cancer and/or birth defects or other reproductive harm.

DO NOT PLACE SOLDER, ELECTRICAL/ELECTRONIC OR PLASTIC COMPONENTS IN YOUR MOUTH FOR ANY REASON

WHAT SO EVER!

Avoid prolonged, unprotected contact between solder and your skin! When soldering, do not inhale solder fumes or expose eyes

to solder/flux vapor!

If you come in contact with solder or components located inside the enclosure of this product, wash your hands before handling

food.

IMPORTANT NOTICE

This manual has been provided for the use of authorized Yamaha Retailers and their service personnel. It has been assumed that

basic service procedures inherent to the industry, and more specifically Yamaha Products, are already known and understood by

the users, and have therefore not been restated.

WARNING: Failure to follow appropriate service and safety procedures when servicing this product may result in personal

injury, destruction of expensive components and failure of the product to perform as specified. For these

reasons, we advise all Yamaha product owners that all service required should be performed by an authorized

Yamaha Retailer or the appointed service representative.

IMPORTANT: This presentation or sale of this manual to any individual or firm does not constitute authorization, certification,

recognition of any applicable technical capabilities, or establish a principal-agent relationship of any form.

The data provided is belived to be accurate and applicable to the unit(s) indicated on the cover. The research engineering, and

service departments of Yamaha are continually striving to improve Yamaha products. Modifications are, therefore, inevitable and

changes in specification are subject to change without notice or obligation to retrofit. Should any discrepancy appear to exist,

please contact the distributor's Service Division.

WARNING: Static discharges can destroy expensive components. Discharge any static electricity your body may have

accumulated by grounding yourself to the ground bus in the unit (heavy gauge black wires connect to this bus).

IMPORTANT: Turn the unit OFF during disassembly and parts replacement. Recheck all work before you apply power to the

unit.

WARNING

Components having special characteristics are marked and must be replaced with parts having specification equal to those

originally installed.

IMPORTANT NOTICE FOR THE UNITED KINGDOM

Connecting the Plug and Cord

IMPORTANT. The wires in this main lead are coloured in

accordance with the following code:

BLUE: NEUTRAL

BROWN: LIVE

As the colours of the wires in the main lead of this apparatus may not

correspond with the coloured markings identifying the terminals in

your plug, proceed as follows:

The BLUE wire must be connected to the terminal that is marked with

the letter N (or coloured BLACK).

The BROWN wire must be connected to the terminal that is marked

with the letter L (or coloured RED).

Be certain that neither core is connected to the earth terminal of the

three pin plug.

SPECIFICATIONS

DIO8

Sampling frequency (external sync)

Power supply

Power consumption

Dimensions (W x H x D)

Weight

Operating temperature

Power cable length

Accessories

39.69 kHz – 50.88 kHz

USA and Canada: 120 V, 60 Hz

Others: 230 V, 50 Hz

70 W

480 mm x 185.5 mm x 411.6 mm

15.5 kg

10 – 35 ˚C

1.5 m

Connection cable (68-pin, D-sub, half-pitch) x 2, Length: 3 m

I/Os

I/O connectors

INPUT A, B

OUTPUT A, B

COM

WORD CLOCK IN

WORD CLOCK OUT (X4)

*1: On the rear panel

RS422

RS422

RS232C

TTL/75 Ω (ON/OFF)

TTL/75 Ω

Level

D-sub, half-pitch, 68-pin connector (female)

D-sub, half-pitch, 68-pin connector (female)

D-sub,9-pin connector (male)

*1

BNC connector

BNC connector

Slots

Eight slots (slots 1-8) are available on the DIO8 for installing digital I/O cards and analog I/O cards.

Slot 1 supports a serial interface card (not released yet).

Type

<Optional interface cards>

Card

MY8-TD

MY8-AT

MY8-AE

MY8-AD

MY4-AD

MY4-DA

TASCAM

ADAT

AES/EBU

ANALOG IN

ANALOG IN

ANALOG OUT

Format

8 IN

8 IN

8 IN

8 IN

4 IN

—

Input

Output

8 OUT

8 OUT

8 OUT

—

—

4 OUT

3-1

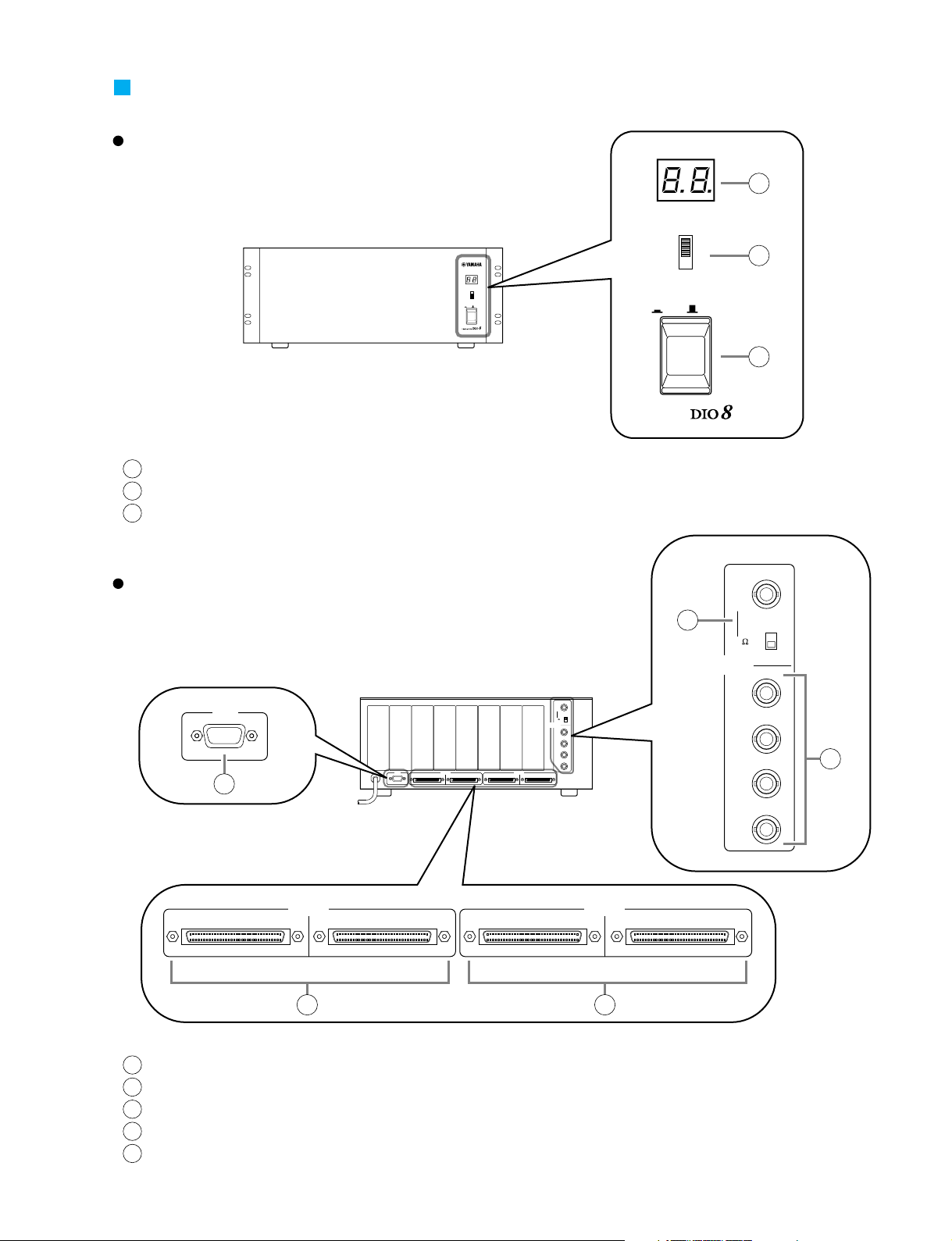

PANEL LAYOUT

*

The illustration shows the unit

without any cards installed.

I/O UNIT ID

PORT B SELECTOR

5-8

1-4

POWER

ON/ OFF

I/O UNIT ID

PORT B SELECTOR

5-8

1-4

POWER

ON/ OFF

DIGITAL IO BOX

12345678

75

IN

ON

OFF

OUT

COM OUTPUT

B (1–4/5–8) A (1–4/1–8)

INPUT

B (1–4/5–8) A (1–4/1–8)

WORD

CLOCK

75

IN

ON

OFF

OUT

OUTPUT

B (1–4/5–8) A (1–4)/(1–8)

INPUT

B (1–4/5–8) A (1–4)/(1–8)

WORD

CLOCK

COM

1

2

3

5

6

7 8

4

1

I/O UNIT ID indicator

2

PORT B SELECTOR switch

3

POWER ON/OFF switch

4

WORD CLOCK IN jack, ON/OFF switch

5

WORD CLOCK OUT jacks

6

COM port

7

OUTPUT connectors A (1-4)/(1-8), B (1-4/5-8)

8

INPUT connectors A (1-4)/(1-8), B (1-4/5-8)

Front Panel

DIO8

Rear Panel

3-2

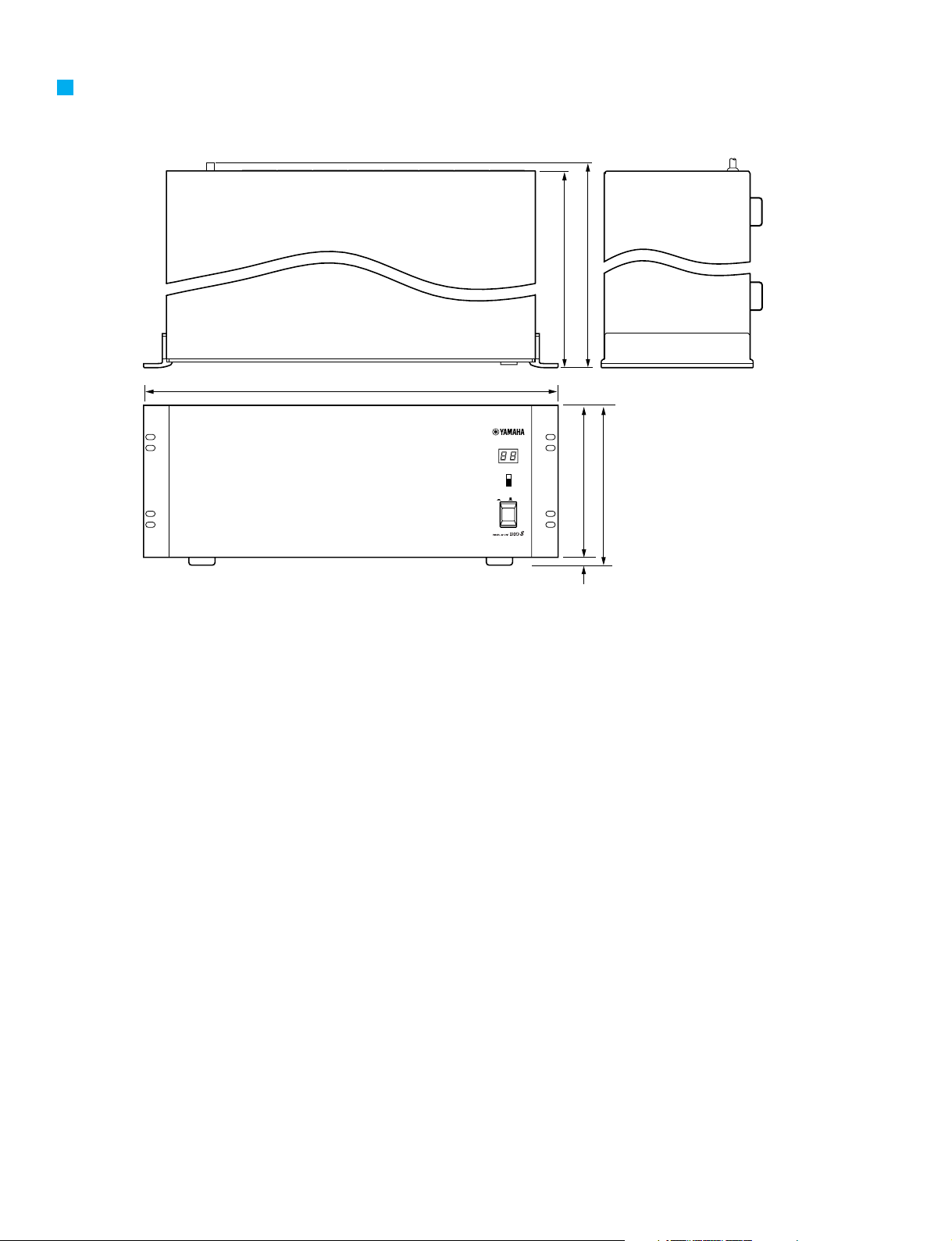

400

411.6

176

480

185.5

I/O UNIT ID

PORT B SELECTOR

5-8

1-4

POWER

ON/ OFF

9.5

DIO8

DIMENSIONS

Unit: mm

3-3

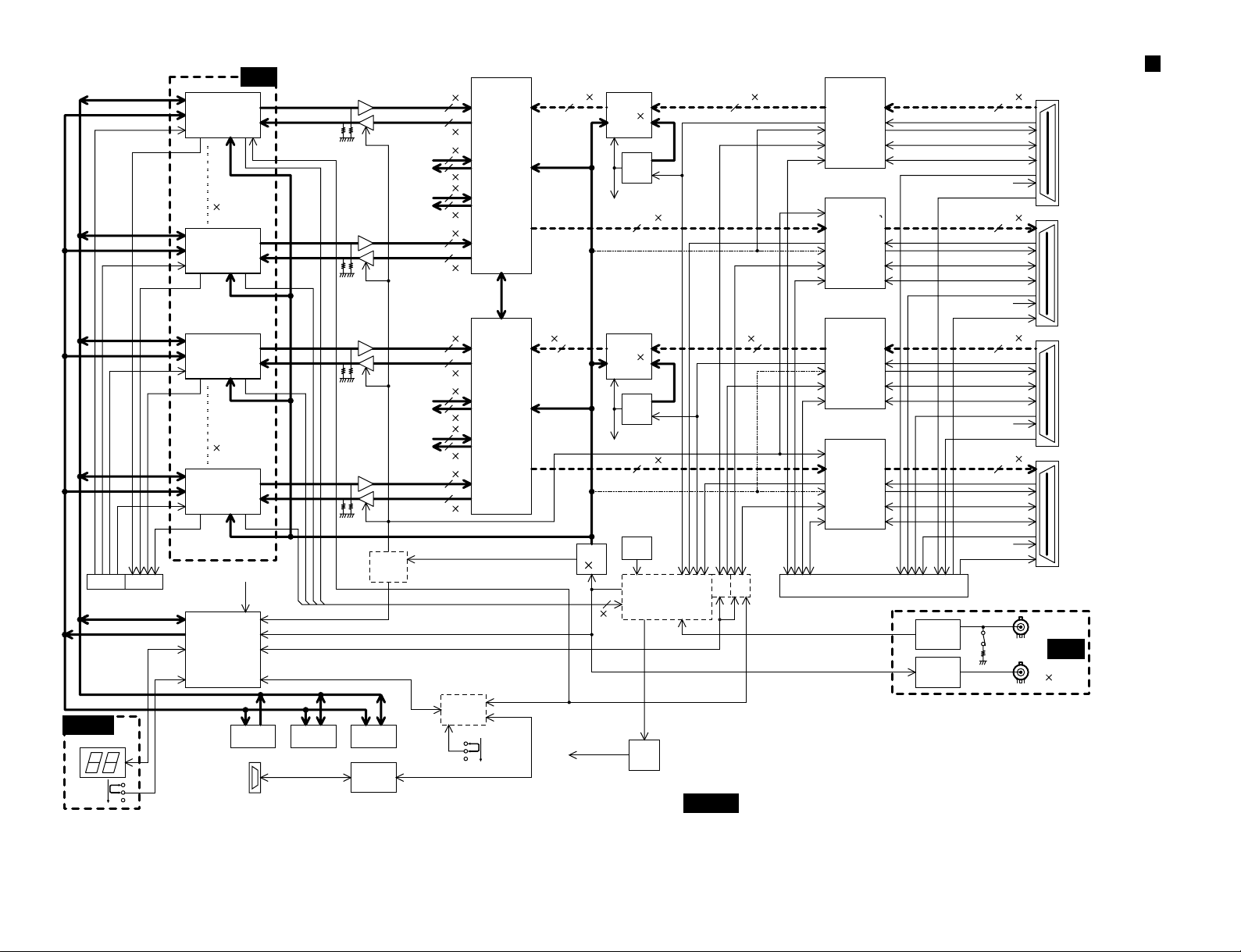

SLOT 1

SLOT 4

SLOT 5

SLOT 8

CN

WC

2ch 4

2ch 4

4

2ch 4

2ch 4

4

2ch 4

2ch 4

2ch or 4ch 16

2ch or 4ch 16

2ch or 4ch 16

2ch or 4ch

16

2 or 4ch

16

2ch or 4ch 16 2ch or 4ch 16

2ch or 4ch 16

2ch or 4ch 16

2ch or 4ch 16

2ch 4

2ch 4

2ch 4

2ch 4

2ch 4

2ch 4

MUTE

MUTE

2ch 4

2ch 4

MUTE

2ch 4

2ch 4

MUTE

Serial (DIO_SLOT1)

Master

CLOCK

Master

CLOCK

Master

CLOCK

Master

CLOCK

Master

CLOCK

Master

CLOCK

Master

CLOCK

4

8

Reg. control, Card IDReg. control, Card ID

PORT B

SEL. SW

SCI

SEL. SW

Slave_LOCK

Serial (DIO_SLOT1)

SCI (DIO_SLOT1/COM)

SCI (Tx_Rx)

Master_WC

Master_LOCK

DATA_bus

ADDRESS_bus

Serial (COM)

UNIT No.

LED3

MAIN

CPU

IC9

ROM RAM

IC13, 14

FLASH

Driver/

Receiver

IC2

IC18

IC104

IC104

COM

FPGA

FPGA

MUTE

UNLOCK

SOFT

POW. OFF

DIO_SLOT1

/COM SEL.

Slave_LOCK

Address

Decoder

Reg.

CS1

:

:

CS8

CON1

:

:

CON8

SLOT_WC[8]

:

:

SLOT_WC[1]

DIR2

IC109

IC104

IC101

IC106, 110

Reg.

Master_WC

Receiver

IC1

Driver

IC2, 3

WC IN

WC OUT

75

Parallel

bus

DSP5

#1

IC201

DSP5

#2

IC202

DIR2

2

INT

48k

44.1K

Slave_LOCK

Slave

LOCK

DIR2

IC108

DIO I/F

ATSC 4

IC307-310

UNLOCK MUTE

Slave_LOCK

Slave

LOCK

DIR2

IC115

DIO I/F

ATSC 4

IC607-610

UNLOCK MUTE

SELSEL

Slave_WC

SLOT_WC[1-8]

FRGA

WC SEL & HDLT

MSB. 2CH OUT

ID OUT

ID IN

OUTPUT B

MUTE

MUTE

MSB. 2CH IN

ID OUT

ID IN

INPUT B

MSB. 2CH IN

ID OUT

ID IN

INPUT A

MSB. 2CH OUT

ID OUT

ID IN

OUTPUT A

Driver/

Recerver

Audio IN

WC IN

WC OUT

Tx, Rx

RTS, DTR

Driver/

Recerver

Audio OUT

WC IN

WC OUT

Tx, Rx

RTS, DTR

Driver/

Recerver

Audio IN

WC IN

WC OUT

Tx, Rx

RTS, DTR

Driver/

Recerver

Audio OUT

WC IN

WC OUT

Tx, Rx

RTS, DTR

IC801-806

IC601-606

IC501-506

IC301-306

KEC-92496

DIO8

4

BLOCK DIAGRAM

DIO8

5

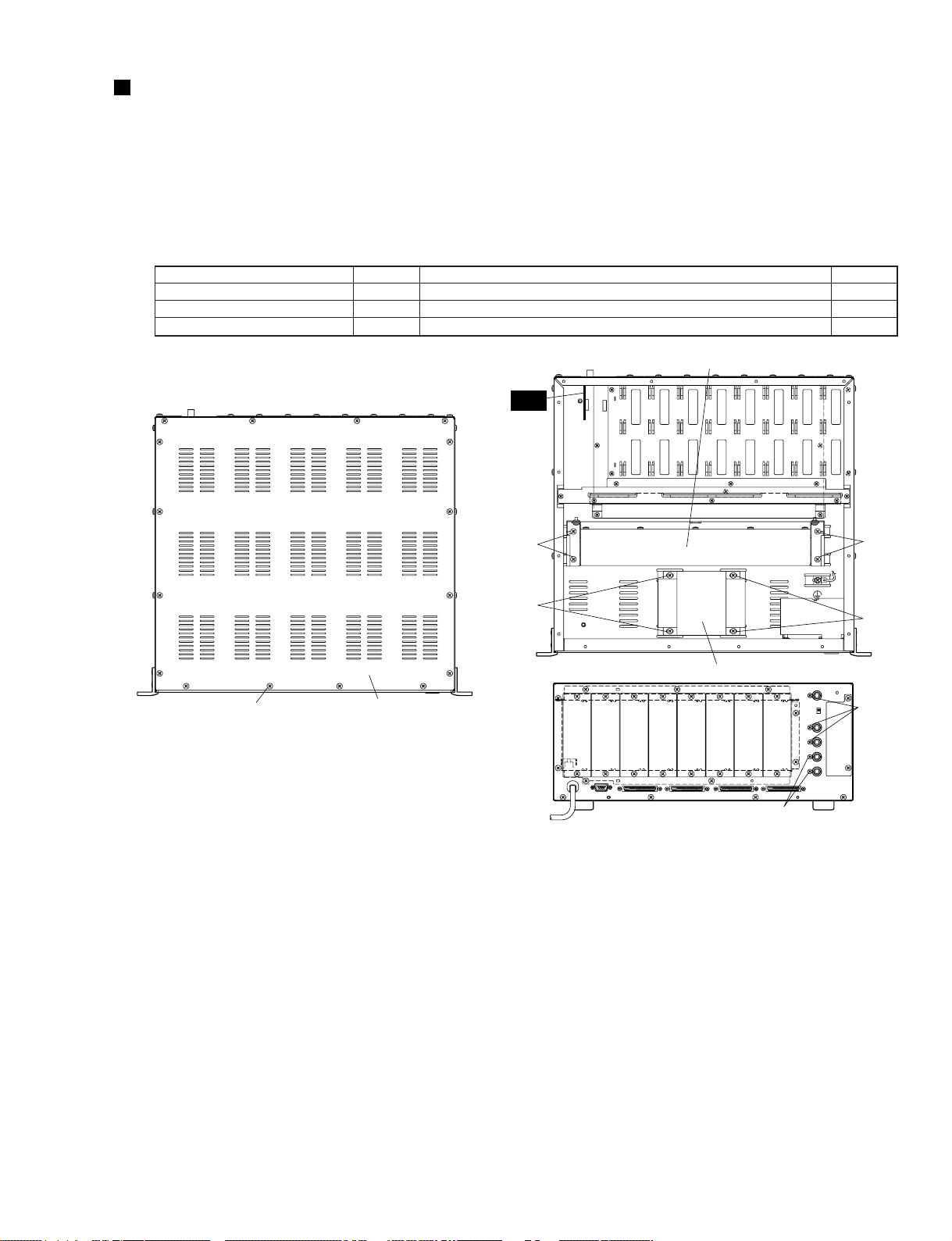

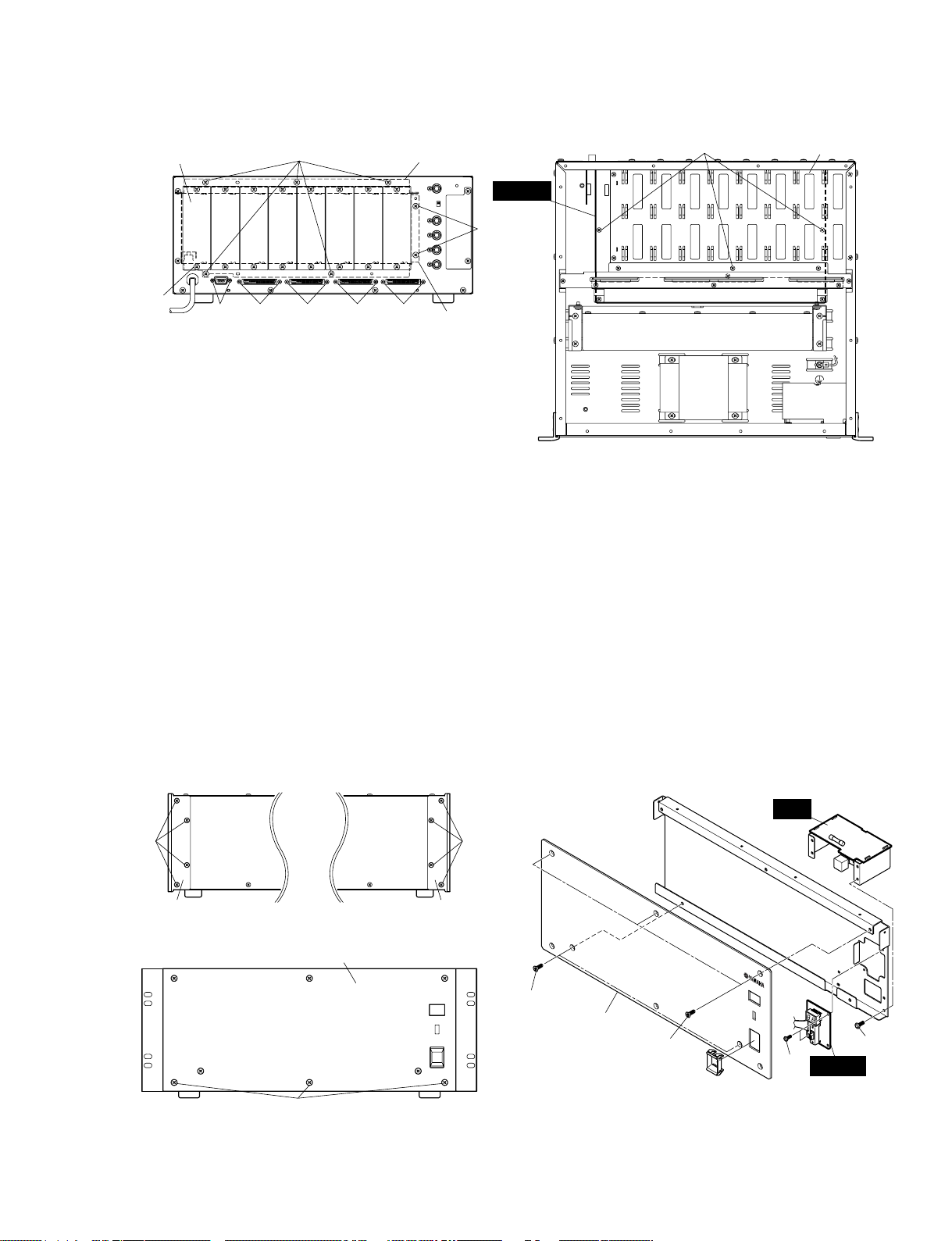

3. DC Circuit Board

3-1 Remove the DC assembly. (See Procedure 2.)

3-2 Remove the four (4) screws marked [80]. The transistor

holder 1 can then be removed. (Fig. 3)

3-3 Remove the five (5) screws marked [100]. The transistor

holder 2 can then be removed. (Fig. 3)

3-4 Remove the three (3) screws marked [50] and the two (2)

screws marked [60]. The DC circuit board can then be

removed. (Fig. 3)

4. CN Circuit Board

* Note that remove all cards before following operation.

4-1 Remove the top cover. (See Procedure 1.)

4-2 Remove the eight (8) screws marked [330]. The angle

bracket can then be removed. (Fig. 4)

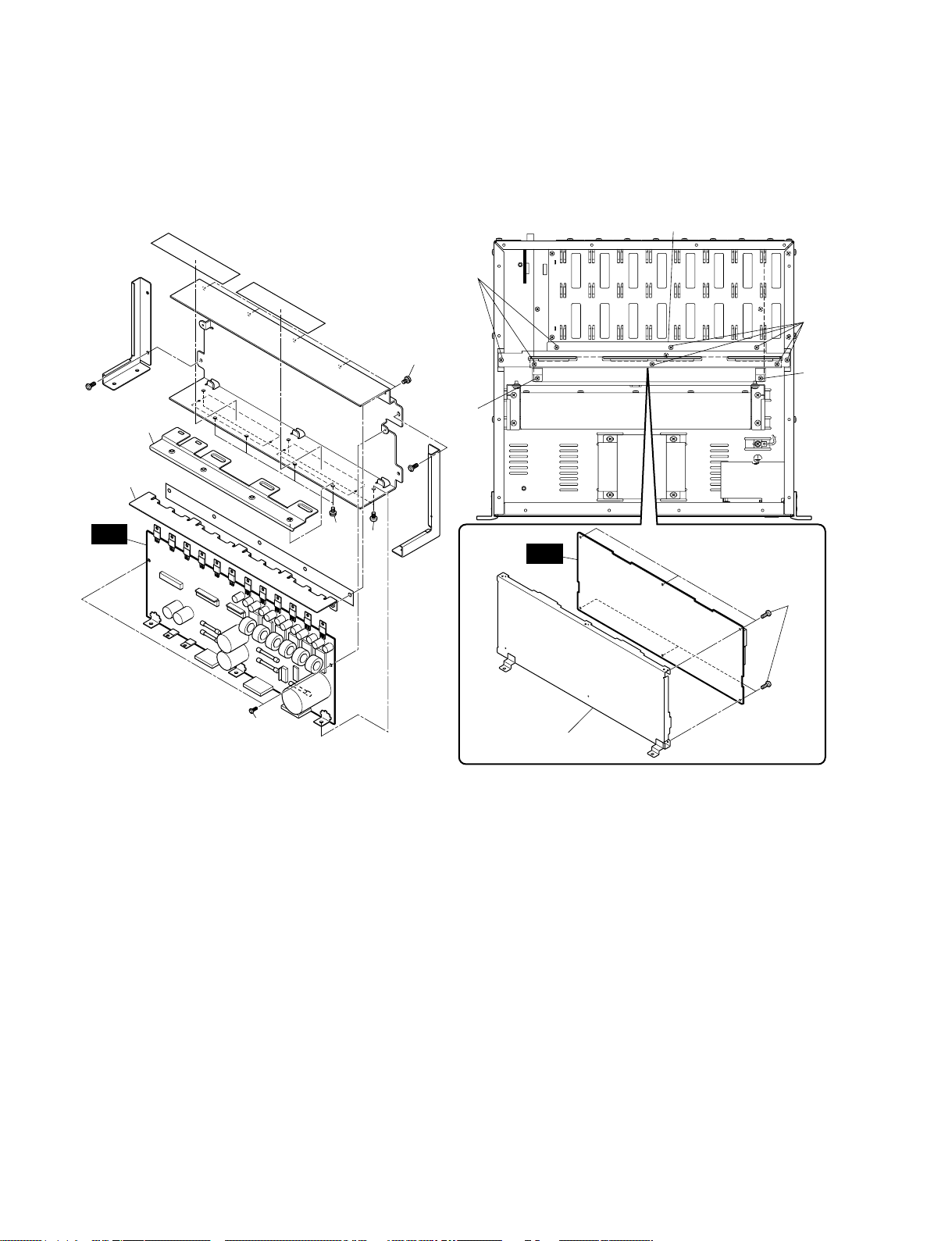

DISASSEMBLY PROCEDURE

DC assembly

Power transformer

[370]

[350]

<Top View>

<Rear View>

<Top View>

Top panel[430] x 16

[220]

[220]

Fig. 1 Fig. 2

[430]: Bind Head Tapping Screw-B A4.0x8 MFZN2BL (VC688800)

WC

[350]

[370]

1. Top Cover

1-1 Remove the sixteen screws (16) marked [430]. The top

cover can then be removed. (Fig. 1)

2. Circuit Boards and Unit

Remove the top cover, each circuit board and unit can

then be removed. (Fig. 2)

Circuit Board and Unit

DC Assembly

Power Transformer

WC

350

370

220

Bind Head Tapping Screw-B A4.0x6 MFZN2BL (VC688800)

Bind Head Tapping Screw-B A4.0x6 MFZN2BL (VC688800)

Flat Head Screw 3.0x6 MFZN2BL (VS863000)

4

4

5

Ref. No. Screw QTY

5. MAIN Circuit Board

5-1 Remove the top cover. (See Procedure 1.)

5-2 Remove the CN circuit board. (See Procedure 4.)

5-3 Remove the sixteen screws (16) marked [450]. The IF

plate can then be removed. (Fig. 5)

5-4 Remove the seven (7) screws marked [260]. The OPT

support can then be removed. (Fig. 5)

5-5 Remove the three (3) screws marked [150]. (Fig. 5)

5-6 Remove the eight (8) screws marked [A] and the two (2)

screws marked [B]. The MAIN circuit board can then be

removed. (Fig. 5)

DIO8

6

• DC Assembly <Top View>

[80]

[100]

[60]

[50]

Transistor holder1

Transistor holder2

Fig. 3

[50]: Bind Head Screw A4.0x8 MFZN2BL (VP156800)

[60]: Bind Head Tapping Screw-B 3.0x8 MFZN2BL (EP600190)

[80]: Pan Head Screw SP 4.0x8 MFZN2Y (EL200020)

[100]: Pan Head Screw SP 4.0x8 MFZN2Y (EL200020)

DC

Angle bracket

[310]

[330]

[310]

[330]

Fig. 4

[290]: Bind Head Tapping Screw-B 3.0x6 MFZN2BL (EP600230)

[310]: Bonding Tapping Screw-B 3.0x8 MFZN2BL (VN413300)

[330]: Bonding Tapping Screw-B 3.0x8 MFZN2BL (VN413300)

[290]

CN

CN support

4-3 Remove the two (2) screws marked [310]. The CN

support can then be removed. (Fig. 4)

4-4 Remove the six (6) screws marked [290]. The CN circuit

board can then be removed. (Fig. 4)

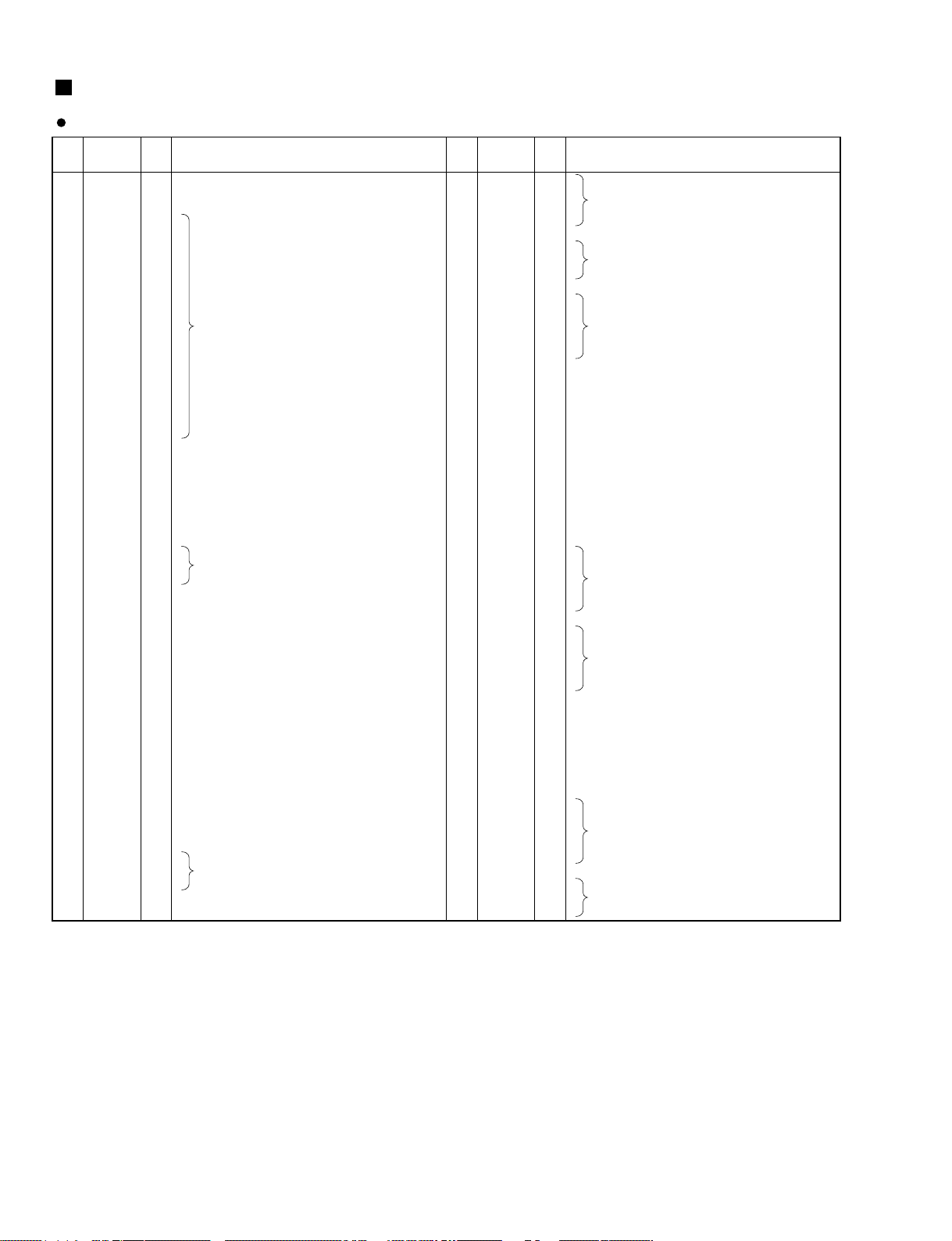

<Right side View>

<Front View>

Front panel assembly

[390]

[410]

Fig. 6 Fig. 7

[390]: Oval Head Screw 4.0x8 MFZN2BL (VS153600)

[410]: Oval Head Screw 4.0x8 MFZN2BL (VS153600)

[60]: Bind Head Tapping Screw-B 3.0x6 MFZN2BL (EP600230)

[80]: Bind Head Tapping Screw-B A4.0x8 MFZN2BL (VC688800)

[100]: Oval Head Screw 4.0x8 MFZN2BL (VS153600)

LED3

AC

Rack mount angle

<Left side View>

[410]

[100]

Rack mount angle

Front panel

• Front Panel Assembly

[100]

[60]

[80] x 4

DIO8

7

<Rear View> <Top View>

Fig. 5

[150]: Bind Head Tapping Screw-B 3.0x6 MFZN2BL (EP600230)

[260]: Bind Head Tapping Screw-B A4.0x8 MFZN2BL (VC688800)

[450]: Bind Head Screw A4.0x12 MFZN2BL (VP156900)

[260]

[450] x 16

[B] [A]

[150]

[260]

OPT support 2

OPT support 2

IF plate

OPT support 1

MAIN

[A] [A] [A]

6. Front Panel Assembly

6-1 Remove the eight (8) screws marked [410]. The rack

mount angle can then be removed. (Fig. 6)

6-2 Remove the three (3) screws marked [390]. The front

panel assembly can then be removed. (Fig. 6)

7. LED3 Circuit Board, AC Circuit Board

7-1 Remove the front panel assembly. (See Procedure 6.)

7-2 Remove th five (5) screws marked [100]. The front panel

can then be removed. (Fig. 7)

7-3 Remove the two (2) screws marked [60]. The LED3

circuit board can then be removed. (Fig. 7)

7-4 Remove the four (4) screws marked [80]. The AC circuit

board can then be removed. (Fig. 7)

DIO8

8

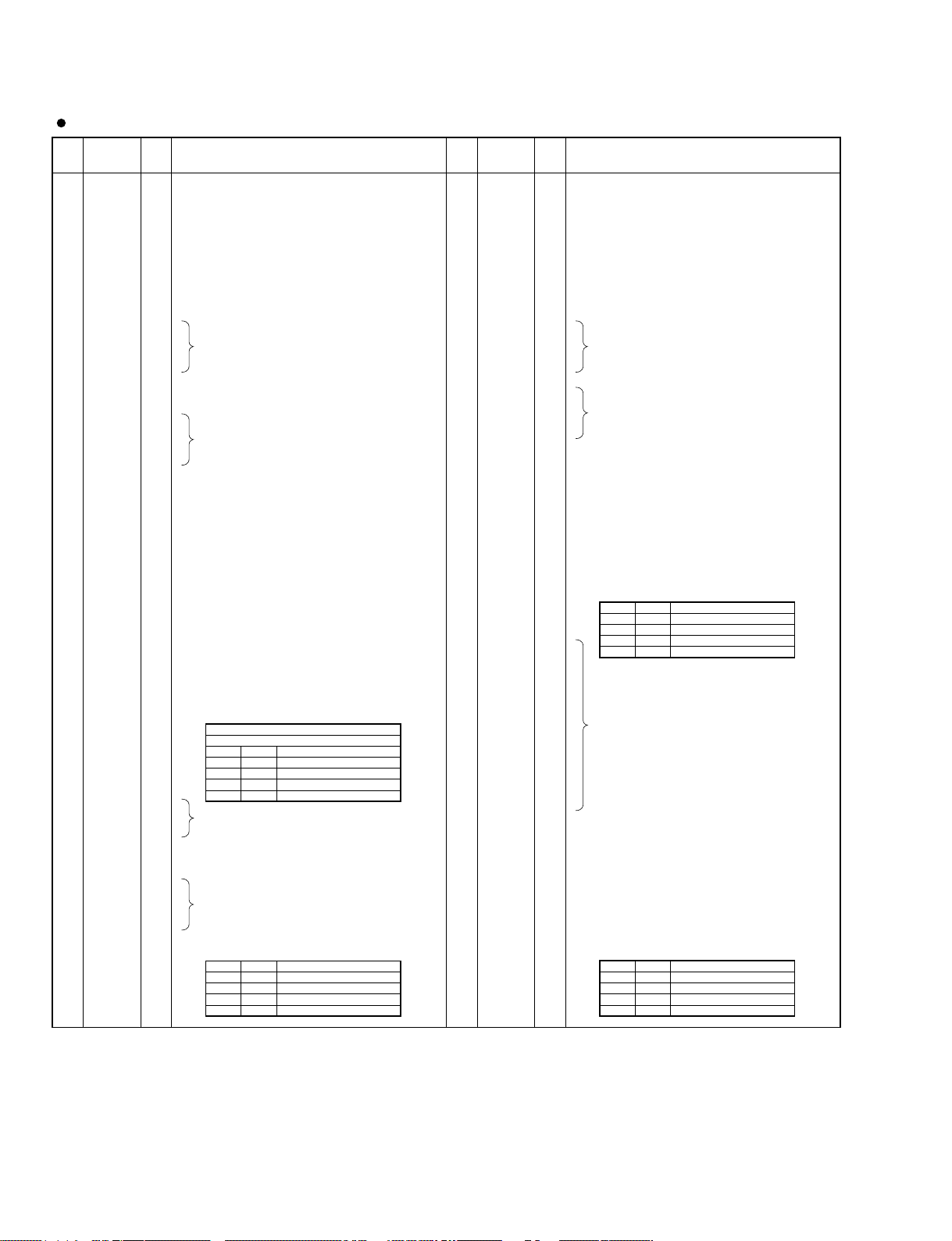

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

PE14

PE15

VSS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

VCC

A17

VSS

/RAS

/CASL

/CASH

VSS

RDWR / PB5

A18

A19

A20

PB9 /A21

VSS

/RD

/WDTOVF

/WRH

VCC

/WRL

VSS

/CS1

/CS0

PA9 / TCLKD

/IRQ2 / TCLKC

/CS3

/CS2

/IRQ1

TXD

RXD

/IRQ0

PA1 / TXD0

PA0 / RXD0

D15

D14

D13

VSS

D12

O

O

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

O

I

O

O

O

O

O

O

O

O

O

I

O

O

O

I

O

I

O

O

O

I

O

O

I

O

I

I

O

I

I/O

I/O

I/O

I

I/O

Port E

Port E

Ground

Address bus

Power supply

Address bus

Ground

Row address strobe

Column address strobe (low)

Column address strobe (high)

Ground

DRAM read/write / Port B

Address bus

Port B / Address bus

Ground

Read

Watch dog timer overflow

High write

Power supply

Low write

Ground

Chip select

Chip select

Port A / Timer clock

Interrupt request / Timer clock

Chip select

Chip select

Interrupt request

Data transmission

Data reception

Interrupt request

Port A / Data transmission

Port A / Data reception

Data bus

Ground

Data bus

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

D11

D10

D9

D8

VSS

D7

D6

D5

VCC

D4

D3

D2

D1

D0

VSS

XTAL

MD3

EXTAL

MD2

NMI

VCC

MD1

MD0

PLLVCC

PLLCAP

PLLVSS

PA15 / CK

/RES

PE0

PE1

PE2

PE3

PE4

VSS

AN0 / PF0

AN1 / PF1

AN2 / PF2

AN3 / PF3

AN4 / PF4

AN5 / PF5

AVSS

AN6 / PF6

AN7 / PF7

AVCC

VSS

PE5

VCC

PE6

PE7

PE8

PE9

PE10

VSS

PE11

PE12

PE13

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

I

I

I

I

I

I

I

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

I

O

O

O

O

O

I

O

O

O

Data bus

Ground

Data bus

Power supply

Data bus

Ground

Crystal oscillator

Mode control

Crystal oscillator

Mode control

Non-maskable interrupt request

Power supply

Mode control

Mode control

PLL Power supply

PLL capacitor

PLL Ground

Port A / Clock

Reset

Port E

Ground

Analog input / Port F

Analog ground

Analog input / Port F

Analog input / Port F

Power supply

Ground

Port E

Power supply

Port E

Ground

Port E

HD6437042AF53F (XY721A00) CPU MAIN: IC009

LSI PIN DESCRIPTION

DIO8

9

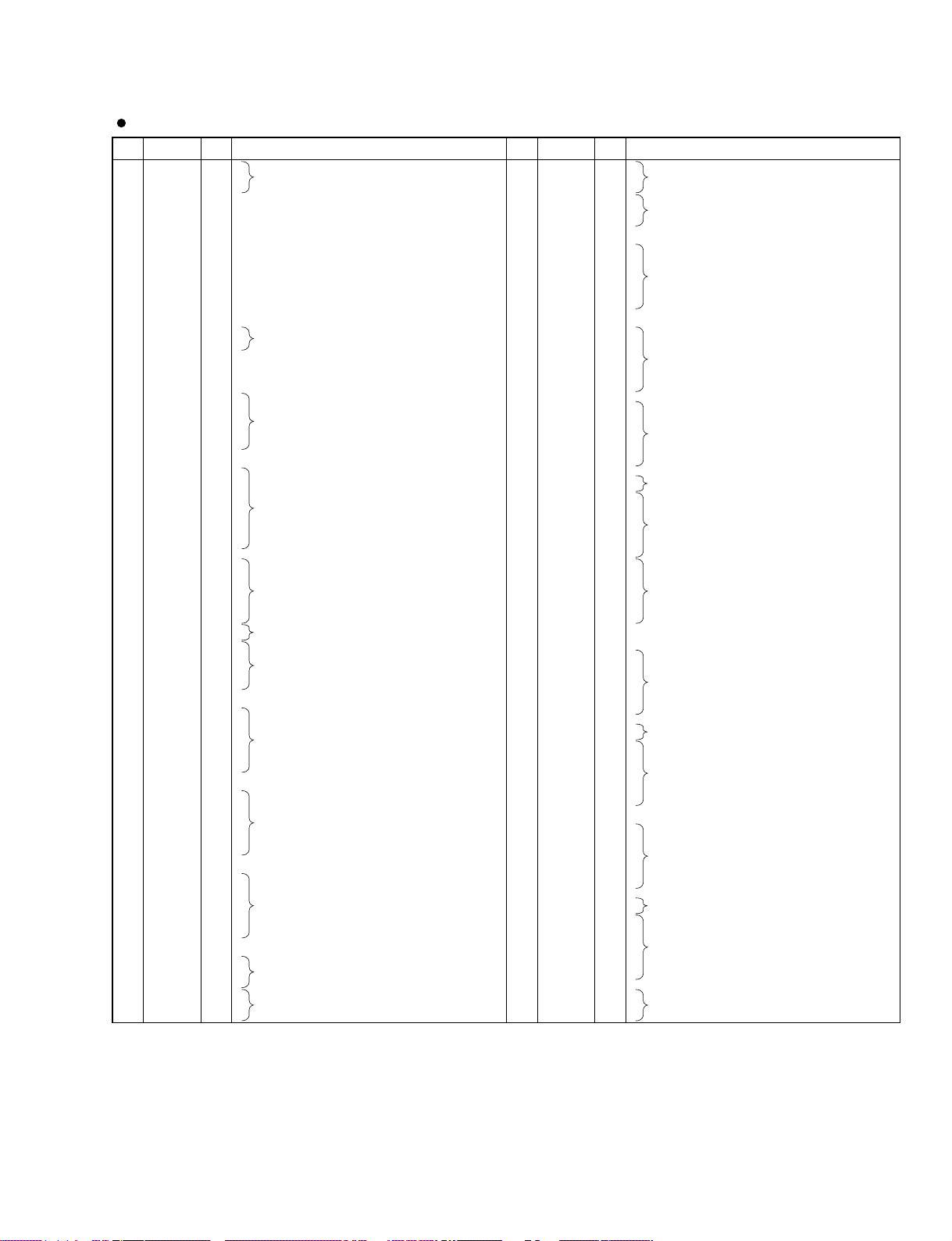

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

DAUX

HDLT

DOUT

VFL

OPT

SYNC

MCC

WC

MCB

MCA

SKSY

XI

XO

P256

LOCK

Vss

TC

DIM1

DIM0

DOM1

DOM0

KM1

I

O

O

O

O

O

O

O

O

O

I

I

O

O

O

O

I

I

I

I

I

Auxiliary input for audio data

Asynchronous buffer operation flag

Audio data output

Parity flag output

Fs x 1 Synchronous output signal for DAC

Fs x 1 Synchronous output signal for DSP

Fs x 64 Bit clock output

FS x 1 Word clock output

Fs x 128 Bit clock output

Fs x 256 Bit clock output

Clock synchronization control input

Crystal oscillator connection or external

clock input

Crystal oscillator connection

VCO oscillating clock connection

PLL lock flag

Logic section power (GND)

PLL time constant switching output

Data input mode selection

Data input mode selection

Data output mode selection

Data output mode selection

Clock mode switching input 1

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

RSTN

Vdda

CTLN

PCO

(NC)

CTLP

Vssa

TSTN

KM2

KM0

FS1

FS0

CSM

EXTW

DDIN

LR

Vdd

ERR

EMP

CD0

CCK

CLD

I

I

O

I

I

I

I

O

O

I

I

I

O

O

O

O

I

I

System reset input

VCO section power (+5V)

VCO control input N

PLL phase comparison output

VCO control input P

VCO section power (GND)

Test terminal. Open for normal use

Clock mode switching input 2

Clock mode switching input 0

Channel status sampling frequency

display output 1

Channel status sampling frequency

display output 0

Channel status output method selection

External synchronous auxiliary input

word clock

EIAJ (AES/EBU) data input

PLL word clock output

Logic section power (+5 V)

Data error flag output

Channel status emphasis control code

output

3-wire type microcomputer interface data

output

3-wire type microcomputer interface clock

input

3-wire type microcomputer interface load

input

YM3436DK (XG948E0) DIR2 (Digital Format Interface Receiver)

MAIN: IC106, 108–110, 115

DIO8

10

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

syncati

mccti

mcbti

VCC

GND

mcati

GND

siat0

siat1

siat2

siat3

ati

GND

ato

soat3

soat2

soat1

soat0

VCC

GND

mcato

GND

mcbto

mccto

syncato

clksel

ato-sel0

ato-sel1

bitsel2

bitsel1

bitsel0

VCC

GND

ext-sync2

ui0

ui1

ui2

ui3

si-sel0

si-sel1

I

I

I

I

I

I

I

I

I

O

O

O

O

O

I

I

I

I

I

I

I

Synch. word input terminal for ati,

siat3-0 input

64 fs clock input terminal for ati,

siat3-0 input

128 fs clock input terminal for ati,

siat3-0 input

Power supply (+5 V)

Ground

256 fs clock input terminal for ati,

siat3-0 input

Ground

Serial data input terminal

Optical input terminal

Ground

Optical output terminal

Serial data output terminal

Power supply (+5 V)

Ground

256 fs clock input terminal for ato,

soat3-0 output

Ground

128 fs clock input terminal for ato,

soat3-0 output

64 fs clock input terminal for ato,

soat3-0 output

Synch. word input terminal for ato,

soat3-0 output

Clock select terminal for ato,

soat 3-0 output

0: mcato,mcbto,mccto,syncato

1: mcai,mcbi,mcci,synci

Format select terminal for ato,

soat3-0 output

Format select terminal for ato,

soat3-0 output

Bit shift select terminal for the ato output

Power supply (+5 V)

Ground

Synch. detect output terminal 2

U-bit input terminal for optical output

input format select terminal for si3-0

input format select terminal for si3-0i

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

synci

mcci

mcbi

VCC

GND

mcai

GND

si0

si1

si2

si3

GND

so3

so2

so1

so0

VCC

GND

mcao

GND

mcbo

mcco

synco

so-sel1

so-sel0

uo3

uo2

uo1

uo0

ext-sync1

VCC

GND

clk

GND

/res

GND

wc-at

mute

ati-sel1

ati-sel0

I

I

I

I

I

I

I

I

O

O

O

O

I

I

I

I

I

I

O

O

O

O

O

I

I

O

I

I

I

Synch. word input terminal for si3-0 input

64 fs clock input terminal for si3-0 input

128 fs clock input terminal for si3-0 input

Power supply (+5 V)

Ground

256 fs clock input terminal for si3-0 input

Ground

Serial data input terminal

Ground

Serial data output terminal

Power supply (+5 V)

Ground

256 fs clock input terminal for so3-0 output

Ground

128 fs clock input terminal for so3-0 output

64 fs clock input terminal for so3-0 output

Synch. word input terminal for so3-0 output

Format select terminal for soat3-0 output

Format select terminal for soat3-0 output

U-bit output terminal for optical output

Synch. detect output terminal 1

Power supply (+5 V)

Ground

Clock input terminal for word clock extract

Ground

System reset input terminal

Ground

Word clock output terminal

Data mute input terminal

Input format select terminal for ati, siat3-0.

input format select terminal for ati, siat3-0.

SGH609080F-47F (XU235A00) ATSC

MAIN: IC307–310, 607–610

1

1

0

0

so sel1

1

0

1

0

so sel0

not enable to set

so0

so2, 0

so3-0

(8ch/line)

(4ch/line)

(2ch/line)

input format

1

1

0

0

ati sel1

1

0

1

0

ati sel0

ati

ati0

ati2, 0

ati3-0

(8ch/line)

(4ch/line)

(2ch/line)

input format

1

1

0

0

ato sel1

0: mcato,mcbto,mccto,syncato

1: mcai,mcbi,mcci,synci

1

0

1

0

ato sel0

ato

soat0

soat2, 0

soat3-0

(8ch/line)

(4ch/line)

(2ch/line)

output format

1

1

0

0

si sel1

1

0

1

0

si sel0

not enable to set

si0

si2, 0

si3-0

(8ch/line)

(4ch/line)

(2ch/line)

input format

DIO8

11

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

NC

NC

NC

NC

Vdd

Vss

XI

XO

Vdd

/SYNCI

/SYNCO

Vdd

CKI

CKO

CKSEL

Vss

MCKD

/SSYNC

/IC

/TEST

NC

NC

NC

Vdd

Vss

/CS

/WR

/RD

CA7

CA6

CA5

CA4

CA3

CA2

CA1

Vss

Vdd

CD15

CD14

CD13

CD12

CD11

CD10

CD09

CD08

CD07

CD06

Vss

NC

NC

NC

NC

NC

NC

NC

NC

Vdd

Vdd

CD05

CD04

CD03

CD02

CD01

CD00

/WAIT

Vss

SIO00

SIO01

SIO02

SIO03

SIO04

SIO05

SIO06

SIO07

Vss

Vdd

SIO08

SIO09

SIO10

SIO11

SIO12

SIO13

SIO14

SIO15

Vss

Vdd

SIO16

SIO17

SIO18

SIO19

SIO20

SIO21

SIO22

SIO23

Vss

Vdd

SIO24

SIO25

SIO26

SIO27

NC

NC

NC

NC

I

O

O

I

O

I

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Not used

Ground

Power supply

System master clock input (60 MHz or 30 MHz)

System master clock output (High or 30 MHz)

Ground

Sync. signal input

Sync. signal output

Ground

System clock input (30 MHz)

System clock output (30 MHz)

System master clock select

Power supply

Serial clock input (256 fs)

Serial. signal input

Initial clear

Test mode setting (0: TEST, 1: Normal)

Not used

Ground

Power supply

Chip select

Write enable input

Read enable input

CPU address bus

Power supply

Ground

CPU data bus

Power supply

Not used

Ground

CPU data bus

Wait output

Power supply

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Ground

Serial data bus

Not used

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

NC

NC

NC

NC

SIO28

SIO29

SIO30

SIO31

Vss

Vdd

SIO32

SIO33

SIO34

SIO35

SIO36

SIO37

SIO38

SIO39

Vss

Vdd

SIO40

SIO41

SIO42

SIO43

SIO44

SIO45

SIO46

SIO47

Vss

SIO48

SIO49

SIO50

SIO51

SIO52

SIO53

SIO54

SIO55

Vss

Vdd

Vdd

SIO56

SIO57

SIO58

SIO59

SIO60

SIO61

SIO62

SIO63

NC

NC

NC

NC

NC

NC

NC

NC

Vss

/POE

Vss

PIO00

PIO01

PIO02

PIO03

PIO04

PIO05

PIO06

PIO07

Vss

Vdd

Vdd

PIO08

PIO09

PIO10

PIO11

PIO12

PIO13

PIO14

PIO15

Vss

NC

PIO16

PIO17

PIO18

PIO19

PIO20

PIO21

PIO22

PIO23

Vss

Vdd

Vdd

PIO24

PIO25

PIO26

PIO27

PIO28

PIO29

PIO30

PIO31

Vss

NC

NC

NC

NC

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Not used

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Serial data bus

Power supply

Ground

Serial data bus

Not used

Power supply

Parallel data bus controll signal

Power supply

Parallel data bus

Power supply

Ground

Parallel data bus

Power supply

Not used

Parallel data bus

Power supply

Ground

Parallel data bus

Power supply

Not used

YSS904-F (XV989A00) DSP5 (Digital Signal Processor)

MAIN: IC201, 202

1

2

3

1A

1Y

42A

52B

62Y

7

VSS

1B

14

13

12

VDD

4A

11 4Y

10 3B

9 3A

8 3Y

4B

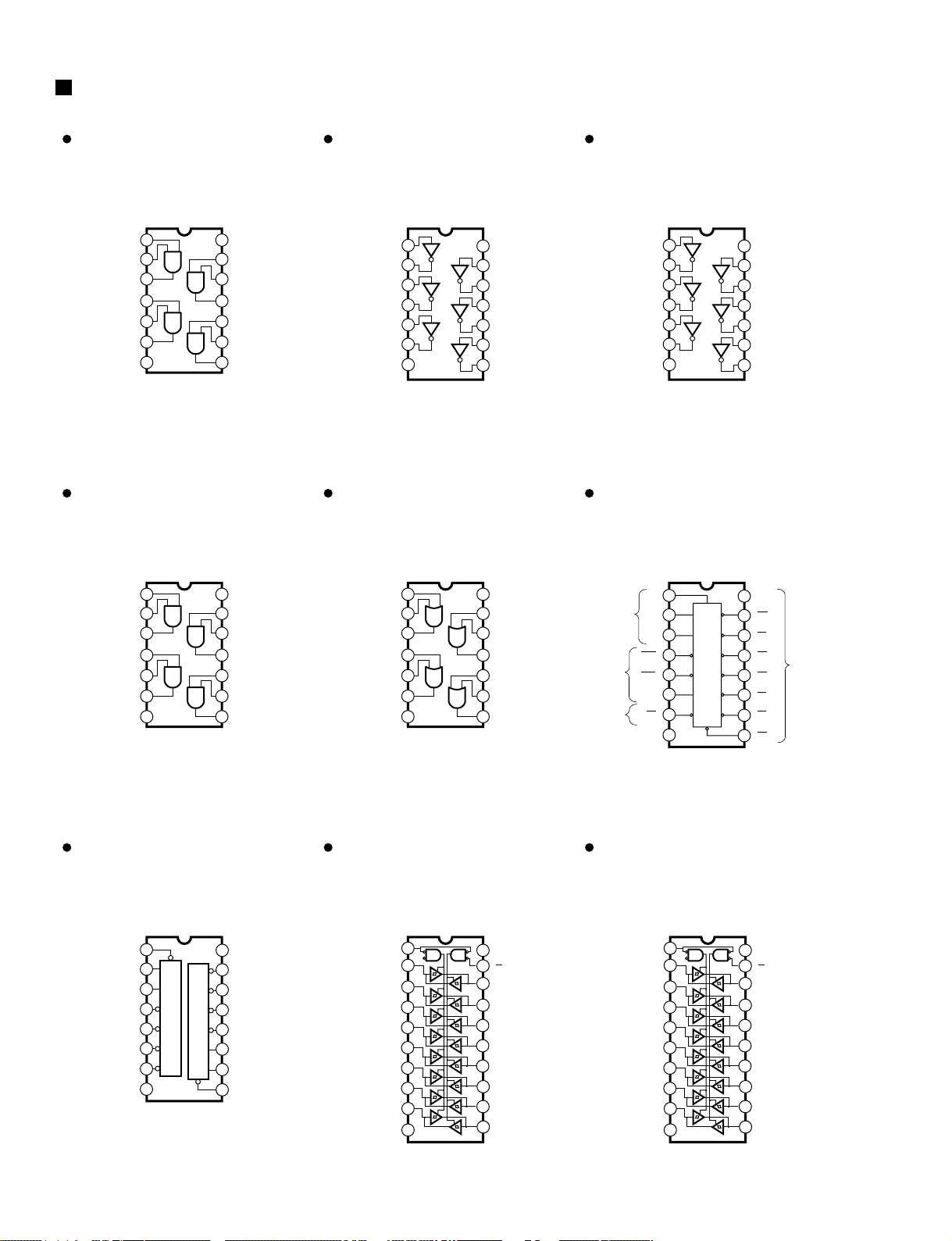

HD74LV00AFPEL (IS000000)

Quad 2 Input NAND

MAIN: IC118

HD74LVU04AFPEL (XY102A00)

Hex Inverter

MAIN: IC101

HD74LV04AFPEL (IS000400)

Hex Inverter

MAIN: IC107

HD74LV08AFPEL (IS000800)

Quad 2 Input AND

MAIN: IC8, 119

HD74LV32AFPEL (IS003200)

Quad 2 Input OR

MAIN: IC16, 17

SN74LV138ANSR (IS013810)

3 to 8 Demultiplexer

MAIN: IC10, 11

SN74LV139ANSR (IS013910)

Dual 2 to 4 Demultiplexer

MAIN: IC24

HD74LV245AFPEL (IS024500)

Octal 3-State Bus Transceiver

MAIN: IC1, 3-6, 19-22, 30-35, 103,

112-114, 203,210

TC74HC245AF (XS720A00)

Octal 3-State Bus Transceiver

MAIN: IC25-29

1

2

3

4

5

6

7

1A

1Y

2A

2Y

3A

3Y

Vss

14

13

12

11

10

9

8

VDD

6A

6Y

5A

5Y

4A

4Y

1

2

3

4

5

6

7

1A

1Y

2A

2Y

3A

3Y

Vss

14

13

12

11

10

9

8

VDD

6A

6Y

5A

5Y

4A

4Y

1

2

3

1A

1Y

42A

52B

62Y

7

VSS

1B

14

13

12

VDD

4A

11 4Y

10 3B

9 3A

8 3Y

4B

1

2

3

1A

1Y

42A

52B

62Y

7GND

1B

14

13

12

Vcc

4A

11 4Y

10 3B

9 3A

8 3Y

4B

1

2

3

4

5

6

7

A

A

Select

Enable

Output

Output

B

B

C

C

G2A

G2A

G2B

G2B

G1

G1

Y7

Y7 Y5

Y4

Y3

Y2

Y1

Y0

Y6

16

15

14

13

12

11

10

Vcc

YO

Y1

Y2

Y3

Y4

Y5

8

GND

9

Y6

1

2

3

4

5

6

7

1G

1A

1B

1Y0

1Y1

1Y2

1Y3

A

G

B

Y0

Y1

Y2

Y3

16

15

14

13

12

11

10

Vcc

2G

2A

2B

2Y0

2Y1

2Y2

8

GND

9

2Y3

Y2

Y3

Y1

Y0

B

A

G

1

2

3

4

5

6

7

20

19

18

17

16

15

14

Vcc

G

B1

B2

B3

B4

B5

B6

B7

B8

8

9

10

12

11

GND

A8

A7

A6

A5

A4

A3

A2

A1

D1R

13

1

2

3

4

5

6

7

20

19

18

17

16

15

14

Vcc

G

B1

B2

B3

B4

B5

B6

B7

B8

8

9

10

12

11

GND

A8

A7

A6

A5

A4

A3

A2

A1

D1R

13

DIO8

12

IC BLOCK DIAGRAM

DIO8

13

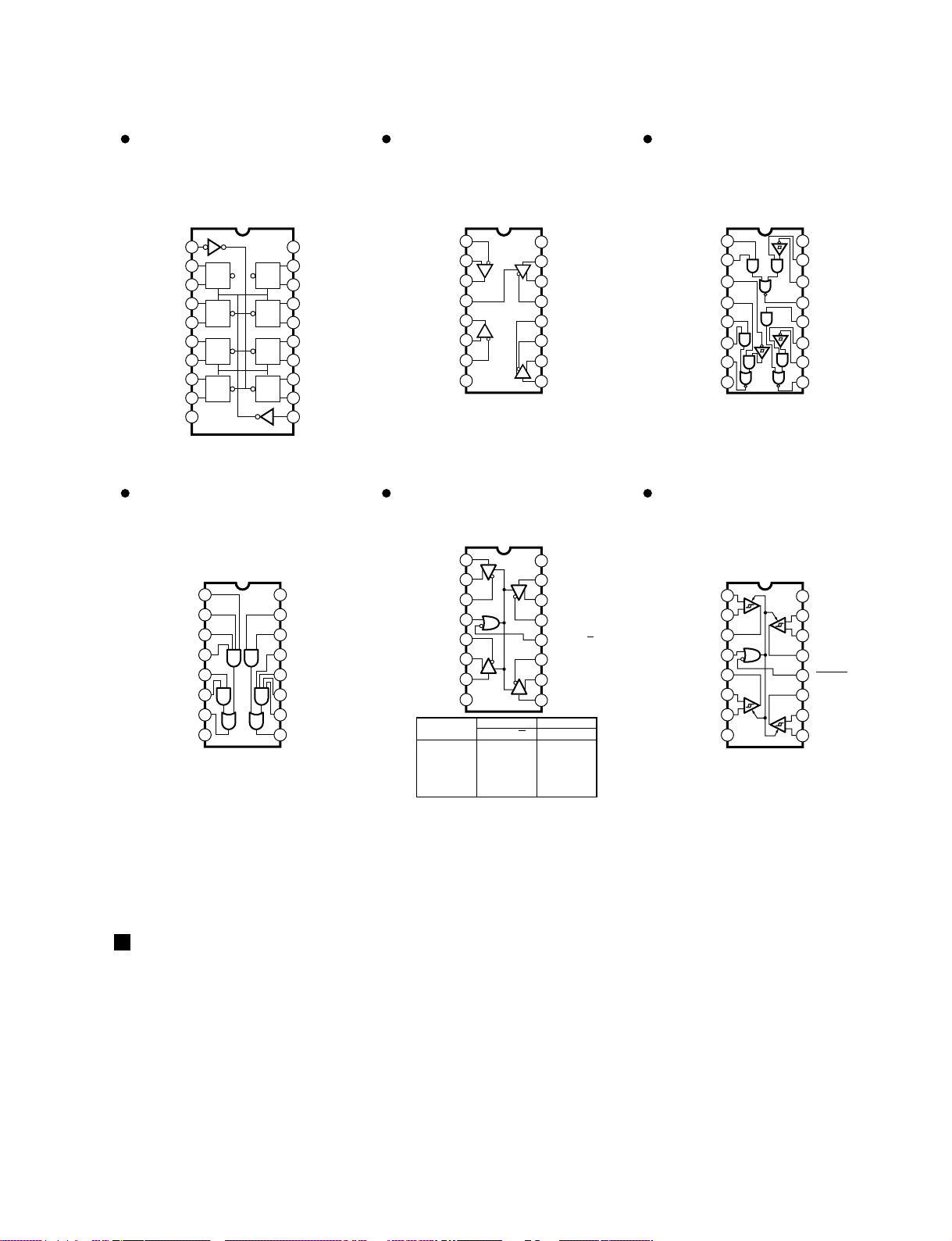

HD74LV273AFPEL (IS027300)

Octal D-Type Flir Flop

MAIN: IC7, 15

SN75C1168NSR (XU073A00)

Line Driver / Receiver

MAIN: IC2

SN75124NS (XN976A00)

Triple Line Receiver

WC: IC1

SN75121NSR (XU816A00)

Dual Line Driver

WC: IC2, 3

AM26LS31CNSR (XU996A00)

Quad Line Driver

MAIN: IC301, 501-505, 601, 801-805

DS26C32ATMX (XU815A00)

Quad Differential Line Receiver

MAIN: IC302-306, 506, 602-606, 806

1

2

3

4

5

6

7

1B

1A

1R

1DE

2R

2A

2B

16

15

14

13

12

11

10

Vcc

1D

1Y

1Z

2DE

2Z

2Y

8

GND

9

2D

1A

1B

2R

2S

2A

2B

2Y

GND

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

Vcc

1S

1R

1Y

3A

3S

3R

3Y

CLEAR

1Q

1D

2D

2Q

3Q

3D

4D

4Q

GND

VCC

8Q

8D

7D

7Q

6Q

6D

5D

5Q

CLOCK

1 20

2 19

3 18

4 17

5 16

6 15

7 14

8 13

9 12

10 11

Q

DCK

CL

D

Q

CK

CL

Q

DCK

CL

D

Q

CK

CL

D

Q

CK

CL

Q

DCK

CL

D

Q

CK

CL

Q

DCK

CL

Vcc

2F

2E

2A

2Y

GND

1Y

2C

2B

2D

1A

1B

1C

1D

1E

1F

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

1A

1Y

1Z

2Z

2Y

2A

GND

ENABLE G

16

15

14

13

12

11

Vcc

4A

4Y

4Z

ENABLE G

3Z

3Y

8

9

10

3A

H= high level

L= low level

X= irrelevant

Z= high impedance (off)

OUTPUTSENABLESINPUT

A

GGYZ

H

H

X

X

L

X

X

L

L

H

H

L

H

L

Z

L

H

L

H

Z

H

L

H

L

X

1

2

3

4

5

6

7

INPUT A

INPUT A

OUTPUT A

OUTPUT C

INPUT C

INPUT C

GND

ENABLE

16

15

14

13

12

11

Vcc

INPUT B

INPUT B

OUTPUT B

ENABLE

OUTPUT D

INPUT D

8

9

10

INPUT D

+

-

-

+

+

-

+

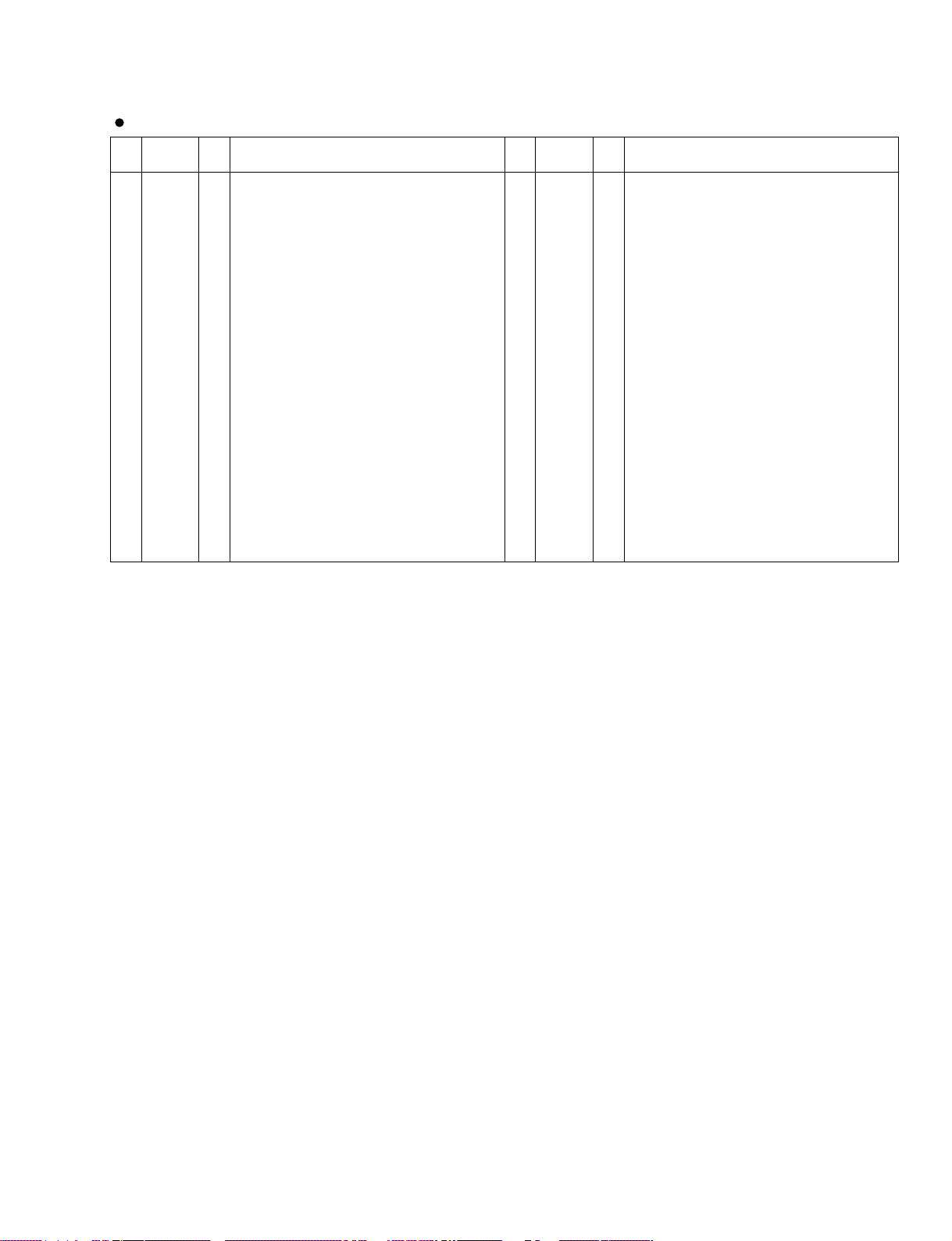

CIRCUIT BOARDS CONTENTS

AC Circuit Board (XW293B0)····················································································· 18

CN Circuit Board (XW283B0)····················································································· 17

DC Circuit Board (XW282A0)····················································································· 16

LED3 Circuit Board (XW286B0)················································································· 18

MAIN Circuit Board (XW293B0)················································································· 14

WC Circuit Board (XW293B0)···················································································· 18

Note: See parts list for details of circuit board component parts.

3NA-V446020

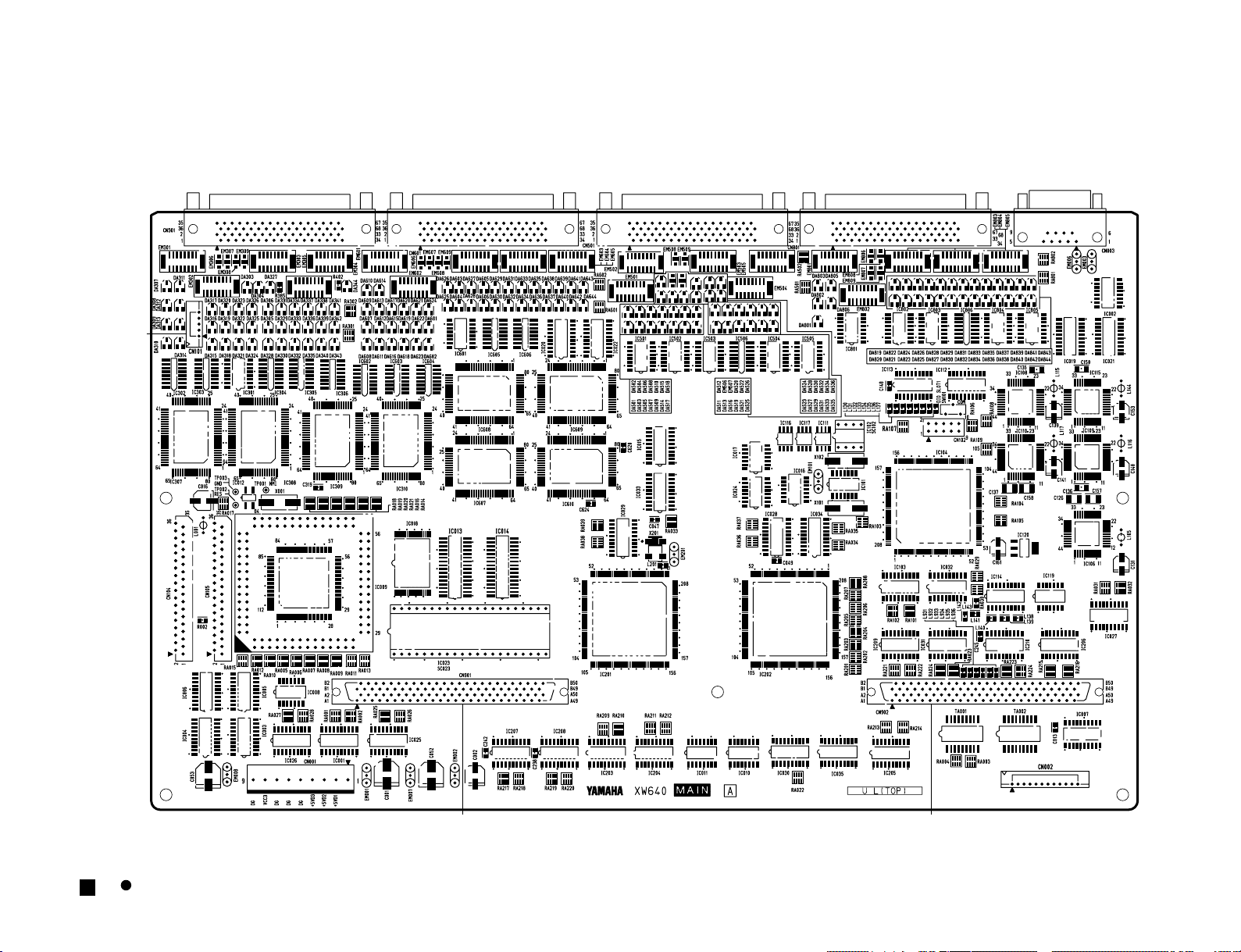

Component side

to WC-CN001

INPUT A INPUT B OUTPUT A OUTPUT B COM

from DC-CN401 to CN-CN909 to LED3-CN100

MAIN Circuit Board

to CN-CN910

DIO8

14

CIRCUIT BOARDS

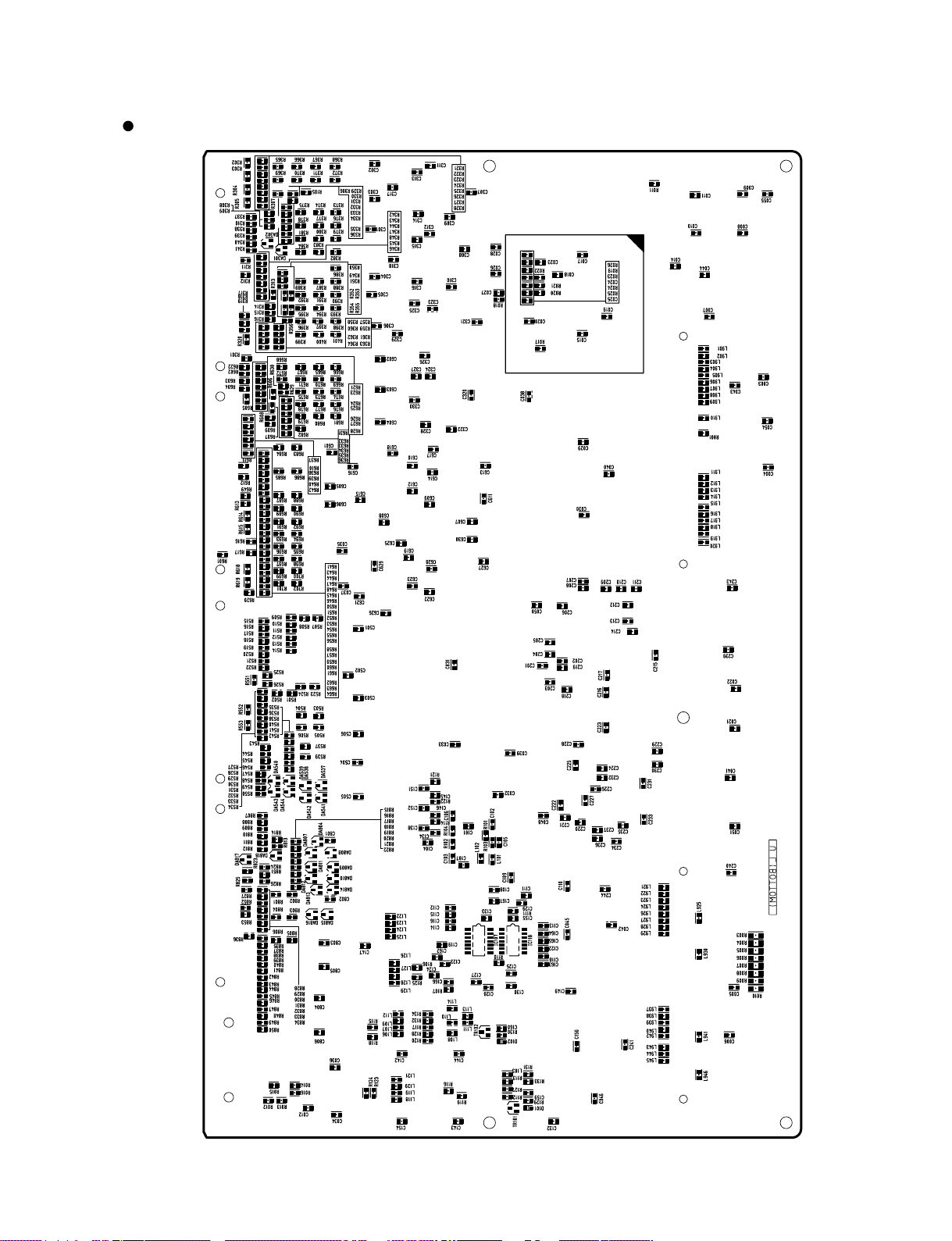

3NA-V446020

Pattern side

MAIN Circuit Board

DIO8

15

Loading...

Loading...