Page 1

Virtex-4 LX/SX

Prototype Platform

User Guide

UG078 (v1.2) May 24, 2006

P/N 0402226-06

R

Page 2

R

Xilinx is disclosing this Document and Intellectual Property (hereinafter “the Design”) to you for use in the development of designs to operate

on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished,

downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical,

photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright

laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents,

copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the

Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx

assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any

liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED “AS IS” WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS

WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR

ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER

EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY,

FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL

DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN,

EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN

CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT

EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT

THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE

AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring failsafe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or

weapons systems (“High-Risk Applications”). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk

Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2004-2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx,

Inc. All other trademarks are the property of their respective owners.

Revision History

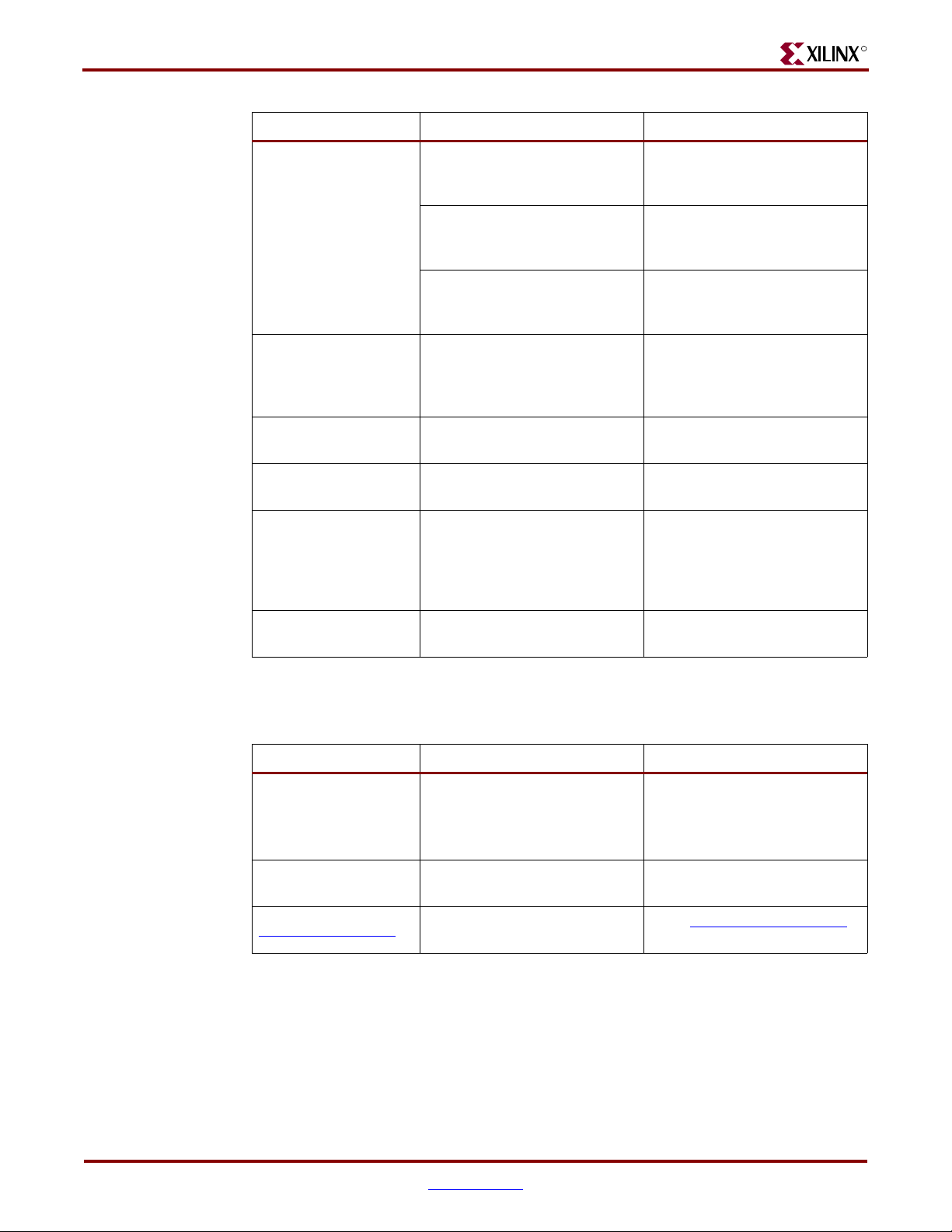

The following table shows the revision history for this document.

Date Version Revision

08/30/04 1.0 Initial Xilinx release.

10/20/04 1.0.1 Minor corrections to text and figures.

06/09/05 1.0.2 Modified title from Virtex-4 Prototype Platform to Virtex-4 LX/SX Prototype Platform.

Updated figure titles and Table 8, Table 9, and Table 10.

06/27/05 1.0.3 Corrected clock names in Table 6 (pin W9) and Table 7 (pins H17, AJ17, and AK19).

05/05/06 1.1 Corrected title of Table 7.

05/24/06 1.2 Updated title of Table 5 and Table 7.

Added revision number to P/N on title page.

Virtex-4 LX/SX Prototype Platform www.xilinx.com UG078 (v1.2) May 24, 2006

Page 3

Table of Contents

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Typographical. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Online Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Virtex-4 LX/SX Prototype Platform

Package Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

CD-ROM Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Detailed Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1. Power Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2. Power Supply Jacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3. Configuration Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4. JTAG Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5. JTAG Termination Jumper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

6a. Upstream System ACE Interface Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6b. Downstream System ACE Interface Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6c. Upstream Interface Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6d. Downstream Interface Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

7. Prototyping Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

8. VCCO-Enable Supply Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

9. VBATT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

10. Oscillator Sockets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

11. Differential Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

12. DUT Socket . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

13. Pin Breakout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

14. User LEDs (Active-High) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

15. PROGRAM Switch. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

16. RESET Switch (Active-Low) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

17. DONE LED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

18. INIT LED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

19. Platform Flash ISPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Virtex-4 LX/SX Prototype Platform www.xilinx.com 3

UG078 (v1.2) May 24, 2006

Page 4

R

4 www.xilinx.com Virtex-4 LX/SX Prototype Platform

UG078 (v1.2) May 24, 2006

Page 5

R

About This Guide

This user guide describes the features and operation of the Virtex™-4 prototype platform

and describes how to configure chains of FPGAs and serial PROMs.

Guide Contents

This manual contains one chapter:

• “Virtex-4 LX/SX Prototype Platform”

Additional Resources

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/literature/index.htm.

Preface

Conventions

Typographical

To search the Answer Database of silicon, software, and IP questions and answers, or to

create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

This document uses the following conventions. An example illustrates each convention.

The following typographical conventions are used in this document:

Convention Meaning or Use Example

Messages, prompts, and

Courier font

Courier bold

Helvetica bold

program files that the system

displays

Literal commands that you enter

in a syntactical statement

Commands that you select from

a menu

Keyboard shortcuts Ctrl+C

speed grade: - 100

ngdbuild design_name

File → Open

Virtex-4 LX/SX Prototype Platform www.xilinx.com 5

UG078 (v1.2) May 24, 2006

Page 6

Preface: About This Guide

Italic font

Square brackets [ ]

Convention Meaning or Use Example

Variables in a syntax statement

for which you must supply

ngdbuild design_name

values

See the Development System

References to other manuals

Reference Guide for more

information.

If a wire is drawn so that it

Emphasis in text

overlaps the pin of a symbol, the

two nets are not connected.

An optional entry or parameter.

However, in bus specifications,

such as bus[7:0], they are

ngdbuild [option_name]

design_name

required.

R

Braces { }

Vertical bar |

Vertical ellipsis

Horizontal ellipsis . . .

Online Document

The following conventions are used in this document:

Convention Meaning or Use Example

Blue text

Red text

A list of items from which you

must choose one or more

Separates items in a list of

choices

lowpwr ={on|off}

lowpwr ={on|off}

IOB #1: Name = QOUT’

.

.

Repetitive material that has

been omitted

.

Repetitive material that has

been omitted

IOB #2: Name = CLKIN’

.

.

.

allow block block_name

loc1 loc2 ... locn;

See the section “Additional

Cross-reference link to a location

in the current document

Resources” for details.

Refer to “Title Formats” in

Chapter 1 for details.

Cross-reference link to a location

in another document

See Figure 2-5 in the Virtex-II

Handbook.

Blue, underlined text

6 www.xilinx.com Virtex-4 LX/SX Prototype Platform

Hyperlink to a website (URL)

Go to http://www.xilinx.com

for the latest speed files.

UG078 (v1.2) May 24, 2006

Page 7

R

Virtex-4 LX/SX Prototype Platform

Package Contents

• Xilinx Virtex™-4 prototype platform board

• User guide

• Device vacuum tool

• Headers for test points

• CD-ROM

• One low-voltage, 14-pin, dual-inline package (DIP) crystal oscillator

CD-ROM Contents

• User guide in PDF format

• Example designs

♦ These designs include the Verilog source code, user constraints files (*.ucf),

documentation in PDF, and a readme.txt file

• Bitstream files (*.bit) for each part type supported by the board (Bitstream synthesized

using Xilinx tools)

• Full schematics of the board in both PDF format and ViewDraw schematic format

• PC board layout in Pads PCB format

• Gerber files in *.pho and *.pdf for the PC board (There are many free or shareware

Gerber file viewers available on the Web for viewing and printing these files)

Introduction

The Virtex-4 prototype platform and demonstration boards allow designers to investigate

and experiment with the features of Virtex-4 series FPGAs. This user guide describes the

features and operation of the Virtex-4 prototype platform, including how to configure

chains of FPGAs and serial PROMs.

Note:

and are not intended for A/C characterization or high-speed I/O evaluation.

Virtex-4 LX/SX Prototype Platform www.xilinx.com 7

UG078 (v1.2) May 24, 2006

Prototype platforms are intended strictly for evaluating the functionality of Virtex-4 features

Page 8

Introduction

Features

R

• Independent power supply jacks for VCCINT, VCCO, and VCCAUX

• Selectable VCCO-enable pins for each SelectIO™ bank

• Configuration port for use with Parallel Cable III and Parallel Cable IV cables

• 32 clock inputs

♦ 4 differential clock pairs

♦ 4 LVTTL-type oscillator sockets

♦ 20 breakout clock pins

• Power indicator LEDs

• Onboard Platform Flash ISPROM (32 Mb) for configuration

• Onboard power supplies for the Platform Flash ISPROM

• JTAG port for reprogramming the XCF32P series reconfigurable ISPROM and the user

FPGA, also known as the device under test (DUT)

• Upstream and downstream System ACE™ connectors and configuration interface

connectors

• Onboard battery holder

• One low-voltage, 14-pin, DIP crystal oscillators

The kit contains headers that can be soldered to the breakout area, if desired. These headers

are useful with certain types of oscilloscope probes for either connecting function

generators or wiring pins to the prototype area.

The Virtex-4 prototype platform (the board) contains a DUT FPGA and one In-System

Programmable Configuration PROM (ISPROM). The ISPROM can hold up to 33,554,432

bits. The DUT can be configured either from the ISPROM or from the configuration ports

(Parallel Cable III/IV cable).

In addition to the ISPROM and the configuration ports, there are upstream connectors and

downstream connectors. The upstream connectors can be connected to configure the DUT

by using the System ACE configuration solution or by chaining another board. The

downstream connectors can be used to connect to another board in a chain for serial

configuration. A maximum of two boards can be chained together.

8 www.xilinx.com Virtex-4 LX/SX Prototype Platform

UG078 (v1.2) May 24, 2006

Page 9

R

Introduction

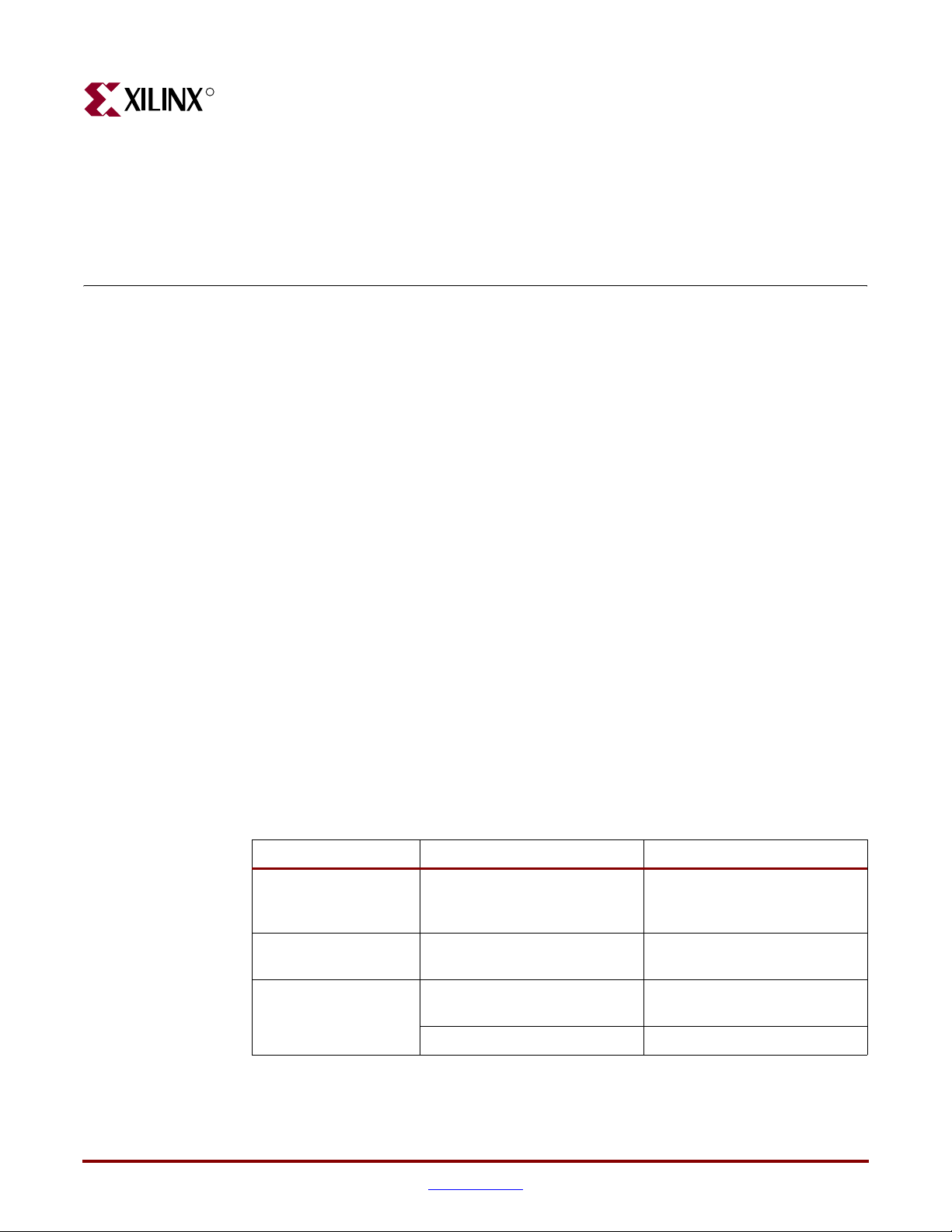

Figure 1 shows a block diagram of the board.

2x Diff Pair

Clocks

Upstream

System ACE

Interface

Connector

LEDs

Upstream

Interface

Connector

2x

LVTTL

Virtex-4 DUT

SMA

SMA

Configuration

Por t

To Test Points

on All Pins

PROGRAM

Downstream

System ACE

Interface

Connector

Power Bus and Switches

5V Jack 5V Brick-or-

VCCINT

VCCO

VCCAUX

VCC3

VCC1V8

AVCC

VBATT

Downstream

Interface

Connector

VCC Jack

VCCO Jack

VCCAUX Jack

LVTTL

2x

SMA

SMA

2x Diff Pair

Clocks

DONE

LED

User RESET

INIT

LED

UG078_01_101204

Figure 1: Virtex-4 LX/SX Prototype Platform Block Diagram

Virtex-4 LX/SX Prototype Platform www.xilinx.com 9

UG078 (v1.2) May 24, 2006

Page 10

Detailed Description

Detailed Description

The Virtex-4 prototype platform board is shown in Figure 2. Each feature is detailed in the

numbered sections that follow.

6a 6c

R

4

10

1

11

13

3

2

9

19

12

1313

8

13

7

14

5

16

17

15

6b 6d

Figure 2: Detailed Description of Virtex-4 LX/SX Prototype Platform Components

18

UG078_02_101904

1. Power Switch

The board has an onboard power supply and an ON|OFF power switch. When lit, a green

LED indicates power from the power brick connector or the 5V jack.

On Position

In the ON position, the power switch enables delivery of all power to the board by way of

voltage regulators situated on the backside of the board. These regulators feed off a 5V

external power brick or the 5V power supply jack.

The voltage regulators deliver fixed voltages. Maximum current range for each supply will

vary. Table 1, page 9 shows the maximum voltage and maximum current for each onboard

power supply. If the current exceeds maximum ratings, use the power jacks to supply

power to the DUT.

10 www.xilinx.com Virtex-4 LX/SX Prototype Platform

UG078 (v1.2) May 24, 2006

Page 11

R

Table 1: Voltage Ranges

Label Maximum Voltage Maximum Current

VCCINT 1.2V 1A

VCCO 3.3V 2A

VCCAUX 2.5V 1.5A

VCC 3.3V 2A

VCC1V8 1.8V 1A

AVCC 2.5V 25 mA

Off Position

In the OFF position, the power switch disables all modes of powering the DUT.

Power Enable Jumpers

For each power supply there are headers marked SUPPLY on one side and JACK on the

other side. Appropriate placements of jumpers on these headers enables delivery of all

power from either the onboard regulators or the three power supply jacks marked

VCCINT, VCCO, and VCCAUX.

Detailed Description

2. Power Supply Jacks

One method of delivering power to the DUT is by way of the power supply jacks. (Consult

the Xilinx data book, http://www.xilinx.com/partinfo/datasheet.htm

voltage rating for each device you are using.) The power supply jacks are:

• VCCINT

♦ Supplies voltage to the V

• VCCO

♦ Supplies I/O voltages to the DUT

♦ Each bank can be powered from one of two sources (V

appropriate placement of jumpers on the header

• VCCAUX

♦ Supplies voltage to the V

CCINT

CCAUX

of the DUT

DUT pins

CCO

, for the maximum

, V

CCINT

) by

Virtex-4 LX/SX Prototype Platform www.xilinx.com 11

UG078 (v1.2) May 24, 2006

Page 12

Detailed Description

3. Configuration Ports

R

These headers can be used to connect a Parallel Cable III or Parallel Cable IV cable to the

board (see Table 2) and support all Virtex-4 device configuration modes. See Table 3 for

connecting the cables to the configuration ports and Figure 3 for setting up the JTAG chain

on the board.

Table 2: Serial Mode

Configuration Port Header Parallel Cable III/IV Pins

VCC3 VCC

GND GND

CCLK CCLK

DONE D/P

DIN DIN

PROG PROG

INIT

Table 3: JTAG Mode

Configuration Port Header

Parallel Cable IV Connector

VCC3V3 VCC VCC

GND GND GND

TMS TMS TMS

TDI TDI TDI

TDO TDO TDO

TCK TCK TCK

INIT

UP

DN

Parallel Cable III Pins Parallel Cable IV Pins

INIT

TDI

PROM

TMS

TCK

TDO

TDO

TDI

TCK

TMS

TDO

TDI

DUT

TDO

UG078_03_082404

Figure 3: JTAG Chain Termination

12 www.xilinx.com Virtex-4 LX/SX Prototype Platform

UG078 (v1.2) May 24, 2006

Page 13

R

4. JTAG Chain

Jumper J17 provides the ability to have the Virtex-4 in the JTAG chain or remove it from the

JTAG chain.

Note:

The Virtex-4 device must not be in the socket when detecting the ISPROM in the chain.

5. JTAG Termination Jumper

The DUT TDO pin can be jumpered to the TDO TERM pin or the downstream TDO pin.

When another board is connected to the downstream System ACE connector or

downstream interface connector, jumper the DUT TDO pin to the downstream TDO pin

for serial chaining. The connection allows the DUT TDO pin to be connected to the next

device in the chain.

The TCK and TMS pins are parallel feedthrough connections from the upstream

System ACE interface connector to the downstream System ACE interface connector and

drive the TCK and TMS pins of the onboard PROM and the DUT.

Note:

The termination jumper must be in place on the last board in the chain to connect the TDO pin

of the final device to the TDO feedback chain.

Detailed Description

Virtex-4 LX/SX Prototype Platform www.xilinx.com 13

UG078 (v1.2) May 24, 2006

Page 14

Detailed Description

6a. Upstream System ACE Interface Connector

R

The upstream System ACE interface connector, as shown in Figure 4, can be used to

configure the DUT. Any JTAG configuration stream can source this connector. For

example, a System ACE controller with a CompactFlash card can be used to generate very

large JTAG streams for configuring multiple Virtex-4 prototype platforms using the

downstream System ACE interface connector.

UPSTREAM_TDO

GND

UPSTREAM_TCK

GND

VCC_TMP

VCC_TMP

VCC_TMP

VCC_TMP

VCC_TMP

GND

GND

UPSTREAM_TDI

GND

UPSTREAM_TMS

NC

135791113151719

2468101214161820

VCC3_EN

VCC3_EN

VCC3_EN

VCC3_EN

GND

Figure 4: Upstream System ACE Interface Connector (20-Pin Female)

6b. Downstream System ACE Interface Connector

The downstream System ACE interface connector, as shown in Figure 5, is used to pass

configuration information to a DUT in a downstream prototype platform board from

sources such as a Parallel Cable III cable or an upstream System ACE interface connector.

GND

VCC_TMP

VCC_TMP

VCC_TMP

VCC_TMP

2468101214161820

UG078_04_051004

GND

VCC3_EN

VCC3_EN

VCC3_EN

VCC3_EN

VCC_TMP

GND

DOWNSTREAM_TCK

GND

DOWNSTREAM_TDO

135791113151719

NC

DOWNSTREAM_TMS

GND

DOWNSTREAM_TDI

GND

UG078_05_051004

Figure 5: Downstream System ACE Interface Connector (20-Pin Male)

14 www.xilinx.com Virtex-4 LX/SX Prototype Platform

UG078 (v1.2) May 24, 2006

Page 15

R

6c. Upstream Interface Connector

The upstream interface connector, as shown in Figure 6, is used to configure the DUT in

select map or slave-serial mode. This connector can be sourced by a downstream interface

connector of another prototype platform board.

Detailed Description

GND

GND

GND

GND

NC

NC

NC

GND

NC

NC

NC

A22

B22

A21

B21

A20

B20

A19

B19

A18

B18

A17

B17

A16

B16

A15

B15

A14

B14

A13

B13

A12

B12

A11

B11

A10

B10

A1

A2

A3

A4

A5

A6

A7

A8

A9

B1

B2

B3

B4

B5

B6

B7

B8

B9

TMS

TDI

TDO

TCK

NC

NC

NC

DOUT_BUSY

INIT

PROG

RW_B

Figure 6: Upstream Interface Connector (44-Pin Female)

GND

GND

GND

NC

AFX_M2

AFX_M1

AFX_M0

NC

NC

NC

CS_B

DIN

D1

D2

D3

D4

D5

D6

D7

DONE

CCLK

NC

UG027_06_051004

Virtex-4 LX/SX Prototype Platform www.xilinx.com 15

UG078 (v1.2) May 24, 2006

Page 16

Detailed Description

6d. Downstream Interface Connector

R

The downstream interface connector, as shown in Figure 7, passes serial configuration

information to the DUT in the downstream prototype platform board.

NC

PROG

INIT

NC

NC

NC

NC

TCK

TDO

DOWNSTREAM_TDI

TMS

GND

NC

NC

GND

GND

GND

GND

GND

GND

GND

NC

Figure 7: Downstream Interface Connector (44-Pin Male)

B22

A22

B21

A21

B20

A20

B19

A19

B18

A18

B17

A17

B16

A16

B15

A15

B14

A14

B13

A13

B12

A12

B11

A11

B10

A10

NC

CLK

DONE

NC

NC

NC

NC

NC

NC

NC

B9

A4

A5

A6

A7

A8

A9

A2

A3

DOUT_BUSY

A1

B1

B2

B3

B4

B5

B6

B7

B8

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

UG027_07_051004

7. Prototyping Area

The prototyping area accommodates 0.10-inch spaced ICs. The kit contains headers that

can be soldered to the breakout area, if desired. Power and ground buses are located at the

top and bottom edges, respectively, of the prototyping area.

8. VCCO-Enable Supply Jumpers

Virtex-4 series devices have 9 to 17 SelectIO banks, labeled 0 through 16, each with a

VCCO-enable supply jumper. The VCCO-enable supply jumpers can connect each bank to

one of the two onboard supplies, VCCINT or the VCCO supply. These jumpers must be

installed for the Virtex-4 device to function normally.

9. VBATT

An onboard battery holder is connected to the VBATT pin of the DUT. If an external power

supply is used, the associated jumper must be removed and instead use a 12 mm lithium

coin battery (3V).

16 www.xilinx.com Virtex-4 LX/SX Prototype Platform

UG078 (v1.2) May 24, 2006

Page 17

R

10. Oscillator Sockets

The board has four crystal oscillator sockets, all wired for standard LVTTL-type oscillators.

These sockets connect to the DUT clock pads as shown in Table 4 and Table 5. Onboard

termination resistors can be changed by the user. The oscillator sockets accept both halfand full-sized oscillators and are powered by the DUT VCCO power supply.

Table 4: Oscillator Socket Clock Pin Connections for SF363 and FF668

Detailed Description

SF363 FF668

Label Clock Name

OSC

Socket

Top 1

OSC

Socket

Top 2

OSC

Socket

Bottom 1

OSC

Socket

Bottom 2

IO_L1N_GCLK_CC_LC_3 A11 IO_L1N_GCLK_CC_LC_3 B14

IO_L1P_GCLK_CC_LC_3 B12 IO_L1P_GCLK_CC_LC_3 B15

IO_L1P_GCLK_CC_LC_4 W13 IO_L1P_GCLK_CC_LC_4 AF12

IO_L1N_GCLK_CC_LC_4 W12 IO_L1N_GCLK_CC_LC_4 AE12

Pin

Number

Clock Name

Table 5: Oscillator Socket Clock Pin Connections for FF1148 and FF1513

FF1148 FF1513

Label Clock Name

Pin

Number

Clock Name

OSC

Socket

IO_L1N_GCLK_CC_LC_3 G18 IO_L1N_GCLK_CC_LC_3 N20

Top 1

Pin

Number

Pin

Number

OSC

Socket

IO_L1P_GCLK_CC_LC_3 F18 IO_L1P_GCLK_CC_LC_3 P20

Top 2

OSC

Socket

IO_L1P_GCLK_CC_LC_4 AF18 IO_L1P_GCLK_CC_LC_4 AH20

Bottom 1

OSC

Socket

IO_L1N_GCLK_CC_LC_4 AE18 IO_L1N_GCLK_CC_LC_4 AH19

Bottom 2

Virtex-4 LX/SX Prototype Platform www.xilinx.com 17

UG078 (v1.2) May 24, 2006

Page 18

Detailed Description

11. Differential Clock Inputs

R

In addition to the oscillator sockets, there are eight 50Ω SMA connectors that allow

connection to an external function generator. These connect to the DUT clock pads as

shown in Table 6 and Table 7. They can also be used as differential clock inputs. The

differential clock pairings (DIFFERENTIAL PAIRS) are as shown in the tables.

Table 6: SMA Clock Pin Connections for SF363 and FF668

SF363 FF668

Label Clock Name

Pin

Number

Clock Name

N IO_L8N_GC_LC_3 B7 IO_L8N_GC_LC_3 C12

P IO_L8P_GC_LC_3 A7 IO_L8P_GC_LC_3 C13

N IO_L2N_GC_VRP_LC_3 B9 IO_L2N_GC_VRP_LC_3 A11

P IO_L2P_GC_VRN_LC_3 A10 IO_L2P_GC_VRN_LC_3 A12

N IO_L2N_GC_LC_4 W5 IO_L2N_GC_LC_4 AB10

P IO_L2P_GC_LC_4 Y5 IO_L2P_GC_LC_4 AC10

N IO_L8N_GC_CC_LC_4 W8 IO_L8N_GC_CC_LC_4 AD11

P IO_L8P_GC_CC_LC_4 W9 IO_L8P_GC_CC_LC_4 AD12

Table 7: SMA Clock Pin Connections for FF1148 and FF1513

FF1148 FF1513

Label Clock Name

Pin

Number

Clock Name

N IO_L8N_GC_CC_LC_3 G16 IO_L8N_GC_CC_LC_3 K21

P IO_L8P_GC_CC_LC_3 G17 IO_L8P_GC_CC_LC_3 L21

Pin

Number

Pin

Number

N IO_L2N_GC_VRP_LC_3 J17 IO_L2N_GC_VRP_LC_3 K19

P IO_L2P_GC_VRP_LC_3 H17 IO_L2P_GC_VRP_LC_3 J19

N IO_L2N_GC_LC_4 AF16 IO_L2N_GC_LC_4 AF18

P IO_L2P_GC_LC_4 AG16 IO_L2P_GC_LC_4 AF19

N IO_L8N_GC_CC_LC_4 AH17 IO_L8N_GC_CC_LC_4 AJ19

P IO_L8P_GC_CC_LC_4 AJ17 IO_L8P_GC_CC_LC_4 AK19

18 www.xilinx.com Virtex-4 LX/SX Prototype Platform

UG078 (v1.2) May 24, 2006

Page 19

R

12. DUT Socket

The DUT socket contains the user FPGA, referred to as the device under test (DUT). The

DUT must be oriented using the P1 indicator on the board.

Detailed Description

Caution!

pin damage, always use the vacuum tool provided when inserting or removing the Virtex-4

device. When using BGA packages, do not apply pressure to the device while activating the

socket. Doing so can damage the socket and/or the device.

13. Pin Breakout

The pin breakout area is used to monitor or apply signals to each of the DUT pins. Headers

can be soldered to the breakout area to use with certain types of oscilloscope probes, for

either connecting function generators or wiring pins to the pin breakout area. Clocks in the

pin breakout area that connect to the DUT clock pads are shown in Table 8 and Table 9,

page 20.

Table 8: Breakout Clock Pin Connections for SF363 and FF668

Label Clock Name

Failure to insert the device to the proper orientation can damage the device. To avoid

SF363 FF668

Pin

Number

IO_L4P_GC_LC_3 B10 IO_L4P_GC_LC_3 B13

IO_L4N_GC_VREF_LC_3 C10 IO_L4N_GC_VREF_LC_3 B12

IO_L5P_GC_LC_3 B13 IO_L5P_GC_LC_3 A16

IO_L5N_GC_LC_3 A13 IO_L5N_GC_LC_3 A15

IO_L6P_GC_LC_3 A8 IO_L6P_GC_LC_3 A10

Clock Name

Pin

Number

IO_L6N_GC_LC_3 B8 IO_L6N_GC_LC_3 B10

IO_L7P_GC_LC_3 B14 IO_L7P_GC_LC_3 B17

IO_L7N_GC_LC_3 A14 IO_L7N_GC_LC_3 A17

IO_L3P_GC_LC_3 C11 IO_L3P_GC_LC_3 C14

IO_L3N_GC_LC_3 B11 IO_L3N_GC_LC_3 C15

IO_L4P_GC_LC_4 Y6 IO_L4P_GC_LC_4 AF11

IO_L4N_GC_VREF_LC_4 W6 IO_L4N_GC_VREF_LC_4 AF10

Breakout Area

IO_L5P_GC_LC_4 W11 IO_L5P_GC_LC_4 AE14

IO_L5N_GC_LC_4 W10 IO_L5N_GC_LC_4 AE13

IO_L6P_GC_LC_4 Y7 IO_L6P_GC_LC_4 AE10

IO_L6N_GC_LC_4 W7 IO_L6N_GC_LC_4 AD10

IO_L7P_GC_VRN_LC_4 Y10 IO_L7P_GC_VRN_LC_4 AD17

IO_L7N_GC_VRP_LC_4 Y9 IO_L7N_GC_VRP_LC_4 AD16

IO_L3P_GC_CC_LC_4 Y12 IO_L3P_GC_CC_LC_4 AB17

IO_L3N_GC_CC_LC_4 Y11 IO_L3N_GC_CC_LC_4 AC17

Virtex-4 LX/SX Prototype Platform www.xilinx.com 19

UG078 (v1.2) May 24, 2006

Page 20

Detailed Description

R

Table 9: Breakout Clock Pin Connections for FF1148 and FF1513

FF1148 FF1513

Label Clock Name

IO_L4P_GC_LC_3 E13 IO_L4P_GC_LC_3 J21

IO_L4N_GC_VREF_LC_3 E17 IO_L4N_GC_VREF_LC_3 J20

IO_L5P_GC_LC_3 K18 IO_L5P_GC_LC_3 M21

IO_L5N_GC_LC_3 K17 IO_L5N_GC_LC_3 M20

IO_L6P_GC_LC_3 E16 IO_L6P_GC_LC_3 L20

IO_L6N_GC_LC_3 F16 IO_L6N_GC_LC_3 L19

IO_L7P_GC_LC_3 K19 IO_L7P_GC_LC_3 P22

IO_L7N_GC_LC_3 J19 IO_L7N_GC_LC_3 P21

IO_L3P_GC_LC_3 H19 IO_L3P_GC_LC_3 N22

IO_L3N_GC_LC_3 H18 IO_L3N_GC_LC_3 M22

IO_L4P_GC_LC_4 AK18 IO_L4P_GC_LC_4 AG20

IO_L4N_GC_VREF_LC_4 AK17 IO_L4N_GC_VREF_LC_4 AF20

Breakout Area

IO_L5P_GC_LC_4 AG18 IO_L5P_GC_LC_4 AL20

IO_L5N_GC_LC_4 AG17 IO_L5N_GC_LC_4 AL19

IO_L6P_GC_LC_4 AE17 IO_L6P_GC_LC_4 AH18

Pin

Number

Clock Name

Pin

Number

IO_L6N_GC_LC_4 AE16 IO_L6N_GC_LC_4 AG18

IO_L7P_GC_VRN_LC_4 AJ19 IO_L7P_GC_VRN_LC_4 AL21

IO_L7N_GC_VRP_LC_4 AK19 IO_L7N_GC_VRP_LC_4 AK21

IO_L3P_GC_CC_LC_4 AH19 IO_L3P_GC_CC_LC_4 AJ21

IO_L3N_GC_CC_LC_4 AH18 IO_L3N_GC_CC_LC_4 AJ20

20 www.xilinx.com Virtex-4 LX/SX Prototype Platform

UG078 (v1.2) May 24, 2006

Page 21

R

14. User LEDs (Active-High)

There are 16 active-high user LEDs on the board. Before configuration, the LEDs reflect the

status of the configuration mode pins. During configuration, the LEDs are in a highimpedance condition. After configuration, the LEDs are available to the user and reflect the

status of pins D0-D7 and D24-D31 (corresponding to LED 0- LED 15). The LED

assignments are shown in Table 10.

Table 10: LED Assignments and Corresponding I/O

LED After Configuration SF363 FF668 FF1148 FF1513

Detailed Description

Pin Number For Package Type

0

U9 AD13 G13 B16

1 V10 AC13 F13 A16

2V11AC15J21R22

3 U12 AC16 H22 T23

4V8AA11H13G15

5V9AA12H14G16

6 V12 AD14 M20 N24

7 V13 AC14 N20 M25

Available as user LEDs

8D6D13K14H15

9E7D14J14J16

10 E14 F15 D21 D26

11 D15 F16 E21 E26

12 F6 F11 L14 L16

13 E6 F12 L15 K16

14 E15 F13 N18 F25

15 F15 F14 N19 F26

Virtex-4 LX/SX Prototype Platform www.xilinx.com 21

UG078 (v1.2) May 24, 2006

Page 22

Detailed Description

15. PROGRAM Switch

16. RESET Switch (Active-Low)

17. DONE LED

R

The active-low PROGRAM switch, when pressed, grounds the program pin on the DUT.

The RESET switch connects to a standard I/O pin on the DUT, allowing the user, after

configuration, to reset the logic within the DUT. When pressed, this switch grounds the

pin.

Table 11 shows the INIT pin locations for the available DUT package types.

Table 11: User Hardware and Corresponding I/O Pins

Pin Number For Package Type

Label SF363 FF668 FF1148 FF1513

RESET R16 W24 AP21 AH23

Note: Refer to the readme.txt file for implementation of this user pin.

The DONE LED indicates the status of the DONE pin on the DUT. This LED lights when

DONE is high or if power is applied to the board without a part in the socket.

18. INIT LED

The INIT LED lights during initialization.

19. Platform Flash ISPROM

A 32-Mb Platform Flash In-System Programmable Configuration PROM (ISPROM) is

provided on the board for configuration (see Table 12). Refer to Platform Flash ISPROM

(DS123) at http://direct.xilinx.com/bvdocs/publications/ds123.pdf

description.

Table 12: Platform Flash ISPROM Configuration

Label Description

J46 Provides power to the ISPROM. These jumpers must be installed for proper

operation of the ISPROM.

J45 Sets the design revision control for the ISPROM.

J43 Enables or disables the ISPROM by placing the address counter in reset and

DATA output lines in high-impedance state.

J42 Sets the ISPROM for serial or select map configuration.

for a detailed

J8 Selects one of two modes of CCLK operation:

• ISPROM provides CCLK (PROM CLKOUT)

• FPGA provides CCLK (FPGA CCLK)

22 www.xilinx.com Virtex-4 LX/SX Prototype Platform

UG078 (v1.2) May 24, 2006

Loading...

Loading...