Page 1

PowerPC™ 405 Processor

Block Reference Guide

Embedded Development Kit

UG018 (v2.0) August 20, 2004

R

Page 2

R

"Xilinx" and the Xilinx logo shown above are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved.

CoolRunner, RocketChips, Rocket IP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, and XC5210 are

registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator,

CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and

Beyond!, HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroBlaze, MicroVia,

MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, RocketIO, SelectIO, SelectRAM, SelectRAM+,

Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze,

VersaBlock, VersaRing, Virtex-II Pro, Virtex-II EasyPath, Virtex-4, Virtex-4-FX, Wave Table, WebFITTER, WebPACK, WebPOWERED,

XABEL, XACT-Floorplanner, XACT-Performance, XACTstep Advanced, XACTstep Foundry, XAM, XAPP, X-BLOX +, XC designated

products, XChecker, XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP and ZERO+ are trademarks of Xilinx,

Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

All other t rademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey

any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any

time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for

the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or

information shown or described herein "as is." By providing the design, code, or information as one possible implementation of a feature,

application, or standard, Xilinx makes no representation that such implementation is free from any claims of infringement. You are

responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with

respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation

is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx, Inc. devi ces

and products are protected under U.S. Patents. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown

or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to

correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability

for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without

the written consent of the appropriate Xilinx officer is prohibited.

The contents of this manual are owne d and copyrigh ted by Xilinx . C opyright 1994-2004 Xilinx, Inc. All Rights Reserved. Except as stated

herein, none of the material may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form

or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written cons ent

of Xilinx. Any unauthorized use of any material contained in this manual may violate copyright laws, trademark laws, the laws of privacy and

publicity, and communications regulations and statutes.

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com UG018 (v2.0) August 20, 2004

1-800-255-7778

Page 3

PowerPC™ 405 Processor Block Reference Guide

UG018 (v2.0) August 20, 2004

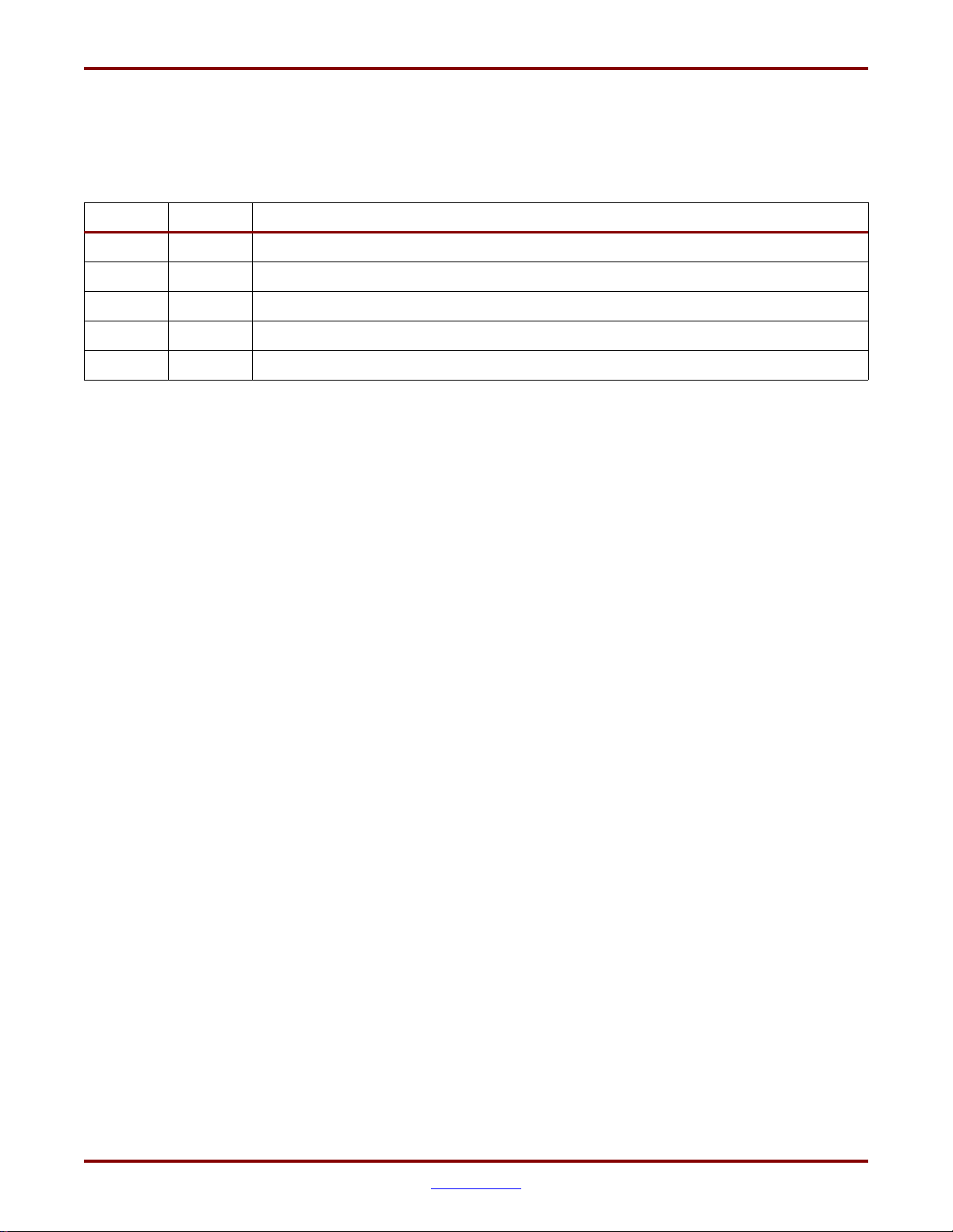

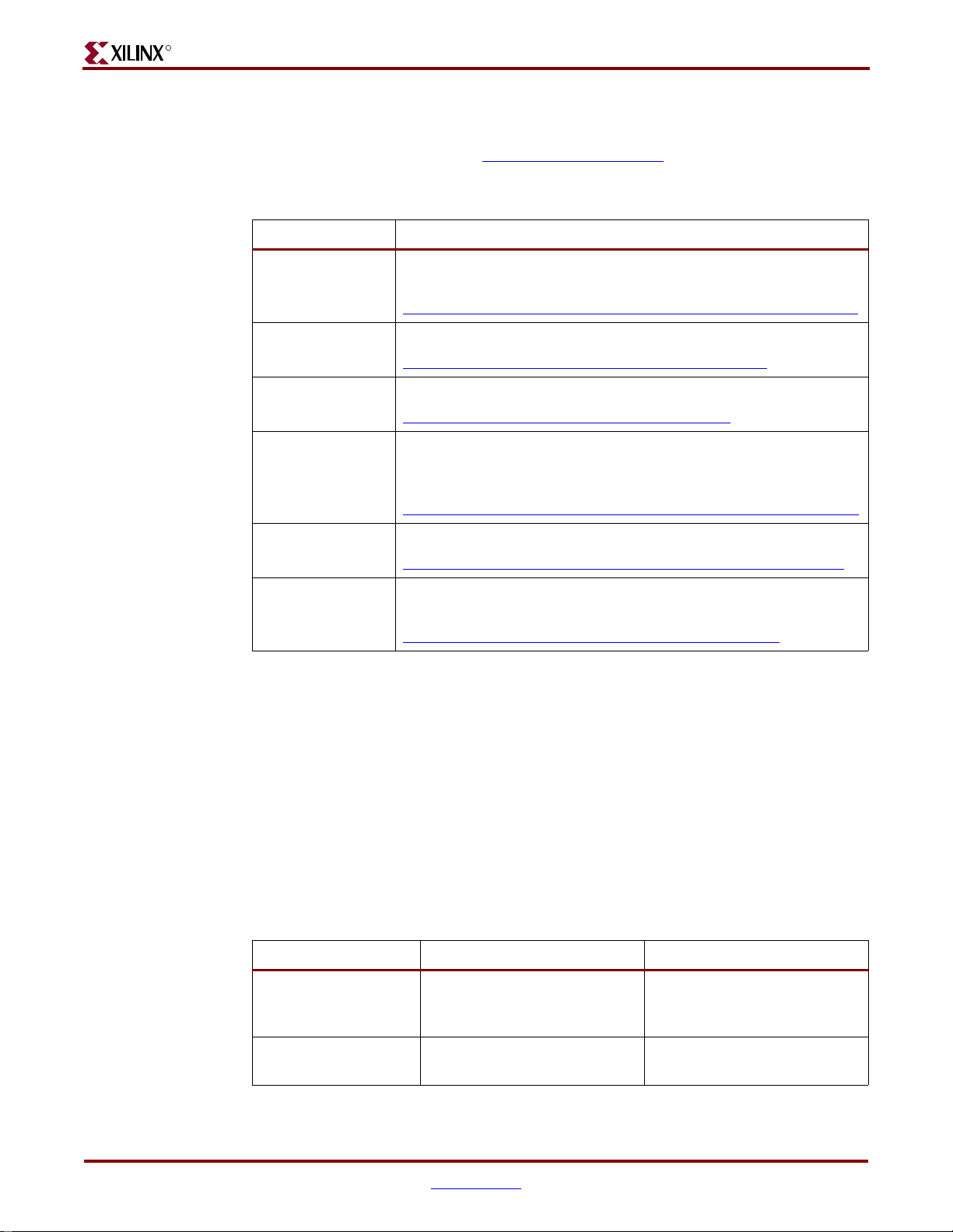

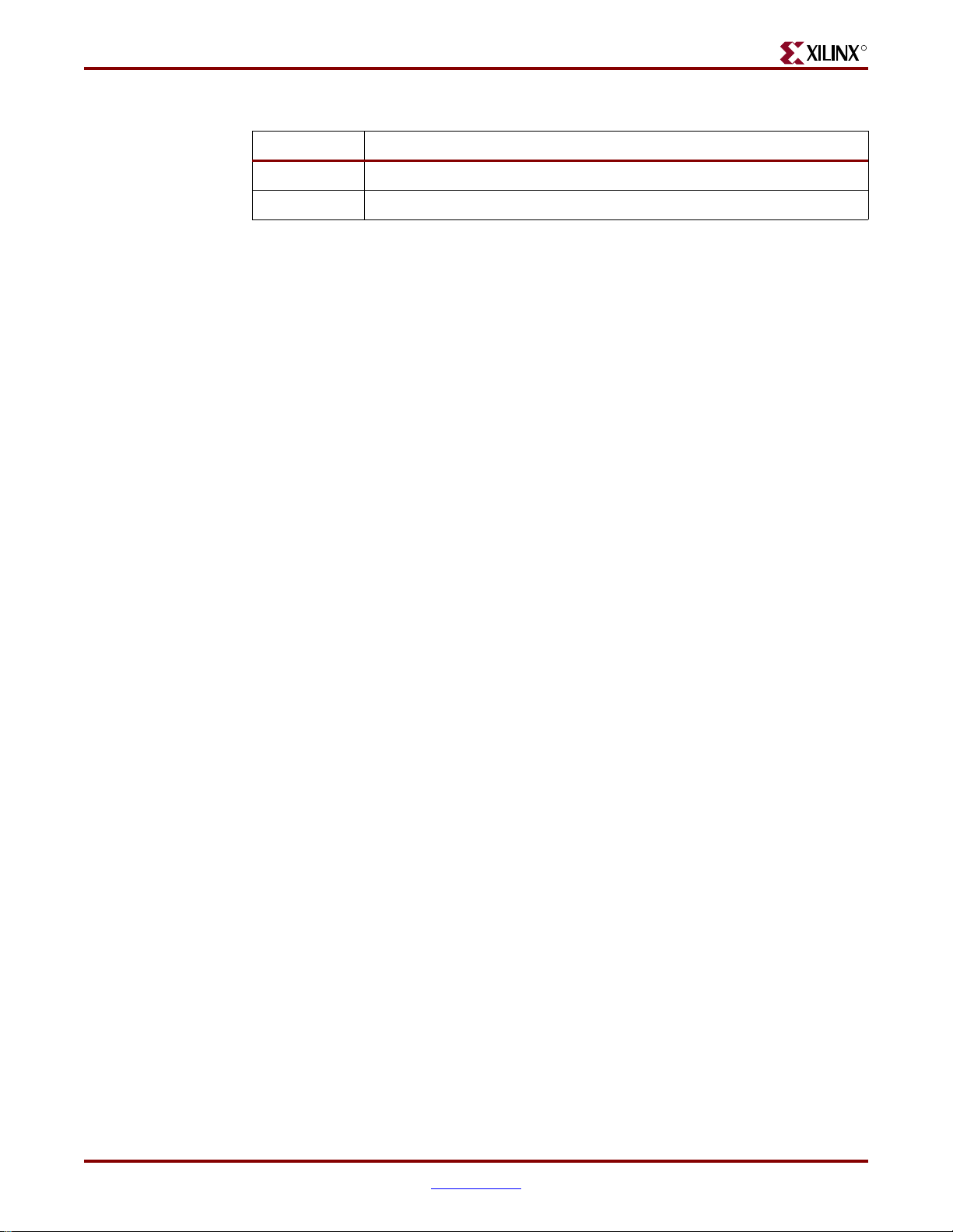

The following table shows the revision history for this document.

Version Revision

09/16/02 1.0 Initial Embedded Development Kit (EDK) release.

09/02/03 1.1 Updated for EDK 6.1 release

04/26/04 DRAFT Early Access release (DRAFT).

06/15/04 DRAFT Second Early Access release (DRAFT).

08/20/04 2.0 Updated to include Virtex-4 functionality.

UG018 (v2.0) August 20 , 20 04 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

1-800-255-7778

Page 4

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com UG018 (v2.0) August 20, 2004

1-800-255-7778

Page 5

Table of Contents

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Typographical. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Online Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

General Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Terms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Chapter 1: Introduction to the PowerPC 405 Processor

PowerPC Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

PowerPC Embedded-Environment Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

PowerPC 405 Software Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Privilege Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Address Translation Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Addressing Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Register Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

PowerPC 405 Hardware Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Central-Processing Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Exception Handling Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Memory Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Instruction and Data Caches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Timer Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

PowerPC 405 Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

PowerPC 405 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Chapter 2: Input/Output Interfaces

Signal Naming Conventions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Clock and Power Management Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

CPM Interface I/O Signal Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

CPM Interface I/O Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

System Design Considerations for Clock Domains . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

CPU Control Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

CPU Control Interface I/O Signal Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

CPU Control Interface I/O Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Reset Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Reset Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Reset Interface I/O Signal Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Reset Interface I/O Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Instruction-Side Processor Local Bus Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 5

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 6

R

Instruction-Side PLB Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Instruction-Side PLB I/O Signal Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Instruction-Side PLB Interface I/O Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . 51

Instruction-Side PLB Interface Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Data-Side Processor Local Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Data-Side PLB Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Data-Side PLB Interface I/O Signal Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Data-Side PLB Interface I/O Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Data-Side PLB Interface Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Device-Control Register Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Internal Device Control Register (DCR) Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Virtex-II Pro and Virtex-II ProX. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Virtex-4-FX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

External DCR Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

External DCR Bus Interface I/O Signal Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

External DCR Bus Interface I/O Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . 105

External DCR Bus Interface Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

External DCR Timing Consideration (Virtex-II Pro/ProX Only) . . . . . . . . . . . . . . . . 109

External Interrupt Controller Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

EIC Interface I/O Signal Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

EIC Interface I/O Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

PPC405 JTAG Debug Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

JTAG Interface I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

JTAG Interface I/O Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

JTAG Instruction Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Connecting PPC405 JTAG Logic Directly to Programmable I/O. . . . . . . . . . . . . . . . 115

Connecting PPC405 JTAG Logic in Series with the Dedicated Device JTAG Logic 119

VHDL and Verilog Instantiation Templates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Debug Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Debug Interface I/O Signal Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Debug Interface I/O Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Trace Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Trace Interface Signal Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Trace Interface I/O Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Processor Version Register (PVR) Interface (Virtex-4-FX Only). . . . . . . . . . . . . . 134

PVR Interface I/O Signal Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

PVR Interface I/O Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Additional FPGA Specific Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Additional FPGA I/O Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Chapter 3: PowerPC 405 OCM Controller

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Comparison of Virtex-II Pro and Virtex-4 OCM Controllers. . . . . . . . . . . . . . . . . 140

Functional Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Common Features for DSOCM and ISOCM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Features for Data-Side OCM (DSOCM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Features for Instruction-Side OCM (ISOCM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

OCM Controller Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

OCM DCR-Based Control Registers (Accessed Via DCR Instructions). . . . . . . . . . . 143

DSOCM Controller Load/Store Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

6 www.xilinx.com PowerPC™ 405 Processor Blo ck R eference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 7

ISOCM Controller Instruction Fetch Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

DSOCM Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

ISOCM Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Programmer’s Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

DCR Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

DSARC/ ISARC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

DSCNTL Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

ISCNTL Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Features Introduced in Virtex-4 and Comparison with Virtex-II Pro . . . . . . . . . . . . 161

DCR Write Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

DCR Read Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Timing Specification for Fixed Latency (Virtex-4 and Virtex-II Pro) . . . . . . . . . 169

Single-Cycle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Multi-Cycle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

ISOCM Instruction Fetching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Writing to ISBRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

DSOCM Data Load, Fixed Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

DSOCM Store, Fixed Latency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Timing Specification for Variable Latency (Virtex-4 DSOCM Controller Only) 177

DSOCM Data Load, Variable Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

DSOCM Data Store, Variable Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Application Notes and Reference Designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

R

Chapter 4: PowerPC 405 APU Controller

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

FCM Instruction Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Enabling the APU Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Instruction Classes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Instruction Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

APU Controller Pre-Defined Instruction Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

APU Controller User-Defined Instruction Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . 189

FCM Pre-Defined Instruction Decoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

FCM User-Defined Instruction Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

FCM Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

FCM Instruction Flushing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

Execution Hazards. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

APU Controller Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

General Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

UDI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

DCR Access to the Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

Interface Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

APU Controller Input Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

APU Controller Output Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

APU Controller Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

FCM Interface Timing Specification. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Autonomous Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Blocking Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Non-Blocking Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

FCM Load Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 7

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 8

R

FCM Store Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

FCM Exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

FCM Decoding Using Decode Busy Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

Appendix A: RISCWatch and RISCTrace Interfaces

RISCWatch Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

RISCTrace Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Appendix B: Signal Summary

Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Appendix C: Processor Block Timing Model

Timing Parameter Tables and Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

8 www.xilinx.com PowerPC™ 405 Processor Blo ck R eference Guide

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 9

R

About This Guide

Preface

This guide serves as a technical reference describing the hardware interface to the

PowerPC

relationships between signals, and the mechanisms software can use to control the

interface operation. The document is intended for use by FPGA and system hardware

designers and by system programmers who need to understand how certain operations

affect hardware external to the processor.

Guide Contents

This manual contains the following chapter s:

x Chapter 1, “Introduction to the PowerPC 405 Processor,” provides an overview of the

x Chapter 2, “Input/Output Interfaces,” describes the interface signals into and out of

x Chapter 3, “PowerPC 405 OCM Controller,” describes the features, interface signals,

x Chapter 4, “PowerPC 405 APU Controller,” describes the Auxiliary Processor Unit

x Appendix A, “RISCWatch and RISCTrace Interfaces,” describes the interface

x Appendix B, “Signal Summary,” lists all PowerPC 405 interface signals in alphabetical

x Appendix C, “Processor Block Timing Model,” explains all of the timing parameters

®

405 processor block. It contains information on input/output signals, timi ng

PowerPC embedded-environment architecture and the features supported by the

PowerPC 405.

the PowerPC 405 processor block. Where appropriate, timing diagrams are provided

to assist in understanding the functional relationship between multiple signals.

timing specifications, and programming model for the PowerPC 405 on-chip memory

(OCM) controller. The OCM controller serves as a dedicated interface between the

block RAMs in the FPGA and OCM signals available on the embedded Pow erPC 405

core.

controller , which allows the designer to extend the native PowerPC 405 instruction set

with custom instructions that are executed by an FPGA Fabric Co-processor Module

(FCM). The APU controller is available only for Virtex-4 family devices.

requirements between the PowerPC 405 processor block and the RISCWatch and

RISCTrace tools.

order .

associated with the IBM PPC405 Processor Block.

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 9

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 10

R

Additional Resources

For additional information, go to http://support.xilinx.com. The following table lists

some of the resources you can access from this website. You can also directly access these

resources using the provided URLs.

Resource Description/URL

Tutorials Tutorials covering Xilinx design flows, from design entry to

Answer Browser Database of Xilinx solution records

Application Notes Descriptions of device-specific design techniques and approaches

Data Sheets Device-spe c ific informati o n on Xilinx device ch ar a c teristics,

Preface: About This Guide

verification and debugging

http://support.xilinx.com/support/techsup/tutorials/index.htm

http://support.xilinx.com/xlnx/xil_ans_browser. jsp

http://support.xilinx.com/apps/appsweb.htm

including readback, boundary scan, configuration, length count,

and debugging

http://support.xilinx.com/xlnx/xweb/xil_publications_index.jsp

Conventions

Typographical

Problem Solvers Interactive tools that allow yo u to troubleshoot your design issues

http://support.xilinx.com/support/troubleshoot/psolvers.htm

Tech Tips Latest news, design tips, and patch informa tion for the Xilinx

design environment

http://www.support.xilinx.com/xlnx/xil_tt_home.jsp

The following documents contain additional information of potential interest to readers of

this manual:

x XILINX PowerPC Processo r Reference Guide

x XILINX Virtex-II Pro Platform FPGA Handbook

This document uses the following conventions. An example illustrates each convention.

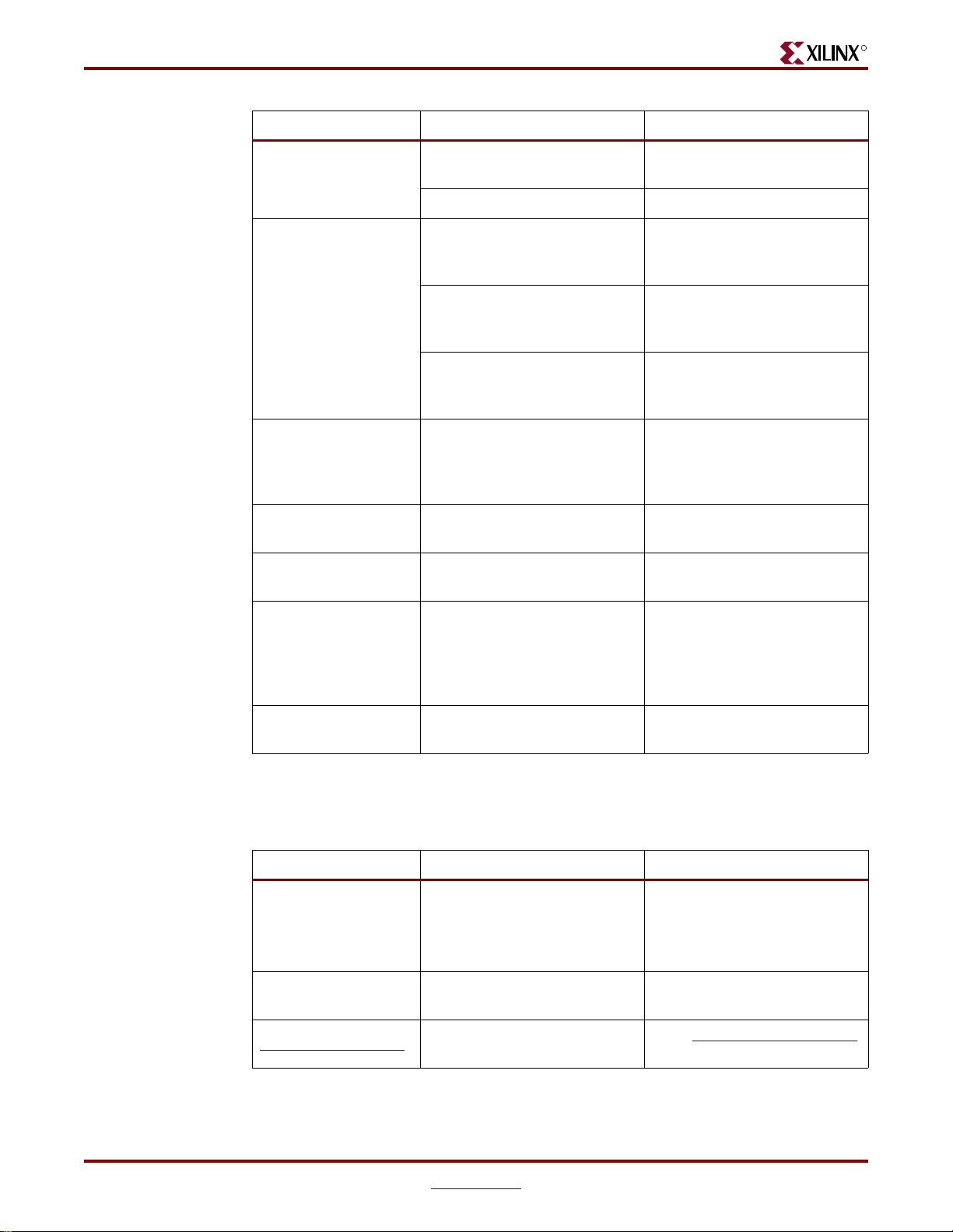

The following typographical conv entions are used in this document:

Convention Meaning or Use Example

Messages, prompts, and

Courier font

program files that the system

displays

speed grade: - 100

Courier bold

10 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

Literal commands that you

enter in a syntactical statement

1-800-255-7778 UG018 (v2.0) August 20, 2004

ngdbuild design_name

Page 11

Convention Meaning or Use Example

R

Helvetica bold

Italic font

Square brackets [ ]

Braces { }

Vertical bar |

Commands that you select

from a menu

File o Open

Keyboar d shortcuts Ctrl+C

Variables in a syntax

statement for which you must

ngdbuild design_name

supply values

See the Development System

References to other manuals

Reference Guide for more

information.

If a wire is drawn so that it

Emphasis in text

overlaps the pin of a symbol,

the two nets are not connected.

An optional entry or

parameter. However, in bus

specifications, such as

ngdbuild [ option_name]

design_name

bus[7:0], they are required.

A list of items from which you

must choose one or more

Separates items in a list of

choices

lowpwr ={on|off}

lowpwr ={on|off}

Vertical ellipsis

Horizont al e lli ps i s . . .

Online Document

The following conventions are used in this document:

Convention Meaning or Use Example

Blue text

Red text

Blue, underlined text

IOB #1: Name = QOUT’

.

.

Repetitive material that has

been omitted

.

Repetitive material that has

been omitted

IOB #2: Name = CLKIN’

.

.

.

allow block block_name

loc1 loc2 ... locn;

See the section “Additional

Cross-reference link to a

location in the current

document

Reference to a location in

another docum ent

Hyperlink to a website (URL)

Resources” for details.

Refer to “Title Formats” in

Chapter 1 for details.

See Figure 2-5 in the Virtex-II

Handbook.

Go to http://www.xilinx.com

for the latest speed files.

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 11

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 12

R

General Conventions

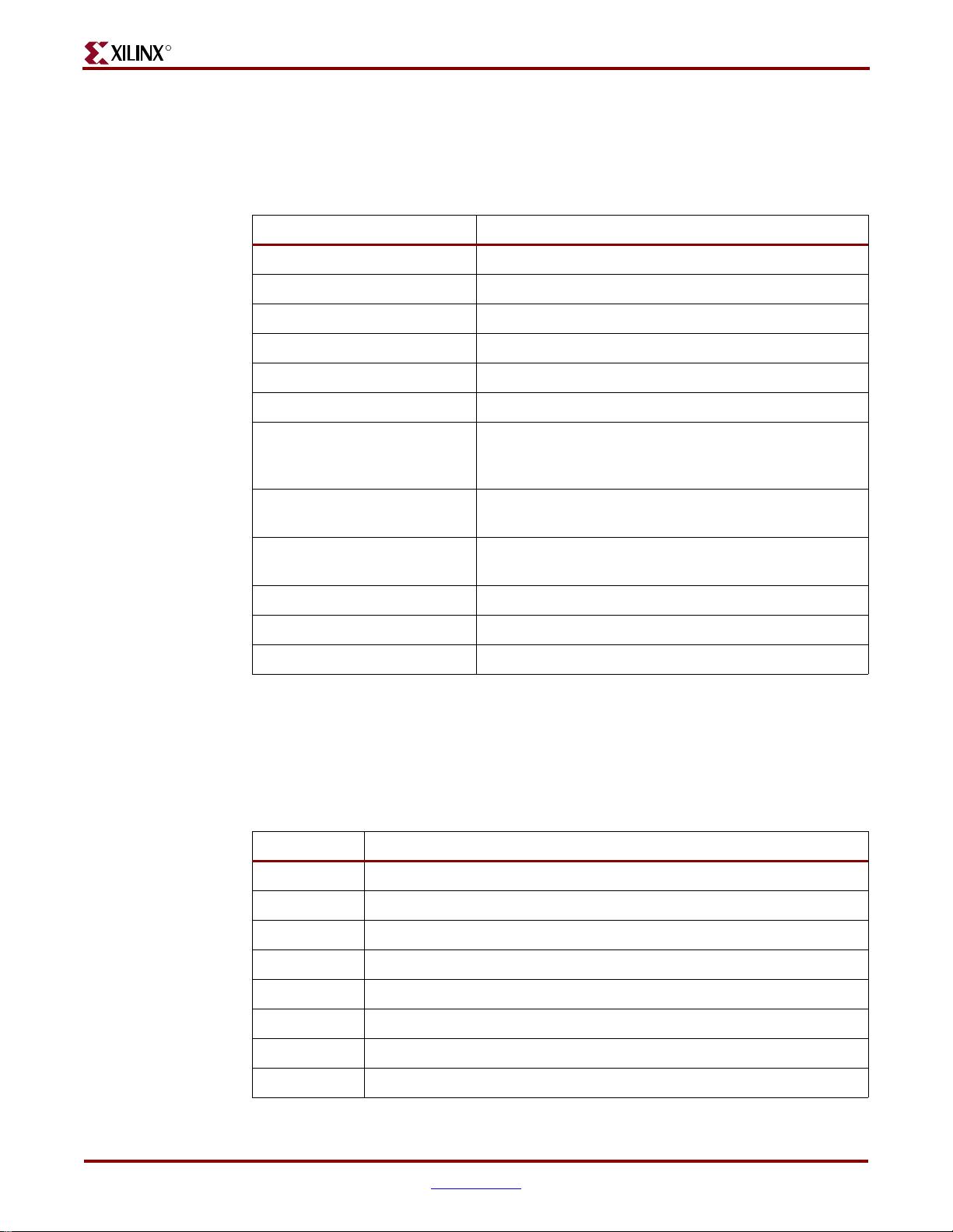

Table 1-1 lists the general notational conventions used throughout this docum e nt.

Table 1-1: General Notational Conventions

Convention Definition

mnemonic Instruction mnemonics are shown in lower-case bold.

variable Variable items are shown in italic.

ActiveLow An overbar indicates an active-low signal.

n A decimal number

0xn A hexadecimal number

0bn A binary number

Preface: About This Guide

Registers

OBJECT

b

A single bit in any object (a register, an instruction, an

address, or a f ield) is shown as a su bscripted number or

name

OBJECT

b:b

A range of bits in any object (a register, an instruction,

an address, or a field)

OBJECT

b,b, . . .

A list of bits in any object (a register, an instruction, an

address, or a field)

REGISTER[FIELD] Fields within any register are shown in square brackets

REGISTER[FIELD, FIELD

REGISTER[FIELD:FIELD] A

]A list of fields in any register

. . .

range of fields in any register

Table 1-2 lists the PowerPC 405 registers used in this document and their descriptive

names.

Table 1-2: PowerPC 405 Registers

Register Descriptive Name

CCR0 Core-configuration register 0

DBCRn Debug-control register n

DBSR Debug-status register

ESR Exception-syndrome register

MSR Machine-state register

PIT Programmable-interval timer

TBL Time-base lower

TBU Time-base upper

12 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 13

Terms

R

Table 1-2: PowerPC 405 Registers (Continued)

Register Descriptive Name

TCR Timer-control register

TSR Timer-status register

active As applied to signals, this term indicates a signal is in a state

that causes an action to occur in the receiving device, or

indicates an action occurred in the sending device. An active-

high signal drives a logic 1 when active. An active-low signal

drives a logic 0 when active.

assert As applied to signals, this term indicates a signal is driven to its

active state.

atomic access A memory access tha t at tempts to read from and write to the

same address uninterrupted by other accesses to that address.

The term refers to the fact that such transactions are indivisible.

big endian A memory byte ordering where the address of an item

corresponds to the most-significant byte.

Book-E An version of the PowerPC architecture designed specifically

for embedded applications.

cache block Synonym for cache line.

cache line A portion of a cache array that contains a copy of contiguous

system-memory addresses. Cache lines are 32-bytes long and

aligned on a 32-b yte address.

cache set Synonym for congruence class.

clear To write a bit value of 0.

clock Unless otherwise specified, this term refers to the PowerPC 405

processor clock.

congruence class A collection of cache lines with the same index.

cycle The time between two successive rising edges of the associated

clock.

dead cycle A cycle in which no useful activity occurs on the associated

interface.

deassert As applied to signals, this term indicates a signal is driven to its

inactive state.

dirty An indication that cache information is more recent than the

copy in memory.

doubleword Eight bytes, or 64 bits.

effective address The untranslated memory address as seen by a program.

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 13

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 14

R

Preface: About This Guide

exception An abnormal event or condition that requires the processor’s

attention. They can be caused by instruction execution or an

external device. The processor records the occurrence of an

exception and they often cause an interrupt to occur.

fill buffer A buffer that receives and sends data and instr uctions between

the processor and PLB. It is used when cache misses occur and

when access to non-cacheable memory occurs.

flush A cache operation that involves writing back a modified entry

to memory, followed by an invalidation of the entry.

GB Gigabyte, or one-billion bytes.

halfword Two bytes, or 16 bits.

hit An indication that requested information exists in the accessed

cache array, the associated fill buffer, or on the corresponding

OCM interface.

inactive As applied to signals, this term indicates a signal is in a state

that does not cause an action to occur, nor does it indicate an

action occurred. An active-high signal drives a logic 0 when

inactive. An active-low signal drives a logic 1 when inactive.

interrupt The process of stopping the currently executing program so that

an exception can b e handl ed.

invalidate A cache or TLB operation that causes an entry to be marked as

invalid. An invalid entry can be subsequently replaced.

KB Kilobyte, or one-thousand bytes.

line buffer A buffer located in the cache array that can temporarily hold the

contents of an entire cache line. It is loaded with the contents of

a cache line when a cache hit occurs.

line fill A transfer of the contents of the instruction or data line buffer

into the appropriate cache.

line transfer A transfer of an aligned, se quentially addressed 4-word or 8-

word quantity (instructions or data) across the PLB interface.

The transfer can be from the PLB slave (read) or to the PLB slave

(write).

little endian A memory byte ordering where the address of an item

corresponds to the least-significant byte.

logical address Synonym for effective address.

MB Megabyte, or one-million bytes.

memory Collectively, cache memory and system memory.

miss An indication that requested information does not exist in the

accessed cache array, the associated fill buffer, or on the

corresponding OCM interface.

14 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 15

OEA The PowerPC operating-environment architecture, which

defines the memory-management model, supervisor-level

registers and instructions, synchronization requirements, the

exception model, and the time-base resources as seen by

supervisor programs.

on chip In system-on-chip implementations, this indicates on the same

FPGA chip as the processor core, but external to the processor

core.

pending As applied to interrupts, this indicates that an exception

occurred, but the interrupt is disabled. The interrupt occurs

when it is later enabled.

physical address The address used to access physically-implemented memory.

This address can be translated from the ef fective address. When

address translation is not used, this address is equal to the

effective address.

PLB Processor local bus.

privileged mode The operating mode typically used by system software.

Privileged operations are allowed and software can access all

registers and memory.

R

problem state Synonym for user mode.

process A program (or portion of a prog ram) and any data required for

the program to run.

real address Synonym for physical address.

scalar Individual data objects and instructions. Scalars are of arbitrary

size.

set To write a bit value of 1.

sleep A state in which the PowerPC 405 processor clock is prevented

from toggling. The execution state of the PowerPC 405 does not

change when in the sleep state.

sticky A bit that can be set by software, but cleared only by the

processor. Alternatively, a bit that can be cleared by software,

but set only by the processor.

string A sequence of consecutive bytes.

supervisor state Synonym for privileged mode.

system memory Physical memory installed in a computer system external to the

processor core, such RAM, ROM, and flash.

tag As applied to caches, a set of address bits used to uniquely

identify a specific cache line within a congruence class. As

applied to TLBs, a set of address bits used to uniquely identify

a specific entry within the TLB.

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 15

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 16

R

Preface: About This Guide

UISA The PowerPC user instruction-set architecture, which defines

the base user-level instruction set, registers, data types, the

memory model, the programming model, and the exception

model as seen by user programs.

user mode The operatin g mode typically used by application software.

Privileged operations are not allowed in user mode, and

software can access a restricted set of registers and memory.

VEA The PowerPC virtual-environment architecture, which defines

a multi-access memory model, the cache model, cache-control

instructions, and the time-base resources as seen by user

programs.

virtual address An intermediate address used to translate an effective address

into a physical address. It consists of a process ID and the

effective address. It is only used when address translation is

enabled.

wake up The transition of the PowerPC 405 out of the sleep state. The

PowerPC 405 p rocesso r clock begin s toggling and the execution

state of the PowerPC 405 advances from that of the sleep state.

word Four bytes, or 32 bits.

16 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 17

R

Introduction to the

PowerPC 405 Processor

The PowerPC 405 is a 32-bit implementation of the PowerPC embedded-environment

architecture that is derived from the PowerPC architecture. Specifically, the PowerPC 405 is

an embedded PowerPC 405D5 (for Virtex-II Pro) or 405F6 (for Virtex-4) processor core. Th e

term processor block is used throughout this document to refer to the combination of a

PPC405D5 or PPC405F6 core, on-chip memory logic (OCM) , an APU controller (Virtex-4

only), and the gasket logic and interface.

The PowerPC architecture provides a software model that ensures compatibility between

implementations of the PowerPC family of microprocessors. The PowerPC architecture

defines parameters that guarantee compatible processor implementations at the

application-program level, allowing broad flexibility in the development of derivative

PowerPC implementations that meet specific market requirements.

Chapter 1

This chapter provides an overview of the PowerPC architecture and an introduction to the

features of the PowerPC 405 core. The following topics are included:

x “PowerPC Architecture”

x “PowerPC 405 Software Features”

x “PowerPC 405 Hardware Organization”

x “PowerPC 405 Performance”

PowerPC Architecture

The PowerPC architect ure is a 64 -bit ar chitectur e with a 32-bit subset. The various fea tures

of the PowerPC architecture are defined at three levels. This layering provides flexibility

by allowing degrees of software compatibility across a wide range of implementations. For

example, an implementation such as an embedded controller can support the user

instruction set, but not the memory management, exception, and cache models where it

might be impractical to do so.

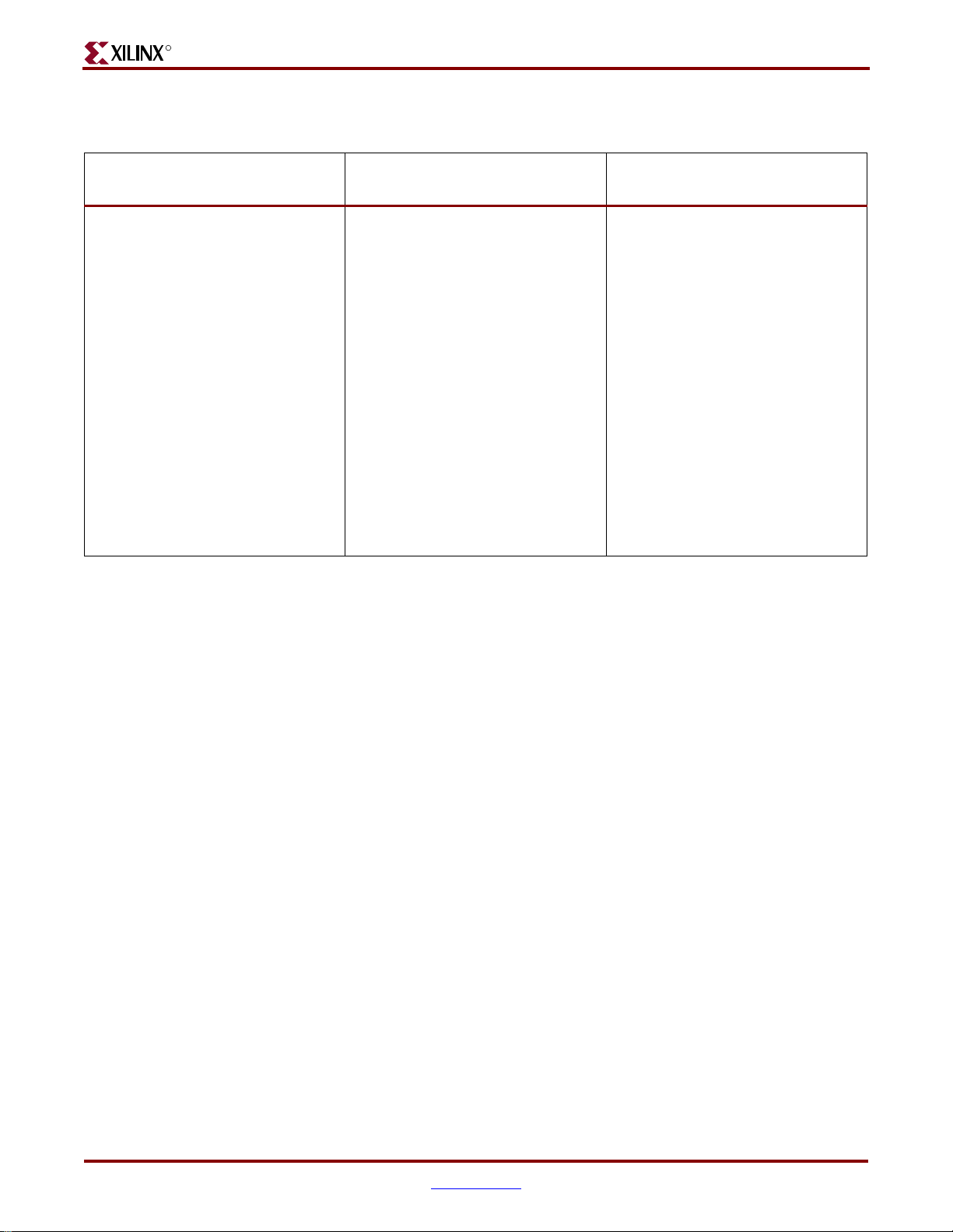

The three levels of the PowerPC architecture are defined in Table 1-1.

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 17

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 18

R

Table 1-1: Three Levels of PowerPC Architecture

Chapter 1: Introduction to the PowerPC 405 Processor

User Instruction-Set Architecture

(UISA)

x

Defines the architecture level to

which user-level (sometimes

referred to as problem state)

software should conform

x Defines the base user-level

instruction set, user-level

registers, data types, floatingpoint memory conventions,

exception model as seen by user

programs, memory model, and

the programming model

Note: All PowerPC implementations

adhere to the UISA.

The PowerPC architecture requir es that all PowerPC implementations adhere to the UISA,

offering compatibility among all PowerPC application programs. However, different

versions of the VEA and OEA are permitted.

Virtual Environment Architecture

(VEA)

x Defines additional user-level

functionality that falls outside

typical user-level software

requirements

x Describes the memory model for

an environment in which

multiple devices can access

memory

x Defines aspects of the cache

model and cache-control

instructions

x Defines the time-base resources

from a user-level perspective

x

Note: Implementations that conform to

the VEA level are guaranteed to conform

to the UISA level.

Operating Environm ent

Architecture (OEA)

x

Defines supervisor-level

resources typically required by

an operating system

x Defines the memory-

management model, supervisorlevel registers, synchronization

requirements, and the exception

model

x Defines the time-base resources

from a supervisor-level

perspective

Note: Implementation s that conform to

the OEA level are guaranteed to confor m

to the UISA and VEA levels.

Embedded applications written for the PowerPC 405 are compatible with other PowerPC

implementations. Privileged software generally is not compatible. The migration of

privileged software from the PowerPC architecture to the PowerPC 405 is in many cases

straightforward because of the simplifications made by the Pow e rPC embed d e d environment architecture. Refer to the PowerPC Processor Reference Guide for more

information on programming the PowerPC 405.

PowerPC Embedded-Environment Architecture

The PowerPC 405 is an implementation of the PowerPC embedded-environment

architecture. This architectur e is optimized for embedded controllers and is a forerunner to

the PowerPC Book-E architecture. The PowerPC embedded-environment architecture

provides an alternative definition for certain features specified by the PowerPC VEA and

OEA. Implementations that adhere to the PowerPC embedded-environment architecture

also adhere to the PowerPC UISA. PowerPC embedded-envir onment processors are 32 -bit

only implementations and thus do not include the special 64-bit extensions to the PowerPC

UISA. Also, floating-point support can be provided either in hardware or software by

PowerPC embedded-environment processors.

The following are features of the PowerPC embedded-environment architecture:

x Memory management optimized for embedded software environments.

x Cache-management instructions for o p timizing performance and memory control in

complex applications that are graphically and numerically intensive.

x Storage attributes for controlling memory-system behavior.

18 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 19

x Special-purpose registers for controlling the use of debug resources, timer resources,

interrupts, real-mode storage attributes, memory-management facilities, and other

architected processor resources.

x A device-control-register address space for mana ging on-chip peripherals such as

memory controllers.

x A dual-level interrupt structure and interrupt-control instructions.

x Multiple timer resources.

x Debug resources that enable hardware-debug and software-debug functions such as

instruction breakpoints, data breakpoints, and program single-stepping.

Virtual Environment

The virtual environment defines architectural features that enable application programs to

create or modify code, to manage storage coherency, and to optimize memory-access

performance. It defines the cache and memory models, the timekeeping resources from a

user perspective, and resources that are accessible in user mode but are primarily used by

system-library routines. The following summarizes the virtual-environment features of the

PowerPC embedded-environment architecture:

x Storage model:

i Storage-control instructions as defined in the PowerPC virtual-environment

architecture. These instructions are used to manage instruction caches and data

caches, and for synchronizing and ordering instruction execution.

i Storage attributes for controlling memory-system behavior. These are: write-

through, cacheability, memory coherence (optional), guarded, and endian.

i Operand-placement requirements and their effect on performance.

x The time-base function as defined by the PowerPC virtual-environment architecture,

for user-mode read access to the 64-bit time base.

R

Operating Environment

The operating environment describes features of the architecture that enable operating

systems to allocate and manage storage, to handle errors encountered by application

programs, to support I/O devices, and to provide operating-system services. It specifies

the resources and mechanisms that require privileged access, including the memoryprotection and address-translation mechanisms, the exception-handling model, and

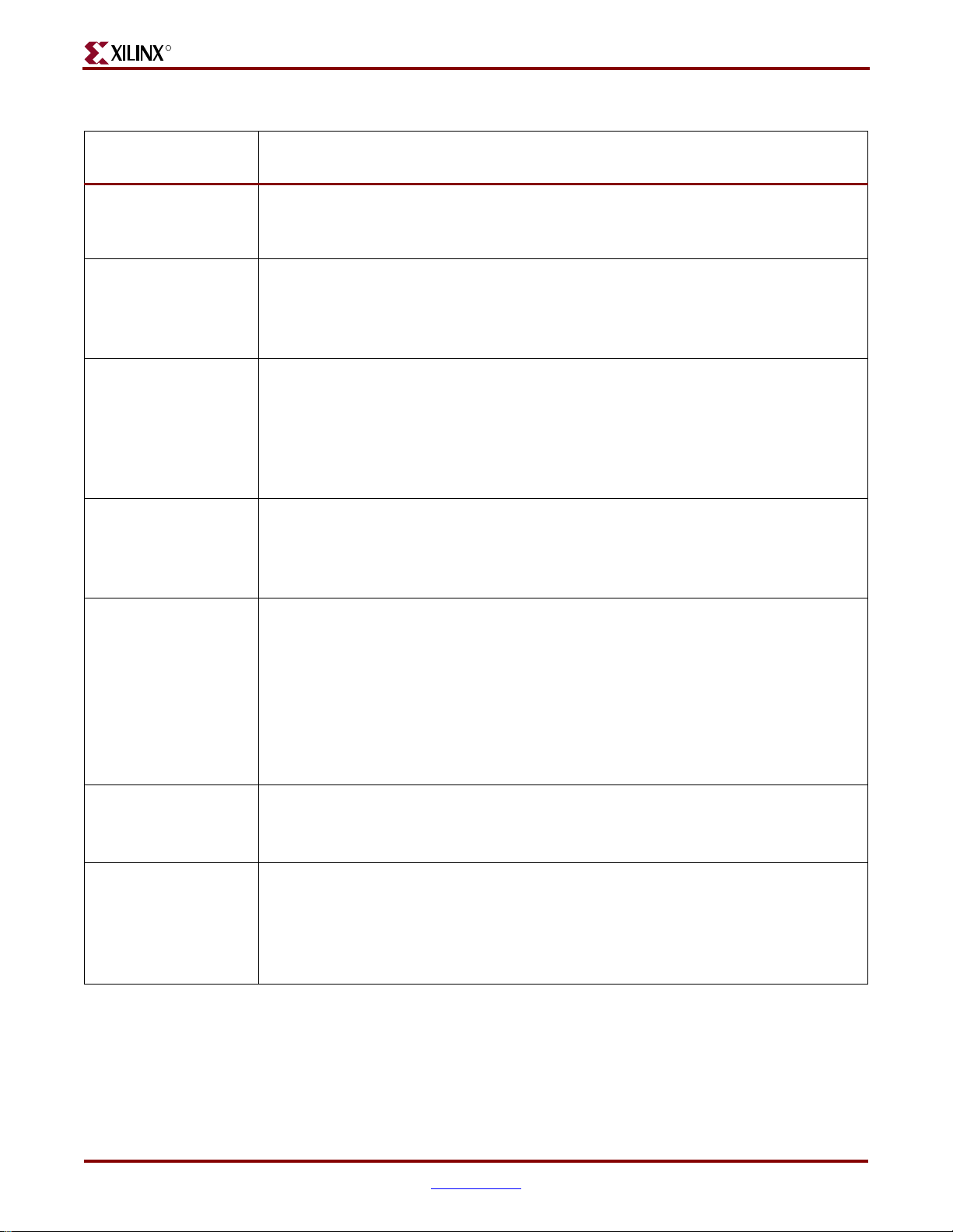

privileged timer resources. Table 1-2 summarizes the operating-environment features of

the PowerPC embedded-environment architecture.

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 19

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 20

R

Chapter 1: Introduction to the PowerPC 405 Processor

Table 1-2: OEA Features of the PowerPC Embedded-Environment Architecture

Operating

Environment

Features

Register model x Privileged special-purpose registers (SPRs) and instructions for accessing those

registers

x Device control registers (DCRs) and instructions f or a ccessing those registers

Storage model

x Privileged cache-management instructions

x Storage-attribute controls

x Address transl ation and memory protection

x Privileged TLB-management instructions

Exception model

x Dual-level interrupt structure supporting various exception types

x Specification of interrupt priorities and masking

x Privileged SPRs for controlling an d han d ling exceptions

x Interrupt-control instructions

x Specification of how partially executed instructions are handled when an interrupt

occurs

Debug model

x Privileged SPRs for controlling debug modes and debug events

x Specification for seven types of debug events

x Specification for allowing a debug event to cause a reset

x The ability of the de bug mechanism to freeze the timer resources

Time -keeping model

Synchronization

requirements

Reset and initialization

requirements

x 64-bit t i me base

x 32-bit decrementer (the programmable-interval timer)

x Three timer-event interrupts:

i Programmable-interval timer (PIT)

i Fixed-interval timer (FIT)

i Watchdog timer (WDT)

x Privileged SPRs for controlling the time r resources

x The ability to freeze the timer resources using the debug mechanism

x Requirements for special registers and the TLB

x Requirements for instruction fetch and for data access

x Specifications for context synchronizat ion and execution sync hronization

x Specification for two internal mechanisms that can cause a reset:

i Debug-control register (DBCR)

i Timer-control register (TCR)

x Contents of processor resources after a reset

x The software-initialization requirements, including an initialization co de exa mple

20 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 21

PowerPC 405 Software Features

The PowerPC 405 processor core is an implementation of the PowerPC embeddedenvironment architecture. The pr ocessor provides fixed-point embedded applications with

high performance at low power consumption. It is compa tible with the PowerPC UISA.

Much of the PowerPC 405 VEA and OEA support is also available in implementations of

the PowerPC Book-E architecture. Key software features of the PowerPC 405 include:

x A fixed-point execution unit fully compliant with the PowerPC UISA:

i 32-bit architecture, containing thirty-two 32-bit general purpose registers (GPRs).

x PowerPC embedded-environment architecture extensions providing addi tional

support for embedded-systems applications:

i True little-endian operation

i Fle xible memory management

i Multiply-accumulate instructions for computational ly intensive applications

i Enhance d de bu g ca pab i l iti e s

i 64-bit time base

i 3 timers: programmable interval timer (PIT), fixed interval timer (FIT), and

watchdog timer (all are synchronous with the time base)

x Performance-enhancing features, including:

i Static branch prediction

i Five-stage pipeline with single-cycle execution of most instructions, including

loads and stores

i Multiply-accumulate instructions

i Hardware multiply/divide for faster integer arithmetic (4-cycle multiply, 35-cycle

divide)

i Enhanced string and multiple-word handling

i Support for unaligned loads and unaligned stores to cache arrays, main memory,

and on-chip memory (OCM)

i Minimized interrupt latency

x Integrated instruction-cache:

i 16 KB, 2-way set associative

i Eight words (32 bytes) per cache line

i Fetch line buffer

i Instruction-fetch hits are supplied from the fetch line buffer

i Programmable prefetch of next-sequential line into the fetch line buffer

i Programmable prefetch of non-cacheable instructions: full line (eight words) or

half line (four words)

i Non-blocking during fetch line fill s

x Integrated data-cache:

i 16 KB, 2-way set associative

i Eight words (32 bytes) per cache line

i Read and write line buffers

i Load and store hits are supplied from/to the line buffers

R

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 21

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 22

R

i Write-back and write-through support

i Programmable load and store cache line allocation

i Operand forwarding during cache line fills

i Non-blocking during cache line fills and flushes

Chapter 1: Introduction to the PowerPC 405 Processor

x Support for on-chip memory (OCM) that can provide memory-access performance

identical to a cache hit

x Flexible memory management:

i Translation of the 4 GB logical-address space into the physical- address space

i Independent control over instruction translation and protection, and data

translation and pro tect io n

i Page-level access control using the translation mechanism

i Software control over the page-replacement strategy

i Write-through, cachea bility, user-defined 0, guarded, and endian (WIU0GE)

storage-attribute control for each virtual-memory region

i WIU0GE storage-attribute control for thirty-two 128 MB regions in real mode

i Additional protection control using zones

x Enhanced debug support with logical operators:

i Four instruction-address compares

i Two data-address compares

i Tw o data-value compares

i JTAG instruction for writing into the instruction cache

i Forward and backward instruction tracing

x Advanced power management support

The following sections describe the software resources available in the PowerPC 405. Refer

to the PowerPC Processor Referenc e Guide for more information on using these resources.

Privilege Modes

Software running on the PowerPC 405 can do so in one of two privilege modes: privileged

and user.

Privileged Mode

Privileged mode allows programs to access all registers and execute al l instructions

supported by the processor. Normally, the operating system and low-level device drivers

operate in this mode.

User Mode

User mode restricts access to some registers and instructions. Normally, application

programs operate in this mode.

Address Tr anslation Modes

The PowerPC 405 also supports two modes of address translation: real and virtual.

22 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 23

Real Mode

In real mode, programs address physical memory directly.

Virtual Mode

In virtual mode, programs address virtual memory and virtual-memory addresses are

translated by the processor into physical-memory addresses. This allows programs to

access much larger address spaces than might be implemented in the system.

Addressing Modes

Whether the PowerPC 405 is running in real mode or virtual mode, data addressing is

supported by the load and store instructions using one of the following addressing modes:

x Register-indirect with immediate index — A base address is stored in a register, and a

displacement from the base address is specified as an immediate value in the

instruction.

x Register-indirect with index — A base address is stored in a register, and a

displacement from the base address is stored in a secon d register.

x Register indirect — The data address is stored in a register.

R

Instructions that use the two indexed forms of addressing also allow for automatic updates

to the base-address register. With these instruction forms, the new data address is

calculated, used in the load or store data access, and stored in the base-address register.

With sequential instruction execution, the next-instruction address is calculated by adding

four bytes to the current-instruction address. In the case of branch instructions, the nextinstruction address is determined using one of four branch-addressing modes:

x Branch to relative — The next-instruction address is at a location relative to the

x Branch to absolute — The next-instruction address is at an absolute location in

x Branch to link register — The next-instruction address is stored in the link register.

x Branch to count register — The next-instruction address is stored in the count register.

Data Types

PowerPC 405 instructions support byte, halfword, and word operands. Multiple-wo rd

operands are supported by the load/store multiple instructions and byte strings are

supported by the load/store string instructions. Integer data are either signed or unsigned,

and signed data is represented using two’s-complement format.

The address of a multi-byte operand is determined using the lowest memory address

occupied by that operand. For example, if the four bytes in a word operand occupy

addresses 4, 5, 6, an d 7, the wor d add res s is 4. The Po werPC 40 5 su pports both bi g-end ian

(an operand’s most significant byte is at the lowest memory address) and little-endian (an

operand’s l east significant byte is at the lowest memory address) addressing.

current-instruction address.

memory.

Register Set Summary

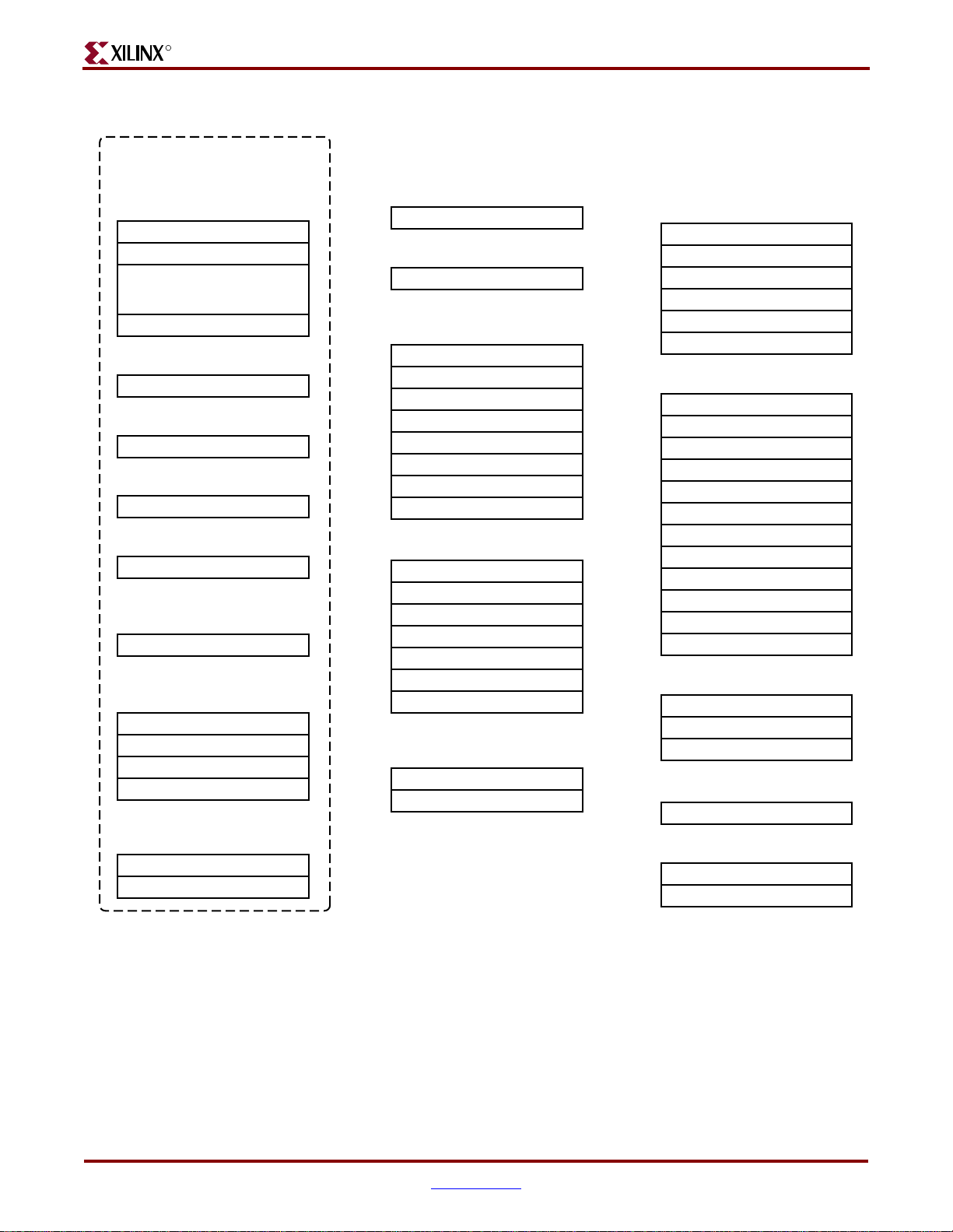

Figure 1-1 shows the registers contained in the PowerPC 405. Descriptions of the registers

are in the following sections.

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 23

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 24

R

Chapter 1: Introduction to the PowerPC 405 Processor

User Registers

General-Purpose Registers

r0

r1

.

.

.

r31

Condition Register

CR

Fixed-Point Exception Register

XER

Link Register

LR

Count Register

CTR

User-SPR General-Purpose

Registers

USPRG0

SPR General-Purpose

Registers

Time-Base Registers

(read only)

SPRG4

SPRG5

SPRG6

SPRG7

(read only)

TBU

TBL

Privileged Registers

Machine-State Register

MSR

Core-Configuration Register

CCR0

SPR General-Purpose

Registers

SPRG0

SPRG1

SPRG2

SPRG3

SPRG4

SPRG5

SPRG6

SPRG7

Exception-Handling Registers

EVPR

ESR

DEAR

SRR0

SRR1

SRR2

SRR3

Memory-Management

Registers

PID

ZPR

Storage-Attribute Control

Registers

DCCR

DCWR

ICCR

SGR

SLER

SU0R

Debug Registers

DBSR

DBCR0

DBCR1

DAC1

DAC2

DVC1

DVC2

IAC1

IAC2

IAC3

IAC4

ICDBR

Timer Registers

TCR

TSR

PIT

Processor-Version Register

PVR

Time-Base Registers

TBU

TBL

UG018_36_102401

Figure 1-1: PowerPC 4 05 Regist ers

General-Purpose Registers

The processor contains thirty-two 32-bit general-purpose registers (GPRs), identified as r0

through r31. The contents of the GPRs are read from memory using load instructions and

written to memory using store instructions. Computational instructions of ten read

operands from the GPRs and write their results in GPRs. Other instructions move data

between the GPRs and other registers. GPRs can be accessed by all software.

24 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 25

Special-Purpose Registers

The processor contains a number of 32-bit special-purpose registers (SPRs). SPRs provide

access to additional processor resources, such as the count register , the link register , debug

resources, timers, interrupt registers, and others. Most SPRs are accessed only by

privileged software, but a few, such as the count register and link register , are accessed by

all software.

Machine-State Register

The 32-bit machine-state register (MSR) contains fields that control the operating s tate of the

processor. This register can be accessed only by privileged software.

Condition Register

The 32-bit condition register (CR) contains eight 4-bit fields, CR0–CR7. The values in the CR

fields can be used to control conditional branching. Arithmetic instructions can set CR0

and compare instructions can set any CR field. Additional instructions are provided to

perform logical operations and tests on CR fields and bits within the fiel ds. The CR can be

accessed by all software.

R

Device Control Registers

The 32-bit device control registers (not shown) are used to configure, control, and report

status for various external devices that are not part of the PowerPC 405 processor. The

OCM controllers are examples of devices that contain DCRs. Although the DCRs are not

part of the PowerPC 405 implementation, they are accessed using the mtdcr and mfdcr

instructions. The DCRs can be accessed only by privileged software.

PowerPC 405 Hardware Organization

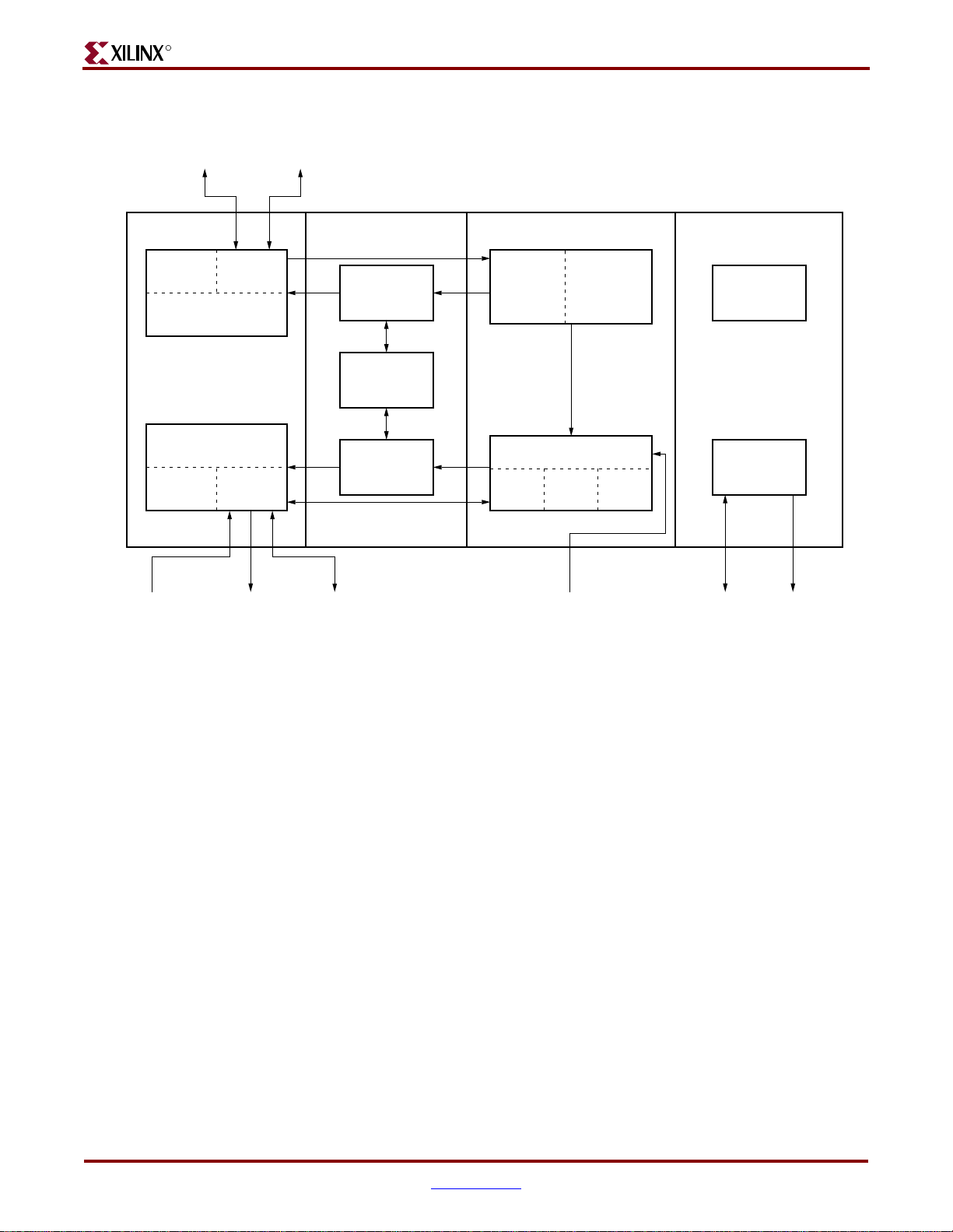

As shown in Figure 1-2, the PowerPC 405 processor contains the following elements:

x A 5-stage pipeline consisting of fetch, decode, execute, write-back, and load write-

back stages

x A virtual-memory-management unit that supports multiple page sizes and a variety

of storage-protection attr ibutes and access-control options

x Separate instruction-cache and data-cache units

x Debug support, including a JTAG interface

x Three programmable timers

The following sections provide an overview of each element. Refer to the PowerPC

Processor Reference Guide for more information on how software interacts with these

elements.

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 25

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 26

R

Chapter 1: Introduction to the PowerPC 405 Processor

PLB Master

Read Interface

I-Cache

Array

Instruction-Cache

I-Cache

Controller

Unit

Cache Units

Data-Cache

Unit

D-Cache

Array

D-Cache

Controller

Instruction

OCM

Instruction

Shadow-TLB

(4-Entry)

Unified TLB

(64-Entry)

Data

Shadow-TLB

(8-Entry)

Fetch

and

Decode

Logic

32x32

GPR

CPUMMU

3-Element

Fetch Queue

Execute Unit

ALU MAC

Timers

Timers

and

Debug

Debug

Logic

PLB Master

Read Interface

a. Figure 1-2 is specific to PPC405D5.

PLB Master

Write Interface

Central-Processing Unit

The PowerPC 405 central-processing unit (CPU) implements a 5-stage instruction pipeline

consisting of fetch, decode, execute, write-back, and load write-back stages.

The fetch and decode logic sends a steady flow of instructions to the execute unit. All

instructions are decoded before they are forwarded to the execute unit. Instructions are

queued in the fetch queue if execution stalls. The fetch queue consists of three elements:

two prefetch buffers and a decode buffer. If the prefetch buffers are empty instructions

flow directly to the decode buffer.

Up to two branches are processed simultaneo usly by the fetch and decode logic. If a branch

cannot be resolved prior to execution, the fetch and decode logic pr edicts how that branch

is resolved, causing the processor to speculatively fetch instructions from the predicted

path. Branches with negative-address displacements are predicted as taken, as are

branches that do not test the condition register or count register. The default prediction can

be overridden by software at assembly or compile time.

The PowerPC 405 has a single-issue execute unit containing the general-purpose register

file (GPR), arithmetic-logic unit (ALU), and the multiply-accumulate unit (MAC). The

GPRs consist of thirty-two 32-bit registers that are accessed by the execute unit using three

Data

OCM

External-Interrupt

Controller Interface

Figure 1-2: PowerPC 405 Organization

JTAG

a

Instruction

Trace

UG018_35_102401

26 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 27

read ports and two write ports. During the decode stage, data is read out of the GPRs for

use by the execute unit. During the write-back stage, results are written to the GPR. The

use of five read/write ports on the GPRs allows the processor to execute load/store

operations in parallel with ALU and MAC operations.

The execute unit supports all 32-bit PowerPC UISA integer instructions in hardware, and is

compliant with the PowerPC embedded-environment architecture specification. Floatingpoint operations are not supported.

The MAC unit supports implementation-specific multiply-accumulate instructions and

multiply-halfword instructions. MAC instructions operate on either signed or unsigned

16-bit operands, and they store their results in a 32-bit GPR. These instructions can

produce results using either modulo arithmetic or saturating arithmetic. All MAC

instructions have a single cycle throughput.

Exception Handling Logic

Exceptions are divided into two classes: critical and noncritical. The PowerPC 405 CPU

services exceptions caused by error conditions, the internal timers, debug events, and the

external interrupt controller (EIC) interface. Across the two classes, a total of 19 possible

exceptions are supported, including the two provided by the EIC interface.

R

Each exception class has its own pair of save/restore registers. SRR0 and SRR1 are used for

noncritical interrupts, and SRR2 and SRR3 are used for critical interrupts. The exceptionreturn address and the machine state are written to these registers when an exception

occurs, and they are automatically restored when an interrupt handler exits using the

return-from-interrupt (rfi) or r et urn- from critical-interrupt (rfci) instruction. Use of

separate save/restore registers allows the PowerPC 405 to handle critical interrupts

independently of noncritical interrupts.

Memory Management Unit

The PowerPC 405 supports 4 GB of flat (non-segmented) address space. The memorymanagement unit (MMU) provides address translation, protection functions, and storageattribute control for this address space. The MMU supports demand-paged virtual

memory using multiple page sizes of 1 KB, 4 KB, 16 KB, 64 KB, 256 KB, 1 MB, 4 MB and

16 MB. Multiple page sizes can improve memory efficiency and minimize the number of

TLB misses. When supported by system software, the MMU provides the following

functions:

x Translation of the 4 GB logical-address spac e into a physical-address space.

x Independent enabling of instruction translati on and protection from that of data

translation and pro tect io n .

x Page-level access control using the translation m e chanism.

x Software control over the page-replacement strategy.

x Additional protection control using zones.

x Storage attributes for cache policy and speculative memory-access control.

The translation look-aside buffer (TLB) is used to control memory translation and

protecti on. Each o ne of i ts 6 4 en trie s s peci fie s a page translation. It is fully associative, and

can simultaneously hold translations for any combination of page sizes. To prevent TLB

contention between data and instruction accesses, a 4-entry instruction and an 8-entry data

shadow-TLB are maintained by the processor transparently to software.

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 27

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 28

R

Software manages the initialization and replacement of TL B entries. The PowerPC 405

includes instructions for managing TLB entries by software running in privileged mode.

This capability gives significant control to system software over the implementation of a

page replacement strategy. For example, software can reduce the potential for TLB

thrashing or delays associated with TLB-entry replacement by reserving a subset of TLB

entries for globally accessible pages or critical pages.

Storage attributes are provided to control access of memory regions. When memory

translation is enabled, storage attributes are maintained on a page basis and read from the

TLB when a memory access occurs. When memory translation is disabled, storage

attributes are maintained in storage-attribute control registers. A zone-protection register

(ZPR) is provided to allow system software to override the TLB access controls without

requiring the manipulation of individual TLB entries. For example, the ZPR can provide a

simple method for denying read access to certain application programs.

Instruction and Data Caches

The PowerPC 405 accesses memory through the instruction-cache unit (ICU) and datacache unit (DCU). Each cache unit includes a PLB-master interface, cache arrays, and a

cache controller . Hits into the instruction cache and data cache appear to the CPU as singlecycle memory accesses. Cache misses are h andled as requests over the PLB bus to another

PLB device, such as an external-memory controller.

Chapter 1: Introduction to the PowerPC 405 Processor

The PowerPC 405 implements separate instruction-cache and data-cache arrays. Each is 16

KB in size, is two-way set-associative, and operates using 8 word (32 byte) cache lines. Th e

caches are non-blocking, allowing the PowerPC 405 to overlap instruction execution with

reads over the PLB (when cache misses occur).

The cache controllers replace cache lines according to a least-recently used (LRU)

replacement policy. When a cache line fill occurs, the most-recently accessed line in the

cache set is retained and the other line is replaced. The cache controller updates the LRU

during a cache line fill.

The ICU supplies up to two instructions every cycle to the fetch and decode unit. The ICU

can also forward instructions to the fetch and decode unit during a cache line fill,

minimizing execution stalls caused by instruction-cache misses. When the ICU is accessed,

four instructions are read from the appropriate cache line and placed temporarily in a line

buffer . Subsequent ICU accesses check this line buf fer for the requested instruction prior to

accessing the cache array. This allows the ICU cache array to be accessed as little as once

every four instructions, significantly reducing ICU power cons umption.

The DCU can independently process load/store operations and cache-control instructions.

The DCU can also dynamically reprioritize PLB requests to reduce the length of an

execution stall. For example, if the DCU is busy with a low-priority request and a

subsequent storage operation requested by the CPU is stalled, the DCU automatically

increases the priority of the current (low-priority) request. The current request is thus

finished sooner, allowing the DCU to process the stalled request sooner. The DCU can

forward data to the execute unit during a cache line fill, further minimizing execution stalls

caused by data-cache misses.

Additional features allow programmers to tailor data-cache performanc e to a specific

application. The DCU can function in write-back or write-through mode, as determined by

the storage-control attributes. Loads and stor es that d o not allocate cache lines can also be

specified. Inhibiting certain cache line fills can reduce potential pipeline sta lls and

unwanted external-bus traffic.

28 www.xilinx.com PowerPC™ 405 Processor Block Reference Gu id e

1-800-255-7778 UG018 (v2.0) August 20, 2004

Page 29

Timer Resources

The PowerPC 405 contains a 64-bit time base and three timers. The time base is

incremented synchronously using the CPU clock or an external clock source. The three

timers are incremented synchronously with the time base. The three timers supported by

the PowerPC 405 are:

x Programmable Interval Timer

x Fixed Interval Timer

x Watch dog Timer

Programmable Interval Timer

The pr ogrammable interval timer (PIT) is a 32-bit register that is decremented at the time-base

increment frequency. The PIT register is loaded with a delay value. When the PIT count

reaches 0, a PIT interrupt occurs. Optionally , the PIT can be programmed to automatically

reload the last delay value and begin decrementing again.

Fixed Interval Timer

The fixed interval timer (FIT) causes an interrupt when a selected bit in the time-base register

changes from 0 to 1. Programmers can select one of four predefined bits in the time-base

for triggering a FIT interrupt.

R

Debug

Watchdog Timer

The watchdog timer causes a hardware reset when a selected bit in the time-base register

changes from 0 to 1. Programmers can select one of four predefined bits in the time-base

for triggering a reset, and the type of reset can be defined by the programmer.

The PowerPC 405 debug resources include special debug modes that support the various

types of debugging used during hardware and software development. These are:

x Internal-debug mode for use by ROM monitors and software debuggers

x External-debug mode for use by JTAG debuggers

x Debug-wait mode, which allows the servicing of interrupts while the processor appears

to be stopped

x Real-time trace mode, which supports event triggering for real-time tracing

Debug events are supported that allow developers to manage the debug process. Debug

modes and debug events are controlled using debug registers in the processor. The debug

registers are accessed either through software running on the processor or through the

JTAG port.

The debug modes, events, controls, and interfaces provide a powerful combination of

debug resour ces f or hardw are and software development tools.

PowerPC 405 Interfaces

The PowerPC 405 provides the following set of interfaces that support the attachment of

cores and user logic:

x Processor local bus interface

PowerPC™ 405 Processor Block Reference Guide www.xilinx.com 29

UG018 (v2.0) August 20 , 20 04 1-800-255-7778

Page 30

R

x Device control register interface

x Clock and power management interface

x JTAG port interface

x On-chip interrupt controller interface

x On-chip memory controller interface

Processor Local Bus

The processor local bus (PLB) i nterface provides a 32-bit address and three 64-bit data buses

attached to the instruction-cache and data-cache units. T wo of the 64-bit buses are attached

to the data-cache unit, one supporting read operations and the other supportin g write

operations. The third 64-bit bus is attached to the instruction-cache unit to support

instruction fetching.

Device Control Register

The device control register (DC R) bus interface supports the attachment of on-chip registers

for device control. Software can access these registers using the mfdcr and mtdcr

instructions.

Chapter 1: Introduction to the PowerPC 405 Processor

Clock and Power Management

The clock and power-management interface supports several methods of clock distribution

and power management.

JTAG Port

The JTAG port interface supports the att achment of external debug tools. Using the JTAG

test-access port, a debug tool can single-step the processor and examine internal-processor

state to facilitate software debugging.

On-Chip Interrupt Controller

The on-chip interrupt controller interface is an external interrupt controller that combines

asynchronous interrupt inputs from on-chip and off-chip sources and presents them to the

core using a pair of interrupt signals (critical and noncritical). Asynchronous interrupt

sources can include external signals, the JTAG and debug units, and any other on-chip

peripherals.

On-Chip Memory Controller

An on-chip memory (OCM) interface supports the attachment of additional memory to the

instruction and data caches that can be accessed at performance levels matching the cache

arrays.

PowerPC 405 Performance